Page 1

Neuron Assembly

Language Reference

Guide

Develop assembly language functions using the

Neuron® Assembly Language.

078-0399-01B

Page 2

Echelon, LONWORKS, LONMARK, NodeBuilder, LonTalk, Neuron,

3120, 3150, ShortStack, LonMaker, and the Echelon logo are

trademarks of Echelon Corporation that may be registered in

the United States and other countries.

Other brand and product names are trademarks or

registered trademarks of their respective holders.

Neuron Chips and other OEM Products were not designed

for use in equipment or systems, which involve danger to

human health or safety, or a risk of property damage and

Echelon assumes no responsibility or liability for use of the

Neuron Chips in such applications.

Parts manufactured by vendors other than Echelon and

referenced in this document have been described for

illustrative purposes only, and may not have been tested

by Echelon. It is the responsibility of the customer to

determine the suitability of these parts for each

application.

ECHELON MAKES AND YOU RECEIVE NO WARRANTIES OR

CONDITIONS, EXPRESS, IMPLIED, STATUTORY OR IN ANY

COMMUNICATION WITH YOU, AND ECHELON SPECIFICALLY

DISCLAIMS ANY IMPLIED WARRANTY OF MERCHANTABILITY

OR FITNESS FOR A PARTIC ULAR PURPOSE.

No part of this publication may be reproduced, stored in a

retrieval system, or transmitted, in any form or by any means,

electronic, mechanical, photocopying, recording, or

otherwise, without the prior written permission of Echelon

Corporation.

Printed in the United States of America.

Copyright © 2006-2014 Echelon Corporation.

Echelon Corporation

www.echelon.com

Page 3

Welcome

Echelon’s Neuron® assembly language is the symbolic programming language for

Series 3100, Series 5000, and Series 6000 Neuron Chips and Smart Transceivers.

You can write a Neuron assembly language function or program that interacts

with a Neuron C application program to provide L

or existing smart devices. The Neuron assembly language is not intended as a

general programming language for L

to optimize new or existing Neuron C applications.

ONWORKS

ONWORKS devices, but should be used only

®

networking for new

This document describes the Neuron assembly language. The Neuron assembly

language can be used with any programmable Series 3100 device (Neuron 3120

Chip, FT 3120 Smart Transceiver, PL 3120 Smart Transceiver, Neuron 3150

Chip, FT 3150 Smart Transceiver, PL 3150 Smart Transceiver, and PL 3170™

Smart Transceiver) and with any programmable Series 5000 device (FT 5000

Smart Transceiver and Neuron 5000 Processor) or Series 6000 device. Where

applicable, this document identifies differences in the Neuron assembly language

that are specific to a particular device series.

Audience

This document assumes that you have a good understanding of general assembly

language programming concepts and techniques. It also assumes that you are

familiar with the Neuron C programming language and L

development. In addition, a general understanding of the Series 3100, Series

5000, or Series 6000 architecture is required.

Related Documentation

The following manuals are available from the Echelon Web site

(www.echelon.com

applications for Neuron Chip or Smart Transceiver devices:

• Series 5000 Chip Data Book (005-0199-01A). This manual provides

detailed technical specifications on the electrical interfaces, mechanical

interfaces, and operating environment characteristics for the Neuron

5000 Processors and FT 5000 Smart Transceivers.

) and provide additional information that can help you develop

ONWORKS device

®

®

• Series 6000 Chip Data Book (005-0230-01). This manual provides

detailed technical specifications on the electrical interfaces, mechanical

interfaces, and operating environment characteristics for the Neuron

6000 Processors and FT 6000 Smart Transceivers.

• I/O Model Reference for Smart Transceivers and Neuron Chips (078-

0392-01C). This manual describes the I/O models that are available for

Series 3100, Series 5000, and Series 6000 devices.

• FT 3120 / FT 3150 Smart Transceiver Data Book (005-0139-01D). This

manual provides detailed technical specifications on the electrical

interfaces, mechanical interfaces, and operating environment

characteristics for the FT 3120

Neuron Assembly Language Reference iii

®

and FT 3150® Smart Transceivers.

Page 4

• Introduction to the LONWORKS Platform (078-0391-01A). This manual

provides an introduction to the ISO/IEC 14908 (ANSI/CEA-709.1 and

EN14908) Control Network Protocol, and provides a high-level

introduction to L

ONWORKS networks and the tools and components that

are used for developing, installing, operating, and maintaining them.

• L

ONMARK

®

Application Layer Interoperability Guidelines. This manual

describes design guidelines for developing applications for open

interoperable L

Web site, www.lonmark.org

ONWORKS devices, and is available from the LONMARK

.

• IzoT Commissioning Tool User's Guide ( 078-0514-01). This manual

describes how to use the IzoT Commissioning Tool to design, commission,

monitor and control, maintain, and manage a network.

• IzoT NodeBuilder® FX User’s Guide ( 078-0516-01). This manual

describes how to develop a L

ONWORKS device using the IzoT NodeBuilder

tool.

• Neuron C Programmer’s Guide (078-0002-01I). This manual describes

how to write programs using the Neuron C Version 2.2 programming

language.

• Neuron C Reference Guide (078-0140-01G). This manual provides

reference information for writing programs using the Neuron C Version

2.2 programming language.

• PL 3120 / PL 3150 / PL 3170 Power Line Smart Transceiver Data Book

(005-0193-01A). This manual provides detailed technical specifications

on the electrical interfaces, mechanical interfaces, and operating

environment characteristics for the PL 3120, PL 3150, and PL 3170™

Smart Transceivers.

All of the Echelon documentation is available in Adobe

PDF files, you must have a current version of the Adobe Reader

PDF format. To view the

, which you can

download from Adobe at: www.adobe.com/products/acrobat/readstep2.html

.

iv

Page 5

Table of Contents

Welcome ......................................................................................................... iii

Audience ........................................................................................................ iii

Related Documentation ................................................................................ iii

Introduction ....................................................................................................... 1

Introduction .................................................................................................... 2

Neuron Assembler Tools ................................................................................ 3

Neuron C Compiler for Assembly Programming ................................... 3

Neuron Assembler Command Line Tool ................................................ 3

Command Usage ............................................................................... 4

NAS Command Switches .................................................................. 4

Neuron Librarian Tool ............................................................................ 5

IzoT NodeBuilder Development Tool ..................................................... 6

Assembler Files .............................................................................................. 6

Source Files .............................................................................................. 6

Naming Convention .......................................................................... 6

File Format ........................................................................................ 7

Output Files ............................................................................................. 7

General Neuron Assembly Syntax ................................................................ 8

Labels ....................................................................................................... 9

Assembly Instructions ............................................................................. 9

Operands ................................................................................................ 10

Literal Constants ............................................................................ 10

Symbols ............................................................................................ 11

Expressions ...................................................................................... 11

Comments .............................................................................................. 14

Assembler Directives ................................................................................... 14

Interfacing with Neuron C Programs ......................................................... 14

Neuron Architecture for Neuron Assembly Programming .................. 15

Neuron Architecture .................................................................................... 16

Hardware Resources for Assembly Programs ............................................ 17

CPU Registers ........................................................................................ 17

General-Purpose Registers ............................................................. 18

Pointer Registers ............................................................................. 19

Flag Register ................................................................................... 21

Instruction Pointer .......................................................................... 21

Base-Page Register and Stack Registers ....................................... 21

Stacks ..................................................................................................... 22

Data Stack ....................................................................................... 22

Return Stack ................................................................................... 23

Stack Manipulation ............................................................................... 24

Segments ................................................................................................ 25

Using Neuron Chip Memory ................................................................. 26

Chips with Off-Chip Memory ......................................................... 26

Chips without Off-Chip Memory .................................................... 28

Chips with Auto-tuned Memory ..................................................... 29

Accessing Global and Static Data ......................................................... 30

Addressing Modes ........................................................................................ 30

Immediate .............................................................................................. 30

Absolute .................................................................................................. 30

Direct ...................................................................................................... 31

Neuron Assembly Language Reference v

Page 6

Implicit ................................................................................................... 31

Pointer Direct......................................................................................... 31

Indirect Relative .................................................................................... 31

Indirect Indexed ..................................................................................... 32

DSP Relative .......................................................................................... 32

BP Relative ............................................................................................ 33

BP Indexed ............................................................................................. 33

Indirect ................................................................................................... 33

Relative .................................................................................................. 33

Writing a Neuron Assembly Utility Function .......................................... 35

Overview of Stack-Oriented Programming ................................................ 36

Designing a Neuron Assembly Function .................................................... 37

Interrupt Tasks with Assembly Code ......................................................... 39

Documenting Changes to the Stack ............................................................ 40

Stack-Effect Comments ......................................................................... 41

Multi-Byte Values ........................................................................... 41

Pointer Values ................................................................................. 41

Conditional Values .......................................................................... 41

Showing the Return Stack .............................................................. 42

Stack-Transformation Comments ........................................................ 42

Integrating the Program .............................................................................. 42

Assembling the Program ............................................................................. 43

Linking the Program .................................................................................... 44

Debugging the Program ............................................................................... 44

Interfacing with a Neuron C Application ................................................. 47

Overview ....................................................................................................... 48

Naming Conventions.................................................................................... 48

Function Parameters ................................................................................... 48

Calling Conventions ..................................................................................... 49

Data Representation .................................................................................... 51

Integers, Characters, and Strings ........................................................ 51

Multi-Byte Values .................................................................................. 51

Arrays ..................................................................................................... 52

Structures and Unions .......................................................................... 52

Bitfields .................................................................................................. 52

Calling a Neuron C Function from Assembly Code ................................... 52

Exploring an Example Function in Neuron Assembly .......................... 55

Overview of the Checksum Example .......................................................... 56

Implementing the Checksum Function ...................................................... 56

Including the Assembly Function in a Neuron C Application .................. 57

Neuron Assembly Language Instruction Statements ............................ 59

Overview of the Assembly Language Instructions .................................... 60

ADC (Add with Carry) ................................................................................. 64

ADD (Add) .................................................................................................... 65

ADD_R (Add and Return) ............................................................................ 66

ALLOC (Allocate) ......................................................................................... 67

AND (And) .................................................................................................... 68

AND_R (And and Return)............................................................................ 69

BR (Branch) .................................................................................................. 70

BRC (Branch If Carry) ................................................................................. 71

BRF (Branch Far) ........................................................................................ 72

vi

Page 7

BRNC (Branch If Not Carry) ....................................................................... 73

BRNEQ (Branch If Not Equal) .................................................................... 74

BRNZ (Branch If Not Zero) ......................................................................... 76

BRZ (Branch If Zero) .................................................................................... 77

CALL (Call Near) ......................................................................................... 78

CALLF (Call Far) ......................................................................................... 79

CALLR (Call Relative) ................................................................................. 80

DBRNZ (Decrement and Branch If Not Zero) ............................................ 81

DEALLOC (Deallocate and Return) ........................................................... 82

DEC (Decrement) ......................................................................................... 84

DIV (Divide) .................................................................................................. 85

DROP (Drop from Stack) ............................................................................. 86

DROP_R (Drop from Stack and Return) .................................................... 87

INC (Increment) ........................................................................................... 88

MUL (Multiply) ............................................................................................ 90

NOP (No Operation) ..................................................................................... 91

NOT (Not) ..................................................................................................... 92

OR (Or) .......................................................................................................... 93

OR_R (Or and Return) ................................................................................. 94

POP (Pop from Stack) .................................................................................. 95

POPD (Pop Pointer Direct) ........................................................................ 100

POPPUSH (Pop from Data Stack and Push onto Return Stack) ............ 101

PUSH (Push onto Stack)............................................................................ 102

PUSHD (Push Pointer Direct) ................................................................... 107

PUSHPOP (Pop from Return Stack and Push onto Data Stack) ............ 109

PUSHS (Push Short) .................................................................................. 110

RET (Return from Call) ............................................................................. 111

ROLC (Rotate Left through Carry) ........................................................... 112

RORC (Rotate Right through Carry) ........................................................ 113

SBC (Subtract with Carry) ........................................................................ 114

SBR (Short Branch) ................................................................................... 115

SBRNZ (Short Branch If Not Zero) ........................................................... 117

SBRZ (Short Branch If Zero) ..................................................................... 119

SHL (Shift Left) .......................................................................................... 121

SHLA (Shift Left Arithmetically) .............................................................. 122

SHR (Shift Right) ....................................................................................... 123

SHRA (Shift Right Arithmetically) ........................................................... 124

SUB (Subtract) ........................................................................................... 125

XCH (Exchange) ......................................................................................... 127

XOR (Exclusive Or) .................................................................................... 128

XOR_R (Exclusive Or and Return) ........................................................... 129

Neuron Assembler Directives .................................................................... 131

Overview of the Assembler Directives ...................................................... 132

APEXP (Application Symbol Export) ........................................................ 134

DATA.B (Reserve Initialized Memory) ..................................................... 135

ELSE (Conditional Assembly) ................................................................... 137

END (Assembly Control) ........................................................................... 138

ENDIF (Conditional Assembly) ................................................................ 139

EQU (Equate Symbol) ................................................................................ 140

ERROR (Conditional Assembly) ............................................................... 141

EXPORT (Export Symbol) ......................................................................... 142

IF (Conditional Assembly) ......................................................................... 143

IFDEF (Conditional Assembly) ................................................................. 144

Neuron Assembly Language Reference vii

Page 8

IFNDEF (Conditional Assembly) .............................................................. 145

IMPORT (Import External Symbol) ......................................................... 146

INCLUDE (Assembly Control) .................................................................. 147

LIBRARY (Include Library) ...................................................................... 148

LIST (Listing Control) ............................................................................... 150

NOLIST (Listing Control).......................................................................... 151

ORG (Segment Control) ............................................................................. 152

PAGE (Listing Control) ............................................................................. 153

RADIX (Default Radix) .............................................................................. 154

RES (Reserve Uninitialized Memory) ....................................................... 155

RESOURCE (Resource Control)................................................................ 156

SEG (Segment Control) ............................................................................. 157

SUBHEAD (Listing Control) ..................................................................... 158

System-Provided Functions ....................................................................... 159

Overview of the Functions ......................................................................... 160

_abs16 (Absolute Value, 16 Bit) ................................................................ 160

_abs8 (Absolute Value, 8 Bit) .................................................................... 161

_add16 (Add, 16 Bit) .................................................................................. 161

_add16s (Add Signed, 16 Bit) .................................................................... 161

_add_8_16f (Add Fast, 8 Bit to 16 Bit) ...................................................... 162

_adds_8_16 (Add Signed, 8 Bit to 16 Bit) ................................................. 162

_alloc (Allocate Stack Space) ..................................................................... 162

_and16 (And, 16 Bit) .................................................................................. 163

_dealloc (Deallocate Stack Space and Return) ......................................... 163

_dec16 (Decrement, 16 Bit) ........................................................................ 163

_div16 (Divide, 16 Bit) ............................................................................... 164

_div16s (Divide Signed, 16 Bit) ................................................................. 164

_div8 (Divide, 8 Bit) ................................................................................... 165

_div8s (Divide Signed, 8 Bit) ..................................................................... 165

_drop_n (Drop N Bytes from Stack) .......................................................... 165

_drop_n_preserve_1 (Drop N Bytes from Stack and Preserve NEXT) ... 166

_drop_n_preserve_2 (Drop N Bytes from Stack and Preserve NEXT and NEXT+1)

..................................................................................................................... 166

_drop_n_return_1 (Drop N Bytes from Stack, Preserve NEXT, and Return) 166

_drop_n_return_2 (Drop N Bytes from Stack, Preserve NEXT and NEXT+1, and

Return) ........................................................................................................ 167

_equal16 (Equality Test, 16 Bit) ............................................................... 167

_equal8 (Equality Test, 8 Bit) ................................................................... 168

_gequ16s (Greater Than or Equal Signed, 16 Bit) ................................... 168

_gequ8 (Greater Than or Equal, 8 Bit) ..................................................... 168

_gequ8s (Greater Than or Equal Signed, 8 Bit) ....................................... 169

_get_sp (Get Stack Pointer) ....................................................................... 169

_inc16 (Increment, 16 Bit) ......................................................................... 169

io_iaccess (Acquire Semaphore) ................................................................ 170

io_iaccess_wait (Acquire Semaphore and Wait) ....................................... 170

io_irelease (Release Semaphore) ............................................................... 171

_l_shift16 (Left Shift, 16 Bit) ..................................................................... 172

_l_shift16s (Left Shift Signed, 16 Bit)....................................................... 172

_l_shift8 (Left Shift, 8 Bit) ......................................................................... 172

_l_shift8s (Left Shift Signed, 8 Bit) ........................................................... 173

_l_shift8_<n> (Left Shift by <n>, 8 Bit) .................................................... 173

_ldP0_fetchl (Load P0 from Fetched Location) ........................................ 173

_less16 (Less Than, 16 Bit) ........................................................................ 174

viii

Page 9

_less16s (Less Than Signed, 16 Bit) ......................................................... 174

_less8 (Less Than, 8 Bit) ............................................................................ 174

_less8s (Less Than Signed, 8 Bit).............................................................. 175

_log16 (Logical Value, 16 Bit) .................................................................... 175

_log8 (Logical Value, 8 Bit) ........................................................................ 175

_lognot16 (Negated Logical Value, 16 Bit) ............................................... 176

_lognot8 (Negated Logical Value, 8 Bit) ................................................... 176

_lshift16_add16 (Left Shift and Add, 16 Bit) ........................................... 177

_lshift8_add16 (Left Shift and Add, Converts 8 Bits to 16 Bits)............. 177

_lshift8by1_add16 (Left Shift By 1 and Add, Converts 8 Bits to 16 Bits)177

_lshift8by2_add16 (Left Shift By 2 and Add, Converts 8 Bits to 16 Bits)178

_max16 (Maximum Value, 16 Bit) ............................................................ 178

_max16s (Maximum Signed Value, 16 Bit) .............................................. 178

_max8 (Maximum Value, 8 Bit) ................................................................ 179

_max8s (Maximum Signed Value, 8 Bit) .................................................. 179

_memcpy (Copy Memory) .......................................................................... 180

_memcpy1 (Copy Memory from Offset) .................................................... 180

_memset (Set Memory) .............................................................................. 180

_memset1 (Set Memory at P0) .................................................................. 181

_min16 (Minimum Value, 16 Bit) ............................................................. 181

_min16s (Minimum Signed Value, 16 Bit) ............................................... 181

_min8 (minimum Value, 8 Bit) .................................................................. 182

_min8s (Minimum Signed Value, 8 Bit) ................................................... 182

_minus16s (Negative Signed Value, 16 Bit) ............................................. 182

_mod8 (Modulo, 8 Bit) ................................................................................ 183

_mod8s (Modulo Signed, 8 Bit) .................................................................. 183

_mul16 (Multiply, 16 Bit) .......................................................................... 183

_mul16s (Multiply Signed, 16 Bit) ............................................................ 184

_mul8 (Multiply, 8 Bit) .............................................................................. 184

_mul8s (Multiply Signed, 8 Bit) ................................................................ 185

_mul_8_16 (Multiply, 8 Bit to 16 Bit) ....................................................... 185

_muls_8_16 (Multiply Signed, 8 Bit to 16 Bit) ......................................... 185

_mul8l (Multiply, 8 Bit with 16 Bit Result).............................................. 186

_mul8ls (Multiply Signed, 8 Bit with 16 Bit Result) ............................... 186

_not16 (Not, 16 Bit) .................................................................................... 186

_or16 (Or, 16 Bit)........................................................................................ 187

_pop (Pop from TOS and Push to Offset) .................................................. 187

_pop1 (Pop from TOS and Push Short to Offset) ..................................... 187

_popd (Pop from TOS and NEXT, Push to Offset, 16 Bit) ....................... 188

_popd1 (Pop from TOS and NEXT, Push Short to Offset, 16 Bit) ........... 188

_push (Push from Offset to TOS) .............................................................. 189

_push1 (Push Short from Offset to TOS) .................................................. 189

_push4 (Copy Top 4 Bytes of Stack, Push to Stack) ................................ 189

_pushd (Push from Offset to TOS and NEXT, 16 Bit) ............................. 190

_pushd1 (Push Short from Offset to TOS and NEXT, 16 Bit) ................. 190

_r_shift16 (Right Shift, 16 Bit) .................................................................. 190

_r_shift16s (Right Shift Signed, 16 Bit) .................................................... 191

_r_shift8 (Right Shift, 8 Bit) ...................................................................... 191

_r_shift8_<n> (Right Shift <n>, 8 Bit) ...................................................... 191

_r_shift8s (Right Shift Signed, 8 Bit) ........................................................ 192

_register_call (Call Function from Register) ............................................ 192

_sign_extend16 (Convert 8 Bit to 16 Bit, Preserve Sign) ........................ 193

_sub16 (Subtract, 16 Bit) ........................................................................... 193

Neuron Assembly Language Reference ix

Page 10

_sub16s (Subtract Signed, 16 Bit) ............................................................. 193

_xor16 (Exclusive OR, 16 Bit) ................................................................... 194

Neuron Assembly Instructions Listed by Mnemonic ........................... 195

Instructions by Mnemonic ......................................................................... 196

Neuron Assembly Instructions Listed by Hexadecimal Opcode ....... 207

Instructions by Opcode .............................................................................. 208

Reserved Keywords ...................................................................................... 219

Keywords .................................................................................................... 220

Index ................................................................................................................. 221

x

Page 11

1

Introduction

This chapter introduces the Neuron assembly language and

the Neuron Assembler.

Neuron Assembly Language Reference 1

Page 12

Introduction

An application program for a LONWORKS device that runs on a Series 3100,

Series 5000, or Series 6000 Neuron Chip or Smart Transceiver uses the Neuron C

programming language. Although this language is very powerful and flexible,

there can be times when you want to optimize the application program for the

ONWORKS device, perhaps for code size or processing speed. You can use

L

Neuron assembly language to write functions or programs that provide such

optimizations.

Although Neuron assembly language functions can be smaller and faster than

those generated by the Neuron C compiler, they also have the following

characteristics:

• TheIzoT NodeBuilder FX Development Tool does not provide a Code

Wizard for assembly functions

• There are fewer automated validations and checks for Neuron assembly

code

• Functions written in assembly language can be harder to write, read, and

maintain

• Functions written in assembly language have a larger potential for error,

compared to higher language implementations

• Code written in assembly language cannot be debugged with the

NodeBuilder Debugger

Nonetheless, the Neuron assembly language is a powerful tool for managing

specific tasks for a Neuron C application program.

This chapter provides an overview of the tools, files, and syntax for Neuron

assembly language functions. The rest of this book contains the following

information:

• Chapter 2, Neuron Architecture for Neuron Assembly Programming,

provides an overview of the Neuron architecture, hardware resources,

and addressing modes.

• Chapter 3, Writing a Neuron Assembly Utility Function, provides an

overview of stack-oriented programming and information about designing

assembly language functions. It also describes a recommended approach

to documenting changes to the stack.

• Chapter 4, Interfacing with a Neuron C Application, describes how a

Neuron assembly language function can work with a Neuron C

application.

• Chapter 5, Exploring an Example Function in Neuron Assembly,

describes a simple example function in Neuron assembly.

• Chapter 6, Neuron Assembly Language Instruction Statements, describes

all of the supported Neuron assembly language instructions.

• Chapter 7, Neuron Assembler Directives, describes the supported Neuron

Assembler directives.

2 Introduction

Page 13

• Chapter 8, System-Provided Functions, describes system-provided

functions for various arithmetical or logical operations or for stack

management.

This book also contains several appendixes with additional information.

Neuron Assembler Tools

You can create and edit Neuron assembly language files using any text editor,

such as Windows Notepad. The primary tool for working with Neuron assembly

language files is the Neuron Assembler. The Neuron Assembler translates your

source code, written in the Neuron Assembly language, into a Neuron object file

(.no extension). You can use the Neuron Librarian to create or manage code

libraries of Neuron object files, including those created from assembly language

files.

In general, you do not need to use the Neuron Assembler when creating a small

number of utility functions for use with one specific Neuron C application. To use

assembly source code within a Neuron C application, the Neuron C Compiler

supports the #pragma include_assembly_file directive, which can be used to

copy a specified assembly source file directly into the compiler-generated output.

The main tools for working with Neuron C applications, which can interact with

Neuron assembly functions, are the IzoT NodeBuilder FX Development Tool, and

the FT 6000 EVB. The IzoT NodeBuilder FX Development Tool can produce

Neuron assembly listing output files for your Neuron C programs.

Neuron C Compiler for Assembly Programming

The Neuron C Compiler supports the #pragma include_assembly_file

directive. This directive can be used repeatedly within the same Neuron C source

code, specifying one assembly source file at a time.

The Neuron C compiler translates your Neuron C source code into Neuron

Assembly output. When it encounters the #pragma include_assembly_file

directive, the compiler copies the content of the referenced assembly source file

directly (without modification) into its own output stream.

See the Neuron C Reference Guide for more information about compiler

directives.

Neuron Assembler Command Line Tool

The Neuron Assembler, available from the command line as NAS.EXE,

translates source files written in the Neuron assembly language (typically using

a .ns file extension) into Neuron object files (.no file extension), which can then

be packaged into function libraries using the Neuron Librarian (NLIB.EXE).

The resulting function libraries can then be provided to the Neuron Linker

(NLD.EXE), and code that is contained in these libraries and referenced by the

Neuron C source code is linked with the application.

To run the Neuron Assembler, open a Windows command prompt (Start →

Programs → Accessories → Command Prompt), and enter the following

command:

nas –switches file.ns

Neuron Assembly Language Reference 3

Page 14

where –switches define any optional command-line switches (see NAS

Command Switches) and file.ns specifies the source input file to assemble.

The command-line tools are installed in the LonWorks\bin directory.

For example, the following command runs the Neuron Assembler, assembles the

abc.ns source file, and generates an abc.no object file in the same directory:

NAS abc.ns

Command Usage

The following command usage notes apply to running the nas command:

• If no command switches or arguments follow the command name, the tool

responds with usage hints and a list of available command switches.

• Most command switches come in two forms: A short form and a long

form.

The short form consists of a single, case-sensitive, character that

identifies the command, and must be prefixed with a single forward slash

'/' or a single dash '-'. Short command switches can be separated from

their respective values with a single space or an equal sign. Short

command switches do not require a separator; the value can follow the

command identifier immediately.

The long form consists of the verbose, case-sensitive, name of the

command, and must be prefixed with a double dash '- -'. Long command

switches require a separator, which can consist of a single space or an

equal sign.

Examples:

Short form: nas –l …

Long form: nas --listing …

• Multiple command switches can be separated by a single space.

• Commands of a Boolean type need not be followed by a value. In this

case, the value yes is assumed. Possible values for Boolean commands

are yes, on, 1, +, no, off, 0, - (a minus sign or dash).

Examples:

nas --listing=yes abc.ns

nas --listing abc.ns

• Command switches can appear at any location within the command line

or in any order (on separate lines) within a script.

NAS Command Switches

Table 1 lists the available command switches for the nas command. All

switches are optional.

4 Introduction

Page 15

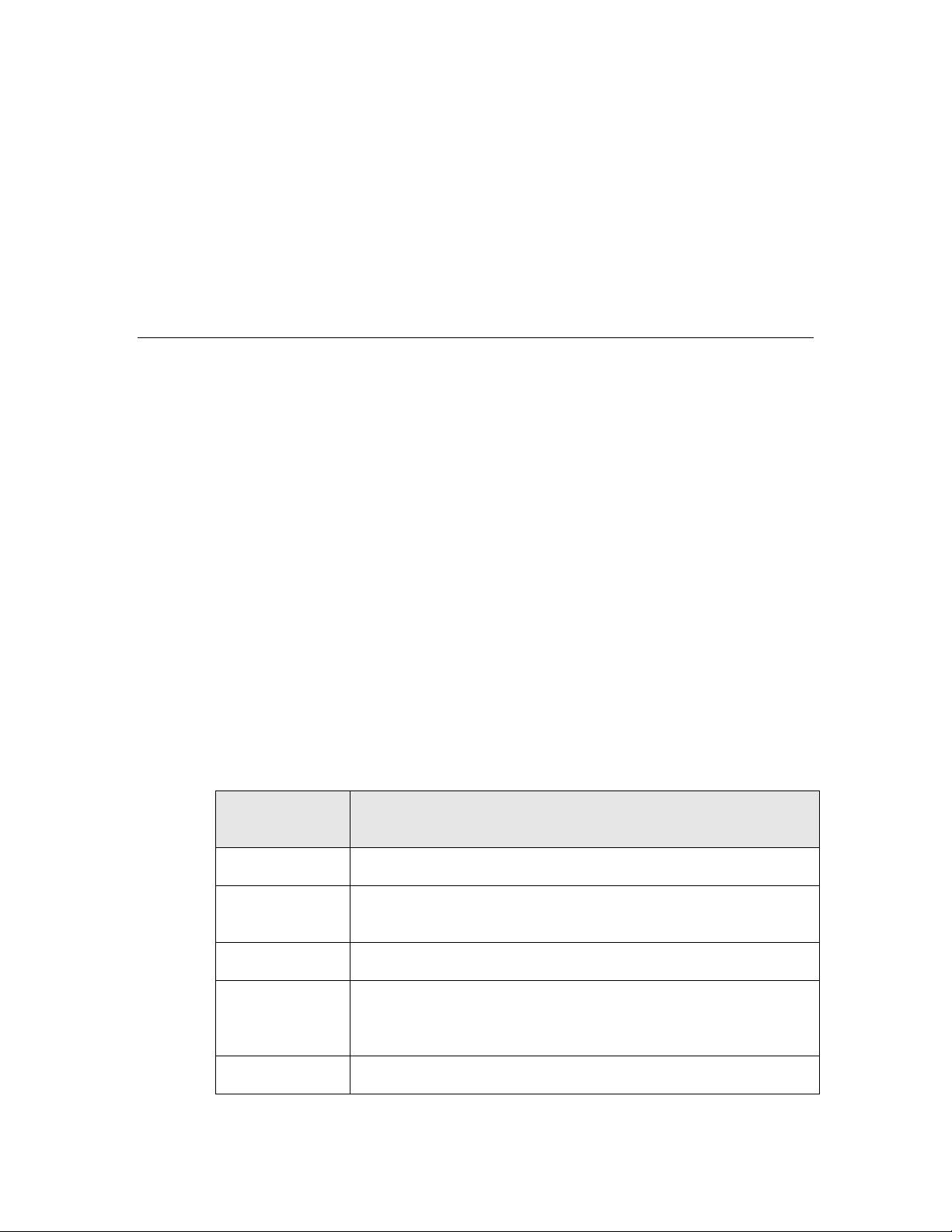

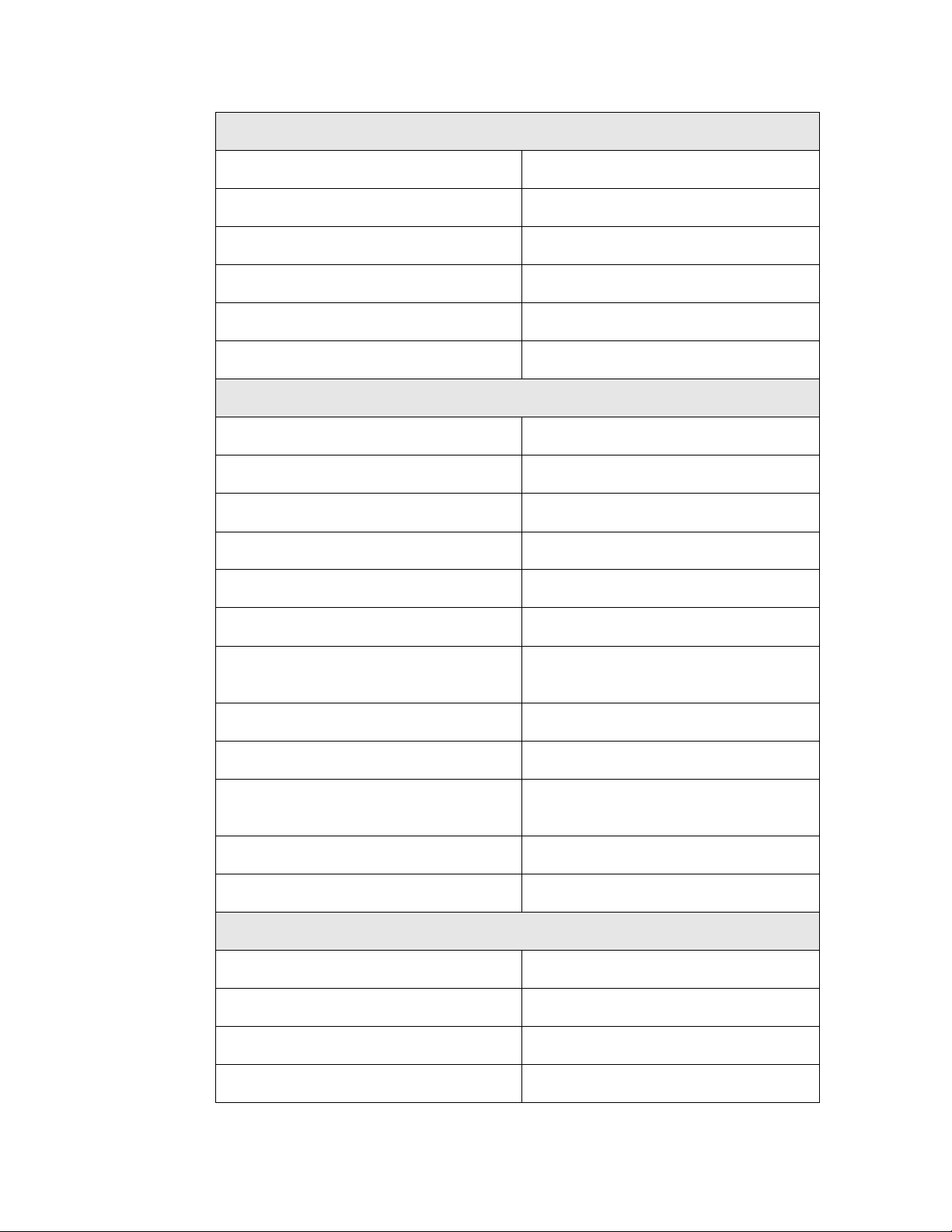

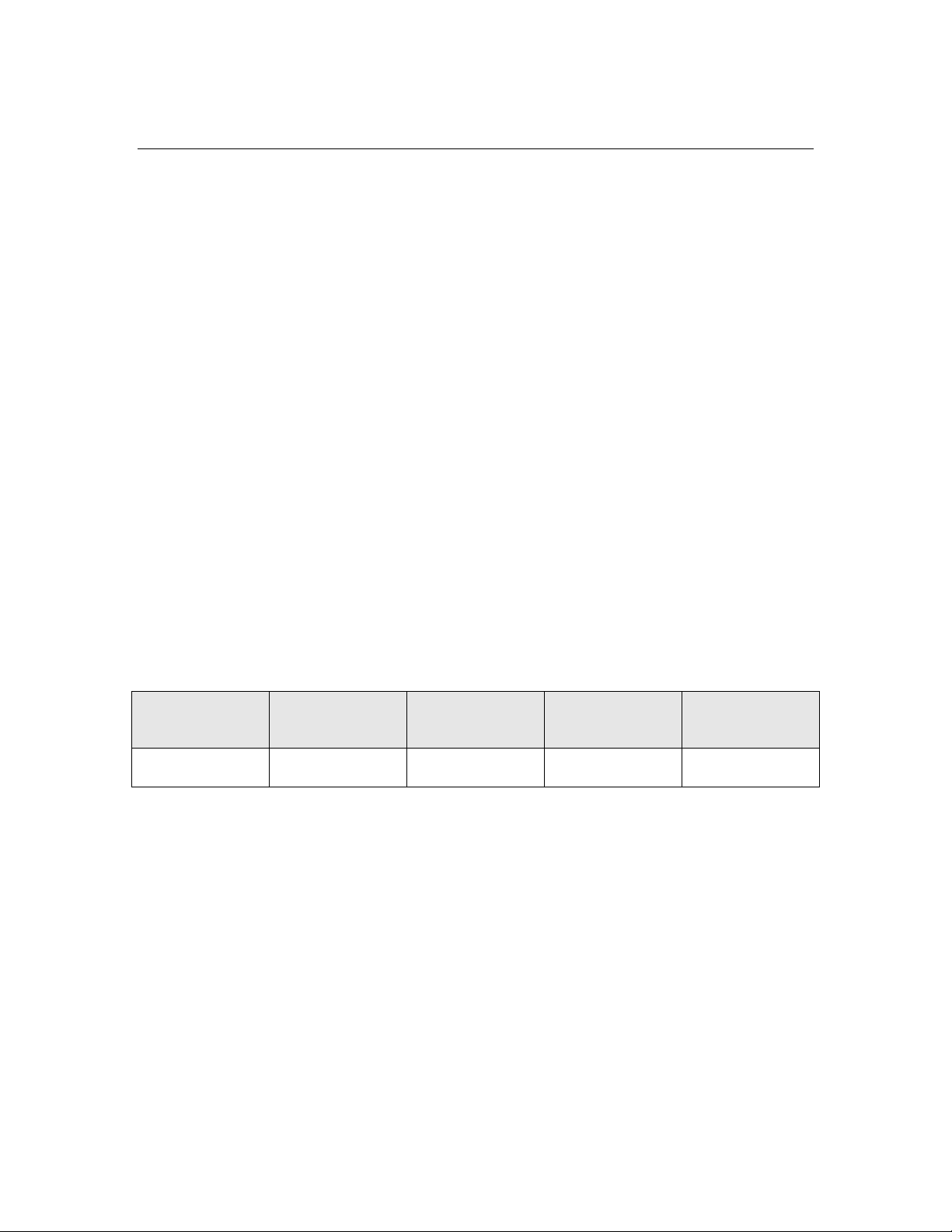

Table 1. Command Switches for the nas Command

Command Switch

Short

Form

--autotrunc -a Auto-truncate literals for byte-immediate operations

--define -d Define a specified conditional-compilation symbol

--defloc Location of an optional default command file

--file -@ Include a command file

--flex -x Specifies interpretation of flex segments

--headroom -h Report available memory headroom

--help -? Display usage hint for command

Description Long Form

--laserjet -j Make the listing LaserJet landscape

--listfile -L Specify an explicit listing file (with -l)

--listing -l Produce an assembly listing output file

--mkscript Generate a command script

--nodefaults Disable processing of default command files

--outfile -o Specify an explicit output file

--search -s Add a path to the search list for include files

--silent Suppress banner message display

--suboptimalwarning -w Display warnings for instructions that are not optimal

size

--warning Display specified value as a warning

Neuron Librarian Tool

A library is a collection of Neuron object files. Each object file contains one or

more compiled ANSI C source files or assembled Neuron assembly source files.

Members of a library are object files created by the Neuron Assembler or the

Neuron C compiler. Although you use the Neuron C compiler to create object

files for a library, you cannot include language constructs that are specific to

Neuron C in these functions.

Neuron Assembly Language Reference 5

Page 16

The Neuron Librarian, available from the command line as NLIB.EXE, allows

you to create and manage libraries, or add and remove individual object files to

and from an existing library.

See the Neuron C Programmer’s Guide for more information about the Neuron

Librarian.

IzoT N odeBuilder Development Tool

The IzoT NodeBuilder FX Development Tool is a hardware and software platform

for developing applications for Neuron Chips and Smart Transceivers. With the

IzoT NodeBuilder FX Development Tool, you can perform many tasks for

developing L

generate Neuron C code for the device interface, compile and build your

application, and debug your application.

The IzoT NodeBuilder FX Development Tool does not work directly with Neuron

assembly language files. However, it can produce an assembly listing output file

for your Neuron C programs, and it can embed your assembly source files into

your application if it includes the #pragma include_assembly_file directive.

The IzoT NodeBuilder FX Development tool can also provide Neuron function

libraries (which can contain object files based on your assembly source) to the

linker, thus making these assembly-coded functions available to your application.

Note that the IzoT NodeBuilder FX Development Tool does not directly support

debugging of code written in assembly or of any code brought in from a function

library.

ONWORKS devices, including: write and edit Neuron C code,

See the IzoT NodeBuilder FX User’s Guide for more information about the IzoT

NodeBuilder FX Development Tool.

Assembler Files

The Neuron Assembler requires a single source input file, and produces one

object output file, and optionally also produces a listing output file. The

descriptions and requirements for native Neuron assembly files also apply to

Neuron assembly source files that are used with the Neuron C Compiler’s

#pragma include_assembly_file directive.

The following sections describe these files.

Source Files

A source file (the input file) contains zero, one, or more lines of Neuron assembly

source code. This source code can consist of Neuron assembly instructions or

Neuron assembly directives.

The following sections describe the file naming convention and file format for

source files.

Naming Convention

A file that contains Neuron assembly source can have any file name that is

allowed by the operating system, but the use of the .ns file extension is

6 Introduction

Page 17

recommended. If no file name extension is provided on the command line, the

Neuron Assembler assumes an .ns extension.

A file that is used with the Neuron Librarian (NLIB) must follow the Windows

8.3 naming convention (for example, filename.ext, where filename is no more than

eight characters and ext is one of the allowable extensions for Neuron assembly

files, such as .ns and .no). Spaces are not allowed in the file name or the

extension.

File Format

Each line in an assembly source file is independent, with no line-continuation

character or terminator character. An assembly source line can contain one of

the following:

• A blank line (zero, one, or more whitespace characters (blanks, spaces, or

tabs), followed by a newline or carriage-return character). The Neuron

Assembler ignores blank lines.

• A comment. A comment starts with a semicolon character (;) and ends

with a newline or carriage-return character. The Neuron Assembler

ignores all characters after the semicolon.

• A label. A label is an identifier for an instruction, directive, or segment.

• An assembly instruction, with zero, one, or more arguments. The line

with the instruction can begin with an optional label, and can also end

with an optional comment.

• An assembler directive. The line with the directive can begin with an

optional label (if the directive allows one), and can also end with an

optional comment.

If the line contains a label, it must begin in the first column. If the line contains

an instruction or directive without a label, the instruction or directive must begin

beyond the first column. A comment can begin in any column, but always

extends to the end of the line.

Spaces or tabs separate the label, the instruction mnemonic or directive, and the

first argument (if any). Multiple arguments are separated by spaces, tabs, or

commas, depending on the syntax of the particular instruction or directive.

Thus, the basic format for an assembly source line is:

label instruction operand ; comment

label DIRECTIVE argument ; comment

By convention, instruction mnemonics are specified in lower case and directives

are specified in upper case.

Output Files

The Neuron Assembler produces the following output files:

• An object output file

• An optional listing output file

Neuron Assembly Language Reference 7

Page 18

The object output file contains assembled code, ready for the Neuron Linker.

Typically, the object output file has the same name as the input source file, but

has an .no file extension.

The listing output file contains the source instructions, directives, and comments

from the source input file, and includes the instruction opcodes and addressing

information (including symbolic or segment-relative addresses that are resolved

by the linker). The listing output file also can include source instructions and

directives from imported files. The listing output file is formatted for ease of

printing or viewing online. Use the --listing (-l) command-line switch to

generate a listing output file. Typically, the listing output file has the same

name as the input source file, but has an .nl file extension.

For both the object output file and the listing output file, you can use the -outfile (-o) command-line switch of the nas command to rename these files.

However, this switch does not allow you to redirect the files to another directory.

A listing output file consists of one or more pages of output. Each page begins

with two header lines and a subhead line:

• The first header line contains information about the version of the

Neuron Assembler and ends with the current page number. This line

starts with a page break control character (form feed), that is used for

printing control. This control character is usually represented by a

special symbol when you view the assembly listing file with a file editor.

• The second header line contains the date and time that the listing file

was created and ends with the name of the source input file.

• The subhead line is blank, unless you specify a subhead using the

SUBHEAD directive (see SUBHEAD (Listing Control).

The rest of a page of a listing output file contains assembly source lines with

additional information in the left-hand columns:

• The first field is a four-digit hexadecimal number that represents the

absolute or relative address of the line. If the assembly source line

defines a label, the four-digit number is the value of the label. For

relocatable segments, the value is relative to the beginning of the

segment.

• The second field (and subsequent fields) is a two-digit or four-digit

hexadecimal number that represents the opcodes or data bytes as

assembled. If the field contains four zeros followed immediately by an

asterisk (*), the field’s value cannot be determined at assembly time, but

must be resolved at link time.

Assembly source lines that are skipped because of conditional assembly are also

included in the listing output file. Lines that are skipped are marked with an

exclamation mark (!) in the left-most column to designate that the line was not

assembled.

General Neuron Assembly Syntax

The general Neuron assembly language syntax is:

label keyword operand1 operand2 ; comment

where:

8 Introduction

Page 19

Labels

• label is an optional identifier, followed by white space

• keyword is a reserved name for an assembly instruction or Assembler

directive

• The operands operand1 and operand2 are optional. There can be zero,

one, or two operands, depending on the specific instruction. When

present, they take the form of either literals or identifiers for data items.

Operand identifiers are either reserved names of registers or stack

pointers, or are assumed to be data items declared in another part of the

file. Depending on the instruction, two operands are separated by either

white space or a comma, and depending on the addressing mode, they can

be enclosed in square brackets ([ ]) or combined with other special

characters.

• The terminating semicolon and comment are optional, but highly

recommended for most assembly source lines. See Documenting Changes

to the Stack for additional comment recommendations.

The following sections provide additional information about these syntax

elements.

A label is an identifier for an instruction, directive, or segment. The Neuron

Assembler defines label values by their position in the source file relative to the

instructions and directives. A relocatable label has no absolute value until link

time.

A label can comprise either lower or upper case letters a..z or A..Z, the digits 0..9,

and any of the following special characters: underscore (_), period (.), or percent

(%). The first character cannot be one of the numeric digits, nor can it be the

period (.) character. Labels are case sensitive.

Note that Neuron Assembler keywords are reserved and cannot be used for

labels, regardless of case. Reserved words include instruction mnemonics,

assembler directives, or register names. See Appendix C, Reserved Keywords, for

a list of assembler keywords.

Assembly Instructions

An assembly instruction is a keyword that represents a class of machine

operation codes (opcodes). The specific opcode is defined by the instruction,

combined with its operands.

An assembly instruction can comprise either upper or lower case characters a..z

or A..Z and the underscore character (_). Assembly instructions are not case

sensitive.

Each instruction accepts zero, one, or two operands (which can include special

characters).

An exclamation character (!) can precede an instruction. This character indicates

that any warning that results from using the -w command line switch is

suppressed for that instruction. Using this character can be useful if the -w

switch warns of something that is intentional or otherwise unavoidable.

Neuron Assembly Language Reference 9

Page 20

See Chapter 6, Neuron Assembly Language Instruction Statements, for a

description of all supported instructions.

Operands

Many Neuron assembly instructions require one or two operands to define the

machine instruction (opcode). Operands add information to the instruction, and

define the data that the instruction should operate on.

For example, some instructions require a register name (such as TOS or DSP) as

an argument to specify the source or destination of the data for the instruction.

In general, you can specify operand names in upper or lower case.

Some instructions use immediate addressing, for which you specify the operand

by prefixing a number sign or hash (#) to the value. An immediate value is used

as a literal value. For example, a PUSH #24 instruction pushes the literal value

“24” onto the stack, whereas a PUSH 24 instruction pushes the contents of

location 24 onto the stack.

Some instructions use base-relative addressing, for which the operand specifies a

location within the base-page relative to its starting address. Specify such a

displacement by prefixing an exclamation mark (!) to the operand.

Some instructions use one or two operands that specify a pointer register,

sometimes also with a displacement, or they specify a displacement relative to

the data stack pointer (DSP) or return stack pointer (RSP). Specify these types of

arguments by enclosing the argument in square brackets ([ ]).

Literal Constants

A literal constant is a numeric value, such as 12 or 173. The Neuron Assembler

supports numeric values in any of four radixes (bases): binary (base 2), octal

(base 8), decimal (base 10), and hexadecimal (base 16).

The RADIX directive specifies the default radix for an assembly language

function (see RADIX (Default Radix). To explicitly specify the radix for a literal

constant, prefix the constant’s value with one of the following letters and the

apostrophe character (‘):

• b’ for binary numbers

• o’ for octal numbers

• d’ for decimal numbers

• h’ for hexadecimal numbers

You can specify the radix letter in either upper or lower case. You can specify

leading zeros for any literal constant without changing its value. However, if the

default radix is hexadecimal, a literal constant must always begin with a numeric

digit or leading zero.

For example, you can specify the decimal value 123 as b’01111011, o’173, d’123,

or h’7b.

10 Introduction

Page 21

Symbols

A symbol is one or more consecutive alphanumeric characters. A symbol can

comprise either lower or upper case letters a..z or A..Z, the digits 0..9, and any of

the following special characters: underscore (_), period (.), or percent (%). The

first character cannot be one of the numeric digits, nor can it be the period (.)

character. Symbols are case sensitive.

Note that Neuron Assembler keywords are reserved and cannot be used for

symbols, regardless of case. Reserved words include instruction mnemonics,

assembler directives, or register names. See Appendix C, Reserved Keywords, for

a list of assembler keywords.

A label is a type of symbol (see Labels). A symbol that acts as a label for the

EQU directive is defined explicitly by the directive’s argument expression,

regardless of whether the directive is in a relocatable segment. See EQU (Equate

Symbol) for more information about this directive.

You can also define a symbol by importing its value from an assembled object file.

The value of an imported symbol is known only at link time. In addition, you can

export a symbol to make it available at link time to another assembly file or a

Neuron C file. See one of the following sections for more information about

importing and exporting symbols: APEXP (Application Symbol Export), EXPORT

(Export Symbol), and IMPORT (Import External Symbol).

Expressions

Some Neuron assembly instructions accept expressions as arguments. The

simplest expression consists of a literal constant or a symbol. However, the

assembler also accepts expressions for which the value is the result of a

computation. The computation can involve multiple literal constants or symbols

and use a variety of operators. If the value of an expression is not computable at

assembly time, the assembly object output file must contain sufficient

information for the Neuron Linker to compute the expression value at link time.

General Expressions

The assembler supports the following types of operators for creating general

expressions:

• Unary

• Binary

• Special operators

All expression values are 16-bit expressions, and all operators produce 16-bit

results. All operations use unsigned two’s-complement arithmetic. You can add

parentheses to an expression to syntactically determine its boundaries without

changing its value.

Unary operators are symbols that appear in front of an expression and perform

an operation on the value of that expression. Table 2 lists the unary operators.

Neuron Assembly Language Reference 11

Page 22

Table 2. Unary Operators

Operator Description

- Two’s-complement arithmetic negation

~ One’s-complement bitwise negation

Binary operators are symbols that appear between two expressions and perform

an operation to combine the values of the two expressions. Table 3 lists the

binary operators.

Table 3. Binary Operators

Operator Description

+ Two’s-complement addition

- Two’s-complement subtraction

* Multiplication

/ Division with integral truncation

& Bitwise AND

| Bitwise OR

^ Bitwise Exclusive OR

The special operators are symbols that instruct the Neuron Assembler to perform

a specific action. The values of expressions that use special operators are

computed at link time. Table 4 lists the special operators.

Table 4. Special Operators

Operator Description

@ Specifies a special operator function

* Specifies the absolute address of the

current assembly instruction (only

computable at link time for relocatable

segments)

A special operator function begins with the @ character, followed by the function

name, and then by a parenthesized expression. The function names can be

specified in either lower or upper case. Table 5 lists the special operator

functions.

12 Introduction

Page 23

Table 5. Special Operator Functions

Function Description

LB Extracts the low byte of the expression

HB Extracts the high byte of the expression

(logical shift right by eight bits)

NEAR Offset value for the RAMNEAR area

(only computable at link time)

Example:

The following example demonstrates the use of the @NEAR expression. The

example implements a one-byte variable in the RAMNEAR segment, and a

function named Example that increments this global variable.

; open RAMNEAR segment, declare one byte

; uninitialized variable

SEG RAMNEAR

ORG

myVariable EXPORT

RES 1

; The Example routine takes no arguments and produces

; no results, but increments the global variable

SEG CODE

ORG

pNear EQU 1

Example APEXP ; ( -- )

push [pNear][@NEAR(myVariable)]

inc

pop [pNear][@NEAR(myVariable)]

ret ; return to caller

Constant Expressions

A constant expression is a general expression that is computable at assembly time

and has a constant value in an appropriate range for the specified instruction or

directive.

An expression that is not constant is one that is computable only at link time or

that has a variable value at runtime. Such symbols must be designated as

imported symbols.

Important: An expression that uses either the * or @NEAR special operator

cannot be a constant expression.

When using negative constants, or expressions that yield negative results, in a

byte context, you must use the @LB special operator (or specify the --autotrunc

[-a] command-line switch) to obtain a one-byte value for the value. For example,

use PUSH #@LB(-1) instead of PUSH #-1 (the latter will fail assembly).

Neuron Assembly Language Reference 13

Page 24

Displacements

A displacement is a relative address value. A displacement can be interpreted as

a signed or unsigned number, depending on the instruction with which the

displacement appears.

To compute the absolute address value, add the displacement (using either

signed or unsigned arithmetic, as appropriate) to the absolute address of the

instruction that contains the displacement.

Address Expressions

An address expression is an expression that specifies an address, and can be one

of the following types of expression: a literal constant, a symbol with an optional

offset expression, or the * special operator with an optional offset expression.

The optional offset expression is a general expression with a prefixed + (addition)

or - (subtraction) operator.

An address expression can consist of a mixture of locally defined and imported

symbols from the same or from multiple segments. However, symbols from other

segments must be exported, even if they are not used by other modules.

Comments

A comment is part of an assembly source line that provides useful information to

the code developer. The Neuron Assembler ignores comments. A comment starts

with a semicolon character (;) and ends with a newline or carriage-return

character.

Recommendation: Use comments to document changes to the data and return

stacks. See Documenting Changes to the Stack for a recommended method of

documenting stack changes.

Assembler Directives

An assembler directive provides information to the Neuron Assembler to control

or affect the processing of the remainder of the assembly file.

The directives have syntax analogous to the assembly instructions. Most

directives require arguments, which are similar to the operands of the assembly

instructions.

See Chapter 7, Neuron Assembler Directives, for more information about the

Neuron Assembler directives.

Interfacing with Neuron C Programs

Typically, you use Neuron assembly language to create utilities that can be used

with an application that is written in Neuron C. The Neuron C program code

might call functions defined in Neuron assembly, or a Neuron assembly function

might call a Neuron C function or program.

See Chapter 4, Interfacing with a Neuron C Application, for more information

about how Neuron assembly language functions and Neuron C program interact.

14 Introduction

Page 25

2

Neuron Architecture for Neuron

Assembly Programming

This chapter describes elements of the Neuron architecture that apply

to writing a function in Neuron assembly language.

Neuron Assembly Language Reference 15

Page 26

Neuron Architecture

For Series 3100 devices, the architecture of a Neuron Chip or Smart Transceiver

includes three independent processors that share a common memory, arithmeticlogic unit (ALU), and control circuitry. Each processor has its own set of

registers, including an instruction pointer (IP) and a flag register (FLAGS),

which contains the processor ID and the Carry flag.

For Series 5000 and 6000 devices, the architecture of a Neuron Chip or Smart

Transceiver is essentially identical to the independent processors of a Series 3100

device; however, Series 5000 and 6000 devices also provide interrupt-processing

support. Depending on the device’s configuration, interrupts can run in a fourth

processor or share the main application processor. As with Series 3100 devices,

each processor has its own set of registers, including an instruction pointer (IP)

and a flag register (FLAGS), which contains the processor ID and the Carry flag.

The Neuron architecture uses a base page model for addressing memory. Each

processor has a base-page register (BP) that points to a 16-byte boundary in

RAM. The first eight bytes of the base page are used as four 16-bit pointers

(named P0 to P3), followed by 16 bytes that implement 16 one-byte data registers

(named R0 to R15).

Some addressing modes refer to those general-purpose registers, and one

addressing mode directly accesses all 256 base-page bytes, including the 24 bytes

for the general-purpose registers.

Many of the general-purpose registers have a pre-defined use within the Neuron

system firmware and application framework. See CPU Registers for more

information.

Base-page pointers or the direct addressing mode is used to access to global data

(defined as memory outside the base page).

Neuron Chips and Smart Transceivers are stack-oriented machines, using two

stacks: the data stack and the return stack. The data stack holds program data,

and the return stack holds return addresses and transient local data. In the

event of an interrupt, the return stack also holds some of the processor’s state

information.

The data stack’s starting address is at low base page memory (after the generalpurpose register area), and moves upward. The data stack pointer (DSP) is an 8bit offset from the BP register. The return stack’s starting address is at the top

of the base-page memory, and moves downward. The return stack pointer (RSP)

is an 8-bit offset from the BP register.

A dedicated hardware register holds the top of data stack element (this element

is called TOS), and a special addressing mode allows for fast access to the

element below TOS (this element is called NEXT).

This stack-oriented architecture, with both data and return stacks growing

towards each other within the same 256-byte base page, is not normally

problematic, but deep recursion or large local variables, or a combination of both,

should be avoided to prevent the stacks from colliding. The programmer is

responsible for seeing that the two stacks never collide. For Series 5000 and

6000 devices, a stack collision or a stack underflow can be recognized by the

system firmware, and results in an entry in the device’s error log.

16 Neuron Architecture for Neuron Assembly Programming

Page 27

A Neuron Chip or Smart Transceiver is a big-endian device, that is, the mostsignificant byte (MSB) of an address or a 16-bit scalar is at a lower memory

address, and the least-significant byte (LSB) of an address or a 16-bit scalar is at

a higher memory address. For 16-bit addresses, a Neuron assembly language

function must be sure to read or write the MSB at a low address before reading or

writing the LSB at higher address.

Because the data stack grows towards higher addresses, 16-bit entities appear on

the data stack with the LSB nearer to TOS. For the return stack, which grows in

the opposite direction, 16-bit entities appear with the MSB nearer to TOS.

Most operations that require arguments require that these arguments are

pushed onto a stack, and when an operation is performed, its arguments are

popped from a stack and its result (if any) pushed back on.

In addition to the DSP, a Neuron assembly language function can use two

registers, TOS and NEXT, to work with the top of the stack and with the next

element below the top of the stack, respectively. See Overview of Stack-Oriented

Programming for additional information about working with stacks.

For more information about the Neuron architecture:

• For Series 3100 devices, see the FT 3120 / FT 3150 Smart Transceiver

Data Book or the PL 3120 / PL 3150 / PL 3170 Power Line Smart

Transceiver Data Book.

• For Series 5000 devices, see the Series 5000 Chip Data Book.

• For Series 6000 devices, see the Series 6000 Chip Data Book.

Hardware Resources for Assembly Programs

The Neuron architecture provides two major sets of hardware resources for a

Neuron assembly language function to use: CPU registers and stacks. To make

effective use of these resources, the Neuron assembly language implements a

number of addressing modes that provide efficient access to data, either through

the registers or through one of the stacks. The following sections describe these

hardware resources. See Addressing Modes for a description of the available

addressing modes.

CPU Registers

The Neuron architecture provides the following types of CPU registers for

Neuron assembly language programming:

• General-purpose 16-bit pointer registers and 8-bit data registers

• A flag register

• An instruction pointer

• A base-page register

• A data-stack pointer register (8-bit, BP-relative)

• A register containing the element on top of the data stack (TOS)

• A return-stack pointer register (8-bit, BP-relative)

The following sections describe these registers.

Neuron Assembly Language Reference 17

Page 28

General-Purpose Registers

The Neuron architecture defines 16 hardware memory locations that the Neuron

Assembler uses as general-purpose registers, typically named R0, R1, R2, and so

on, to R15, as described in Table 6. Each of the general-purpose registers is

eight bits wide.

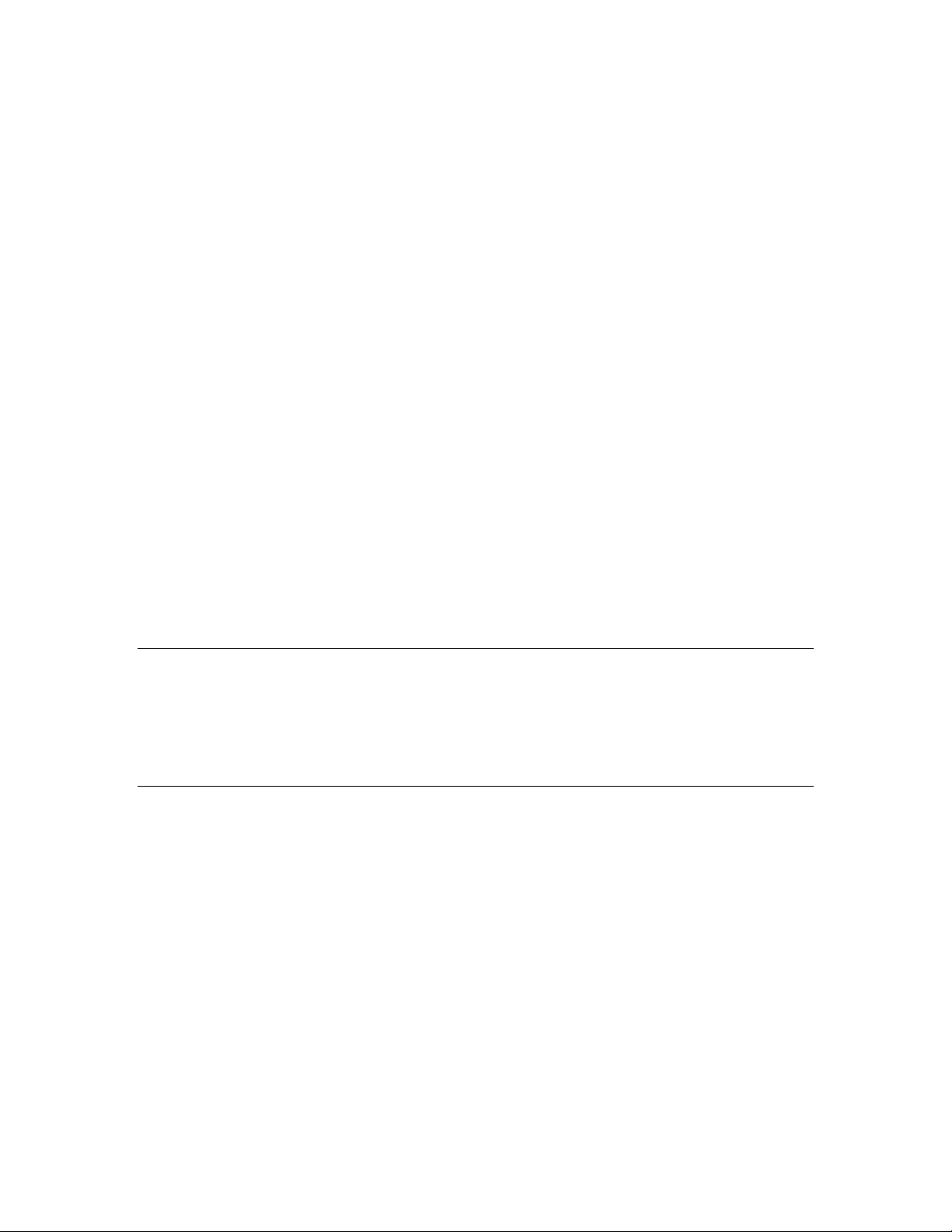

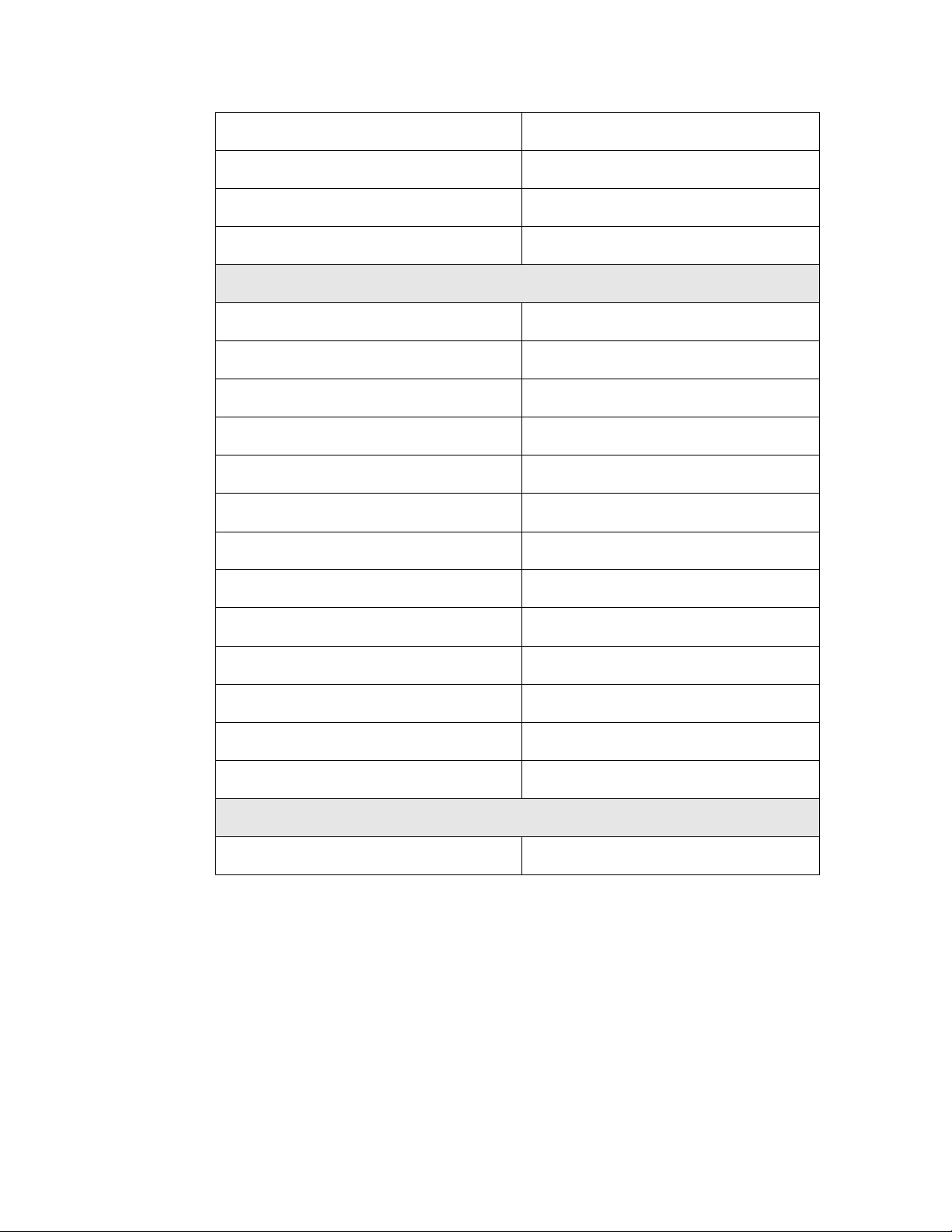

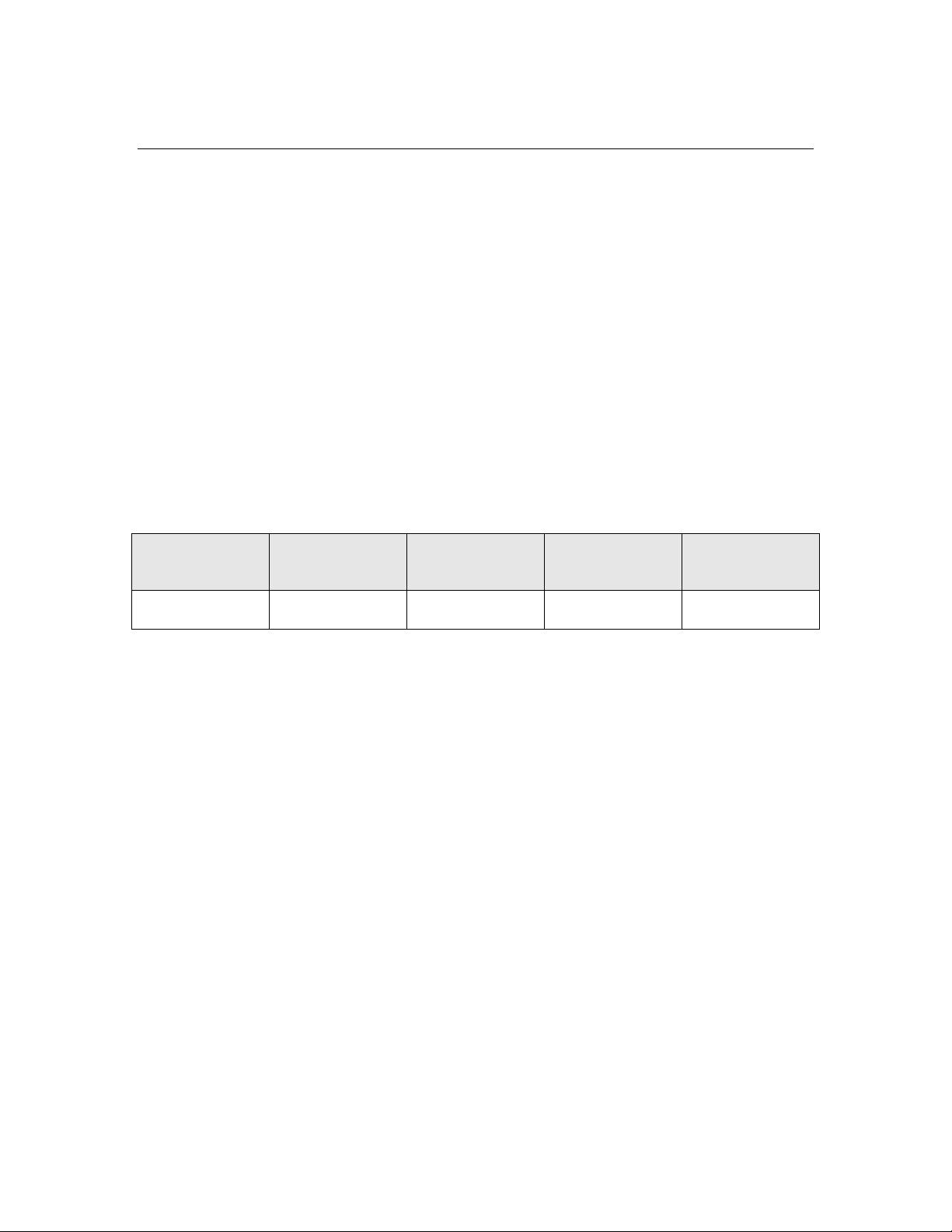

Table 6. General-Purpose Registers

GeneralPurpose

Register

R0 Scratch register. A function can use this register as needed.

R1 Scratch register. A function can use this register as needed.

R2 Scratch register. A function can use this register as needed.

R3 Reserved for use by the system firmware.

R4 Reserved for use by the system firmware.

R5 Reserved for use by the system firmware.

Description

Assume that any call to the firmware, or to any function in a

library or written in Neuron C, might change the contents of

this register.

Assume that any call to the firmware, or to any function in a

library or written in Neuron C, might change the contents of

this register.

Assume that any call to the firmware, or to any function in a

library or written in Neuron C, might change the contents of

this register.

R6 Reserved for use by the system firmware.

R7 Reserved for use by the system firmware.

R8 Reserved for use by the system firmware.

R9 Reserved for use by the system firmware.

R10 Reserved for use by the system firmware.

R11 Reserved for use by the system firmware.

R12 Reserved for use by the system firmware.

R13 Reserved for use by the system firmware.

R14 Reserved for use by the system firmware.

R15 Reserved for use by the system firmware.

18 Neuron Architecture for Neuron Assembly Programming

Page 29

A scratch register is one that can be used for temporary data storage by multiple

programs or functions. Although some operations support a special addressing

mode to index data through the general-purpose registers, you should consider

registers R0..R2 as modified after calling any other function. See Chapter 8,

System-Provided Functions, for a description of these functions, including which

general-purpose registers each function uses and modifies.

Important: Do not use or modify R4 in your Neuron assembly functions because

the network processor uses it. Modifying the other reserved general-purpose

registers (R3 to R15) can also cause unpredictable results.

The Neuron Assembly language refers to the general purpose data registers by

their base-page relative indices, 8..23. A typical assembly language function

defines the mnemonics R0 to R15 for these registers by using the EQU assembly

directive.

Example: The following push instruction uses base page relative addressing.

This addressing mode addresses the argument through one operand, the index of

one of the general purpose data registers within the base page. This index must

be in the 8..23 range.

The following instruction pushes the value of the R0 register onto the data stack:

push !8

Defining mnemonic names for the general-purpose registers makes this

instruction more easily readable. The following example is equivalent to the

previous one:

R0 EQU 8

push !R0

However, because you define the R0 mnemonic, it carries no special meaning for

the Neuron Assembler. The Assembler does not validate that the mnemonic

refers to the correct or intended register.

For the purpose of clarity (and unless explicitly mentioned to the contrary), all

source code examples in this book assume that the following mnemonics are

defined:

R0 EQU 8

R1 EQU R0+1

...

R15 EQU R14+1

Finally, note that the mnemonics are user-defined symbols. Unlike pre-defined

register names or assembly instructions, user-defined symbols are case-sensitive.

Pointer Registers

The Neuron architecture defines four general-purpose pointer registers, typically

named P0, P1, P2, and P3, as described in Table 7. Each of the pointer registers

is 16 bits wide.

Neuron Assembly Language Reference 19

Page 30

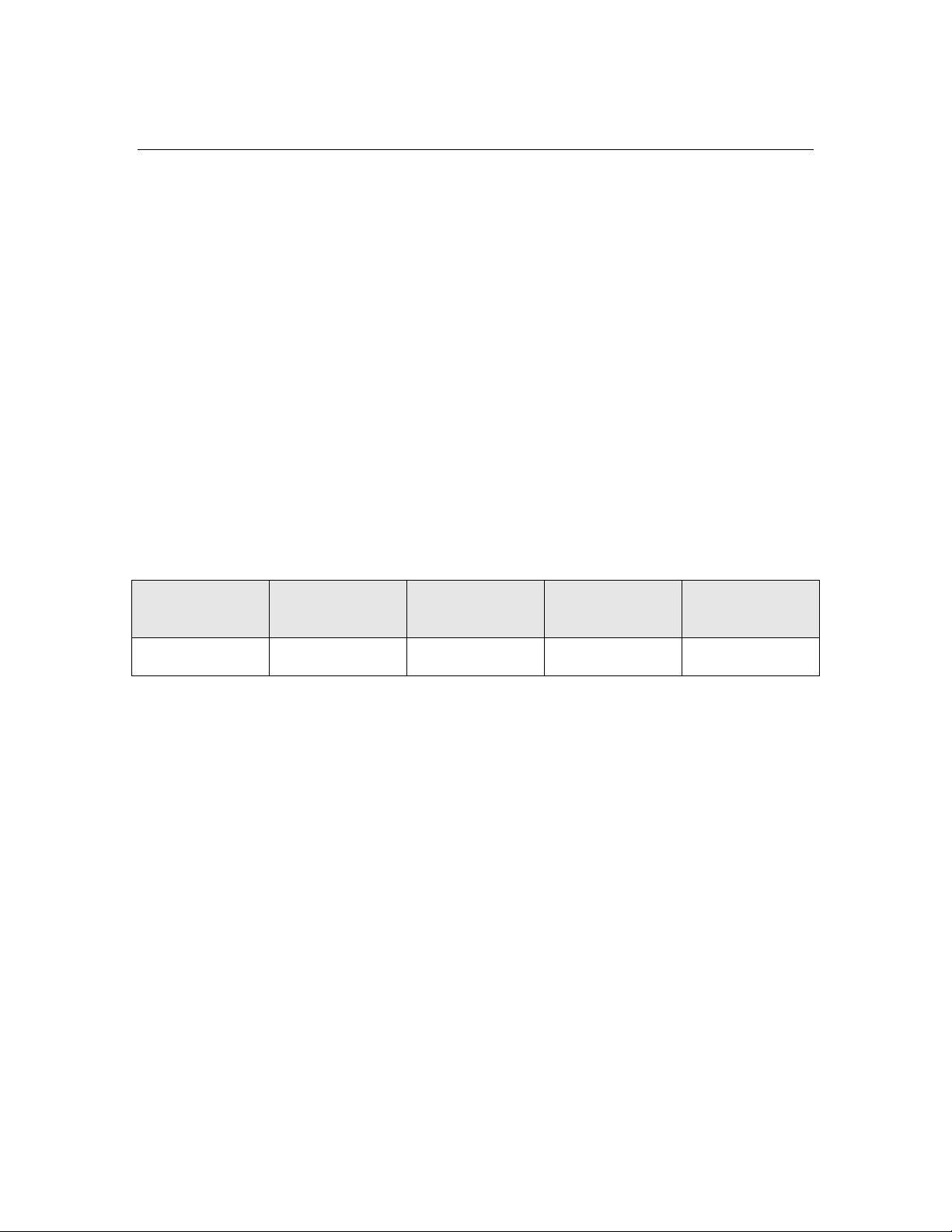

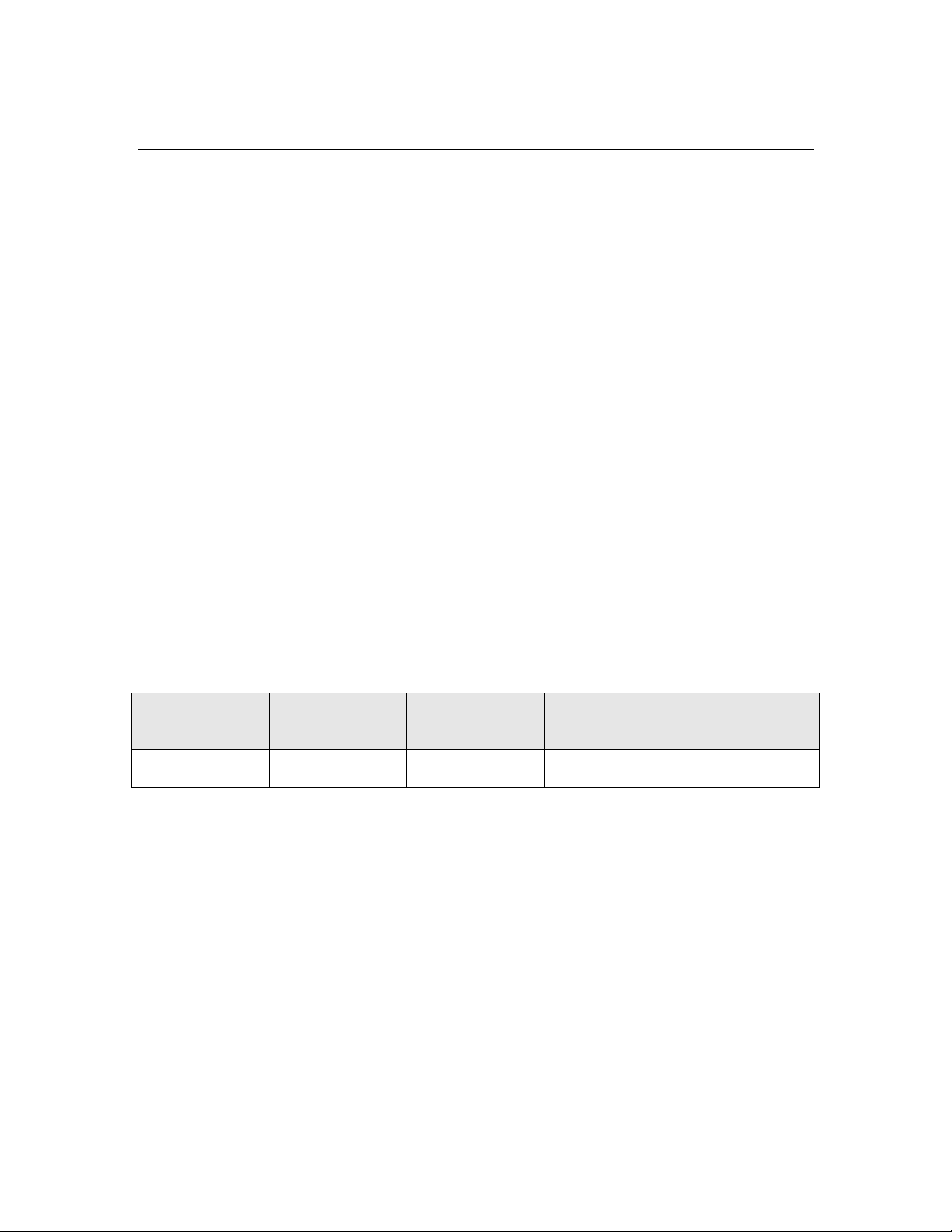

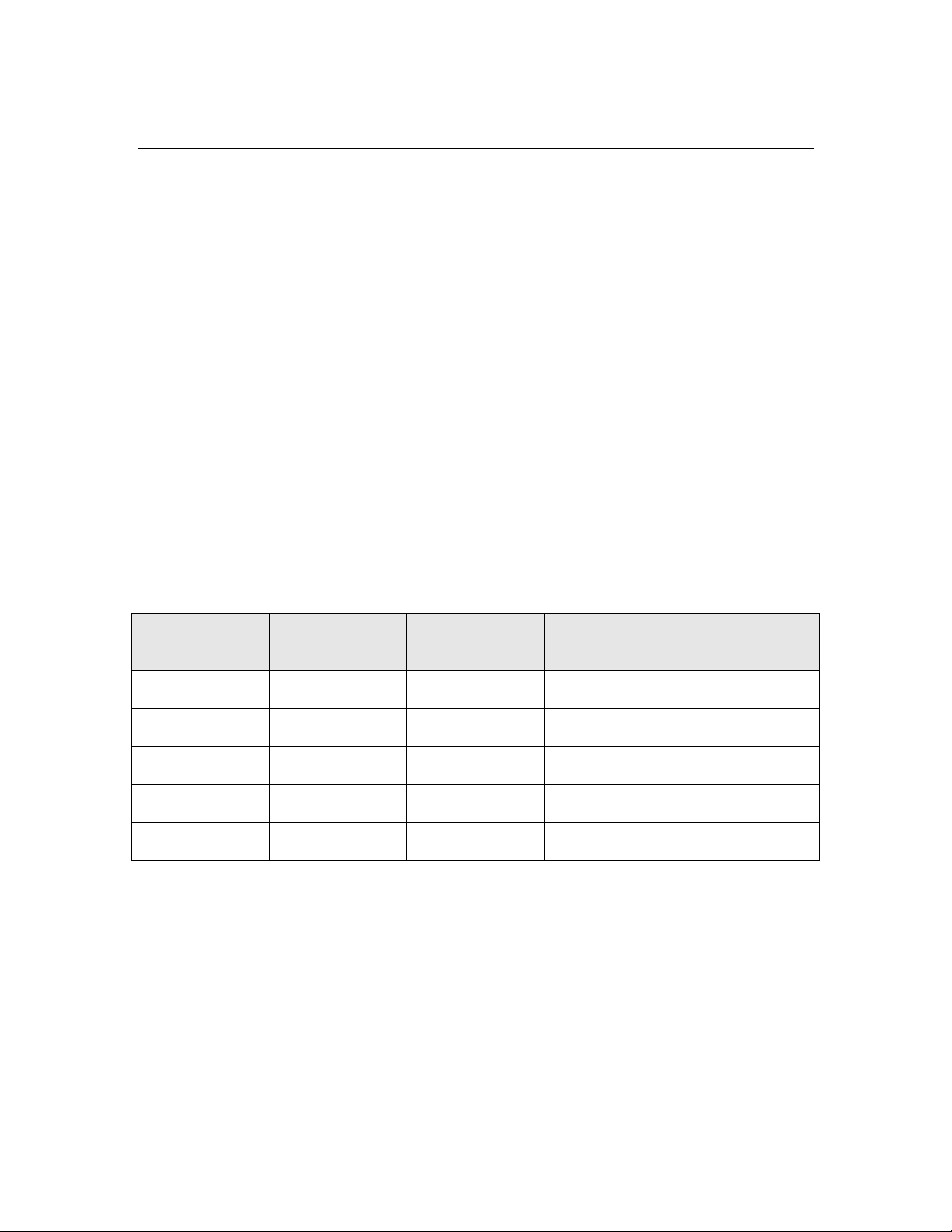

Table 7. Pointer Registers

Pointer

Register

P0 Scratch register. A function can use this register as needed.

P1 Always points to the beginning of the RAMNEAR segment.

P2 Used by Neuron C programs. Assume that any call to the

P3 Scratch register. Assume that any call to the firmware, or to

A scratch register is one that can be used for temporary data storage by multiple

programs or functions. That is, must typically be saved before and restored after

calling any other function.

Important: Do not modify P1 or P2 in your Neuron assembly functions.

Description

Assume that any call to the firmware, or to any function in a

library or written in Neuron C, might change the contents of

this register.

Do not change this register’s content when working in a

Neuron C context.

firmware, or to any function in a library or written in

Neuron C, might change the contents of this register.

any function in a library or written in Neuron C, might

change the contents of this register.

The Neuron Assembly language refers to the general-purpose pointer registers by