Page 1

LONWORKS® Router

User’s Guide

078-0018-01H

Page 2

Echelon, LNS, LONMARK, LonTalk, LONWORKS, Neuron,

NodeBuilder, 3120, 3150, and the Echelon logo are

trademarks of Echelon Corporation registered in the United

States and other countries.

Other brand and product names are trademarks or

registered trademarks of their respective holders.

Smart Transceivers, Neuron Chips, and other OEM Products

were not designed for use in equipment or systems, which

involve danger to human health or safety, or a risk of

property damage and Echelon assumes no responsibility or

liability for use of the Smart Transceivers or Neuron Chips in

such applications.

Parts manufactured by vendors other than Echelon and

referenced in this document have been described for

illustrative purposes only, and may not have been tested

by Echelon. It is the responsibility of the customer to

determine the suitability of these parts for each

application.

ECHELON MAKES AND YOU RECEIVE NO WARRANTIES OR

CONDITIONS, EXPRESS, IMPLIED, STATUTORY OR IN ANY

COMMUNICATION WITH YOU, AND ECHELON SPECIFICALLY

DISCLAIMS ANY IMPLIED WARRANTY OF MERCHANTABILITY

OR FITNESS FOR A PARTICULAR PURP O SE .

No part of this publication may be reproduced, stored in a

retrieval system, or transmitted, in any form or by any means,

electronic, mechanical, photocopying, recording, or

otherwise, without the prior written permission of Echelon

Corporation.

Printed in the United States of America.

Copyright © 1992, 2014 Echelon Corporation.

Echelon Corporation

www.echelon.com

Page 3

Welcome

A LONWORKS® router connects two communications channels within a

ONWORKS network, and routes LonTalk

L

ONWORKS router supports the installation of small or large networks, with

L

dozens to thousands of nodes.

This document describes how to design and develop a L

the Echelon Router 5000 chip, the Echelon FT Router 5000 chip, or the Echelon

RTR-10 Router Core Module.

This document does not describe any of the following Echelon prepackaged router

products: MPR-50 Multi-Port Router, i.LON

3000 Power Line/RF Bridge, or LonPoint Router.

Audience

This guide provides user instructions for users of LONWORKS routers. It also

provides information for developers who plan to develop a L

based on either the Router 5000 chip or the FT Router 5000 chip, or who plan to

integrate the RTR-10 router into embedded or standalone routers.

Related Documen tation

The following manuals are available from the Echelon Web site

(www.echelon.com

applications for Neuron® Chip or Smart Transceiver devices:

) and provide additional information that can help you develop

®

messages between them. Using a

ONWORKS router based on

®

600 LONWORKS/IP Server, CRD

ONWORKS router

• Connecting a Neuron 5000 Processor to an External Transceiver

Engineering Bulletin (005-0202-01D). This bulletin describes how to

connect a Neuron 5000 Processor’s communications port to external

transceivers for TP/XF-1250 channels or for EIA-485 networks, using an

external transceiver circuit. It also describes how to connect a Neuron

5000 Processor to a link-power TP/FT-10 channel using a L

LPT-11 Link Power Transceiver.

• FT 3120 / FT 3150 Smart Transceiver Data Book (005-0139-01D). This

manual provides detailed technical specifications on the electrical

interfaces, mechanical interfaces, and operating environment

characteristics for the FT 3120

• Introduction to the LONWORKS Platform (078-0391-01B). This manual

provides an introduction to the ISO/IEC 14908 (ANSI/CEA-709.1 and

EN14908) Control Network Protocol, and provides a high-level

introduction to L

are used for developing, installing, operating, and maintaining them.

• Junction Box and Wiring Guidelines for Twisted Pair LonWorks Networks

(005-0023-01P). This bulletin identifies the different types of junction

boxes and interconnections that can be used in twisted pair L

networks in building and industrial control applications.

ONWORKS networks and the tools and components that

®

and FT 3150® Smart Transceivers.

ONWORKS

ONWORKS

Page 4

• LonMark

®

Application Layer Interoperability Guidelines. This manual

describes design guidelines for developing applications for open

interoperable L

Web site, www.lonmark.org

ONWORKS devices, and is available from the LonMark

.

• LonWorks FTT-10A Free Topology Transceiver User's Guide (078-0156-

01G). This manual provides specifications and user instructions for the

FTT-10A Free Topology Transceiver.

• LonWorks LPT-11 Link Power Transceiver User's Guide (078-0198-01A).

This manual provides technical specifications on the electrical and

mechanical interfaces and operating characteristics for the LPT-11 Link

Power Transceiver.

• LonWorks TPT Twisted Pair Transceiver Module User's Guide (078-0025-

01C). This manual provides detailed specifications on the electrical and

mechanical interfaces and operating environment characteristics for the

TPT/XF-78 and TPT/XF-1250 transceiver modules.

®

• NodeBuilder

how to develop a L

FX User’s Guide (078-0405-01A). This manual describes

ONWORKS device using the NodeBuilder tool.

• PL 3120 / PL 3150 / PL 3170 Power Line Smart Transceiver Data Book

(005-0193-01C). This manual provides detailed technical specifications

on the electrical interfaces, mechanical interfaces, and operating

environment characteristics for the PL 3120, PL 3150, and PL 3170™

Smart Transceivers.

• Series 5000 Chip Data Book (005-0199-01C). This manual provides

detailed specifications on the electrical interfaces, mechanical interfaces,

and operating environment characteristics for the FT 5000 Smart

Transceiver and Neuron 5000 Processor.

All of the Echelon documentation is available in Adobe

PDF files, you must have a current version of the Adobe Reader

download from Adobe at: get.adobe.com/reader

For information about previous generation Neuron Chips, see one of the Neuron

Chip Data Books: Motorola

Neuron Chip TMPN3150/3120, or Cypress™ Neuron Chip Technical Reference

Manual.

Getting Support

You can get technical support for any of Echelon’s current product offerings by

contacting Echelon Support: www.echelon.com/support

You can also search the Echelon Knowledge Base for known product issues:

www.echelon.com/support/kb/search.asp

of information about Echelon products and technologies, including technical

articles that range from “How to” articles that describe how to complete a specific

task to “Bug” articles that document known issues with Echelon products.

PDF format. To view the

, which you can

.

®

LONWORKS Technology Device Data, Toshiba

.

. The Knowledge Base contains a wealth

iv

Page 5

FCC Notice

The RTR-10 Router Core Module is designed to comply with the limits for a Class

B digital device, pursuant to Part 15 of the FCC Rules. The Router 5000 chip is

designed to comply with FCC Part 15 Subpart B and EN 55022 Level B.

These limits are designed to provide reasonable protection against harmful

interference when the equipment is operated in a commercial environment. This

equipment generates, uses, and can radiate radio frequency energy and, if not

installed and used in accordance with the instruction manual, may cause harmful

interference to radio communications. However, there is no guarantee that

interference will not occur in a particular installation.

Caution: Changes or modifications not covered in this manual must be

approved in writing by the manufacturer’s Regulatory Engineering

department. Changes or modifications made without written approval

may void the user’s authority to operate this equipment.

VDE Notice

The RTR-10 Router Core Module product is designed to comply with VDE 0871

Level B as a peripheral device. To ensure continued compliance, this product

should only be used in conjunction with other compliant devices.

Canadian DoC Notice

The RTR-10 Router Core Module digital apparatus does not exceed the Class A

limits for radio noise emissions from digital apparatus set out in the Radio

Interference Regulations of the Canadian Department of Communications.

L’ appareil RTR-10 Router Core Module numérique n’émet pas de bruits

radioélectriques dépassant les limites applicables aux appareils numériques de la

classe A prescrites dans le règlement sur la brouillage radioélectrique édicté par

le Ministère des Communications du Canada.

Page 6

Page 7

Table of Contents

Welcome ......................................................................................................... iii

Audience ........................................................................................................ iii

Related Documentation ................................................................................ iii

Getting Support ............................................................................................. iv

FCC Notice ..................................................................................................... v

VDE Notice ..................................................................................................... v

Canadian DoC Notice ..................................................................................... v

Introduction to LONWORKS Routers .......................................................... 1

Introduction .................................................................................................... 2

LONWORKS Router Products ...................................................................... 3

RTR-10 Overview ..................................................................................... 4

Router 5000 and FT Router 5000 Overview .......................................... 6

Comparing the RTR-10, Router 5000, and FT Router 5000 ................. 8

Router Types .................................................................................................. 9

Repeater ................................................................................................... 9

Bridge ....................................................................................................... 9

Configured Router ................................................................................... 9

Learning Router..................................................................................... 10

Loop Topology ............................................................................................... 12

Power Line Routers ...................................................................................... 13

LonTalk Protocol Support for Routers ........................................................ 14

Message Buffers ........................................................................................... 14

RTR-10 Message Buffers and Transaction Records ............................ 15

Router 5000 and FT Router 5000 Message Buffers ............................ 18

Router Performance ..................................................................................... 18

LONWORKS Router Electrical Interfaces ................................................ 21

Overview ....................................................................................................... 22

Electrical Interface ....................................................................................... 22

RTR-10 Electrical Interface .................................................................. 22

ACLK2, BCLK1, and BCLK2 ......................................................... 24

ACP[4..0] and BCP[4..0] ................................................................. 24

ASVC~ and BSVC~ ......................................................................... 24

AXID[4..0] and BXID[4..0] .............................................................. 24

PKT .................................................................................................. 26

RESET~ ........................................................................................... 26

SERVICE~ ....................................................................................... 27

Series 5000 Router Electrical Interface ............................................... 27

Router 5000 Pinout ......................................................................... 27

FT Router 5000 Pinout ................................................................... 29

Clock Pins (XIN and XOUT) ........................................................... 32

CP[4..0] – Router 5000 Only ........................................................... 34

NETP and NETN – FT Router 5000 Only ..................................... 35

IO[11..0] ........................................................................................... 36

JTAG Interface (TCK, TDI, TDO, TMS, and TRST~) .................. 37

Memory Interface (CS0~, MISO, MOSI, SCK, SCL, SDA_CS1~) 37

Power and Ground .......................................................................... 37

RST~ ................................................................................................ 38

SVC~ ................................................................................................ 40

Network Activity Indicator – Router 5000 .................................... 43

Network Activity Indicator – FT Router 5000 ............................ 45

Page 8

Power Requirements .................................................................................... 45

RTR-10 Power Requirements ............................................................... 45

Series 5000 Router Power Requirements ............................................ 45

Power Supply Decoupling and Filtering ..................................................... 46

Low Voltage Protection ................................................................................ 46

LONWORKS Router Mechanical Interfaces ............................................. 49

RTR-10 Mechanical Description ................................................................. 50

Series 5000 Router Mechanical Description .............................................. 52

Developing a LONWORKS Router .............................................................. 55

Developing a Router with the RTR-10 Module .......................................... 56

Using Predefined Transceivers ............................................................. 58

Using Custom Transceivers .................................................................. 58

Developing a Router with the Router 5000 Chip ....................................... 59

Using an External Transceiver with the Router 5000 ........................ 60

Using a TP/XF-1250 Transceiver ................................................... 60

Using an EIA-485 Transceiver ....................................................... 64

Using an FTT-10A Transceiver ...................................................... 65

Using an LPT-11 Link Power Transceiver .................................... 68

Example Router 5000 Schematics ........................................................ 71

Developing a Router with the FT Router 5000 Chip ................................. 74

Connecting Half-Routers: Series 5000 and Series 3100 ............................ 76

Configuring a Series 5000 Half-Router ...................................................... 79

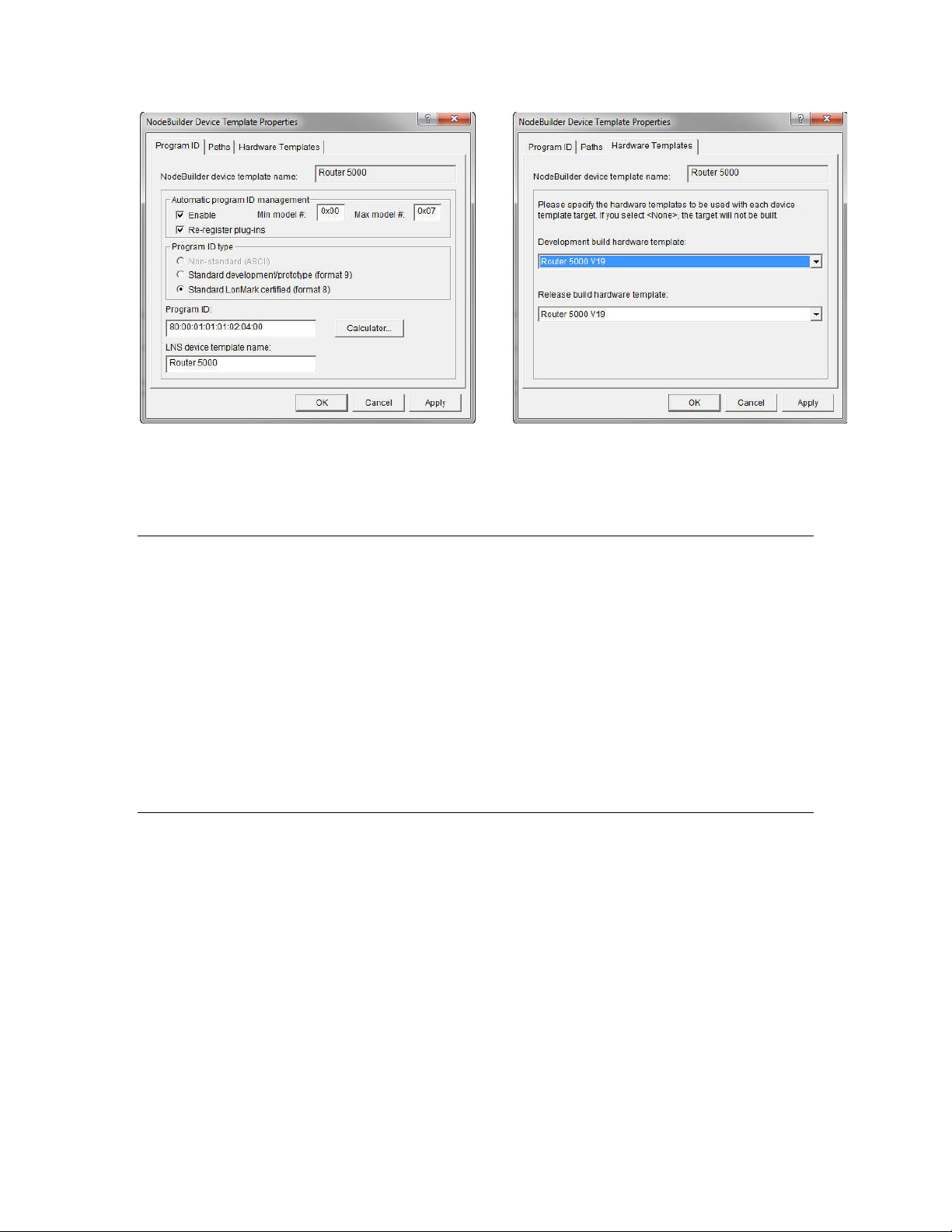

NodeBuilder Hardware Template ........................................................ 80

NodeBuilder Device Template .............................................................. 81

Buffer Configurations ............................................................................ 82

Creating a Pre-Configured NME File .................................................. 82

Example Neuron C Source .................................................................... 83

LONWORKS Router Design Issues ............................................................. 85

PCB Layout Guidelines ............................................................................... 86

Router 5000 ............................................................................................ 86

FT Router 5000 ...................................................................................... 88

EMI Design Issues ....................................................................................... 89

Designing Systems for EMC (Electromagnetic Compatibility) ................. 89

EMC Design Tips ................................................................................... 89

ESD Design Issues ................................................................................ 90

Designing Systems for ESD Immunity ................................................ 90

Installing a LONWORKS Router ................................................................. 93

Introduction .................................................................................................. 94

Defining a Network Topology ...................................................................... 94

Attaching the Router to a Network ............................................................. 94

Connecting Power ........................................................................................ 95

Installing the Router on a Network ............................................................ 96

Router Installation with OpenLNS CT ................................................ 96

Router Installation with Network Management Messages ................ 96

Testing Router Installation ......................................................................... 97

Network Management Messages ................................................................. 99

Introduction ................................................................................................ 100

Standard Messages .................................................................................... 100

Router-Specific Messages .......................................................................... 101

Router-Specific Network Management Messages ............................. 102

viii

Page 9

Set Router Mode ............................................................................ 102

Group or Subnet Table Clear ....................................................... 103

Group or Subnet Table Download ................................................ 103

Group Forward .............................................................................. 103

Subnet Forward............................................................................. 104

Group No Forward ........................................................................ 104

Subnet No Forward ....................................................................... 104

Group or Subnet Table Report ..................................................... 105

Router Status ................................................................................ 105

Far Side Escape Code ................................................................... 106

Router Options Set with Write Memory ............................................ 106

Set Routing Algorithm .................................................................. 106

Set Buffer Size ............................................................................... 106

Set Priority Output Buffer Queue Count .................................... 107

Set Input and Non-Priority Buffer Queue Count ....................... 108

Communications Parameters for LONWORKS Routers ..................... 109

Communications Parameters .................................................................... 110

Determining RTR-10 Firmware Version ................................................. 117

Router Firmware Version .......................................................................... 118

Page 10

Page 11

1

Introduction to LONWORKS Routers

This chapter describes the router theory of operation, including router

types, LonTalk protocol support for routers, and router use of message

buffers.

ONWORKS Router User’s Guide 1

L

Page 12

Introduction

LONW

ORKS

Device 1

LONW

ORKS

Device

2

L

ONWORKS

Device 3

LONW

ORKS

Device 4

TP/XF-1250 Backbone Channel

TP/FT-10 Channel TP/XF-78 Channel

TP/XF-1250

to

TP/FT-10

Router

TP/XF-1250

to

TP/XF-78

Router

In general terms, a router is a device that forwards data packets between

communications networks. The router connects to the data lines from each

network, and reads address information in each data packet to determine the

packet’s destination.

ONWORKS router connects two communications channels within a LONWORKS

A L

network, and routes LonTalk messages between them. Using a L

router supports the installation of small or large networks, with dozens to

thousands of nodes.

Figure 1 shows a typical router installation, with a free topology channel and a

78 kbps bus topology channel connected to a 1.25 Mbps backbone twisted pair

channel. Because the network includes the routers, applications on each of the

ONWORKS devices can communicate with each other transparently, as if they

L

were installed on a common channel.

ONWORKS

A single router can connect two channels, or multiple routers (called redundant

routers) can connect the same pair of channels. Redundant routers provide fault

tolerance by providing more than one routing path from one channel to another.

They are also required when not all devices on a given channel are able to hear

one another (referred to as an “ear shot problem”), for example on a radio

frequency channel. For a router to function as a redundant router, the router

must be configured to be a Configured router (see Router Types).

ONWORKS routers are used to:

L

2 Introduction to LONWORKS Routers

Figure 1. Sample Router Installation

• Extend the limits of a single channel. You can use a router to add a

channel to a L

ONWORKS network to support additional devices or to

extend the maximum channel length. You can add multiple routers,

depending on the capacity or distance needed.

• Interface different communications media, or bit rates, in a L

network. For example, you might want to trade data rate for distance on

portions of the network, or to use a 1.25 Mbps backbone twisted pair

channel to connect several 78 kbps free topology and link power channels.

ONWORKS

Alternatively, you might want to use power line for a portion of the

Page 13

network where the devices are subject to frequent physical relocation, or

if cable installation is difficult. For each of these cases, you use a router

to connect the dissimilar L

ONWORKS channels.

• Enhance the reliability of the L

ONWORKS network. The two channels that

connect to a router are logically isolated, so a failure on one channel does

not affect the other channel. For example, in an industrial control

network, isolation among connected cells might be desirable to prevent a

failure in a single cell from bringing down multiple cells. You can achieve

this goal by dedicating channels to individual cells and isolating them

from one another with routers.

• Improve overall network performance. You can use routers to isolate

traffic within subsystems. For example, in a cluster of industrial cells,

most of the communications might be between devices within cells rather

than across cells. Using intelligent routers across cells avoids forwarding

messages addressed to devices within specific cells, thus increasing the

capacity and decreasing the response time of the overall network.

The use of routers across channels is transparent to the application programs

within devices. Thus, you can develop applications without needing to know the

workings of the routers or even if the device’s channel will use a router. You only

need to consider routers when determining the network image of a device. When

you move a device from one channel to another, you need only change the

network image. Use a network management tool, such as OpenLNS CT, to

manage network images.

LONWORKS Router Products

Echelon provides the following router products:

• MPR-50 Multi-Port Router (Model: 42150)

Five-channel (one TP/XF-1250 channel and four TP/FT-10 channels)

ONWORKS router. The MPR-50 can be used to connect two, three, or

L

four TP/FT-10 channels together, or it can be used to connect these

TP/FT-10 channels to a high-speed TP/XF-1250 backbone.

• i.LON 600 L

ONWORKS/IP Server (Model: 7260x)

An EIA-852 compliant LonTalk-to-IP router. The i.LON 600 provides

secure Internet access to L

ONWORKS devices and transforms the Internet

(or other IP-based network) into a pathway for L

information.

• CRD 3000 Power Line/RF Bridge (Model: 76520R)

A Power Line (PL) to RF communications device, designed primarily for

intelligent L

ONWORKS street lighting networks.

• LonPoint Router (Model: 4210x)

A two-channel router for TP/FT-10, TP/XF-78, or TP/XF-1250 L

channels. Three models are available for various network connection

combinations.

ONWORKS control

ONWORKS

ONWORKS Router User’s Guide 3

L

Page 14

• RTR-10 Router Core Module (Model: 61000R)

A compact module used by OEMs to build L

ONWORKS routers. The RTR-

10 consists of the core electronics and firmware needed to implement a

router.

• Router 5000 (Model: 14315R)

A semiconductor product used by OEMs to build half-routers or full

routers for various L

ONWORKS channel types. The Router 5000 includes

the firmware required to implement a half-router.

• FT Router 5000 (Model: 14285R)

A semiconductor product used by OEMs to build half-routers or full

routers for L

ONWORKS Free Topology (FT) channels. The FT Router 5000

includes the firmware required to implement a half-router.

Packaged routers eliminate the need to build hardware and obtain the necessary

electrical interference and safety certifications. Thus, they allow direct, off-the-

shelf integration into the user’s L

ONWORKS network. This manual does not

describe how to use the Echelon prepackaged router products. See the Echelon

router Web page (www.echelon.com/products/routers

) for information about the

pre-packaged Echelon router products.

This manual describes those Echelon router products that allow OEMs to design

and build their own custom routers for L

ONWORKS channels: the RTR-10 Router

Core Module, the Router 5000 chips, and the FT Router 5000 chips.

RTR-10 Overview

The RTR-10 Router Core Module is a compact module used by OEMs to design

and build L

channels and route LonTalk messages between them. They support installation

of networks with dozens to thousands of devices.

The RTR-10 Module consists of the core electronics and firmware required to

implement a router. Its compact single inline module (SIM) form factor

minimizes the board space required to implement a router. Vertical SIM sockets

are available to minimize board space; right-angle SIM sockets are also available

to minimize component height.

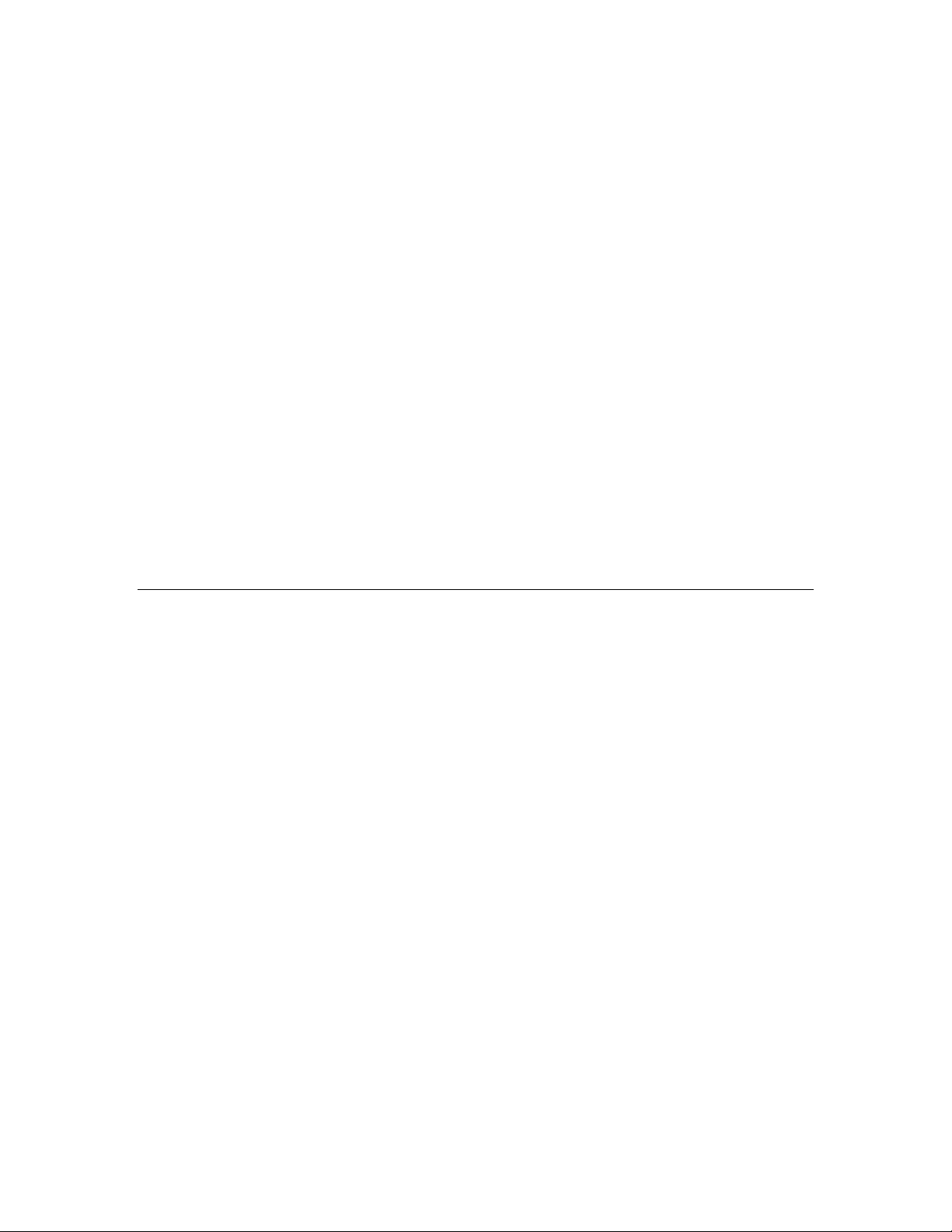

A complete router, using an RTR-10 module, consists of the module, two

transceivers, and a motherboard to connect the RTR-10 router to the two

transceivers, as shown in Figure 2.

ONWORKS routers. A LONWORKS router connects two communications

4 Introduction to LONWORKS Routers

Page 15

RTR-10 Router Core Module

Side A

Transceiver

Side B

Transceiver

Side A

Network

Connector

Side B

Network

Connector

Power Supply

Service

Button and

LEDs

Figure 2. Block Diagram of a LonWorks Router Based on the RTR-10

As the figure shows, an RTR-10 router and two transceiver modules (one to

handle each of two channels connected by the router) can be mounted on a

motherboard, along with a single power supply and two network connectors.

This sub-assembly constitutes a L

ONWORKS router. It can be packaged in an

enclosure to meet unique form factor and environmental requirements.

Depending on the application, the package could contain a single router sub-

assembly, or could include other application-specific hardware. Multiple routers

can be packaged together for some applications, such as a backbone connecting

multiple channels.

The RTR-10 router comes preconfigured with many common L

ONWORKS

transceiver parameters. Two sets of five transceiver identification (XID) pins on

the RTR-10 router select the appropriate transceiver type for each side. The

transceiver ID inputs eliminate a manufacturing step by automatically

configuring the RTR-10 router for most transceivers. A special transceiver ID is

reserved for programming any custom type.

One side of the RTR-10 router has a fixed input clock rate of 10 MHz. This side

can be used with transceivers running at interface bit rates from 9.8 kbps to 1.25

Mbps. The second side of the RTR-10 router can be tied to the 10 MHz output of

the first side, requiring no external components for interface bit rates from 9.8

kbps to 1.25 Mbps. Alternatively, the 10 MHz output can be divided to a lower

frequency with external hardware and used as the input clock for the second side

to support transceivers running at bit rates as low as 610 bps.

Any pair of channel types can be connected by a router by selecting the

appropriate pair of transceivers. The RTR-10 router is compatible with all

ONWORKS Router User’s Guide 5

L

Page 16

LONWORKS transceivers, including standard transceivers for free topology, link

power, twisted pair, and power line. Using multiple communications media can

minimize installation costs and increase system performance by allowing easily

installed media, such as power line or link power, to be combined with high-

performance media such as TP/XF-1250 twisted pair.

Router 5000 and FT Router 5000 Overview

The Router 5000 chip and the FT Router 5000 chip (generically referred to as

Series 5000 router chips) are Echelon semiconductor products, based on the

Echelon Neuron 5000 Core, that are used to build half-routers and full routers for

ONWORKS channels. A LONWORKS router connects two communications

L

channels and route LonTalk messages between them. They support installation

of networks with dozens to thousands of devices.

Both the Router 5000 and FT Router 5000 include the Router firmware required

to implement a half-router. Each chip’s compact form factor minimizes the space

required to develop a half-router. You can implement two half-routers to develop

a full router for the same, or different, external transceiver types.

The FT Router 5000 integrates the high performance Neuron 5000 Core with a

free topology (FT) twisted pair transceiver. Thus, the FT Router 5000 supports

ONWORKS TP/FT-10 channel type.

the L

Table 1 lists commonly used channel and transceiver types for Router 5000-

based router halves; see Developing a Router with the Router 5000 Chip for

additional information about connecting a Router 5000 chip to these external

transceiver types. These external transceivers can run at interface bit rates from

9.8 kbps to 1.25 Mbps.

Table 1. Common Channel and Transceiver Types for a Router 5000

Channel Type Transceiver for Half Router Notes

TP/FT-10 Echelon FTT-10A Free Topology

Transceiver (Model 50051)

TP-RS485 Any EIA-485 transceiver Can use any standard 3.3V or 5V

TP/XF-78 Echelon TPT Twisted Pair

Transceiver Module (Model 50010)

TP/XF-1250 Echelon TPT Twisted Pair

Transceiver Module (Model 50020)

Connection to the Router 5000 is

similar to the connection to a

Neuron Chip.

Use an FT Router 5000 for a

standard (non-link-powered)

TP/FT-10 channel or for a locally

powered device on a link-power

TP/FT-10 channel.

EIA-485 transceiver.

Add differential driver and

differential comparator circuits

(contact Echelon Support).

Add differential driver and

differential comparator circuits.

6 Introduction to LONWORKS Routers

Page 17

Channel Type Transceiver for Half Router Notes

Side A

Transceiver

Side B

Transceiver

Side A

Network

Connector

Side B

Network

Connector

Power Supply

Service

Buttons and

LEDs

Router 5000

Half Router

Router 5000

Half Router

Side A

Network

Connector

Side B

Network

Connector

Power Supply

Service

Buttons and

LEDs

FT Router

5000

(with FT-X3)

Half Router

FT Router

5000

(with FT-X3)

Half Router

LonWorks Router Based on the

Router 5000

LonWorks Router Based on the

FT Router 5000

Link-power Echelon LPT-11 Link Power

Transceiver (Model 50040)

Echelon provides special licensing for other transceiver types, such as a Power

Line Smart Transceiver; contact Echelon Support for additional information.

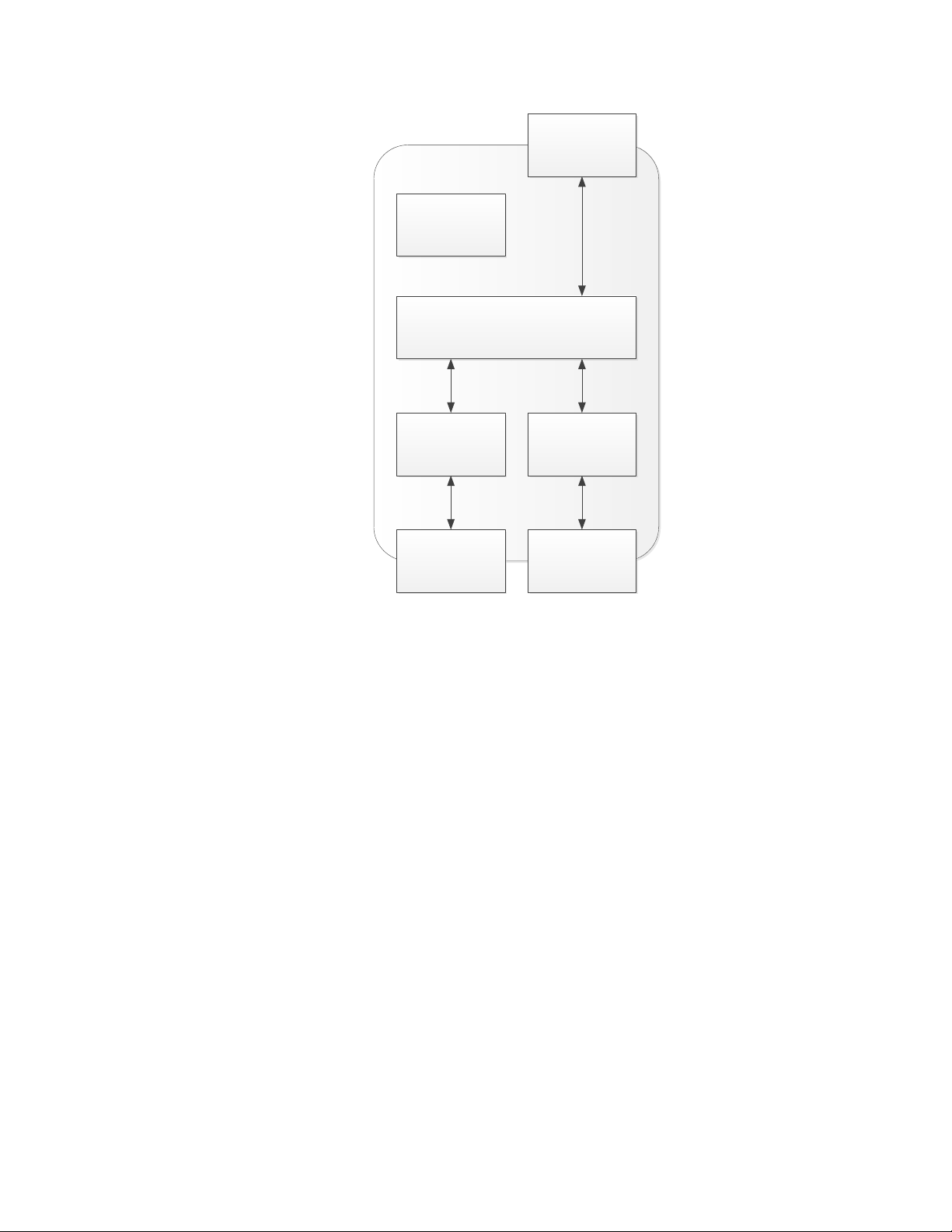

A complete router using the Router 5000 consists of two Router 5000 half routers,

two transceivers, and a motherboard to connect the two half routers. A complete

router using the FT Router 5000 consists of two FT Router 5000 half routers

(each with its own FT-X3 Communications Transformer), and a motherboard to

connect the two half routers. Figure 3 shows block diagrams of both types of

Series 5000 based routers.

Add linear regulator and TX buffer

circuit.

Figure 3. Block Diagrams of L

ONWORKS Routers Based on a Series 5000 Router Chip

In the left side of the figure, two Router 5000 half routers and two transceiver

ONWORKS Router User’s Guide 7

L

modules, one to handle each of two channels connected by the router, can be

mounted on a motherboard, along with a single power supply and two network

connectors. This sub-assembly constitutes a L

of the figure, two FT Router 5000 half routers, one to handle each of two channels

connected by the router, can be mounted on a motherboard, along with a single

ONWORKS router. In the right side

power supply and two network connectors. This sub-assembly constitutes a

Page 18

LONWORKS router. Although not shown in the figure, you can place a Router

5000 half router (with its transceiver module) and FT Router 5000 half router on

the same motherboard to create a L

ONWORKS router.

A complete L

form factor and environmental requirements. Depending on the application, the

package could contain a single router sub-assembly, or could include other

application-specific hardware. Multiple routers can be packaged together for

some applications, such as a backbone connecting multiple channels.

Unlike an RTR-10 router, you store the L

each Router 5000 or FT Router 5000 half router in external EEPROM, thus

allowing you to define the appropriate transceiver type for each side.

ONWORKS router can be packaged in an enclosure to meet unique

ONWORKS transceiver parameters for

Comparing the RTR-10, Router 5000, and FT Router 5000

Table 2 lists some of the major characteristics of the three router products

described in this manual.

Table 2. Comparing the RTR-10, Router 5000, and FT Router 5000

Parameter RTR-10 Router 5000 FT Router 5000

Package Integrated module with

both A side and B side

Voltage 5 V 3.3 V 3.3 V

7mm x 7mm QFN chip 7mm x 7mm QFN chip

Clock rate 10 MHz A side

≤10 MHz B side

Router Buffers 1408 bytes 25 KB 25 KB

Transceivers Any TP/FT-10

The main difference between the Router 5000 and the FT Router 5000 is their

transceiver support. The FT Router 5000 supports only the TP/FT-10 channel,

but because the transceiver is integrated into the chip, you do not need to use an

FTT-10A Free Topology Transceiver (and associated circuitry to accommodate the

different voltage standards between the half router and transceiver).

5, 10, 20, or 40 MHz

system clock

(10 MHz crystal)

TP-RS485

TP/XF-78

TP/XF-1250

LPT-11 Link-power

Other (contact Echelon

Support)

5, 10, 20, or 40 MHz

system clock

(10 MHz crystal)

TP/FT-10

(requires an FT-X3

Communications

Transformer)

8 Introduction to LONWORKS Routers

Page 19

Router Types

A LONWORKS router can use one of four routing algorithms: configured router,

learning router, bridge, and repeater. This selection allows you to trade system

performance for ease of installation. The configured router and learning router

algorithms create intelligent routers that selectively forward messages based on

network topology. Both sides of a router must use the same routing algorithm.

The following general rules apply to all four routing algorithms:

• For a message to be forwarded, it must fit into the router’s input and

output message buffers. A free input message buffer must be available.

• For a message to be forwarded, it must have a valid cyclic redundancy

check (CRC) code.

• Priority messages are forwarded as priority messages, but with the

priority level of the transmitting side rather than the priority level of the

originator of the message. If the transmitting side has not been installed

with a priority value, then priority messages are not forwarded in a

priority slot. The priority message is still flagged as a priority message,

so that if it passes through a second router that is installed with a

priority level, the second router transmits the message in a priority slot.

Repeater

A Repeater is a router that forwards all messages in both directions, regardless of

the message’s destination or domain. That is, a repeater forwards all valid

messages (that is, messages with a valid CRC code) to the other channel.

A Permanent Repeater behaves similarly, but its type cannot be changed after

creation.

Bridge

A Bridge is a router that forwards all messages received on either of the router’s

domains, regardless of the message’s destination. That is, a bridge forwards

packets received on one channel to the other channel, if the packet is sent on a

domain to which the bridge belongs. Use a bridge to span domains. In a single

domain network, a bridge functions essentially the same as a repeater.

A Permanent Bridge behaves similarly, but its type cannot be changed after

creation.

Configured Rout er

A Configured Router determines which packets to forward based on internal

routing tables. A configured router forwards only those messages which are

received on either of the router’s domains and which meet the forwarding rules

shown in Figure 4 and Figure 5. Configured routers maintain their routing

tables in non-volatile memory, and thus retain them after a reset. These tables

control forwarding of subnet and group-addressed messages, and are managed by

a network management tool.

ONWORKS Router User’s Guide 9

L

Page 20

A forwarding table is used for each domain on each side of the router. Each

forwarding table contains a forwarding flag for each of the 255 subnets and 255

groups in a domain. As shown in Figure 4 and Figure 5, these flags determine

whether or not a message should be forwarded or dropped based on the

destination subnet or group address of the message.

A network management tool initializes the forwarding tables using the network

management messages described in Chapter 7, Network Management Messages,.

By configuring the routing tables based on network topology, a network

management tool can optimize network performance and make the most efficient

use of available bandwidth. Configured routers should be used for looping

topologies; see Loop Topology.

For a L

volatile memory (typically EEPROM) and one in RAM. The non-volatile table is

copied to the RAM table when the router is initially powered-up, after a reset,

and when the router receives the Set Router Mode command with the Initialize

Routing Table option. The RAM table is used for all forwarding decisions.

Several of the operations in shown in Figure 4 and Figure 5 help prevent

message loops for service-pin messages. Service-pin messages require special

handling because they are broadcast to all nodes on the zero-length domain, and

have a source subnet ID of zero. When a router receives a service-pin message

with a source subnet ID of zero, the router modifies the source subnet field of the

message to be the router’s subnet on the receiving side. If the receiving side is

installed in two domains, two service-pin messages are forwarded, one for each

domain. Thus, the router can drop the service-pin message if a loop causes the

message to be received again on the same side.

ONWORKS router, there are two sets of forwarding tables, one in non-

Learning Router

A Learning Router, like a configured router, determines which packets to forward

based on internal routing tables. A learning router forwards only those messages

which are received on either of the router’s domains and which meet the

forwarding rules shown in Figure 4 and Figure 5. A learning router always

forwards all group-addressed messages. Learning routers maintain their routing

tables in non-volatile memory, and thus retain them after a reset. These tables

control forwarding of subnet and group-addressed messages, and are updated

automatically by the router firmware, rather than their being configured by a

network management tool. The group forwarding tables are configured to always

forward (flood) all messages with group destination addresses.

When a router receives a packet with a destination address using a subnet ID, it

uses the subnet ID to determine whether to forward the packet. Learning

routers learn network topology by examining the source subnet of all messages

received by the router. Whenever a learning router receives a packet from one of

its channels, it uses the source subnet ID to learn the network topology. It sets

the corresponding routing table entries to indicate that the subnet in question is

to be found in the direction from which the packet was received. Because subnets

cannot span two channels connected to an intelligent router, the router can learn

which side a subnet is on whenever that subnet ID appears in the source address.

The subnet forwarding tables are initially configured to forward all messages

with subnet destination addresses. Each time a new subnet ID is observed in the

source address field of a message, its corresponding flag is cleared (that is,

forwarding is disabled) in the subnet forwarding table. The forwarding flag for

10 Introduction to LONWORKS Routers

Page 21

the destination address is then checked to determine whether the message

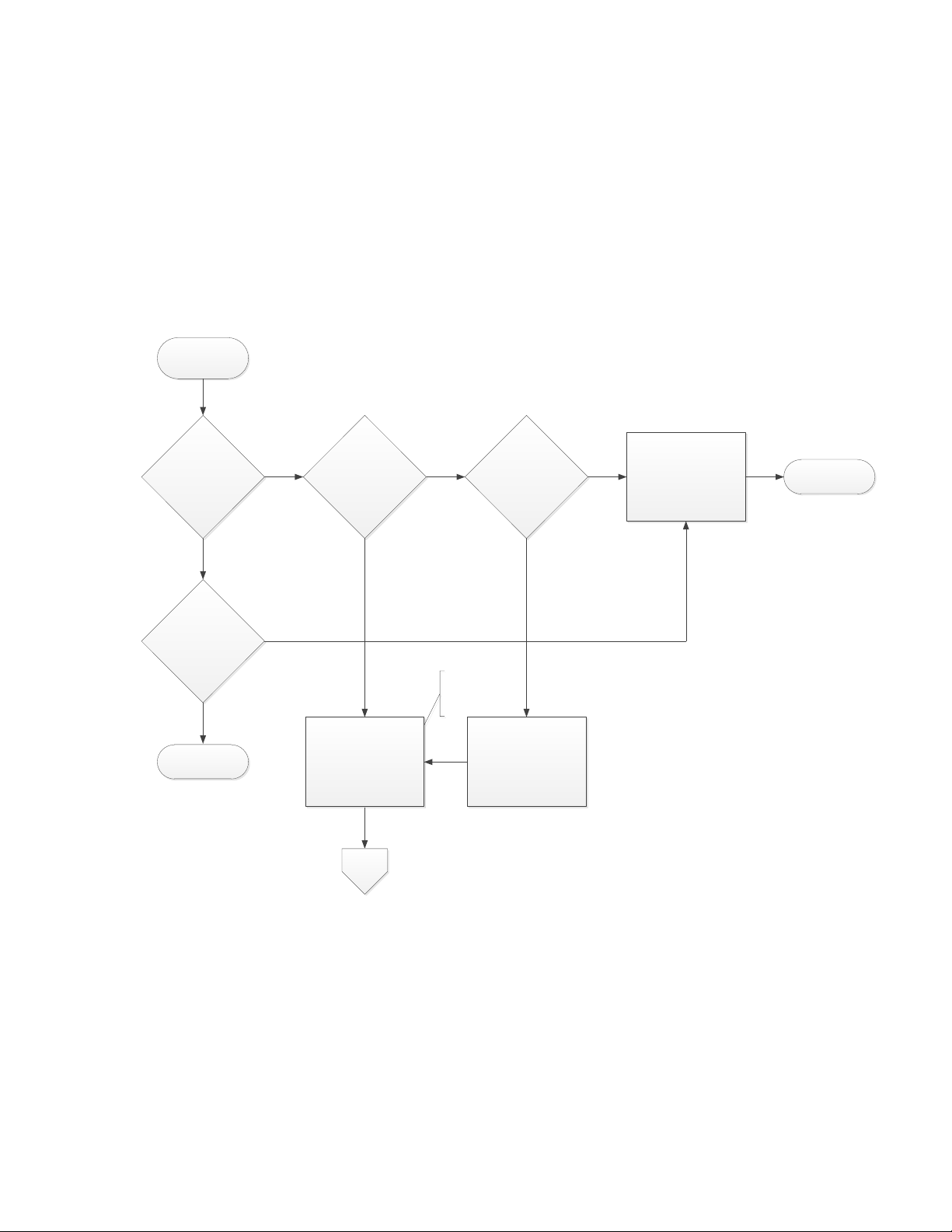

Router receives

message packet

Is message addressed

to either of the router’s

domains?

Is message domain

length zero,

source

subnet zero

, addressed

as broadcast?

Drop packet

Is message source

subnet zero

?

Is message domain

length zero

,

addressed

as broadcast?

Clear subnet fwd flag

Set message source subnet

=

router subnet

Substitute one or both

domains from the router

,

source subnet = our

subnet, dest subnet zero

Forward one or two

packets

No

Yes Yes

Yes

No

Yes

No No

Page 2

*

Applies to

learning

router only

should be forwarded or dropped. The forwarding flags are all cleared whenever

the router is reset, so the learning process restarts after a reset.

The forwarding flag for a given subnet should never be cleared on both sides of a

router. However, the flag can be cleared on both sides if a device is moved from

one side of a router to the other side. For example, if subnet 1 is located on side

A of a router, the router will learn subnet 1’s location as soon as it receives a

message generated by any device in subnet 1. If any subnet 1 device is moved to

side B without reinstalling it, the router will learn that subnet 1 is also on side B,

and will stop forwarding subnet 1 messages to side A. The router detects this

error and logs it, as described in Chapter 7, Network Management Messages.

Figure 4. Configured and Learning Router Forwarding Rules, Part 1

ONWORKS Router User’s Guide 11

L

Page 22

Is message addressed

to group

?

Is message addressed

to subnet

/node

?

Message must be

addressed as broadcast or

48

-bit Neuron ID

Is the group fwd flag

of the dest group set to

forward

?

Drop packet

Is the subnet fwd flag

for the dest subnet set

to forward

?

Is the subnet fwd flag

for the source subnet

set to forward

?

Drop packet

Is message dest subnet

=

zero?

Yes

Yes

Yes

No

No

Yes

No

No

Yes

No

A

Yes

A

No

B

B

Page

1

Forward packet

*

Applies to

configured

router only

Figure 5. Configured and Learning Router Forwarding Rules, Part 2

As with configured routers, learning routers sometimes modify source addresses

for service-pin messages to help prevent message loops.

Learning routers, in general, are less efficient in using channel bandwidth

because they always forward all messages with group destination addresses.

Their advantage is simplified installation because the installation tool does not

need to know the network topology to configure the router.

Loop Topology

A looping topology is a network topology that has the potential for message loops.

A loop is a path through two or more routers that forwards a message from a

channel to itself. For example, Figure 6 shows a looping topology with two

channels and two routers. A message on channel A could be forwarded by router

12 Introduction to LONWORKS Routers

Page 23

1 to channel B, then the same message could be forwarded by router 2 back to

Channel A

Router 1 Router 2

Channel B

channel A, starting an endless loop of forwarded messages.

Figure 6. Looping Topology

The LonTalk protocol does not support topologies where loops can occur.

However, looping topologies can be desirable for the following reasons:

• Increased Reliability. Redundant routers can increase system reliability

by providing multiple paths between two channels.

• Support for Open Media. Open media (such as radio frequency [RF]

communications) might require redundant routers with overlapping

coverage to ensure complete coverage of an area.

You can use configured routers (see Configured Router) to support looping

topologies by configuring the routers to prevent message loops. For example, the

topology in Figure 6 can be supported if both routers are configured to forward

all messages addressed to subnets on channel B from channel A; and all

messages addressed to subnets on channel A from channel B. Any groups with

members on both channels can only be forwarded by one of the two routers.

Network management tools, such as OpenLNS CT, can automatically set up the

forwarding tables for configured redundant routers.

Power Line Router s

A looping topology can be inadvertently created when using power line (PL)

media. Passive coupling between different phases of a power line system can

cause packets transmitted on one phase to be received by devices installed on

another phase. A loop can be formed when active coupling provided by a router is

combined with passive coupling. Figure 7 shows an example looping topology

with a power line router.

ONWORKS Router User’s Guide 13

L

Page 24

PL Phase A

Power Line

Router

Passive

Coupling

PL Phase B

Figure 7. A Looping Topology with One Router

Routers can be used between power line channels only if the two channels are

fully isolated. Such isolation is generally not the case between two phases on the

same circuit, but can be the case between phases on different distribution

transformers. Use an Echelon PLCA-22 Power Line Communication Analyzer to

confirm isolation between power line channels before installing power-line-topower-line routers.

LonTalk Protocol Support for Routers

The LonTalk protocol1 is designed to provide transparent routing of messages

between devices that communicate through routers. To increase the efficiency of

routers, the LonTalk protocol defines a hierarchical form of addressing using

domain, subnet, and device (node) addresses. An intelligent router operates at

the subnet level. The router determines which subnets lie on each of its two

sides, and forwards packets accordingly.

Subnets do not span intelligent routers, which allow intelligent routers to make

routing decisions based on the subnet component of a device’s logical address. To

further facilitate the addressing of multiple dispersed devices, the LonTalk

protocol defines another class of addresses using domain and group addresses.

Intelligent routers also can be configured to make routing decisions based on the

group addressing component of a message.

In general, a network management tool, such as OpenLNS CT, is responsible for

domain, subnet, node, and group address assignments.

See the ISO/IEC 14908 Control Network Protocol specification for detailed

information about the LonTalk protocol.

Message Buffers

As messages are received by a router, they are placed in an input buffer queue. By

default, this queue is limited to two message buffers to ensure that priority

messages are never enqueued behind more than one non-priority message. When

forwarded to the transmitting side of the router, priority messages have their own

1

Echelon’s implementation of the ISO/IEC 14908 Control Network Protocol is called the

LonTalk protocol. Echelon has implementations of the LonTalk protocol in several product

offerings, including the Neuron firmware, OpenLNS

network interfaces. This document refers to the ISO/IEC 14908-1 Control Network Protocol

as the “LonTalk protocol,” although other interoperable implementations exist.

14 Introduction to LONWORKS Routers

®

Server, SmartServers, and various

Page 25

outgoing buffer queue. Thus, priority processing of these outgoing messages is

1 2

1 2

1 2 3

N - 1 N

Message Receiving Side

Message Sending Side

Input Buffer Queue

Priority Output Buffer Queue

Normal Output Buffer Queue

Direction of Message Flow

assured because the transmitting side will send messages from the priority output

buffer queue before sending messages from the non-priority output buffer queue.

Figure 8 shows the message flow through the input and output buffer queues. This

message flow is duplicated for messages moving in the opposite direction, that is,

another set of input and output buffer queues exist for messages flowing in the

opposite direction.

Figure 8. Buffering Scheme for a L

ONWORKS Router

The size and count of the message buffers is limited by the amount of RAM on

the router.

RTR-10 Message Buffers and Transact i on Records

There are three different versions of the router firmware for the RTR-10 router.

To determine the router firmware version of your router, see Appendix B,

Determining RTR-10 Firmware Version.

Some versions of the RTR-10 routers were shipped with a reduced buffer and

transaction record capacity. This does not impact system performance. However, a

catastrophic failure of the router can occur if the buffers or transaction records on a

router with reduced buffer and transaction record capacity are reconfigured and

assume that a larger buffer and transaction record space is available. This could

occur if you are using a manufacturing test station to reconfigure routers based on

the higher router buffer and transaction record capacity. It can also occur if you

use a network installation tool that reconfigures router buffers or transaction

records when replacing a router using a non-standard configuration. The failure

condition that occurs is that the router will go into the application-less state and

will no longer function as a router. This failure mode cannot be recovered in the

field. If you are making the change with a tool based on the OpenLNS Server or

the OpenLNS Commissioning Tool (or LNS and the LonMaker Turbo Integration

Tool), in some cases, the tool will prevent an invalid configuration; however, in

other cases the tool may allow an invalid configuration and the router will fail. Use

the tables, below, to understand the correct buffer and transaction record

configurations for your RTR-10 router.

Depending on your firmware, buffers and transaction records are allocated

according to the following tables. For versions A and C, Table 3 shows the

transaction record configurations for receive and transmit transactions, and the

ONWORKS Router User’s Guide 15

L

Page 26

buffer configurations for input buffers, output buffers, priority buffers, and non-

Application Buffer In

1

42

42

lication

Receive Transaction Record

3

13

39

Application Buffer In

1

42

42

priority buffers.

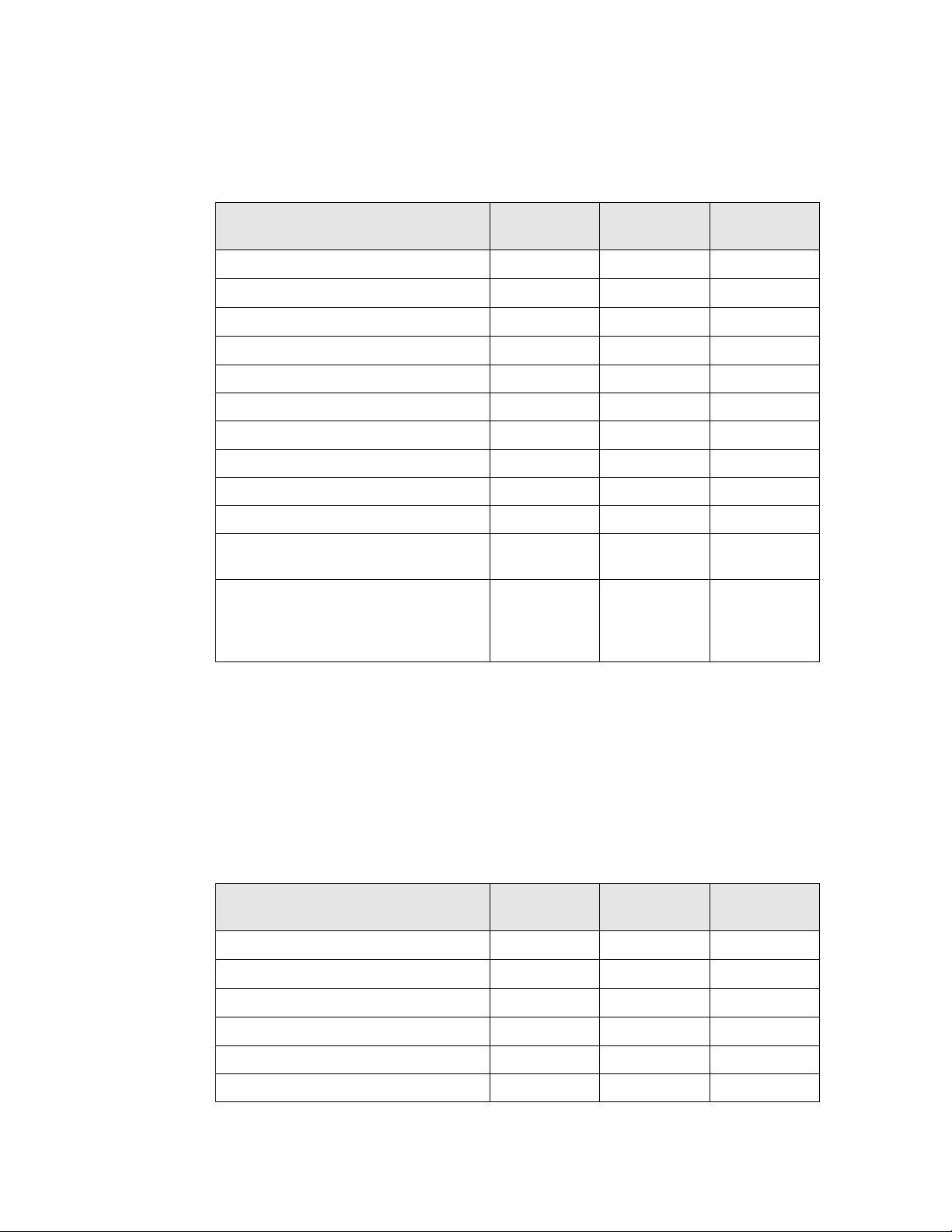

Table 3. RTR-10 Default Buffer and Transaction Record Configuration,

Firmware A and C

Size

Type Count

Receive Transaction Record 3 13 39

Transmit Transaction Record 2 28 56

Application Buffer Out 1 42 42

Network Buffer In 2 66 132

Network Buffer Out 15 66 990

(Bytes) Total Bytes

App

Network Buffer Out Priority 2 66 132

Total Allocated Bytes 1475

Unused 1 25 25

Total Available Bytes for Transaction

Records and Buffers

Total Available Bytes for Buffers,

including Default Transaction

Records shown in first two lines,

above

The default buffer sizes allow the router to handle packets with maximum

address overhead and data size for any network variable message and explicit

messages with up to 40 bytes of data; this is large enough for any network

management or network diagnostic message.

For RTR-10 routers with version B firmware, Table 4 shows the transaction

record configurations for receive and transmit transactions, and the buffer

configurations for input buffers, output buffers, priority buffers, and non-priority

buffers.

Table 4. RTR-10 Default Buffer and Transaction Record Configuration,

Buffer Out Priority

Firmware B

1 42 42

1500

1405

16 Introduction to LONWORKS Routers

Size

Type Count

Transmit Transaction Record 2 28 56

Application Buffer Out 1 42 42

Network Buffer In 3 66 198

Network Buffer Out 11 66 726

(Bytes) Total Bytes

Page 27

Application Buffer Out Priority

1 42 42

Network Buffer Out Priority 3 66 198

Total Allocated Bytes 1343

Unused 1 65 65

Total Available Bytes for Transaction

Records and Buffers

1408

Total Available Bytes for Buffers,

including Default Transaction

Records shown in first two lines,

1313

above

You will not have a problem interchanging routers with Router Firmware

Versions A, B, or C if you are not changing the router buffer or transaction record

configuration. If you need to change the configuration, make sure that the total

number of bytes required for the buffers and transaction records does not exceed

the capacity for the version of the router firmware that you are using. For

example, to use the OpenLNS Commissioning Tool or the LonMaker Turbo

Integration Tool to safely change the buffer configuration for a router, right-click

the router shape in the OpenLNS CT or LonMaker drawing and then click

Properties on the shortcut menu. Click the Buffers tab to display and change

the buffer configuration. As you change the buffer configuration, the required

memory for each side of the router for your buffer configuration is displayed

under the Memory heading. Verify that the memory required is less than the

buffer capacity listed in Table 3 or Table 4 (as appropriate for your router

firmware version) before clicking OK or Apply. When you click OK or Apply,

the buffer configuration you selected is written to the router if you are attached

to the network and you are OnNet. If the memory required is larger than the

buffer and transaction record capacity, the router will fail to operate.

In applications that must route large explicit messages with more than 40 bytes

of data, the buffer size must be increased, and the count of nonpriority buffers

decreased. See the Neuron C Programmer’s Guide to understand how the

network buffer sizes are calculated. See Network Management Messages in this

guide for a description of how to change the size and count of buffers. You can

also use the NodeUtil Node Utility, which you can download from the Echelon

Web site. However you allocate the transaction record counts and the buffer

sizes and counts, the total memory required by the transaction records and buffer

must not exceed the total available memory size in Table 3 or Table 4 (as

appropriate for your router firmware version).

The default buffer configuration places the bulk of the buffers on the output

queues of the router. The reasoning behind this configuration is to keep buffered

packets on the output queues, after they have been processed for forwarding.

This processing includes checking for priority packets. Priority packets are

sensed and forwarded through the router’s priority output buffers, so that

priority packets are processed as quickly as possible, rather than allowing them

to be delayed behind non-priority packages in a large input queue.

There are applications, however, where the network traffic can be “bursty”,

where many packets appear on the network almost at the same time. In these

cases, the traffic bursts could cause the input queue to become full and lose

excess packets.

ONWORKS Router User’s Guide 17

L

Page 28

In this case, reduce the number of lost messages by moving more of the packet

Priority Output Buffer Queue

2

255

510

buffering from the output queue to the input queue by increasing the size of the

input queue and decreasing the size of the output queue. A router with a larger

input queue can handle larger bursts of traffic, at the risk of priority messages

being queued behind a number of non-priority messages.

Router 5000 and FT Router 5000 Message Buffers

Each router side has maximum 26 623 bytes of buffer space available. Because

both the Router 5000 and FT Router 5000 have sufficient RAM available for any

router configuration, you can allocate this space with any combination of buffers,

for example, seven input buffers, two priority output buffers, and seven nonpriority buffers. You can specify any valid buffer size (see the Neuron C

Programmer’s Guide for information about valid buffer sizes), but, in general,

there is no reason not to specify the maximum size of 255 bytes. Table 5 shows a

general buffer configuration.

Table 5. General Series 5000 Router Buffer Configuration

Queue Count

Input Buffer Queue 7 255 1785

Non-Priority Output Buffer Queue 7 255 1785

Total 4080

The buffer size of 255 bytes allows the router to handle packets with maximum

address overhead and data size for any network variable message or explicit

message. See Configuring a Series 5000 Half-Router for a description of how to

change the size and count of buffers. However you allocate the buffer sizes and

counts, the total memory required by the three buffer queues must not exceed 25

K bytes.

The general buffer configuration shown in Table 5 balances the buffers between

the input and output queues of the router. For systems with large bursts of

traffic, you could specify additional non-priority output buffers. Priority packets

are sensed and forwarded through the router’s priority output buffers, so that

priority packets are processed as quickly as possible, rather than allowing them

to be delayed behind non-priority packages in a large input queue.

Router Performance

A major criterion of router performance is network throughput. An optimal

router would be able to forward traffic at the wire-rate, with zero packet loss and

minimal delay. Thus, an optimal router would forward traffic from 9.8 kbps to

1.25 Mbps, depending on the router’s transceiver type.

Size (Bytes)

Total Bytes

18 Introduction to LONWORKS Routers

A real router typically does not perform at the wire-rate because of latency within

the router, including the time to receive and buffer the incoming packet at the

near side, the time to forward the packet between the halves, and the time to

buffer and transmit the packet at the far side. You should measure your router

device’s latency to determine if its design meets your system’s needs.

Page 29

Example: For a 20 MHz Router 5000 device (where both halves use the Router

5000 chip), a measured data transfer rate for sending a service-pin message

between the router halves was approximately 1.2 μs per byte (or 830 kbytes/sec).

Some additional latency was seen for the time between the beginning of the

original packet transmission and the beginning of the forwarded packet

transmission.

For slower channel types, this router latency is not significant, but could become

significant for faster channel types.

The latency between router halves is relatively invariant, with respect to router

configuration, whereas overall router latency depends on the router type and

configuration. For an RTR-10 device, the maximum data transfer rate between

router halves is approximately 2.4 μs per byte (or 416 kbytes/sec). For a Router

5000 device (where both halves use the Router 5000 chip), the maximum data

transfer rate between router halves is approximately 600 ns per byte (or 1.6

Mbytes/sec, assuming a 40 MHz system clock for both halves; this rate scales

with the system clock setting). An FT Router 5000 performs similarly to the

Router 5000.

ONWORKS Router User’s Guide 19

L

Page 30

Page 31

2

LONWORKS Router Electrical

Interfaces

This chapter provides an overview of the electrical interfaces for the

RTR-10 Router Core Module, the Router 5000 chip, and the FT Router

5000 chip.

ONWORKS Router User’s Guide 21

L

Page 32

Overview

This chapter describes the electrical interface and power requirements for a

ONWORKS router.

L

Electrical Interface

The following sections describe the electrical interface for a LONWORKS router,

including detailed descriptions of each of the RTR-10, Router 5000, and FT

Router 5000 pins.

RTR-10 Electrical Interface

Figure 9 shows a schematic view of a connector for the RTR-10 Router Core

Module, and Table 6 shows the pinout of the RTR-10 Router Core Module. See

the Neuron Chip Data Book for more information about the use of the Neuron

Chip communications port pins.

Figure 9. RTR-10 Header Pinout

Table 6. RTR-10 Pinout

Pin Name Pin Description Pin Number

ACLK2 A-side output clock 27

ACP0 A-side network communication port 0 8

ACP1 A-side network communication port 1 7

ACP2 A-side network communication port 2 6

ACP3 A-side network communication port 3 9

ACP4 A-side network communication port 4 5

22 LONWORKS Router Electrical Interfaces

Page 33

Pin Name Pin Description Pin Number

ASVC~ A-side Service output 12

AXID0 A-side transceiver ID 0 (LSB) 20

AXID1 A-side transceiver ID 1 18

AXID2 A-side transceiver ID 2 17

AXID3 A-side transceiver ID 3 16

AXID4 A-side transceiver ID 4 (MSB) 15

BCLK1 B-side input clock 29

BCLK2 B-side output clock 33

BCP0 B-side network communication port 0 37

BCP1 B-side network communication port 1 38

BCP2 B-side network communication port 2 39

BCP3 B-side network communication port 3 36

BCP4 B-side network communication port 4 40

BXID0 B-side transceiver ID 0 (LSB) 22

BXID1 B-side transceiver ID 1 24

BXID2 B-side transceiver ID 2 23

BXID3 B-side transceiver ID 3 21

BXID4 B-side transceiver ID 4 (MSB) 19

BSVC~ B-side Service output 28

GND Ground 1, 2, 3, 11, 26, 30, 32, 34

PKT Packet forward output 14

RESET~ Reset input and output) 25

SERVICE~ Combined Service input 13

VCC +5 VDC input 10, 31

NC No Connect 4, 35

LONWORKS Router User’s Guide 23

Page 34

ACLK2, BCLK1, and BCLK2

A 10 MHz crystal is provided for Side A of the RTR-10 router, which can run at

only 10 MHz. This clock rate allows Side A to be used with transceivers running

at interface bit rates from 9.8 kbps to 1.25 Mbps. The 10 MHz clock is output on

the ACLK2 pin, which allows Side B to be tied directly to the same clock through

pin BCLK1. Thus, no external components are required to support the same

range of bit rates on Side B.

The 10 MHz output can be divided to a lower frequency with external hardware,

and used as the input clock for Side B to support transceivers running at

interface bit rates as low as 610 bps.

ACLK2 can drive five LS-TTL loads.

ACP[4..0] and BCP[4..0]

The ACP[4..0] and BCP[4..0] signals are connected to the CP[4..0] pins of the

core module Neuron Chips. The function of these pins is described in the Neuron

Chip Data Book.

ASVC~ and BSVC~

Each side of the RTR-10 router has an independent service-pin output: ASVC~

for the A Side and BSVC~ for the B Side. You can connect these output pins to

service LEDs, as shown in Figure 27 (in chapter 4). The function of the service

pin is described in the Neuron Chip Data Book. The internal pullup resistor for

the service pin on each side is enabled.

The service LEDs reflect the firmware status:

• Blinking means that the router side is unconfigured

• Off means that the side is configured

• On means that the side has failed

AXID[4..0] and BXID[4..0]

The RTR-10 router comes preconfigured with many common LONWORKS

transceiver parameters. Two sets of five transceiver identification (ID) pins on

the RTR-10 router select the appropriate transceiver type for each side. The

transceiver ID inputs eliminate a manufacturing step by automatically

configuring the RTR-10 router for most transceivers. A special transceiver ID is

reserved for programming any custom transceiver type; this value causes the

communication port pins to be configured as inputs so that no line will be driven

by both the transceiver and RTR-10 Neuron before the RTR-10 Neuron Chips can

be properly configured.

The RTR-10 firmware reads the transceiver ID inputs on power up and reset. If

the router is being powered-up for the first time, or if the transceiver ID is

different from the last time it was powered-up, the parameters specified in the

table on page 25 are loaded. If the router is being re-powered-up, and the

transceiver ID is not 30 (0x1E), the RTR-10 firmware compares the network bit

rate and input clock for the specified transceiver to the current transceiver

parameters. If these parameters do not match, all transceiver parameters are

24 LONWORKS Router Electrical Interfaces

Page 35

reinitialized. This reinitialization allows a network services tool to change

parameters, such as the number of priority slots, without the new values’ being

overwritten by the RTR-10 firmware.

Table 7. RTR-10 Router Transceiver IDs

ID Name Media

Bit Rate

(bps)

Input

Clock

01 (0x01) TP/XF-78 Transformer-isolated twisted pair 78k 10 MHz

03 (0x03) TP/XF-1250 Transformer-isolated twisted pair 1.25M 10 MHz

04 (0x04) TP/FT-10 Free Topology and Link Power 78k 10 MHz

05 (0x05) TP/RS485-39 EIA-485 twisted pair 39k 10 MHz

07 (0x07) RF-10 Radio Frequency (49 MHz) 4.9k 5 MHz

09 (0x09) PL-10 Power Line spread-spectrum 10k 10 MHz

10 (0x0A) TP/RS485-625 EIA-485 twisted pair 625k 10 MHz

11 (0x0B) TP/RS485-125 EIA-485 twisted pair 1.25M 10 MHz

12 (0x0C) TP/RS485-78 EIA-485 twisted pair 78k 10 MHz

16 (0x10) PL-20C Power Line C-Band 5.4k 10 MHz

17 (0x11) PL-20N Power Line C-Band 5.4k 10 MHz

18 (0x12) PL-30 Power Line A-Band 2.7k 10 MHz

24 (0x18) FO-10 Direct Connect 1.25M 10 MHz

27 (0x1B) DC-78 Direct Connect 78k 10 MHz

28 (0x1C) DC-625 Direct Connect 625k 10 MHz

29 (0x1D) DC-1250 Direct Connect 1.25M 10 MHz

30 (0x1E) Custom Custom Custom Custom

Notes:

• Type 07 (0x07) can be used for Side B only.

• PL-20C channels use the CENELEC protocol; PL-20N channels do not use the

CENELEC protocol.

• Type 30 (0x1E) can be used for any transceiver type; the communications port is

initially defined as all inputs to prevent circuit conflicts. The side using type 30

(0x1E) must be reprogrammed through the other router side.

ONWORKS Router User’s Guide 25

L

Page 36

See Appendix A, Communications Parameters for LONWORKS Routers, for a

RTR-

10

A Side

RESET

~

5 V

5 V

68

pF

68

pF

5 V

To other

devices

RTR-10

B Side

RESET~

Reset

Note: RTR-10 Modules

are limited to 2 x 68 pF

external on the RESET~

line

listing of the communications parameters for each transceiver type.

PKT

The PKT output can be used as a network activity indicator. When packets are

passed between the router sides, PKT is active. This signal uses the unbuffered

IO0 signal from the Neuron Chips. You can add a pulse stretcher circuit driven

by PKT to make an activity LED flash, as in the example circuit shown in

Figure 27 in chapter 4.

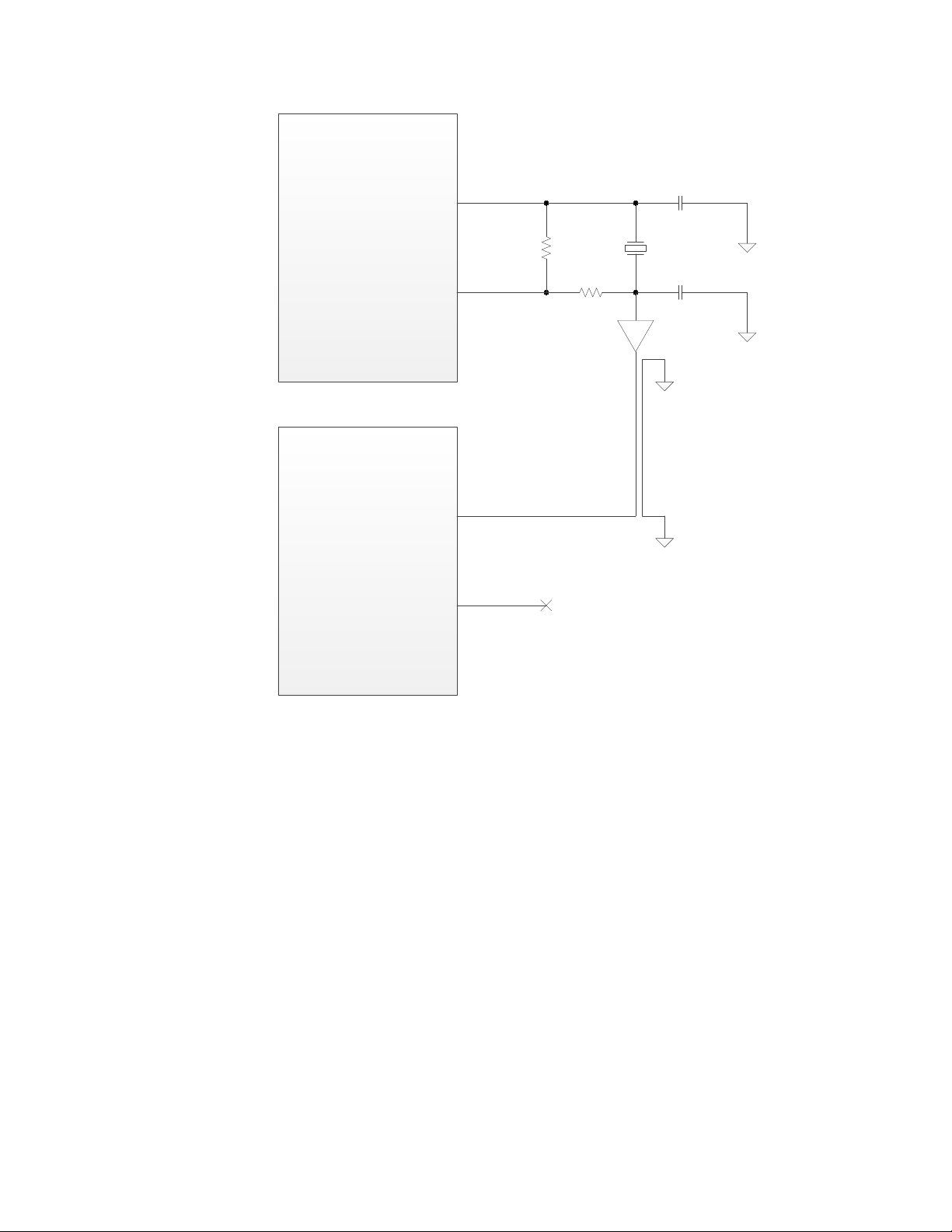

RESET~

The Neuron Chip reset pins are tied together and brought out on one pin.

Figure 10 shows the reset circuitry on the RTR-10 router.

Typical applications do not require debounce conditioning of a momentary

Figure 10. RTR-10 Reset Circuit

pushbutton attached to the RESET~ pin. The software response time associated

with this input is long enough to effectively provide a software debounce for

switches with a contact bounce settling time as long as 20 milliseconds. The

RESET~ signal must be driven low by a low voltage protection circuit on the

router motherboard as described in Low Voltage Protection.

26 LONWORKS Router Electrical Interfaces

Page 37

SERVICE~

SVC~

IO0

IO1

IO2

IO3

VDD1V8

IO4

VDD3V3

IO5

IO6

IO7

IO8 VDDPLL

GNDPLL

VOUT1V8

RST~

VIN3V3

VDD3V3

AVDD3V3

CP0

AGND

CP1

NC

GND

IO9

IO10

IO11

VDD1V8

TRST~

VDD3V3

TCK

TMS

TDI

TDO

XIN

XOUT

CP2

CP3

CP4

CS0~

VDD3V3

VDD3V3

SDA_CS1~

VDD1V8

SCL

MISO

SCK

MOSI

37

38

39

40

41

42

43

44

45

46

47

48

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

GND PAD

Router 5000

®

The SERVICE~ input drives both sides of the RTR-10 router from a single input.

You can connect a pushbutton to this pin broadcast each side’s 48-bit Neuron ID

on its channel (for example, during installation).

Typical applications do not require debounce conditioning of a momentary

pushbutton attached to the SERVICE~ pin. The software response time

associated with this input is long enough to effectively provide a software

debounce for switches with a contact bounce settling time as long as 20

milliseconds.

Series 5000 Router Electrical Interf ac e

The electrical interfaces for the Router 5000 chip and FT Router 5000 chip are

similar to the electrical interfaces of the Neuron 5000 Processor and the FT 5000

Smart Transceiver, as described in the Series 5000 Chip Data Book.

Router 5000 Pinout

Figure 11 shows the pinout for the Router 5000 chip. The central rectangle in

the figure represents the bottom pad (pin 49), which must be connected to

ground.

L

ONWORKS Router User’s Guide 27

Figure 11. Router 5000 Chip Pinout

Page 38

Table 8 lists the pin assignments for the Router 5000 chip. All digital inputs are low-voltage

SVC~

1

Digital I/O

Service (active low)

VDD3V3

18

Power

3.3 V Power

TMS

20

Digital Input

JTAG Test Mode Select

TDO

22

Digital Output

JTAG Test Data Out

transistor-transistor logic (LVTTL) compatible, 5 V tolerant, with low leakage. All digital

outputs are slew-rate limited to reduce Electromagnetic Interference (EMI) concerns.

Table 8. Router 5000 Chip Pin Assignments

Pin

Name

IO0 2 Digital I/O IO0 (side A to side B)

IO1 3 Digital I/O IO1 (side A to side B)

IO2 4 Digital I/O IO2 (side A to side B)

IO3 5 Digital I/O IO3 (side A to side B)

VDD1V8 6 Power 1.8 V Power Input

IO4 7 Digital I/O IO4 (side A to side B)

VDD3V3 8 Power 3.3 V Power

IO5 9 Digital I/O IO5 (side A to side B)

IO6 10 Digital I/O IO6 (side A to side B)

Number Type Description

(from internal voltage regulator)

IO7 11 Digital I/O IO7 (side A to side B)

IO8 12 Digital I/O IO8 (side A to side B)

IO9 13 Digital I/O IO9 (side A to side B)

IO10 14 Digital I/O IO10 (side A to side B)

IO11 15 Digital I/O IO11 (not used for routers)

VDD1V8 16 Power 1.8 V Power Input

(from internal voltage regulator)

TRST~ 17 Digital Input JTAG Test Reset (active low)