Diodes DMN4800LSS User Manual

DMN4800LSS

N-CHANNEL ENHANCEMENT MODE MOSFET

Product Summary

V

R

(BR)DSS

30V

max

DS(ON)

14mΩ @ V

20mΩ @ VGS = 4.5V

= 10V

GS

I

TA = +25°C

Description

This MOSFET has been designed to minimize the on-state resistance

) and yet maintain superior switching performance, making it

(R

DS(ON)

ideal for high efficiency power management applications.

Applications

NEW PRODUCT

Backlighting

Power Management Functions

DC-DC Converters

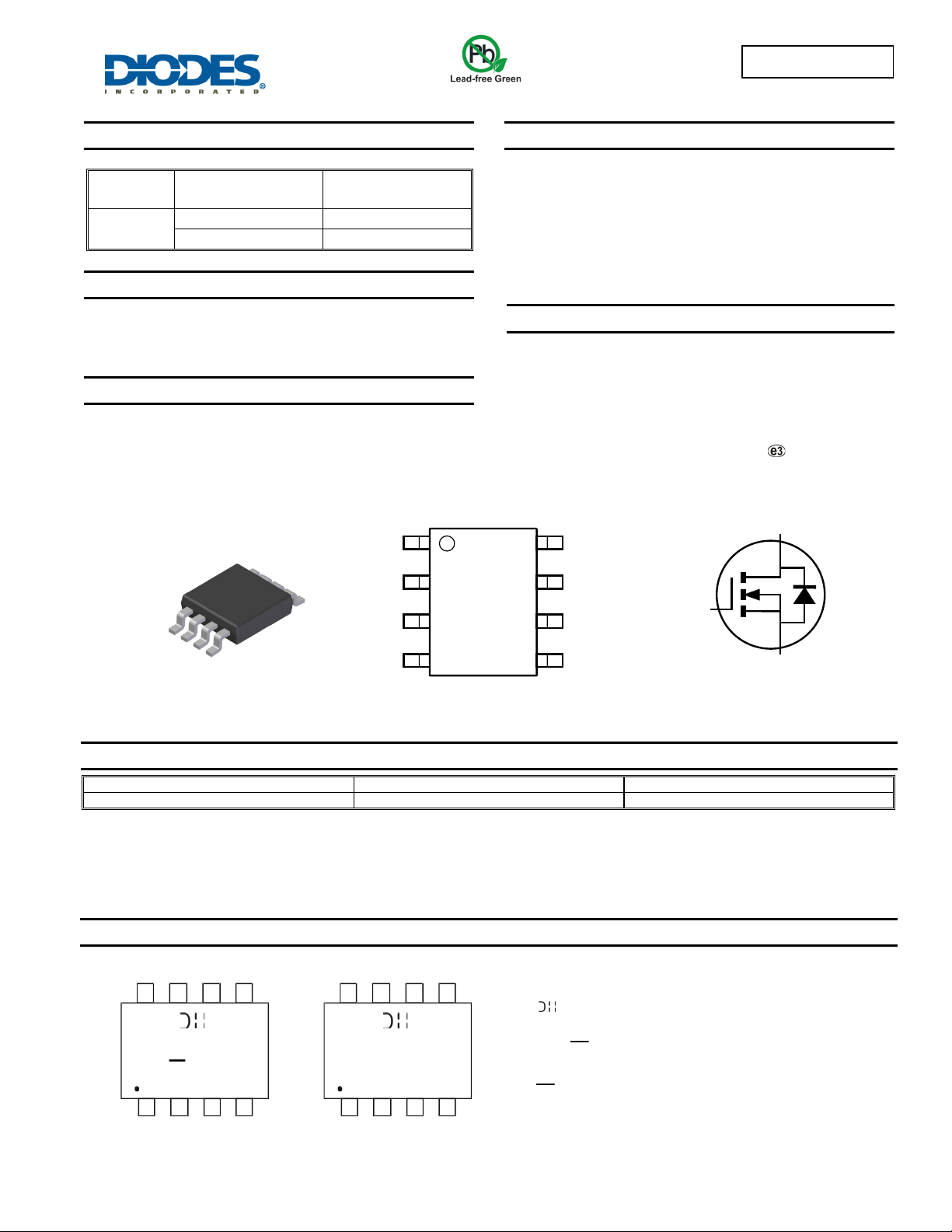

SO-8

Top View

max

D

8.6A

7.1A

S

S

G

Features

Low On-Resistance

Low Input Capacitance

Fast Switching Speed

Low Input/Output Leakage

Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

Halogen and Antimony Free. “Green” Device (Note 3)

Qualified to AEC-Q101 Standards for High Reliability

Mechanical Data

Case: SO-8

Case Material: Molded Plastic, “Green” Molding Compound.

Moisture Sensitivity: Level 1 per J-STD-020

Terminals Connections: See Diagram

Terminals: Finish - Matte Tin annealed over Copper lead frame.

Weight: 0.072g (approximate)

Top View

Internal Schematic

UL Flammability Classification Rating 94V-0

Solderable per MIL-STD-202, Method 208

DS

D

D

G

D

Equivalent circuit

D

S

Ordering Information (Note 4)

Part Number Case Packaging

DMN4800LSS-13 SO-8 2500/Tape & Reel

Notes: 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.

2. See http://www.diodes.com/quality/lead_free.html for more information about Diodes Incorporated’s definitions of Halogen- and Antimony-free, "Green"

and Lead-free.

3. Halogen- and Antimony-free "Green” products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and

<1000ppm antimony compounds.

4. For packaging details, go to our website at http://www.diodes.com/products/packages.html.

Marking Information

DMN4800LSS

Document number: DS31736 Rev. 7 - 2

8 5

N4800LS

WW

YY

1 4

Chengdu A/T Site Shanghai A/T Site

8 5

N4800LS

YY

WW

1 4

= Manufacturer’s Marking

N4800LS = Product Type Marking Code

YYWW = Date Code Marking

YY or YY = Year (ex: 13 = 2013)

WW = Week (01 - 53)

YY = Date Code Marking for SAT (Shanghai Assembly/ Test site)

YY = Date Code Marking for CAT (Chengdu Assembly/ Test site)

1 of 6

www.diodes.com

October 2013

© Diodes Incorporated

)

g

g

g

)

r

)

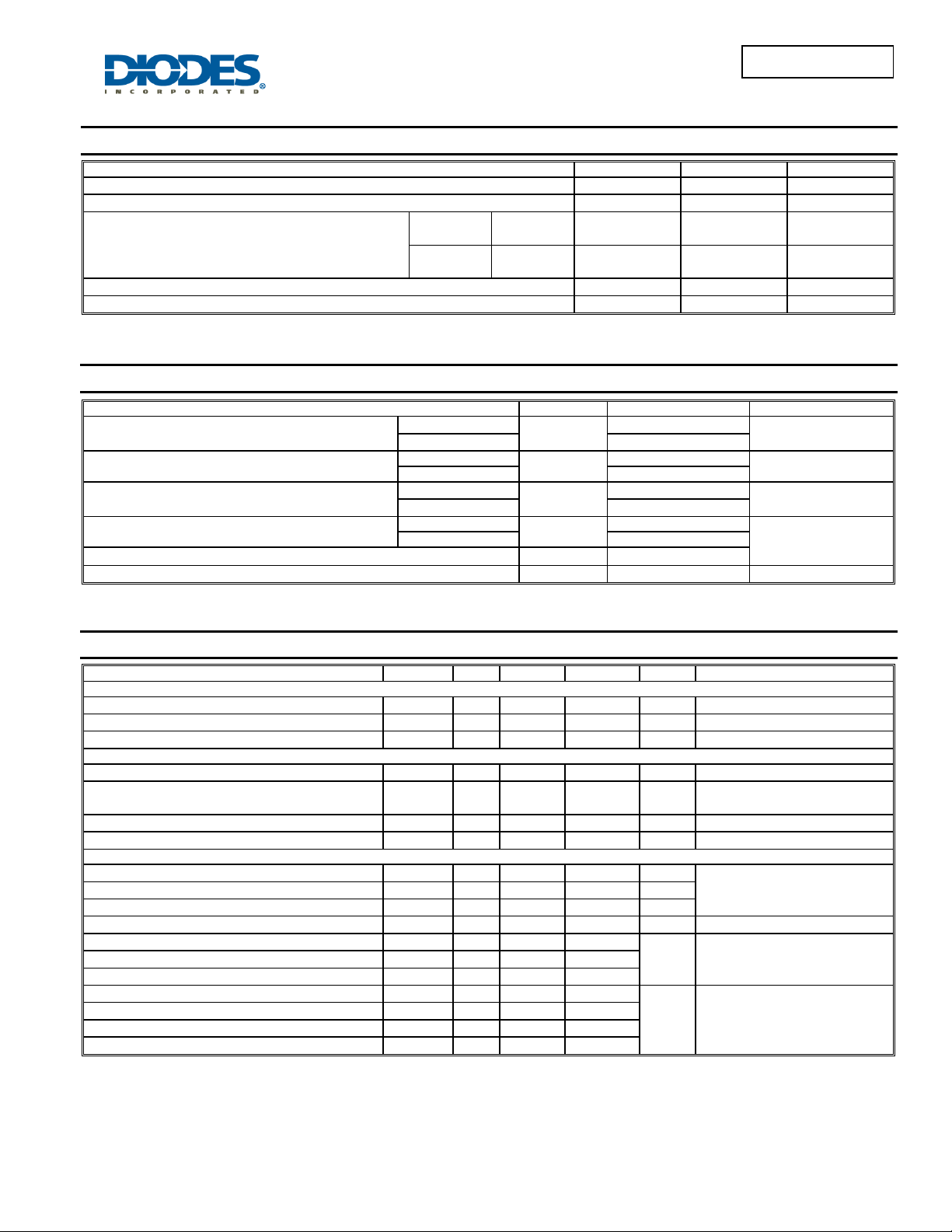

Maximum Ratings (@T

Drain-Source Voltage

Gate-Source Voltage

Continuous Drain Current (Note 6) VGS = 10V

Maximum Body Diode Forward Current (Note 6)

Pulsed Drain Current (Note 7)

Thermal Characteristics

NEW PRODUCT

Total Power Dissipation (Note 5)

Thermal Resistance, Junction to Ambient (Note 5)

Total Power Dissipation (Note 6)

Thermal Resistance, Junction to Ambient (Note 6)

Thermal Resistance, Junction to Case (Note 6)

Operating and Storage Temperature Range

Characteristic Symbol Value Units

DMN4800LSS

= +25°C, unless otherwise specified.)

A

Characteristic Symbol Value Units

V

DSS

V

GSS

= +25°C

Steady

State

t<10s

= +25°C

T

A

TA = +70°C

Steady state

t<10s 46

= +25°C

T

A

TA = +70°C

Steady state

t<10s 40

T

A

T

= +70°C

A

= +25°C

T

A

= +70°C

T

A

P

R

P

R

R

T

J, TSTG

I

D

I

D

I

S

I

DM

D

JA

D

JA

JC

1.46

0.9

86

1.7

1.0

75

15

-55 to +150 °C

30 V

25

8.6

6.3

11.8

9.0

V

A

A

2.4 A

50 A

W

°C/W

W

°C/W

Electrical Characteristics (@T

= +25°C, unless otherwise specified.)

A

Characteristic Symbol Min Typ Max Unit Test Condition

OFF CHARACTERISTICS (Note 8)

Drain-Source Breakdown Voltage

Zero Gate Voltage Drain Current

Gate-Source Leakage

BV

I

DSS

I

GSS

DSS

30

1 μA

100

ON CHARACTERISTICS (Note 8)

Gate Threshold Voltage

Static Drain-Source On-Resistance

Forward Transconductance

Diode Forward Voltage (Note 8)

V

GS(th

R

DS (ON)

V

g

fs

SD

0.8 1.2 1.6 V

11

14

8

0.72 0.94 V

14

20

DYNAMIC CHARACTERISTICS (Note 9)

Input Capacitance

Output Capacitance

Reverse Transfer Capacitance

Gate Resistance

Total Gate Charge

Gate-Source Charge

Gate-Drain Charge

Turn-On Delay Time

Rise Time

Turn-Off Delay Time

Fall Time

Notes: 5. Device mounted on FR-4 substrate PC board, 2oz copper, with minimum recommended pad layout.

6. Device mounted on FR-4 substrate PC board, 2oz copper, with 1inch square copper pad layout

7. Repetitive rating, pulse width limited by junction temperature.

8. Short duration pulse test used to minimize self-heating effect.

9. Guaranteed by design. Not subject to product testing.

t

t

C

C

C

R

Q

Q

Q

d(on

d(off

iss

oss

rss

t

t

G

f

s

d

798

128

122

1.37

8.7

1.7

2.4

5.03

4.50

26.33

8.55

V

V

= 0V, ID = 250μA

GS

V

= 30V, VGS = 0V

nA

mΩ

DS

VGS = 20V, VDS = 0V

V

= VGS, ID = 250μA

DS

= 10V, ID = 9A

V

GS

V

= 4.5V, ID = 7A

GS

S

V

= 10V, ID = 9A

DS

VGS = 0V, IS = 1A

pF

pF

pF

Ω

nC

ns

= 10V, VGS = 0V

V

DS

f = 1.0MHz

VDS = 0V, VGS = 0V, f = 1.0MHz

= 5V, VDS = 15V, ID = 9A

V

GS

= 15V, V

V

DD

R

= 15ΩRG = 6.0ΩID = 1A

L

GEN

= 10V,

DMN4800LSS

Document number: DS31736 Rev. 7 - 2

2 of 6

www.diodes.com

October 2013

© Diodes Incorporated

Loading...

Loading...