132 X 64 Dot Matrix OLED/PLED

SH1101A

Preliminary Segment/Common Driver with Controller

Features

Support maximum 132 X 64 dot matrix panel

Embedded 132 X 64 bits SRAM

Operating voltage:

- Logic voltage supply: V

- DC-DC voltage supply: V

- OLED Operating voltage supply: V

Maximum segment output current: 320µA

Maximum common sink current: 45mA

8-bit 6800-series parallel interface, 8-bit 8080-series

parallel interface, serial peripheral interface

Programmable frame frequency and multiplexing ratio

Row re-mapping and column re-mapping (ADC)

DD1 = 2.4V - 3.5V

= 2.4V - 3.5V

DD2

PP = 7.0V - 16.0V

Vertical scrolling

On-chip oscillator

Available internal DC-DC converter

256-step contrast control on monochrome passive OLED panel

Low power consumption

- Sleep mode: <5µA

Wide range of operating temperatures: -40 to +85°C

Available in COG and TCP form

General Description

SH1101A is a single-chip CMOS OLED/PLED driver with controller for organic/polymer light emitting diode dot-matrix graphic

display system. SH1101A consists of 132 segments, 64 commons that can support a maximum display resolution of 132 X 64.

It is designed for Common Cathode type OLED panel.

SH1101A embeds with contrast control, display RAM oscillator and efficient DC-DC converter, which reduces the number of

external components and power consumption. SH1101A is suitable for a wide range of compact portable applications, such as

sub-display of mobile phone, calculator and MP3 player, etc.

1 V0.13

SH1101A

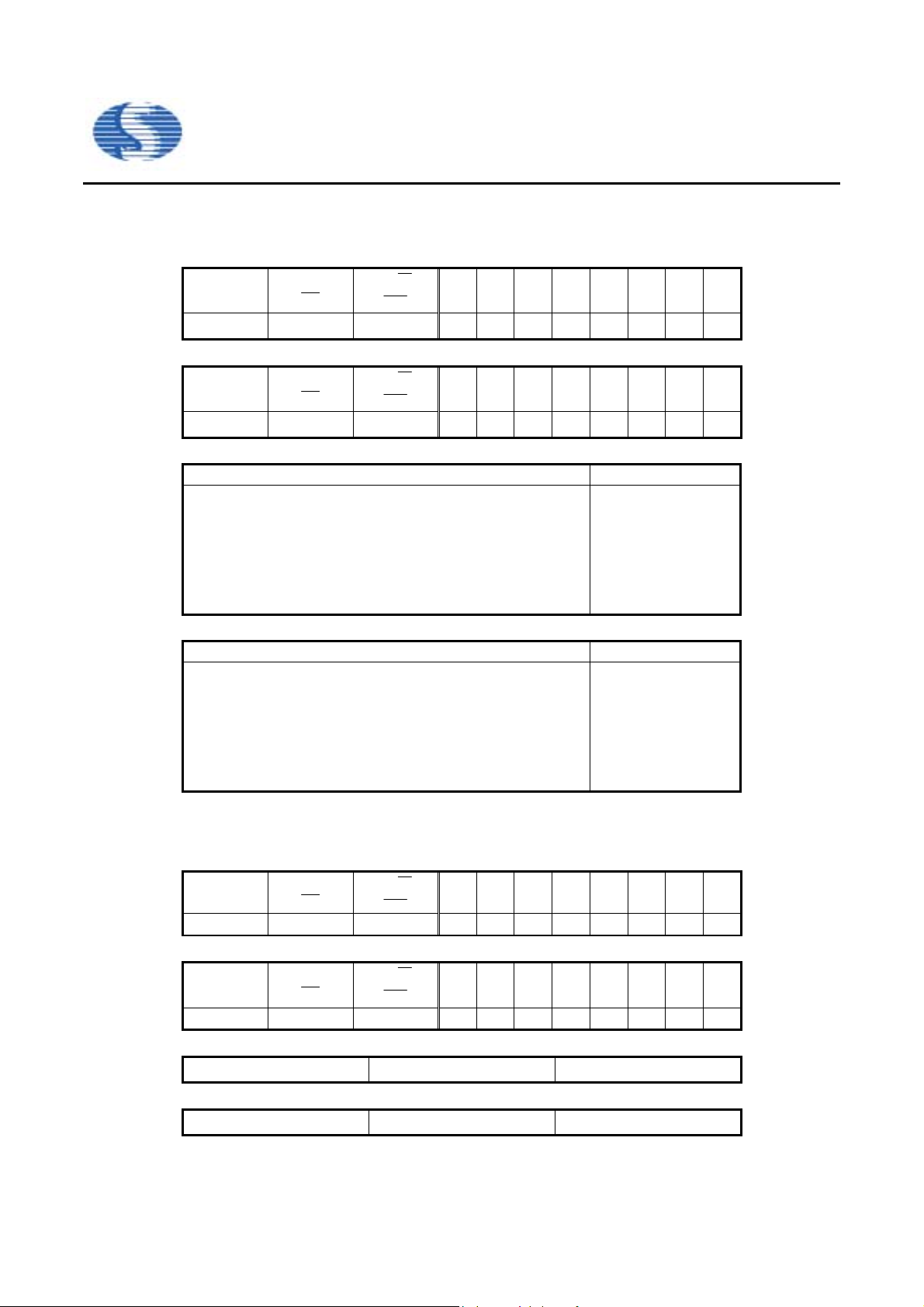

Pin Configuration

NC

COM61NCCOM63

208

209

210

211

1

2

3

NC

35

COM62NCCOM60

34

33

COM3

179

COM1

178

NC

177

NC

170

SEG95

169

SEG94

168

SEG1

75

SEG0

74

NC

73

66

65

COM2NCCOM0

64

SH1101A-TCP03

(Copper Side View)

4

5

6

7

8

9

101112131415161718192021222324252627282930

31NC 32

SS

NC

SW

V

Pad Configuration

269

SH1101A

X

1

DD2

V

FB

SENSE

NCNCNC

BREF

V

DD1

V

C86

P/S

RES

A0

CS

NC

D0D1D2D3D4D5D6

RD

WR

D7

REF

I

VPP

VCOMH

74

xxx x

X

73

( 0 , 0 )

105106237238

Y

Dummy Pad

X

x

2 V0.13

SH1101A

Block Diagram

V

DD1

V

DD2

V

SS

V

COMH

V

CL

V

SL

I

REF

V

REF

V

PP

SW

SENSE DC-DC

FB

BREF

V

Power supply

Page Address

Register

circuit

Output status

selector circuit

SEG0 SEG131 COM0 COM63

Segment driver Common driver

Shift register

Display data latch

132 X 64-dots

Display Data RAM

I/O buffer circuit

line address decoder

Line counter

Column address decoder

Initial display line register

8-bit column address counter

Display Timing

Generator Circuit

CL

8-bit column address counter

Bus Holder Command Decoder Bus Holder Oscillator

Microprocessor Interface

P/SWRRDA0CS

(R/W)

(E)

RESC86

D7 D6 D5 D4 D3 D2 D1 D0

I/O Buffer

(SI) (SCL)

CLS

3 V0.13

SH1101A

Pad Description

Power Supply

Pad No. Symbol I/O Description

28 - 31 VDD1 Supply 2.4 - 3.5V power supply input.

34,44,62 VDD1 Supply 2.4 - 3.5V power supply output for pad option.

17 - 20 VDD2 Supply 2.4 - 3.5V power supply pad for the internal buffer of the DC-DC voltage converter.

7 - 13 VSS Supply Ground.

21, 32, 36, 42, 64 VSS Supply Ground output for pad option.

49 - 53, 71 - 73 VPP Supply

66 VPP Supply

4 - 6 VSL Supply

1 - 3 VCL Supply

This is the most positive voltage supply pad of the chip.

It should be supplied externally.

This is the most positive voltage output for pad option,

which cannot be used as the most positive voltage input.

This is a segment voltage reference pad.

This pad should be connected to V

SS externally.

This is a common voltage reference pad.

This pad should be connected to V

SS externally.

OLED Driver Supplies

Pad No. Symbol I/O Description

This is a voltage reference pad for pre-charge voltage in driving OLED device.

70 VREF I

65 IREF O

45 - 48, 67 - 69 VCOMH O

14 - 16 SW O This is an output pad driving the gate of the external NMOS of the booster circuit.

22 FB I

23 SENSE I This is a source current pad of the external NMOS of the booster circuit.

24 V

O

BREF

Voltage should be set to match with the OLED driving voltage in current drive

phase. It can either be supplied externally or by connecting to V

This is a segment current reference pad. A resistor should be connected

between this pad and V

. Set the current at 10µA.

SS

This is a pad for the voltage output high level for common signals.

A capacitor should be connected between this pad and V

SS.

This is a feedback resistor input pad for the booster circuit. It is used to

adjust the booster output voltage level, V

PP.

This is an internal voltage reference pad for booster circuit. A stabilization

capacitor, typical 1µF, should be connected to V

SS.

PP.

4 V0.13

SH1101A

System Bus Connection Pads

Pad No. Symbol I/O Description

This pad is the system clock input. When internal clock is enabled, this pad should be

37 CL I/O

63 CLS I

33 C86 I

35 P/S I

Left open. The internal clock is output from this pad. When internal oscillator is disabled,

this pad receives display clock signal from external clock source.

This is the internal clock enable pad.

CLS = “H”: Internal oscillator circuit is enabled.

CLS = “L”: Internal oscillator circuit is disabled (requires external input).

When CLS = “L”, an external clock source must be connected to the CL pad for

normal operation.

This is the MPU interface switch pad.

C86 = “H”: 8080 series MPU interface.

C86 = “L”: 6800 series MPU interface.

This is the parallel data input/serial data input switch pad.

P/S = “H”: Parallel data input.

P/S = “L”: Serial data input.

When P/S = “L”, D2 to D7 are HZ. D2 to D7 may be “H”, “L” or Open.

WR ( W/R ) are fixed to either “H” or “L”. With serial data input, RAM display

data reading is not supported. These are MPU interface input selection pads.

See the following table for selecting different interfaces:

C86

P/S

6800-Parallel

Interface

0

11

8080-Parallel

Interface

10

Serial Interface

RD (E) and

0

38

39

40 A0 I

41

43

CS

RES

WR

(

RD

(E)

WR / )

I

I

I

I

This pad is the chip select input. When

and data/command I/O is enabled.

This is a reset signal input pad. When

reset operation is performed by the

This is the Data/Command control pad which determines whether the data bits are

data or a command.

A0 = “H”: the inputs at D0 to D7 are treated as display data.

A0 = “L”: the inputs at D0 to D7 are transferred to the command registers.

This is a MPU interface input pad.

When connected to an 8080 MPU, this is active LOW. This pad connects to the 8080

MPU

When connected to a 6800 Series MPU: This is the read/write control signal input terminal.

When

When

This is a MPU interface input pad.

When connected to an 8080 series MPU, it is active LOW. This pad is connected to the

RD signal of the 8080 series MPU, and the SH1101A data bus is in an output status

when this signal is “L”.

When connected to a 6800 series MPU , this is active HIGH. This is used as an enable

clock input of the 6800 series MPU.

signal. The signals on the data bus are latched at the rising edge of the WR signal.

WR

WR / = “H”: Read.

WR / = “L”: Write.

CS = “L”, then the chip select becomes active,

RES is set to “L”, the settings are initialized. The

RES signal level.

5 V0.13

SH1101A

System Bus Connection Pads (continued)

Pad No. Symbol I/O Description

This is an 8-bit bi-directional data bus that connects to an 8-bit or 16-bit standard

54 – 61

54

55

D0 - D7

(SCL)

(SI)

MPU data bus.

I/O

When the serial interface is selected, then D0 serves as the serial clock input pad

I

(SCL) and D1 serves as the serial data input pad (SI). At this time, D2 to D7 are

I

set to high impedance.

When the chip select is inactive, D0 to D7 are set to high impedance.

OLED Drive Pads

Pad No. Symbol I/O Description

105 - 74,

238 - 269

106 - 237 SEG0 - 131 O These pads are Segment signal output for OLED display.

COM0 - 63 O These pads are Common signal output for OLED display.

Test Pads

Pad No. Symbol I/O Description

25 TEST1 I Test pads, internal pull low, no connection for user.

27 TEST2 O Test pads, no connection for user.

26 TEST3 I Test pads, no connection for user.

- NC - NC pads, no connection for user.

6 V0.13

SH1101A

Functional Description

Microprocessor Interface Selection

The 8080-Parallel Interface, 6800-Parallel Interface or Serial Interface (SPI) can be selected by different selections of C86, P/S

as shown in Table 1.

Table. 1

6800-Parallel Interface 8080-Parallel Interface Serial Interface

C86

P/S

0 1 0

1 1 0

6800-series Parallel Interface

The parallel interface consists of 8 bi-directional data pads (D7-D0),

“H”, read operation from the display RAM or the status register occurs. When

WR

(

WR / ),

WR

RAM or internal command registers occurs, depending on the status of A0 input. The

(clock) when it is “H”, provided that

CS = “L” as shown in Table. 2.

(E), A0 and

RD

(

WR / ) = “L”, Write operation to display data

(E) input serves as data latch signal

RD

CS . When

WR

(

WR / ) =

Table. 2

P/S C86 Type

1 0 6800 microprocessor bus

CS

CS

A0

A0 E

RD WR

WR /

D0 to D7

D0 to D7

In order to match the operating frequency of display RAM with that of the microprocessor, some pipeline processings are

internally performed, which require the insertion of a dummy read before the first actual display data read. This is shown in

Figure. 1 below.

A0

MPU

E

R/W

DATA

Address preset

n+1N N n

Internal

timing

Read signal

Column address

BUS holder

Set address n

IncrementedPreset

N N+1 N+2

N n n+1 n+2

Dummy read

Data Read

address n

Data Read

address n+1

Figure. 1

7 V0.13

SH1101A

8080-series Parallel Interface

The parallel interface consists of 8 bi-directional data pads (D7-D0),

serves as data read latch signal (clock) when it is “L” provided that

by A0 signal. The

data or command register write is controlled by A0 as shown in Table. 3.

P/S C86 Type

1 1 8080 microprocessor bus

Similar to 6800-series interface, a dummy read is also required before the first actual display data read.

WR

(

WR / ) input serves as data write latch signal (clock) when it is “L” and provided that CS = “L”. Display

Table. 3

CS

CS

CS = “L”. Display data or status register read is controlled

A0

A0

WR

(

WR / ),

RD WR

RD WR

(E), A0 and

RD

Data Bus Signals

The SH1101A identifies the data bus signal according to A0,

Common 6800 processor 8080 processor

A0

1 1 0 1 Reads display data.

1 0 1 0 Writes display data.

0 1 0 1 Reads status.

0 0 1 0 Writes control data in internal register. (Command)

(

W/R)

RD WR

(E) and WR(

RD

Table. 4

WR / ) signals.

Function

CS . The

D0 to D7

D0 to D7

(E) input

RD

8 V0.13

SH1101A

Serial Interface (SPI)

The serial interface consists of serial clock SCL, serial data SI, A0 and CS . SI is shifted into an 8-bit shift register on every

rising edge of SCL in the order of D7, D6, … and D0. A0 is sampled on every eighth clock and the data byte in the shift register

is written to the display data RAM or command register in the same clock. See Figure. 2.

Table. 5

P/S C86 Type

0 0 Serial Interface (SPI)

Note: “-” Must always be HIGH or LOW.

CS

SI (D1)

SCL(D0)

A0

When the chip is not active, the shift registers and the counter are reset to their initial statuses.

Read is not possible while in serial interface mode.

Caution is required on the SCL signal when it comes to line-end reflections and external noise. We recommend the operation

be rechecked on the actual equipment.

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5

1234567891011

CS

CS

A0

A0 - - SCL SI

Figure. 2

RD WR

D0 D1 D2 to D7

(HZ)

Access to Display Data RAM and Internal Registers

This module determines whether the input data is interpreted as data or command. When A0 = “H”, the inputs at D7 - D0 are

interpreted as data and be written to display RAM. When A0 = “L”, the inputs at D7 - D0 are interpreted as command, they will

be decoded and be written to the corresponding command registers.

Display Data RAM

The Display Data RAM is a bit mapped static RAM holding the bit pattern to be displayed. The size of the RAM is 132 X 64 bits.

For mechanical flexibility, re-mapping on both segment and common outputs can be selected by software.

For vertical scrolling of the display, an internal register storing display start line can be set to control the portion of the RAM data

to be mapped to the display.

9 V0.13

SH1101A

The Page Address Circuit

As shown in Figure. 3, page address of the display data RAM is specified through the Page Address Set Command. The page

address must be specified again when changing pages to perform access.

The Column Address

As shown in Figure. 3, the display data RAM column address is specified by the Column Address Set command. The specified

column address is incremented (+1) with each display data read/ write command. This allows the MPU display data to be

accessed continuously. Because the column address is independent of the page address, when moving, for example, from

page0 column 83H to page 1 column 00H, it is necessary to re-specify both the page address and the column address.

Furthermore, as shown in Table. 6, the Column re-mapping (ADC) command (segment driver direction select command) can

be used to reverse the relationship between the display data RAM column address and the segment output. Because of this,

the constraints on the IC layout when the OLED module is assembled can be minimized.

Table. 6

Segment Output SEG0 SEG131

ADC “0” 0 (H) Column Address 83 (H)

ADC “1” 83 (H) Column Address 0 (H)

The Line Address Circuit

The line address circuit, as shown in Figure. 3, specifies the line address relating to the common output when the contents of

the display data RAM are displayed. Using the display start line address set command, what is normally the top line of the

display can be specified (this is the COM0 output when the common output mode is normal, and the COM63 output for

SH1101A, when the common output mode is reversed. The display area is a 64-line area for the SH1101A from the display start

line address.

If the line addresses are changed dynamically using the display start line address set command, screen scrolling, page

swapping, etc. that can be performed relationship between display data RAM and address (if initial display line is 1DH).

10 V0.13

SH1101A

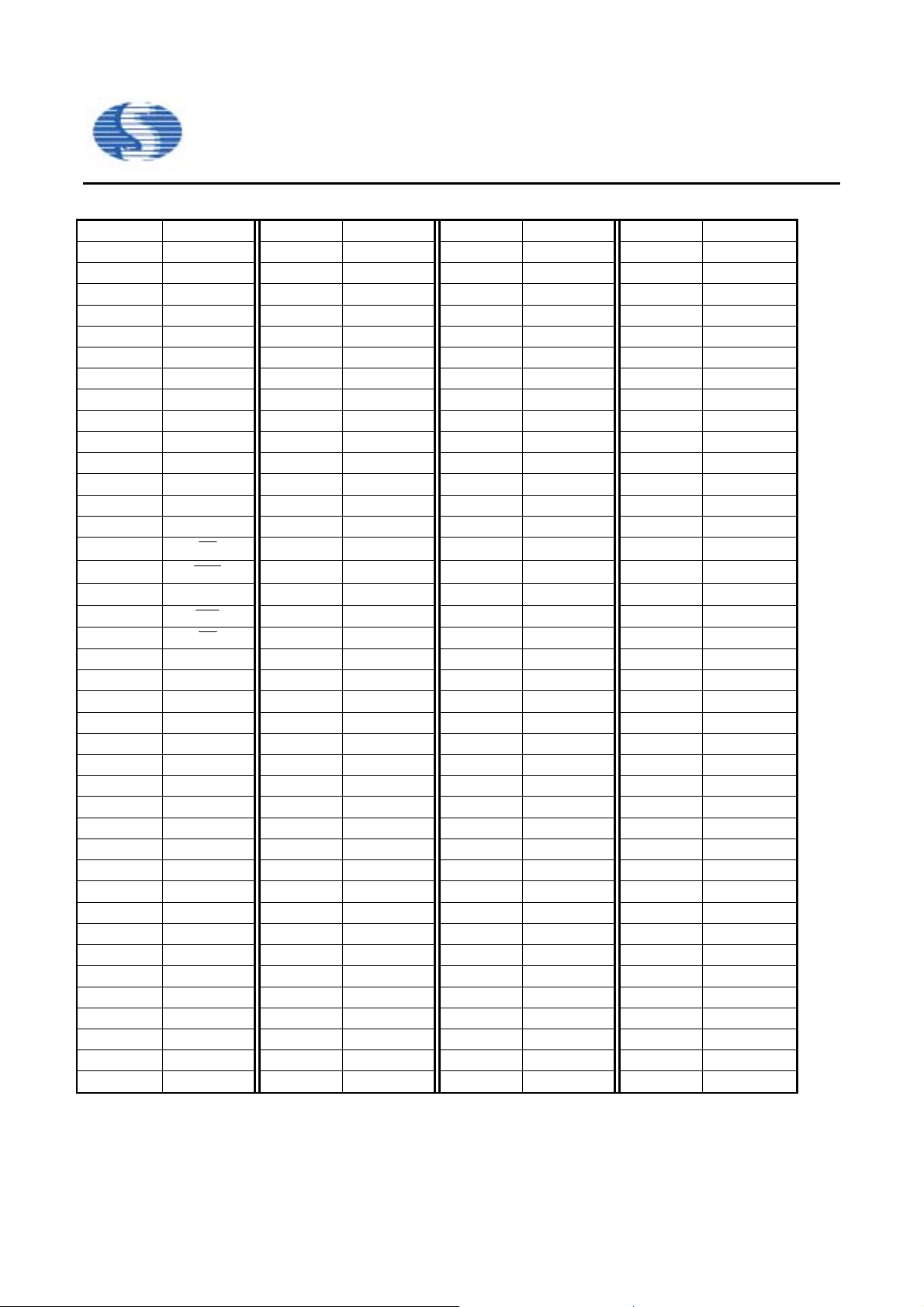

Page Address

D3 D2 D1 D0 01H

0000 03H

D3 D2 D1 D0 09H

0001 0BH

D3 D2 D1 D0 11H

0010 13H

D3 D2 D1 D0 19H

0011 1BH

D3 D2 D1 D0 21H

0100 23H

D3 D2 D1 D0 29H

0101 2BH

D3 D2 D1 D0 31H

0110 33H

D3 D2 D1 D0 39H

0111 3BH

Data

D0

D1

D2

D3

D4

D5

D6

D7

D0

D1

D2

D3

D4

D5

D6

D7

D0

D1

D2

D3

D4

D5

D6

D7

D0

D1

D2

D3

D4

D5

D6

D7

D0

D1

D2

D3

D4

D5

D6

D7

D0

D1

D2

D3

D4

D5

D6

D7

D0

D1

D2

D3

D4

D5

D6

D7

D0

D1

D2

D3

D4

D5

D6

D7

PAGE 0

PAGE1

PAGE2

PAGE3

PAGE4

PAGE5

PAGE6

PAGE7

Line Address

00H

02H

04H

05H

06H

07H

08H

0AH

0CH

0DH

0EH

0FH

10H

12H

14H

15H

16H

17H

18H

1AH

1CH

1DH

1EH

1FH

20H

22H

24H

25H

26H

27H

28H

2AH

2CH

2DH

2EH

2FH

30H

32H

34H

35H

36H

37H

38H

3AH

3CH

3DH

3EH

3FH

OUTPUT

COM0

COM1

COM2

COM3

COM4

COM5

COM6

COM7

COM8

COM9

COM10

COM11

COM12

COM13

COM14

COM15

COM16

COM17

COM18

COM19

COM20

COM21

COM22

COM23

COM24

COM25

COM26

COM27

COM28

COM29

COM30

COM31

COM32

COM33

COM34

COM35

COM36

COM37

COM38

COM39

COM40

COM41

COM42

COM43

COM44

COM45

COM46

COM47

COM48

COM49

COM50

COM51

COM52

COM53

COM54

COM55

COM56

COM57

COM58

COM59

COM60

COM61

COM62

COM63

Column

Address

ADC

LCD

D0=”0”

D0=”1”

OUT

00H

83H

SEG0

01H

82H

SEG1

02H

81H

SEG2

81H

82H

83H

02H

01H

00H

SEG129

SEG130

SEG131

Figure. 3

11 V0.13

SH1101A

The Oscillator Circuit

This is a RC type oscillator (Figure. 4) that produces the display clock. The oscillator circuit is only enabled when CLS = “H”.

When CLS = “L”, the oscillation stops and the display clock is inputted through the CL terminal.

CL

CLS

Internal OSC

MUX

Figure. 4

CLK

DIVIDER

DCLK

Internal Display

Clock

12 V0.13

SH1101A

DC-DC Voltage Converter

It is a switching voltage generator circuit, designed for hand held applications. In SH1101A, built-in DC-DC voltage converter

accompanied with an external application circuit (shown in Figure. 5) can generate a high voltage supply V

supply input V

. VPP is the voltage supply to the OLED driver block.

DD2

LD

V

DD2

+

C

2

+

C

3

V

C

V

DD2

BREF

+

1

V

SS

DC-DC

SW

SENSE

QR

1

C

4

+

R

3

PP from a low voltage

V

PP

V

SS

V

SS

FB

R

2

+

C

5

V

SS

Figure. 5

1R

VPP=(1+

) X V

BREF, (R2: 80 - 120kΩ )

2R

Current Control and Voltage Control

This block is used to derive the incoming power sources into different levels of internal use voltage and current. VPP and VDD2

are external power supplies. V

REF is a reference current source for segment current drivers.

I

REF, a reference voltage, which is used to derive the driving voltage for segments and commons.

Common Drivers/Segment Drivers

Segment drivers deliver 132 current sources to drive OLED panel. The driving current can be adjusted up to 320µA with 256

steps. Common drivers generate voltage scanning pulses.

13 V0.13

SH1101A

Reset Circuit

When the RES input falls to “L”, these reenter their default state. The default settings are shown below:

1. Display is OFF. Common and segment are in high impedance state.

2. 132 X 64 Display mode

3. Normal segment and display data column address and row address mapping (SEG0 is mapped to column address 00H and

COM0 mapped to row address 00H).

4. Shift register data clear in serial interface.

5. Display start line is set at display RAM line address 00H.

6. Column address counter is set at 0.

7. Normal scanning direction of the common outputs.

8. Contrast control register is set at 80H.

9. Internal DC-DC is selected.

14 V0.13

Commands

SH1101A

The SH1101A uses a combination of A0,

executes each command using internal timing clock only regardless of external clock, its processing speed is very high and its

busy check is usually not required. The 8080 series microprocessor interface enters a read status when a low pulse is input to

the

RD pad and a write status when a low pulse is input to the WR pad. The 6800 series microprocessor interface enters a

read status when a high pulse is input to the

pulse is input to the E pad, the command is activated. (For timing, see AC Characteristics.). Accordingly, in the command

explanation and command table,

display data. This is an only different point from the 8080 series microprocessor interface.

Taking the 8080 series, microprocessor interface as an example command will explain below.

When the serial interface is selected, input data starting from D7 in sequence.

RD (E) becomes 1(HIGH) when the 6800 series microprocessor interface reads status of

(E) and

RD

WR / pad and a write status when a low pulse is input to this pad. When a high

WR

(

WR / ) signals to identify data bus signals. As the chip analyzes and

Command Set

1. Set Lower Column Address: (00H - 0FH)

2. Set Higher Column Address: (10H - 1FH)

Specifies column address of display RAM. Divide the column address into 4 higher bits and 4 lower bits. Set each of them

into successions. When the microprocessor repeats to access to the display RAM, the column address counter is

incremented during each access until address 132 is accessed. The page address is not changed during this time.

Higher bits 0 1 0 0 0 0 1 A7 A6 A5 A4

Lower bits 0 1 0 0 0 0 0 A3 A2 A1 A0

A7 A6 A5 A4 A3 A2 A1 A0 Line address

0 0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 1 1

1 0 0 0 0 0 1 1 131

A0

E

RD

WR /

WR

: :

D7 D6 D5 D4 D3 D2 D1 D0

Note: Don’t use any commands not mentioned above.

3~5. Reserved Command

These three commands are reserved for user.

15 V0.13

SH1101A

6. Set Display Start Line: (40H - 7FH)

Specifies line address (refer to Figure. 3) to determine the initial display line or COM0. The RAM display data becomes the

top line of OLED screen. It is followed by the higher number of lines in ascending order, corresponding to the duty cycle.

When this command changes the line address, the smooth scrolling or page change takes place.

A0

0 1 0 0 1 A5 A4 A3 A2 A1 A0

A5 A4 A3 A2 A1 A0 Line address

0 0 0 0 0 0 0

0 0 0 0 0 1 1

1 1 1 1 1 0 62

1 1 1 1 1 1 63

E

RD

WR /

WR

: :

D7 D6 D5 D4 D3 D2 D1 D0

16 V0.13

SH1101A

7. Set Contrast Control Register: (Double Bytes Command)

This command is to set contrast setting of the display. The chip has 256 contrast steps from 00 to FF. The segment output

current increases as the contrast step value increases.

Segment output current setting: ISEG = α/256 X IREF X scale factor

Where:

α is contrast step; IREF is reference current equals 10µA; Scale factor = 32.

The Contrast Control Mode Set: (81H)

When this command is input, the contrast data register set command becomes enabled. Once the contrast control mode

has been set, no other command except for the contrast data register command can be used. Once the contrast data set

command has been used to set data into the register, then the contrast control mode is released.

A0

0 1 0 1 0 0 0 0 0 0 1

E

RD

WR /

WR

D7 D6 D5 D4 D3 D2 D1 D0

Contrast Data Register Set: (00H - FFH)

By using this command to set eight bits of data to the contrast data register; the OLED segment output assumes one of the

256 current levels.

When this command is input, the contrast control mode is released after the contrast data register has been set.

A0

0 1 0 0 0000000 Small

0 1 0 0 0000010

0 1 0 0 0000011

0 1 0 : :

0 1 0 1 0000000 POR

0 1 0 : :

0 1 0 1 1111110

0 1 0 1 1 1 1 1 1 1 1 Large

When the contrast control function is not used, set the D7 - D0 to 1000,0000.

8. Set Segment Re-map: (A0H - A1H)

Change the relationship between RAM column address and segment driver. The order of segment driver output pads can be

reversed by software. This allows flexible IC layout during OLED module assembly. For details, refer to the column address

section of Figure. 3. When display data is written or read, the column address is incremented by 1 as shown in Figure. 1.

A0

E

RD

0 1 0 1 0 1 0 0 0 0 ADC

E

RD

WR /

WR

D7 D6 D5 D4 D3 D2 D1 D0 I

WR /

WR

D7 D6 D5 D4 D3 D2 D1 D0

SEG

When ADC = “L”, the right rotates (normal direction). (POR)

When ADC = “H”, the left rotates (reverse direction).

9. Set Entire Display OFF/ON: (A4H - A5H)

Forcibly turns the entire display on regardless of the contents of the display data RAM. At this time, the contents of the

display data RAM are held.

This command has priority over the normal/reverse display command.

A0

0 1 0 1 0 1 0 0 1 0 D

When D = “L”, the normal display status is provided. (POR)

When D = “H”, the entire display ON status is provided.

E

RD

WR /

WR

D7 D6 D5 D4 D3 D2 D1 D0

17 V0.13

SH1101A

play

10. Set Normal/Reverse Display: (A6H -A7H)

Reverses the display ON/OFF status without rewriting the contents of the display data RAM.

A0

0 1 0 1 0 1 0 0 1 1 D

When D = “L”, the RAM data is high, being OLED ON potential (normal display). (POR)

When D = “H”, the RAM data is low, being OLED ON potential (reverse display)

11. Set Multiplex Ration: (Double Bytes Command)

This command switches default 64 multiplex modes to any multiplex ratio from 1 to 64. The output pads COM0-COM63 will

be switched to corresponding common signal.

E

RD

Multiplex Ration Mode Set: (A8H)

A0

0 1 0 1 0 1 0 1 0 0 0

E

RD

Multiplex Ration Data Set: (00H - 3FH)

A0

0 1 0 * * 000000 1

0 1 0 * * 000010 2

0 1 0 * * 000011 3

0 1 0 : :

0 1 0 * * 1 1 1 1 1 0 63

0 1 0 * * 111111 64 (POR)

E

RD

WR

WR /

WR /

WR

WR /

WR

D7 D6 D5 D4 D3 D2 D1 D0 Multiplex Ratio

D7 D6 D5 D4 D3 D2 D1 D0

D7 D6 D5 D4 D3 D2 D1 D0

12. Set DC-DC OFF/ON: (Double Bytes Command)

This command is to control the DC-DC voltage converter. The converter will be turned on by issuing this command then

display ON command. The panel display must be off while issuing this command.

DC-DC Control Mode Set: (ADH)

A0

0 1 0 1 0 1 0 1 1 0 1

E

RD

WR /

WR

D7 D6 D5 D4 D3 D2 D1 D0

DC-DC ON/OFF Mode Set: (8AH - 8BH)

A0

0 1 0 1 0 0 0 1 0 1 D

When D = “L”, DC-DC is disable.

When D = “H”, DC-DC will be turned on when display on. (POR)

E

RD

WR /

WR

D7 D6 D5 D4 D3 D2 D1 D0

Table. 7

DC-DC STATUS DISPLAY ON/OFF STATUS Description

0 0 Sleep mode

0 1 External V

1 0 Sleep mode

1 1

Built-in DC-DC is used,

must be used.

PP

Normal Dis

18 V0.13

SH1101A

13. Display OFF/ON: (AEH - AFH)

Alternatively turns the display on and off.

A0

0 1 0 1 0 1 0 1 1 1 D

When D = “L”, Display OFF OLED. (POR)

When D = “H”, Display ON OLED.

When the display OFF command is executed, power saver mode will be entered.

Sleep mode:

This mode stops every operation of the OLED display system, and can reduce current consumption nearly to a static current

value if no access is made from the microprocessor. The internal status in the sleep mode is as follows:

(1) Stops the oscillator circuit and DC-DC circuit.

(2) Stops the OLED drive and outputs HZ as the segment/common driver output.

(3) Holds the display data and operation mode provided before the start of the sleep mode.

(4) The MPU can access to the built-in display RAM.

14. Set Page Address: (B0H - B7H)

Specifies page address to load display RAM data to page address register. Any RAM data bit can be accessed when its

page address and column address are specified. The display remains unchanged even when the page address is changed.

A0

0 1 0 1 0 1 1 A3 A2 A1 A0

A

3 A2 A1 A0 Page address

0 0 0 0 0

0 0 0 1 1

0 0 1 0 2

0 0 1 1 3

0 1 0 0 4

0 1 0 1 5

0 1 1 0 6

0 1 1 1 7

E

RD

E

RD

WR

WR

WR /

WR /

D7 D6 D5 D4 D3 D2 D1 D0

D7 D6 D5 D4 D3 D2 D1 D0

Note: Don’t use any commands not mentioned above for user.

19 V0.13

SH1101A

15. Set Common Output Scan Direction: (C0H - C8H)

This command sets the scan direction of the common output allowing layout flexibility in OLED module design. In addition,

the display will have immediate effect once this command is issued. That is, if this command is sent during normal display,

the graphic display will be vertically flipped.

E

E

RD

E

RD

WR /

WR

A0

0 1 0 1 1 0 0 D * * *

When D = “L”, Scan from COM0 to COM [N -1]. (POR)

When D = “H”, Scan from COM [N -1] to COM0.

16. Set Display Offset: (Double Bytes Command)

This is a double byte command. The next command specifies the mapping of display start line to one of COM0-63 (it is

assumed that COM0 is the display start line, that equals to 0). For example, to move the COM16 towards the COM0

direction for 16 lines, the 6-bit data in the second byte should be given by 010000. To move in the opposite direction by 16

lines, the 6-bit data should be given by (64-16), so the second byte should be 100000.

Display Offset Mode Set: (D3H)

A0

0 1 0 1 1 0 1 0 0 1 1

Display Offset Data Set: (00H~3FH)

A0

0 1 0 * * 000000 0 (POR)

0 1 0 * * 000010 1

0 1 0 * * 000011 2

0 1 0 : :

0 1 0 * * 1 1 1 1 1 0 62

0 1 0 * * 1 1 1 1 1 1 63

RD

WR /

WR

WR /

WR

D7 D6 D5 D4 D3 D2 D1 D0 COMx

D7 D6 D5 D4 D3 D2 D1 D0

D7 D6 D5 D4 D3 D2 D1 D0

Note: “*” stands for “Don’t care”

20 V0.13

SH1101A

17. Set Display Clock Divide Ratio/Oscillator Frequency: (Double Bytes Command)

This command is used to set the frequency of the internal display clocks (DCLKs). It is defined as the divide ratio (Value

from 1 to 16) used to divide the oscillator frequency. POR is 1. Frame frequency is determined by divide ratio, number of

display clocks per row, MUX ratio and oscillator frequency.

Divide Ratio/Oscillator Frequency Mode Set: (D5H)

A0

E

RD

0 1 0 1 1 0 1 0 1 0 1

Divide Ratio/Oscillator Frequency Data Set: (00H - 3FH)

A0

E

RD

0 1 0 A7 A6 A5 A4 A3 A2 A1 A0

A3 - A0 defines the divide ration of the display clocks (DCLK). Divide Ration = A[3:0]+1.

WR /

WR

WR /

WR

D7 D6 D5 D4 D3 D2 D1 D0

D7 D6 D5 D4 D3 D2 D1 D0

A

A

3

A

2

A

1

Divide Ration

0

0 0 0 0 1 (POR)

: :

1 1 1 1 16

A7 - A4 sets the oscillator frequency. Oscillator frequency increase with the value of A[7:4] and vice versa.

A

7 A6 A5 A4

Oscillator Frequency of

ƒ

OSC

0 0 0 0 -25%

0 0 0 1 -20%

0 0 1 0 -15%

0 0 1 1 -10%

0 1 0 0 -5%

0 1 0 1 ƒ

OSC

(POR)

0 1 1 0 +5%

0 1 1 1 +10%

1 0 0 0 +15%

1 0 0 1 +20%

1 0 1 0 +25%

1 0 1 1 +30%

1 1 0 0 +35%

1 1 0 1 +40%

1 1 1 0 +45%

1 1 1 1 +50%

21 V0.13

SH1101A

18. Set Dis-charge/Pre-charge Period: (Double Bytes Command)

This command is used to set the duration of the pre-charge period. The interval is counted in number of

DCLK. POR is 2 DCLKs.

Pre-charge Period Mode Set: (D9H)

A0

E

RD

0 1 0 1 1 0 1 1 0 0 1

Dis-charge/Pre-charge Period Data Set: (00H - FFH)

A0

E

RD

0 1 0 A7A6A5A4A3A2 A1 A0

Pre-charge Period Adjust: (A3 - A0)

3 A2 A1 A0 Pre-charge Period

A

0 0 0 0 INVALID

0 0 0 1 1 DCLKs

0 0 1 0 2 DCLKs (POR)

: :

1 1 1 0 14 DCLKs

1 1 1 1 15 DCLKs

Dis-charge Period Adjust: (A7 - A

)

4

A7 A6 A5 A4 Dis-charge Period

0 0 0 0 INVALID

0 0 0 1 1 DCLKs

0 0 1 0 2 DCLKs (POR)

: :

1 1 1 0 14 DCLKs

1 1 1 1 15 DCLKs

19. Set Common pads hardware configuration: (Double Bytes Command)

This command is to set the common signals pad configuration (sequential or alternative) to match the OLED panel

hardware layout

Common Pads Hardware Configuration Mode Set: (DAH)

A0

E

RD

0 1 0 1 1 0 1 1 0 1 0

Sequential/Alternative Mode Set: (02H - 12H)

A0

E

RD

0 1 0 0 0 0 D 0 0 1 0

When D = “L”, Sequential.

COM31, 30 – 1, 0 SEG0, 1 - 130, 131 COM32, 33 - 62, 63

When D = “H”, Alternative. (POR)

COM62, 60 – 2, 0 SEG0, 1 - 130, 131 COM1, 3 - 61, 63

WR /

WR

WR /

WR

WR /

WR /

WR

D7 D6 D5 D4 D3 D2 D1 D0

D7 D6 D5 D4 D3 D2 D1 D0

D7 D6 D5 D4 D3 D2 D1 D0

D7 D6 D5 D4 D3 D2 D1 D0

22 V0.13

SH1101A

20. Set VCOM Deselect Level: (Double Bytes Command)

This command is to set the common pad output voltage level at deselect stage.

VCOM Deselect Level Mode Set: (DBH)

A0

E

RD

0 1 0 1 1 0 1 1 0 1 1

VCOM Deselect Level Data Set: (00H - FFH)

A0

E

RD

0 1 0 A7 A6 A5 A4 A3 A2 A1 A0

V

COM

= β X V

= (0.430+ A[7:0] X 0.006415) X V

REF

A[7:0] β A[7:0] β

00H 0.430 20H

01H 21H

02H 22H

03H 23H

04H 24H

05H 25H

06H 26H

07H 27H

08H 28H

09H 29H

0AH 2AH

0BH 2BH

0CH 2CH

0DH 2DH

0EH 2EH

0FH 2FH

10H 30H

11H 31H

12H 32H

13H 33H

14H 34H

15H 35H 0.770 (POR)

16H 36H

17H 37H

18H 38H

19H 39H

1AH 3AH

1BH 3BH

1CH 3CH

1DH 3DH

1EH 3EH

1FH 3FH

40H - FFH 1

WR /

WR

WR /

WR

D7 D6 D5 D4 D3 D2 D1 D0

D7 D6 D5 D4 D3 D2 D1 D0

REF

23 V0.13

SH1101A

21. Read-Modify-Write: (E0H)

A pair of Read-Modify-Write and End commands must always be used. Once read-modify-write is issued, column address

is not incremental by read display data command but incremental by write display data command only. It continues until End

command is issued. When the End is issued, column address returns to the address when read-modify-write is issued. This

can reduce the microprocessor load when data of a specific display area is repeatedly changed during cursor blinking or

others.

A0

0 1 0 1 1 1 0 0 0 0 0

Cursor display sequence:

E

RD

WR /

WR

D7 D6 D5 D4 D3 D2 D1 D0

Set Page Address

Set Column Address

Read-Modify-Write

Dummy Read

No

Read Data

Data process

Write Data

Completed?

Yes

End

Figure. 6

22. End: (EEH)

Cancels Read-Modify-Write mode and returns column address to the original address (when Read-Modify-Write is issued.)

A0

E

RD

WR /

WR

D7 D6 D5 D4 D3 D2 D1 D0

0 1 0 1 1 1 0 1 1 1 0

Return

Column address

N N+1 N+2 N+m N

Read-Modify-Write

mode is selected

N+3

Figure. 7

24 V0.13

End

SH1101A

23. NOP: (E3H)

Non-Operation Command.

A0

E

RD

0 1 0 1 1 1 0 0 0 1 1

24. Write Display Data

Write 8-bit data in display RAM. As the column address is incremental by 1 automatically after each write, the

microprocessor can continue to write data of multiple words.

WR

WR /

D7 D6 D5 D4 D3 D2 D1 D0

A0

E

RD

WR /

WR

D7 D6 D5 D4 D3 D2 D1 D0

1 1 0 Write RAM data

25. Read Status

A0

E

RD

0 0 1

WR /

WR

D7 D6 D5 D4 D3 D2 D1 D0

BUSY ON/OFF

* * *

0 0 0

BUSY: When high, the SH1101A is busy due to internal operation or reset. Any command is rejected until BUSY goes

low. The busy check is not required if enough time is provided for each cycle.

ON/OFF: Indicates whether the display is on or off. When goes low the display turns on. When goes high, the display turns

off. This is the opposite of Display ON/OFF command.

26. Read Display Data

Reads 8-bit data from display RAM area specified by column address and page address. As the column address is

increment by 1 automatically after each write, the microprocessor can continue to read data of multiple words. A single

dummy read is required immediately after column address being setup. Refer to the display RAM section of FUNCTIONAL

DESCRIPTION for details. Note that no display data can be read via the serial interface.

A0

E

RD

WR /

WR

D7 D6 D5 D4 D3 D2 D1 D0

1 0 1 Read RAM data

25 V0.13

SH1101A

Command Table

Command

1. Set Column Address

4 lower bits

2. Set Column

Address 4 higher

bits

3. Reserved

Command

4. Reserved

Command

5. Reserved

Command

6. Set Display Start

Line

7. The Contrast

Control Mode Set

Contrast Data

Register Set

8. Set Segment

Re-map (ADC)

9. Set Entire Display

OFF/ON

10. Set Normal/

Reverse Display

11. Multiplex Ration

Mode Set

Multiplex Ration

Data Set

12. DC-DC Control

Mode Set

DC-DC ON/OFF

Mode Set

Code

A0

RD WR

0 1 0 0 0 0 0 Lower column address

0 1 0 0 0 0 1 Higher column address

0 1 0

0 1 0 0 0 1 0 0 1 1 0

0 1 0

0 1 0

0 1 0

0 1 0

0 1 0

0 1 0

0 1 0

0 1 0

0 1 0 * *

0 1 0

0 1 0 1 0 0 0 1 0 1 D

D7 D6 D5 D4 D3 D2 D1 D0

0 0 1 0 0 1 0 0

0 0 1 0 1 1 1 D

0 1 Line address

1 0 0 0 0 0 0 1

Contrast Data

1 0 1 0 0 0 0 ADC

1 0 1 0 0 1 0 D

1 0 1 0 0 1 1 D

1 0 1 0 1 0 0 0

Multiplex Ratio

1 0 1 0 1 1 0 1

Function

Sets 4 lower bits of column

address of display RAM in

register. (POR = 00H)

Sets 4 higher bits of column

address of display RAM in

register. (POR = 10H)

Reserved

Reserved

Reserved

Specifies RAM display line

for COM0. (POR = 40H)

This command is to set Contrast

Setting of the display.

The chip has 256 contrast steps

from 00 to FF. (POR = 80H)

The right (0) or left (1)

rotation. (POR = A0H)

Selects normal display (0) or

Entire Display ON (1). (POR

= A4H)

Normal indication (0) when

low, but reverse indication (1)

when high. (POR = A6H)

This command switches

default 63 multiplex mode to

any multiplex ratio from 1 to

64. (POR = 3FH)

This command is to control the

DC-DC voltage DC-DC will be

turned on when display on

converter (1) or DC-DC OFF (0).

(POR = 8BH)

26 V0.13

SH1101A

Command Table (Continued)

Command

A0

RD WR

13. Display OFF/ON 0 1 0

14. Set Page Address 0 1 0

15. Set Common

Output Scan

0 1 0

Direction

16. Display Offset

Mode Set

Display Offset Data

Set

0 1 0

0 1 0 * *

17. Set Display Divide

Ratio/Oscillator

Frequency Mode

0 1 0 1 1 0 1 0 1 0 1

Set

Divide Ratio/Oscillator

Frequency Data Set

0 1 0 Oscillator Frequency

18. Dis-charge /

Pre-charge Period

0 1 0

Mode Set

Dis-charge

/Pre-charge Period

0 1 0 Dis-charge Period

Data Set

19. Common Pads

Hardware

Configuration

0 1 0 1 1 0 1 1 0 1 0

Mode Set

Sequential/Alternat

ive Mode Set

20. VCOM Deselect

Level Mode Set

VCOM Deselect

Level Data Set

21. Read-Modify-Write

22. End

23. NOP

24. Write Display Data

25. Read Status

26. Read Display Data

0 1 0

0 1 0 1 1 0 1 1 0 1 1

0 1 0

0 1 0 1 1 1 0 0 0 0 0 Read-Modify-Write start.

0 1 0 1 1 1 0 1 1 1 0 Read-Modify-Write end.

0 1 0 1 1 1 0 0 0 1 1 Non-Operation Command

1 1 0 Write RAM data

0 0 1

1 0 1 Read RAM data

Code

D7 D6 D5 D4 D3 D2 D1 D0

1 0 1 0 1 1 1 D

1 0 1 1 Page Address

1 1 0 0 D * * *

1 1 0 1 0 0 1 1

COMx

Divide Ratio

1 1 0 1 1 0 0 1

Pre-charge Period

0 0 0 D 0 0 1 0

BUSY

ON/

OFF

VCOM (β X V

* * * 0 0 0

REF)

Function

Turns on OLED panel (1) or

turns off (0). (POR = AEH)

Specifies page address to

load display RAM data to

page address register. (POR

= B0H)

Scan from COM0 to COM [N

- 1] (0) or Scan from COM [N

-1] to COM0 (1). (POR = C0H)

This is a double byte

command which specifies

the mapping of display start

line to one of COM0-63.

(POR = 00H)

This command is used to set

the frequency of the internal

display clocks.

(POR = 50H)

This command is used to

set the duration of the

dis-charge and pre-charge

period. (POR = 22H)

This command is to set the

common signals pad

configuration. (POR = 12H)

This command is to set the

common pad output voltage

level at deselect stage.

(POR = 35H)

Note: Do not use any other command, or the system malfunction may result.

27 V0.13

SH1101A

Command Description

Instruction Setup: Reference

1. Power On and Initialization

1.1. When the built-in DC-DC pump power is being used immediately after turning on the power:

V

DD1

- VSS is off

DD2

- VSS is off

V

Turn on the V

DD1

- V

SS

and V

DD2

- V

keeping the pin = "L"

RES

SS

power

When the power is stabilized

Release the reset state. ( pin = "H").

RES

Reset timing depends on SH1101A data sheet.

Initialized state (Default)

Function setup by command input (User setup):

( 8 ) Segment Re-map (ADC) selection

( 19 ) COM Sequential / Alternative Mode

selection

( 15 ) COM Output Scan Direction selection

( 11 ) Multiplex Ration Mode selection

( 17 ) Display Divide Ratio / Oscillator

Frequency Mode selection

Function setup by command input (User setup):

( 20 ) VCOM Deselect Level set

( 7 ) Contrast set

Function setup by command input (User setup):

( 12 ) DC-DC Control set: ADH

Built-in DC-DC turn on: 8BH ( POR )

Function setup by command input (User setup):

( 13 ) Display ON set: AFH

Typically, 150ms delay is recommended to wait.

Function setup by command input (User setup):

( 6 ) Display Start Line set

( 14 ) Page Address set

( 1,2 ) Column Address set

Display Data Send

Function setup by command input (User setup):

Clear internal RAM to "00H"

28 V0.13

SH1101A

1.2. When the external DC-DC pump power is being used immediately after turning on the power:

V

DD1

- VSS is off

External DC-DC is off

Turn on the V

DD1

RES

- V

SS

power keeping the

pin = "L"

When the power is stabilized

Release the reset state. ( pin = "H").

RES

Reset timing depends on SH1101A data sheet.

Initialized state (Default)

Function setup by command input (User setup):

( 8 ) Segment Re-map (ADC) selection

( 19 ) COM Sequential / Alternative Mode

selection

( 15 ) COM Output Scan Direction selection

( 11 ) Multiplex Ration Mode selection

( 17 ) Display Divide Ratio / Oscillator

Frequency Mode selection

Function setup by command input (User setup):

( 20 ) VCOM Deselect Level set

( 7 ) Contrast set

Turn on the external DC-DC Power and VPP is

on.

When the external DC-DC Power ( VPP )is

stabilized .

Typically, 100ms delay is recommended to wait.

Function setup by command input (User setup):

( 12 ) DC-DC Control set: ADH

Built-in DC-DC turn off: 8AH

Function setup by command input (User setup):

( 13 ) Display ON set: AFH

Typically, 50ms delay is recommended to wait.

Function setup by command input (User setup):

( 6 ) Display Start Line set

( 14 ) Page Address set

( 1,2 ) Column Address set

Display Data Send

Function setup by command input (User setup):

Clear internal RAM to "00H"

29 V0.13

2. Power Off

SH1101A

Optional status

Function setup by command input (User setup):

(13) Display OFF set: AEH

Turn off the External DC-DC Power off and V

PP

is off.

When the external DC-DC Power (VPP) reach

0V.

Typically, 100ms delay is recommended to wait.

Turn off the V

DD1

- VSS and V

DD2

- VSS power

30 V0.13

SH1101A

Absolute Maximum Rating*

DC Supply Voltage (VDD1, VDD2) . . . . . . . .. . -0.3V to +3.6V

DC Supply Voltage (V

Input Voltage . . . . . . . . . . . . . . . . . . . . -0.3V to V

Operating Ambient Temperature . . . . . . . . . -40

Storage Temperature . . . . . . . . . .. . . . . . . -55

PP) . . . . . . . . . . . . . . . . -0.3V to +18V

DD1 + 0.3V

°C to +85°C

°C to +125°C

*Comments

Stresses above those listed under "Absolute Maximum

Ratings" may cause permanent damage to this device.

These are stress ratings only. Functional operation of this

device under these or any other conditions above those

indicated in the operational sections of this specification is

not implied or intended. Exposure to the absolute maximum

rating conditions for extended periods may affect device

reliability.

Electrical Characteristics

DC Characteristics (VSS = 0V, VDD1 = 2.4 - 3.5V TA =+25

Symbol Parameter Min. Typ. Max. Unit Condition

V

Operating voltage 2.4 - 3.5 V

DD1

VDD2 Operating voltage 2.4 - 3.5 V

VPP OLED Operating voltage 7.0 - 16.0 V

VBREF Internal voltage reference 1.20 1.26 1.32 V

IDD1

IDD2

Dynamic current

consumption 1

Dynamic current

consumption 2

OLED dynamic current

IPP

consumption

Sleep mode current

consumption in V

ISP

Sleep mode current

consumption in V

DD1 & VDD2

PP

- 110 160

- 190 285

- 550 825

- 0.01 5

- 0.01 5

-308 -320 -342

- -220 -

ISEG Segment output current

- -120 -

- -20 -

∆ISEG1

∆ISEG2

Segment output current

uniformity

Adjacent segment output

current uniformity

- -

- -

C, unless otherwise specified)

°

With one 1

DD1 = 3V, VDD2 = 3V, IREF = 10µA, Contrast α = 256,

V

Bulid-in DC-DC OFF, Display ON, display data = All ON,

µA

µF capacitor

No panel attached.

DD1 = 3V, VDD2 = 3V, VPP = 12V, IREF = -10µA,

V

µA

Contrast

α = 256, Bulid-in DC-DC ON, Display ON,

Display data = All ON, No panel attached.

DD1 = 3V, VDD2 = 3V, VPP = 12V, IREF = -10µA,

V

A

µ

Contrast

α = 256, Display ON, All ON,

No panel attached.

µA During sleep, TA = +25°C, VDD1 = 3V, VDD2 = 3V.

µA During sleep, TA = +25°C, VPP = 12V.

DD1 = 3V, VPP = 12V, IREF = -10

±3

±2

V

µA

Display ON. Contrast

DD1 = 3V, VPP = 12V, IREF = -10

V

µA

Display ON. Contrast

DD1 = 3V, VPP = 12V, IREF = -10µA, RLOAD = 20kΩ,

V

µA

Display ON. Contrast α = 96.

DD1 = 3V, VPP = 12V, IREF = -10µA, RLOAD = 20kΩ,

V

µA

Display ON. Contrast α = 16.

∆I

SEG1 = (ISEG - IMID)/IMID X 100%

I

MID = (IMAX + IMIN)/2

%

SEG [0:131] at contrast α = 256.

I

∆I

= (I

SEG

[N] - I

SEG2

%

SEG [0:131] at contrast

I

SEG

α = 256.

α = 176.

[N+1])/(I

= 256.

α

SEG

µ

µ

[N] + I

A, RLOAD = 20kΩ,

A, RLOAD = 20kΩ,

SEG

[N+1]) X 100%

31 V0.13

SH1101A

DC Characteristics (Continued)

Symbol Parameter Min. Typ. Max. Unit Condition

VIHC High-level input voltage 0.8 X VDD1 - VDD1 V

VILC Low-level input voltage VSS - 0.2 X VDD1 V

A0, D0 - D7,

CL, C86, P/S and

RD (E), WR ( WR / ), CS , CLS,

RES .

VOHC High-level output voltage 0.8 X VDD1 - VDD1 V IOH = -0.5mA (D0 - D7, and CL).

VOLC Low -level output voltage VSS - 0.2 X VDD1 V IOL = 0.5mA (D0 - D7, and CL).

ILI Input leakage current -1.0 - 1.0

IHZ HZ leakage current -1.0 - 1.0

f

Oscillation frequency 315 360 420 kHz

OSC

f

Frame frequency for 64

FRM

Commons

- 104 - Hz

IN = VDD1 or VSS (A0,

V

A

µ

CS , CLS, C86, P/S and

When the D0 - D7, and CL are in high

A

µ

impedance.

A = +25

T

When f

C.

°

OSC = 360kHz, Divide ratio = 1, common

width = 54 DCLKs.

RD

(E),

RES

).

WR ( WR / ),

32 V0.13

SH1101A

AC Characteristics

(1) System buses Read/Write characteristics 1 (For the 8080 Series Interface MPU)

A0

t

CS

,

RD

WR

D0~D7

(WRITE)

D0~D7

(READ)

AS8

t

F

t

CCLW

t

CCLR

t

DS8

t

ACC8

t

AH8

t

t

R

DH8

t

CH8

t

CYC8

t

CCHW

t

CCHR

(V

DD1 = 2.4 - 3.5V, TA = +25°C)

Symbol Parameter Min. Typ. Max. Unit Condition

t

System cycle time 300 - - ns

CYC8

tAS8 Address setup time 0 - - ns

t

Address hold time 0 - - ns

AH8

tDS8 Data setup time 40 - - ns

t

Data hold time 15 - - ns

DH8

tCH8 Output disable time 10 - 70 ns CL = 100pF

tACC8

RD access time

- - 140 ns C

L = 100pF

tCCLW Control L pulse width (WR) 100 - - ns

tCCLR Control L pulse width (RD) 120 - - ns

tCCHW Control H pulse width (WR) 100 - - ns

tCCHR Control H pulse width (RD) 100 - - ns

tR Rise time - - 15 ns

tF Fall time - - 15 ns

33 V0.13

SH1101A

(2) System buses Read/Write Characteristics 2 (For the 6800 Series Interface MPU)

A0

W/R

t

AS6

t

AH6

CS

t

F

t

EWHWtEWHR

t

R

t

CYC6

E

t

t

DS6

t

EWLW

DH6

t

EWLR

D0~D7

(WRITE)

t

ACC6

t

OH6

D0~D7

(READ)

(V

DD1 = 2.4 - 3.5V, TA = +25

Symbol Parameter Min. Typ. Max. Unit Condition

tCYC6 System cycle time 300 - - ns

tAS6 Address setup time 0 - - ns

tAH6 Address hold time 0 - - ns

t

Data setup time 40 - - ns

DS6

tDH6 Data hold time 15 - - ns

t

Output disable time 10 - 70 ns CL = 100pF

OH6

tACC6 Access time - - 140 ns CL = 100pF

t

Enable H pulse width (Write) 100 - - ns

EWHW

tEWHR Enable H pulse width (Read) 120 - - ns

tEWLW Enable L pulse width (Write) 100 - - ns

tEWLR Enable L pulse width (Read) 100 - - ns

tR Rise time - - 15 ns

tF Fall time - - 15 ns

°

C)

34 V0.13

SH1101A

(3) System buses Write characteristics 3(For the Serial Interface MPU)

t

CS

A0

SCL

SI

CSS

t

SAS

t

SCYC

t

SLW

t

F

t

SDS

t

t

SAH

R

t

SDH

t

SHW

t

CSH

t

F

(V

DD1 = 2.4 - 3.5V, TA = +25

°

C)

Symbol Parameter Min. Typ. Max. Unit Condition

tSCYC Serial clock cycle 250 - - ns

tSAS Address setup time 150 - - ns

tSAH Address hold time 150 - - ns

tSDS Data setup time 100 - - ns

tSDH Data hold time 100 - - ns

t

CSS

tCSH

t

SHW

CS setup time

CS hold time time

Serial clock H pulse width 100 - - ns

120 - - ns

60 - - ns

tSLW Serial clock L pulse width 100 - - ns

tR Rise time - - 15 ns

tF Fall time - - 15 ns

35 V0.13

(4) Reset Timing

SH1101A

RW

t

RES

t

R

Internal circuit

status

During reset End of reset

(V

DD1 = 2.4 - 3.5V, TA = +25°C)

Symbol Parameter Min. Typ. Max. Unit Condition

tR Reset time - - 1.0

tRW Reset low pulse width 5.0 - -

µs

µ

s

36 V0.13

SH1101A

Application Circuit (for reference only)

Reference Connection to MPU:

1. 8080 series interface: (Internal oscillator, External V

V

PP)

DD

MPU

CS

RES

A0

WR

RD

D7~D0

C

1

+

V

DD1

V

DD2

V

CL

V

SL

V

SS

SW

FB

SENSE

BREF

V

C86

SH1101A

P/S

CS

RES

A0

WR

RD

D7~D0

External V

PP

Note:

C1 - C3: 4.7µF.

R1: about 910kΩ, R1 = (Voltage at IREF - VSS)/IREF

CL

CLS

V

V

V

I

REF

COMH

REF

PP

C

2

+

C

3

+

R

1

Figure. 8

37 V0.13

SH1101A

2. 6800 Series Interface: (Internal oscillator, Built-in DC-DC)

C

+

C

1

D

C

4

+

R

1

+

C

5

2

R

R

3

C

L

Q

V

DD1

V

6

+

V

DD2

+

2

DD1

V

DD2

V

CL

V

SL

V

SS

SW

FB

SENSE

C

3

+

V

BREF

SH1101A

C86

P/S

MPU

CS

RES

A0

R / W

E

D7~D0

CS

RES

A0

WR

RD

D7~D0

CL

CLS

V

V

V

I

REF

COMH

REF

PP

C

7

+

R

4

Figure. 9

Note:

L, D, Q, R1, R2, R3, C1 - C6: Please refer to following description of DC-DC module.

, C7: 4.7µF

C

6

R3: about 910kΩ, R4 = (Voltage at IREF - VSS)/IREF

38 V0.13

SH1101A

3. Serial Interface: (External oscillator, External VPP)

1

C

V

DD

V

+

DD1

V

DD2

V

CL

V

SL

V

SS

SW

FB

SENSE

BREF

V

RES

MPU

SCL

External Clock

External V

PP

CS

A0

C86

SH1101A

P/S

CS

RES

A0

WR

RD

SI

D7~D2

D1

D0

CL

CLS

V

V

V

COMH

REF

PP

C

2

+

C

3

+

Note:

C

: 4.7µF

1 - C3

R1: about 910kΩ, R1 = (Voltage at I

REF

- VSS)/I

REF

I

REF

R

1

Figure. 10

39 V0.13

SH1101A

DC-DC:

Below application circuit is an example for the input voltage of 3V VDD2 to generate VPP of about 12V@10mA-25mA application.

LD

V

V

DD2

+

C

2

+

C

3

V

C

V

DD2

BREF

+

1

V

SS

C

4

+

3

DC-DC

SW

SENSE

QR

1

R

PP

V

SS

V

SS

FB

R

2

+

C

5

V

SS

Figure. 11

Symbol Value Recommendation

L

10µH

LQH3C100K24

D SCHOTTKY DIODE 20V@0.5A, MBR0520

Q MOSFET

R1

R2

R3

C1

C2

C3

C4

930k

110k

0.12

Ω

1 - 10

0.1 - 1

µF

1

µF

6.8

Ω

Ω

µF

µ

F

N-FET with low R

MGSF1N02LT1

1%, 1/8W

1%, 1/8W

1%, 1/2W

Ceramic/16V

Ceramic/16V

Ceramic/16V

Low ESR/25V

DS(ON)

and low V

TH,

C5 1000pF Ceramic/16V

40 V0.13

SH1101A

TCP Pin Layout

(Copper Side View)

41 V0.13

SH1101A

TCP Pin Assignment (Total: 211 pins)

Designation Pin No. Designation Pin No. Designation Pin No. Designation

Pin No.

1 NC 41

2 VSS 42

3 SW 43

4 V

44

DD2

5 FB 45

6 SENSE 46

7 VBREF 47

8 NC 48

9 NC 49

10 NC 50

11 V

51

DD1

12 C86 52

13 P/S 53

14 NC 54

15

16

CS

RES

55

56

17 A0 57

18

19

WR

RD

58

59

20 D0 60

COM48

COM46

COM44

COM42

COM40

COM38

COM36

COM34

COM32

COM30

COM28

COM26

COM24

COM22

COM20

COM18

COM16

COM14

COM12

COM10

21 D1 61

22 D2 62

23 D3 63

24 D4 64

25 D5 65

26 D6 66

COM8

COM6

COM4

COM2

COM0

NC

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

27 D7 67 NC 107

28 IREF 68

NC

108

29 VCOMH 69 NC 109

30 VPP 70

NC

110

31 NC 71 NC 111

32 NC 72 NC 112

33 NC 73 NC 113

34

35

36

37

38

39

40

COM62

COM60

COM58

COM56

COM54

COM52

COM50

74

75

76

77

78

79

80

SEG0

SEG1

SEG2

SEG3

SEG4

SEG5

SEG6

114

115

116

117

118

119

120

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

SEG13

SEG14

SEG15

SEG16

SEG17

SEG18

SEG19

SEG20

SEG21

SEG22

SEG23

SEG24

SEG25

SEG26

SEG27

SEG28

SEG29

SEG30

SEG31

SEG32

SEG33

SEG34

SEG35

SEG36

SEG37

SEG38

SEG39

SEG40

SEG41

SEG42

SEG43

SEG44

SEG45

SEG46

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

139

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

SEG47

SEG48

SEG49

SEG50

SEG51

SEG52

SEG53

SEG54

SEG55

SEG56

SEG57

SEG58

SEG59

SEG60

SEG61

SEG62

SEG63

SEG64

SEG65

SEG66

SEG67

SEG68

SEG69

SEG70

SEG71

SEG72

SEG73

SEG74

SEG75

SEG76

SEG77

SEG78

SEG79

SEG80

SEG81

SEG82

SEG83

SEG84

SEG85

SEG86

42 V0.13

SH1101A

TCP Pin Assignment (continued)

Pin No. Designation Pin No. Designation Pin No. Designation Pin No. Designation

161 SEG87 176 NC 191 COM27 206 COM57

162 SEG88 177 NC 192 COM29 207 COM59

163 SEG89 178 COM1 193 COM31 208 COM61

164 SEG90 179 COM3 194 COM33 209 COM63

165 SEG91 180 COM5 195 COM35 210 NC

166 SEG92 181 COM7 196 COM37 211 NC

167 SEG93 182 COM9 197 COM39

168 SEG94 183 COM11 198 COM41

169 SEG95 184 COM13 199 COM43

170 NC 185 COM15 200 COM45

171 NC 186 COM17 201 COM47

172 NC 187 COM19 202 COM49

173 NC 188 COM21 203 COM51

174 NC 189 COM23 204 COM53

175 NC 190 COM25 205 COM55

Note:

Following is the details of pad connection in SH1101A-TCP03 (TCP Form).

“CLS” pad connects to “VDD1” pad, Internal oscillator circuit is enabled.

“V

“VCL“ & “VSL“ pad connects to “VSS“ pad.

“C86“ & “P/S“ pad options can be selected by user. So SH1101A-TCP03 (TCP Form) supports 8-bit 6800-series parallel

“ pad connects to “VPP“ pad.

REF

interface, 8-bit 8080-series parallel interface or serial peripheral interface.

SH1101A-TCP03 (TCP Form) supports internal DC-DC converter function.

43 V0.13

SH1101A

External View of TCP Pins

□

44 V0.13

SH1101A

Cautions Concerning Storage:

1. When storing the product, it is recommended that it be left in its shipping package.

After the seal of the packing bag has been broken, store the products in a nitrogen atmosphere.

2. Storage conditions:

Storage state Storage conditions

unopened (less than 90 days)

After seal of broken (less than 30 days)

3. Don't store in a location exposed to corrosive gas or excessive dust.

4. Don't store in a location exposed to direct sunlight of subject to sharp changes in temperature.

5. Don't store the product such that it subjected to an excessive load weight, such as by stacking.

Deterioration of the plating may occur after long-term storage, so special care is required.

6.

It is recommended that the products be inspected before use.

Temperature: 5 to 30

Room temperature, dry nitrogen atmosphere

; humidity: 80%RH or less.

℃

45 V0.13

SH1101A

Ordering Information

Part No. Package

SH1101A-COG01 Gold bump on chip tray

SH1101A-TCP03 TCP Form

46 V0.13

SH1101A

Data Sheet Revision History

Version

Ordering Information:

0.13

0.1

0.0 Original Mar. 2005

1, SH1101AG changed to SH1101A-COG01

2, SH1101AB1 changed to SH1101A-TCP03 (Page 46)

1. “Pin Configuration”, “Pad Configuration” addition. (Page2)

2. “TAB Pin Layout”, “TAB Pin Assignment” addition. (Page

41~45)

3. “Ordering Information” addition. (Page 46)

Content Date

July. 2005

May. 2005

47 V0.13

Loading...

Loading...