Page 1

5

D D

4

3

2

1

Greenland

Napa

C C

REV : X03G

12/28/2005

@ : Nopop Component

B B

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Cover Sheet

Greenland-LA2732P

163Wednesday, December 28, 2005

1

X03

http://hobi-elektronika.net

5

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

4

3

2

Title

Size Document Number Rev

Custom

Date: Sheet of

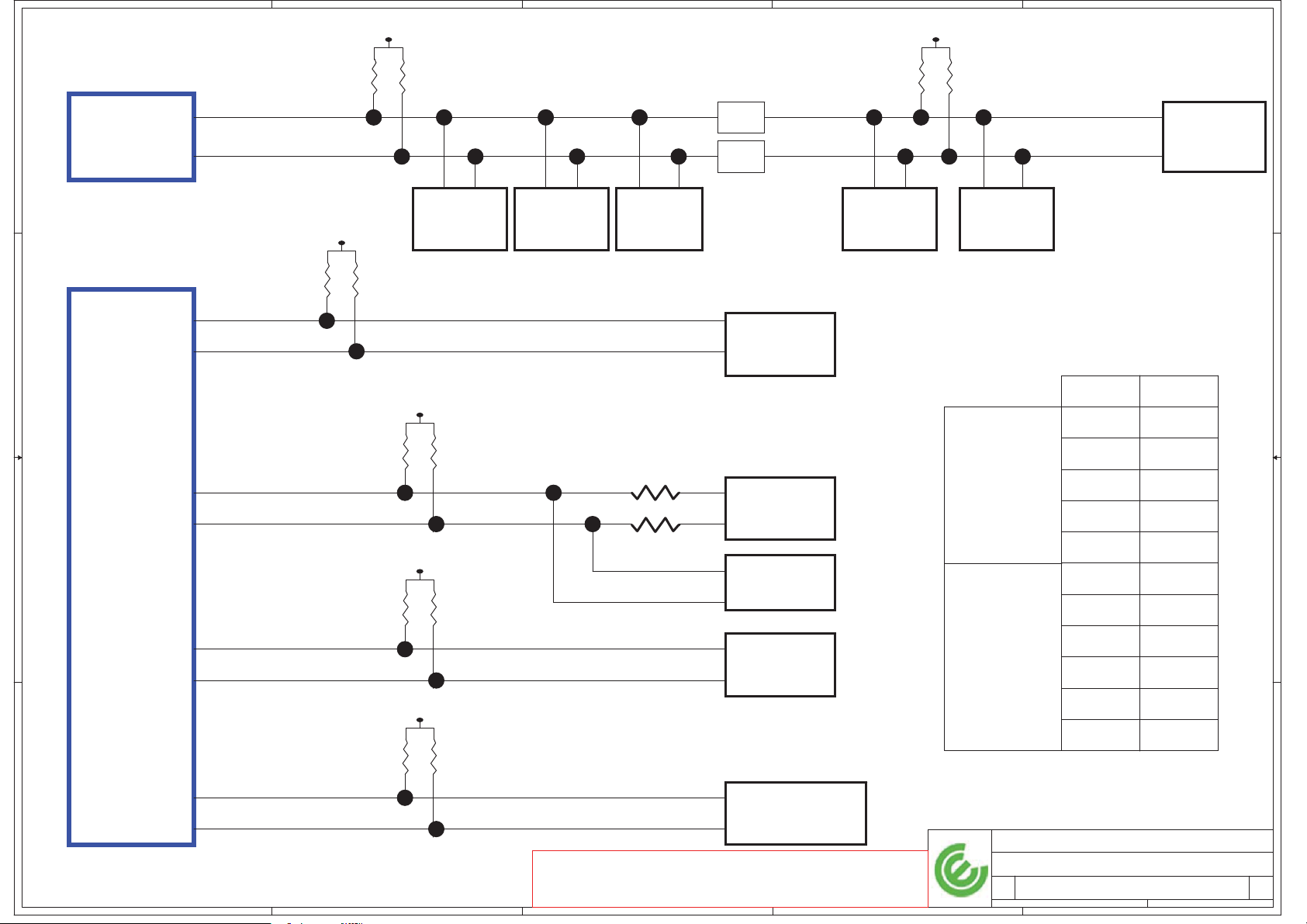

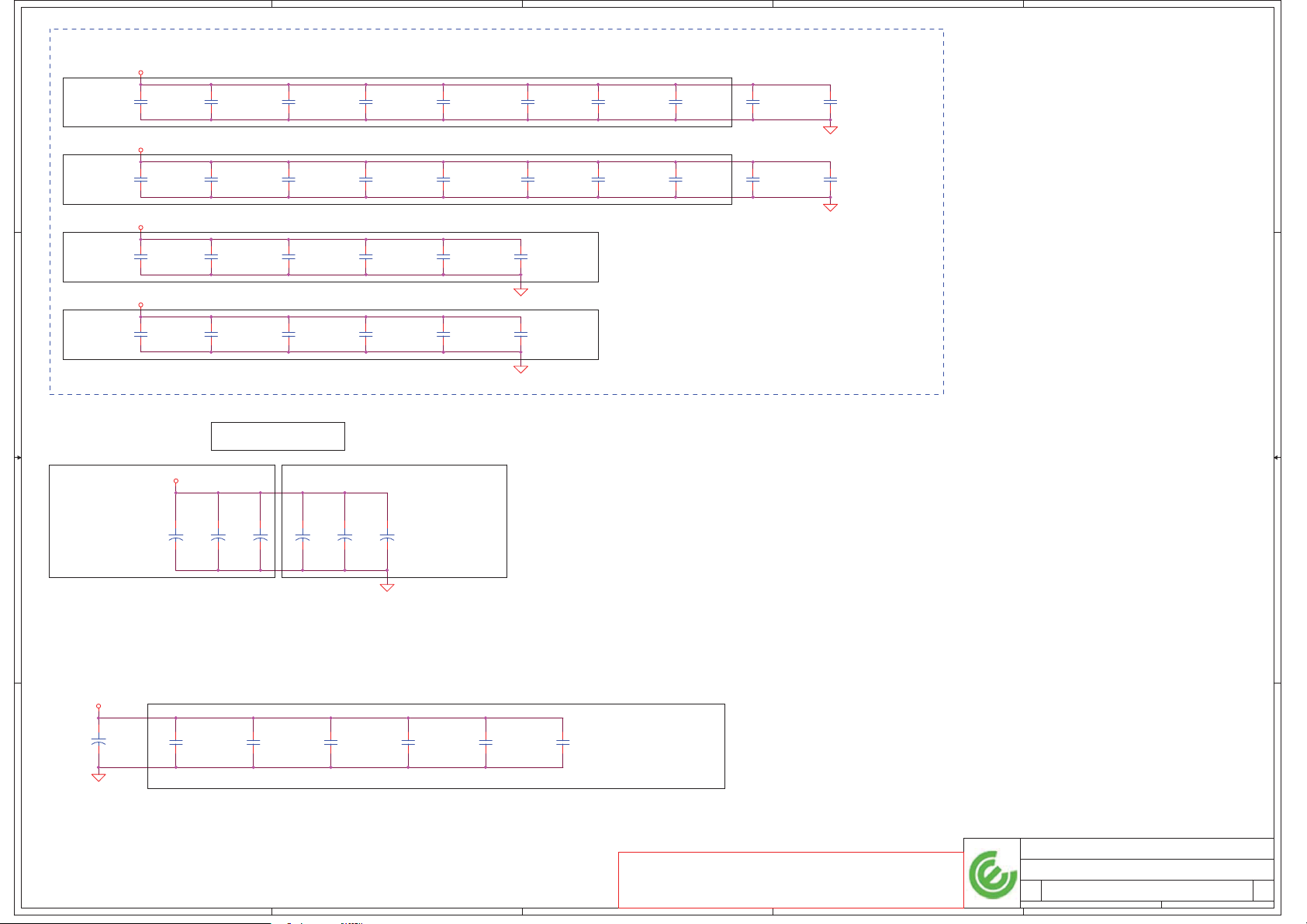

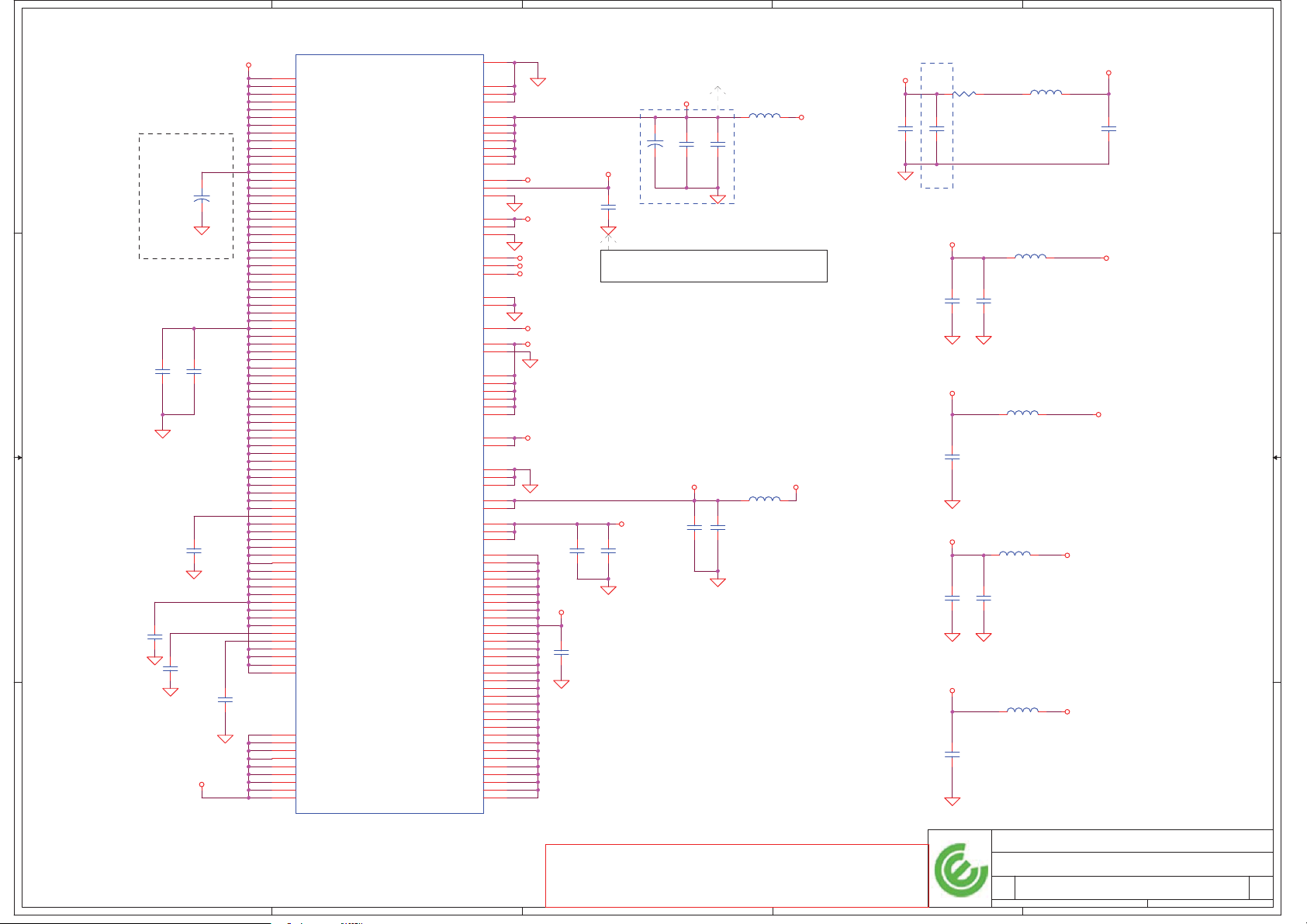

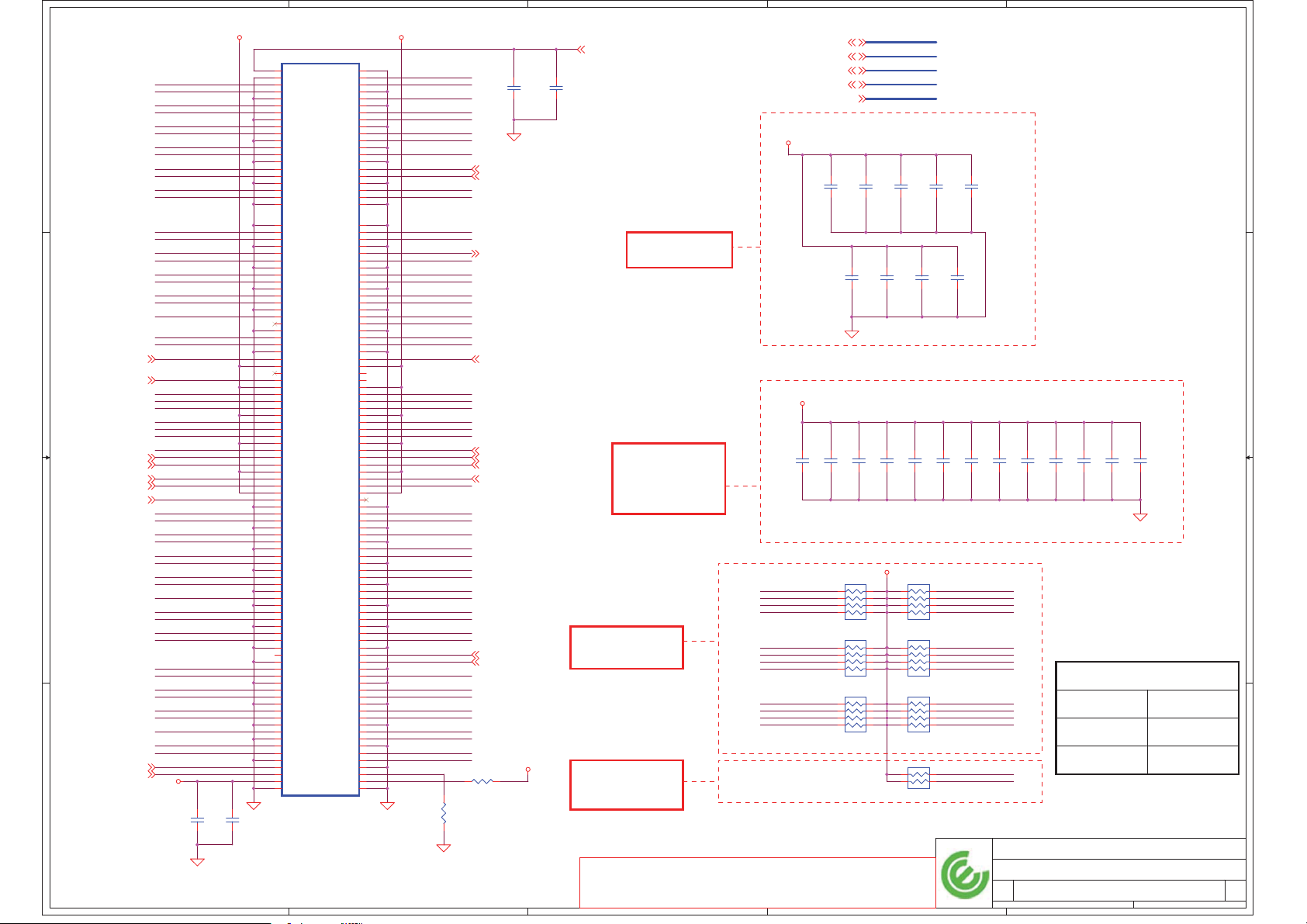

Page 2

5

4

3

2

1

Compal confidential

Block Diagram

Pentium-M

D D

GUARDIAN II

EMC4000

/+2.5V

page 16

SMBus

Yonah

uFCPGA CPU

page 7,8,9

Clock Generator

CK410M

page 6

Fan Control

CRT CONN.

HA#(3..31)

& TV-OUT

page 20

VGA

Board

VGA CONN.

page 19

C C

PCI-E 16X

System Bus

FSB 533/667 MHz

INTEL

Calistoga

1466pin BGA

page 10,11,12,13,14,15

DMI

1.5V

100MHz

PCI BUS

IDSEL:AD17

(PIRQA/B#,GNT#2,REQ#2)

3.3V 33MHz

INTEL

ICH7-M

652pin BGA

CardBus Controller

B B

CF card

page35

A A

http://hobi-elektronika.net

page 23

page 36

page 31

page 36

5

RICHO R5C843

4-in-1 Conn

page34

Int.KBD

ST M25P80

ICH7M-Port1

Mini Card WLAN

WUSB

Mini Card TV

page 34,35

1394 Conn

page 39

page 37

USBPORT 0

USBPORT 1

USBPORT 2

USBPORT 3

USBPORT 4

SPI

page34

4

SPI

SMSC

MEC 5004

SMSC

ECE 5011

LPC BUS

3.3V 33MHz

page 37

BC BUS

page 38

21,22,23,24page

HD#(0..63)

PCI Express

48MHz / 480Mb

Memory

BUS(DDRII)

1.8V 533 / 667MHz

PORT1

PORT2

PORT4

PORT3

3.3V BitCLK

3.3V or 5V SATA

ATA100

Mini Card TV

Mini Card WLAN

Express card

LAN BCM5753

SATA

SO-DIMM X2

BANK 0, 1, 2, 3

page 36

page 36

page 40

page 32 page 33

page 17,18

USBPORT 4 of ECE5011

USBPORT 1 of ECE5011

USBPORT 2 of ICH7

RJ45 with Giga Magnetic

Azalia CODEC

STAC9220

page 26

CDROM

page 25

USB2.0

page 31

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

HDD X2

page 25

USBPORT 0

USBPORT 1

USBPORT 2

USBPORT 3

USBPORT 4

USBPORT 5

USBPORT 6

USBPORT 7

AMP &

Phone Jack

Blue Tooth

ECE USB[0]

Express Card

CIR

JUSB1

JUSB2

JUSB3

JUSB4

page 28

page 29

page 38

page 40

page 29

page 31

page 31

page 31

page 31

2

Azalia

Subwoofer

page 29

Power Control

Power Sequence

LED & PWR switch

DC IN

BATT IN

1.5V/1.05V(+VCCP)

MDC

page 29

5V/3.3V/12V

1.8V / 0.9V

VCORE

CHARGER

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Block Diagram

Greenland-LA2732P

1

page 16

page 42

page 43

page 41

page 45

page 46

page 47

page 48,49

page 50

page 51

page 52

263Wednesday, December 28, 2005

X03

of

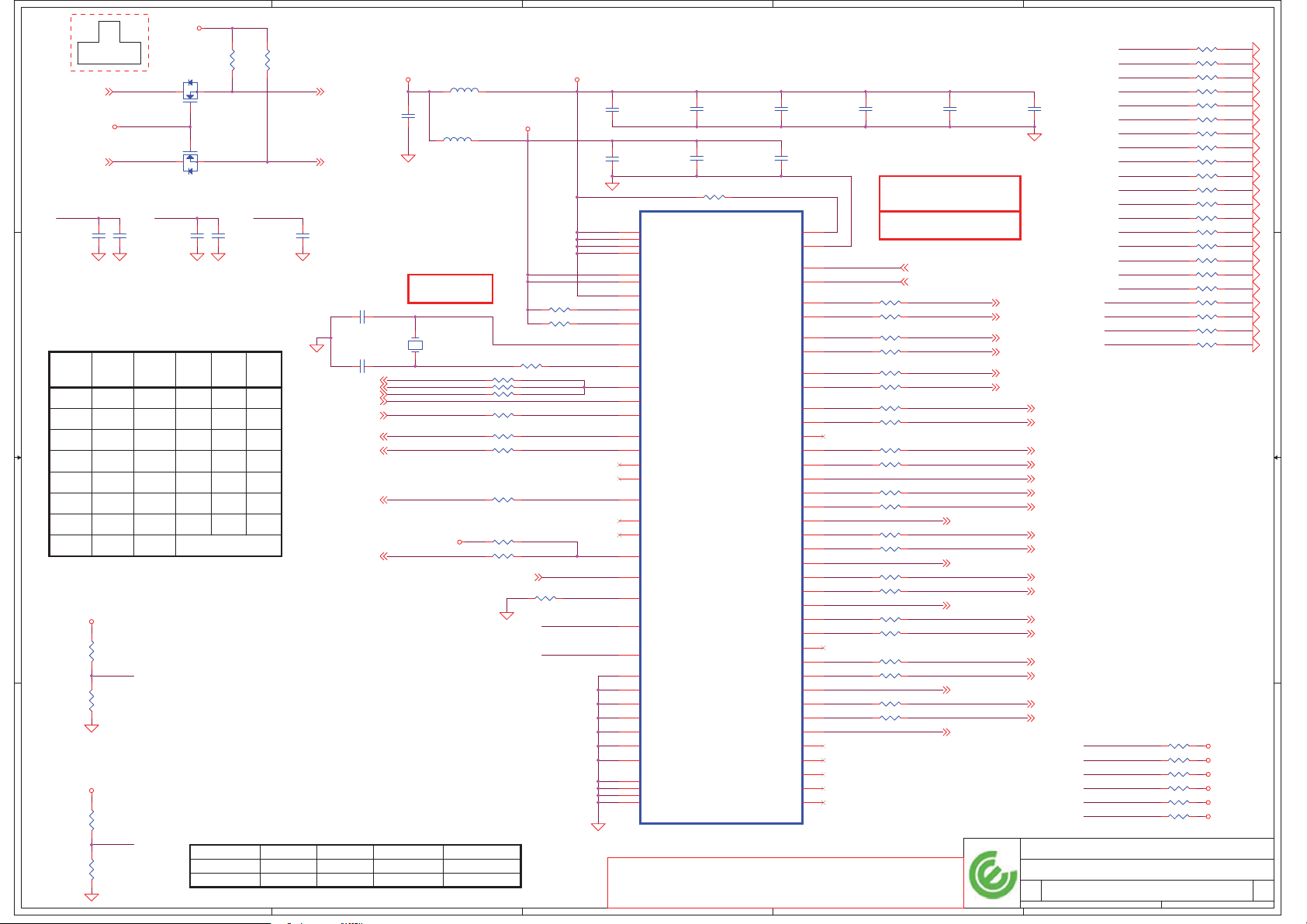

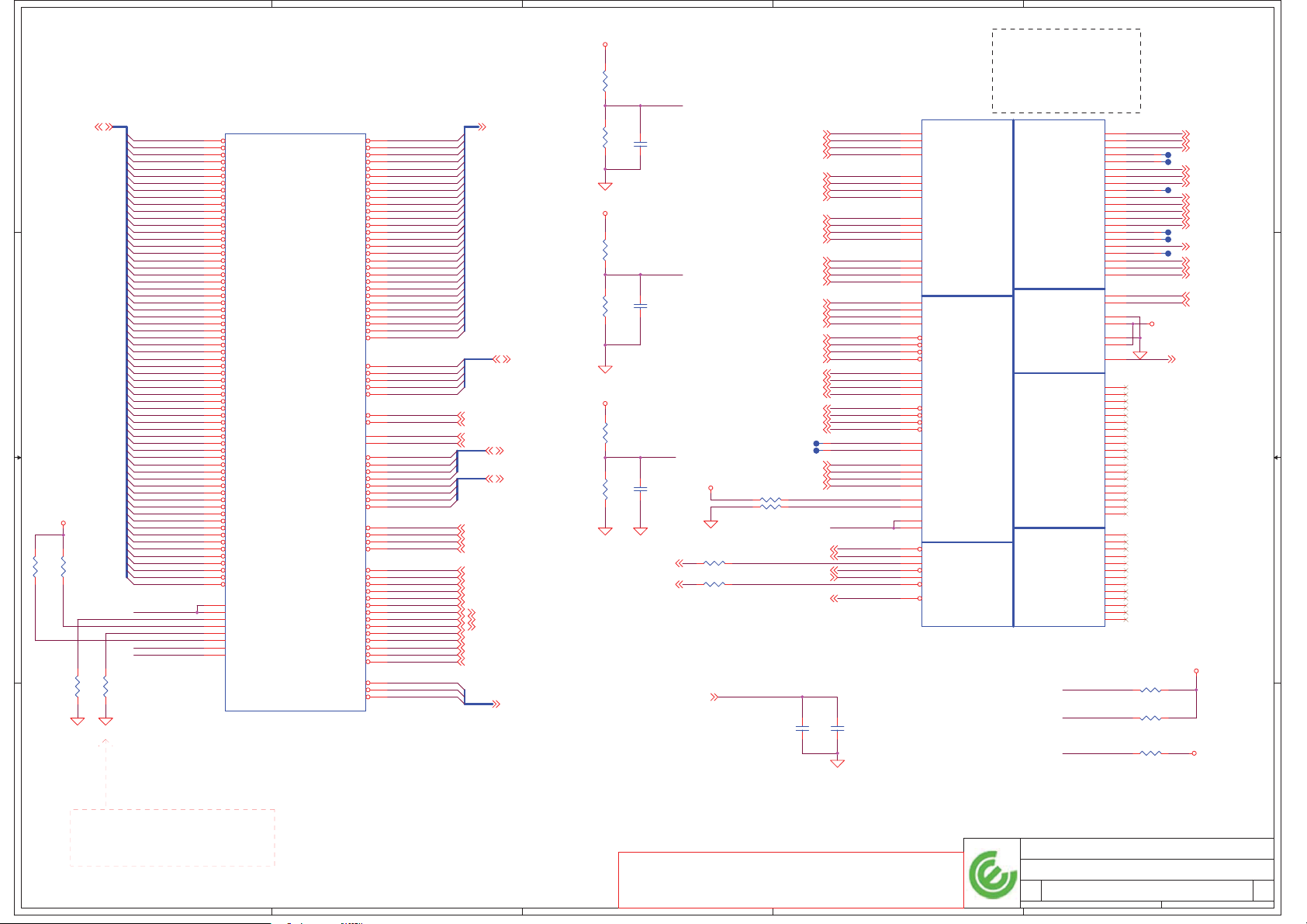

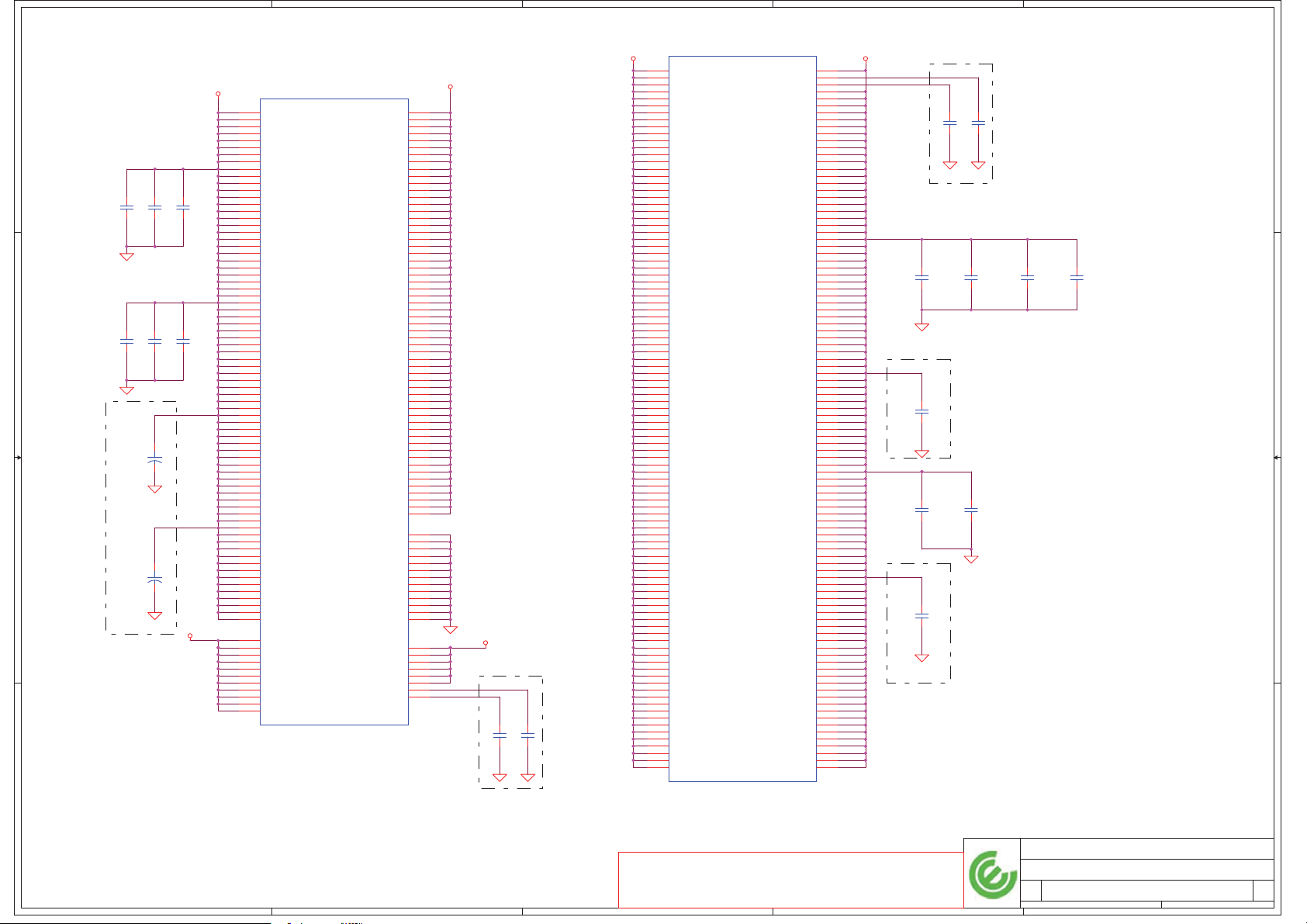

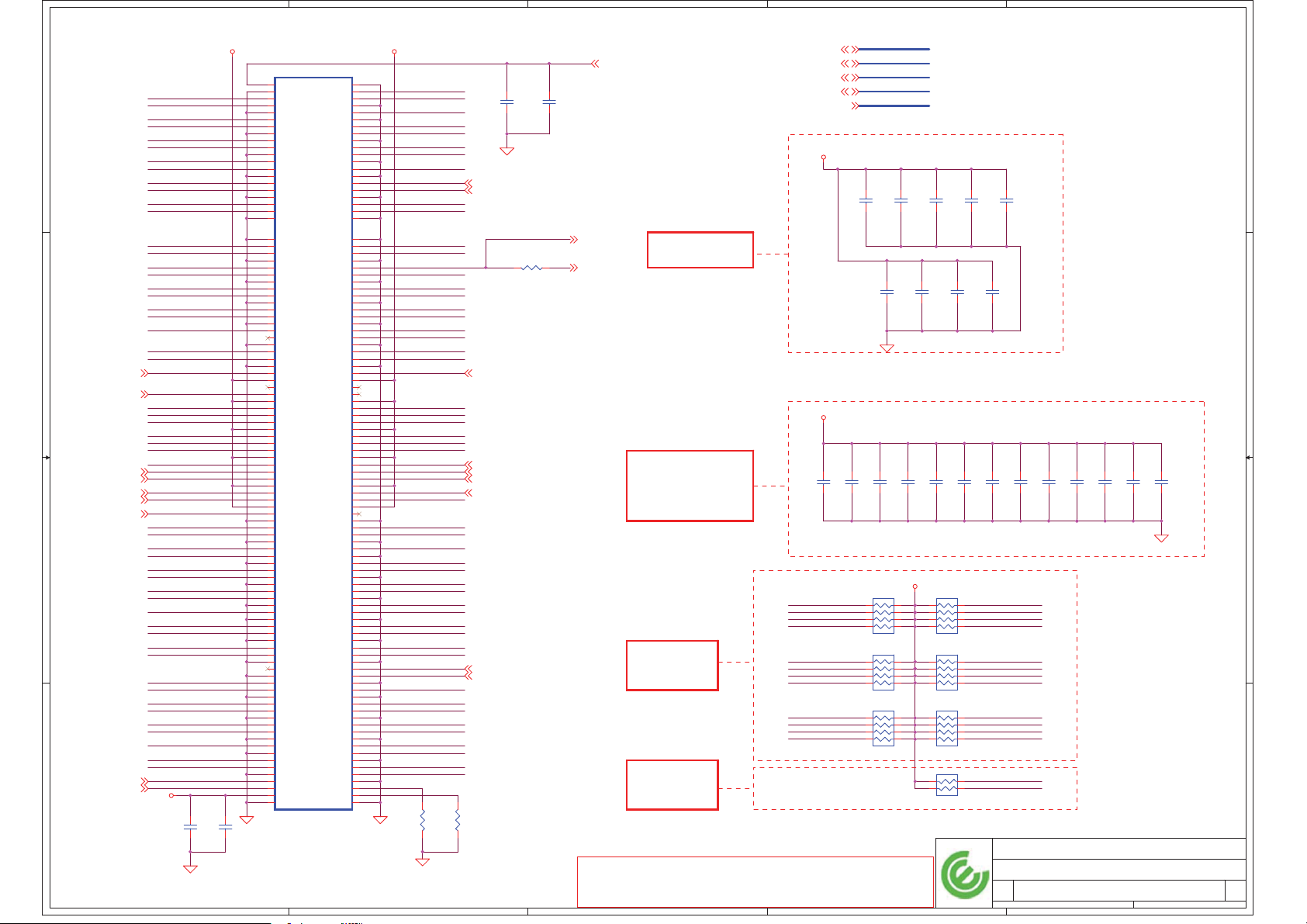

Page 3

5

4

3

2

1

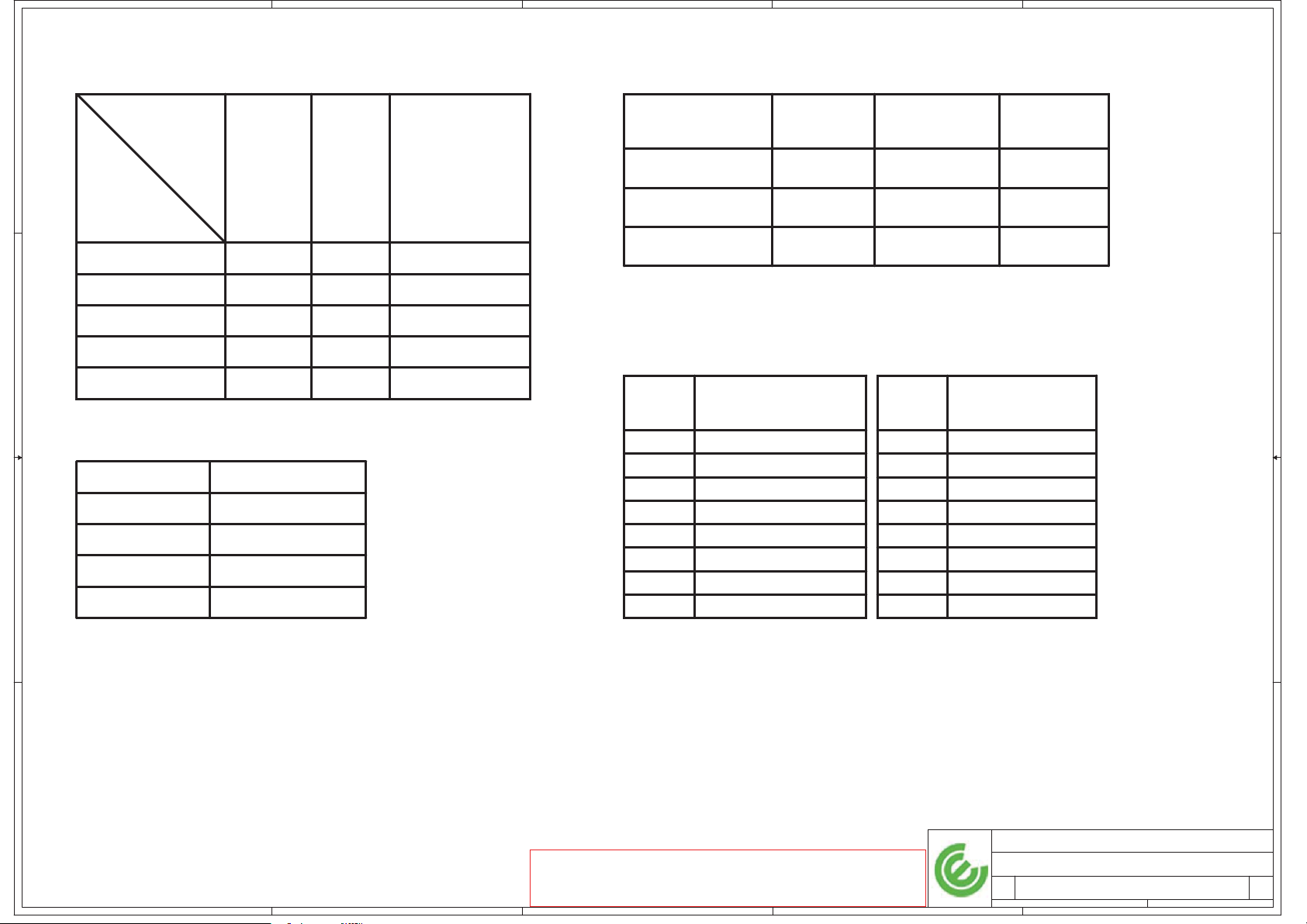

PM TABLE

D D

power

plane

State

S0

S1

S3

C C

S5 S4/AC

S5 S4/AC don't exist

PCI EXPRESS

Lane 1

Lane 2

B B

Lane 3

Lane 4

+3VALW

ON

ON

ON

ON

+3VSUS

+5VSUS+5VALW

+1.8VSUS

DESTINATION

MINI CARD TV

MINI CARD WLAN

GIGA LAN

EXPRESS CARD

ON ON

ON

ON

OFF

OFFOFF

+12VRUN

+5VRUN

+3VRUN

+2.5VRUN

+1.8VRUN

+1.5VRUN

+VCC_CORE

+VCCP

+0.9V_DDR_VTT

ON

OFF

OFF

OFF

PCI TABLE

PCI DEVICE

CARD BUS

ICH7M USB TABLE

USB

PORT#

0

1

2

3

4

5

6

7

DESTINATION

BLUETOOTH

USB[0] of ECE5011

Express Card

CIR

JUSB1(M/B)

JUSB2(M/B)

JUSB3(USB/BD)

JUSB4(USB/BD)

IDSEL

AD17

REQ#/GNT# PIRQ

2

D,C

ECE5011 USB TABLE

USB

PORT#

0

1

DESTINATION

USB[1] of ICH7M

Mini Card WLAN

2

WUSB3

4

Mini Card TV

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Elec tronics, Inc.

Index and Config.

Greenland-LA2732P

363Wednesday, December 28, 2005

1

X03

http://hobi-elektronika.net

5

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

4

3

2

Title

Size Document Number Rev

Date: Sheet of

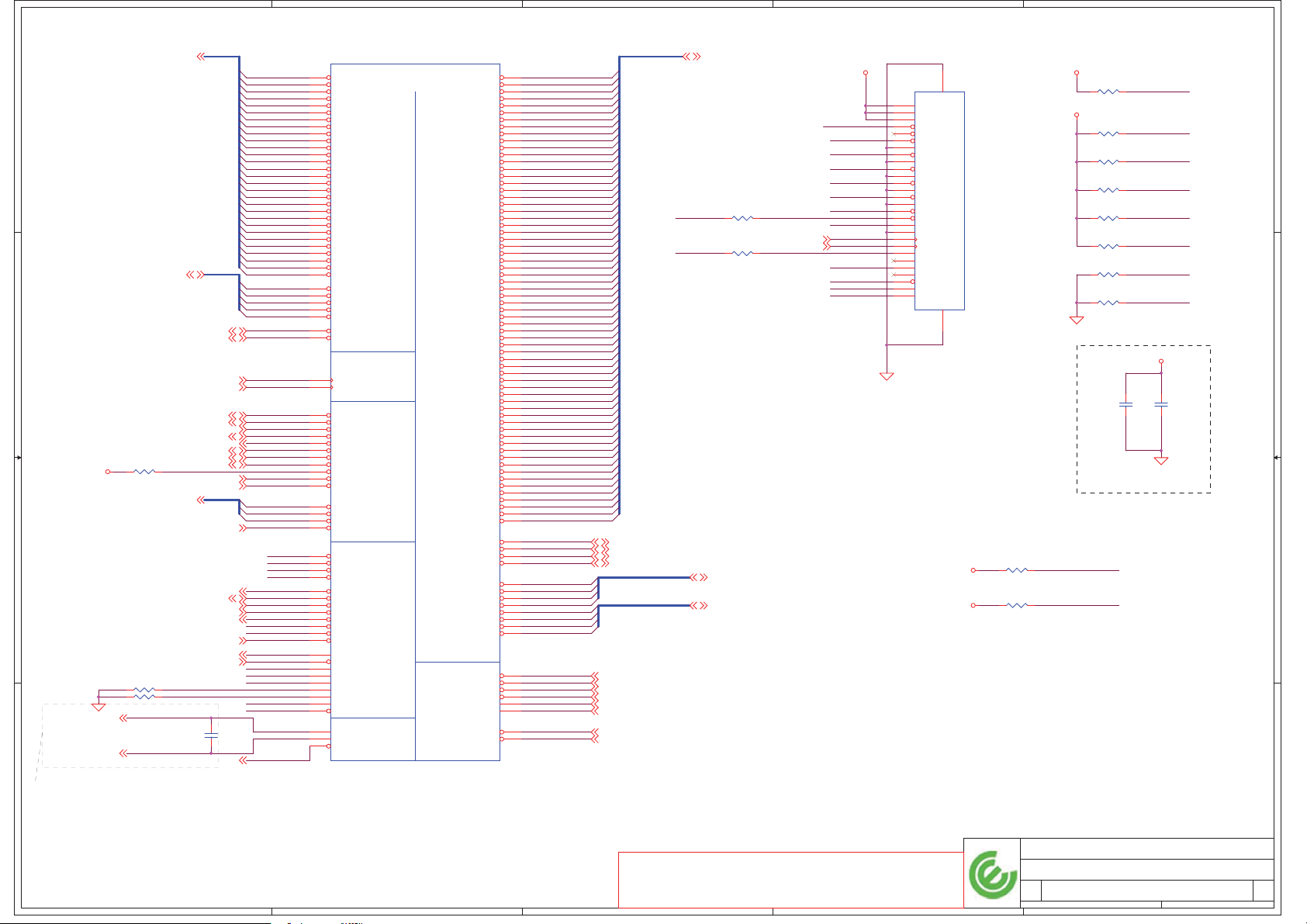

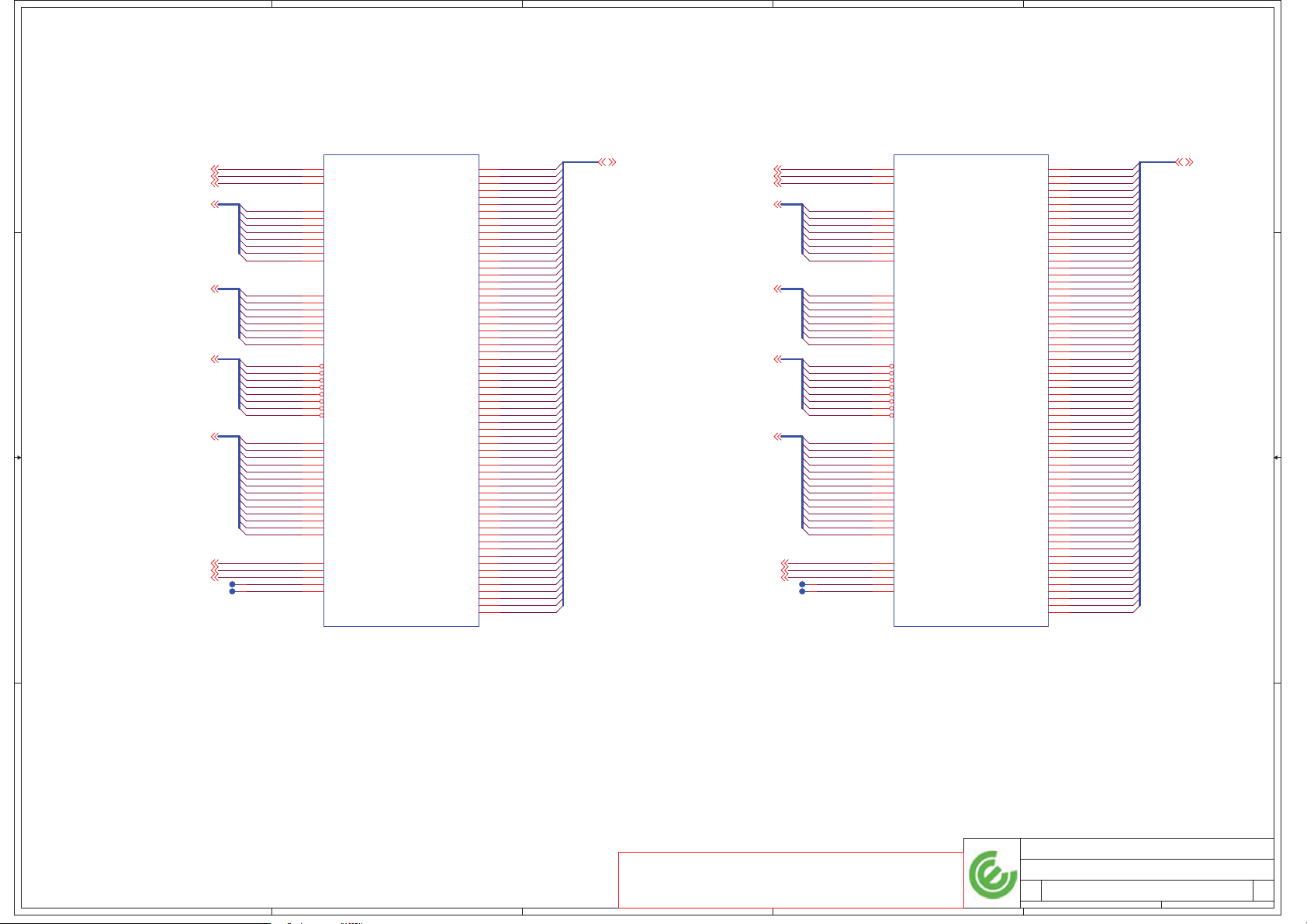

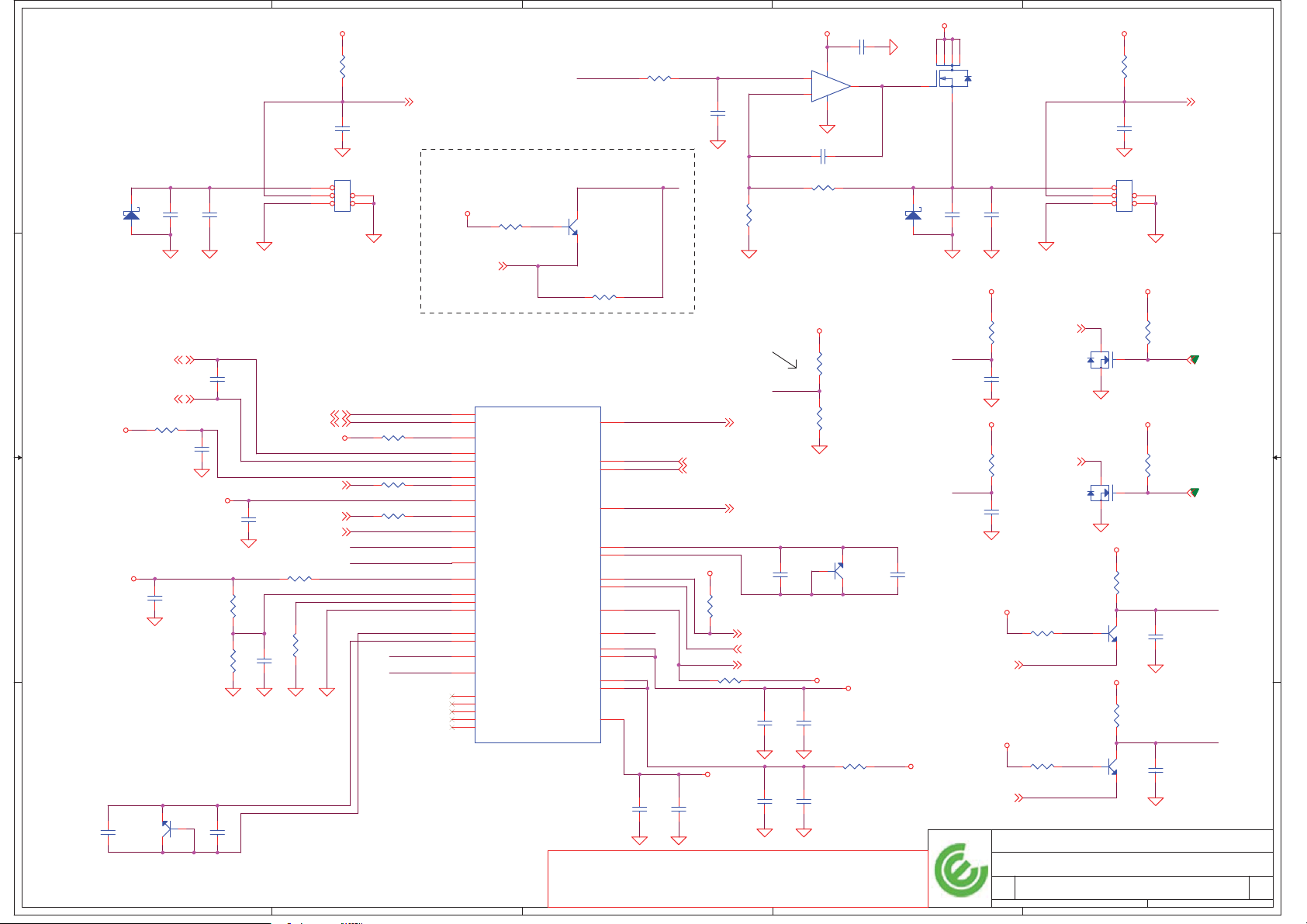

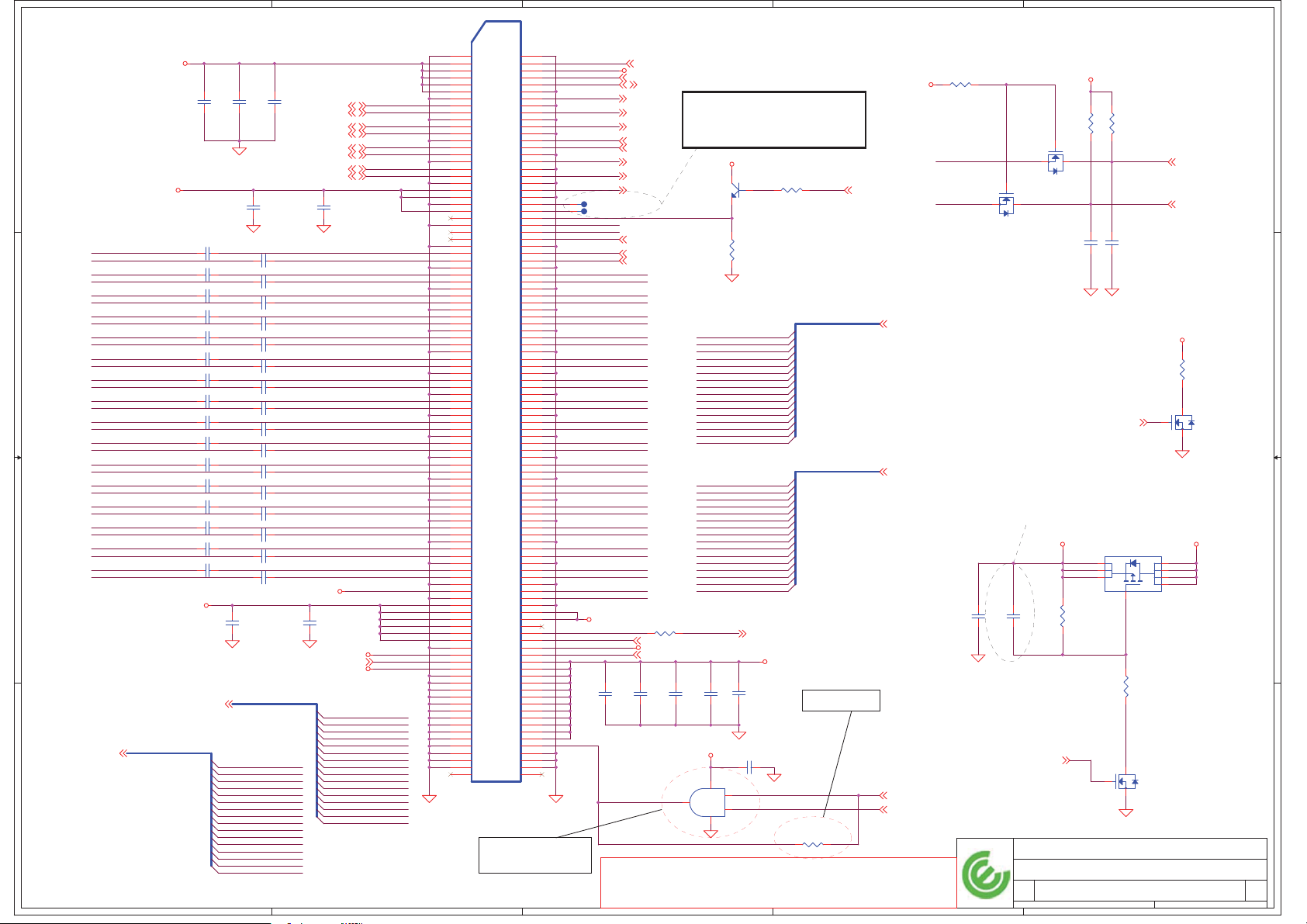

Page 4

5

4

3

2

1

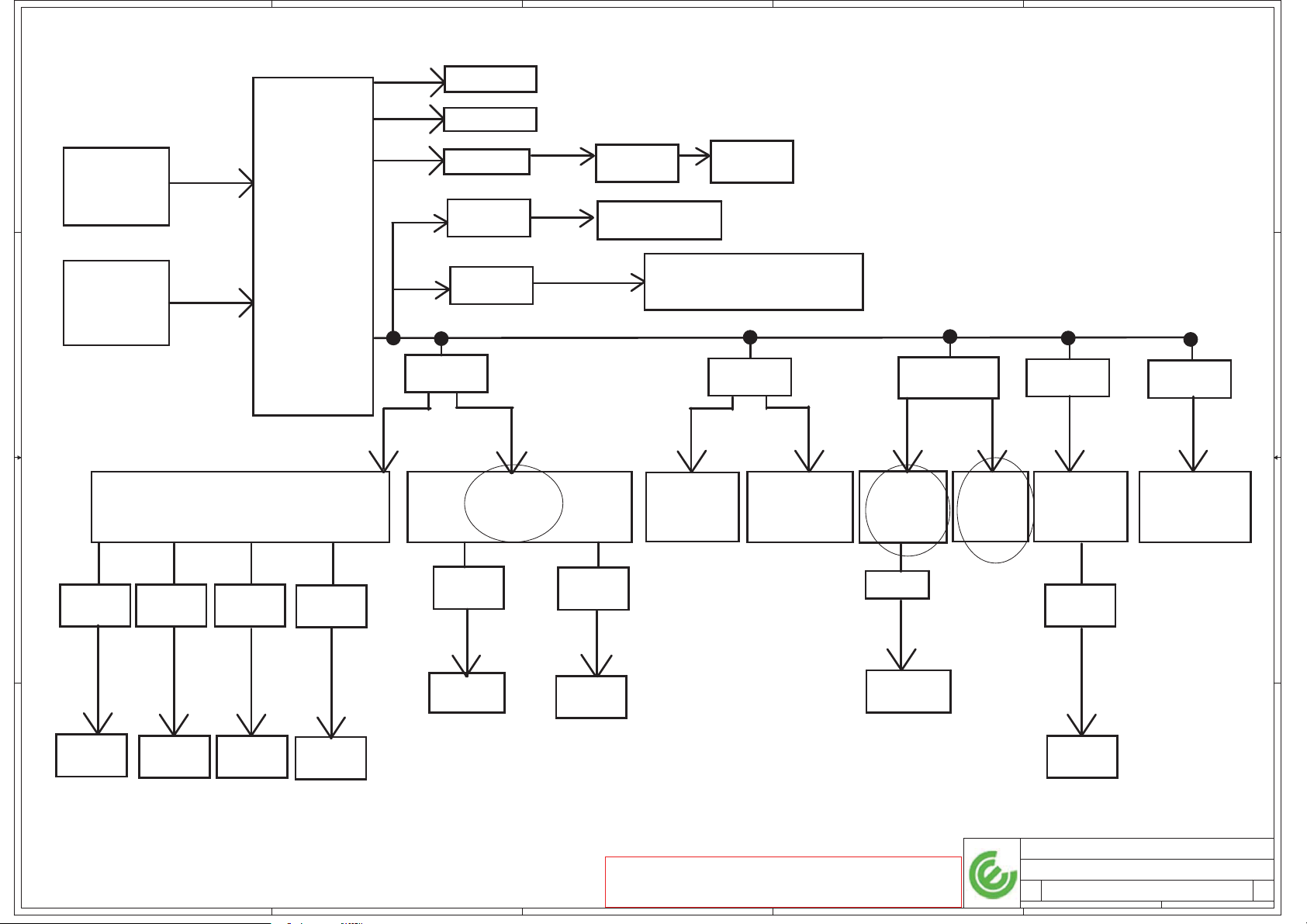

+5VALW

D D

ADAPTER

PWR_SRC

BATTERY

C C

MAX8734

SUS_ON

+5VSUS

Thermal: 6.3A

Peak: 8.4A

OCP: 10.5A

+3VALW

PL17, PL18

SI4825DT

L5973D

SUS_ON

+3VSRC

Thermal: 5A

Peak: 7.2A

OCP: 10.4A

SCL, SDA

RUN_ON

EN_KB_PRECHG_5V#

MAX8731

G_PWR_SRC

+VCHGR

+5V_Pre-charge

TPS51116 MAX8743 MAX1745

SUSPWROK_5V

+1.8VSUSP

Thermal: 8.2A

Peak: 9.7A

OCP: 12A

Thermal: 0.8A

Peak: 1A

OCP: 2.5~3A

RUN_ON

+0.9V_DDR_VTT

Thermal: 1.5A

Peak: 3A

OCP: 3.8A

RUN_ON

+1.5VRUNP

Thermal: 4.6A

Peak: 6.6A

OCP min: 6.7A

RUN_ON

+VCCP

Thermal: 4.5A

Peak: 6.4A

OCP min: 6.6A

+3.3VX

+12VALW_SLND

Thermal: 2.5A

Peak: 3.5A

OCP: 4.5A

ADP3207

RUNPWROK

+VCC_CORE

Thermal:

Peak: 44A

OCP: A

B B

SI3456DVSI4800DY

HDDC_EN#

+5VHDD

A A

MODC_EN#

+5VMOD

STS11NF30L

RUN_ON

+5VRUN

TPS793475

RUN_ON

+3VRUN

AUDIO_AVDD_ON

+VDDA

SI3456DV

STS11NF30L

SUS_ON

+3VSUS

PJP7

SI4435BDY

+1.5VRUN

RUNPWROK

+12RUN

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Power Rail

Greenland-LA2732P

463Wednesday, December 28, 2005

1

X03

of

http://hobi-elektronika.net

5

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

4

3

2

Title

Size Document Number Rev

Date: Sheet

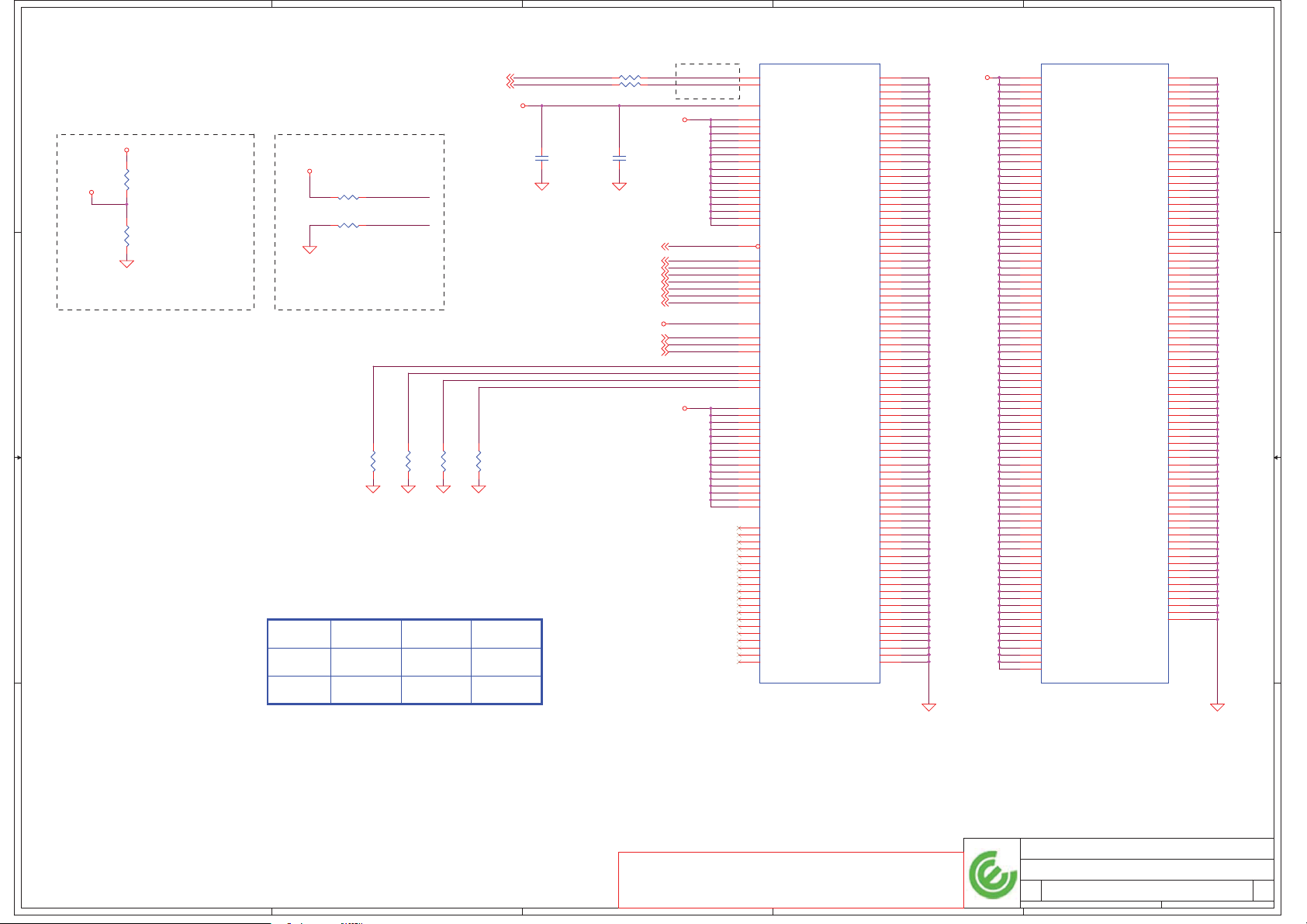

Page 5

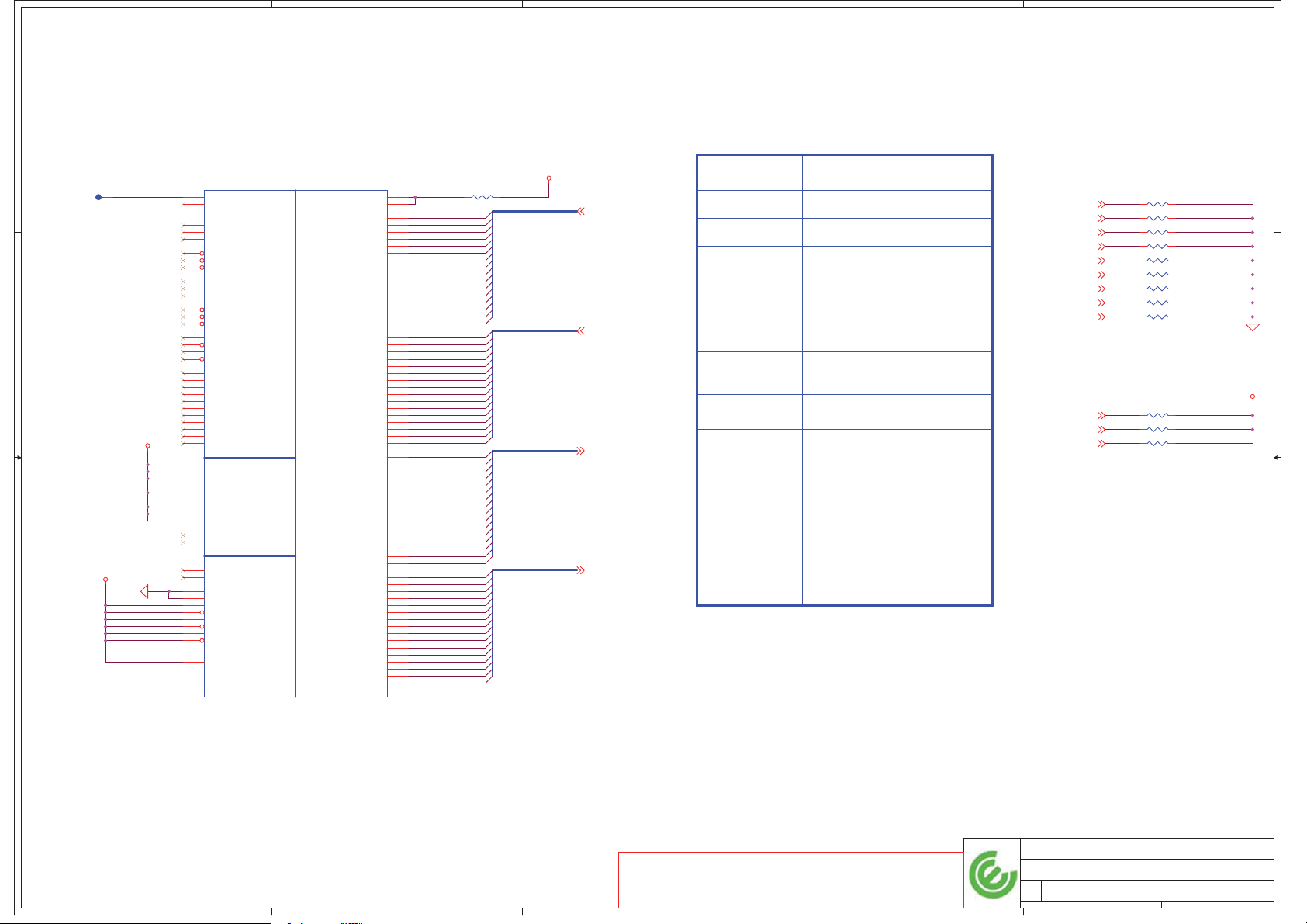

5

4

3

2

1

+3VSUS

2.2K 2.2K

ICH_SMBCLK

D D

ICH7M

C C

C22

ICH_SMBDATA

B22

+3VSUS

30 30

Mini Card

+3VALW

10K 10K

CLK_SMB

10

DAT_SMB +3VALW

9

TV

32

32 7 8

Mini Card

WLAN

Express

Card

7002

7002

8

7

GUARDIAN

+3VRUN

197 195 197 195

+3VRUN

2.2K 2.2K

CK_SCLK

CK_SDATA

16

CLK GEN.

17

DIMM1DIMM0

Device Address

+3VALW

DIM0 A0h

PBAT_SMBCLK

8

8.2K8.2K

100

3

ICH7M-SMBus

DIM1

CLK GEN.

A2h

D2h

PBAT_SMBDAT BATTERY+3VALW

7

SIO

B B

A A

http://hobi-elektronika.net

Macallan IV

5

SBAT_SMBCLK

112

SBAT_SMBDAT +3VALW VGA

111

DOCK_SMB_CLK

6

DOCK_SMB_DAT

5

+3VALW

8.2K8.2K

+5V_MEDIA

10K10K

4

Note. +5V_MEDIA is from

+5VRUN or +5VSUS

+5V_MEDIA

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

100

3

4

9

CHARGER

10

10

8

13

Media BTN BD

14

EC-SMBus

Mini WLAN

Express

GUARDIA N

Media BTN

VGA

Battery

Charger

h

h

5Eh

86h for Cypress

40h

98h

16h

12h

LED PWM C0h

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

2

Date: Sheet of

Compal Elec tronics, Inc.

SMBUS TOPOLOGY

Greenland-LA2732P

563Wednesday, December 28, 2005

1

X03

Page 6

5

D

1

2

G

3

2N7002

ICH_SMBDATA23,36,40

D D

ICH_SMBCLK23,36,40

C C

FSC FSB FSA CPU

CLKSEL0 CLKSEL1 CLKSEL2

ICH_SMBDATA CK_SDATA

+3VRUN

ICH_SMBCLK

1

1

C540

2

2

4.7U_0805_6.3V6K~D

00

0

0

0

1

1

1

0

1

11

0

0

1

*

11

B B

A A

Table : ICS 9 54305AK / Silego SLG84450VTR

+3VRUN

12

R796

10K_0402_5%~D

FSA

12

R799

10K_0402_5%~D

@

+3VRUN

12

R471

10K_0402_5%~D

PCICLK4

12

R472

10K_0402_5%~D

@

http://hobi-elektronika.net

+3VRUN

S

+CK_VDD_48+CK_VDD_A

C529

0.047U_0402_16V4Z~D

R226

2.2K_0402_5%~D

Q53

D

S

1 3

2N7002_SOT23~D

G

2

2

G

2N7002_SOT23~D

1 3

D

S

Q52

1

C537

2

4.7U_0805_6.3V6K~D

1

2

SRC

MHz

MHz

100 33.30

266

1

0

0

1

0

0

133

200

166

333

100

400

100

100

100

100

100

100

RESERVED

12

C199

0.047U_0402_16V4Z~D

12

R227

2.2K_0402_5%~D

CK_SCLK

+CK_VDD_REF

PCI

MHz

33.3

33.3

33.3

33.3

33.3

33.3

CK_SDATA 17,18

CK_SCLK 17,18

1

C201

2

0.047U_0402_16V4Z~D

CPU_MCH_BSEL08,10

CPU_MCH_BSEL18,10

CPU_MCH_BSEL28,10

CLK_PCI_PCCARD34

27P_0402_50V8J~D

1 2

27P_0402_50V8J~D

1 2

CK_48M_CB34

CLK_ICH_48M23

CLK_PCI_SIO37

CLK_ICH_14M23

CK_33M_ICHPCI21

Note: Solder Thermal pad to GND minimun 9 GND VIA.

PCICLK4 = FCTSEL1

FCTSEL1 Pin 43 Pin 44 Pin 47 Pin 48

UMA

0 DOT96T DOT96C LCD100/96T LCD100/96C

Discrete

1 27MHz 27MHz SRC0_T SRC0_C

5

C220

C215

4

L46

1 2

BLM21PG600SN1D_0805~D

1

C520

2

L25

1 2

BLM21PG600SN1D_0805~D

0.1U_0402_16V4Z~D

Place crystal within

500 mils of CK410

CK_XTAL_IN

12

X3

14.31818MHz_20P_1BX14318CC1A~D

CK_XTAL_OUT

CK_48M_CB

CLK_ICH_48M

CPU_MCH_BSEL0

CPU_MCH_BSEL1

CPU_MCH_BSEL2

CLK_PCI_PCCARD

CLK_PCI_SIO

CLK_ICH_14M CK_14M

+3VRUN

4

+CK_VDD_MAIN2

R209 390_0402_5%~D

R875 15_0402_5%~D

R205 15_0402_5%~D

R795 8.2K_0402_5%~D

R534 8.2K_0402_5%~D

R221 33_0402_5%~D

R229 33_0402_5%~D

R223 33_0402_5%~D

R473 10K_0402_5%~D

R216 33_0402_5%~D

CLK_ENABLE#51

+CK_VDD_MAIN+3VRUN

1 2

R460 1_0603_5%~D

1 2

R459 2.2_0603_5%~D

1 2

12

12

12

12

12

12

12

12

12

1 2

R450 475_0402_1%~D

CK_XTAL_OUT_R

CLK_ENABLE#

CK_SCLK

CK_SDATA

3

2

C523

10U_0805_10V4Z~D

1

2

C551

10U_0805_10V4Z~D

1

U16

1

VDDSRC

49

VDDSRC

54

VDDSRC

65

VDDSRC

30

VDDPCI

36

VDDPCI

12

+CK_VDD_REF

+CK_VDD_48

FSA

FSC

PCICLK4

PCICLK3

PCICLKF0CK_33M_ICHPCI

CLKIREF

VDDCPU

18

VDDREF

40

VDD48

20

X1

19

X2

41

USB_48MHz/FSLA

45

FSLB/TEST_MODE

23

REF0/FSLC/TEST_SEL

34

PCICLK4/FCTSEL1

33

PCICLK3

32

PCICLK2

27

PCICLK1

22

REF1

43

DOTT_96MHz/27MHz

44

DOTC_96MHz/27MHz(SS)

37

ITP_EN/PCICLK_F0

39

Vtt_PwrGd#/PD

9

IREF

16

SMBCLK

17

SMBDAT

4

GNDSRC

15

GNDCPU

21

GNDREF

31

GNDPCI

35

GNDPCI

42

GND48

68

GNDSRC

73

THRM_PAD

74

THRM_PAD

75

THRM_PAD

76

THRM_PAD

SLG84450VTR_QFN72~D

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

1

C197

0.1U_0402_16V4Z~D

2

1

C217

0.1U_0402_16V4Z~D

2

R452

2.2_0603_5%~D

1 2

1

2

1

2

+CK_VDD_A

VDDA

GNDA

PCI_SRC_STOP#

CPU_STOP#

CPUT1

CPUC1

CPUT0

CPUC0

CPUT_ITP/SRCT10

CPUC_ITP/SRCC10

SRCT9

SRCC9

CLKREQ9#

SRCT8

SRCC8

CLKREQ8#

SRCT7

SRCC7

CLKREQ7#

SRCT6

SRCC6

CLKREQ6#

SRCT5

SRCC5

CLKREQ5#

SRCT4

SRCC4

CLKREQ4#

SRCT3

SRCC3

CLKREQ3#

SRCT2

SRCC2

CLKREQ2#

SRCT1

SRCC1

CLKREQ1#

LCD100/96/SRC0_T

LCD100/96/SRC0_C

C182

0.1U_0402_16V4Z~D

C204

0.1U_0402_16V4Z~D

7

8

H_STP_PCI#

25

H_STP_CPU#

24

CK_CPU1

11

CK_CPU1#

10

CK_CPU0

14

CK_CPU0#

13

CK_CPU_ITP

6

CK_CPU_ITP#

5

SRC9

3

SRC9#

2

72

SRC8

70

SRC8#

69

71

SRC7 CLK_PCIE_LOM

66

SRC7#

67

LOM_CLKREQ#

38

SRC6 CLK_PCIE_EXPR

63

64

EXPR_CARD_REQ#

62

SRC5

60

SRC5#

61

SATA_CLKREQ#

29

SRC4

58

SRC4# CLK_PCIE_ICH#

59

57

SRC3

55

56

MINI_CARD1_REQ#

28

SRC2

52

53

MINI_CARD2_REQ#

26

50

51

46

47

48

2

1

C187

0.1U_0402_16V4Z~D

2

1

2

Place near each pin

W>40 mil

Place near CK410M

H_STP_PCI# 23

H_STP_CPU# 23

1 2

R192 33_0402_5%~D

1 2

R188 33_0402_5%~D

1 2

R208 33_0402_5%~D

1 2

R204 33_0402_5%~D

1 2

R179 33_0402_5%~D

1 2

R174 33_0402_5%~D

1 2

R182 33_0402_5%~D

1 2

R176 33_0402_5%~D

1 2

R154 33_0402_5%~D

1 2

R149 33_0402_5%~D

1 2

R147 33_0402_5%~D

1 2

R140 33_0402_5%~D

1 2

R152 33_0402_5%~D

1 2

R146 33_0402_5%~D

1 2

R171 33_0402_5%~D

1 2

R165 33_0402_5%~D

1 2

R198 33_0402_5%~D

1 2

R189 33_0402_5%~D

1 2

R168 33_0402_5%~D

1 2

R159 33_0402_5%~D

1 2

R801 33_0402_5%~D

1 2

R802 33_0402_5%~D

CLK_MCH_BCLK

CLK_MCH_BCLK#

CLK_CPU_BCLK

CLK_CPU_BCLK#

CK_ITP

CK_ITP#

CLK_PCIE_VGA

CLK_PCIE_VGA#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

3GPLL_REQ#

CLK_PCIE_LOM#

LOM_CLKREQ#

CLK_PCIE_EXPR#SRC6#

EXPR_CARD_REQ# 40

CLK_PCIE_SATA

CLK_PCIE_SATA#

SATA_CLKREQ# 23

CLK_PCIE_ICH

CLK_PCIE_M INI_CARD1

CLK_PCIE_MI NI_CARD1#SRC3#

MINI_CARD1_REQ# 36

CLK_PCIE_M INI_CARD2

CLK_PCIE_MI NI_CARD2#SRC2#

MINI_CARD2_REQ# 36

2

1

CLK_MCH_BCLK

CLK_MCH_BCLK#

CLK_CPU_BCLK

CLK_CPU_BCLK#

CK_ITP

CK_ITP#

CLK_PCIE_SATA

CLK_PCIE_SATA#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CLK_PCIE_VGA

CLK_PCIE_VGA#

CLK_PCIE_LOM

CLK_PCIE_LOM#

CLK_PCIE_EXPR

CLK_PCIE_EXPR#

CLK_PCIE_M INI_CARD2

CLK_PCIE_MI NI_CARD2#

CLK_PCIE_M INI_CARD1

CLK_PCIE_MI NI_CARD1#

3GPLL_REQ#

EXPR_CARD_REQ#

SATA_CLKREQ#

MINI_CARD1_REQ#

MINI_CARD2_REQ#

LOM_CLKREQ#

1 2

10K_0402_5%~D

1 2

10K_0402_5%~D

1 2

10K_0402_5%~D

1 2

10K_0402_5%~D

1 2

10K_0402_5%~D

1 2

10K_0402_5%~D

C522

0.1U_0402_16V4Z~D

CLK_MCH_BCLK 10

CLK_MCH_BCLK# 10

CLK_CPU_BCLK 7

CLK_CPU_BCLK# 7

CK_ITP 7

CK_ITP# 7

1

C954

0.1U_0402_16V4Z~D

2

CLK_PCIE_VGA 19

CLK_PCIE_VGA# 19

CLK_MCH_3GPLL 10

CLK_MCH_3GPLL# 10

3GPLL_REQ# 10

CLK_PCIE_LOM 32

CLK_PCIE_LOM# 32

CLK_PCIE_EXPR 40

CLK_PCIE_EXPR# 40

CLK_PCIE_SATA 22

CLK_PCIE_SATA# 22

CLK_PCIE_ICH 23

CLK_PCIE_ICH# 23

CLK_PCIE_MI N I_CARD1 36

CLK_PCIE_MI N I_CARD1# 36

CLK_PCIE_MI N I_CARD2 36

CLK_PCIE_MI N I_CARD2# 36

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

Custom

Date: Sheet

Compal Electronics, Inc.

Clock Generator

Greenland-LA2732P

1

49.9_0402_1%~D

49.9_0402_1%~D

49.9_0402_1%~D

49.9_0402_1%~D

49.9_0402_1%~D

49.9_0402_1%~D

1 2

49.9_0402_1%~D

1 2

49.9_0402_1%~D

1 2

49.9_0402_1%~D

1 2

49.9_0402_1%~D

1 2

49.9_0402_1%~D

1 2

49.9_0402_1%~D

1 2

49.9_0402_1%~D

1 2

49.9_0402_1%~D

1 2

49.9_0402_1%~D

1 2

49.9_0402_1%~D

1 2

49.9_0402_1%~D

1 2

49.9_0402_1%~D

1 2

49.9_0402_1%~D

1 2

49.9_0402_1%~D

1 2

49.9_0402_1%~D

1 2

49.9_0402_1%~D

R728

R539

R829

R538

R800

R890

663Wednesday, December 28, 2005

R191

R187

R207

R203

R178

R173

R148

R141

R822

R823

R167

R158

12

12

12

12

12

12

R172

R166

R199

R190

R155

R150

R183

R177

R151

R145

+3VRUN

+3VRUN

+3VRUN

+3VRUN

+3VRUN

+3VRUN

X03

of

Page 7

5

4

3

2

1

H_A#[3..31]10

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

D D

H_REQ#[0..4]10

H_ADSTB#010

C C

R584

56_0402_5%~D

1 2

+VCCP

B B

Stuff R840 for

Yonah B0 and

forward, no stuff

for A1

R901 1K_0402_5%~D @

1 2

R840 51_0402_5%~D

1 2

H_THERMDA16

H_THERMDC16

H_THERMDA, H_THERMDC routing together.

Trace width / Spacing = 10 / 10 mil

A A

H_ADSTB#110

CLK_CPU_BCLK6

CLK_CPU_BCLK#6

H_ADS#10

H_BNR#10

H_BPRI#10

H_BR0#10

H_DEFER#10

H_DRDY#10

H_HIT#10

H_HITM#10

H_LOCK#10

H_RS#[0..2]10

2200P_0402_50V7K~D@

H_RESET#10

H_TRDY#10

ITP_DBRESET#23,37

H_DBSY#10

H_DPSLP#22

H_DPRSTP#22,51

H_DPWR#10

CPU_PROCHOT#38

H_PWRGOOD22

H_CPUSLP#10,22

1

C746

2

H_THERMTRIP#16

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CLK_CPU_BCLK

CLK_CPU_BCLK#

H_ADS#

H_BNR#

H_BPRI#

H_BR0#

H_DEFER#

H_DRDY#

H_HIT#

H_HITM#

H_IERR#

H_LOCK#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_DBRESET#

H_DBSY#

H_DPSLP#

H_DPRSTP#

H_DPWR#

ITP_BPM#4

ITP_BPM#5

CPU_PROCHOT#

H_PWRGOOD

H_CPUSLP#

ITP_TCK

ITP_TDI

ITP_TDO

TEST1

TEST2

ITP_TMS

ITP_TRST#

H_THERMDA

H_THERMDC

H_THERMTRIP#

JCPU1A

J4

A3#

L4

A4#

M3

A5#

K5

A6#

M1

A7#

N2

A8#

J1

A9#

N3

A10#

P5

A11#

P2

A12#

L1

A13#

P4

A14#

P1

A15#

R1

A16#

Y2

A17#

U5

A18#

R3

A19#

W6

A20#

U4

A21#

Y5

A22#

U2

A23#

R4

A24#

T5

A25#

T3

A26#

W3

A27#

W5

A28#

Y4

A29#

W2

A30#

Y1

A31#

K3

REQ0#

H2

REQ1#

K2

REQ2#

J3

REQ3#

L5

REQ4#

L2

ADSTB0#

V4

ADSTB1#

A22

BCLK0

A21

BCLK1

H1

ADS#

E2

BNR#

G5

BPRI#

F1

BR0#

H5

DEFER#

F21

DRDY#

G6

HIT#

E4

HITM#

D20

IERR#

H4

LOCK#

B1

RESET#

F3

RS0#

F4

RS1#

G3

RS2#

G2

TRDY#

AD4

BPM0#

AD3

BPM1#

AD1

BPM2#

AC4

BPM3#

C20

DBR#

E1

DBSY#

B5

DPSLP#

E5

DPRSTP#

D24

DPWR#

AC2

PRDY#

AC1

PREQ#

D21

PROCHOT#

D6

PWRGOOD

D7

SLP#

AC5

TCK

AA6

TDI

AB3

TDO

C26

TEST1

D25

TEST2

AB5

TMS

AB6

TRST#

A24

THERMDA

A25

THERMDC

C7

THERMTRIP#

FOX_PZ47903-2741-42_YONAH~D

YONAH

ADDR GROUP

HOST CLK

CONTROL

MISC

THERMAL

DIODE

DATA GROUP

LEGACY CPU

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

A20M#

FERR#

IGNNE#

INIT#

LINT0

LINT1

STPCLK#

SMI#

E22

F24

E26

H22

F23

G25

E25

E23

K24

G24

J24

J23

H26

F26

K22

H25

N22

K25

P26

R23

L25

L22

L23

M23

P25

P22

P23

T24

R24

L26

T25

N24

AA23

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

J26

M26

V23

AC20

H23

M24

W24

AD23

G22

N25

Y25

AE24

A6

A5

C4

B3

C6

B4

D5

A3

H_D#0H_A#3

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20H_A#23

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_A20M#

H_FERR#

H_IGNNE#

H_INIT#

H_INTR

H_NMI

H_STPCLK#

H_SMI#

H_DINV#0 10

H_DINV#1 10

H_DINV#2 10

H_DINV#3 10

H_A20M# 22

H_FERR# 22

H_IGNNE# 22

H_INIT# 22

H_INTR 22

H_NMI 22

H_STPCLK# 22

H_SMI# 22

H_RESET#

ITP_TDO

H_D#[0..63] 10

R578

22.6_0402_1%~D

1 2

R579

22.6_0402_1%~D

1 2

H_DSTBN#[0..3] 10

H_DSTBP#[0..3] 10

+VCCP

ITP_DBRESET#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TCK

CK_ITP

CK_ITP6

CK_ITP#

CK_ITP#6

ITP_TDO_R

ITP_TCK

ITP_TRST#

ITP_TMS

ITP_TDI

Check ITP connector.

+3VSUS

R575

+VCCP

150_0402_1%~D

1 2

R576

51_0402_5%~D

1 2

R577

51_0402_5%~D

1 2

R839

@

54.9_0402_1%~D

1 2

R581

39_0402_5%~D

1 2

R580

150_0402_5%~D

1 2

R583

680_0402_5%~D

1 2

R582

27_0402_5%~D

1 2

C956

0.1U_0402_16V4Z~D

ITP_DBRESET#

ITP_TDO_R

H_RESET#

ITP_BPM#5

ITP_TMS

ITP_TDI

This shall place near CPU

ITP_TRST#

This shall place near CPU

ITP_TCK

+VCCP

1

1

C686

2

2

0.1U_0402_16V4Z~D

29

JITP1

29

28

VTT1

27

VTT0

26

VTAP

25

DBR#

24

DBA#

23

BPM0#

22

GND5

21

BPM1#

20

GND4

19

BPM2#

18

GND3

17

BPM3#

16

GND2

15

BPM4#

14

GND1

13

BPM5#

12

RESET#

11

FBO

10

GND0

9

BCLKP

8

BCLKN

7

TDO

6

NC2

5

TCK

4

NC1

3

TRST#

2

TMS

1

TDI

30

MOLEX_52435-2891_28P~D@

30

Place near JITP1

R585

+VCCP

+VCCP

56_0402_5%~D

1 2

R781

75_0402_5%~D

1 2

H_THERMTRIP#

CPU_PROCHOT#

C746 close to CPU

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Yonah in mFCPGA479

Greenland-LA2732P

763Wednesday, December 28, 2005

1

X03

of

http://hobi-elektronika.net

5

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

4

3

2

Title

Size Document Number Rev

Date: Sheet

Page 8

5

4

3

2

1

Length match within 25 mils

R586

VCCSENSE51

VSSSENSE51

D D

+VCCP

R_A

12

V_CPU_GTLREF

R589

1K_0402_1%~D

R_B

12

R588

2K_0402_1%~D

Layout close CPU PIN AD26

+VCC_CORE

R590

100_0402_1%~D

1 2

R591

100_0402_1%~D

1 2

Layout close CPU

VCCSENSE

VSSSENSE

VCCSENSE

VSSSENSE VSSSENSE_R

+1.5VRUN

1

C688

2

10U_0805_10V4Z~D

C687

Layout close CPU PIN B26

0.5 inch (max)

C C

Resistor placed within

0.5" of CPU pin.Trace

should be at least 25

12

12

R592

R593

27.4_0402_1%~D

B B

CPU_BSEL CPU_BSEL2 CPU_BSEL1

133

166

00

0

12

12

R594

27.4_0402_1%~D

54.9_0402_1%~D

mils away from any

other toggling signal.

R595

54.9_0402_1%~D

CPU_BSEL0

1

1

1

0_0402_5%~D

1 2

1 2

R587

0_0402_5%~D

1

C687

2

0.01U_0402_16V7K~D

H_PSI#51

VID051

VID151

VID251

VID351

VID451

VID551

VID651

V_CPU_GTLREF

CPU_MCH_BSEL06,10

CPU_MCH_BSEL16,10

CPU_MCH_BSEL26,10

+VCCP

+VCC_CORE

VCCSENSE_R

H_PSI#

VID0

VID1

VID2

VID3

VID4

VID5

VID6

CPU_MCH_BSEL0

CPU_MCH_BSEL1

CPU_MCH_BSEL2

COMP0

COMP1

COMP2

COMP3

JCPU1B

AF7

VCCSENSE

AE7

VSSSENSE

B26

VCCA

K6

VCCP

J6

VCCP

M6

VCCP

N6

VCCP

YONAH

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

PSI#

VID0

VID1

VID2

VID3

VID4

VID5

VID6

GTLREF

BSEL0

BSEL1

BSEL2

COMP0

COMP1

COMP2

COMP3

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

FOX_PZ47903-2741-42_YONAH~D

M21

W21

AD6

AD26

AB20

AA20

AF20

AE20

AB18

AB17

AA18

AA17

AD18

AD17

AC18

AC17

AF18

AF17

T6

R6

K21

J21

N21

T21

R21

V21

V6

G21

AE6

AF5

AE5

AF4

AE3

AF2

AE2

B22

B23

C21

R26

U26

U1

V1

E7

D2

F6

D3

C1

AF1

D22

C23

C24

AA1

AA4

AB2

AA3

M4

N5

T2

V3

B2

C3

T22

B25

AB26

VSS

AA25

VSS

AD25

VSS

AE26

VSS

AB23

VSS

AC24

VSS

AF24

VSS

AE23

VSS

AA22

VSS

AD22

VSS

AC21

VSS

AF21

VSS

AB19

VSS

AA19

VSS

AD19

VSS

AC19

VSS

AF19

VSS

AE19

VSS

AB16

VSS

AA16

VSS

AD16

VSS

AC16

VSS

AF16

VSS

AE16

VSS

AB13

VSS

AA14

VSS

AD13

VSS

AC14

VSS

AF13

VSS

AE14

VSS

AB11

VSS

AA11

VSS

AD11

VSS

AC11

VSS

AF11

VSS

AE11

VSS

AB8

VSS

AA8

VSS

AD8

VSS

AC8

VSS

AF8

VSS

AE8

VSS

AA5

VSS

AD5

VSS

AC6

VSS

AF6

VSS

AB4

VSS

AC3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF3

AE4

AB1

AA2

AD2

AE1

B6

C5

F5

E6

H6

J5

M5

L6

P6

R5

V5

U6

Y6

A4

D4

E3

H3

G4

K4

L3

P3

N4

T4

U3

Y3

W4

D1

C2

F2

G1

POWER, GROUNG, RESERVED SIGNALS AND NC

+VCC_CORE

JCPU1C

AE18

VCC

AE17

VCC

AB15

VCC

AA15

VCC

AD15

VCC

AC15

VCC

AF15

VCC

AE15

VCC

AB14

VCC

AA13

VCC

AD14

VCC

AC13

VCC

AF14

VCC

AE13

VCC

AB12

VCC

AA12

VCC

AD12

AC12

AF12

AE12

AB10

AA10

AD10

AC10

AF10

AE10

AB9

AA9

AD9

AC9

AF9

AE9

AB7

AA7

AD7

AC7

B20

A20

F20

E20

B18

B17

A18

A17

D18

D17

C18

C17

F18

F17

E18

E17

B15

A15

D15

C15

F15

E15

B14

A13

D14

C13

F14

E13

B12

A12

D12

C12

F12

E12

B10

B9

A10

A9

D10

D9

C10

C9

F10

F9

E10

E9

B7

A7

F7

YONAH

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

POWER, GROUND

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

FOX_PZ47903-2741-42_YONAH~D

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K1

J2

M2

N1

T1

R2

V2

W1

A26

D26

C25

F25

B24

A23

D23

E24

B21

C22

F22

E21

B19

A19

D19

C19

F19

E19

B16

A16

D16

C16

F16

E16

B13

A14

D13

C14

F13

E14

B11

A11

D11

C11

F11

E11

B8

A8

D8

C8

F8

E8

G26

K26

J25

M25

N26

T26

R25

V25

W26

H24

G23

K23

L24

P24

N23

T23

U24

Y24

W23

H21

J22

M22

L21

P21

R22

V22

U21

Y21

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Yonah in mFCPGA479

Greenland-LA2732P

863Wednesday, December 28, 2005

1

X03

of

http://hobi-elektronika.net

5

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

4

3

2

Title

Size Document Number Rev

Date: Sheet

Page 9

5

+VCC_CORE

Place these inside

socket cavity on L8

(North side

D D

C C

Secondary)

Place these inside

socket cavity on L8

(Sorth side

Secondary)

Place these inside

socket cavity on L8

(North side

Primary)

Place these inside

socket cavity on L8

(Sorth side

Primary)

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

C689

10U_0805_4VAM~D

C699

10U_0805_4VAM~D

C709

10U_0805_4VAM~D

C715

10U_0805_4VAM~D

1

C690

10U_0805_4VAM~D

2

1

C700

10U_0805_4VAM~D

2

1

C710

10U_0805_4VAM~D

2

1

C716

10U_0805_4VAM~D

2

1

C691

10U_0805_4VAM~D

2

1

C701

10U_0805_4VAM~D

2

1

C711

10U_0805_4VAM~D

2

1

C717

10U_0805_4VAM~D

2

4

1

C692

10U_0805_4VAM~D

2

1

C702

10U_0805_4VAM~D

2

1

C712

10U_0805_4VAM~D

2

1

C718

10U_0805_4VAM~D

2

1

C693

10U_0805_4VAM~D

2

1

C703

10U_0805_4VAM~D

2

1

C713

10U_0805_4VAM~D

2

1

C719

10U_0805_4VAM~D

2

1

C694

10U_0805_4VAM~D

2

1

C704

10U_0805_4VAM~D

2

1

C714

10U_0805_4VAM~D

2

1

C720

10U_0805_4VAM~D

2

1

C695

10U_0805_4VAM~D

2

1

C705

10U_0805_4VAM~D

2

10uF 0805 X6S

3

1

C696

10U_0805_4VAM~D

2

1

C706

10U_0805_4VAM~D

2

1

C697

10U_0805_4VAM~D

2

1

C707

10U_0805_4VAM~D

2

1

C698

10U_0805_4VAM~D

2

1

C708

10U_0805_4VAM~D

2

2

1

High Frequence Decoupling

Near VCORE regulator.

+VCC_CORE

South Side Secondary

C721

@

B B

+VCCP

1

+

C727

@

2

330U_D2E_2.5VM~D

CRB was 270uF

A A

330U_D_2VM_R6~D

6mOhm

PS CAP

1

+

C722

2

330U_D_2VM_R6~D

6mOhm

PS CAP

1

C728

0.1U_0402_10V7K~D

2

1

+

C723

2

330U_D_2VM_R6~D

6mOhm

PS CAP

1

2

1

1

+

C724

2

2

330U_D_2VM_R6~D

6mOhm

PS CAP

C729

0.1U_0402_10V7K~D

+

1

+

C725

2

@

330U_D_2VM_R6~D

6mOhm

PS CAP

1

C730

0.1U_0402_10V7K~D

2

North Side Secondary

1

+

C726

2

330U_D_2VM_R6~D

6mOhm

PS CAP

1

2

C731

0.1U_0402_10V7K~D

1

C732

0.1U_0402_10V7K~D

2

ESR <= 1.5m ohm

1

C733

0.1U_0402_10V7K~D

2

Place these inside

socket cavity on L8

(North side

Secondary)

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

CPU Bypass

Greenland-LA2732P

963Wednesday, December 28, 2005

1

X03

of

http://hobi-elektronika.net

5

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

4

3

2

Title

Size Document Number Rev

Date: Sheet

Page 10

5

4

3

2

1

+VCCP

12

R596

H_SWNG1

221_0402_1%~D

+VCCP

+VCCP

R605

12

1

R597

2

C734

100_0402_1%~D

0.1U_0402_16V4Z~D

12

R598

H_SWNG0

221_0402_1%~D

12

1

R599

2

100_0402_1%~D

12

100_0402_1%~D

12

200_0402_1%~D

C735

0.1U_0402_16V4Z~D

R600

H_VREF

1

C736

2

DPRSLPVR23,51

PLTRST2#21,32,37

+1.8VSUS

0.1U_0402_16V4Z~D

R841

0_0402_5%~D

R606

100_0402_1%~D

V_DDR_MCH_REF17,18,50

DMI_MRX_ITX_N023

DMI_MRX_ITX_N123

DMI_MRX_ITX_N223

DMI_MRX_ITX_N323

DMI_MRX_ITX_P023

DMI_MRX_ITX_P123

DMI_MRX_ITX_P223

DMI_MRX_ITX_P323

DMI_MTX_IRX_N023

DMI_MTX_IRX_N123

DMI_MTX_IRX_N223

DMI_MTX_IRX_N323

DMI_MTX_IRX_P023

DMI_MTX_IRX_P123

DMI_MTX_IRX_P223

DMI_MTX_IRX_P323

M_CLK_DDR018

M_CLK_DDR118

M_CLK_DDR217

M_CLK_DDR317

M_CLK_DDR#018

M_CLK_DDR#118

M_CLK_DDR#217

M_CLK_DDR#317

DDR_CKE0_DIMMA18

DDR_CKE1_DIMMA18

DDR_CKE2_DIMMB17

DDR_CKE3_DIMMB17

DDR_CS0_DIMMA#18

DDR_CS1_DIMMA#18

DDR_CS2_DIMMB#17

DDR_CS3_DIMMB#17

T33 PAD~D

T36 PAD~D

R602 80.6_0402_1%~D

1 2

R601 80.6_0402_1%~D

1 2

PM_BMBUSY#23

12

12

V_DDR_MCH_REF

PM_EXTTS#018

THERMTRIP_MCH#16

ICH_PWRGD23,43

MCH_ICH_SYNC#21

C737

@

M_ODT018

M_ODT118

M_ODT217

M_ODT317

1

2

0.1U_0402_16V4Z~D

DMI_MRX_ITX_N0

DMI_MRX_ITX_N1

DMI_MRX_ITX_N2

DMI_MRX_ITX_N3

DMI_MRX_ITX_P0

DMI_MRX_ITX_P1

DMI_MRX_ITX_P2

DMI_MRX_ITX_P3

DMI_MTX_IRX_N0

DMI_MTX_IRX_N1

DMI_MTX_IRX_N2

DMI_MTX_IRX_N3

DMI_MTX_IRX_P0

DMI_MTX_IRX_P1

DMI_MTX_IRX_P2

DMI_MTX_IRX_P3

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR2

M_CLK_DDR3

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR#2

M_CLK_DDR#3

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

DDR_CKE2_DIMMB

DDR_CKE3_DIMMB

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

M_OCDCOMP0

M_OCDCOMP1

M_ODT0

M_ODT1

M_ODT2

M_ODT3

SMRCOMPN

SMRCOMPP

V_DDR_MCH_REF

PM_BMBUSY#

PM_E XTTS#0

PM_E XTTS#1

THERMTRIP_MCH#

ICH_PWRGD

PLTRST2#_R#

MCH_ICH_SYNC#

1

C738

2

@

0.1U_0402_16V4Z~D

D D

H_D#[0..63]7

C C

+VCCP

12

12

B B

R603

R604

54.9_0402_1%~D

54.9_0402_1%~D

12

12

R607

24.9_0402_1%~D

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_VREF

H_XRCOMP

H_XSCOMP

H_YRCOMP

H_YSCOMP

H_SWNG0

H_SWNG1

R608

24.9_0402_1%~D

U39A

F1

HD0#

J1

HD1#

H1

HD2#

J6

HD3#

H3

HD4#

K2

HD5#

G1

HD6#

G2

HD7#

K9

HD8#

K1

HD9#

K7

HD10#

J8

HD11#

H4

HD12#

J3

HD13#

K11

HD14#

G4

HD15#

T10

HD16#

W11

HD17#

T3

HD18#

U7

HD19#

U9

HD20#

U11

HD21#

T11

HD22#

W9

HD23#

T1

HD24#

T8

HD25#

T4

HD26#

W7

HD27#

U5

HD28#

T9

HD29#

W6

HD30#

T5

HD31#

AB7

HD32#

AA9

HD33#

W4

HD34#

W3

HD35#

Y3

HD36#

Y7

HD37#

W5

HD38#

Y10

HD39#

AB8

HD40#

W2

HD41#

AA4

HD42#

AA7

HD43#

AA2

HD44#

AA6

HD45#

AA10

HD46#

Y8

HD47#

AA1

HD48#

AB4

HD49#

AC9

HD50#

AB11

HD51#

AC11

HD52#

AB3

HD53#

AC2

HD54#

AD1

HD55#

AD9

HD56#

AC1

HD57#

AD7

HD58#

AC6

HD59#

AB5

HD60#

AD10

HD61#

AD4

HD62#

AC8

HD63#

J13

HVREF0

K13

HVREF1

E1

HXRCOMP

E2

HXSCOMP

Y1

HYRCOMP

U1

HYSCOMP

E4

HXSWING

W1

HYSWING

CALISTOGA A0_FCBGA1466~D

H9

HA3#

C9

HA4#

E11

HA5#

G11

HA6#

F11

HA7#

G12

HA8#

F9

HA9#

H11

HA10#

J12

HA11#

G14

HA12#

D9

HA13#

J14

HA14#

H13

HA15#

J15

HA16#

F14

HA17#

D12

HA18#

A11

HA19#

C11

HA20#

A12

HA21#

A13

HA22#

E13

HA23#

G13

HA24#

F12

HA25#

B12

HA26#

B14

HA27#

C12

HA28#

A14

HA29#

C14

HA30#

D14

HA31#

D8

HREQ#0

G8

HREQ#1

B8

HREQ#2

F8

HREQ#3

A8

HREQ#4

B9

HADSTB#0

C13

HADSTB#1

HCLKN

HCLKP

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HCPURST#

HADS#

HTRDY#

HDPWR#

HDRDY#

HDEFER#

HHITM#

HHIT#

HLOCK#

HBREQ0#

HBNR#

HBPRI#

HDBSY#

HCPUSLP#

HRS0#

HRS1#

HRS2#

AG1

AG2

K4

T7

Y5

AC4

K3

T6

AA5

AC5

J7

W8

U3

AB10

B7

E8

E7

J9

H8

C3

D4

D3

B3

C7

C6

F6

A7

E3

B4

E6

D6

HOST

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CLK_MCH_BCLK#

CLK_MCH_BCLK

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_RESET#

H_ADS#

H_TRDY#

H_DPWR#

H_DRDY#

H_DEFER#

H_HITM#

H_HIT#

H_LOCK#

H_BR0#

H_BNR#

H_BPRI#

H_DBSY#

H_CPUSLP#

H_RS#0

H_RS#1

H_RS#2

H_A#[3..31] 7

H_ADSTB#0 7

H_ADSTB#1 7

CLK_MCH_BCLK# 6

CLK_MCH_BCLK 6

H_DSTBN#[0..3] 7

H_DSTBP#[0..3] 7

H_DINV#0 7

H_DINV#1 7

H_DINV#2 7

H_DINV#3 7

H_RESET# 7

H_ADS# 7

H_TRDY# 7

H_DPWR# 7

H_DRDY# 7

H_DEFER# 7

H_HITM# 7

H_HIT# 7

H_LOCK# 7

H_BR0# 7

H_BNR# 7

H_BPRI# 7

H_DBSY# 7

H_CPUSLP# 7,22

H_RS#[0..2] 7

H_REQ#[0..4] 7

U39B

AE35

DMIRXN0

AF39

DMIRXN1

AG35

DMIRXN2

AH39

DMIRXN3

AC35

DMIRXP0

AE39

DMIRXP1

AF35

DMIRXP2

AG39

DMIRXP3

AE37

DMITXN0

AF41

DMITXN1

AG37

DMITXN2

AH41

DMITXN3

AC37

DMITXP0

AE41

DMITXP1

AF37

DMITXP2

AG41

DMITXP3

AY35

SM_CK0

AR1

SM_CK1

AW7

SM_CK2

AW40

SM_CK3

AW35

SM_CK0#

AT1

SM_CK1#

AY7

SM_CK2#

AY40

SM_CK3#

AU20

SM_CKE0

AT20

SM_CKE1

BA29

SM_CKE2

AY29

SM_CKE3

AW13

SM_CS0#

AW12

SM_CS1#

AY21

SM_CS2#

AW21

SM_CS3#

AL20

SM_OCDCOMP0

AF10

SM_OCDCOMP1

BA13

SM_ODT0

BA12

SM_ODT1

AY20

SM_ODT2

AU21

SM_ODT3

AV9

SM_RCOMPN

AT9

SM_RCOMPP

AK1

SM_VREF0

AK41

SM_VREF1

G28

PM_BMBUSY#

F25

PM_EXTTS0#

H26

PM_EXTTS1#

G6

PM_THERMTRIP#

AH33

PWROK

AH34

RSTIN#

K28

ICH_SYNC#

CALISTOGA A0_FCBGA1466~D

Description at page12

Note :

CFG3:17 has

internal pullup,

CFG18:19 has

internal pulldown

DMI

DDR MUXING

PM

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG

CFG18

CFG19

CFG20

G_CLKP

G_CLKN

D_REF_CLKN

D_REF_CLKP

CLKNC

D_REF_SSCLKN

D_REF_SSCLKP

CLK_REQ#

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

RESERVED6

RESERVED7

RESERVED8

RESERVED9

RESERVED10

RESERVED11

RESERVED12

RESERVED13

RESERVED

PM_EXTTS#0

PM_EXTTS#1

THERMTRIP_MCH#

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

CPU_MCH_BSEL0

K16

CPU_MCH_BSEL1

K18

CPU_MCH_BSEL2

J18

CFG3

F18

CFG4

E15

CFG5

F15

CFG6

E18

CFG7

D19

CFG8

D16

CFG9

G16

CFG10

E16

CFG11

D15

CFG12

G15

CFG13

K15

CFG14

C15

CFG15

H16

CFG16

G18

CFG17

H15

CFG18

J25

CFG19

K27

CFG20

J26

AG33

AF33

A27

A26

C40

D41

H32

A3

A39

A4

A40

AW1

AW41

AY1

BA1

BA2

BA3

BA39

BA40

BA41

C1

AY41

B2

B41

C41

D1

T32

R32

F3

F7

AG11

AF11

H7

J19

A41

A34

D28

D27

A35

10K_0402_5%~D

10K_0402_5%~D@

1 2

+1.5VRUN

R609

12

R610

12

R613

75_0402_5%~D

CPU_MCH_BSEL0 6,8

CPU_MCH_BSEL1 6,8

CPU_MCH_BSEL2 6,8

T26PAD~D

T31PAD~D

CFG5 12

CFG6 12

CFG7 12

T32PAD~D

CFG9 12

CFG10 12

CFG11 12

CFG12 12

CFG13 12

T29PAD~D

T28PAD~D

CFG16 12

T30PAD~D

CFG18 12

CFG19 12

CFG20 12

CLK_MCH_3GPLL 6

CLK_MCH_3GPLL# 6

3GPLL_REQ# 6

+3VRUN

+VCCP

close to AK1, AK41

A A

Layout Note:

H_XRCOMP & H_YRCOMP trace width

and spacing is 10/20

http://hobi-elektronika.net

5

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

4

3

2

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Calistoga(1 of 6)

Greenland-LA2732P

10 63W ed nes da y, De ce mber 28, 2005

1

of

X03

Page 11

5

D D

4

3

2

1

U39D

DDR_A_BS018

DDR_A_BS118

DDR_A_BS218 DDR_B_BS217

DDR_A_DM[0..7]18

DDR_A_DQS[0..7]18

C C

B B

DDR_A_DQS#[0..7]18

DDR_A_MA[0..13]18

DDR_A_CAS#18

DDR_A_RAS#18

DDR_A_WE#18

PAD~D

T40

PAD~D

T42

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11 DDR_B_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_CAS#

DDR_A_RAS#

DDR_A_WE#

SA_RCVENIN#

SA_RCVENOUT#

AU12

SA_BS0

AV14

SA_BS1

BA20

SA_BS2

AJ33

SA_DM0

AM35

SA_DM1

AL26

SA_DM2

AN22

SA_DM3

AM14

SA_DM4

AL9

SA_DM5

AR3

SA_DM6

AH4

SA_DM7

AK33

SA_DQS0

AT33

SA_DQS1

AN28

SA_DQS2

AM22

SA_DQS3

AN12

SA_DQS4

AN8

SA_DQS5

AP3

SA_DQS6

AG5

SA_DQS7

AK32

SA_DQS0#

AU33

SA_DQS1#

AN27

SA_DQS2#

AM21

SA_DQS3#

AM12

SA_DQS4#

AL8

SA_DQS5#

AN3

SA_DQS6#

AH5

SA_DQS7#

AY16

SA_MA0

AU14

SA_MA1

AW16

SA_MA2

BA16

SA_MA3

BA17

SA_MA4

AU16

SA_MA5

AV17

SA_MA6

AU17

SA_MA7

AW17

SA_MA8

AT16

SA_MA9

AU13

SA_MA10

AT17

SA_MA11

AV20

SA_MA12

AV12

SA_MA13

AY13

SA_CAS#

AW14

SA_RAS#

AY14

SA_WE#

AK23

SA_RCVENIN#

AK24

SA_RCVENOUT#

CALISTOGA A0 _ FCBGA1466~D

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

DDR SYS MEMORY A

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

AJ35

AJ34

AM31

AM33

AJ36

AK35

AJ32

AH31

AN35

AP33

AR31

AP31

AN38

AM36

AM34

AN33

AK26

AL27

AM26

AN24

AK28

AL28

AM24

AP26

AP23

AL22

AP21

AN20

AL23

AP24

AP20

AT21

AR12

AR14

AP13

AP12

AT13

AT12

AL14

AL12

AK9

AN7

AK8

AK7

AP9

AN9

AT5

AL5

AY2

AW2

AP1

AN2

AV2

AT3

AN1

AL2

AG7

AF9

AG4

AF6

AG9

AH6

AF4

AF8

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

PAD~D

PAD~D

DDR_B_BS0

DDR_B_BS1

DDR_B_BS2

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6DDR_A_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA12

DDR_B_MA13

DDR_B_CAS#

DDR_B_RAS#

DDR_B_WE#

SB_RCVENIN#

SB_RCVENOUT#

DDR_B_BS017

DDR_B_BS117

DDR_B_DM[0..7]17

DDR_B_DQS[0..7]17

DDR_B_DQS#[0..7]17

DDR_B_MA[0..13]17

DDR_B_CAS#17

DDR_B_RAS#17

DDR_B_WE#17

T41

T43

U39E

AT24

SB_BS0

AV23

SB_BS1

AY28

SB_BS2

AK36

SB_DM0

AR38

SB_DM1

AT36

SB_DM2

BA31

SB_DM3

AL17

SB_DM4

AH8

SB_DM5

BA5

SB_DM6

AN4

SB_DM7

AM39

SB_DQS0

AT39

SB_DQS1

AU35

SB_DQS2

AR29

SB_DQS3

AR16

SB_DQS4

AR10

SB_DQS5

AR7

SB_DQS6

AN5

SB_DQS7

AM40

SB_DQS0#

AU39

SB_DQS1#

AT35

SB_DQS2#

AP29

SB_DQS3#

AP16

SB_DQS4#

AT10

SB_DQS5#

AT7

SB_DQS6#

AP5

SB_DQS7#

AY23

SB_MA0

AW24

SB_MA1

AY24

SB_MA2

AR28

SB_MA3

AT27

SB_MA4

AT28

SB_MA5

AU27

SB_MA6

AV28

SB_MA7

AV27

SB_MA8

AW27

SB_MA9

AV24

SB_MA10

BA27

SB_MA11

AY27

SB_MA12

AR23

SB_MA13

AR24

SB_CAS#

AU23

SB_RAS#

AR27

SB_WE#

AK16

SB_RCVENIN#

AK18

SB_RCVENOUT#

CALISTOGA A0 _ FCBGA1466~D

AK39

SB_DQ0

AJ37

SB_DQ1

AP39

SB_DQ2

AR41

SB_DQ3

AJ38

SB_DQ4

AK38

SB_DQ5

AN41

SB_DQ6

AP41

SB_DQ7

AT40

SB_DQ8

AV41

SB_DQ9

AU38

SB_DQ10

AV38

SB_DQ11

AP38

SB_DQ12

AR40

SB_DQ13

AW38

SB_DQ14

AY38

SB_DQ15

BA38

SB_DQ16

AV36

SB_DQ17

AR36

SB_DQ18

AP36

SB_DQ19

BA36

SB_DQ20

AU36

SB_DQ21

AP35

SB_DQ22

AP34

SB_DQ23

AY33

SB_DQ24

BA33

SB_DQ25

AT31

SB_DQ26

AU29

SB_DQ27

AU31

SB_DQ28

AW31

SB_DQ29

AV29

SB_DQ30

AW29

SB_DQ31

AM19

SB_DQ32

AL19

SB_DQ33

AP14

SB_DQ34

AN14

SB_DQ35

AN17

SB_DQ36

AM16

SB_DQ37

AP15

SB_DQ38

AL15

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

AJ11

AH10

AJ9

AN10

AK13

AH11

AK10

AJ8

BA10

AW10

BA4

AW4

AY10

AY9

AW5

AY5

AV4

AR5

AK4

AK3

AT4

AK5

AJ5

AJ3

DDR SYS MEMORY B

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_B_D[0..63] 17DDR_A_D[0..63] 18

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Calistogo(2 of 6)

Greenland-LA2732P

11 63W ed nes da y, De ce mber 28, 2005

1

X03

of

http://hobi-elektronika.net

5

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

4

3

2

Title

Size Document Number Rev

Date: Sheet

Page 12

5

D D

4

3

2

1

Strap Pin Table

T44 PAD~D

C C

B B

SDVOCTRL_DATA

+1.5VRUN

+VCCP

U39C

H27

SDVOCTRL_DATA

H28

SDVOCTRL_CLK

B37

LA_DATA0

B34

LA_DATA1

A36

LA_DATA2

C37

LA_DATA#0

B35

LA_DATA#1

A37

LA_DATA#2

F30

LB_DATA0

D29

LB_DATA1

F28

LB_DATA2

G30

LB_DATA#0

D30

LB_DATA#1

F29

LB_DATA#2

A32

LA_CLK

A33

LA_CLK#

E26

LB_CLK

E27

LB_CLK#

D32

LBKLT_CTL

J30

LBKLT_EN

H30

LCTLA_CLK

H29

LCTLB_DATA

G26

LDDC_CLK

G25

LDDC_DATA

F32

LVDD_EN

B38

LIBG

C35

LVBG

C33

LVREFH

C32

LVREFL

A16

TVDAC_A

C18

TVDAC_B

A19

TVDAC_C

J20

TV_IREF

B16

TV_IRTNA

B18

TV_IRTNB

B19

TV_IRTNC

J29

TV_DCONSEL1

K30

TV_DCONSEL0

C26

DDCCLK

C25

DDCDATA

H23

VSYNC

G23

HSYNC

E23

BLUE

D23

BLUE#

C22

GREEN

B22

GREEN#

A21

RED

B21

RED#

J22

CRT_IREF

CALISTOGA A0 _ FCBGA1466~D

EXP_COMPI

EXP_COMPO

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

LVDS

TV CRT

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

EXP_TXN7

EXP_TXN8

PCI-EXPRESS GRAPHICS

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

D40

D38

PCIE_MRX_GTX_N0

F34

PCIE_MRX_GTX_N1

G38

PCIE_MRX_GTX_N2

H34

PCIE_MRX_GTX_N3

J38

PCIE_MRX_GTX_N4

L34

PCIE_MRX_GTX_N5

M38

PCIE_MRX_GTX_N6

N34

PCIE_MRX_GTX_N7

P38

PCIE_MRX_GTX_N8

R34

PCIE_MRX_GTX_N9

T38

PCIE_MRX_GTX_N10

V34

PCIE_MRX_GTX_N11

W38

PCIE_MRX_GTX_N12

Y34

PCIE_MRX_GTX_N13

AA38

PCIE_MRX_GTX_N14

AB34

PCIE_MRX_GTX_N15

AC38

PCIE_MRX_GTX_P0

D34

PCIE_MRX_GTX_P1

F38

PCIE_MRX_GTX_P2

G34

PCIE_MRX_GTX_P3

H38

PCIE_MRX_GTX_P4

J34

PCIE_MRX_GTX_P5

L38

PCIE_MRX_GTX_P6

M34

PCIE_MRX_GTX_P7

N38

PCIE_MRX_GTX_P8

P34

PCIE_MRX_GTX_P9

R38

PCIE_MRX_GTX_P10

T34

PCIE_MRX_GTX_P11

V38

PCIE_MRX_GTX_P12

W34

PCIE_MRX_GTX_P13

Y38

PCIE_MRX_GTX_P14

AA34

PCIE_MRX_GTX_P15

AB38

PCIE_MTX_GRX_N0

F36

PCIE_MTX_GRX_N1

G40

PCIE_MTX_GRX_N2

H36

PCIE_MTX_GRX_N3

J40

PCIE_MTX_GRX_N4

L36

PCIE_MTX_GRX_N5

M40

PCIE_MTX_GRX_N6

N36

PCIE_MTX_GRX_N7

P40

PCIE_MTX_GRX_N8

R36

PCIE_MTX_GRX_N9

T40

PCIE_MTX_GRX_N10

V36

PCIE_MTX_GRX_N11

W40

PCIE_MTX_GRX_N12

Y36

PCIE_MTX_GRX_N13

AA40

PCIE_MTX_GRX_N14

AB36

PCIE_MTX_GRX_N15

AC40

PCIE_MTX_GRX_P0

D36

PCIE_MTX_GRX_P1

F40

PCIE_MTX_GRX_P2

G36

PCIE_MTX_GRX_P3

H40

PCIE_MTX_GRX_P4

J36

PCIE_MTX_GRX_P5

L40

PCIE_MTX_GRX_P6

M36

PCIE_MTX_GRX_P7

N40

PCIE_MTX_GRX_P8

P36

PCIE_MTX_GRX_P9

R40

PCIE_MTX_GRX_P10

T36

PCIE_MTX_GRX_P11

V40

PCIE_MTX_GRX_P12

W36

PCIE_MTX_GRX_P13

Y40

PCIE_MTX_GRX_P14

AA36

PCIE_MTX_GRX_P15

AB40

PEGCOMP

R615

24.9_0402_1%~D

1 2

+1.5VRUN_PCIE

PCIE_MRX_GTX_N[0..15]

PCIE_MRX_GTX_P[0..15]

PCIE_MTX_GRX_N[0..15]

PCIE_MTX_GRX_P[0..15]

PCIE_MRX_GTX_N[0..15] 19

PCIE_MRX_GTX_P[0..15] 19

PCIE_MTX_GRX_N[0..15] 19

PCIE_MTX_GRX_P[0..15] 19

CFG5

CFG6

CFG7

CFG9

CFG10

CFG11

CFG[13:12]

CFG16

(FSB Dynamic ODT)

CFG18

(VCC Select)

CFG19

(DMI Lane Reversal)

SDVO_CTRLDATA

CFG20

(PCIE/SDVO select)

Low = DMI x 2

High = DMI x 4

Low = Moby Dick

High = Calistoga

Low = DT/Transportable CPU

High = Mobile CPU

Low = Reverse Lane

High = Normal Operation

*

*

*

*

Low = Reserved

High = Mobility

PSB 4x Clock Enable

Low = Calistoga

High = Reserved

00 = Reserved

01 = XOR Mode Enabled

10 = All Z Mode Enabled

11 = Normal Operation

(Default)

*

*

*

Low = Disabled

High = Enabled

Low = 1.05V (Default)

High = 1.5V

Low = Normal

Operation (Default):

Lane number in Order

*

*

*

High = Reverse Lane

Low = No SDVO Device Present

High = SDVO Device Present

Low = Only PCIE or SDVO is

operational.

High = PCIE/SDVO are operating

simu.

(Default)

(Default)

*

*

R617 2.2K_0402_5%~D@

CFG510

CFG610

CFG710

CFG910

CFG1010

CFG1110

CFG1210

CFG1310

CFG1610

1 2

R622 2.2K_0402_5%~D@

1 2

R625 2.2K_0402_5%~D@

1 2

R618 2.2K_0402_5%~D@

1 2

R624 2.2K_0402_5%~D@

1 2

R619 2.2K_0402_5%~D@

1 2

R626 2.2K_0402_5%~D@

1 2

R620 2.2K_0402_5%~D@

1 2

R621 2.2K_0402_5%~D@

1 2

CFG[3:17] have internal pullup

R623 1K_0402_5%~D@

CFG1810

CFG1910

CFG2010

1 2

R627 1K_0402_5%~D@

1 2

R628 1K_0402_5%~D@

1 2

CFG[18:19] have internal pulldown

+3VRUN

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Calistoga(3 of 6)

Greenland-LA2732P

12 63W ed nes da y, De ce mber 28, 2005

1

X03

of

http://hobi-elektronika.net

5

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

4

3

2

Title

Size Document Number Rev

Date: Sheet

Page 13

5

4

3

2

1

+VCCP

D D

CRB 270uF

1

+

C747

2

330U_D2E_2.5VM~D

C C

B B

A A

1

C754

C755

2

4.7U_0805_10V4Z~D

2.2U_0603_6.3V6K~D

C763

0.47U_0402_10V4Z~D

1

C772

2

1

C773

0.22U_0402_10V4Z~D

2

0.22U_0402_10V4Z~D

+1.5VRUN

1

2

U39_A6

1

2

U39_D2

U39_AB1

1

C775

2

0.47U_0402_10V4Z~D

U39H

AC14

VTT0

AB14

VTT1

W14

VTT2

V14

VTT3

T14

VTT4

R14

VTT5

P14

VTT6

N14

VTT7

M14

VTT8

L14

VTT9

AD13

VTT10

AC13

VTT11

AB13

VTT12

AA13

VTT13

Y13

VTT14

W13

VTT15

V13

VTT16

U13

VTT17

T13

VTT18

R13

VTT19

N13

VTT20

M13

VTT21