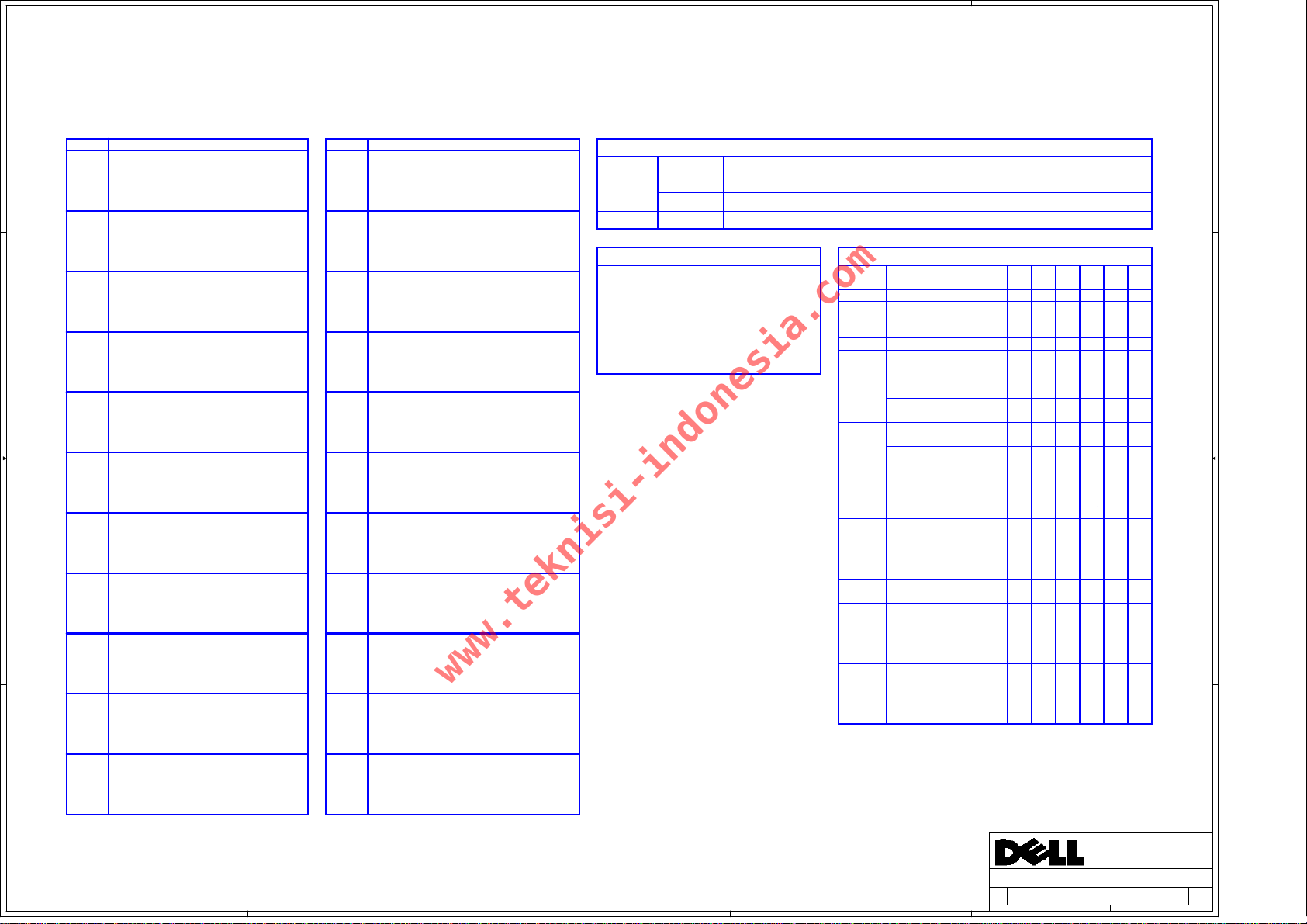

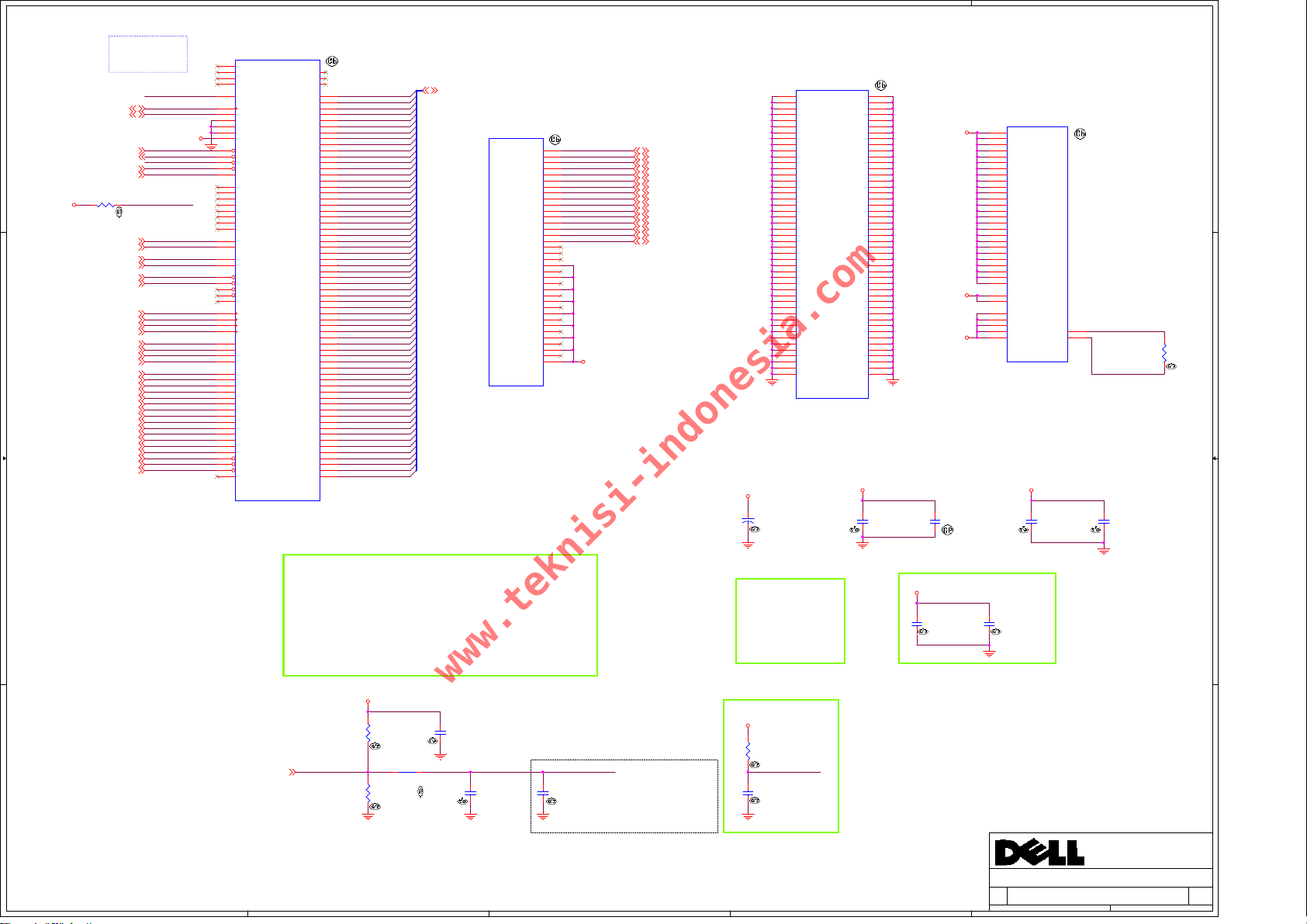

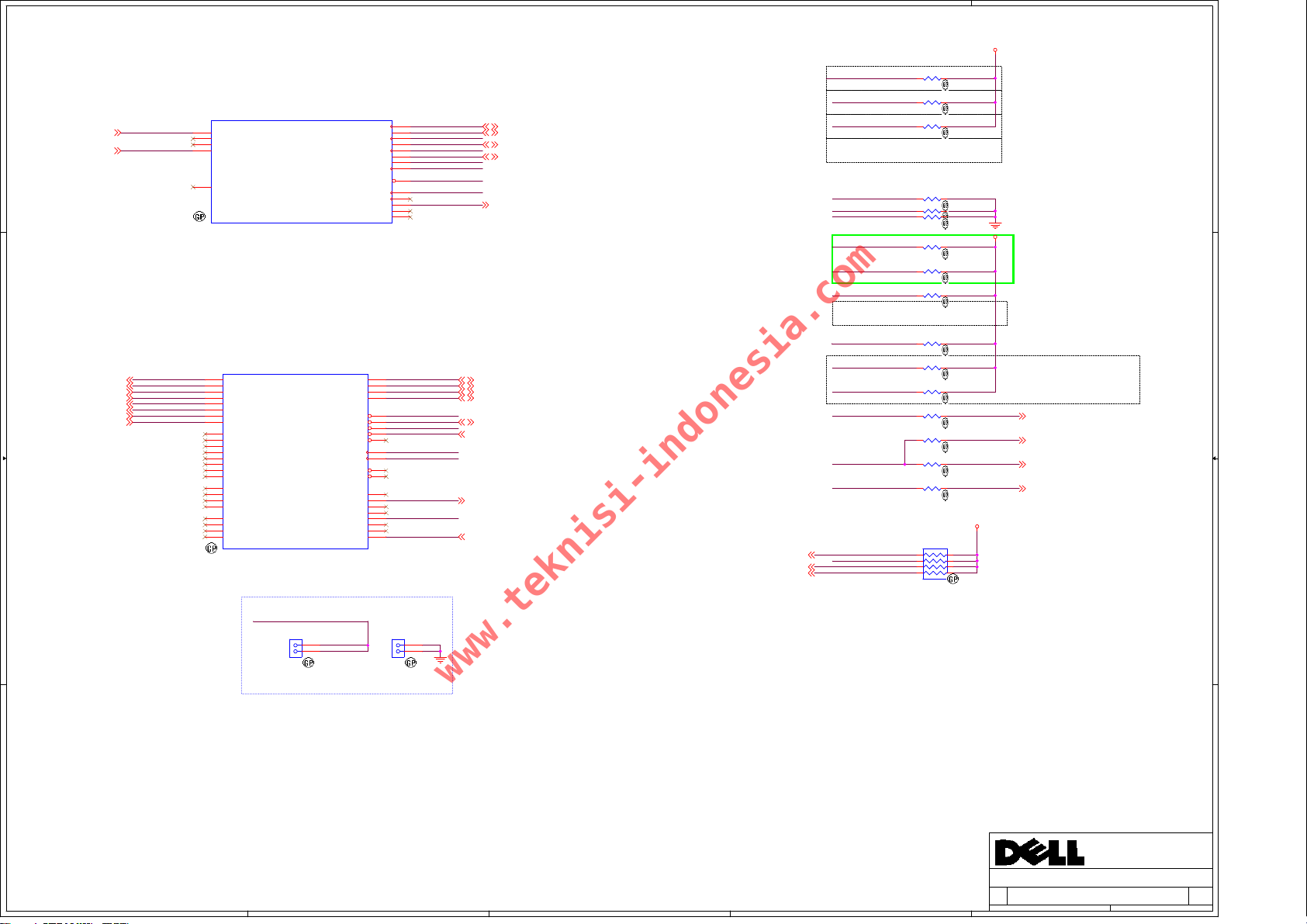

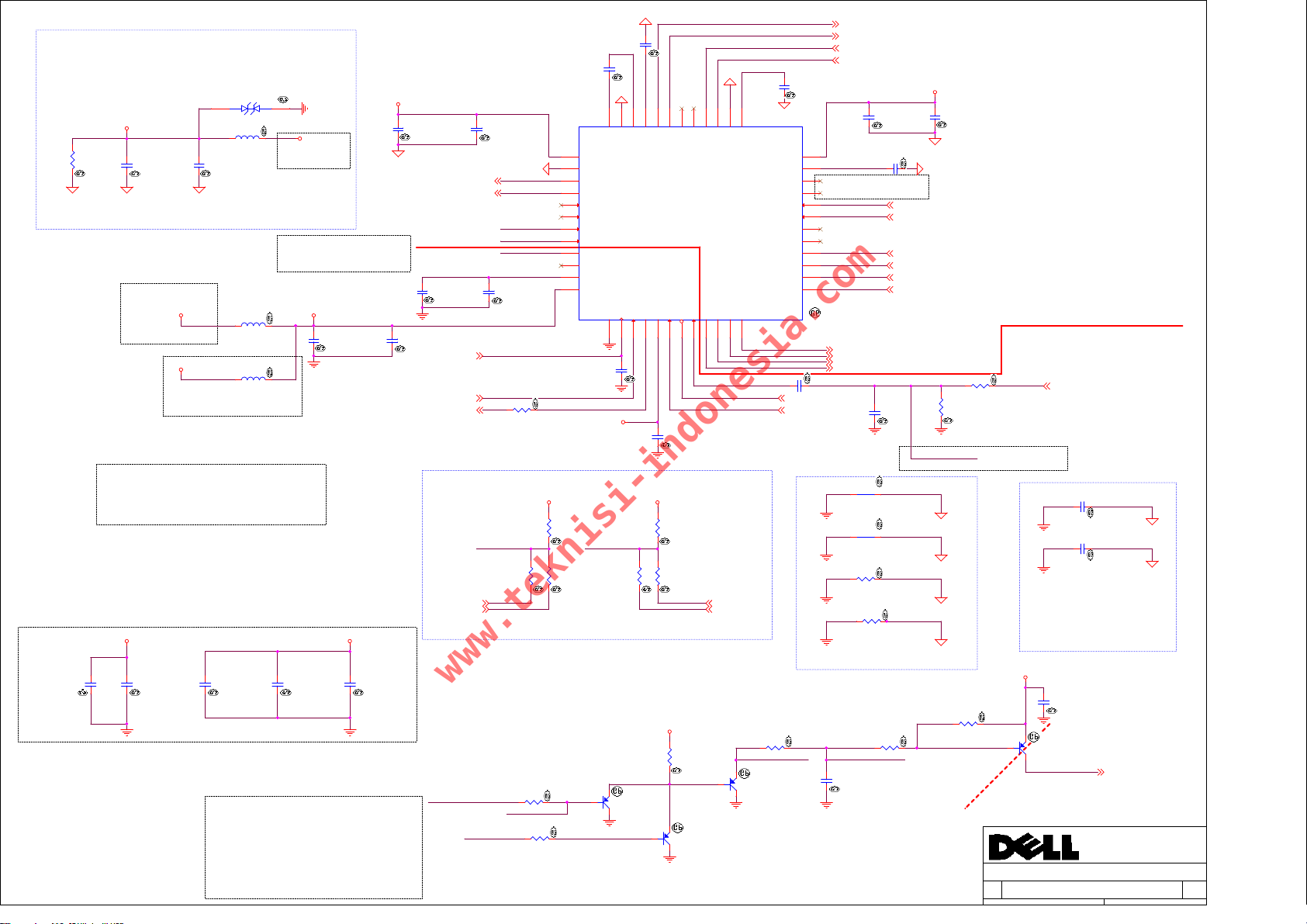

Dell Vostro Inspiron 3470 Schematic

5

www.teknisi-indonesia.com

4

3

2

1

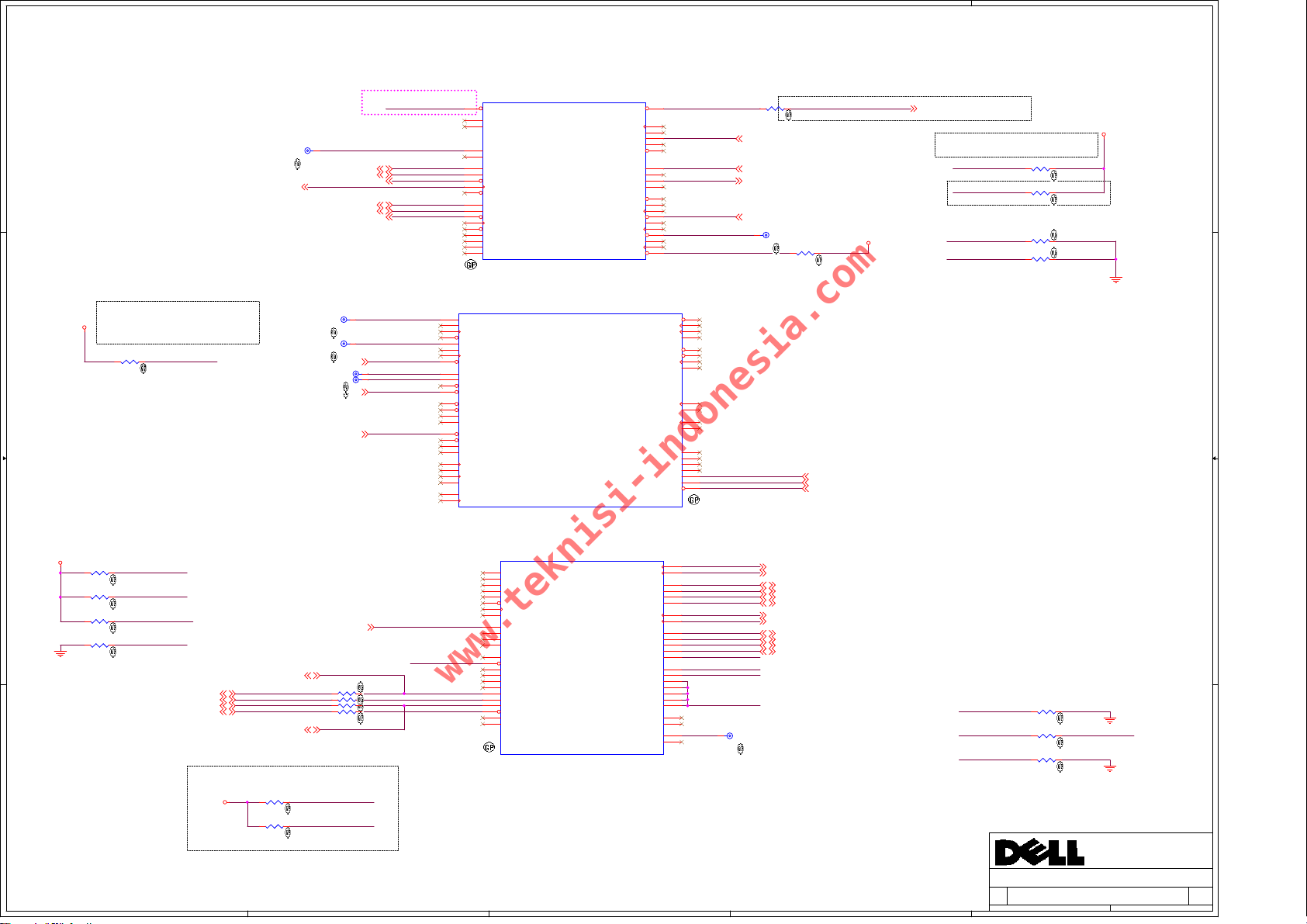

Project Namel: Gambit MLK SFF

PCB Number: 17530

PCBA Ver.: A00

SCH Ver.: A00

Project Code : 3PD06M010001

D D

C C

B B

A A

PCB Size: 285.7 x 200mm, 1.6mm, 4 Layers

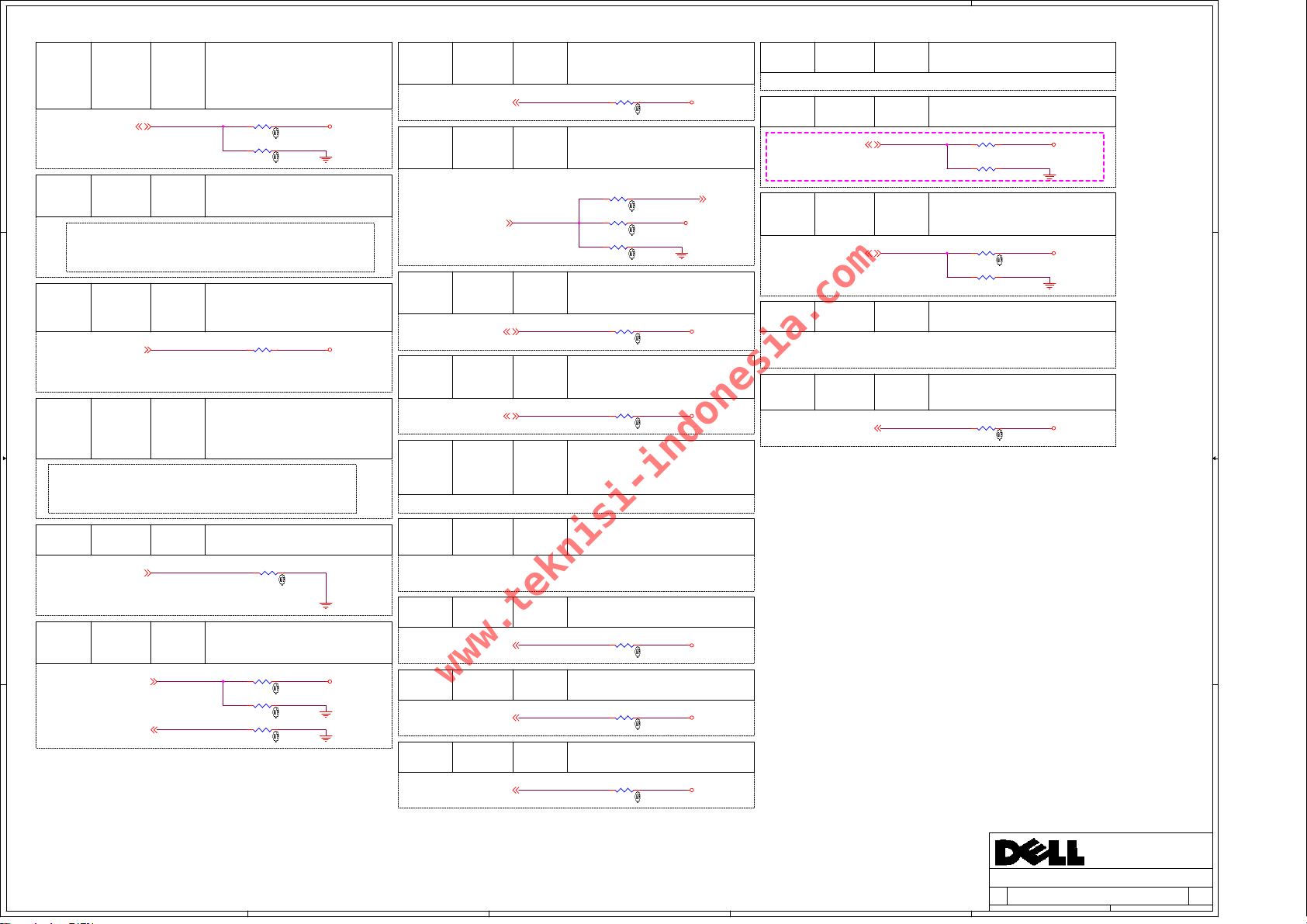

PAGE

TITLE

01

Cover Page

02

Block Diagram

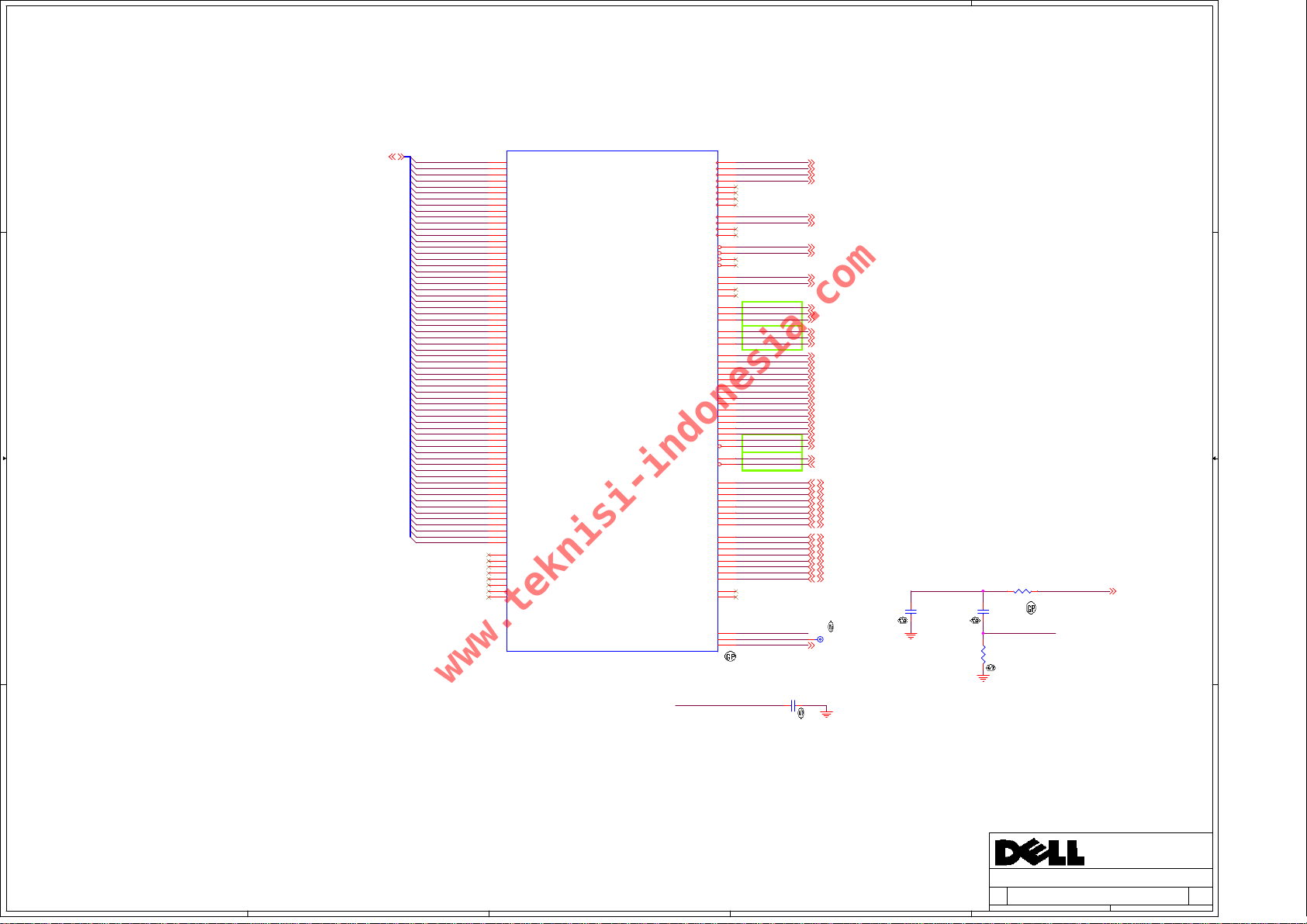

03 CPU_DDRA_DDRB

CPU_CFG/CLOCK

04

CPU_(PCIE)

05

06

CPU_(VSS)

CPU_(VCC_CORE/SENCE)

07

08

CPU_(DDI/EDP)

09

CPU_(POWER CAP)

CPU_(R)

10

11

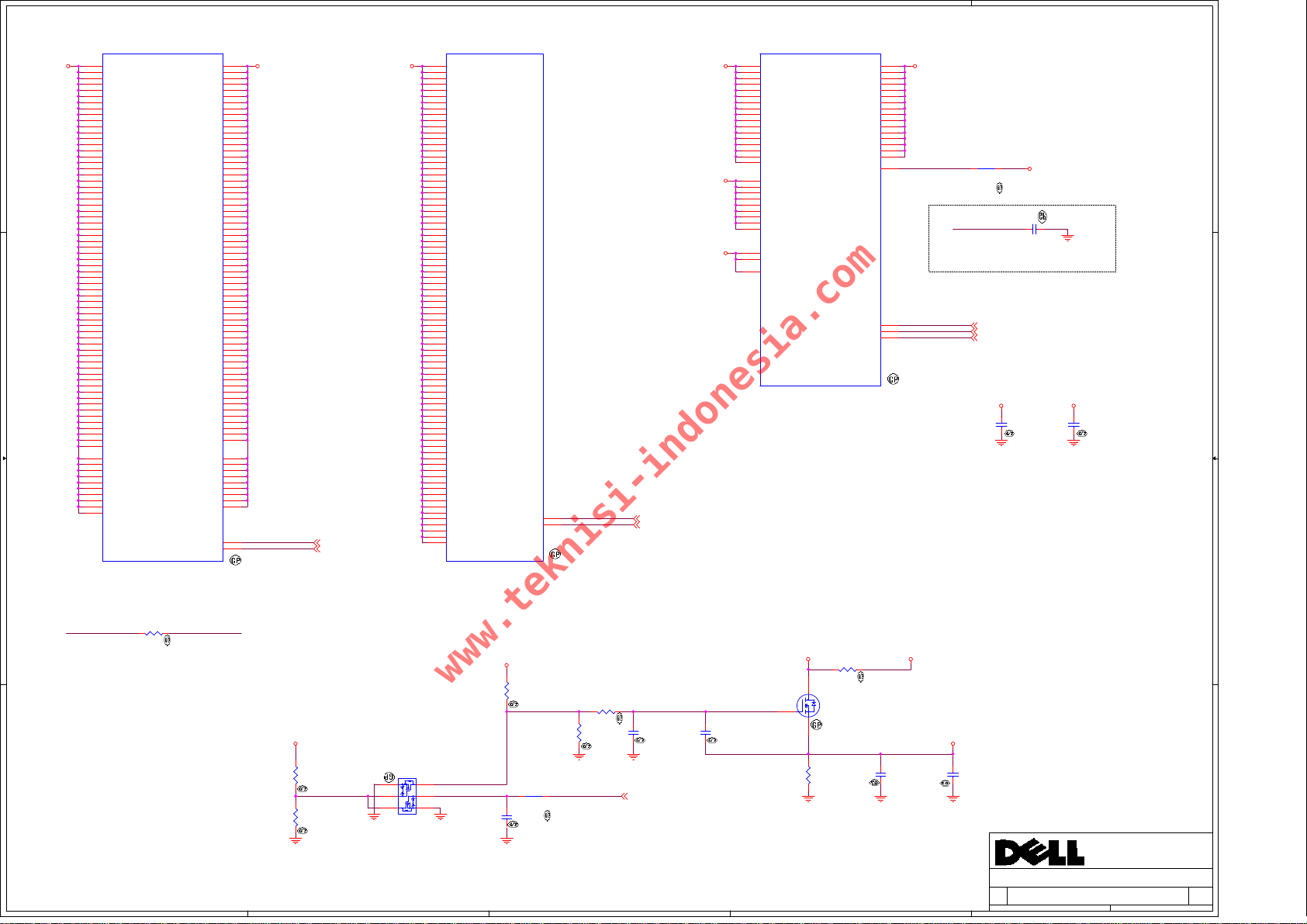

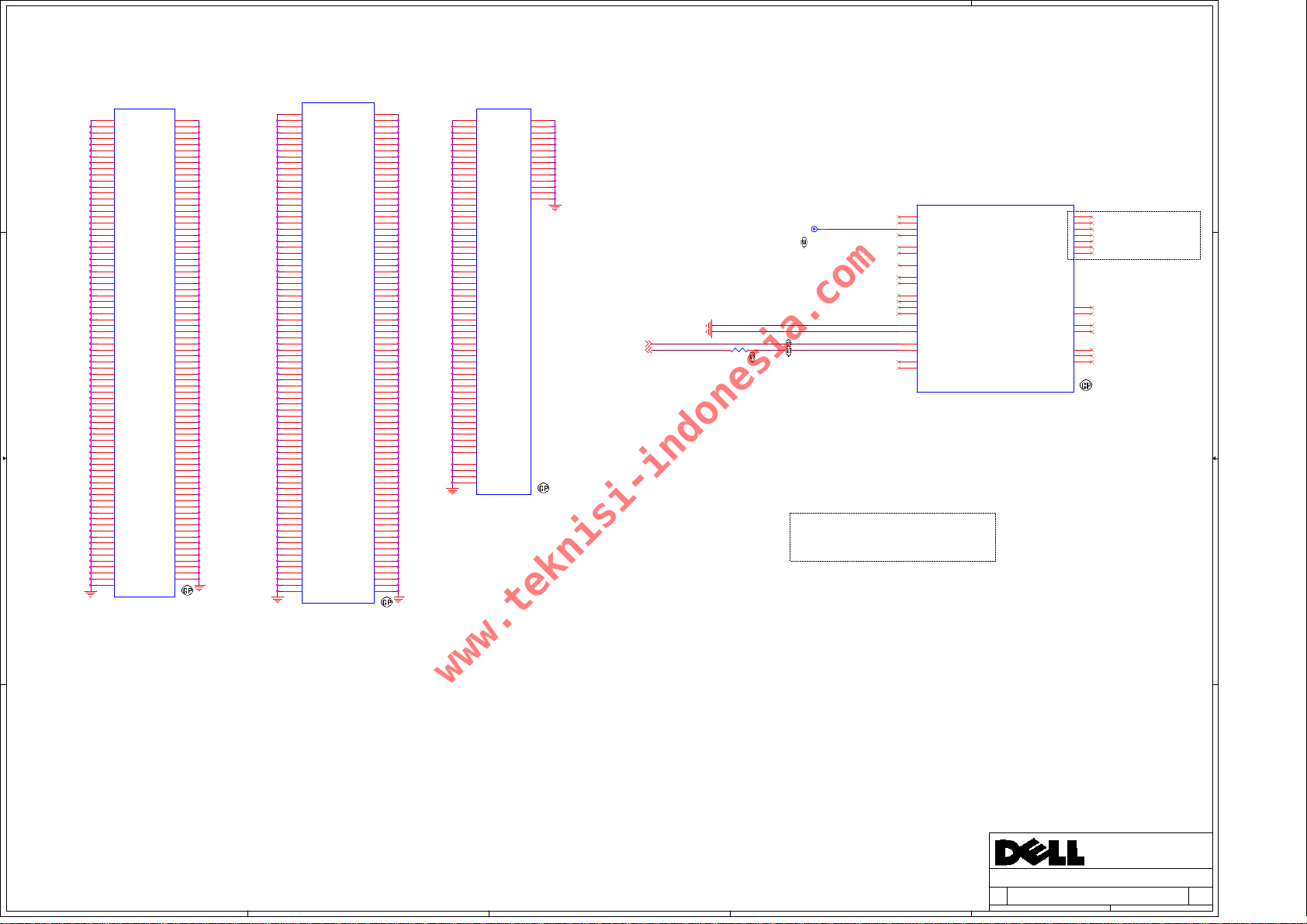

DDR4 CHA DIMM 0

12

(R)

13

DDR4 CHB DIMM 0

14 (R)

15

PCH_(Audio/SMBUS/JTAG/GPIO)

16

PCH_(CLK)

17

PCH_(SATA/PCIE/HOST)

PCH_(DMI/USB2/USB3/PCIE)

18

19

PCH_(DDI/USB3/GPIO)

20

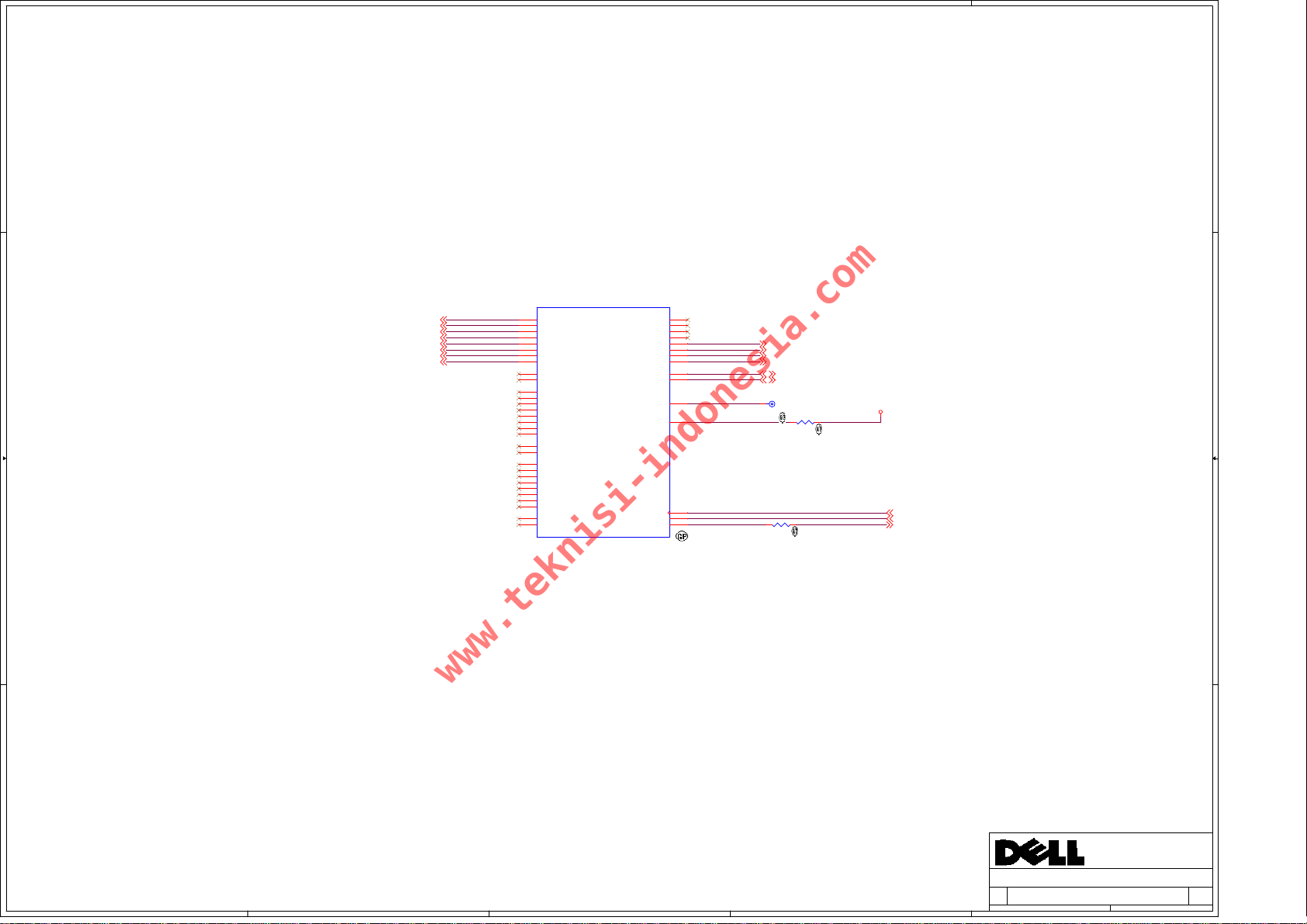

PCH_(UART/GPIO/I2C)

21

PCH_(Strap Pin)

PCH_(VCC)

22

PCH_(VSS/GPIO)

23

SIO_(SMSC5533)

24

25

SPI/RTC/BAT

FAN Control/Thermal sensor

26

27

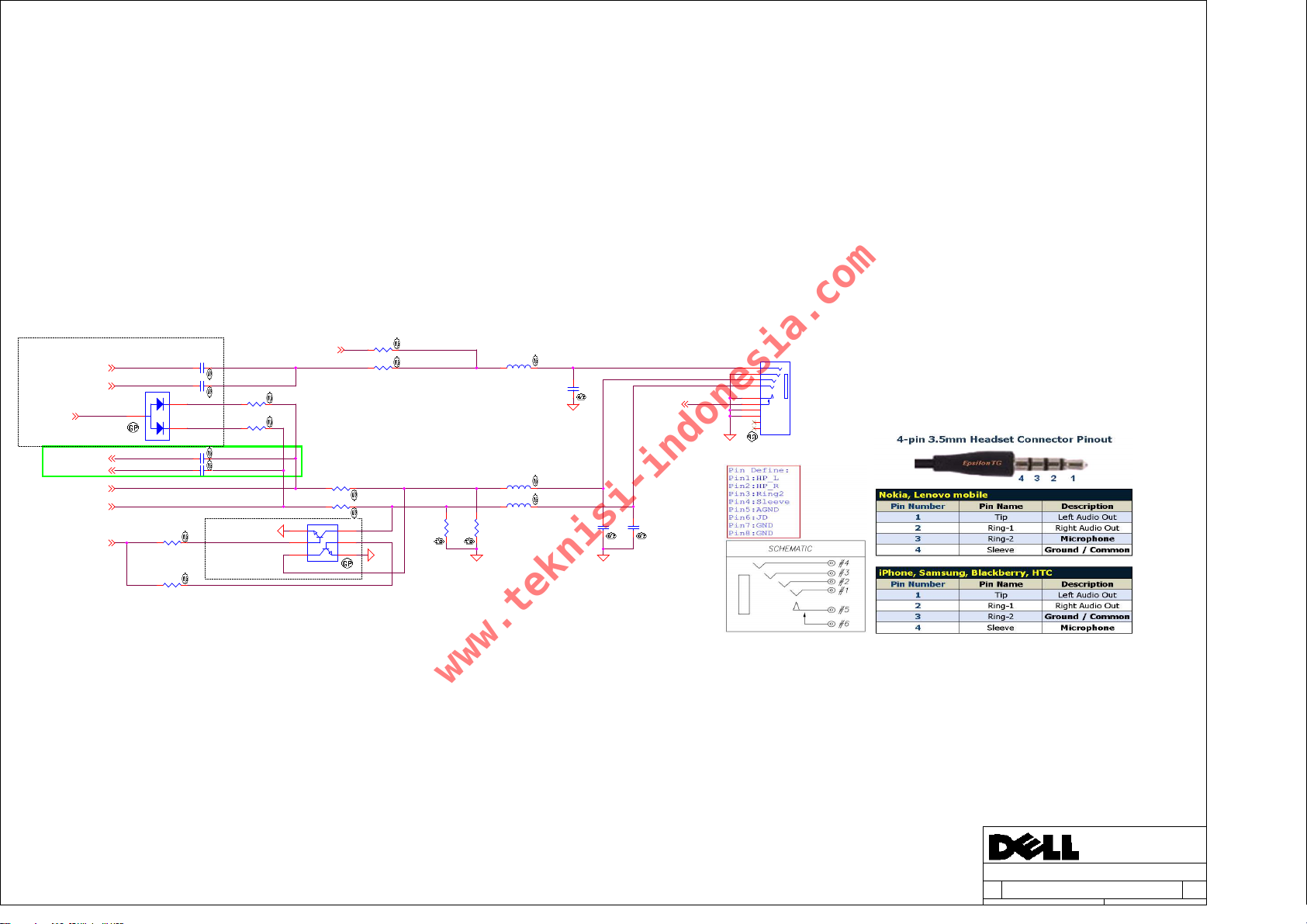

AUDIO_(ALC3820)

(R)

28

29

AUDIO JACK

(R)

30

31

LAN_(RTL8111H)

32

RJ45+USB2.0

33

Card Reader_(RTS5170)

34

(R)

(R)

35

Rear USB2.0

36

(R)

37

38

(R)

39

Front USB3.0

40

(R)

41

ATX CONNECTOR

(R)

42

3P3V_SB & 5V_S0 Power

43

44

VCORE/V_GT_(NCP81203)

45

VCORE OUTPUT_(NCP81166)

46

V_GT OUTPUT_(NCP81166)

47

VCCSA_(RT8237C)

48

VCCIO_(APL5611A)

49

5V_S5/3P3V_S5_(RT6575D)

50

DDR_PWR_(RT8231A)

51

PCH_1D0V_(RT8237C)

DDR_2D5V_VPP

52

MINUS 12V_(NCP3063)

53

3P3V_S0 Power

54

Sequence Circuit

55

PAGE

57

58 VGA_(RTD2166)

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

TITLE

HDMI56

(R)

(R)

HDD/ODD

(R)

NGFF

PCI_SLOT

PWR BTM/LED

(R)

(R)

(R)

LPC/UART Port

(R)

(R)

(R)

(R)

(R)

(R)

(R)

(R)

(R)

(R)

(R)

(R)

(R)

(R)

(R)

(R)

(R)

(R)

(R)

(R)

(R)

(R)

TPM

(R)

PCIeX16

PCIeX1

(R)

(R)

(R)

(R)

XDP & APS

(R)

(R)

Power Sequence

Power Block Diagram

Power Good & Reset Diagram

Clock Diagram

Reset Flow Chart

Change Histroy

Jumper Setting

With Jumper to ME Disable

Without Jumper to Clear Password

With Jumper to Clear CMOS

PD 1K to GND for Debug, All Power-On

JMP1

DB1

Pin 1-2

Pin 3-4

Pin 5-6

PD 1K

BOM Configuration

(R_): Unmount

(X_): Debug

(GAM_): Gambit MLK SFF

(EAG_): Eagle SFF

(TPM_): With TPM

(NONTPM_): Without TPM

Power sates

+12V

-12V

3.3V

VBAT

VDDQ

DIMM

V_12P0_A

+12V

V_12V_CPU_S0

-12V

5V_S0

USBVCC12

USBVCC34

+5V

USBVCC78

5V_S5

V_5_CODEC

3P3V_S0

3P3V_AUD_S0

3P3V_SB

3P3V_SPI

3P3V_LAN

3P3V_M2VAUX

3P3V_PCIVAUX

3P3V_S5

3P0V_BAT_VREG

VBAT1

VBAT2

+VCCPLL_OC

V_SM

V_SM_VTT

V_VPP

V1P0_PCH_SB

+V1P0A_VCCAPLL

+V1P0A_VCCF24_1P0

PCH

+V1P0A_VCCAMPHYPLL

V_CPU_ST_PLL

V_CPU_CORE

V_CPU_GT

V_CPU_IO

CPU

V_CPU_SA

+VCCFUSEPRG

G3 DSW S4 S3 S0Name

O O OO

O O O O O

O O O O O

O

O

O

O

O

OOOS5O

O

OOOO

OOOO

OOOOOO

O

OO

O

OOOO

O

5

4

3

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Cover Page

Cover Page

Cover Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Gambits MLK SFF

Gambits MLK SFF

Gambits MLK SFF

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

1 107Friday, February 02, 2018

1 107Friday, February 02, 2018

1

1 107Friday, February 02, 2018

A00C

A00C

A00C

5

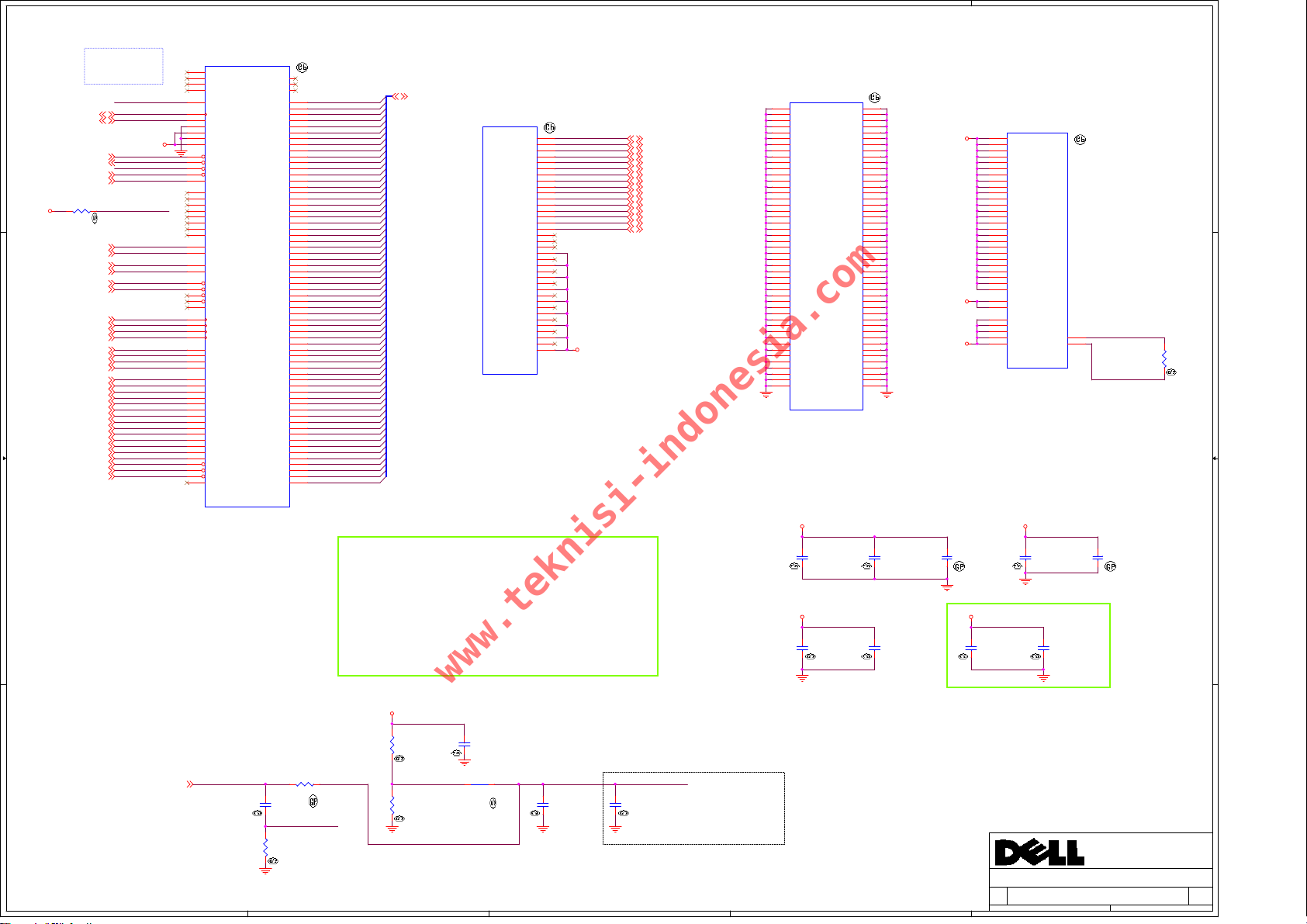

www.teknisi-indonesia.com

4

3

2

1

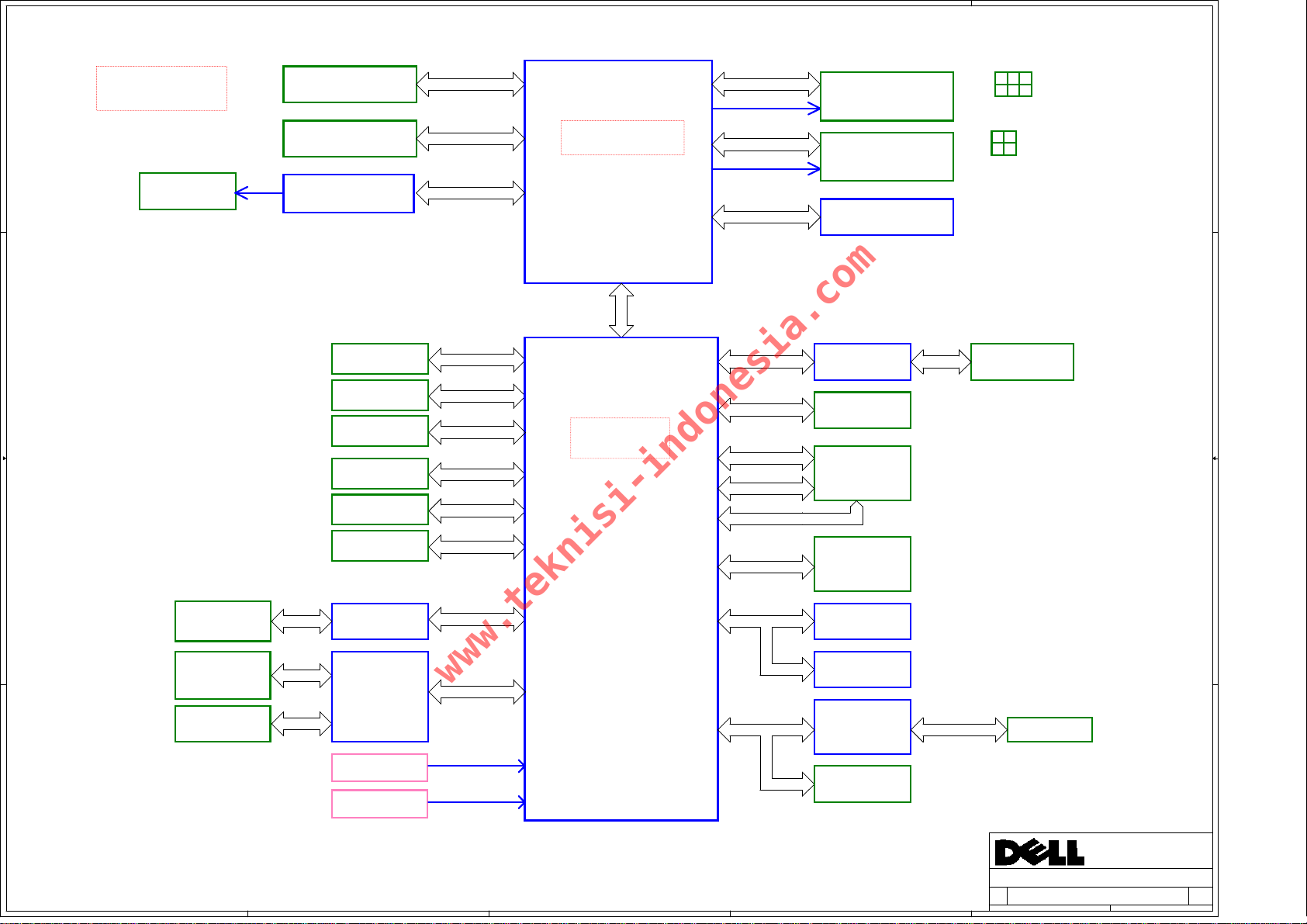

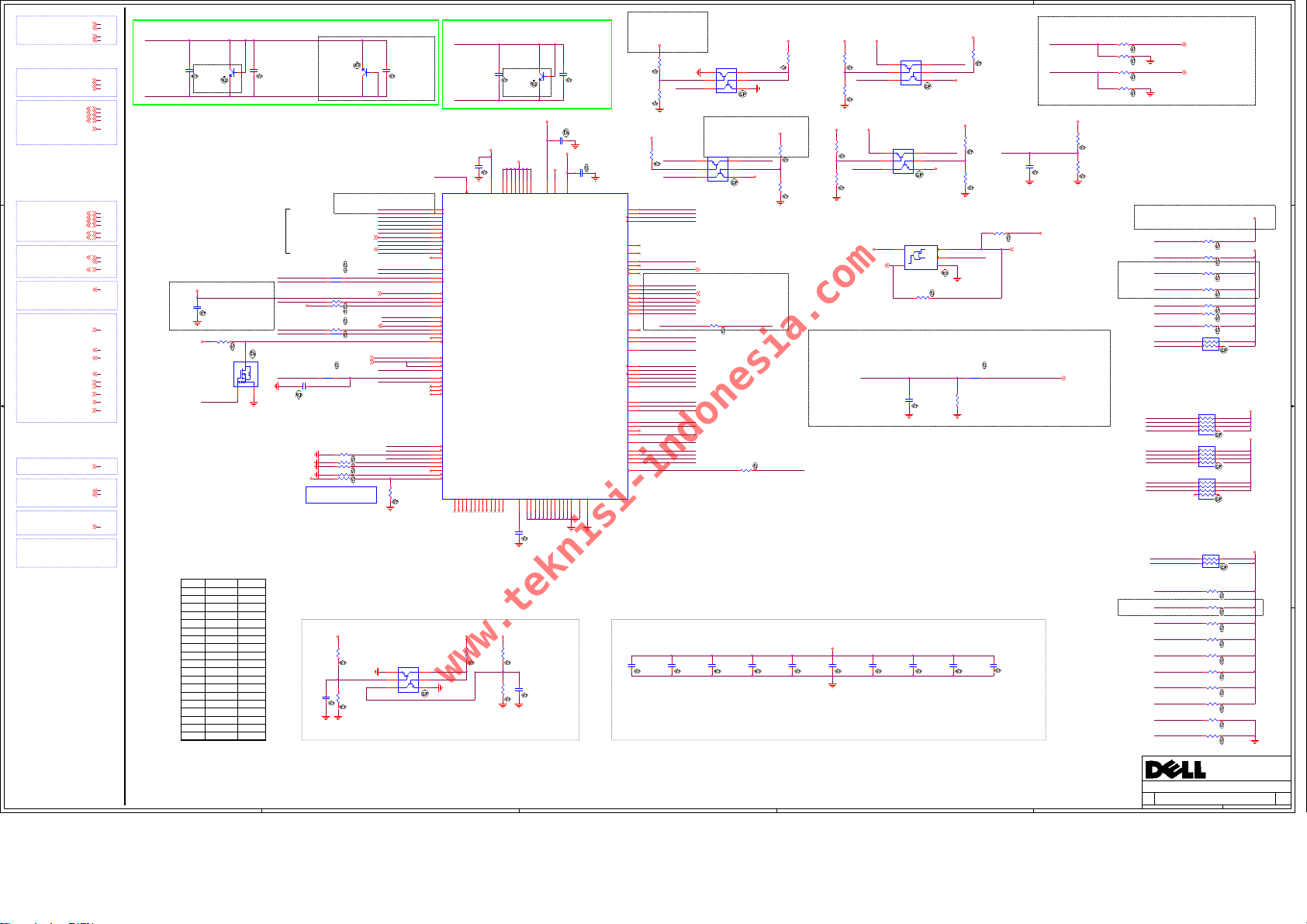

PCB BOARD SIZE

285.7 x 200mm

4 Layer

D D

PCIE X16 SLOT

HDMI PORT v1.4

D-SUB PORT

eDP to VGA

Realtek RTD2166

PCI EXPRESS Gen3

DDI1

eDP(1.4)

INTEL

Coffee Lake-S

(65W 4C + GT2)

SKT H4 LGA1151

42.5 mm x 42.5 mm

Channel A

64 bit

2666MHz

Channel B

64 bit

2666MHz

DDR4 UDIMM *1

DDR4 UDIMM *1

ATX-6PIN CONN

CPU-4PIN CONN

IMVP8

(Vcore 4 Phase + VGT 2 Phase)

DMI

C C

B B

SATA 3.0

(Port 0)

SATA 2.0

(Port 1)

SATA 2.0

(Port 2)

Front USB 3.0*2

Rear USB 2.0*2

(RJ45 USB Conn.)

Rear USB 2.0*2

(DUAL USB Conn.)

SATA3.0

SATA3.0

SATA3.0

USB3.0

USB2.0

USB2.0

INTEL PCH

Canonlake

PCH-H370

FCBGA 837PIN

23 mm x 23 mm

PCIE Interface

PCIE Gen2 Interface

PCIE Interface

USB2.0

CNVI

SATA3.0

Realtek

RTL8111H

PCIE X1 SLOT

WLAN NGFF Conn.

SSD M.2 E KEY Conn.

RJ45 Conn.

3 in 1 Card reader

Rear AUDIO

Line - In

Line - Out

Mic - In

Front AUDIO

CTIA (Apple)

Standard Headset

Realtek

RTS5170

HDA CODEC

Realtek

ALC3820

32.768KHz

A A

5

24MHz

4

USB2.0

HDA

32.768KHz

24MHz

SPI BUS

LPC BUS

3

SPI Flash ROM

(32MB)

Nuvoton TPM

NPCT750

SIO

SMSC SCH5553

Debug Conn.

2

Eagle only

CPU FAN CNTL

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU 1X4 FAN

Block Diagram

Block Diagram

Block Diagram

Gambits MLK SFF

Gambits MLK SFF

Gambits MLK SFF

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

2 107Friday, February 02, 2018

2 107Friday, February 02, 2018

1

2 107Friday, February 02, 2018

A00C

A00C

A00C

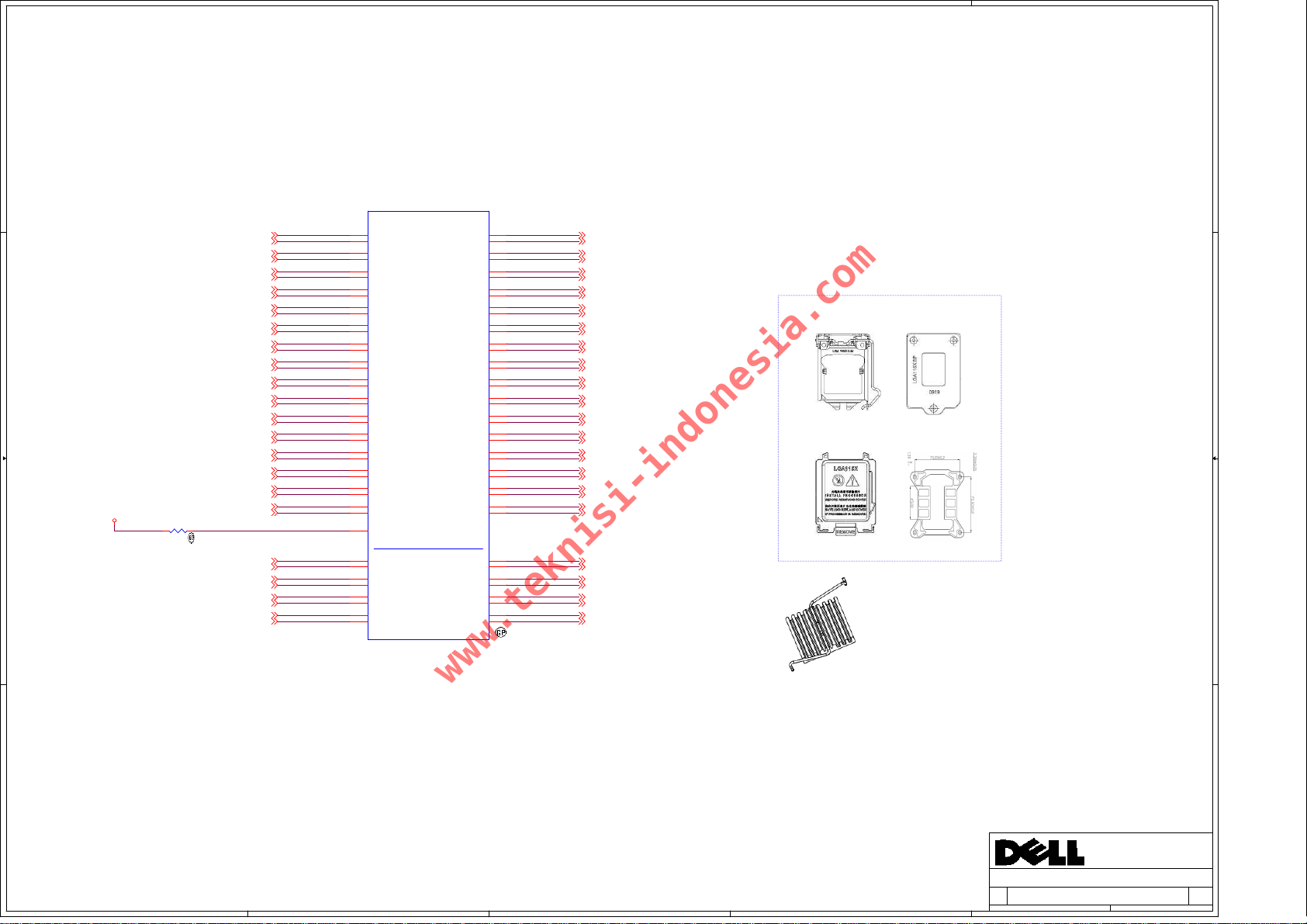

5

www.teknisi-indonesia.com

D D

4

3

2

1

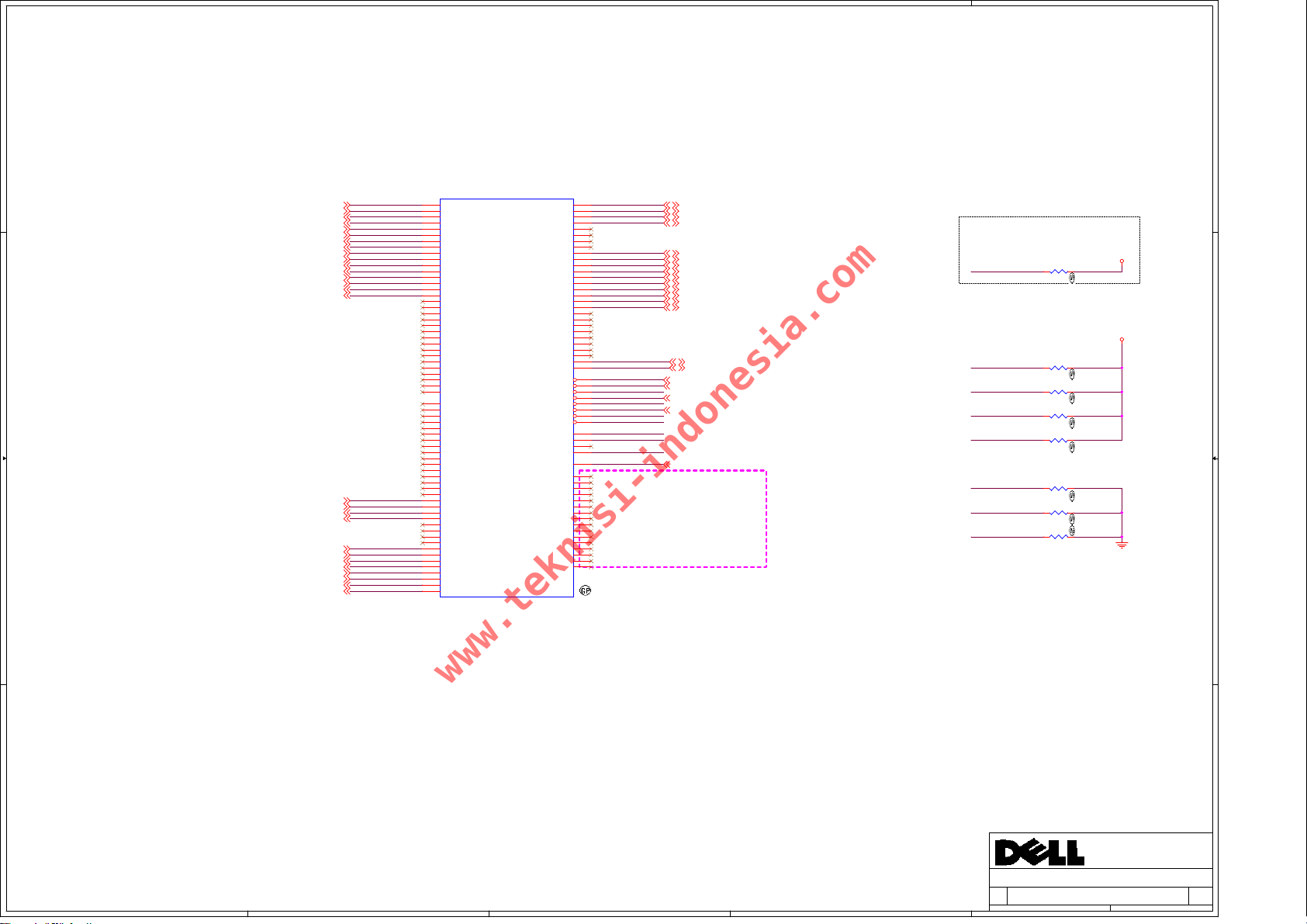

CPU1C

PEG_RX_CPU_P0[93]

PEG_RX_CPU_N0[93]

PEG_RX_CPU_P1[93]

PEG_RX_CPU_N1[93]

PEG_RX_CPU_P2[93]

PEG_RX_CPU_N2[93]

PEG_RX_CPU_P3[93]

PEG_RX_CPU_N3[93]

PEG_RX_CPU_P4[93]

PEG_RX_CPU_N4[93]

PEG_RX_CPU_P5[93]

PEG_RX_CPU_N5[93]

C C

0D95V_CPU_VCCIO

B B

R301 24D9R2F-L-GP

1 2

PEG_RX_CPU_P6[93]

PEG_RX_CPU_N6[93]

PEG_RX_CPU_P7[93]

PEG_RX_CPU_N7[93]

PEG_RX_CPU_P8[93]

PEG_RX_CPU_N8[93]

PEG_RX_CPU_P9[93]

PEG_RX_CPU_N9[93]

PEG_RX_CPU_P10[93]

PEG_RX_CPU_N10[93]

PEG_RX_CPU_P11[93]

PEG_RX_CPU_N11[93]

PEG_RX_CPU_P12[93]

PEG_RX_CPU_N12[93]

PEG_RX_CPU_P13[93]

PEG_RX_CPU_N13[93]

PEG_RX_CPU_P14[93]

PEG_RX_CPU_N14[93]

PEG_RX_CPU_P15[93]

PEG_RX_CPU_N15[93]

DMI_RX_CPU_P0[16]

DMI_RX_CPU_N0[16]

DMI_RX_CPU_P1[16]

DMI_RX_CPU_N1[16]

DMI_RX_CPU_P2[16]

DMI_RX_CPU_N2[16]

DMI_RX_CPU_P3[16]

DMI_RX_CPU_N3[16]

PEG_RX_CPU_P0

PEG_RX_CPU_N0

PEG_RX_CPU_P1

PEG_RX_CPU_N1

PEG_RX_CPU_P2

PEG_RX_CPU_N2

PEG_RX_CPU_P3

PEG_RX_CPU_N3

PEG_RX_CPU_P4

PEG_RX_CPU_N4

PEG_RX_CPU_P5

PEG_RX_CPU_N5

PEG_RX_CPU_P6

PEG_RX_CPU_N6

PEG_RX_CPU_P7

PEG_RX_CPU_N7

PEG_RX_CPU_P8

PEG_RX_CPU_N8

PEG_RX_CPU_P9

PEG_RX_CPU_N9

PEG_RX_CPU_P10

PEG_RX_CPU_N10

PEG_RX_CPU_P11

PEG_RX_CPU_N11

PEG_RX_CPU_P12

PEG_RX_CPU_N12

PEG_RX_CPU_P13

PEG_RX_CPU_N13

PEG_RX_CPU_P14

PEG_RX_CPU_N14

PEG_RX_CPU_P15

PEG_RX_CPU_N15

PEG_RCOMP_CPU

DMI_RX_CPU_P0

DMI_RX_CPU_N0

DMI_RX_CPU_P1

DMI_RX_CPU_N1

DMI_RX_CPU_P2

DMI_RX_CPU_N2

DMI_RX_CPU_P3

DMI_RX_CPU_N3

B8

B7

C7

C6

D6

D5

E5

E4

F6

F5

G5

G4

H6

H5

J5

J4

K6

K5

L5

L4

M6

M5

N5

N4

P6

P5

R5

R4

T6

T5

U5

U4

L7

Y3

Y4

AA4

AA5

AB4

AB3

AC4

AC5

Lake-S

PEG_RXP_0

PEG_RXN_0

PEG_RXP_1

PEG_RXN_1

PEG_RXP_2

PEG_RXN_2

PEG_RXP_3

PEG_RXN_3

PEG_RXP_4

PEG_RXN_4

PEG_RXP_5

PEG_RXN_5

PEG_RXP_6

PEG_RXN_6

PEG_RXP_7

PEG_RXN_7

PEG_RXP_8

PEG_RXN_8

PEG_RXP_9

PEG_RXN_9

PEG_RXP_10

PEG_RXN_10

PEG_RXP_11

PEG_RXN_11

PEG_RXP_12

PEG_RXN_12

PEG_RXP_13

PEG_RXN_13

PEG_RXP_14

PEG_RXN_14

PEG_RXP_15

PEG_RXN_15

PEG_RCOMP

DMI_RXP_0

DMI_RXN_0

DMI_RXP_1

DMI_RXN_1

DMI_RXP_2

DMI_RXN_2

DMI_RXP_3

DMI_RXN_3

SKYLAKE-1,SKL-S,LAKE-S

3 OF 12

PEG_TXP_0

PEG_TXN_0

PEG_TXP_1

PEG_TXN_1

PEG_TXP_2

PEG_TXN_2

PEG_TXP_3

PEG_TXN_3

PEG_TXP_4

PEG_TXN_4

PEG_TXP_5

PEG_TXN_5

PEG_TXP_6

PEG_TXN_6

PEG_TXP_7

PEG_TXN_7

PEG_TXP_8

PEG_TXN_8

PEG_TXP_9

PEG_TXN_9

PEG_TXP_10

PEG_TXN_10

PEG_TXP_11

PEG_TXN_11

PEG_TXP_12

PEG_TXN_12

PEG_TXP_13

PEG_TXN_13

PEG_TXP_14

PEG_TXN_14

PEG_TXP_15

PEG_TXN_15

DMI_TXP_0

DMI_TXN_0

DMI_TXP_1

DMI_TXN_1

DMI_TXP_2

DMI_TXN_2

DMI_TXP_3

DMI_TXN_3

A5

A6

B4

B5

C3

C4

D2

D3

E1

E2

F2

F3

G1

G2

H2

H3

J1

J2

K2

K3

L1

L2

M2

M3

N1

N2

P2

P3

R2

R1

T2

T3

AC2

AC1

AD3

AD2

AE2

AE1

AF2

AF3

PEG_TX_CPU_P0

PEG_TX_CPU_N0

PEG_TX_CPU_P1

PEG_TX_CPU_N1

PEG_TX_CPU_P2

PEG_TX_CPU_N2

PEG_TX_CPU_P3

PEG_TX_CPU_N3

PEG_TX_CPU_P4

PEG_TX_CPU_N4

PEG_TX_CPU_P5

PEG_TX_CPU_N5

PEG_TX_CPU_P6

PEG_TX_CPU_N6

PEG_TX_CPU_P7

PEG_TX_CPU_N7

PEG_TX_CPU_P8

PEG_TX_CPU_N8

PEG_TX_CPU_P9

PEG_TX_CPU_N9

PEG_TX_CPU_P10

PEG_TX_CPU_N10

PEG_TX_CPU_P11

PEG_TX_CPU_N11

PEG_TX_CPU_P12

PEG_TX_CPU_N12

PEG_TX_CPU_P13

PEG_TX_CPU_N13

PEG_TX_CPU_P14

PEG_TX_CPU_N14

PEG_TX_CPU_P15

PEG_TX_CPU_N15

DMI_TX_CPU_P0

DMI_TX_CPU_N0

DMI_TX_CPU_P1

DMI_TX_CPU_N1

DMI_TX_CPU_P2

DMI_TX_CPU_N2

DMI_TX_CPU_P3

DMI_TX_CPU_N3

PEG_TX_CPU_P0 [93]

PEG_TX_CPU_N0 [93]

PEG_TX_CPU_P1 [93]

PEG_TX_CPU_N1 [93]

PEG_TX_CPU_P2 [93]

PEG_TX_CPU_N2 [93]

PEG_TX_CPU_P3 [93]

PEG_TX_CPU_N3 [93]

PEG_TX_CPU_P4 [93]

PEG_TX_CPU_N4 [93]

PEG_TX_CPU_P5 [93]

PEG_TX_CPU_N5 [93]

PEG_TX_CPU_P6 [93]

PEG_TX_CPU_N6 [93]

PEG_TX_CPU_P7 [93]

PEG_TX_CPU_N7 [93]

PEG_TX_CPU_P8 [93]

PEG_TX_CPU_N8 [93]

PEG_TX_CPU_P9 [93]

PEG_TX_CPU_N9 [93]

PEG_TX_CPU_P10 [93]

PEG_TX_CPU_N10 [93]

PEG_TX_CPU_P11 [93]

PEG_TX_CPU_N11 [93]

PEG_TX_CPU_P12 [93]

PEG_TX_CPU_N12 [93]

PEG_TX_CPU_P13 [93]

PEG_TX_CPU_N13 [93]

PEG_TX_CPU_P14 [93]

PEG_TX_CPU_N14 [93]

PEG_TX_CPU_P15 [93]

PEG_TX_CPU_N15 [93]

DMI_TX_CPU_P0 [16]

DMI_TX_CPU_N0 [16]

DMI_TX_CPU_P1 [16]

DMI_TX_CPU_N1 [16]

DMI_TX_CPU_P2 [16]

DMI_TX_CPU_N2 [16]

DMI_TX_CPU_P3 [16]

DMI_TX_CPU_N3 [16]

SKYLAKE SOCKET

SKT301

Load Plate

(22.78003.021)

SKT303

ILMCOVER

(22.78005.281)

SKT302

Back Plate

(22.78006.031)

SKT304

ASSY BACK PLATE

(60.3EQ19.002)

PCH HSINK D7 AURAS

(R_)

A A

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

3 107Friday, February 02, 2018

3 107Friday, February 02, 2018

1

3 107Friday, February 02, 2018

A00C

A00C

A00C

5

4

3

Title

Title

Title

CPU_(PCIE/DMI)

CPU_(PCIE/DMI)

CPU_(PCIE/DMI)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Gambits MLK SFF

Gambits MLK SFF

Gambits MLK SFF

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

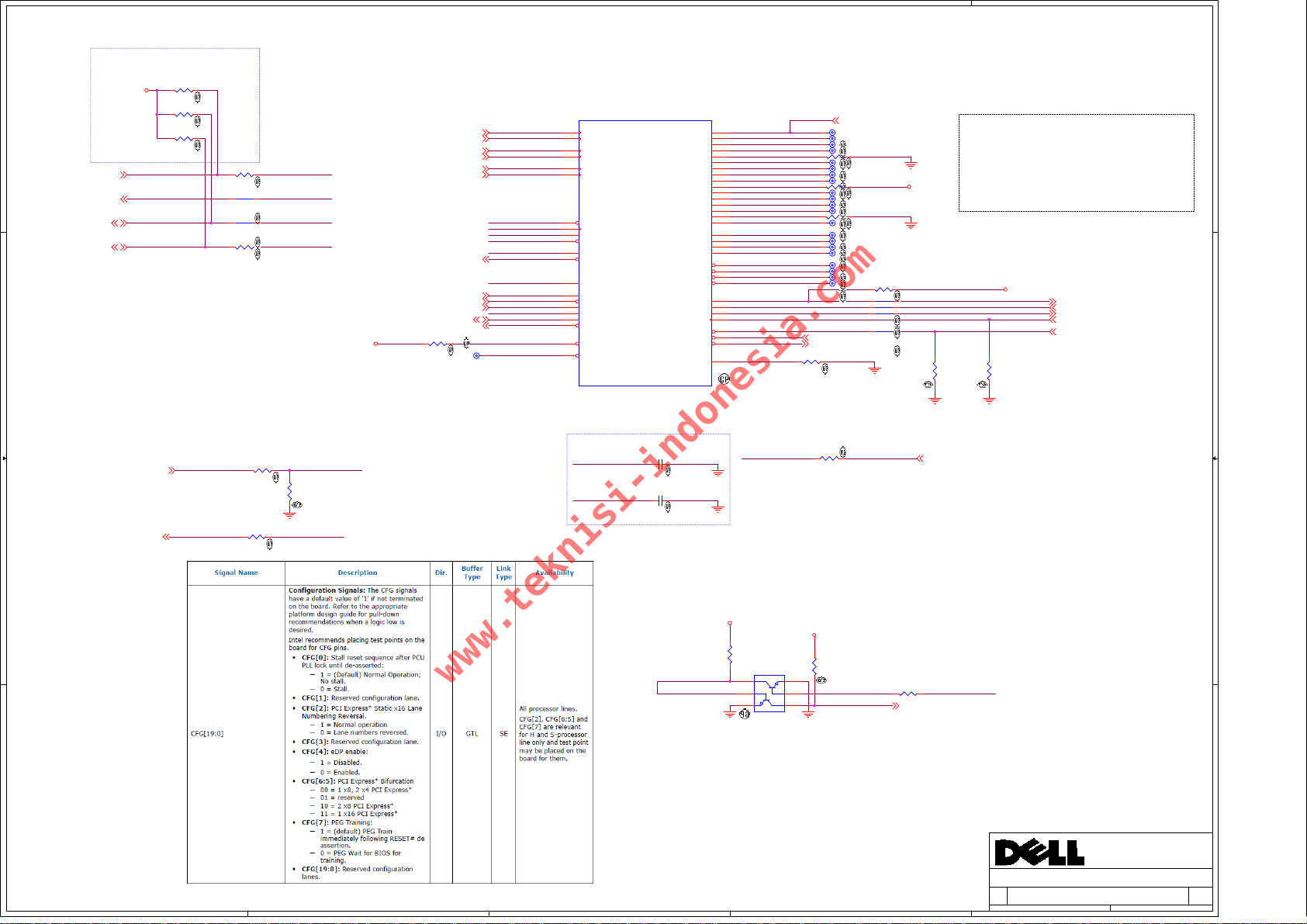

5

www.teknisi-indonesia.com

4

3

2

1

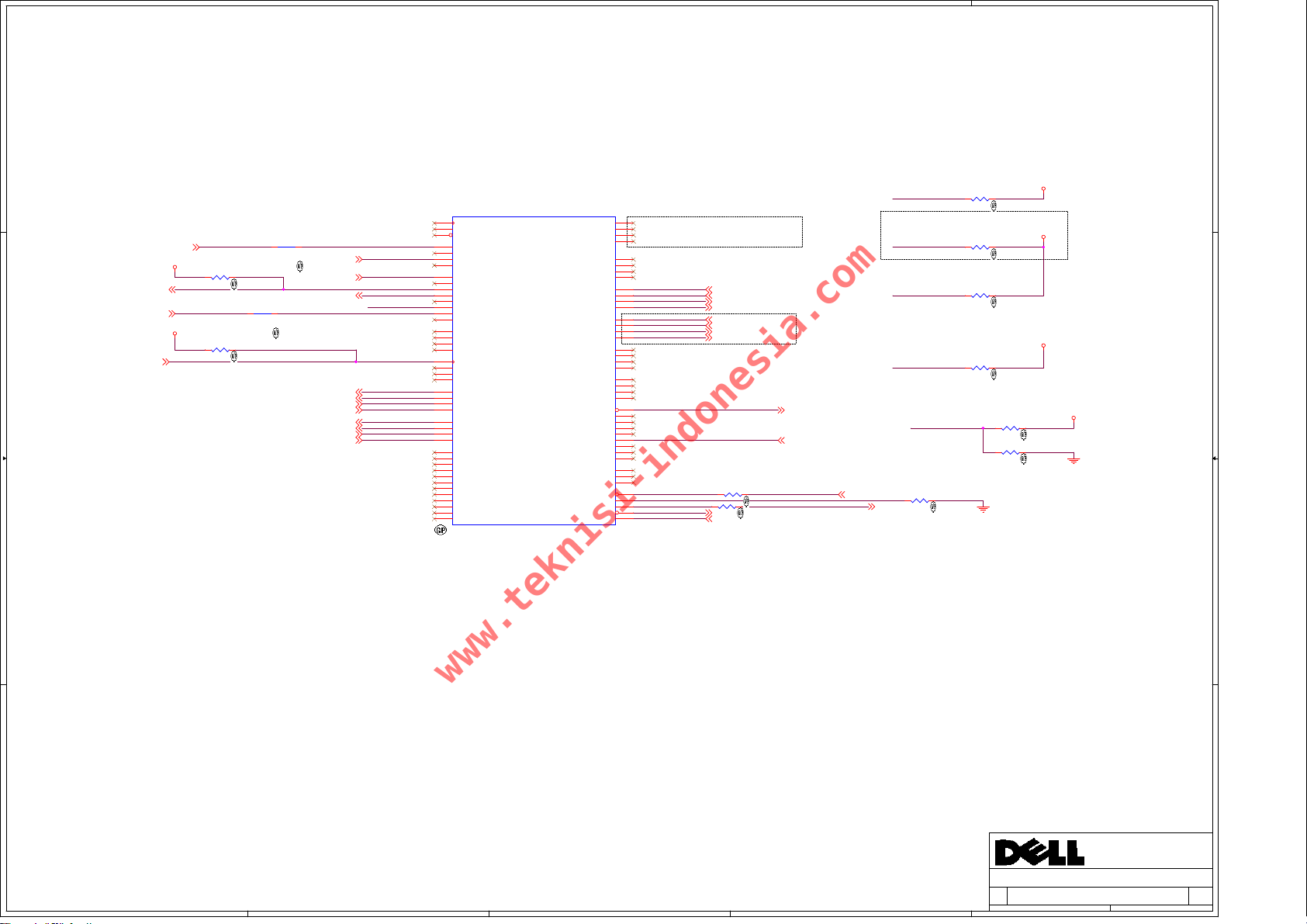

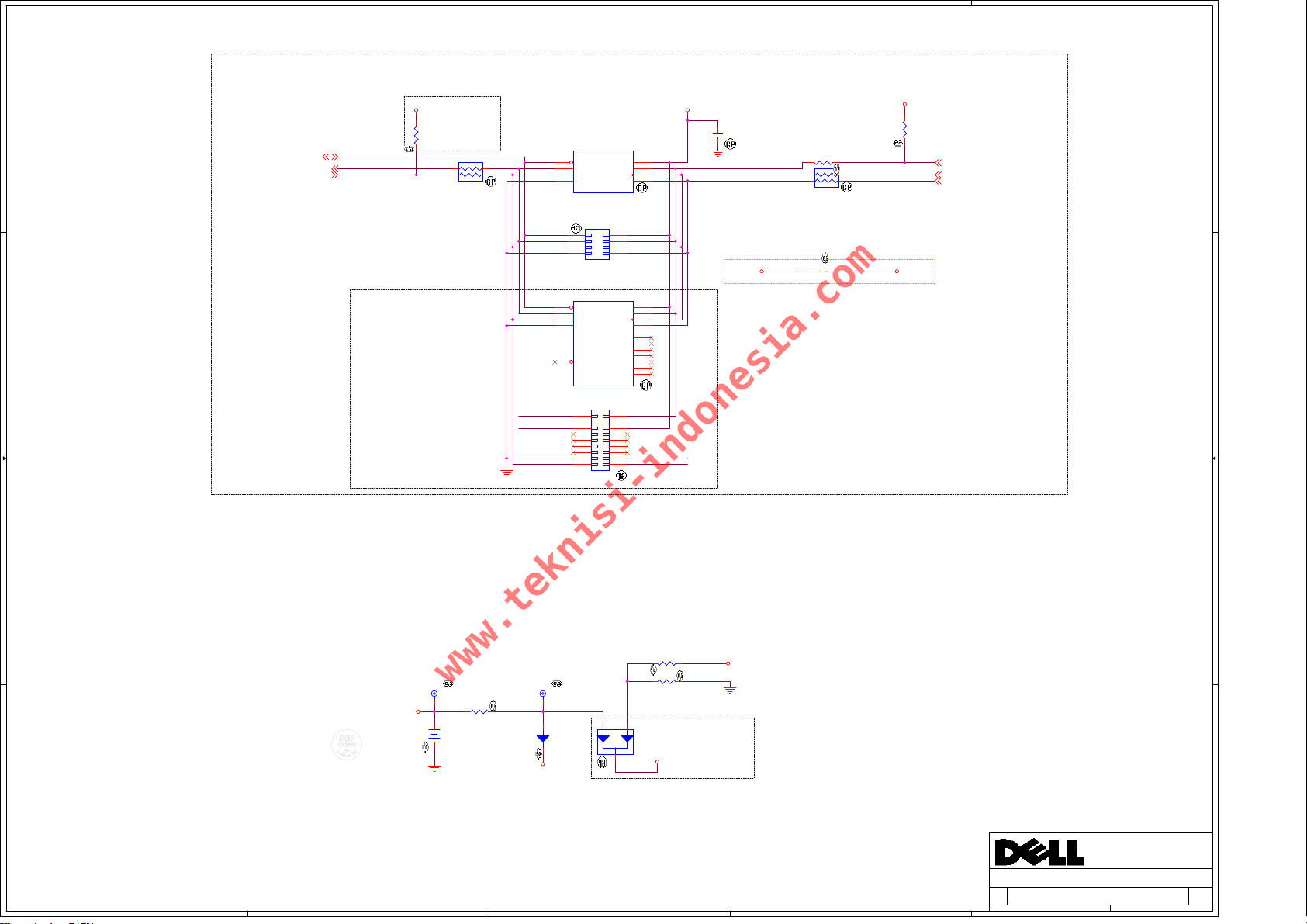

PLACE NEAR CPU

R401 56D2R2F-GP

V_CPU_ST_PLL

D D

VIDSOUT_CPU_R[44]

PROCHOT#_CPU_R[24,44]

C C

20170417

add R2422

VIDALERT#_CPU_R[44]

VIDSCK_CPU_R[44]

VCCST_GD_DRIVER[40,99]

PM_DOWN_PCH[17]

1 2

R403 100R2F-L1-GP-U

1 2

R404 1KR2F-3-GP

1 2

VIDALERT#_CPU_R

VIDSCK_CPU_R

VIDSOUT_CPU_R

PROCHOT#_CPU_R

VCCST_GD_DRIVER

R405 220R2F-GP

VIDALERT#_CPU

1 2

R407 0R0402-PAD-2-GP

VIDSCK_CPU

1 2

R408 0R0402-PAD-2-GP

VIDSOUT_CPU

1 2

R409 499R2F-2-GP

PROCHOT#_CPU

1 2

R419 6K04R2F-GP

1 2

R421 20R2F-GP

PM_DOWN_CPUPM_DOWN_PCH

1 2

VCCST_GD_CPU

12

R420

2K8R2F-GP

0D95V_CPU_VCCIO

PCH_CPU_BCLK_DP[18]

PCH_CPU_BCLK_DN[18]

PCH_CPU_PCIBCLK_DP[18]

PCH_CPU_PCIBCLK_DN[18]

PCH_CPU_NSSC_CLK_DP[18]

PCH_CPU_NSSC_CLK_DN[18]

H_SKTOCC_CPU[24]

H_PWRGD[20,99]

PLTRST_CPU_N[17,99]

PM_SYNC_CPU[17]

PECI_CPU[24]

THERMTRIP#_CPU[17]

1 2

R422 10KR2J-3-GP

(R_)

TP403

PCH_CPU_BCLK_DP

PCH_CPU_BCLK_DN

PCH_CPU_PCIBCLK_DP

PCH_CPU_PCIBCLK_DN

PCH_CPU_NSSC_CLK_DP

PCH_CPU_NSSC_CLK_DN

VIDALERT#_CPU

VIDSCK_CPU

VIDSOUT_CPU

PROCHOT#_CPU

SM_PGCNTL

H_SKTOCC_CPU

VCCST_GD_CPU

H_PWRGD

PLTRST_CPU_N

PM_SYNC_CPU

PM_DOWN_CPU

PECI_CPU

THERMTRIP#_CPU

SKL_CNL_N

CATERR#_CPU

1

CPU1E

W5

BCLKP

W4

BCLKN

W1

PCI_BCLKP

W2

PCI_BCLKN

K9

CLK24P

J9

CLK24N

E39

VIDALERT#

E38

VIDSCK

E40

VIDSOUT

C39

PROCHOT#

AC36

DDR_VTT_CNTL

AC38

SKTOCC#

U2

VCCST_PWRGD

F8

PROCPWRGD

E7

RESET#

E8

PM_SYNC

D8

PM_DOWN

G7

PECI

D11

THERMTRIP#

AB36

PROC_SELECT#

D13

CATERR#

SKYLAKE-1,SKL-S,LAKE-S

For EMI

H_PWRGD

PLTRST_CPU_N

Lake-S

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST#

PROC_PREQ#

PROC_PRDY#

CFG_RCOMP

C402 SCD1U16V2KX-L-GP

1 2

(R_)

C403 SCD1U16V2KX-L-GP

1 2

(R_)

5 OF 12

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_17

CFG_16

CFG_19

CFG_18

BPM#_0

BPM#_1

BPM#_2

BPM#_3

SKL_PCUDEBUG_0

H15

SKL_PCUDEBUG_1

F15

SKL_PCUDEBUG_2

F16

SKL_PCUDEBUG_3

H16

SKL_PCUDEBUG_4

F19

SKL_PCUDEBUG_5

H18

SKL_PCUDEBUG_6

G21

SKL_PCUDEBUG_7

H20

SKL_PCUDEBUG_8

G16

SKL_PCUDEBUG_9

E16

SKL_PCUDEBUG_10

F17

SKL_PCUDEBUG_11

H17

SKL_PCUDEBUG_12

G20

SKL_PCUDEBUG_13

F20

SKL_PCUDEBUG_14

F21

SKL_PCUDEBUG_15

H19

SKL_PCUSTB_0_DP

F14

SKL_PCUSTB_0_DN

E14

SKL_PCUSTB_1_DP

F18

SKL_PCUSTB_1_DN

G18

BPM_CPU_N0

D16

BPM_CPU_N1

D17

BPM_CPU_N2

G14

BPM_CPU_N3

H14

H_TDO

H13

H_TDI

G12

H_TMS

F13

H_TCK

F11

H_TRST_N

F12

H_PREQ_N

B9

H_PRDY_N

B10

TPEV_CFG_RCOMP

M11

SKL_PCUDEBUG_3 XDP_PCUDEBUG_3

1

1

1

1

1 2

R424 1KR2J-1-GP

1

1

1

1

1 2

R425 1KR2J-1-GP (R_)

1

1

1

1

1 2

R426 1KR2J-1-GP (R_)

1

1

1

1

1

1

1

1

1

H_TDO

H_PREQ_N [99]

H_PRDY_N [99]

R418 49D9R2F-GP

1 2

R423

1K5R2F-2-GP

1 2

SKL_PCUDEBUG_0 [99]

TP404

TP405

TP406

TP407

TP408

TP409

TP410

TP411

TP412

TP413

TP414

TP415

TP416

TP419

TP420

TP421

TP422

TP417

TP418

TP401

TP402

R402 100R2F-L1-GP-U

R410 0R0402-PAD-2-GP

R411 0R0402-PAD-2-GP

R412 0R0402-PAD-2-GP

R417 0R0402-PAD-2-GP

1 2

1 2

1 2

1 2

1 2

0D95V_CPU_VCCIO

XDP_PCUDEBUG_3 [99]

12

R427

51R2F-2-GP

(R_)

12

V_CPU_ST_PLL

PCH_JTAG_TDO

PCH_JTAG_TDI

PCH_JTAG_TMS

H_TRST_N_R

R415

51R2F-2-GP

20170607

Remove R406 & C401

PCH_JTAG_TDO [20]

PCH_JTAG_TDI [20]

PCH_JTAG_TMS [20]

H_TCK [20]

H_TRST_N_R [22]

B B

3D3V_SB

12

R413

10KR2J-3-GP

DDR_VTT_CNTL_GATE

A A

5

4

3

U401

6

5

4

MMDT3904-2-GP

3D3V_SB

12

R414

100KR2J-1-GP

1

DDR_VTT_CNTL_R SM_PGCNTL

2

DDR_VTT_CNTL_CPU

3

2

R416 10KR2J-3-GP

1 2

DDR_VTT_CNTL_CPU [40]

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU_(THERMAL/CLOCK/PM/CFG)

CPU_(THERMAL/CLOCK/PM/CFG)

CPU_(THERMAL/CLOCK/PM/CFG)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Gambits MLK SFF

Gambits MLK SFF

Gambits MLK SFF

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

4 107Friday, February 02, 2018

4 107Friday, February 02, 2018

1

4 107Friday, February 02, 2018

A00C

A00C

A00C

5

www.teknisi-indonesia.com

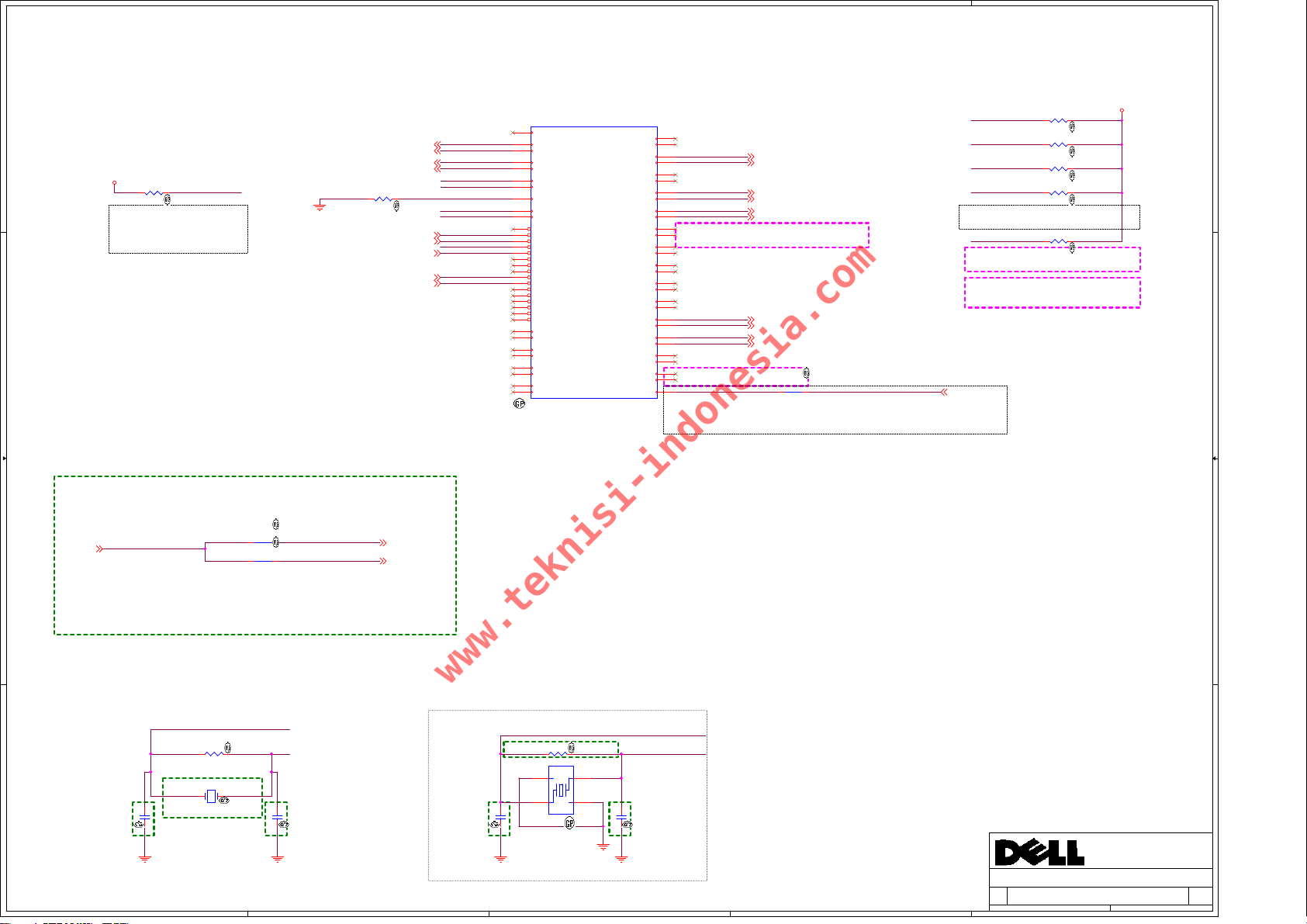

D D

4

3

2

1

M_A_DQ[0..63][11]

C C

B B

M_A_DQ5

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ0

M_A_DQ6

M_A_DQ7

M_A_DQ13

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ8

M_A_DQ12

M_A_DQ14

M_A_DQ15

M_A_DQ21

M_A_DQ16

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ17

M_A_DQ22

M_A_DQ23

M_A_DQ25

M_A_DQ28

M_A_DQ27

M_A_DQ31

M_A_DQ29

M_A_DQ24

M_A_DQ30

M_A_DQ26

M_A_DQ32

M_A_DQ36

M_A_DQ34

M_A_DQ35

M_A_DQ33

M_A_DQ37

M_A_DQ39

M_A_DQ38

M_A_DQ44

M_A_DQ40

M_A_DQ47

M_A_DQ43

M_A_DQ41

M_A_DQ45

M_A_DQ46

M_A_DQ42

M_A_DQ49

M_A_DQ54

M_A_DQ53

M_A_DQ50

M_A_DQ52

M_A_DQ51

M_A_DQ48

M_A_DQ55

M_A_DQ61

M_A_DQ63

M_A_DQ60

M_A_DQ59

M_A_DQ62

M_A_DQ57

M_A_DQ58

M_A_DQ56

CPU1A

AE38

DDR0_DQ_0/DDR0_DQ_0

AE37

DDR0_DQ_1/DDR0_DQ_1

AG38

DDR0_DQ_2/DDR0_DQ_2

AG37

DDR0_DQ_3/DDR0_DQ_3

AE39

DDR0_DQ_4/DDR0_DQ_4

AE40

DDR0_DQ_5/DDR0_DQ_5

AG39

DDR0_DQ_6/DDR0_DQ_6

AG40

DDR0_DQ_7/DDR0_DQ_7

AJ38

DDR0_DQ_8/DDR0_DQ_8

AJ37

DDR0_DQ_9/DDR0_DQ_9

AL38

DDR0_DQ_10/DDR0_DQ_10

AL37

DDR0_DQ_11/DDR0_DQ_11

AJ40

DDR0_DQ_12/DDR0_DQ_12

AJ39

DDR0_DQ_13/DDR0_DQ_13

AL39

DDR0_DQ_14/DDR0_DQ_14

AL40

DDR0_DQ_15/DDR0_DQ_15

AN38

DDR0_DQ_16/DDR0_DQ_32

AN40

DDR0_DQ_17/DDR0_DQ_33

AR38

DDR0_DQ_18/DDR0_DQ_34

AR37

DDR0_DQ_19/DDR0_DQ_35

AN39

DDR0_DQ_20/DDR0_DQ_36

AN37

DDR0_DQ_21/DDR0_DQ_37

AR39

DDR0_DQ_22/DDR0_DQ_38

AR40

DDR0_DQ_23/DDR0_DQ_39

AW37

DDR0_DQ_24/DDR0_DQ_40

AU38

DDR0_DQ_25/DDR0_DQ_41

AV35

DDR0_DQ_26/DDR0_DQ_42

AW35

DDR0_DQ_27/DDR0_DQ_43

AU37

DDR0_DQ_28/DDR0_DQ_44

AV37

DDR0_DQ_29/DDR0_DQ_45

AT35

DDR0_DQ_30/DDR0_DQ_46

AU35

DDR0_DQ_31/DDR0_DQ_47

AY8

DDR0_DQ_32/DDR1_DQ_0

AW8

DDR0_DQ_33/DDR1_DQ_1

AV6

DDR0_DQ_34/DDR1_DQ_2

AU6

DDR0_DQ_35/DDR1_DQ_3

AU8

DDR0_DQ_36/DDR1_DQ_4

AV8

DDR0_DQ_37/DDR1_DQ_5

AW6

DDR0_DQ_38/DDR1_DQ_6

AY6

DDR0_DQ_39/DDR1_DQ_7

AY4

DDR0_DQ_40/DDR1_DQ_8

AV4

DDR0_DQ_41/DDR1_DQ_9

AT1

DDR0_DQ_42/DDR1_DQ_10

AT2

DDR0_DQ_43/DDR1_DQ_11

AV3

DDR0_DQ_44/DDR1_DQ_12

AW4

DDR0_DQ_45/DDR1_DQ_13

AT4

DDR0_DQ_46/DDR1_DQ_14

AT3

DDR0_DQ_47/DDR1_DQ_15

AP2

DDR0_DQ_48/DDR1_DQ_32

AM4

DDR0_DQ_49/DDR1_DQ_33

AP3

DDR0_DQ_50/DDR1_DQ_34

AM3

DDR0_DQ_51/DDR1_DQ_35

AP4

DDR0_DQ_52/DDR1_DQ_36

AM2

DDR0_DQ_53/DDR1_DQ_37

AP1

DDR0_DQ_54/DDR1_DQ_38

AM1

DDR0_DQ_55/DDR1_DQ_39

AK3

DDR0_DQ_56/DDR1_DQ_40

AH1

DDR0_DQ_57/DDR1_DQ_41

AK4

DDR0_DQ_58/DDR1_DQ_42

AH2

DDR0_DQ_59/DDR1_DQ_43

AH4

DDR0_DQ_60/DDR1_DQ_44

AK2

DDR0_DQ_61/DDR1_DQ_45

AH3

DDR0_DQ_62/DDR1_DQ_46

AK1

DDR0_DQ_63/DDR1_DQ_47

AU33

DDR0_ECC_0

AT33

DDR0_ECC_1

AW33

DDR0_ECC_2

AV31

DDR0_ECC_3

AU31

DDR0_ECC_4

AV33

DDR0_ECC_5

AW31

DDR0_ECC_6

AY31

DDR0_ECC_7

Lake-S

DDR0_DQSN_0/DDR0_DQSN_0

DDR0_DQSN_1/DDR0_DQSN_1

DDR0_DQSN_2/DDR0_DQSN_4

DDR0_DQSN_3/DDR0_DQSN_5

DDR0_DQSN_4/DDR1_DQSN_0

DDR0_DQSN_5/DDR1_DQSN_1

DDR0_DQSN_6/DDR1_DQSN_4

DDR0_DQSN_7/DDR1_DQSN_5

DDR0_DQSP_0/DDR0_DQSP_0

DDR0_DQSP_1/DDR0_DQSP_1

DDR0_DQSP_2/DDR0_DQSP_4

DDR0_DQSP_3/DDR0_DQSP_5

DDR0_DQSP_4/DDR1_DQSP_0

DDR0_DQSP_5/DDR1_DQSP_1

DDR0_DQSP_6/DDR1_DQSP_4

DDR0_DQSP_7/DDR1_DQSP_5

DDR0_DQSP_8/DDR0_DQSP_8

DDR0_DQSN_8/DDR0_DQSN_8

1 OF 12

DDR0_CKP_0

DDR0_CKN_0

DDR0_CKP_1

DDR0_CKN_1

DDR0_CKP_2

DDR0_CKN_2

DDR0_CKP_3

DDR0_CKN_3

DDR0_CKE_0

DDR0_CKE_1

DDR0_CKE_2

DDR0_CKE_3

DDR0_CS#_0

DDR0_CS#_1

DDR0_CS#_2

DDR0_CS#_3

DDR0_ODT_0

DDR0_ODT_1

DDR0_ODT_2

DDR0_ODT_3

DDR0_BA_0

DDR0_BA_1

DDR0_BG_0

DDR0_MA_16

DDR0_MA_14

DDR0_MA_15

DDR0_MA_0

DDR0_MA_1

DDR0_MA_2

DDR0_MA_3

DDR0_MA_4

DDR0_MA_5

DDR0_MA_6

DDR0_MA_7

DDR0_MA_8

DDR0_MA_9

DDR0_MA_10

DDR0_MA_11

DDR0_MA_12

DDR0_MA_13

DDR0_BG_1

DDR0_ACT#

DDR0_PAR

DDR0_ALERT#

AW18

AV18

AW17

AY17

AW16

AV16

AT16

AU16

AY24

AW24

AV24

AV25

AW12

AU11

AV13

AV10

AW11

AU14

AU12

AY10

AY13

AV15

AW23

AW13

AV14

AY11

AW15

AU18

AU17

AV19

AT19

AU20

AV20

AU21

AT20

AT22

AY14

AU22

AV22

AV12

AV23

AU24

AY15

AT23

AF39

AK39

AP39

AU36

AW7

AU3

AN3

AJ3

AF38

AK38

AP38

AV36

AV7

AU2

AN2

AJ2

AV32

AU32

M_A_CLK0

M_A_CLK#0

M_A_CLK1

M_A_CLK#1

M_A_CKE0

M_A_CKE1

M_A_CS#0

M_A_CS#1

M_A_ODT0

M_A_ODT1

M_A_BS0

M_A_BS1

M_A_BG0

M_A_A16

M_A_A14

M_A_A15

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_BG1

M_A_ACT#

M_A_PARITY

M_A_ALERT#

M_A_DQS_DN0

M_A_DQS_DN1

M_A_DQS_DN2

M_A_DQS_DN3

M_A_DQS_DN4

M_A_DQS_DN5

M_A_DQS_DN6

M_A_DQS_DN7

M_A_DQS_DP0

M_A_DQS_DP1

M_A_DQS_DP2

M_A_DQS_DP3

M_A_DQS_DP4

M_A_DQS_DP5

M_A_DQS_DP6

M_A_DQS_DP7

M_A_CLK0 [11]

M_A_CLK#0 [11]

M_A_CLK1 [11]

M_A_CLK#1 [11]

M_A_CKE0 [11]

M_A_CKE1 [11]

M_A_CS#0 [11]

M_A_CS#1 [11]

M_A_ODT0 [11]

M_A_ODT1 [11]

M_A_BS0 [11]

M_A_BS1 [11]

M_A_BG0 [11]

M_A_A16 [11]

M_A_A14 [11]

M_A_A15 [11]

M_A_A0 [11]

M_A_A1 [11]

M_A_A2 [11]

M_A_A3 [11]

M_A_A4 [11]

M_A_A5 [11]

M_A_A6 [11]

M_A_A7 [11]

M_A_A8 [11]

M_A_A9 [11]

M_A_A10 [11]

M_A_A11 [11]

M_A_A12 [11]

M_A_A13 [11]

M_A_BG1 [11]

M_A_ACT# [11]

M_A_PARITY [11]

M_A_ALERT# [11]

M_A_DQS_DN0 [11]

M_A_DQS_DN1 [11]

M_A_DQS_DN2 [11]

M_A_DQS_DN3 [11]

M_A_DQS_DN4 [11]

M_A_DQS_DN5 [11]

M_A_DQS_DN6 [11]

M_A_DQS_DN7 [11]

M_A_DQS_DP0 [11]

M_A_DQS_DP1 [11]

M_A_DQS_DP2 [11]

M_A_DQS_DP3 [11]

M_A_DQS_DP4 [11]

M_A_DQS_DP5 [11]

M_A_DQS_DP6 [11]

M_A_DQS_DP7 [11]

DDR CHANNEL A

SKYLAKE-1,SKL-S,LAKE-S

A A

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

5 107Friday, February 02, 2018

5 107Friday, February 02, 2018

1

5 107Friday, February 02, 2018

A00C

A00C

A00C

5

4

3

Title

Title

Title

CPU_(DDR_CHA)

CPU_(DDR_CHA)

CPU_(DDR_CHA)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Gambits MLK SFF

Gambits MLK SFF

Gambits MLK SFF

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

5

www.teknisi-indonesia.com

D D

C C

B B

4

M_B_DQ[0..63][12]

M_B_DQ4

M_B_DQ5

M_B_DQ7

M_B_DQ3

M_B_DQ1

M_B_DQ0

M_B_DQ6

M_B_DQ2

M_B_DQ13

M_B_DQ9

M_B_DQ14

M_B_DQ15

M_B_DQ12

M_B_DQ8

M_B_DQ10

M_B_DQ11

M_B_DQ16

M_B_DQ20

M_B_DQ22

M_B_DQ23

M_B_DQ17

M_B_DQ21

M_B_DQ18

M_B_DQ19

M_B_DQ28

M_B_DQ24

M_B_DQ30

M_B_DQ26

M_B_DQ25

M_B_DQ29

M_B_DQ27

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ38

M_B_DQ34

M_B_DQ36

M_B_DQ37

M_B_DQ39

M_B_DQ35

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ42

M_B_DQ41

M_B_DQ40

M_B_DQ47

M_B_DQ43

M_B_DQ52

M_B_DQ53

M_B_DQ55

M_B_DQ51

M_B_DQ48

M_B_DQ49

M_B_DQ54

M_B_DQ50

M_B_DQ61

M_B_DQ56

M_B_DQ63

M_B_DQ58

M_B_DQ60

M_B_DQ57

M_B_DQ59

M_B_DQ62

CPU1B

AD34

DDR1_DQ_0/DDR0_DQ_16

AD35

DDR1_DQ_1/DDR0_DQ_17

AG35

DDR1_DQ_2/DDR0_DQ_18

AH35

DDR1_DQ_3/DDR0_DQ_19

AE35

DDR1_DQ_4/DDR0_DQ_20

AE34

DDR1_DQ_5/DDR0_DQ_21

AG34

DDR1_DQ_6/DDR0_DQ_22

AH34

DDR1_DQ_7/DDR0_DQ_23

AK35

DDR1_DQ_8/DDR0_DQ_24

AL35

DDR1_DQ_9/DDR0_DQ_25

AK32

DDR1_DQ_10/DDR0_DQ_26

AL32

DDR1_DQ_11/DDR0_DQ_27

AK34

DDR1_DQ_12/DDR0_DQ_28

AL34

DDR1_DQ_13/DDR0_DQ_29

AK31

DDR1_DQ_14/DDR0_DQ_30

AL31

DDR1_DQ_15/DDR0_DQ_31

AP35

DDR1_DQ_16/DDR0_DQ_48

AN35

DDR1_DQ_17/DDR0_DQ_49

AN32

DDR1_DQ_18/DDR0_DQ_50

AP32

DDR1_DQ_19/DDR0_DQ_51

AN34

DDR1_DQ_20/DDR0_DQ_52

AP34

DDR1_DQ_21/DDR0_DQ_53

AN31

DDR1_DQ_22/DDR0_DQ_54

AP31

DDR1_DQ_23/DDR0_DQ_55

AL29

DDR1_DQ_24/DDR0_DQ_56

AM29

DDR1_DQ_25/DDR0_DQ_57

AP29

DDR1_DQ_26/DDR0_DQ_58

AR29

DDR1_DQ_27/DDR0_DQ_59

AM28

DDR1_DQ_28/DDR0_DQ_60

AL28

DDR1_DQ_29/DDR0_DQ_61

AR28

DDR1_DQ_30/DDR0_DQ_62

AP28

DDR1_DQ_31/DDR0_DQ_63

AR12

DDR1_DQ_32/DDR1_DQ_16

AP12

DDR1_DQ_33/DDR1_DQ_17

AM13

DDR1_DQ_34/DDR1_DQ_18

AL13

DDR1_DQ_35/DDR1_DQ_19

AR13

DDR1_DQ_36/DDR1_DQ_20

AP13

DDR1_DQ_37/DDR1_DQ_21

AM12

DDR1_DQ_38/DDR1_DQ_22

AL12

DDR1_DQ_39/DDR1_DQ_23

AP10

DDR1_DQ_40/DDR1_DQ_24

AR10

DDR1_DQ_41/DDR1_DQ_25

AR7

DDR1_DQ_42/DDR1_DQ_26

AP7

DDR1_DQ_43/DDR1_DQ_27

AR9

DDR1_DQ_44/DDR1_DQ_28

AP9

DDR1_DQ_45/DDR1_DQ_29

AR6

DDR1_DQ_46/DDR1_DQ_30

AP6

DDR1_DQ_47/DDR1_DQ_31

AM10

DDR1_DQ_48/DDR1_DQ_48

AL10

DDR1_DQ_49/DDR1_DQ_49

AM7

DDR1_DQ_50/DDR1_DQ_50

AL7

DDR1_DQ_51/DDR1_DQ_51

AM9

DDR1_DQ_52/DDR1_DQ_52

AL9

DDR1_DQ_53/DDR1_DQ_53

AM6

DDR1_DQ_54/DDR1_DQ_54

AL6

DDR1_DQ_55/DDR1_DQ_55

AJ6

DDR1_DQ_56/DDR1_DQ_56

AJ7

DDR1_DQ_57/DDR1_DQ_57

AE6

DDR1_DQ_58/DDR1_DQ_58

AF7

DDR1_DQ_59/DDR1_DQ_59

AH7

DDR1_DQ_60/DDR1_DQ_60

AH6

DDR1_DQ_61/DDR1_DQ_61

AE7

DDR1_DQ_62/DDR1_DQ_62

AF6

DDR1_DQ_63/DDR1_DQ_63

AR25

DDR1_ECC_0

AR26

DDR1_ECC_1

AM26

DDR1_ECC_2

AM25

DDR1_ECC_3

AP26

DDR1_ECC_4

AP25

DDR1_ECC_5

AL25

DDR1_ECC_6

AL26

DDR1_ECC_7

SKYLAKE-1,SKL-S,LAKE-S

DDR CHANNEL B

3

Lake-S

2 OF 12

DDR1_CKP_0

DDR1_CKN_0

DDR1_CKP_1

DDR1_CKN_1

DDR1_CKP_2

DDR1_CKN_2

DDR1_CKP_3

DDR1_CKN_3

DDR1_CKE_0

DDR1_CKE_1

DDR1_CKE_2

DDR1_CKE_3

DDR1_CS#_0

DDR1_CS#_1

DDR1_CS#_2

DDR1_CS#_3

DDR1_ODT_0

DDR1_ODT_1

DDR1_ODT_2

DDR1_ODT_3

DDR1_MA_16

DDR1_MA_14

DDR1_MA_15

DDR1_BA_0

DDR1_BA_1

DDR1_BG_0

DDR1_MA_0

DDR1_MA_1

DDR1_MA_2

DDR1_MA_3

DDR1_MA_4

DDR1_MA_5

DDR1_MA_6

DDR1_MA_7

DDR1_MA_8

DDR1_MA_9

DDR1_MA_10

DDR1_MA_11

DDR1_MA_12

DDR1_MA_13

DDR1_BG_1

DDR1_ACT#

DDR1_PAR

DDR1_ALERT#

DDR1_DQSN_0/DDR0_DQSN_2

DDR1_DQSN_1/DDR0_DQSN_3

DDR1_DQSN_2/DDR0_DQSN_6

DDR1_DQSN_3/DDR0_DQSN_7

DDR1_DQSN_4/DDR1_DQSN_2

DDR1_DQSN_5/DDR1_DQSN_3

DDR1_DQSN_6/DDR1_DQSN_6

DDR1_DQSN_7/DDR1_DQSN_7

DDR1_DQSP_0/DDR0_DQSP_2

DDR1_DQSP_1/DDR0_DQSP_3

DDR1_DQSP_2/DDR0_DQSP_6

DDR1_DQSP_3/DDR0_DQSP_7

DDR1_DQSP_4/DDR1_DQSP_2

DDR1_DQSP_5/DDR1_DQSP_3

DDR1_DQSP_6/DDR1_DQSP_6

DDR1_DQSP_7/DDR1_DQSP_7

DDR1_DQSP_8/DDR1_DQSP_8

DDR1_DQSN_8/DDR1_DQSN_8

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

AM20

AM21

AP22

AP21

AN20

AN21

AP19

AP20

AY29

AV29

AW29

AU29

AP17

AN15

AN17

AM15

AM16

AL16

AP15

AL15

AN18

AL17

AP16

AL18

AM18

AW28

AL19

AL22

AM22

AM23

AP23

AL23

AW26

AY26

AU26

AW27

AP18

AU27

AV27

AR15

AY28

AU28

AL20

AY25

AF34

AK33

AN33

AN29

AN13

AR8

AM8

AG6

AF35

AL33

AP33

AN28

AN12

AP8

AL8

AG7

AN25

AN26

AB40

AC40

AC39

M_B_CLK0

M_B_CLK#0

M_B_CLK1

M_B_CLK#1

M_B_CKE0

M_B_CKE1

M_B_CS#0

M_B_CS#1

M_B_ODT0

M_B_ODT1

M_B_A16

M_B_A14

M_B_A15

M_B_BS0

M_B_BS1

M_B_BG0

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_BG1

M_B_ACT#

M_B_PARITY

M_B_ALERT#

M_B_DQS_DN0

M_B_DQS_DN1

M_B_DQS_DN2

M_B_DQS_DN3

M_B_DQS_DN4

M_B_DQS_DN5

M_B_DQS_DN6

M_B_DQS_DN7

M_B_DQS_DP0

M_B_DQS_DP1

M_B_DQS_DP2

M_B_DQS_DP3

M_B_DQS_DP4

M_B_DQS_DP5

M_B_DQS_DP6

M_B_DQS_DP7

V_SM_VREF_CNT

M_VREF_DQ_DIM0

M_VREF_DQ_DIM1

2

M_B_CLK0 [12]

M_B_CLK#0 [12]

M_B_CLK1 [12]

M_B_CLK#1 [12]

M_B_CKE0 [12]

M_B_CKE1 [12]

M_B_CS#0 [12]

M_B_CS#1 [12]

M_B_ODT0 [12]

M_B_ODT1 [12]

M_B_A16 [12]

M_B_A14 [12]

M_B_A15 [12]

For DDR4 Modify

M_B_BS0 [12]

M_B_BS1 [12]

M_B_BG0 [12]

M_B_A0 [12]

M_B_A1 [12]

M_B_A2 [12]

M_B_A3 [12]

M_B_A4 [12]

M_B_A5 [12]

M_B_A6 [12]

M_B_A7 [12]

M_B_A8 [12]

M_B_A9 [12]

M_B_A10 [12]

M_B_A11 [12]

M_B_A12 [12]

M_B_A13 [12]

M_B_BG1 [12]

M_B_ACT# [12]

For DDR4 Modify

M_B_PARITY [12]

M_B_ALERT# [12]

M_B_DQS_DN0 [12]

M_B_DQS_DN1 [12]

M_B_DQS_DN2 [12]

M_B_DQS_DN3 [12]

M_B_DQS_DN4 [12]

M_B_DQS_DN5 [12]

M_B_DQS_DN6 [12]

M_B_DQS_DN7 [12]

M_B_DQS_DP0 [12]

M_B_DQS_DP1 [12]

M_B_DQS_DP2 [12]

M_B_DQS_DP3 [12]

M_B_DQS_DP4 [12]

M_B_DQS_DP5 [12]

M_B_DQS_DP6 [12]

M_B_DQS_DP7 [12]

1

TP601

M_VREF_DQ_DIM1 [12]

12

C601

SCD1U16V2KX-3DLGP

R601 2R2F-GP

1 2

C602

SCD022U16V2KX-3DLGP

2 1

DIMM_CA_CPU_VREF_RC

12

R602

24D9R2F-L-GP

1

DIMM_CA_VREF_AV_SM_VREF_CNT

DIMM_CA_VREF_A [11]

M_VREF_DQ_DIM1

A A

5

4

3

1 2

C603 SCD1U16V2KX-3DLGP

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU_(DDR_CHB)

CPU_(DDR_CHB)

CPU_(DDR_CHB)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Gambits MLK SFF

Gambits MLK SFF

Gambits MLK SFF

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

6 107Friday, February 02, 2018

6 107Friday, February 02, 2018

1

6 107Friday, February 02, 2018

A00C

A00C

A00C

5

www.teknisi-indonesia.com

D D

4

3

2

1

HDMI_DATA_CPU_P0[56]

HDMI_DATA_CPU_N0[56]

HDMI_DATA_CPU_P1[56]

HDMI_DATA_CPU_N1[56]

C C

B B

HDMI_DATA_CPU_P2[56]

HDMI_DATA_CPU_N2[56]

HDMI_DATA_CPU_P3[56]

HDMI_DATA_CPU_N3[56]

HDMI_DATA_CPU_P0

HDMI_DATA_CPU_N0

HDMI_DATA_CPU_P1

HDMI_DATA_CPU_N1

HDMI_DATA_CPU_P2

HDMI_DATA_CPU_N2

HDMI_DATA_CPU_P3

HDMI_DATA_CPU_N3

CPU1D

C21

DDI1_TXP_0

D21

DDI1_TXN_0

D22

DDI1_TXP_1

E22

DDI1_TXN_1

B23

DDI1_TXP_2

A23

DDI1_TXN_2

C23

DDI1_TXP_3

D23

DDI1_TXN_3

B13

DDI1_AUXP

C13

DDI1_AUXN

B18

DDI2_TXP_0

A18

DDI2_TXN_0

D18

DDI2_TXP_1

E18

DDI2_TXN_1

C19

DDI2_TXP_2

D19

DDI2_TXN_2

D20

DDI2_TXP_3

E20

DDI2_TXN_3

A12

DDI2_AUXP

B12

DDI2_AUXN

B14

DDI3_TXP_0

A14

DDI3_TXN_0

C15

DDI3_TXP_1

B15

DDI3_TXN_1

B16

DDI3_TXP_2

A16

DDI3_TXN_2

C17

DDI3_TXP_3

B17

DDI3_TXN_3

B11

DDI3_AUXP

C11

DDI3_AUXN

SKYLAKE-1,SKL-S,LAKE-S

Lake-S

4 OF 12

EDP_TXP_0

EDP_TXN_0

EDP_TXP_1

EDP_TXN_1

EDP_TXN_2

EDP_TXP_2

EDP_TXN_3

EDP_TXP_3

EDP_AUXP

EDP_AUXN

EDP_DISP_UTIL

DISP_RCOMP

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

E10

D10

D9

C9

DDI_VGA_DATA_CPU_N2

H10

DDI_VGA_DATA_CPU_P2

G10

DDI_VGA_DATA_CPU_N3

G9

DDI_VGA_DATA_CPU_P3

F9

DP_AUX_CPU_P

D12

DP_AUX_CPU_N

E12

DISP_UTIL_CPU

D14

FDI_COMP

M9

AUD_AZACPU_SCLK

V3

AUD_AZACPU_SDO

V2

AUD_AZACPU_SDI AUD_AZACPU_SDI_R

U1

DDI_VGA_DATA_CPU_N2 [59]

DDI_VGA_DATA_CPU_P2 [59]

DDI_VGA_DATA_CPU_N3 [59]

DDI_VGA_DATA_CPU_P3 [59]

DP_AUX_CPU_P [59]

DP_AUX_CPU_N [59]

1

TP701

R701 24D9R2F-L-GP

1 2

1 2

R702

20R2J-3-GP

0D95V_CPU_VCCIO

AUD_AZACPU_SCLK [20]

AUD_AZACPU_SDO [20]

AUD_AZACPU_SDI_R [20]

A A

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

7 107Friday, February 02, 2018

7 107Friday, February 02, 2018

1

7 107Friday, February 02, 2018

A00C

A00C

A00C

5

4

3

Title

Title

Title

CPU_(DDI/EDP)

CPU_(DDI/EDP)

CPU_(DDI/EDP)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Gambits MLK SFF

Gambits MLK SFF

Gambits MLK SFF

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

5

www.teknisi-indonesia.com

4

3

2

1

CPU1G

A25

A26

A27

A28

A29

A30

B25

B27

B29

D D

C C

B B

B31

B32

B33

B34

B35

B36

B37

C25

C26

C27

C28

C29

C30

C32

C34

C36

D25

D27

D29

D31

D32

D33

D34

D35

D36

E24

E25

E26

E27

E28

E29

E30

E32

E34

E36

F23

F24

F25

F27

F29

F31

G30

G32

H22

H23

H25

H27

H29

H31

AJ11

AJ13

AJ15

AJ17

AJ19

AJ21

M32

L31

K32

J33

H33

G34

AJ25

AJ26

AJ27

AJ28

SKYLAKE-1,SKL-S,LAKE-S

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC80

VCC81

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC7

VCC9

VCC11

VCC13

VCC15

VCC17

VCC146

VCC134

VCC115

VCC104

VCC91

VCC82

VCC18

VCC19

VCC20

VCC21

Lake-S

7 OF 12

VCC90

VCC93

VCC68

VCC69

VCC70

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

VCC101

VCC102

VCC103

VCC106

VCC107

VCC108

VCC109

VCC110

VCC111

VCC112

VCC113

VCC114

VCC117

VCC118

VCC119

VCC120

VCC121

VCC122

VCC123

VCC124

VCC125

VCC126

VCC127

VCC128

VCC129

VCC130

VCC131

VCC132

VCC133

VCC136

VCC137

VCC138

VCC139

VCC140

VCC141

VCC142

VCC143

VCC144

VCC145

VCC8

VCC10

VCC12

VCC14

VCC16

VCC22

VCC23

VCC71

VCC72

VCC83

VCC92

VCC105

VCC116

VCC135

VCC_SENSE

VSS_SENSE

H32

1V_CPU_CORE1V_CPU_CORE 1V_CPU_GT 1D05V_CPU_SA

J21

F32

F33

F34

G23

G24

G25

G26

G27

G28

G29

J22

J23

J24

J25

J26

J27

J28

J29

J30

J31

K16

K18

K20

K21

K23

K25

K27

K29

K31

L14

L15

L16

L17

L18

L19

L20

L21

L22

L23

L24

L25

L26

L27

L28

L29

L30

M13

M14

M16

M18

M20

M22

M24

M26

M28

M30

AJ12

AJ14

AJ16

AJ18

AJ20

AJ29

AK21

F35

F37

G35

H34

J35

K34

L33

VCORE_VCC_SEN

C38

D38

VCORE_VSS_SEN

VCORE_VCC_SEN [44]

VCORE_VSS_SEN [44]

CPU1H

AA34

VCCGT1

AA35

VCCGT2

AA36

VCCGT3

AA37

VCCGT4

AA38

VCCGT5

AB33

VCCGT6

AB34

VCCGT7

G36

VCCGT8

G37

VCCGT9

G38

VCCGT10

G39

VCCGT11

G40

VCCGT12

H36

VCCGT13

H38

VCCGT14

H40

VCCGT15

J36

VCCGT16

J37

VCCGT17

J38

VCCGT18

J39

VCCGT19

J40

VCCGT20

K36

VCCGT21

K38

VCCGT22

K40

VCCGT23

L34

VCCGT24

L35

VCCGT25

L36

VCCGT26

L37

VCCGT27

L38

VCCGT28

L39

VCCGT29

L40

VCCGT30

M33

VCCGT31

M34

VCCGT32

M36

VCCGT33

M38

VCCGT34

M40

VCCGT35

N34

VCCGT36

N35

VCCGT37

N36

VCCGT38

N37

VCCGT39

N38

VCCGT40

N39

VCCGT41

N40

VCCGT42

P33

VCCGT43

P34

VCCGT44

P36

VCCGT45

P38

VCCGT46

P40

VCCGT47

R34

VCCGT48

R35

VCCGT49

R36

VCCGT50

R37

VCCGT51

R38

VCCGT52

R39

VCCGT53

R40

VCCGT54

T33

VCCGT55

T34

VCCGT56

T36

VCCGT57

T38

VCCGT58

T40

VCCGT59

U34

VCCGT60

U35

VCCGT61

U36

VCCGT62

U37

VCCGT63

U38

VCCGT64

U39

VCCGT65

U40

VCCGT66

V33

VCCGT67

V34

VCCGT68

V36

VCCGT69

V38

VCCGT70

V40

VCCGT71

W34

VCCGT72

W35

VCCGT73

W36

VCCGT74

W37

VCCGT75

W38

VCCGT76

Y33

VCCGT77

Y34

VCCGT78

Y36

VCCGT79

Y38

VCCGT80

SKYLAKE-1,SKL-S,LAKE-S

Lake-S

8 OF 12

VCCGT_SENSE

VSSGT_SENSE

F39

F38

VCCGT_VCC_SEN

VCCGT_VSS_SEN

0D95V_CPU_VCCIO

V_CPU_ST_PLL

VCCGT_VCC_SEN [44]

VCCGT_VSS_SEN [44]

CPU1I

AA7

VCCSA2

AB6

VCCSA3

AB7

VCCSA4

AB8

VCCSA5

AC7

VCCSA6

AC8

VCCSA7

N7

VCCSA8

P7

VCCSA9

R7

VCCSA10

T7

VCCSA11

U7

VCCSA12

Y6

VCCSA15

Y7

VCCSA16

Y8

VCCSA17

W7

VCCSA14

V7

VCCSA13

AA6

VCCSA1

AK11

VCCIO2

AK14

VCCIO3

AK24

VCCIO4

AJ23

VCCIO1

M8

VCCIO5

P8

VCCIO6

T8

VCCIO7

U8

VCCIO8

W8

VCCIO9

V5

VCCST1

V6

VCCST2

V4

VCCPLL

SKYLAKE-1,SKL-S,LAKE-S

Lake-S

9 OF 12

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VCCPLL_OC

VCCSA_SENSE

VCCIO_SENSE

VSS_SAIO_SENSE

AT18

AT21

AU13

AU15

AU19

AU23

AV11

AV17

AV21

AW10

AW14

AW25

AY12

AY16

AY18

AY23

AJ9

AD5

AF4

AE4

1D2V_SM_S3

VCCPLL_OC_R

VCCSA_SENSE

VCCIO_SENSE

VSS_SA_IO_SENSE

R801 0R0402-PAD-2-GP

1 2

VCCPLL_OC_R

20170414

follow CPU EDS change to mount 1x 1uF 0402

1D2V_SM_S3

C801 SC1U10V2KX-1DLGP

1 2

VCCSA_SENSE [47]

VCCIO_SENSE [48]

VSS_SA_IO_SENSE [47]

1D2V_SM_S3 1D2V_SM_S3

12

C808

SCD1U16V2KX-3DLGP

12

C807

SCD1U16V2KX-3DLGP

VCORE_VCC_SEN VCORE_VSS_SEN

A A

R802 49D9R2F-GP

1 2

(R_)

5

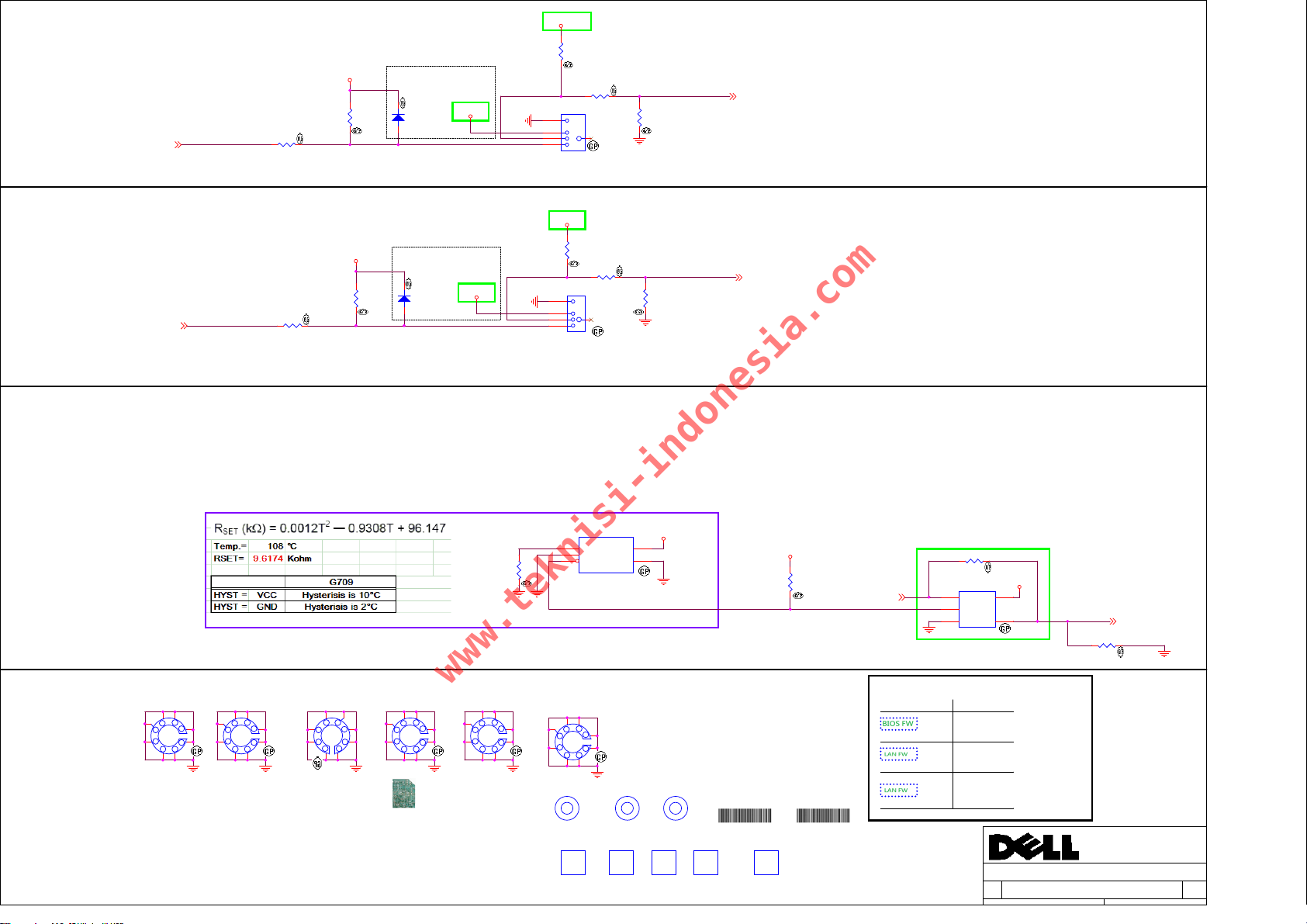

12V_S5

12

R807

100KR2J-1-GP

12

R810

100KR2J-1-GP

(R_)

4

Q802

5

6

2N7002KDW-1-GP

34

2

1

SLP_S4_N_SFR_2

SLP_S4_N_SFR

12V_S5

12

R804

47KR2J-2-GP

R809 0R0402-PAD-2-GP

1 2

12

C806

SCD1U16V2KX-L-GP

(R_)

SLP_S4_NSLP_S4_N_SFR_1

R805 10KR2J-3-GP

1 2

12

R806

100KR2J-1-GP

12

C802

SCD1U25V2KX-1-DL-GP

SLP_S4_N [20,24,32,38,39,40,99]

3

SLP_S4_N_SFR_G

12

C803

SCD1U16V2KX-L-GP

(R_)

1V_PCH_SB

G

DS

Q801

AO3418L-GP

(084.03404.0031)

12

R808

4K7R2J-2-GP

(R_)

R803 0R3J-0-U-GP

1 2

(R_)

2

V_CPU_ST_PLL

12

C804

SC10U25V5KX-DL-GP

V_CPU_ST_PLL

12

C805

SCD1U16V2KX-3DLGP

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU_(CPU Power)

CPU_(CPU Power)

CPU_(CPU Power)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Gambits MLK SFF

Gambits MLK SFF

Gambits MLK SFF

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

8 107Friday, February 02, 2018

8 107Friday, February 02, 2018

1

8 107Friday, February 02, 2018

A00

A00

A00

5

www.teknisi-indonesia.com

4

3

2

1

Lake-S

11 OF 12

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

12 OF 12

C37

C5

C8

C10

D24

D26

D28

D30

D37

D39

D4

D7

E11

E13

E15

E17

E19

E21

E23

E3

E31

E33

E35

E37

E6

E9

F1

F10

F22

F26

F28

F30

F4

F40

F7

G11

G13

G15

G17

G19

G22

G3

G31

G33

G6

H1

H21

H24

H26

H28

H30

H35

H37

H39

H4

H7

H9

J10

J12

L11

J16

J18

J20

J3

J32

J34

J6

K1

K14

K15

K17

K19

K22

K24

K26

K28

K30

K33

K35

K37

CPU1L

K39

VSS

K4

VSS

K7

VSS

L13

VSS

L3

VSS

L32

VSS

L6

VSS

L9

VSS

M1

VSS

M10

VSS

M12

VSS

M15

VSS

M17

VSS

M19

VSS

M21

VSS

M23

VSS

M25

VSS

M27

VSS

M29

VSS

M35

VSS

M37

VSS

M39

VSS

M4

VSS

M7

VSS

N3

VSS

N33

VSS

N6

VSS

N8

VSS

P1

VSS

P35

VSS

P37

VSS

P39

VSS

P4

VSS

R3

VSS

R33

VSS

R6

VSS

R8

VSS

T1

VSS

T35

VSS

T37

VSS

T39

VSS

T4

VSS

U3

VSS

U33

VSS

U6

VSS

V1

VSS

V35

VSS

V37

VSS

V39

VSS

V8

VSS

W3

VSS

W33

VSS

W6

VSS

Y35

VSS

Y37

VSS

Y5

VSS

A4

VSS_NCTF_A4

B38

VSS_NCTF_B38

C2

VSS_NCTF_C2

D40

VSS_NCTF_D40

SKYLAKE-1,SKL-S,LAKE-S

Lake-S

AJ24

VSS

AJ30

VSS

AK22

VSS

AK27

VSS

AR22

VSS

AR23

VSS

AT15

VSS

AU39

VSS

AU40

VSS

AV39

VSS

AW38

VSS

F36

VSS

H11

VSS

H12

VSS

TP_CPU1_L8

1

TP903

20170519

Remove R903, CPU1_AY3 change to test point

R902 0R0402-PAD-2-GP

1 2

1 2

PROC_TRIGIN_CPU[22]

PROC_TRIGOUT_PCH[22]

PROC_TRIGOUT_PCH PROC_TRIGOUT_CPU

1 2

R901

20R2F-GP

R903 0R0402-PAD-2-GP

CPU1_G8

CPU1_AY3

PROC_TRIGIN_CPU

20170519

Remove R903, CPU1_AY3 change to test point

CPU1J

J8

RSVD_TP2

J7

RSVD_TP1

L8

IST_TRIG

K8

RSVD_TP3

AV1

RSVD8

AW2

RSVD9

H8

RSVD13

K10

RSVD20

L10

RSVD24

J17

RSVD18

B39

RSVD10

C40

RSVD11

J19

RSVD19

G8

VSS_G8

AY3

VSS_AY3

D1

PROC_TRIGIN

B3

PROC_TRIGOUT

L12

RSVD25

K12

RSVD22

SKYLAKE-1,SKL-S,LAKE-S

Lake-S

10 OF 12

RSVD4

RSVD1

RSVD2

RSVD3

RSVD5

RSVD12

RSVD21

RSVD17

RSVD16

RSVD7

RSVD6

RSVD15

RSVD23

RSVD14

AC37

AB35

AB37

20170510

AB38

Remove TP901 & TP902 & TP904

AJ22

TP905 &TP906 & TP907

D15

K11

J15

J14

AU9

AU10

J13

K13

J11

D D

C C

B B

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A24

VSS

A7

VSS

AA3

VSS

AA33

VSS

AA8

VSS

AB39

VSS

AB5

VSS

AC3

VSS

AC33

VSS

AC34

VSS

AC35

VSS

AC6

VSS

AD1

VSS

AD33

VSS

AD36

VSS

AD37

VSS

AD38

VSS

AD39

VSS

AD4

VSS

AD40

VSS

AD6

VSS

AD7

VSS

AD8

VSS

AE3

VSS

AE33

VSS

AE36

VSS

AE5

VSS

AE8

VSS

AF1

VSS

AF33

VSS

AF36

VSS

AF37

VSS

AF40

VSS

AF5

VSS

AF8

VSS

AG1

VSS

AG2

VSS

AG3

VSS

AG33

VSS

AG36

VSS

AG4

VSS

AG5

VSS

AG8

VSS

AH33

VSS

AH36

VSS

AH37

VSS

AH38

VSS

AH39

VSS

AH40

VSS

AH5

VSS

AH8

VSS

AJ1

VSS

AJ31

VSS

AJ32

VSS

AJ33

VSS

AJ34

VSS

AJ35

VSS

AJ36

VSS

AJ4

VSS

AJ5

VSS

AJ8

VSS

AK10

VSS

AK12

VSS

AK13

VSS

AK15

VSS

AK16

VSS

AK17

VSS

AK18

VSS

AK19

VSS

AK20

VSS

AK23

VSS

AK25

VSS

AK26

VSS

AK28

VSS

SKYLAKE-1,SKL-S,LAKE-S

AK29

VSS

AK30

VSS

AK36

VSS

AK37

VSS

AK40

VSS

AK5

VSS

AK6

VSS

AK7

VSS

AK8

VSS

AK9

VSS

AL1

VSS

AL11

VSS

AL14

VSS

AL2

VSS

AL21

VSS

AL24

VSS

AL27

VSS

AL3

VSS

AL30

VSS

AL36

VSS

AL4

VSS

AL5

VSS

AM11

VSS

AM14

VSS

AM17

VSS

AM19

VSS

AM24

VSS

AM27

VSS

AM30

VSS

AM31

VSS

AM32

VSS

AM33

VSS

AM34

VSS

AM35

VSS

AM36

VSS

AM37

VSS

AM38

VSS

AM39

VSS

AM40

VSS

AM5

VSS

AN1

VSS

AN10

VSS

AN11

VSS

AN14

VSS

AN16

VSS

AN19

VSS

AN22

VSS

AN23

VSS

AN24

VSS

AN27

VSS

AN30

VSS

AN36

VSS

AN4

VSS

AN5

VSS

AN6

VSS

AN7

VSS

AN8

VSS

AN9

VSS

AP11

VSS

AP14

VSS

AP24

VSS

AP27

VSS

AP30

VSS

AP36

VSS

AP37

VSS

AP40

VSS

AP5

VSS

AR1

VSS

AR11

VSS

AR14

VSS

AR16

VSS

AR17

VSS

AR18

VSS

AR19

VSS

AR2

VSS

AR20

VSS

AR21

VSS

6 OF 12

CPU1F

Lake-S

CPU1K

AR24

VSS

AR27

VSS

AR3

VSS

AR30

VSS

AR31

VSS

AR32

VSS

AR33

VSS

AR34

VSS

AR35

VSS

AR36

VSS

AR4

VSS

AR5

VSS

AT10

VSS

AT11

VSS

AT12

VSS

AT13

VSS

AT14

VSS

AT17

VSS

AT24

VSS

AT25

VSS

AT26

VSS

AT27

VSS

AT28

VSS

AT29

VSS

AT30

VSS

AT31

VSS

AT32

VSS

AT34

VSS

AT36

VSS

AT37

VSS

AT38

VSS

AT39

VSS

AT40

VSS

AT5

VSS

AT6

VSS

AT7

VSS

AT8

VSS

AT9

VSS

AU1

VSS

AU25

VSS

AU30

VSS

AU34

VSS

AU4

VSS

AU5

VSS

AU7

VSS

AV2

VSS

AV26

VSS

AV28

VSS

AV30

VSS

AV34

VSS

AV38

VSS

AV5

VSS

AV9

VSS

AW3

VSS

AW30

VSS

AW32

VSS

AW34

VSS

AW36

VSS

AW5

VSS

AW9

VSS

AY27

VSS

AY30

VSS

AY5

VSS

AY7

VSS

AY9

VSS

B24

VSS

B26

VSS

B28

VSS

B30

VSS

B6

VSS

C12

VSS

C14

VSS

C16

VSS

C18

VSS

C20

VSS

C22

VSS

C24

VSS

C31

VSS

C33

VSS

C35

VSS

SKYLAKE-1,SKL-S,LAKE-S

A A

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

9 107Friday, February 02, 2018

9 107Friday, February 02, 2018

1

9 107Friday, February 02, 2018

A00C

A00C

A00C

5

4

3

Title

Title

Title

CPU_(VSS)

CPU_(VSS)

CPU_(VSS)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Gambits MLK SFF

Gambits MLK SFF

Gambits MLK SFF

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

5

www.teknisi-indonesia.com

PLACE ALL 0805 CAPS ON TOP SIDE OF CPU CAVITY PLACE ALL 0603 CAPS

1V_CPU_CORE

12

PC1007

SC22U6D3V5MX-2DLGP

D D

20170518

Follow Tahoe MT MLK A00 22uF 0805*12pcs

12

PC1008

SC22U6D3V5MX-2DLGP

12

PC1009

SC22U6D3V5MX-2DLGP

(R_)

12

PC1010

SC22U6D3V5MX-2DLGP

(R_)

4

12

PC1011

SC22U6D3V5MX-2DLGP

(R_)

12

PC1012

SC22U6D3V5MX-2DLGP

12

PC1018

SC22U6D3V5MX-2DLGP

3

20170518

Follow Tahoe MT MLK A00 22uF 0603*2pcs

1V_CPU_CORE

1V_CPU_CORE

ON TOP SIDE OF CPU CAVITY

12

PC1001

SC22U6D3V3MX-1-DL-GP

12

PC1002

SC22U6D3V3MX-1-DL-GP

PLACE ALL 0805 CAPS AT TOP SOCKET EDGE

12

PC1019

SC22U6D3V5MX-L3-GP

(78.22610.51LDL)

12

PC1020

SC22U6D3V5MX-L3-GP

(78.22610.51LDL)

12

PC1021

SC22U6D3V5MX-L3-GP

(78.22610.51LDL)

20170518

Follow Tahoe MT MLK A00 unmount 22uF 0805*5pcs

12

PC1022

SC22U6D3V5MX-L3-GP

(78.22610.51LDL)

2

20170518

Follow Tahoe MT MLK A00 unmount 22uF 0805*3pcs

1V_CPU_CORE

IF Have enough TOP SIDE OF CPU CAVITY, On it,

Or at socket EDGE

12

PC1004

SC22U6D3V5MX-L3-GP

(78.22610.51LDL)

12

PC1023

SC22U6D3V5MX-L3-GP

(78.22610.51LDL)

12

PC1005

SC22U6D3V5MX-L3-GP

(78.22610.51LDL)

12

PC1006

SC22U6D3V5MX-L3-GP

(78.22610.51LDL)

1

Need EE check

PLACE CAPS FOR DIMM PLACE CAPS IN SOCKET EDGE TOP

1D2V_SM_S3

12

C1025

SC22U6D3V5MX-L3-GP

(R_)

C C

PLACE CAPS ON TOP SIDE

SOCKET CAVITY

1V_CPU_GT

12

PC1034

SC22U6D3V5MX-2DLGP

(R_)

12

PC1042

B B

1D05V_CPU_SA

SC22U6D3V5MX-2DLGP

20170518

Follow Tahoe MT MLK A00 unmount 22uF 0805*4pcs

PLACE CAPS ON TOP SIDE

SOCKET CAVITY

12

PC1050

SC47U6D3V5MX-1DL-GP

12

PC1035

SC22U6D3V5MX-2DLGP

PLACE CAPS

AT SOCKET EDGE ON TOP

12

PC1043

SC22U6D3V5MX-2DLGP

12

PC1051

SC47U6D3V5MX-1DL-GP

12

C1026

SC22U6D3V5MX-L3-GP

(R_)

20170518

Follow Tahoe MT MLK A00 22uF 0805*7pcs + unmont 2pcs

12

PC1036

(R_)

20170518

Follow Tahoe MT MLK A00 47uF 0805*4pcs

SC22U6D3V5MX-2DLGP

(R_)

12

PC1044

SC22U6D3V5MX-2DLGP

12

PC1052

SC47U6D3V5MX-1DL-GP

12

C1027

SC22U6D3V5MX-L3-GP

(R_)

12

PC1037

SC22U6D3V5MX-2DLGP

(R_)

12

PC1045

SC22U6D3V5MX-2DLGP

PLACE CAPS AT TOP SOCKET EDGE

12

PC1053

SC47U6D3V5MX-1DL-GP

1D2V_SM_S3

12

PC1038

SC22U6D3V5MX-2DLGP

(R_)

12

C1028

SC47U6D3V5MX-1DL-GP

20170414

follow PDG change to mount 4x 47uF 0805

12

PC1039

SC22U6D3V5MX-2DLGP

(R_)

12

C1029

SC47U6D3V5MX-1DL-GP

12

0D95V_CPU_VCCIO

12

C1030

SC47U6D3V5MX-1DL-GP

PC1040

SC22U6D3V5MX-2DLGP

12

PC1046

SC22U6D3V3MX-1-DL-GP

12

C1031

SC47U6D3V5MX-1DL-GP

PLACE CAPS

IN SOCKET EDGE TOP

12

PC1041

SC22U6D3V5MX-2DLGP

20170518

Follow Tahoe MT MLK A00 22uF 0603*4pcs

12

12

PC1047

SC22U6D3V3MX-1-DL-GP

PC1058

SC22U6D3V5MX-2DLGP

12

PC1048

SC22U6D3V3MX-1-DL-GP

PLACE CAPS ON TOP SIDE

SOCKET CAVITY

12

PC1049

SC22U6D3V3MX-1-DL-GP

Need EE check

VCCST/VCCSTG

PLACE CAPS AT TOP SOCKET EDGE

V_CPU_ST_PLL

12

C1032

SC22U6D3V5MX-2DLGP

CRB:1*22U

0805,1*1U 0402

12

C1033

SC1U10V2KX-1DLGP

A A

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

10 107Friday, February 02, 2018

10 107Friday, February 02, 2018

1

10 107Friday, February 02, 2018

A00

A00

A00

5

4

3

Title

Title

Title

CPU Power CAP

CPU Power CAP

CPU Power CAP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Gambits MLK SFF

Gambits MLK SFF

Gambits MLK SFF

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

5

www.teknisi-indonesia.com

DIMM1:

SA0: 0, SA1: 0

Write Address: 0xA0

Read Address: 0xA1

DIMM_CA_VREF_A_L

M_A_ACT#[5]

M_A_ODT0[5]

M_A_ODT1[5]

M_A_CKE0[5]

M_A_CKE1[5]

M_A_CS#0[5]

M_A_CS#1[5]

M_A_CLK#0[5]

M_A_CLK0[5]

M_A_CLK#1[5]

M_A_CLK1[5]

M_A_BG0[5]

M_A_BG1[5]

M_A_BS0[5]

M_A_BS1[5]

M_A_A0[5]

M_A_A1[5]

M_A_A2[5]

M_A_A3[5]

M_A_A4[5]

M_A_A5[5]

M_A_A6[5]

M_A_A7[5]

M_A_A8[5]

M_A_A9[5]

M_A_A10[5]

M_A_A11[5]

M_A_A12[5]

M_A_A13[5]

M_A_A14[5]

M_A_A15[5]

M_A_A16[5]

SMB_CLK_MAIN

SMB_DATA_MAIN

M_A_ACT#

M_A_ALERT#

DIMM1_EVENT_N

SM_DRAMRST#

M_A_PARITY

DIMM1_EVENT_N

M_A_ODT0

M_A_ODT1

M_A_CKE0

M_A_CKE1

M_A_CS#0

M_A_CS#1

M_A_CLK#0

M_A_CLK0

M_A_CLK#1

M_A_CLK1

M_A_BG0

M_A_BG1

M_A_BS0

M_A_BS1

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_A16

3D3V_S0

SMB_CLK_MAIN[12,24,59]

1D2V_SM_S3

SMB_DATA_MAIN[12,24,59]

M_A_ALERT#[5]

SM_DRAMRST#[12,20]

M_A_PARITY[5]

R1101 240R2F-1-GP

1 2

D D

C C

DIMM1A

205

RFU#205

227

RFU#227

230

RFU#230

144

RFU#144

146

VREFCA

141

SCL

285

SDA

139

SA0

140

SA1

238

SA2

284

VDDSPD

62

ACT#

208

ALERT#

78

EVENT#

58

RESET#

222

PAR

49

CB0

194

CB1

56

CB2

201

CB3

47

CB4

192

CB5

54

CB6

199

CB7

87

ODT0

91

ODT1

60

CKE0

203

CKE1

84

S0#

89

S1#

93

S2#_C0

237

S3#_C1

235

C2

75

CK0#

74

CK0

219

CK1#

218

CK1

63

BG0

207

BG1

81

BA0

224

BA1

79

A0

72

A1

216

A2

71

A3

214

A4

213

A5

69

A6

211

A7

68

A8

66

A9

225

A10

210

A11

65

A12

232

A13

228

A14_WE#

86

A15_CAS#

82

A16_RAS#

234

A17

DDR4-288P-82-GP

(022.10010.0A61)

NP3

NP2

NP1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

1/4

DIMM288_DDR4

1 OF 4

4

NP3

NP2

NP1

M_A_DQ0

5

M_A_DQ1

150

M_A_DQ2

12

M_A_DQ3

157

M_A_DQ4

3

M_A_DQ5

148

M_A_DQ6

10

M_A_DQ7

155

M_A_DQ8

16

M_A_DQ9

161

M_A_DQ10

23

M_A_DQ11

168

M_A_DQ12

14

M_A_DQ13

159

M_A_DQ14

21

M_A_DQ15

166

M_A_DQ16

27

M_A_DQ17

172

M_A_DQ18

34

M_A_DQ19

179

M_A_DQ20

25

M_A_DQ21

170

M_A_DQ22

32

M_A_DQ23

177

M_A_DQ24

38

M_A_DQ25

183

M_A_DQ26

45

M_A_DQ27

190

M_A_DQ28

36

M_A_DQ29

181

M_A_DQ30

43

M_A_DQ31

188

M_A_DQ32

97

M_A_DQ33

242

M_A_DQ34

104

M_A_DQ35

249

M_A_DQ36

95

M_A_DQ37

240

M_A_DQ38

102

M_A_DQ39

247

M_A_DQ40

108

M_A_DQ41

253

M_A_DQ42

115

M_A_DQ43

260

M_A_DQ44

106

M_A_DQ45

251

M_A_DQ46

113

M_A_DQ47

258

M_A_DQ48

119

M_A_DQ49

264

M_A_DQ50

126

M_A_DQ51

271

M_A_DQ52

117

M_A_DQ53

262

M_A_DQ54

124

M_A_DQ55

269

M_A_DQ56

130

M_A_DQ57

275

M_A_DQ58

137

M_A_DQ59

282

M_A_DQ60

128

M_A_DQ61

273

M_A_DQ62

135

M_A_DQ63

280

M_A_DQ[0..63] [5]

DIMM1B

DQS10#

DQS11#

DQS12#

DQS13#

DQS14#

DQS15#

DQS16#

DQS17#

2/4

DDR4-288P-82-GP

(022.10010.0A61)

DQS0#

DQS0

DQS1#

DQS1

DQS2#

DQS2

DQS3#

DQS3

DQS4#

DQS4

DQS5#

DQS5

DQS6#

DQS6

DQS7#

DQS7

DQS8#

DQS8

DQS9#

DQS9

DQS10

DQS11

DQS12

DQS13

DQS14

DQS15

DQS16

DQS17

DIMM288_DDR4

152

153

163

164

174

175

185

186

244

245

255

256

266

267

277

278

196

197

8

7

19

18

30

29

41

40

100

99

111

110

122

121

133

132

52

51

2 OF 4

M_A_DQS_DN0

M_A_DQS_DP0

M_A_DQS_DN1

M_A_DQS_DP1

M_A_DQS_DN2

M_A_DQS_DP2

M_A_DQS_DN3

M_A_DQS_DP3

M_A_DQS_DN4

M_A_DQS_DP4

M_A_DQS_DN5

M_A_DQS_DP5

M_A_DQS_DN6

M_A_DQS_DP6

M_A_DQS_DN7

M_A_DQS_DP7

1D2V_SM_S3

3

DIMM1C

2

VSS

4

VSS

6

VSS

9

VSS

11

VSS

13

VSS

15

VSS

17

VSS

20

VSS

12

TC1101

E820U2D5VM-6-GP

(R_)

22

VSS

24

VSS

26

VSS

28

VSS

31

VSS

33

VSS

35

VSS

37

VSS

39

VSS

42

VSS

44

VSS

46

VSS

48

VSS

50

VSS

53

VSS

55

VSS

57

VSS

94

VSS

96

VSS

98

VSS

101

VSS

103

VSS

105

VSS

107

VSS

109

VSS

112

VSS

114

VSS

116

VSS

118

VSS

120

VSS

123

VSS

125

VSS

127

VSS

129

VSS

131

VSS

134

VSS

136

VSS

138

VSS

DDR4-288P-82-GP

(022.10010.0A61)

M_A_DQS_DN0 [5]

M_A_DQS_DP0 [5]

M_A_DQS_DN1 [5]

M_A_DQS_DP1 [5]

M_A_DQS_DN2 [5]

M_A_DQS_DP2 [5]

M_A_DQS_DN3 [5]

M_A_DQS_DP3 [5]

M_A_DQS_DN4 [5]

M_A_DQS_DP4 [5]

M_A_DQS_DN5 [5]

M_A_DQS_DP5 [5]

M_A_DQS_DN6 [5]

M_A_DQS_DP6 [5]

M_A_DQS_DN7 [5]

M_A_DQS_DP7 [5]

1D2V_SM_S3

2

147

VSS

149

VSS

151

VSS

154

VSS

156

VSS

158

VSS

160

VSS

162

VSS

165

VSS

167

VSS

169

VSS

171

VSS

173

VSS

176

VSS

178

VSS

180

VSS

182

VSS

184

VSS

187

VSS

189

VSS

191

VSS

193

VSS

195

VSS

198

VSS

200

VSS

202

VSS

239

VSS

241

VSS

243

VSS

246

VSS

248

VSS

250

VSS

252

VSS

254

VSS

257

VSS

259

VSS

261

VSS

263

VSS

265

VSS

268

VSS

270

VSS

272

VSS

274

VSS

276

VSS

279

VSS

281

VSS

283

VSS

3/4

DIMM288_DDR4

3 OF 4

3D3V_S0

12

C1109

SCD1U16V2KX-3DLGP

1D2V_SM_S3

0D675V_VTT_S0

2D5V_VPP_S3

12

C1110

SC2D2U6D3V2MX-DL-GP

DIMM1D

59

VDD

61

VDD

64

VDD

67

VDD

70

VDD

73

VDD

76

VDD

80

VDD

83

VDD

85

VDD

88

VDD

90

VDD

92

VDD

204

VDD

206

VDD

209

VDD

212

VDD

215

VDD

217

VDD

220

VDD

223

VDD

226

VDD

229

VDD

231

VDD

233

VDD

236

VDD

77

VTT

221

VTT

142

VPP

143

VPP

286

VPP

287

VPP