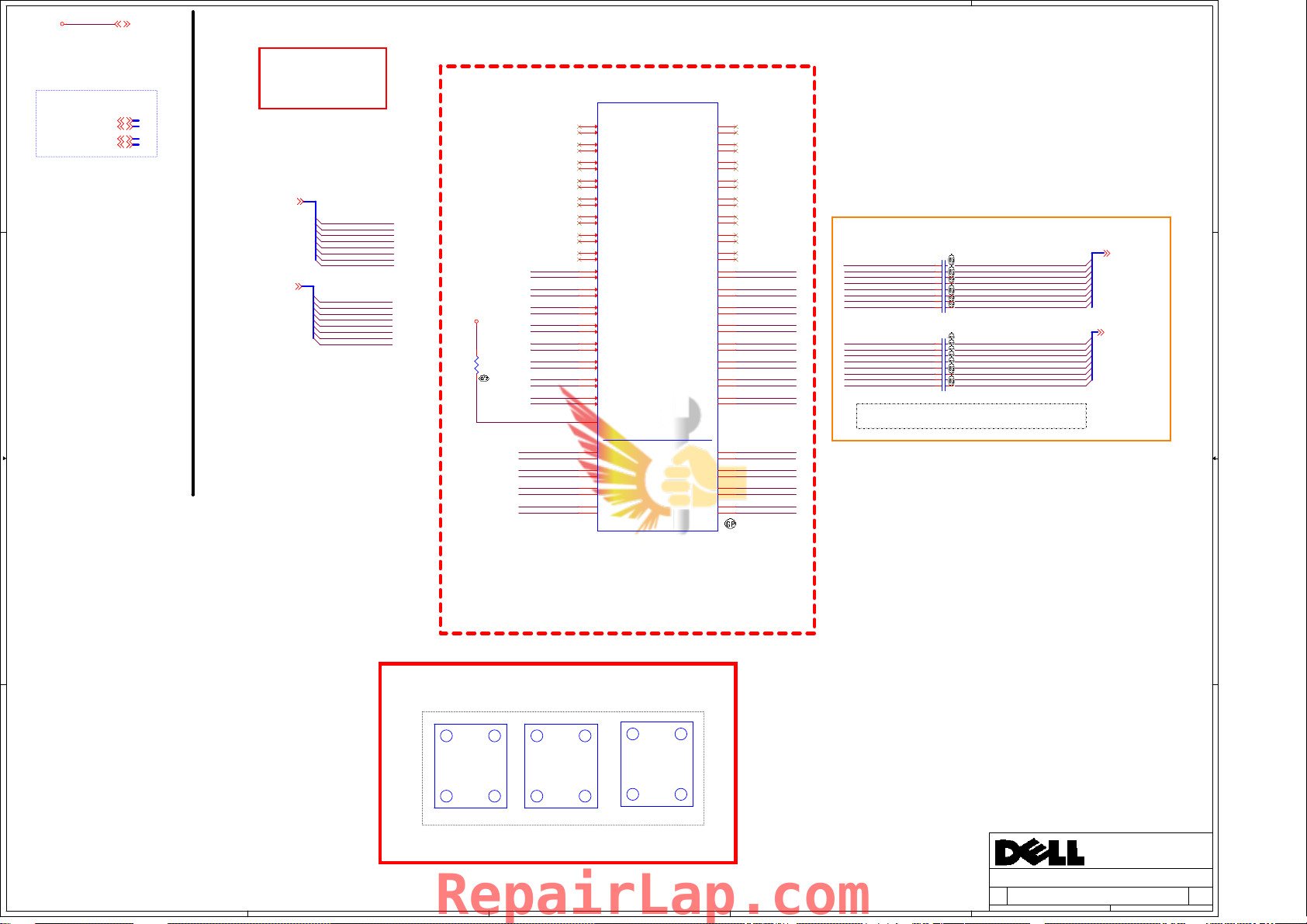

Dell Vostro 5460 , Inspiron 5488 Schematics

5

RepairLap.com

4

3

2

1

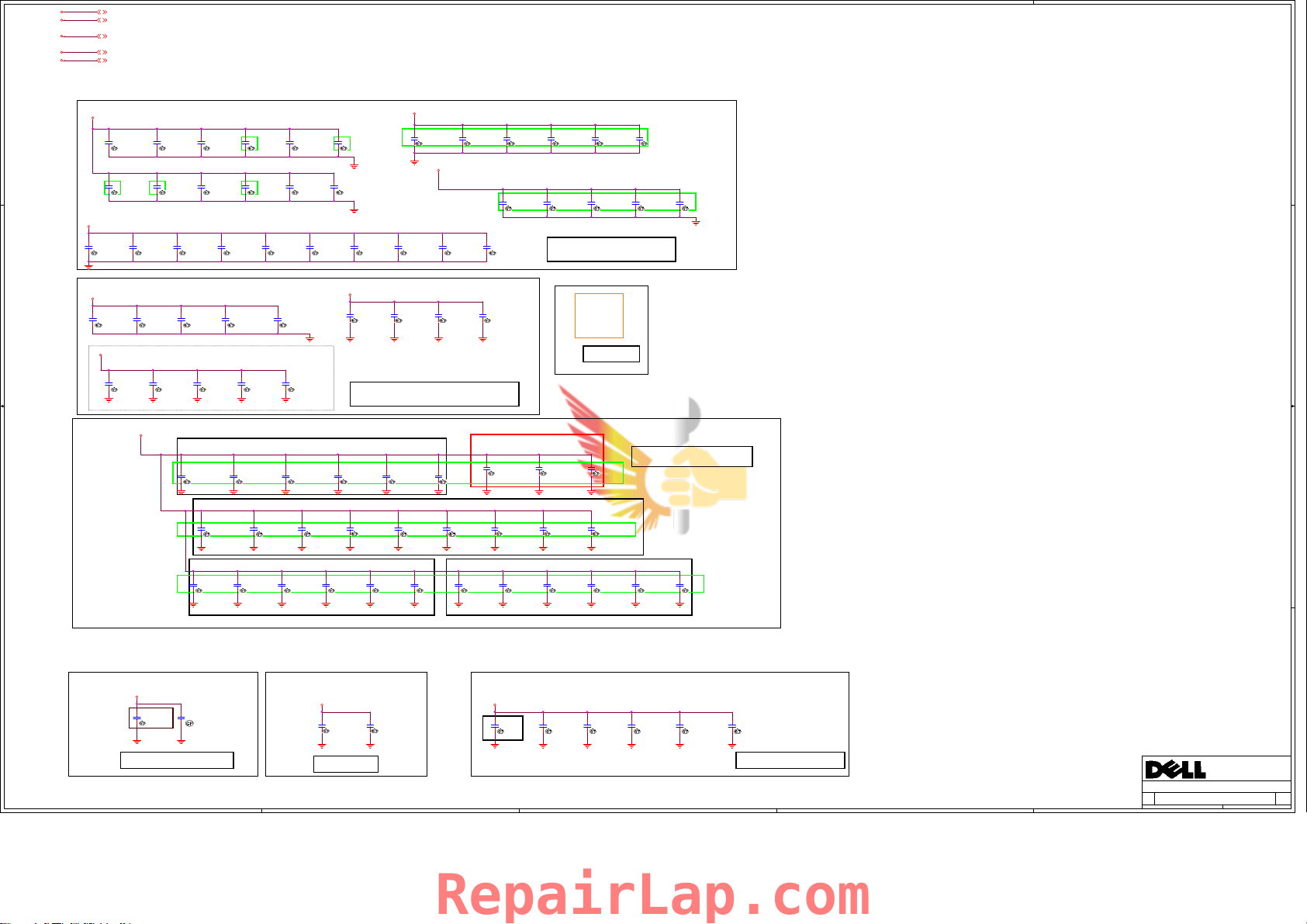

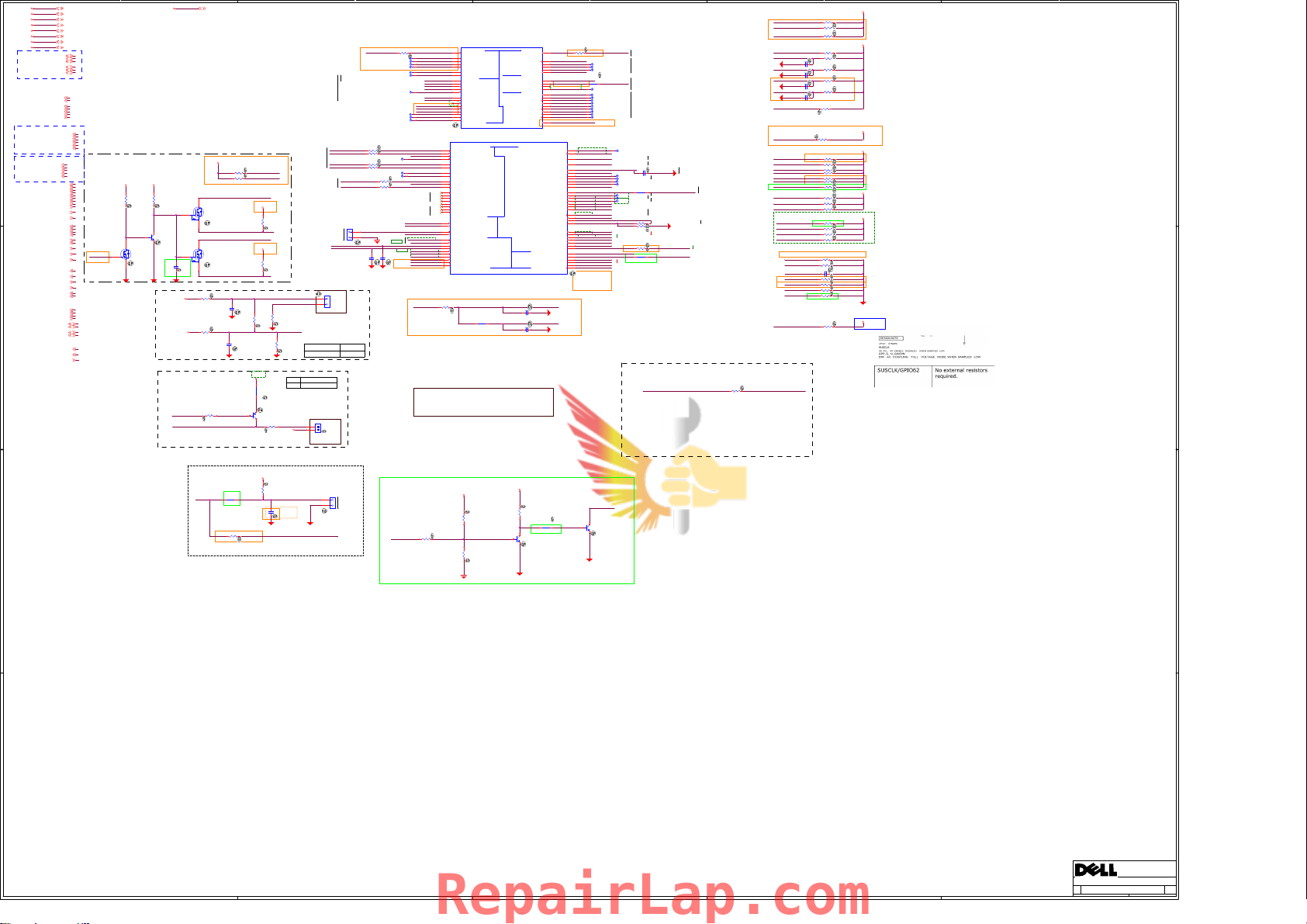

BOM Configuration

(R):Unmount

(G):GPU

PCB Number: 14058-2

ECO# number : 776481

D D

C C

B B

A A

PAGE

58

5

TITLE

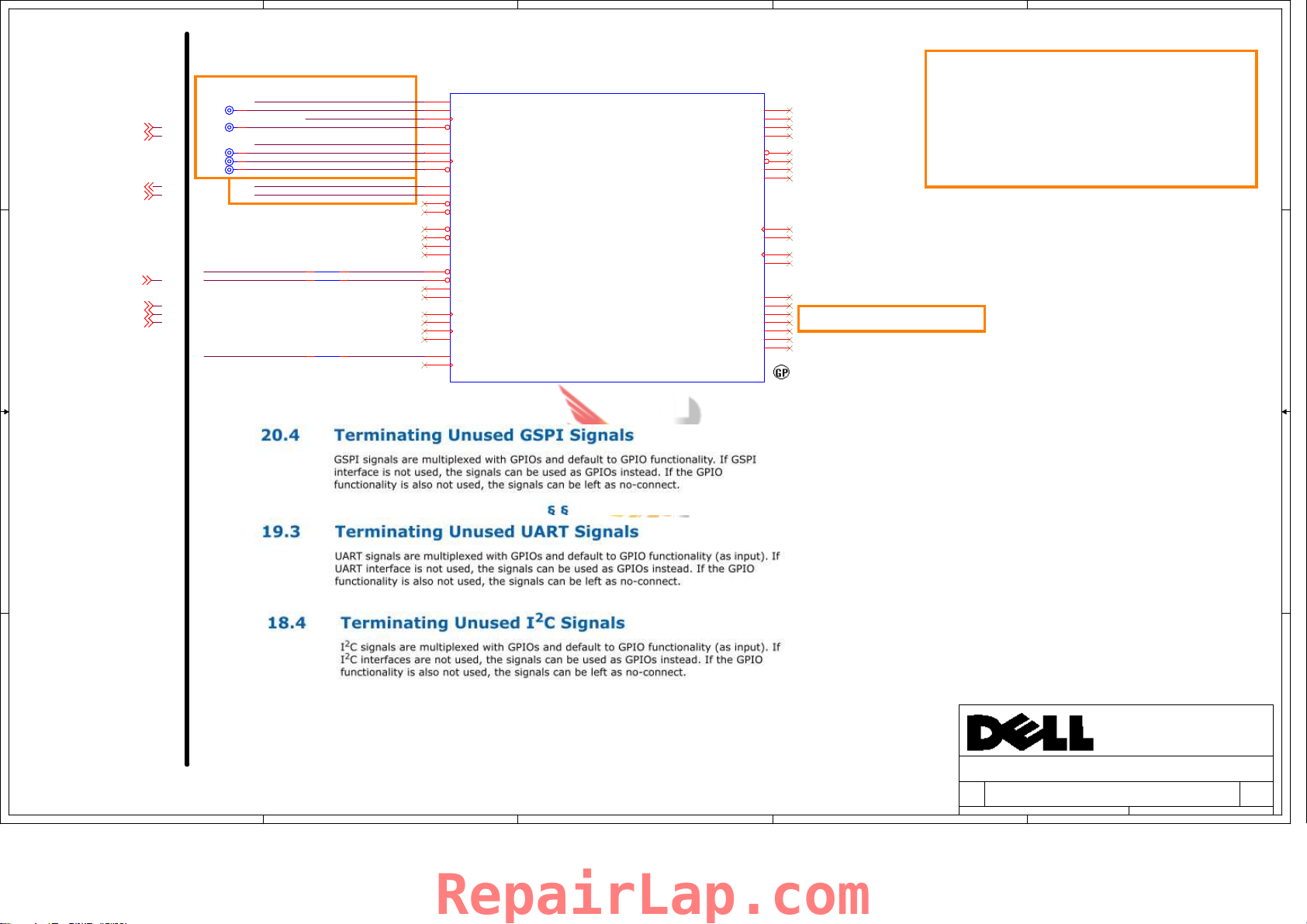

01

Cover Page

02

Block Diagram

03 CPU_DDRA_DDRB

CPU_CFG/CLOCK

04

CPU_PCIE

05

06

CPU_ (VSS)

CPU_(VCC_CORE/TP)

07

08

CPU_(DDI/EDP)

09

CPU_(POWER CAP1)

CPU_(POWER CAP2)

10

11

Reserved

12

DDR3_SODIMM1

13

DDR3_SODIMM2

14 Reserved

15

PCH(SPI/SMBUS/Audio/JTAG)

16

PCH_(Clock)

17

PCH (PCIE/SATA/USB)

PCH (USB3.0/GPIO/HPD)

18

19

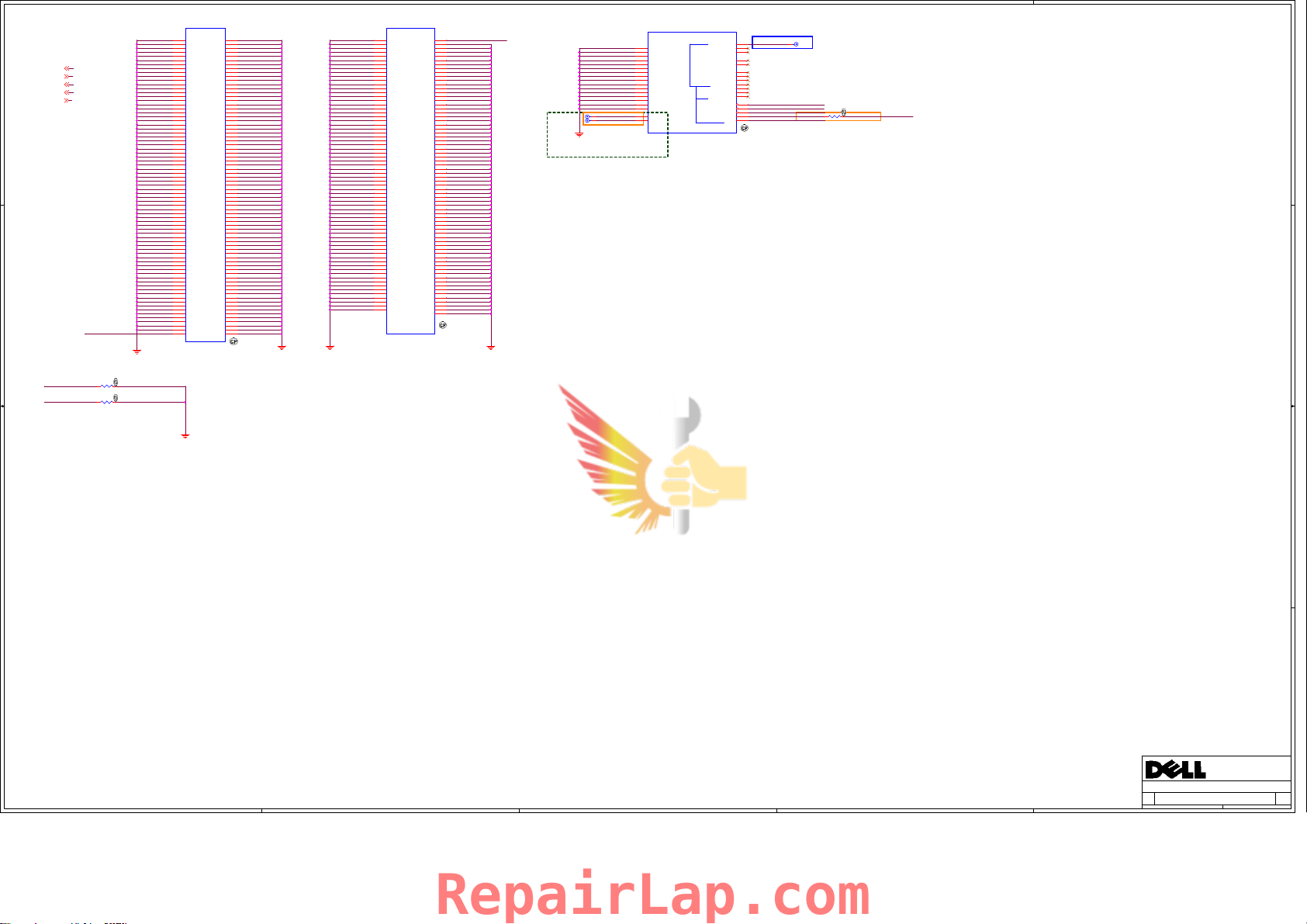

PCH (GPIO)

20

PCH_(Stap Pin)

21

PCH_(Power)

PCH_(Vss/TP)

22

PCH_(Reserved)

23

24

SIO_ITE8739

25

Flash ROM/RTC

26

FAN CIRCUITS/HOLE

27

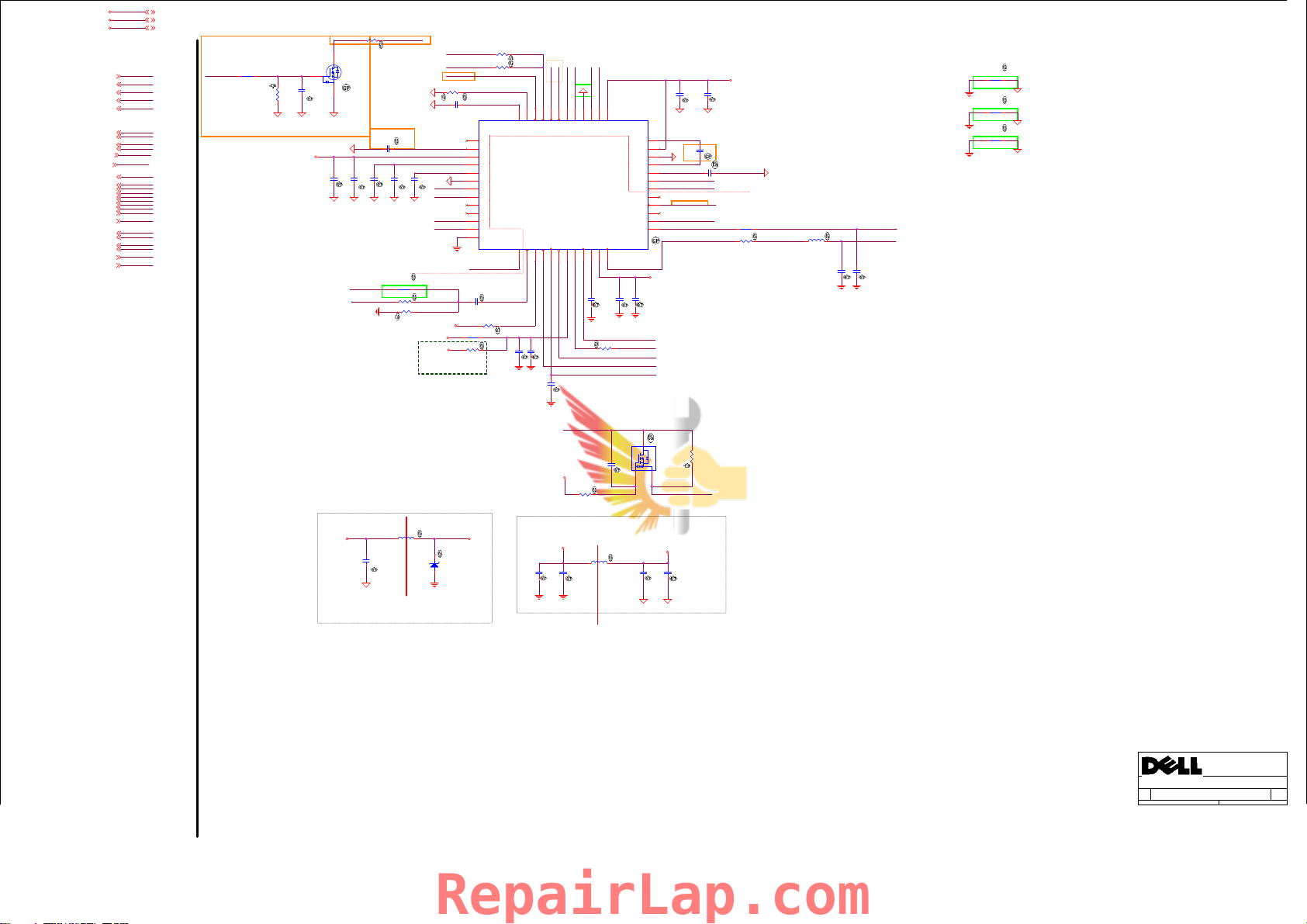

AUDIO ALC3661

28

AMP TPA3131

29

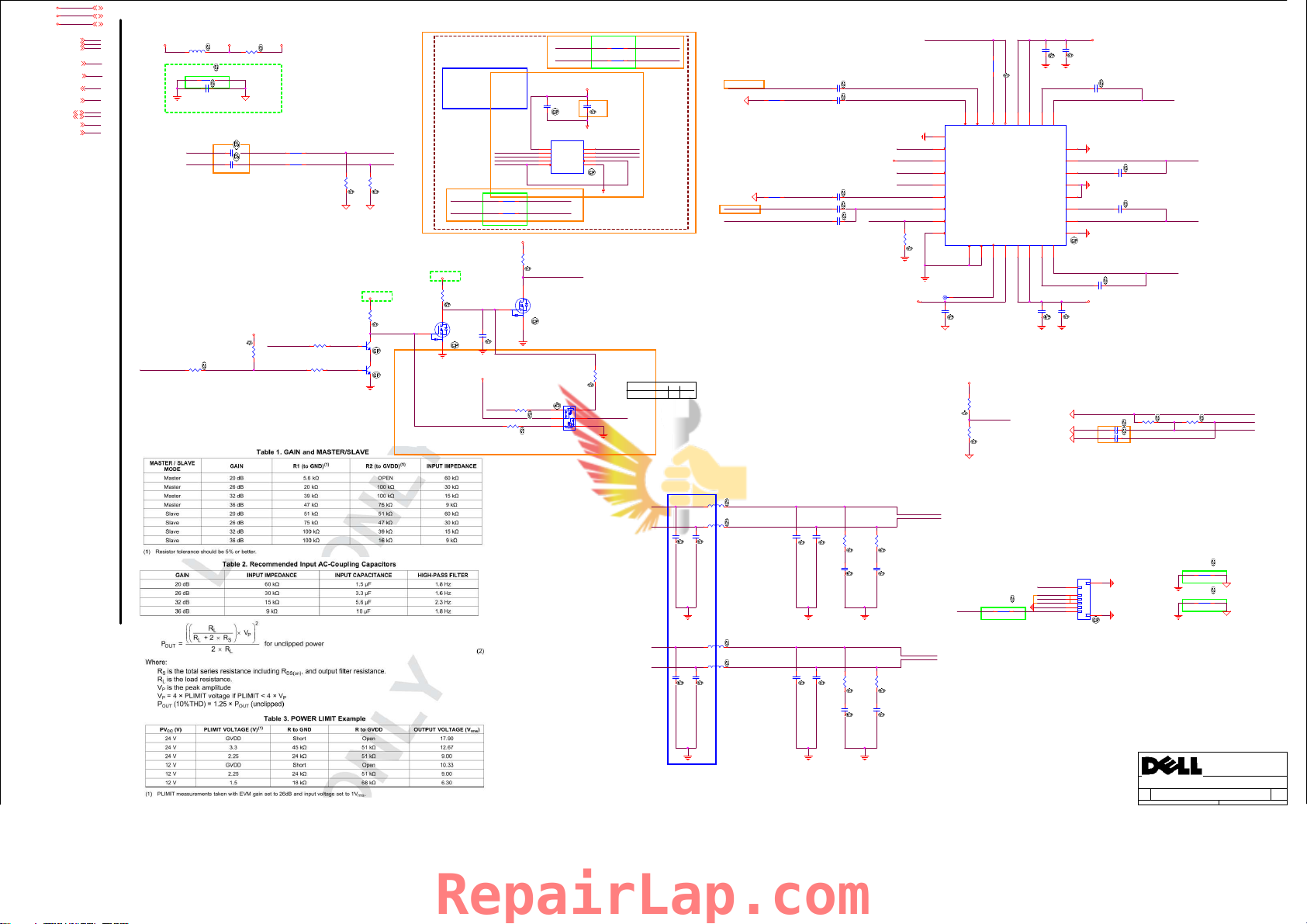

MIC/SPEAKER/AUDIO JACK

30

Reserved

31

LAN_RTL8111HSD

32

RJ45+TRANSFORMER

33

READER CONN

34

USB2.0 CONN

35

USB3.0 CONN

36

Reserved

37

Reserved

38

WEBCAM

39

Reserved

40

Power enable & sequence

41

DCIN

42

Run PWR/USB/ DSWPWR

43

CHARGER

44

VCORE & V_GT(NCP81203)

45

VCORE OUTPUT (NCP81151)

46

V_GT OUTPUT(NCP81151)

47

VCCSA(RT8237)

48

VCCIO(RT8237)

49

5V & 3.3V(RT8243A)

50

DDR_PWR (RT8207M)

51

PCH_1D0V(RT8237)

1D8V(RT9025)

52

12V(RT8289)

53

54

Reserved

Scalar

55

HDMI OUT

56

HDMI IN

57

PANEL CONTROL

Quantity

4

(U):UMA

(X):Debug used

(T):Touch

TITLEPAGE Quantity

59

OZ554A LED Converter

60

HDD/ODD

61

NGFF CONN

62

TOUCH

63

Reserved

64

LED BOARD/POWER BUTTON

65

Reserved

66

Reserved

67

FFS

68

DEBUG CONNECTOR

69

Reserved

70

Reserved

71

Reserved

72

Reserved

73

Reserved

74

Reserved

75

Reserved

76

GPU(1/5) PEG

77

GPU(2/5)DIGITALOUT

78

GPU(3/5):VRAM I/F

79

GPU(4/5):GPIO/STRAP

80

080_GPU(5/5):PWR/GND

81

VRAM 1,2(1/2)

82

VRAM 3,4(2/2)

83

VRAM5,6(3/4)

84

VRAM7,8(4/4)

Reserved85

86

PWR_GPU_LDO

Reserved

87

88

PWR_GPU_CORE

Reserved

89

Reserved

90

91

Reserved

92

Reserved

Reserved

93

Reserved

94

Reserved

95

Reserved

96

Reserved

97

98 Reserved

CPU_XDP

99

100

Reserved

Reserved

101

102 POWER Sequence

103

POWER BLOCK DIAGRAM

104 POWER GOOD & RESET DIAGRAM

105 CLOCK DIAGRAM

3

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

001_Cover Page

001_Cover Page

001_Cover Page

Size Document Number Rev

C

Size Document Number Rev

C

Size Document Number Rev

C

COLORADO MLK SKYLAKE-S

COLORADO MLK SKYLAKE-S

COLORADO MLK SKYLAKE-S

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

1 107

1 107

1

1 107

-2

-2

-2

5

RepairLap.com

Project code:3PD025010001

ECO# Number: 776481

PCB Number: 14058

Revision:A01

D D

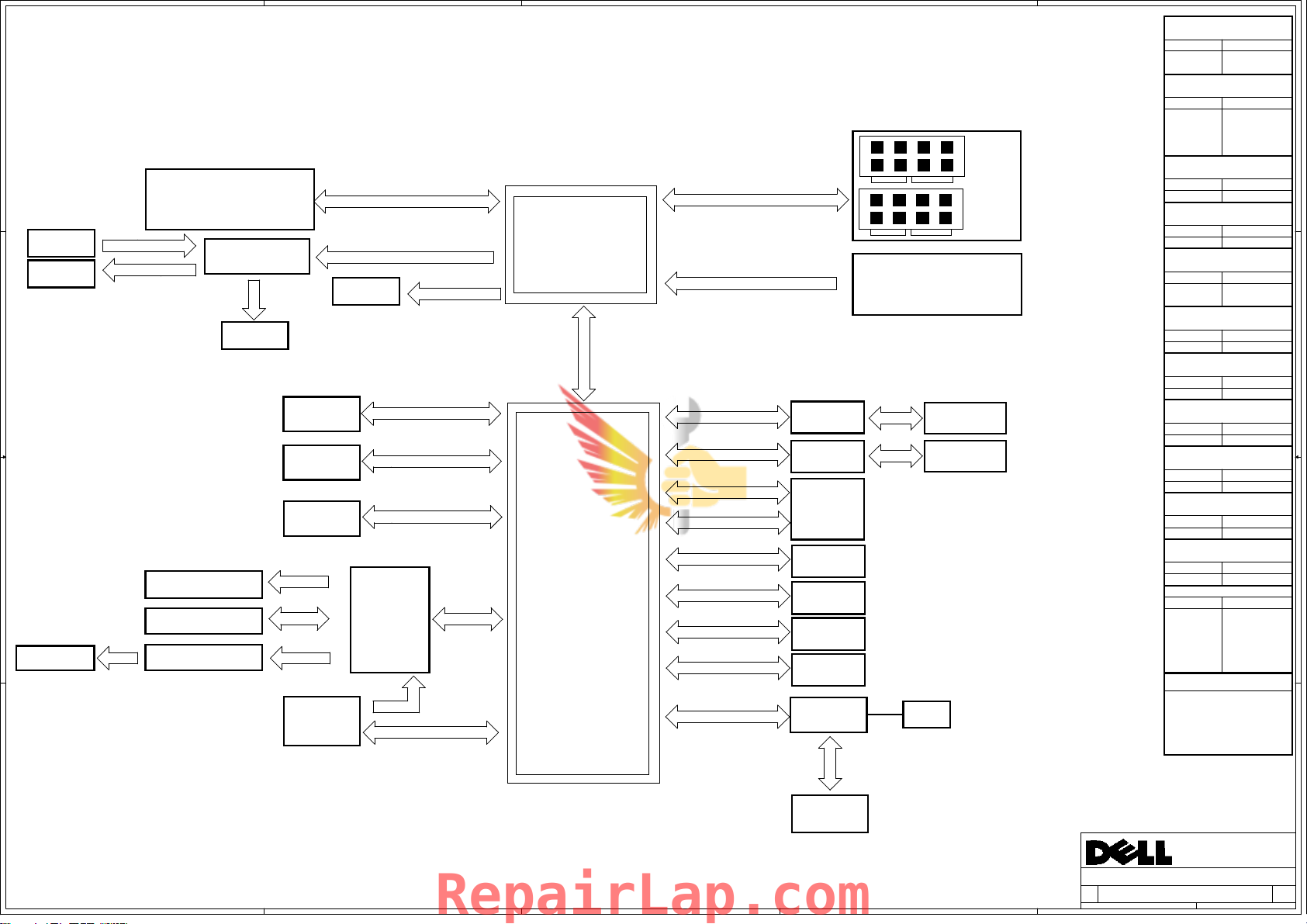

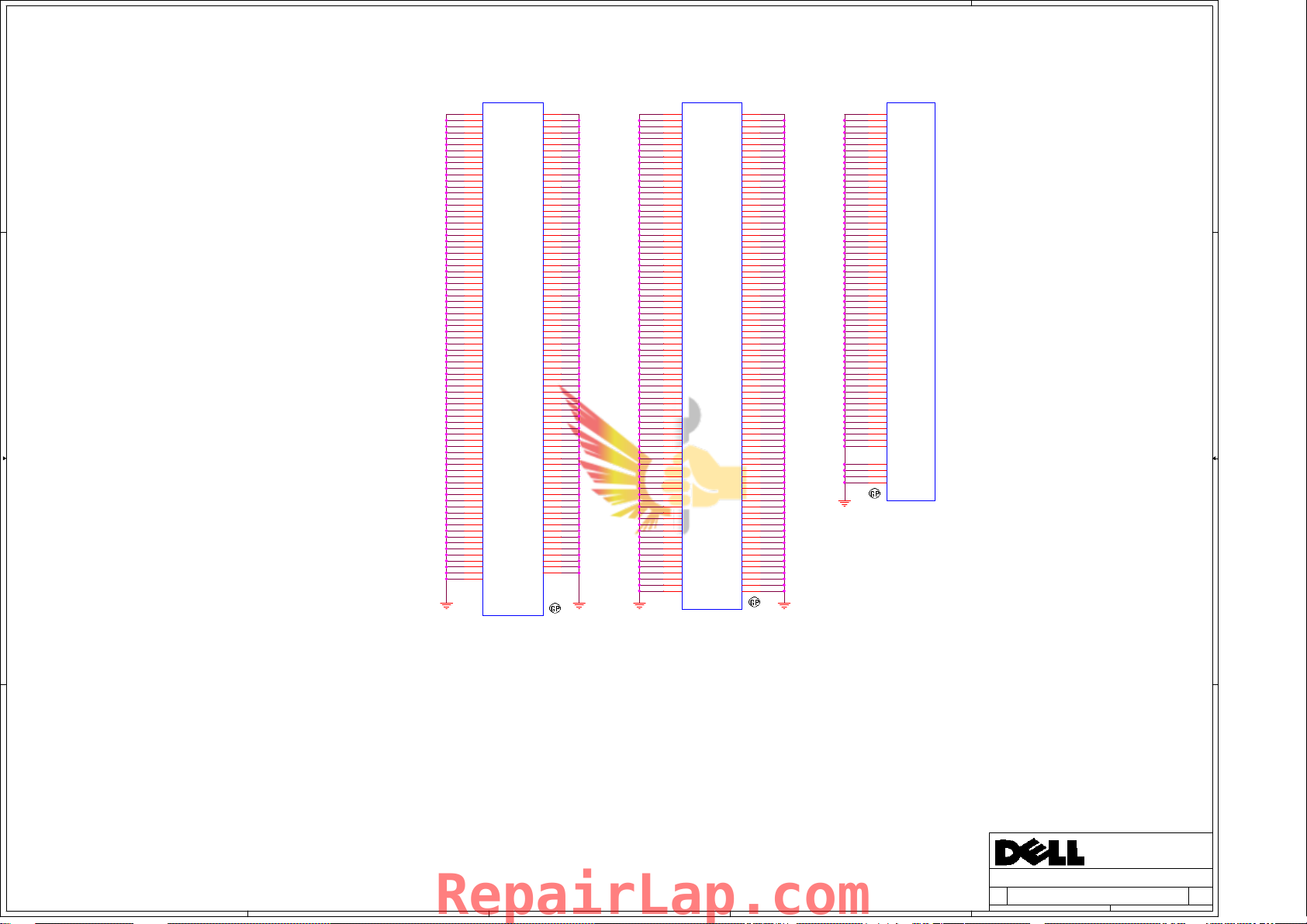

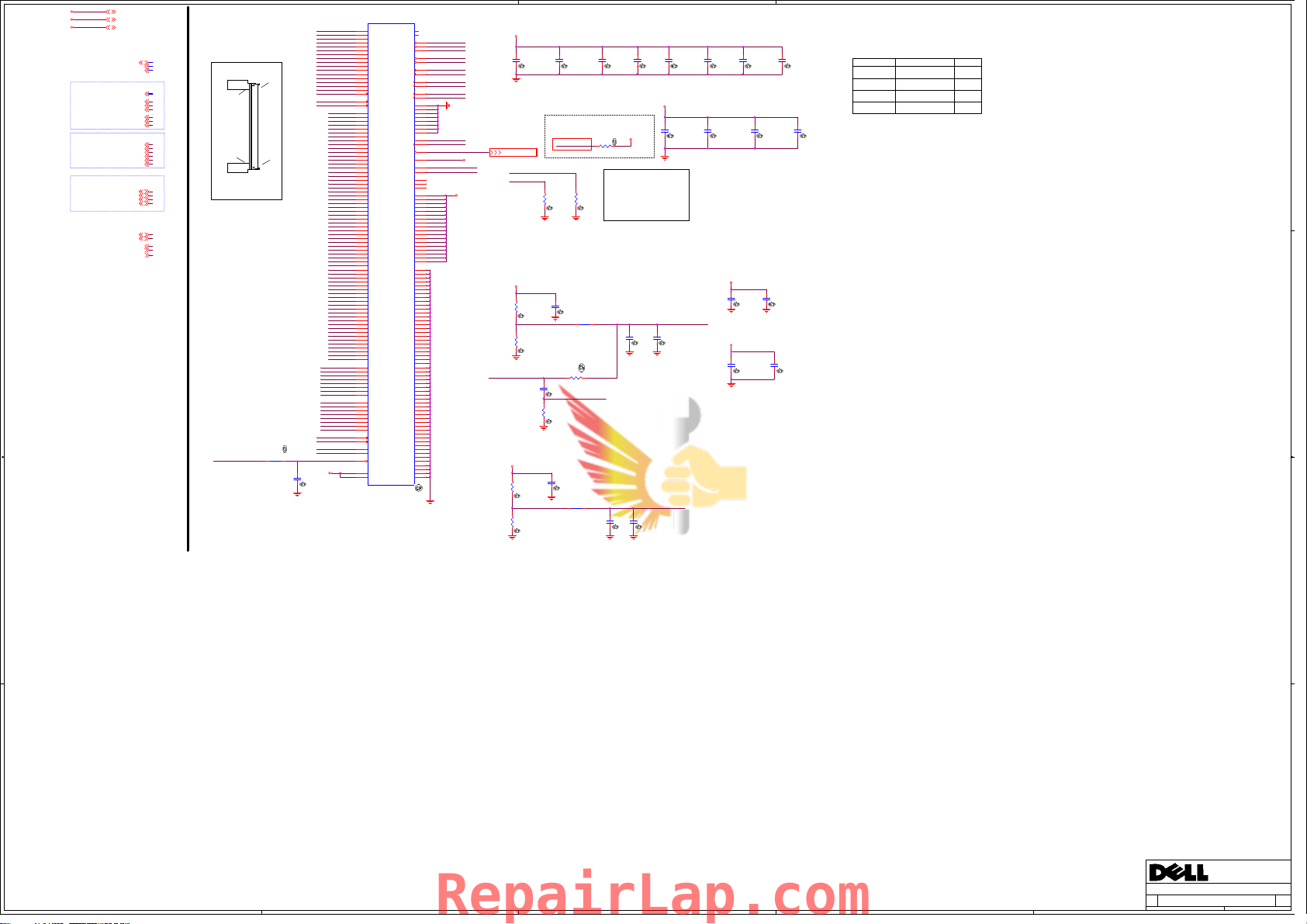

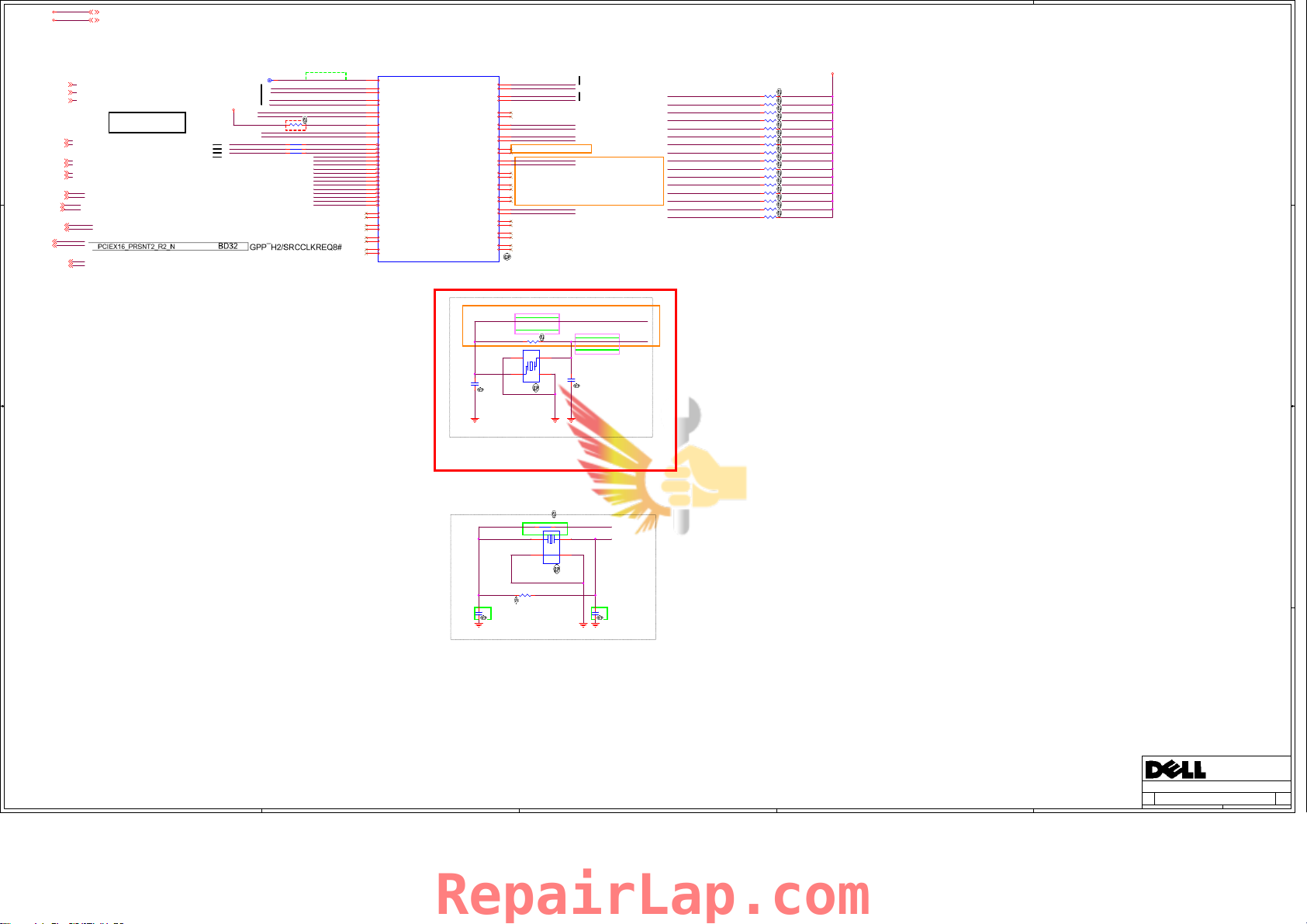

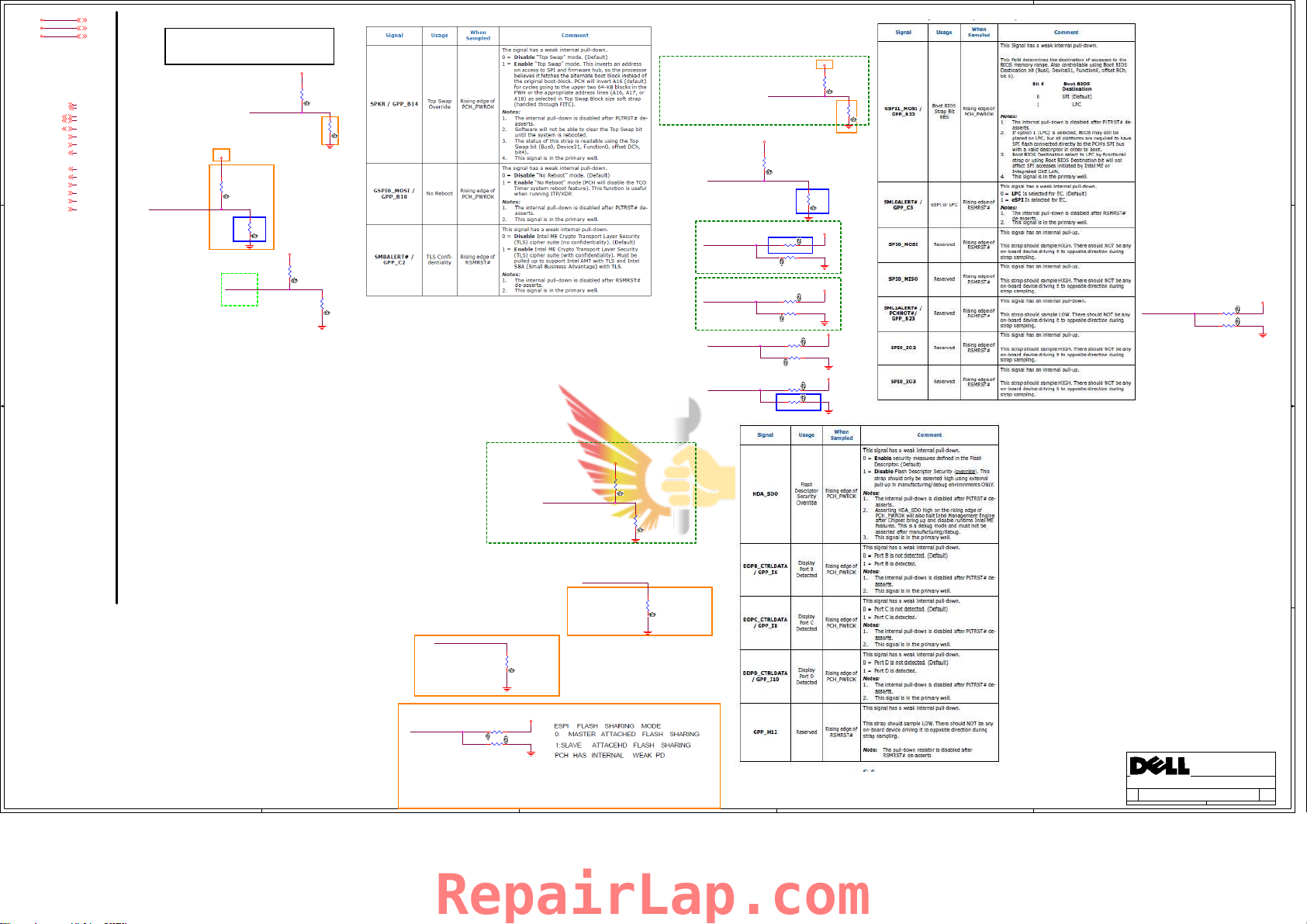

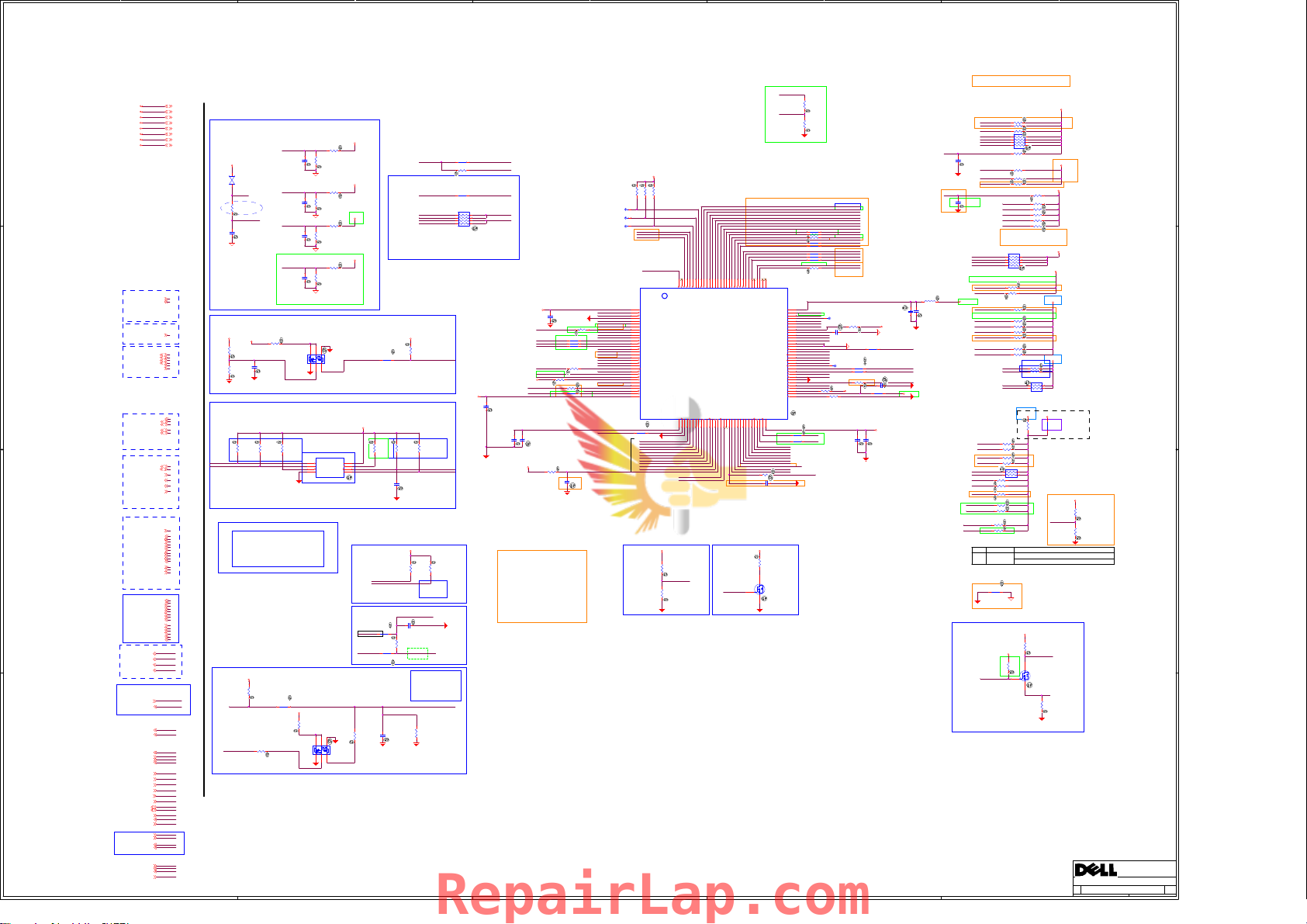

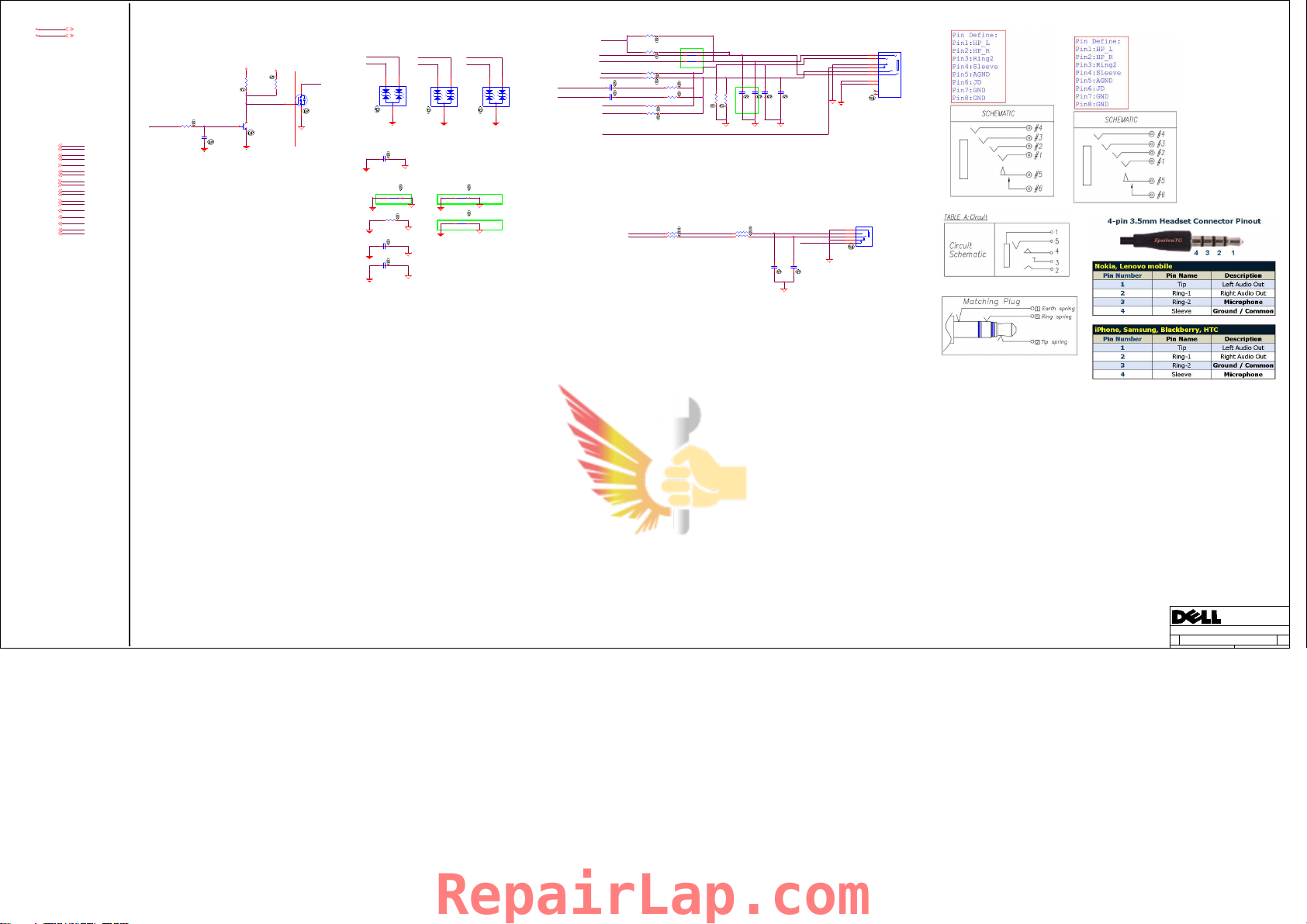

COLORADO MLK Skylake-S Block Diagram

4

3

2

1

CHARGER

BQ24727RGRR-1-GP

INPUTS

SYSTEM DC/DC

RT8243AZQW-GP

INPUTS

DCBATOUT

AD+

BT+

OUTPUTS

DCBATOUT

OUTPUTS

V_3P3_A

V_5P0_A

43

49

CPU Core Power

DDR3L

NVIDIA 25W N16S-GMR-S-A2

76-88

HDMI Input

Panel

55

HDMI

LVDS

LVDS Out 55

LVDS Conn 58

Scaler RTD2586

55

GPIO

OSD Button

C C

55

HDD

ODD

PEG X4

eDP

HDMI Output

60

60

56

HDMI

SATA(Gen3) x 1

SATA port 2

SATA(Gen2) x 1

SATA port 3

Intel CPU

Skylake-S 35W

LGA-1151

DMI X4

Skylake

SPI ROM

8MB

B B

Line Out (Rear)

Universal Jack (Side)

3.5W SPK*2

AMP TPA3131

HPO L/R

LINEOUT L/R

28

Webcam/Mic

25

Audio Codec

ALC3661

38

DMIC

SPI

27

USB2.0 X1

USB port 9

PCH-H110

HDA

DDR3L 1866MHz Daul-Channel A/B

IMVP8 SVID

PCI-E X1

PCI-E port 5

PCI-E X1

PCI-E port 6

LAN

RTL8111H

Card Reader

RTS5249S

PCI-E X1

PCI-E port 8

USB2.0 X1

WLAN + BT

(NGFF)

USB port 10

USB2.0 X1

USB port 9

USB2.0 X1

USB port 8

USB2.0 X1

USB port 3-6

USB3.0 X1

Webcam

Touch

USB2.0*4

USB3.0*2

USB port 1-2

LPC

EC SIO

ITE8739

For 35W 1MVP8:

Core 2 Phases 2H2L

Gfx 2 Phase 1H2L

31

33

61

38

62

34

35

24

RJ-45 Fast Giga LAN

FAN

1600

SODIMM A

12, 13

44

32

SD Card 4.0

NCP81203MNTXG-SI2-GP

INPUTS

DCBATOUT

GFX Core Power

NCP81172MNTXG-GP-U

INPUTS

DCBATOUT

DDR3L SUS

TPS51716RUKR-GP

INPUTS OUTPUTS

DCBATOUT

CPU GT POWER

NCP81203MNTXG-SI2-GP

DCBATOUT

CPU 1.05V

NCP5230MNTWG

DCBATOUT

CPU 0.95V

RT8237CZQW-2-GP

DCBATOUT V_CPU_IO

PCH 1.0V

S-1339D15-M5001-GP

DCBATOUT

FAN 12V

RT8289GSP-GP

DCBATOUT

GPU 1.35V

APW8713QBI-GP

DCBATOUT86+V_1P35_VGA

System switchs

INPUTS OUTPUTS

V_5P0_A SB5V

V_5P0_A VCC

V_3P3_A VCC3

V_SM

PCB LAYER

L1:Top

L2:GND

L3:Signal

L4:Signal

L5:GND

L6:Bottom

44,45

OUTPUTS

V_CPU_CORE

88

33

OUTPUTS

+V_GPU_CORE

50

V_SM

V_SM_VTT

44,46

OUTPUTSINPUTS

V_CPU_GT

47

OUTPUTSINPUTS

V_CPU_SA

48

OUTPUTSINPUTS

51

OUTPUTSINPUTS

V1P0_PCH_S5

53

OUTPUTSINPUTS

12V_S0

OUTPUTSINPUTS

SB3VV_3P3_A

+V_1P05_VGA

SPI

A A

Flash ROM

5

4

1MB

3

2

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

002_Block Diagram

002_Block Diagram

002_Block Diagram

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

COLORADO MLK SKYLA KE-S -2Custom

COLORADO MLK SKYLA KE-S -2Custom

COLORADO MLK SKYLA KE-S -2Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

1

2 107

2 107

2 107

5

RepairLap.com

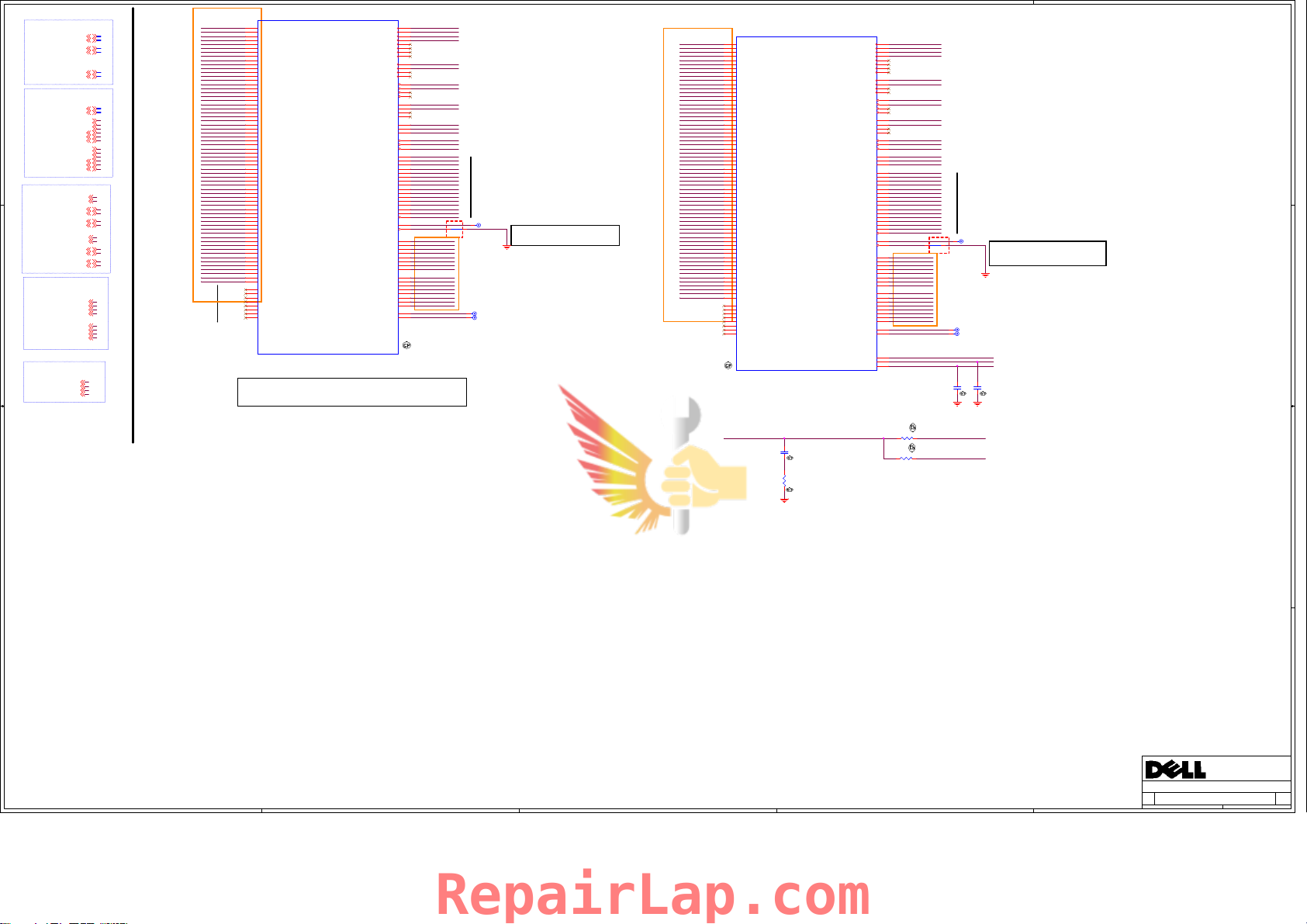

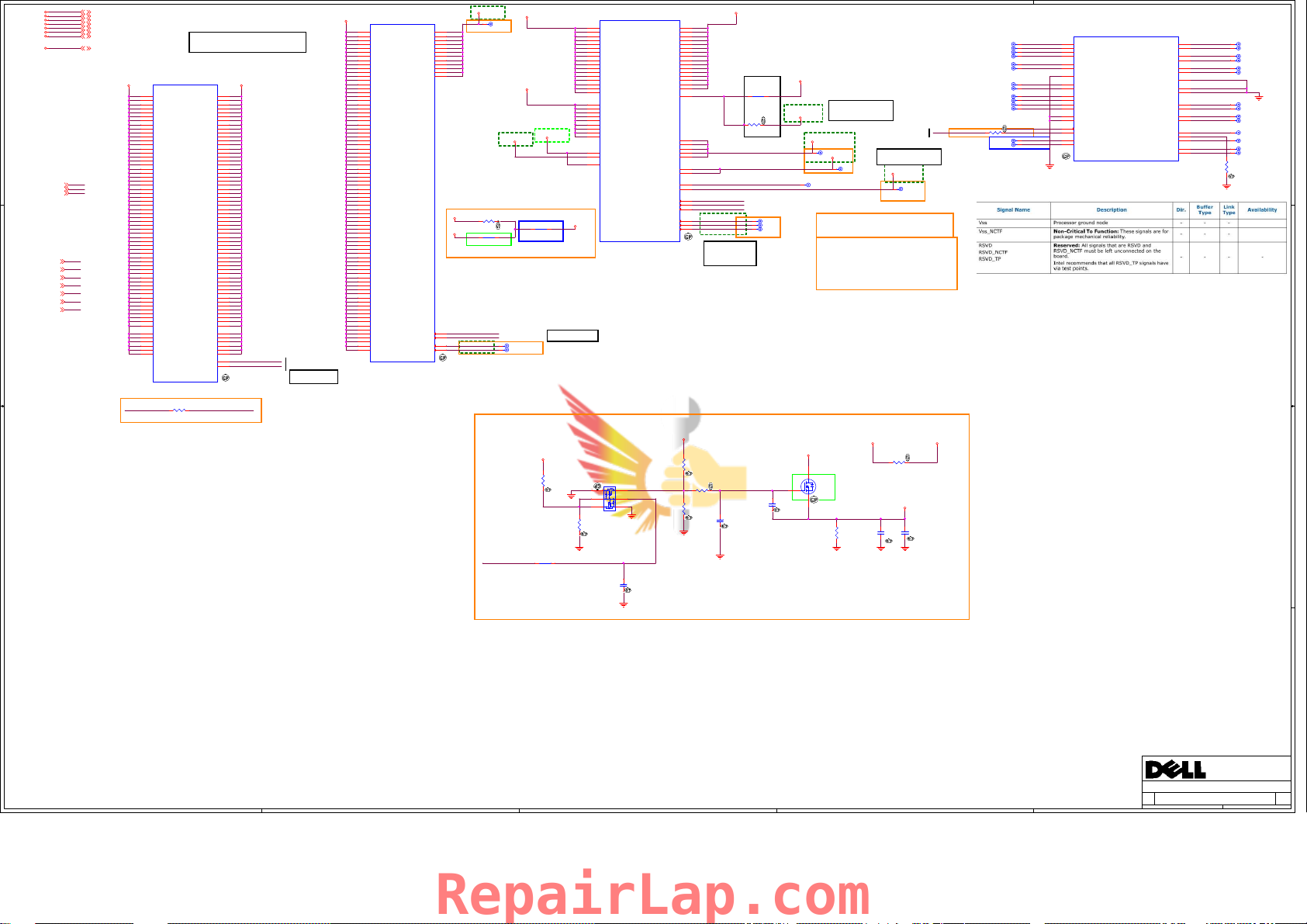

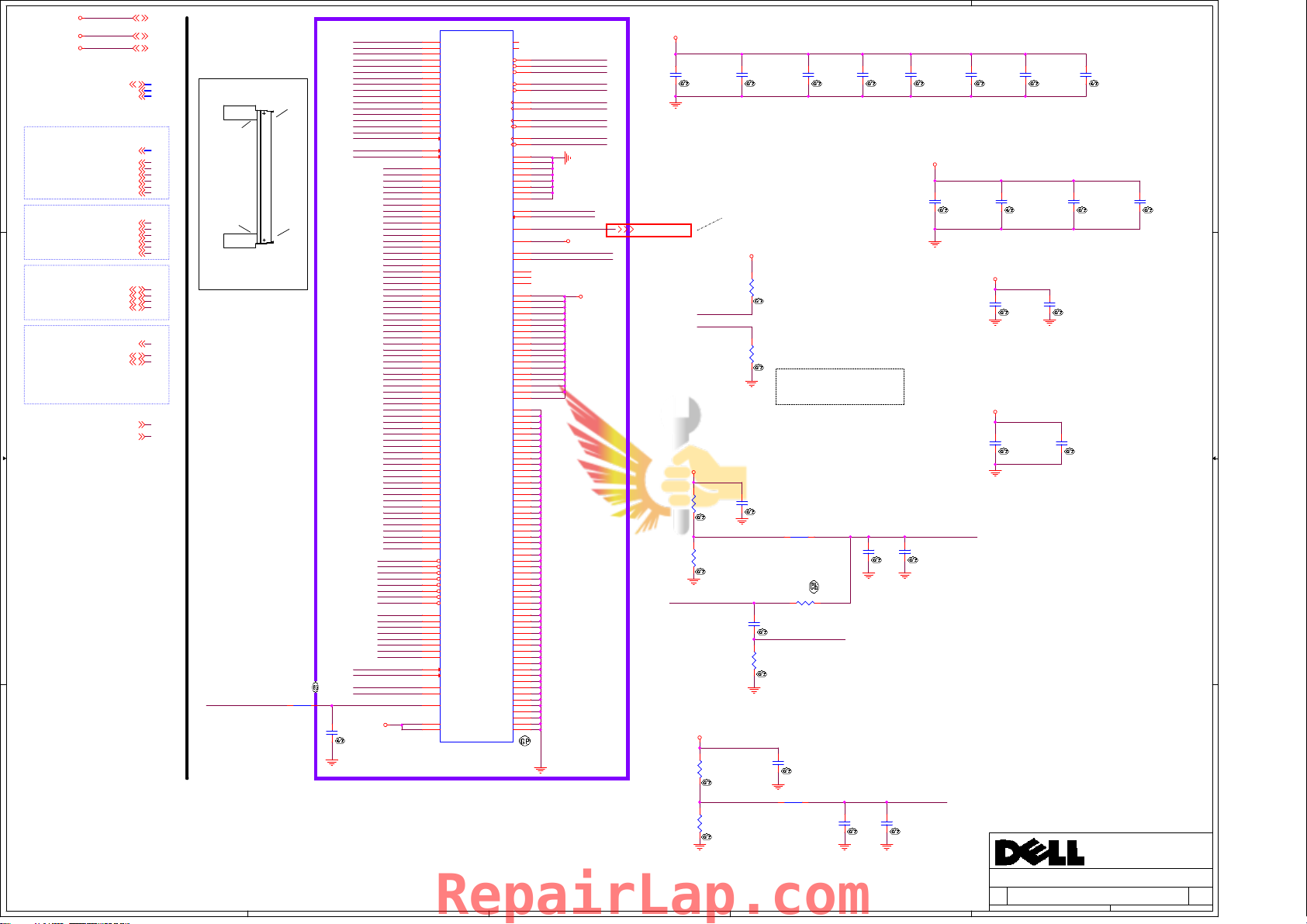

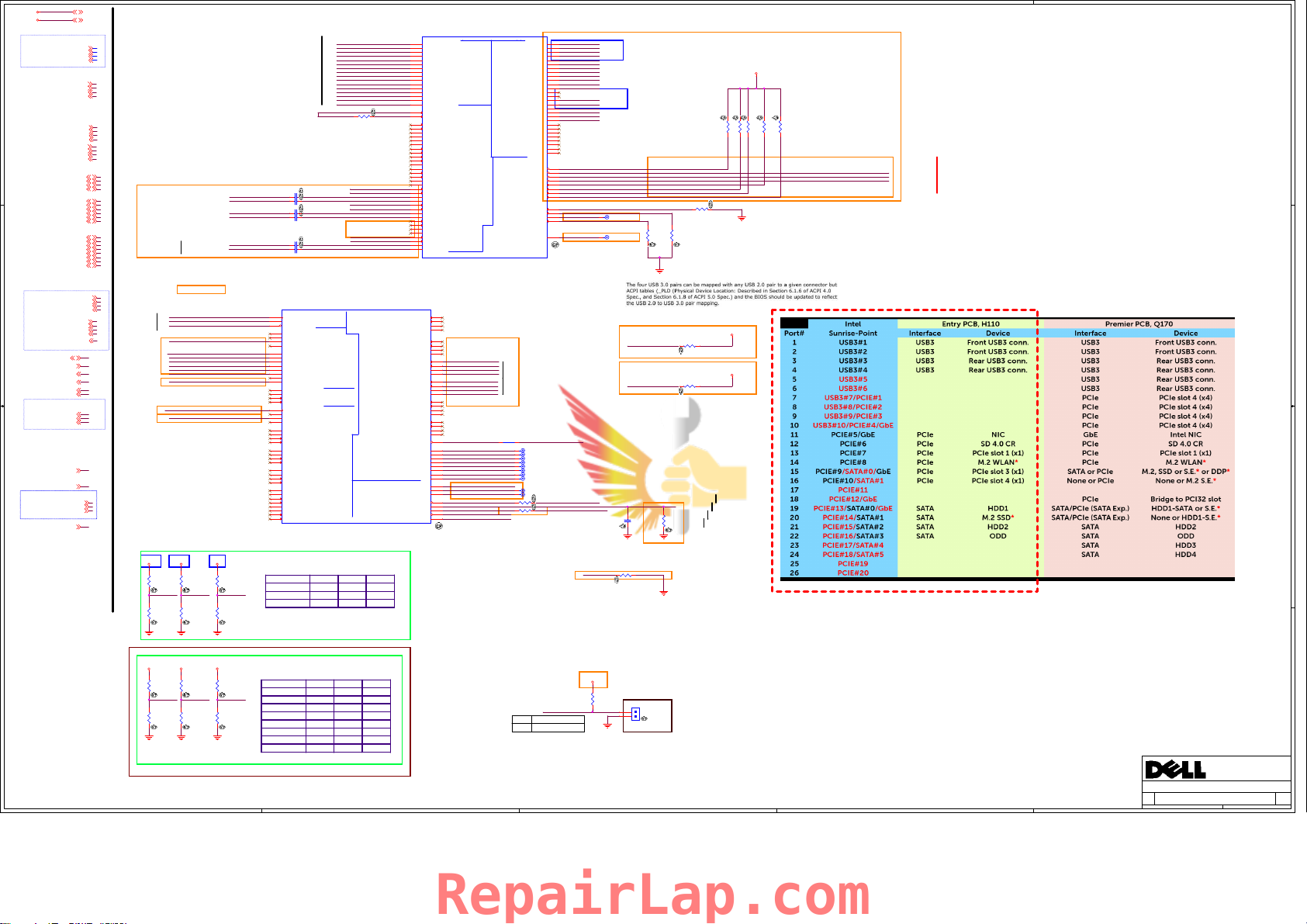

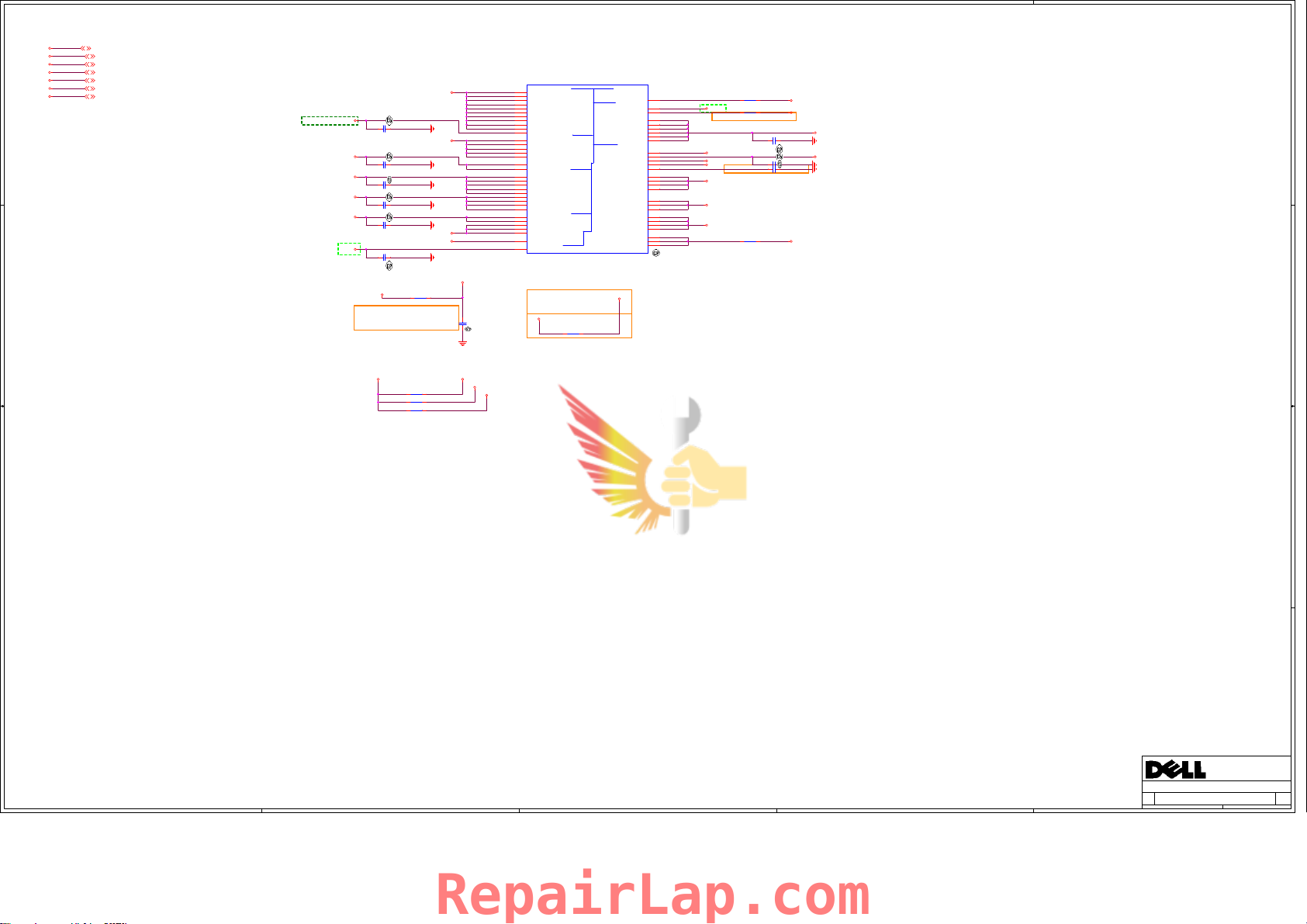

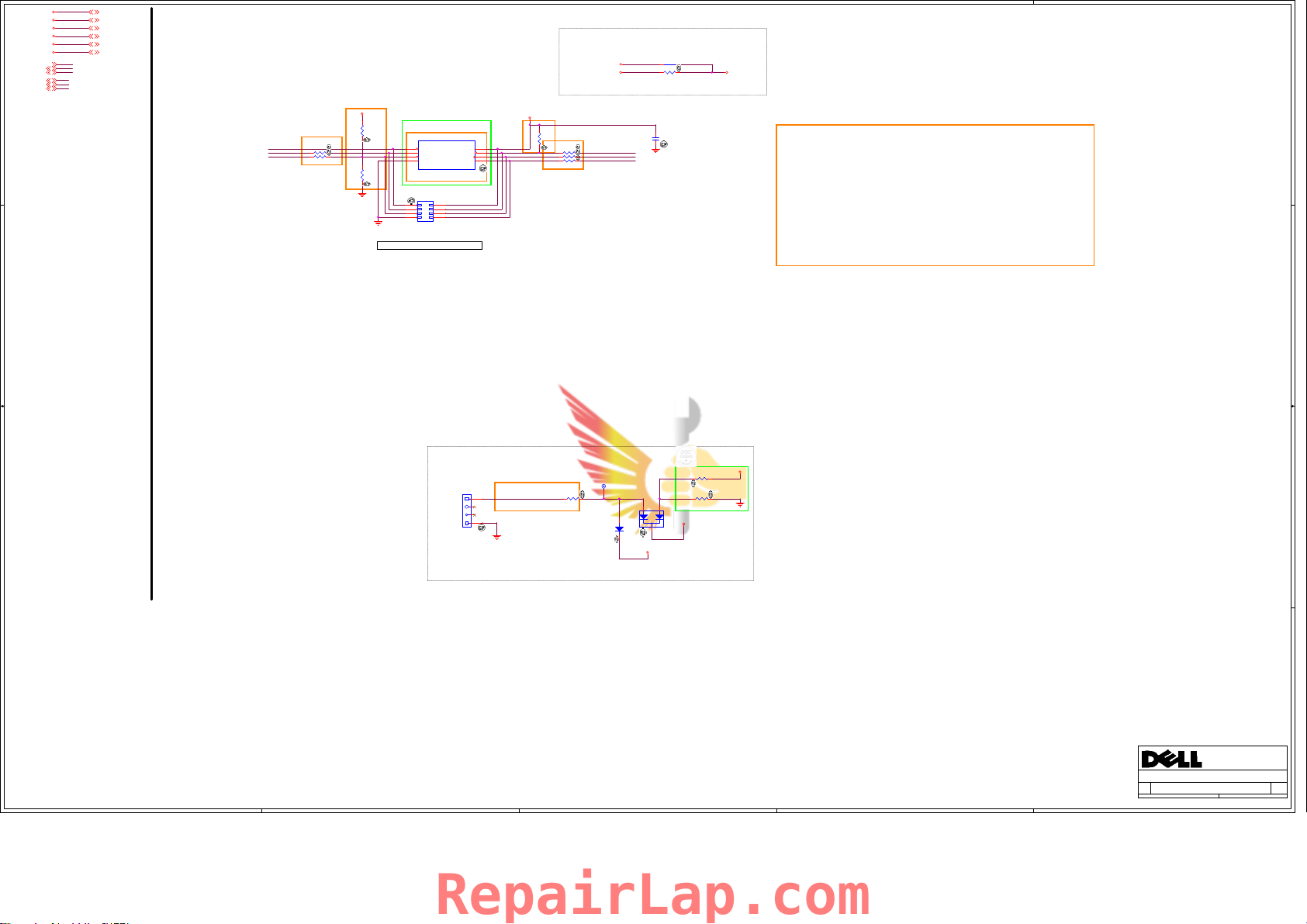

DDR DATA

M_DATA_ A[0..63]12

M_DATA_ B[0..63]13

M_DQS_A _DP[0..7]12

M_DQS_A _DN[0..7]12

M_DQS_B _DP[0..7]13

M_DQS_B _DN[0..7]13

DDR CMD/ADD

D D

C C

M_MAA_A[0..1 5]12

M_MAA_B[0..1 5]13

M_SBS_A 012

M_SBS_A 112

M_SBS_A 212

M_SBS_B 013

M_SBS_B 113

M_SBS_B 213

DDR CTRL

M_SCS_A _N012

M_SCS_A _N112

M_SCKE_ A012

M_SCKE_ A112

M_ODT_A 012

M_ODT_A 112

M_SCS_B _N013

M_SCS_B _N113

M_SCKE_ B013

M_SCKE_ B113

M_ODT_B 013

M_ODT_B 113

DDR CLOCK

CK_M_DD R0_A_D P12

CK_M_DD R0_A_D N12

CK_M_DD R1_A_D P12

CK_M_DD R1_A_D N12

CK_M_DD R0_B_D P13

CK_M_DD R0_B_D N13

CK_M_DD R1_B_D P13

CK_M_DD R1_B_D N13

DDR OTHERS

DIMM_DQ_ CPU_VREF _A12

DIMM_DQ_ CPU_VREF _B13

DIMM_CA_ VREF_A12

DIMM_CA_ VREF_B13

M_WE_A _N12

M_CAS_A _N12

M_RAS_A _N12

M_WE_B _N13

M_CAS_B _N13

M_RAS_B _N13

Can be left as no connects

if no support ECC.

06/24 Allen modify

M_DATA_ A5

M_DATA_ A1

M_DATA_ A2

M_DATA_ A3

M_DATA_ A4

M_DATA_ A0

M_DATA_ A6

M_DATA_ A7

M_DATA_ A13

M_DATA_ A9

M_DATA_ A10

M_DATA_ A11

M_DATA_ A8

M_DATA_ A12

M_DATA_ A14

M_DATA_ A15

M_DATA_ A21

M_DATA_ A16

M_DATA_ A18

M_DATA_ A19

M_DATA_ A20

M_DATA_ A17

M_DATA_ A22

M_DATA_ A23

M_DATA_ A25

M_DATA_ A28

M_DATA_ A27

M_DATA_ A31

M_DATA_ A29

M_DATA_ A24

M_DATA_ A30

M_DATA_ A26

M_DATA_ A32

M_DATA_ A36

M_DATA_ A34

M_DATA_ A35

M_DATA_ A33

M_DATA_ A37

M_DATA_ A39

M_DATA_ A38

M_DATA_ A44

M_DATA_ A40

M_DATA_ A47

M_DATA_ A43

M_DATA_ A41

M_DATA_ A45

M_DATA_ A46

M_DATA_ A42

M_DATA_ A49

M_DATA_ A54

M_DATA_ A53

M_DATA_ A50

M_DATA_ A52

M_DATA_ A51

M_DATA_ A48

M_DATA_ A55

M_DATA_ A61

M_DATA_ A63

M_DATA_ A60

M_DATA_ A59

M_DATA_ A62

M_DATA_ A57

M_DATA_ A58

M_DATA_ A56

CPU1A

AE38

DDR0_DQ0

AE37

DDR0_DQ1

AG38

DDR0_DQ2

AG37

DDR0_DQ3

AE39

DDR0_DQ4

AE40

DDR0_DQ5

AG39

DDR0_DQ6

AG40

DDR0_DQ7

AJ38

DDR0_DQ8

AJ37

DDR0_DQ9

AL38

DDR0_DQ10

AL37

DDR0_DQ11

AJ40

DDR0_DQ12

AJ39

DDR0_DQ13

AL39

DDR0_DQ14

AL40

DDR0_DQ15

AN38

DDR0_DQ16/DDR0_DQ32

AN40

DDR0_DQ17/DDR0_DQ33

AR38

DDR0_DQ18/DDR0_DQ34

AR37

DDR0_DQ19/DDR0_DQ35

AN39

DDR0_DQ20/DDR0_DQ36

AN37

DDR0_DQ21/DDR0_DQ37

AR39

DDR0_DQ22/DDR0_DQ38

AR40

DDR0_DQ23/DDR0_DQ39

AW37

DDR0_DQ24/DDR0_DQ40

AU38

DDR0_DQ25/DDR0_DQ41

AV35

DDR0_DQ26/DDR0_DQ42

AW35

DDR0_DQ27/DDR0_DQ43

AU37

DDR0_DQ28/DDR0_DQ44

AV37

DDR0_DQ29/DDR0_DQ45

AT35

DDR0_DQ30/DDR0_DQ46

AU35

DDR0_DQ31/DDR0_DQ47

AY8

DDR0_DQ32/DDR1_DQ0

AW8

DDR0_DQ33/DDR1_DQ1

AV6

DDR0_DQ34/DDR1_DQ2

AU6

DDR0_DQ35/DDR1_DQ3

AU8

DDR0_DQ36/DDR1_DQ4

AV8

DDR0_DQ37/DDR1_DQ5

AW6

DDR0_DQ38/DDR1_DQ6

AY6

DDR0_DQ39/DDR1_DQ7

AY4

DDR0_DQ40/DDR1_DQ8

AV4

DDR0_DQ41/DDR1_DQ9

AT1

DDR0_DQ42/DDR1_DQ10

AT2

DDR0_DQ43/DDR1_DQ11

AV3

DDR0_DQ44/DDR1_DQ12

AW4

DDR0_DQ45/DDR1_DQ13

AT4

DDR0_DQ46/DDR1_DQ14

AT3

DDR0_DQ47/DDR1_DQ15

AP2

DDR0_DQ48/DDR1_DQ32

AM4

DDR0_DQ49/DDR1_DQ33

AP3

DDR0_DQ50/DDR1_DQ34

AM3

DDR0_DQ51/DDR1_DQ35

AP4

DDR0_DQ52/DDR1_DQ36

AM2

DDR0_DQ53/DDR1_DQ37

AP1

DDR0_DQ54/DDR1_DQ38

AM1

DDR0_DQ55/DDR1_DQ39

AK3

DDR0_DQ56/DDR1_DQ40

AH1

DDR0_DQ57/DDR1_DQ41

AK4

DDR0_DQ58/DDR1_DQ42

AH2

DDR0_DQ59/DDR1_DQ43

AH4

DDR0_DQ60/DDR1_DQ44

AK2

DDR0_DQ61/DDR1_DQ45

AH3

DDR0_DQ62/DDR1_DQ46

AK1

DDR0_DQ63/DDR1_DQ47

AU33

DDR0_ECC0

AT33

DDR0_ECC1

AW33

DDR0_ECC2

AV31

DDR0_ECC3

AU31

DDR0_ECC4

AV33

DDR0_ECC5

AW31

DDR0_ECC6

AY31

DDR0_ECC7

SKYLAKE -1

DDR CHANNEL A

SKYLAKE

LGA1151

DDR0_BA0/DDR0_CAB4/DDR0_BA0

DDR0_BA1/DDR0_CAB6/DDR0_BA1

DDR0_BA2/DDR0_CAA5/DDR0_BG0

DDR0_RAS#/DDR0_CAB3/DDR0_MA16

DDR0_WE#/DDR0_CAB2/DDR0_MA14

DDR0_CAS#/DDR0_CAB1/DDR0_MA15

DDR0_MA0/DDR0_CAB9/DDR0_MA0

DDR0_MA1/DDR0_CAB8/DDR0_MA1

DDR0_MA2/DDR0_CAB5/DDR0_MA2

DDR0_MA5/DDR0_CAA0/DDR0_MA5

DDR0_MA6/DDR0_CAA2/DDR0_MA6

DDR0_MA7/DDR0_CAA4/DDR0_MA7

DDR0_MA8/DDR0_CAA3/DDR0_MA8

DDR0_MA9/DDR0_CAA1/DDR0_MA9

DDR0_MA10/DDR0_CAB7/DDR0_MA10

DDR0_MA11/DDR0_CAA7/DDR0_MA11

DDR0_MA12/DDR0_CAA6/DDR0_MA12

DDR0_MA13/DDR0_CAB0/DDR0_MA13

DDR0_MA14/DDR0_CAA9/DDR0_BG1

DDR0_MA15/DDR0_CAA8/DDR0_ACT#

All types of DIMMs are DDR3L

DDR0_CKP0

DDR0_CKN0

DDR0_CKP1

DDR0_CKN1

DDR0_CKP2

DDR0_CKN2

DDR0_CKP3

DDR0_CKN3

DDR0_CKE0

DDR0_CKE1

DDR0_CKE2

DDR0_CKE3

DDR0_CS#0

DDR0_CS#1

DDR0_CS#2

DDR0_CS#3

DDR0_ODT0

DDR0_ODT1

DDR0_ODT2

DDR0_ODT3

DDR0_MA3

DDR0_MA4

DDR0_PAR

DDR0_ALERT#

DDR0_DQSN0

DDR0_DQSN1

DDR0_DQSN2/DDR0_DQSN4

DDR0_DQSN3/DDR0_DQSN5

DDR0_DQSN4/DDR1_DQSN0

DDR0_DQSN5/DDR1_DQSN1

DDR0_DQSN6/DDR1_DQSN4

DDR0_DQSN7/DDR1_DQSN5

DDR0_DQSP0

DDR0_DQSP1

DDR0_DQSP2/DDR0_DQSP4

DDR0_DQSP3/DDR0_DQSP5

DDR0_DQSP4/DDR1_DQSP0

DDR0_DQSP5/DDR1_DQSP1

DDR0_DQSP6/DDR1_DQSP4

DDR0_DQSP7/DDR1_DQSP5

DDR0_DQSP8

DDR0_DQSN8

1 OF 12

4

AW18

AV18

AW17

AY17

AW16

AV16

AT16

AU16

AY24

AW24

AV24

AV25

AW12

AU11

AV13

AV10

AW11

AU14

AU12

AY10

AY13

AV15

AW23

AW13

AV14

AY11

AW15

AU18

AU17

AV19

AT19

AU20

AV20

AU21

AT20

AT22

AY14

AU22

AV22

AV12

AV23

AU24

AY15

AT23

AF39

AK39

AP39

AU36

AW7

AU3

AN3

AJ3

AF38

AK38

AP38

AV36

AV7

AU2

AN2

AJ2

AV32

AU32

CK_M_DD R0_A_D P

CK_M_DD R0_A_D N

CK_M_DD R1_A_D P

CK_M_DD R1_A_D N

M_SCKE_ A0

M_SCKE_ A1

M_SCS_A _N0

M_SCS_A _N1

M_ODT_A 0

M_ODT_A 1

M_SBS_A 0

M_SBS_A 1

M_SBS_A 2

M_RAS_A _N

M_WE_A _N

M_CAS_A _N

M_MAA_A0

M_MAA_A1

M_MAA_A2

M_MAA_A3

M_MAA_A4

M_MAA_A5

M_MAA_A6

M_MAA_A7

M_MAA_A8

M_MAA_A9

M_MAA_A1 0

M_MAA_A1 1

M_MAA_A1 2

M_MAA_A1 3

M_MAA_A1 4

M_MAA_A1 5

TP_DDR 0_PAR

DDR0_A LERT#

M_DQS_A _DN0

M_DQS_A _DN1

M_DQS_A _DN2

M_DQS_A _DN3

M_DQS_A _DN4

M_DQS_A _DN5

M_DQS_A _DN6

M_DQS_A _DN7

M_DQS_A _DP0

M_DQS_A _DP1

M_DQS_A _DP2

M_DQS_A _DP3

M_DQS_A _DP4

M_DQS_A _DP5

M_DQS_A _DP6

M_DQS_A _DP7

TP_DDR 0_DQSP 8

TP_DDR 0_DQSN8

NOTE CMD SIGNALS FOR DIFFERENT MEMORY TECHINOLOGIES:

LEFT TO RIGHT: DDR3L/LPDDR3/DDR4

1

1 2

R1 0R040 2-PAD

06/24 Allen modify

1

TP3 TPAD28

1

TP4 TPAD28

TP1 TPAD28

THIS IS FOR RVP10 ONLY

Short PAD ,if Layout placement inpact

3

06/24 Allen modify

M_DATA_ B4

M_DATA_ B5

M_DATA_ B7

M_DATA_ B3

M_DATA_ B1

M_DATA_ B0

M_DATA_ B6

M_DATA_ B2

M_DATA_ B13

M_DATA_ B9

M_DATA_ B14

M_DATA_ B15

M_DATA_ B12

M_DATA_ B8

M_DATA_ B10

M_DATA_ B11

M_DATA_ B16

M_DATA_ B20

M_DATA_ B22

M_DATA_ B23

M_DATA_ B17

M_DATA_ B21

M_DATA_ B18

M_DATA_ B19

M_DATA_ B28

M_DATA_ B24

M_DATA_ B30

M_DATA_ B26

M_DATA_ B25

M_DATA_ B29

M_DATA_ B27

M_DATA_ B31

M_DATA_ B32

M_DATA_ B33

M_DATA_ B38

M_DATA_ B34

M_DATA_ B36

M_DATA_ B37

M_DATA_ B39

M_DATA_ B35

M_DATA_ B44

M_DATA_ B45

M_DATA_ B46

M_DATA_ B42

M_DATA_ B41

M_DATA_ B40

M_DATA_ B47

M_DATA_ B43

M_DATA_ B52

M_DATA_ B53

M_DATA_ B55

M_DATA_ B51

M_DATA_ B48

M_DATA_ B49

M_DATA_ B54

M_DATA_ B50

M_DATA_ B61

M_DATA_ B56

M_DATA_ B63

M_DATA_ B58

M_DATA_ B60

M_DATA_ B57

M_DATA_ B59

M_DATA_ B62

Can be left as no connects

if no support ECC.

CPU1B

AD34

DDR1_DQ0/DDR0_DQ16

AD35

DDR1_DQ1/DDR0_DQ17

AG35

DDR1_DQ2/DDR0_DQ18

AH35

DDR1_DQ3/DDR0_DQ19

AE35

DDR1_DQ4/DDR0_DQ20

AE34

DDR1_DQ5/DDR0_DQ21

AG34

DDR1_DQ6/DDR0_DQ22

AH34

DDR1_DQ7/DDR0_DQ23

AK35

DDR1_DQ8/DDR0_DQ24

AL35

DDR1_DQ9/DDR0_DQ25

AK32

DDR1_DQ10/DDR0_DQ26

AL32

DDR1_DQ11/DDR0_DQ27

AK34

DDR1_DQ12/DDR0_DQ28

AL34

DDR1_DQ13/DDR0_DQ29

AK31

DDR1_DQ14/DDR0_DQ30

AL31

DDR1_DQ15/DDR0_DQ31

AP35

DDR1_DQ16/DDR0_DQ48

AN35

DDR1_DQ17/DDR0_DQ49

AN32

DDR1_DQ18/DDR0_DQ50

AP32

DDR1_DQ19/DDR0_DQ51

AN34

DDR1_DQ20/DDR0_DQ52

AP34

DDR1_DQ21/DDR0_DQ53

AN31

DDR1_DQ22/DDR0_DQ54

AP31

DDR1_DQ23/DDR0_DQ55

AL29

DDR1_DQ24/DDR0_DQ56

AM29

DDR1_DQ25/DDR0_DQ57

AP29

DDR1_DQ26/DDR0_DQ58

AR29

DDR1_DQ27/DDR0_DQ59

AM28

DDR1_DQ28/DDR0_DQ60

AL28

DDR1_DQ29/DDR0_DQ61

AR28

DDR1_DQ30/DDR0_DQ62

AP28

DDR1_DQ31/DDR0_DQ63

AR12

DDR1_DQ32/DDR1_DQ16

AP12

DDR1_DQ33/DDR1_DQ17

AM13

DDR1_DQ34/DDR1_DQ18

AL13

DDR1_DQ35/DDR1_DQ19

AR13

DDR1_DQ36/DDR1_DQ20

AP13

DDR1_DQ37/DDR1_DQ21

AM12

DDR1_DQ38/DDR1_DQ22

AL12

DDR1_DQ39/DDR1_DQ23

AP10

DDR1_DQ40/DDR1_DQ24

AR10

DDR1_DQ41/DDR1_DQ25

AR7

DDR1_DQ42/DDR1_DQ26

AP7

DDR1_DQ43/DDR1_DQ27

AR9

DDR1_DQ44/DDR1_DQ28

AP9

DDR1_DQ45/DDR1_DQ29

AR6

DDR1_DQ46/DDR1_DQ30

AP6

DDR1_DQ47/DDR1_DQ31

AM10

DDR1_DQ48

AL10

DDR1_DQ49

AM7

DDR1_DQ50

AL7

DDR1_DQ51

AM9

DDR1_DQ52

AL9

DDR1_DQ53

AM6

DDR1_DQ54

AL6

DDR1_DQ55

AJ6

DDR1_DQ56

AJ7

DDR1_DQ57

AE6

DDR1_DQ58

AF7

DDR1_DQ59

AH7

DDR1_DQ60

AH6

DDR1_DQ61

AE7

DDR1_DQ62

AF6

DDR1_DQ63

AR25

DDR1_ECC0

AR26

DDR1_ECC1

AM26

DDR1_ECC2

AM25

DDR1_ECC3

AP26

DDR1_ECC4

AP25

DDR1_ECC5

AL25

DDR1_ECC6

AL26

DDR1_ECC7

SKYLAKE -1

DDR CHANNEL B

SKYLAKE

LGA1151

DDR1_RAS#/DDR1_CAB3/DDR1_MA16

DDR1_WE#/DDR1_CAB2/DDR1_MA14

DDR1_CAS#/DDR1_CAB1/DDR1_MA15

DDR1_BA0/DDR1_CAB4/DDR1_BA0

DDR1_BA1/DDR1_CAB6/DDR1_BA1

DDR1_BA2/DDR1_CAA5/DDR1_BG0

DDR1_MA0/DDR1_CAB9/DDR1_MA0

DDR1_MA1/DDR1_CAB8/DDR1_MA1

DDR1_MA2/DDR1_CAB5/DDR1_MA2

DDR1_MA5/DDR1_CAA0/DDR1_MA5

DDR1_MA6/DDR1_CAA2/DDR1_MA6

DDR1_MA7/DDR1_CAA4/DDR1_MA7

DDR1_MA8/DDR1_CAA3/DDR1_MA8

DDR1_MA9/DDR1_CAA1/DDR1_MA9

DDR1_MA10/DDR1_CAB7/DDR1_MA10

DDR1_MA11/DDR1_CAA7/DDR1_MA11

DDR1_MA12/DDR1_CAA6/DDR1_MA12

DDR1_MA13/DDR1_CAB0/DDR1_MA13

DDR1_MA14/DDR1_CAA9/DDR1_BG1

DDR1_MA15/DDR1_CAA8/DDR1_ACT#

DDR1_DQSN0/DDR0_DQSN2

DDR1_DQSN1/DDR0_DQSN3

DDR1_DQSN2/DDR0_DQSN6

DDR1_DQSN3/DDR0_DQSN7

DDR1_DQSN4/DDR1_DQSN2

DDR1_DQSN5/DDR1_DQSN3

DDR1_DQSP0/DDR0_DQSP2

DDR1_DQSP1/DDR0_DQSP3

DDR1_DQSP2/DDR0_DQSP6

DDR1_DQSP3/DDR0_DQSP7

DDR1_DQSP4/DDR1_DQSP2

DDR1_DQSP5/DDR1_DQSP3

DDR1_CKP0

DDR1_CKN0

DDR1_CKP1

DDR1_CKN1

DDR1_CKP2

DDR1_CKN2

DDR1_CKP3

DDR1_CKN3

DDR1_CKE0

DDR1_CKE1

DDR1_CKE2

DDR1_CKE3

DDR1_CS#0

DDR1_CS#1

DDR1_CS#2

DDR1_CS#3

DDR1_ODT0

DDR1_ODT1

DDR1_ODT2

DDR1_ODT3

DDR1_MA3

DDR1_MA4

DDR1_PAR

DDR1_ALERT#

DDR1_DQSN6

DDR1_DQSN7

DDR1_DQSP6

DDR1_DQSP7

DDR1_DQSP8

DDR1_DQSN8

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

2

2 OF 12

CK_M_DD R0_B_D P

AM20

CK_M_DD R0_B_D N

AM21

CK_M_DD R1_B_D P

AP22

CK_M_DD R1_B_D N

AP21

AN20

AN21

AP19

AP20

M_SCKE_ B0

AY29

M_SCKE_ B1

AV29

AW29

AU29

M_SCS_B _N0

AP17

M_SCS_B _N1

AN15

AN17

AM15

M_ODT_B 0

AM16

M_ODT_B 1

AL16

AP15

AL15

M_RAS_B _N

AN18

M_WE_B _N

AL17

M_CAS_B _N

AP16

M_SBS_B 0

AL18

M_SBS_B 1

AM18

M_SBS_B 2

AW28

M_MAA_B0

AL19

M_MAA_B1

AL22

M_MAA_B2

AM22

M_MAA_B3

AM23

AP23

AL23

AW26

AY26

AU26

AW27

AP18

AU27

AV27

AR15

AY28

AU28

AL20

AY25

AF34

AK33

AN33

AN29

AN13

AR8

AM8

AG6

AF35

AL33

AP33

AN28

AN12

AP8

AL8

AG7

AN25

AN26

AB40

AC40

AC39

M_MAA_B4

M_MAA_B5

M_MAA_B6

M_MAA_B7

M_MAA_B8

M_MAA_B9

M_MAA_B1 0

M_MAA_B1 1

M_MAA_B1 2

M_MAA_B1 3

M_MAA_B1 4

M_MAA_B1 5

TP_DDR 1_PAR

DDR1_A LERT#

R2 0R04 02-PAD

M_DQS_B _DN0

M_DQS_B _DN1

M_DQS_B _DN2

M_DQS_B _DN3

M_DQS_B _DN4

M_DQS_B _DN5

M_DQS_B _DN6

M_DQS_B _DN7

M_DQS_B _DP0

M_DQS_B _DP1

M_DQS_B _DP2

M_DQS_B _DP3

M_DQS_B _DP4

M_DQS_B _DP5

M_DQS_B _DP6

M_DQS_B _DP7

TP_DDR 1_DQSP 8

TP_DDR 1_DQSN8

DIMM_CA_ CPU_VREF _A

DIMM_DQ_ CPU_VREF _A

DIMM_DQ_ CPU_VREF _B

C2

SCD1U16 V2KX-3D LGP

NOTE CMD SIGNALS FOR DIFFERENT MEMORY TECHINOLOGIES:

LEFT TO RIGHT: DDR3L/LPDDR3/DDR4

1

TP2 TPAD28

1 2

THIS IS FOR RVP10 ONLY

Short PAD ,if Layout placement inpact

06/24 Allen modify

1

TP5 TPAD2 8

1

TP6 TPAD2 8

12

12

C1

SCD1U16 V2KX-3D LGP

1

DIMM_CA_ CPU_VREF _A

B B

A A

5

4

3

C3

SCD022 U16V2KX -3DLGP

2 1

DIMM_CA_ CPU_VREF _RC

12

R5

24D9R2 F-L-GP

1 2

R3 2R 2F-GP

1 2

R4 2R 2F-GP

DIMM_CA_ VREF_A

DIMM_CA_ VREF_B

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, S ec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, S ec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, S ec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 22 1, Taiwan, R.O.C.

Taipei Hsien 22 1, Taiwan, R.O.C.

Title

Title

Title

003_CP U_DDRA_ DDRB

003_CP U_DDRA_ DDRB

003_CP U_DDRA_ DDRB

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

COLORADO MLK SKYLAKE-S

COLORADO MLK SKYLAKE-S

COLORADO MLK SKYLAKE-S

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

1

Taipei Hsien 22 1, Taiwan, R.O.C.

3 1 07

3 1 07

3 1 07

-2D

-2D

-2D

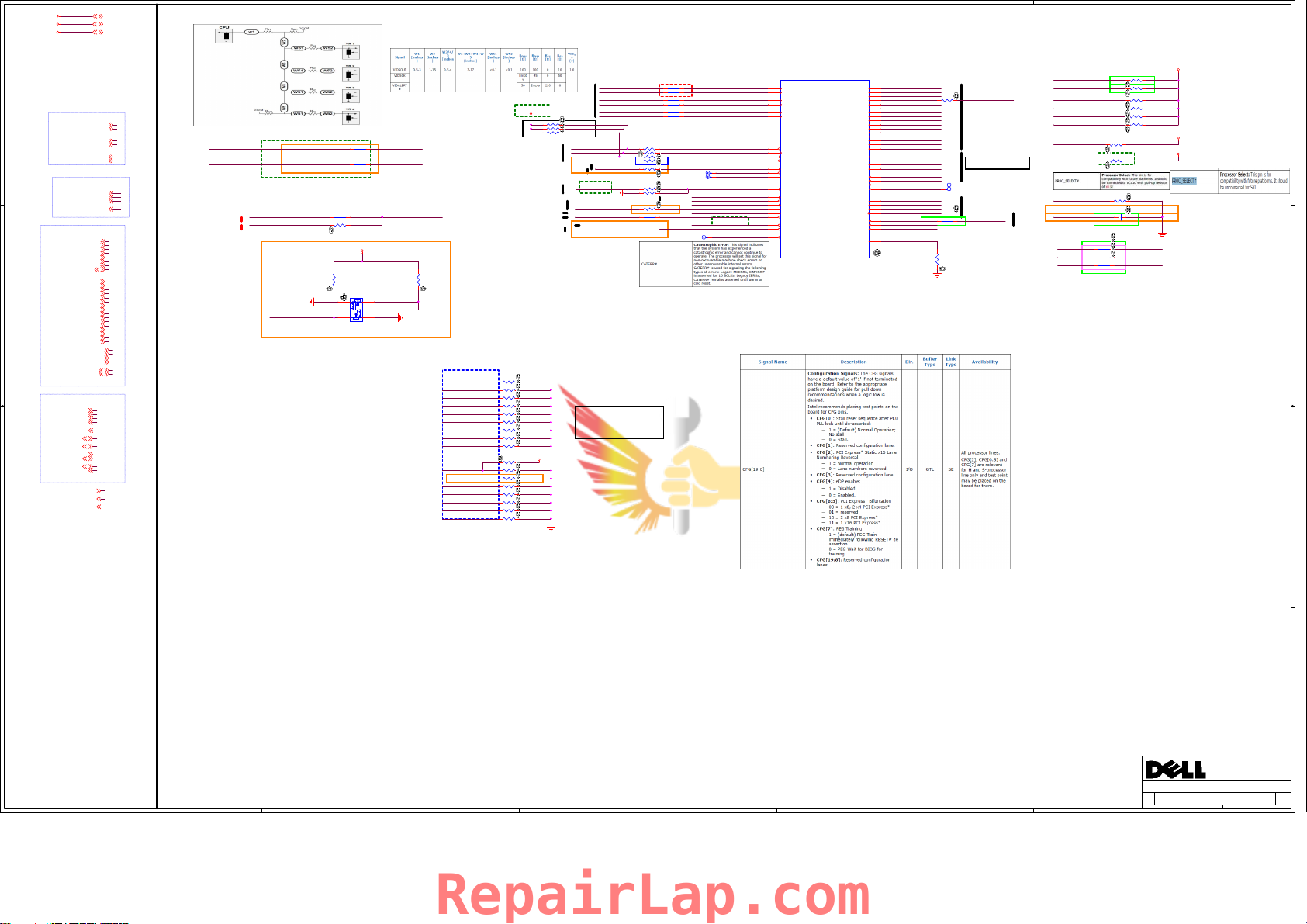

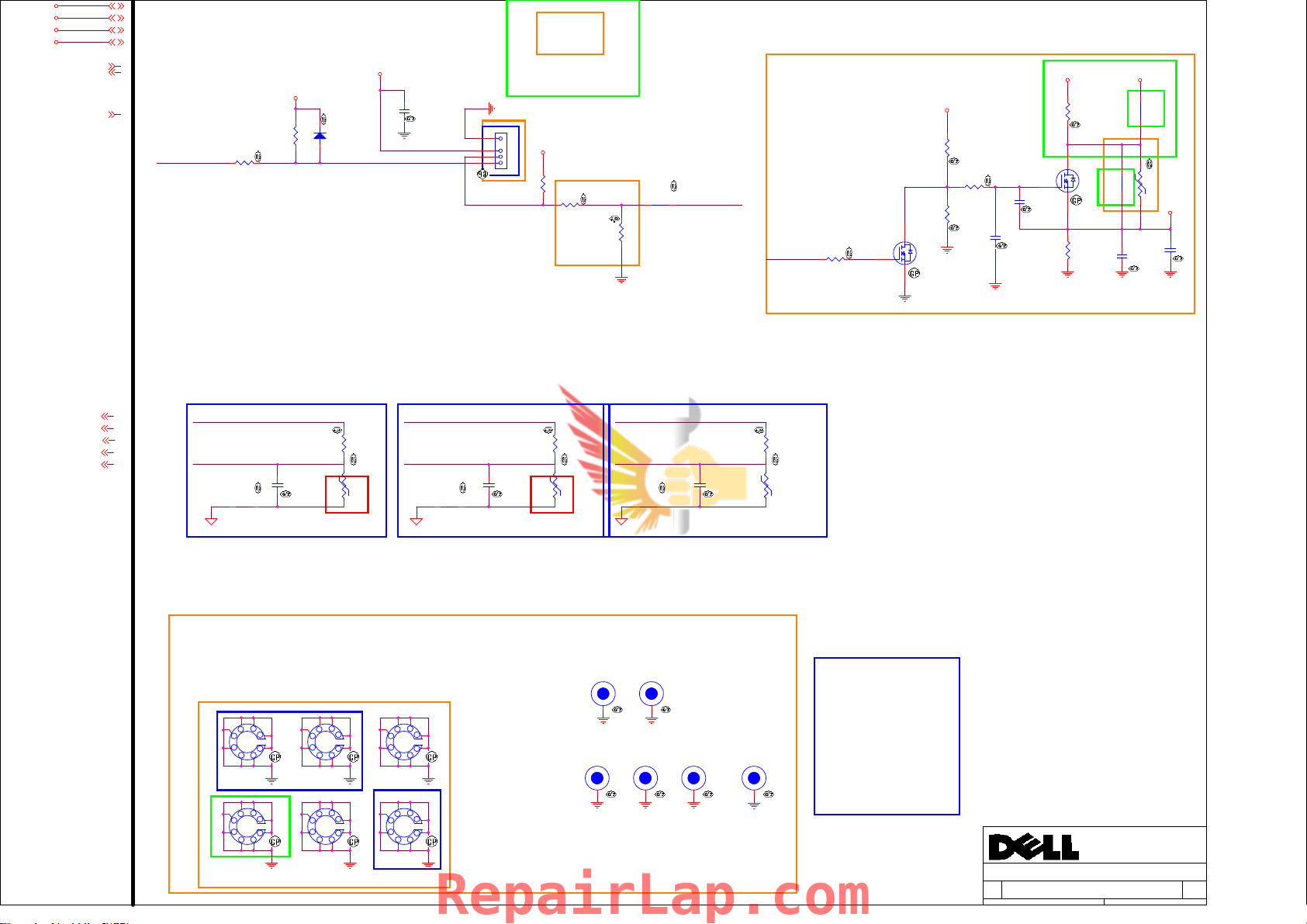

V_CPU_S T_PLL

RepairLap.com

SB3V

V_CPU_I O

5

V_CPU_S T_PLL 7,44,99

SB3V 15 ,17,18,20 ,21,24,25 ,31,35,38,4 0,42,47,4 8,51,53,5 5,56,57,5 8,59,61,6 4,86

V_CPU_I O 5 ,7,8,9,48,9 9

4

VIDSCK

VIDSOUT

VIDALERT#

Need to add Pull UP on both C PU and VR side.

3

2

1

Double Check

12

12

1-003 05/28 Allen modify

PCH_JTA G_TDO

PCH_JTA G_TDI

PCH_JTA G_TMS

V_CPU_S T_PLL

12

12

12

12

12

12

SB3V

V_CPU_I O

07/17 Allen del

To CPU XDP

1A020 04/20 Allen modify

H_TDI

1A020 04/20 Allen modify

H_TMS

1A020 04/20 Allen modify

PCH_THER MTRIP_N

H_PREQ_ N

H_PROCHO T_N

H_TDO

If the SKTOCC no use, del this sche

H_SKTOC C_N

SKL_CNL _N

H_TCK

H_PROCHO T_N

07/14 Allen add

H_TDO

R40 0R0402-P AD-2-GP

H_TDI

R43 0R0402-P AD-2-GP

H_TMS

R44 0R0402-P AD-2-GP

R80242 51R2F-2-G P

R80241 51R2F-2-G P

PR1 1 KR2J-1-G P

R8 51R2F -2-GP

(R_)

R12 51R2F-2-G P

R14 51R2F-2-G P

(R_)

R20 10KR2J-3 -GP

R24 10KR2J-3 -GP

(R_)

This RES Value unconfirm.

1 2

R32 51R2F-2 -GP

1 2

C12125

SC47P5 0V2JN-5D LGP

SC011 11/14 BOM cost1A015 04/14 Allen modify

1 2

1 2

1 2

LGA1151

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

BPM#0

BPM#1

BPM#2

BPM#3

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST#

PROC_PREQ#

PROC_PRDY#

CFG_RCOMP

5 OF 12

SKL_PC UDEBUG_0

H15

CFG0

SKL_PC UDEBUG_1

F15

CFG1

SKL_PC UDEBUG_2

F16

CFG2

SKL_PC UDEBUG_3

H16

CFG3

SKL_PC UDEBUG_4

F19

CFG4

SKL_PC UDEBUG_5

H18

CFG5

SKL_PC UDEBUG_6

G21

CFG6

SKL_PC UDEBUG_7

H20

CFG7

SKL_PC UDEBUG_8

G16

CFG8

SKL_PC UDEBUG_9

E16

CFG9

SKL_PC UDEBUG_10

F17

SKL_PC UDEBUG_11

H17

SKL_PC UDEBUG_12

G20

SKL_PC UDEBUG_13

F20

SKL_PC UDEBUG_14

F21

SKL_PC UDEBUG_15

H19

SKL_PC USTB_0_ DN

E14

SKL_PC USTB_0_ DP

F14

SKL_PC USTB_1_ DN

G18

SKL_PC USTB_1_ DP

F18

SKL_XD P_MBP_0

D16

SKL_XD P_MBP_1

D17

TP_CPU_ G38

G14

TP_CPU_ H37

H14

H_TDO

H13

H_TDI

G12

H_TMS

F13

H_TCK

F11

H_TRST_ N

F12

H_PREQ_ N

B9

B10

M11

H_PRDY_N

TPEV_C FG_RCO MP

R39 0R0402-P AD-2-GP

1 2

R10

1KR2J-1 -GP

1

1

1 2

12

R45

49D9R2 F-GP

XDP_PC UDERBUG_3

To CPU XDP

Differential pairs

To CPU XDP

TP9 TP AD28

TP10 TPAD28

To PCH XDP

H_TRST_ N_R

AC36

AC38

AC37

AB35

AB36

W5

W4

W1

W2

K9

J9

E39

E38

E40

C39

U2

F8

E7

E8

D8

G7

D11

D13

CPU1E

BCLKP

BCLKN

PCI_BCLKP

PCI_BCLKN

CLK24P

CLK24N

VIDALERT#

VIDSCK

VIDSOUT

PROCHOT#

DDR_VTT_CNTL

ZVM#

RSVD_AC37

VCCST_PWRGD

PROCPWRGD

RESET#

PM_SYNC

PM_DOWN

PECI

THERMTRIP#

SKTOCC#

PROC_SELECT#

CATERR#

SKYLAKE -1

SKYLAKE

Only left one 0 ohm on it

PCH_CPU_ BCLK_DP

PCH_CPU_ BCLK_DN

PCH_CPU_ PCIBCLK _DP

D D

C C

B B

CLOCK

PCH_CPU_ BCLK_DP16

PCH_CPU_ BCLK_DN16

PCH_CPU_ PCIBCLK _DP1 6

PCH_CPU_ PCIBCLK _DN16

PCH_CPU_ NSSC_CLK _DP16

PCH_CPU_ NSSC_CLK _DN16

CPU_VCORE

VIDALE RT#44

VIDSCK44

VIDSOUT44

VCCST_ PWRGD4 0,99

XDP

XDP_PC UDERBUG_399

SKL_PC UDEBUG_099

SKL_PC UDEBUG_199

SKL_PC UDEBUG_299

SKL_PC UDEBUG_399

SKL_PC UDEBUG_499

SKL_PC UDEBUG_599

SKL_PC UDEBUG_699

SKL_PC UDEBUG_799

SKL_PC UDEBUG_899

SKL_PC UDEBUG_999

SKL_PC UDEBUG_1099

SKL_PC UDEBUG_1199

SKL_PC UDEBUG_1299

SKL_PC UDEBUG_1399

SKL_PC UDEBUG_1499

SKL_PC UDEBUG_1599

SKL_PC USTB_0_ DP99

SKL_PC USTB_0_ DN99

SKL_PC USTB_1_ DP99

SKL_PC USTB_1_ DN99

SKL_XD P_MBP_099

SKL_XD P_MBP_199

OTHER

H_TRST_ N_R22

H_PM_SYNC17

H_PWRG D15,99

H_SKTOC C_N18

H_PM_DOW N17

PCH_PEC I17

EC_PEC I24

PLTRST _CPU_N1 7,99

H_PROCHO T_N24,43,44

PCH_THER MTRIP_N17,79

VTT_EN50

PCH_JTA G_TDI15

PCH_JTA G_TDO15

PCH_JTA G_TMS15

CPU sideVR side

VIDALE RT#

VIDSCK

VIDSOUT

1 2

R22 0R0402-P AD

1 2

R27 0R0402-P AD

1 2

R30 0R0402-P AD

H_VIDAL ERT_N

H_VIDSC K

H_VIDSO UT

08/18 Allen modify

DDR_VT T_CNTL_ GATE

H_PECIEC_PEC I

12

R1734

10KR2F -2-GP

(R_)

To SIO

H_TDO99

H_TDI99

H_TCK15,99

H_TMS99

H_TRST_ N99

H_PRDY_N99

H_PREQ_ N99

To PCH

06/24 Allen modify

PCH_PEC I

PWR_V TT_EN

VTT_EN

R37 0R0402-P AD

(R_)

12

(R_)

R1735

100KR2 J-1-GP

6

12

R410R2J-2-GP

SB3V

Q1228

2N7002K DW-GP

(75.2700 2.F7C)

2345

1

1 2

PLACE NEAR CPU

from CPU VR

IN CRB Using SLP_S3_N to contr ol VDDQ

CRB using VR_READY in sequence

SEQUENCE need to check

To PCH GPIO to detect CPU in SKT

For future platforms

MCP TERMINATION

SKL_PC UDEBUG_0

SKL_PC UDEBUG_1

SKL_PC UDEBUG_2

SKL_PC UDEBUG_3

SKL_PC UDEBUG_4

SKL_PC UDEBUG_5

SKL_PC UDEBUG_6

SKL_PC UDEBUG_7

SKL_PC UDEBUG_8

SKL_PC UDEBUG_9

SKL_PC UDEBUG_10

SKL_PC UDEBUG_11

SKL_PC UDEBUG_12

SKL_PC UDEBUG_13

SKL_PC UDEBUG_14

SKL_PC UDEBUG_15

1 2

R46 1KR2J-1-G P(R_)

1 2

R47 1KR2J-1-G P(R_)

1 2

R48 1KR2J-1-G P

1 2

R49 1KR2J-1-G P(R_)

1 2

R50 1KR2J-1-G P

1 2

R51 1KR2J-1-G P(R_)

1 2

R52 1KR2J-1-G P(R_)

1 2

R53 1KR2J-1-G P(R_)

1 2

R54 1KR2J-1-G P(R_)

1 2

R56 1KR2J-1-G P(R_)

1 2

R57 1KR2J-1-G P

(R_)

1 2

R58 1KR2J-1-G P(R_)

1 2

R59 1KR2J-1-G P(R_)

1 2

R60 1KR2J-1-G P(R_)

1 2

R61 1KR2J-1-G P(R_)

1 2

R62 1KR2J-1-G P(R_)

from PCH

V_CPU_S T_PLL

1 2

R16 56D2R2F -GP

1 2

R17 45D3R2F -L-GP(R _)

1 2

R18 100R2F-L 1-GP-U

06/24 Allen modify

OPC VR need the pin

To PCH& TO XDP, SEQUENCE need to check

To PCH

PECI to SIO

To PCH

06/24 Allen modify

V_CPU_I O

12

R551KR2J-1-GP (R_)

PCH_CPU_ PCIBCLK _DN

PCH_CPU_ NSSC_CLK _DP

PCH_CPU_ NSSC_CLK _DN

H_VIDAL ERT_N

H_VIDSC K

H_VIDSO UT

H_PROCHO T_N

PWR_V TT_EN

VCCST_ PWRGD VCCST_ PWRGD _CPU

07/14 Allen modify

H_PM_DOW N

PCH_THER MTRIP_N

CFG[2]:PCIE reversed

CFG[4]:EDP Enable

UNSTUFF R56 FOR SPT-H

06/24 Allen modify

Need to check intel. DT and AI O define difference.

UNSTUFF R59 AND R60 FOR SPT-H

1 2

1 2

R6 0R040 2-PAD

R7 0R040 2-PAD

1 2

1 2

R9 0R040 2-PAD

R11 0R0402-P AD

1 2

R13 0R0402-P AD

1 2

R15 0R0402-P AD

R23

220R2F -GP

12

1 2

R25 0R2J-2-GP

1 2

R28 0R2J-2-GP

1 2

R1821 100R2F -L1-GP-U

1 2

R31 0R2J-2-GP

(R_)

1 2

R33 6K04R2F -GP

1 2

R35 2K8R2F-G P

1 2

R79774 20R2J-3-G P

1 2

R38 0R0402-P AD

Debug Pin

SB024 10/06 Allen modify

TP7TPAD2 8

TP8TPAD2 8

TP11TPAD28

PCH_CPU_ BCLK_R_ DP

PCH_CPU_ BCLK_R_ DN

PCH_CPU_ PCIBCLK _R_DP

PCH_CPU_ PCIBCLK _R_DN

CPU_24MHZ_ R_DP

CPU_24MHZ_ R_DN

CPU_VAI DALERT _N

CPU_VID SCK_N

CPU_VID SOUT_N

H_PROCHO T_R_N

DDR_VT T_CNTL

TP_FM_O PC_ZVM_N

1

TP_AC3 7

1

H_PWRG D

PLTRST _CPU_N

H_PM_SYNC

H_PM_DOW N_R

H_PECI

CPU_THER MTRIP_N

H_SKTOC C_N

SKL_CNL _N

TP_H_CA TERR_N

1

A A

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, S ec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, S ec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, S ec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 22 1, Taiwan, R.O.C.

Taipei Hsien 22 1, Taiwan, R.O.C.

Title

Title

Title

004_CP U_CFG/CL OCK

004_CP U_CFG/CL OCK

004_CP U_CFG/CL OCK

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

COLORADO MLK SKYLAKE-S

COLORADO MLK SKYLAKE-S

COLORADO MLK SKYLAKE-S

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Taipei Hsien 22 1, Taiwan, R.O.C.

4 1 07

4 1 07

4 1 07

-2D

-2D

-2D

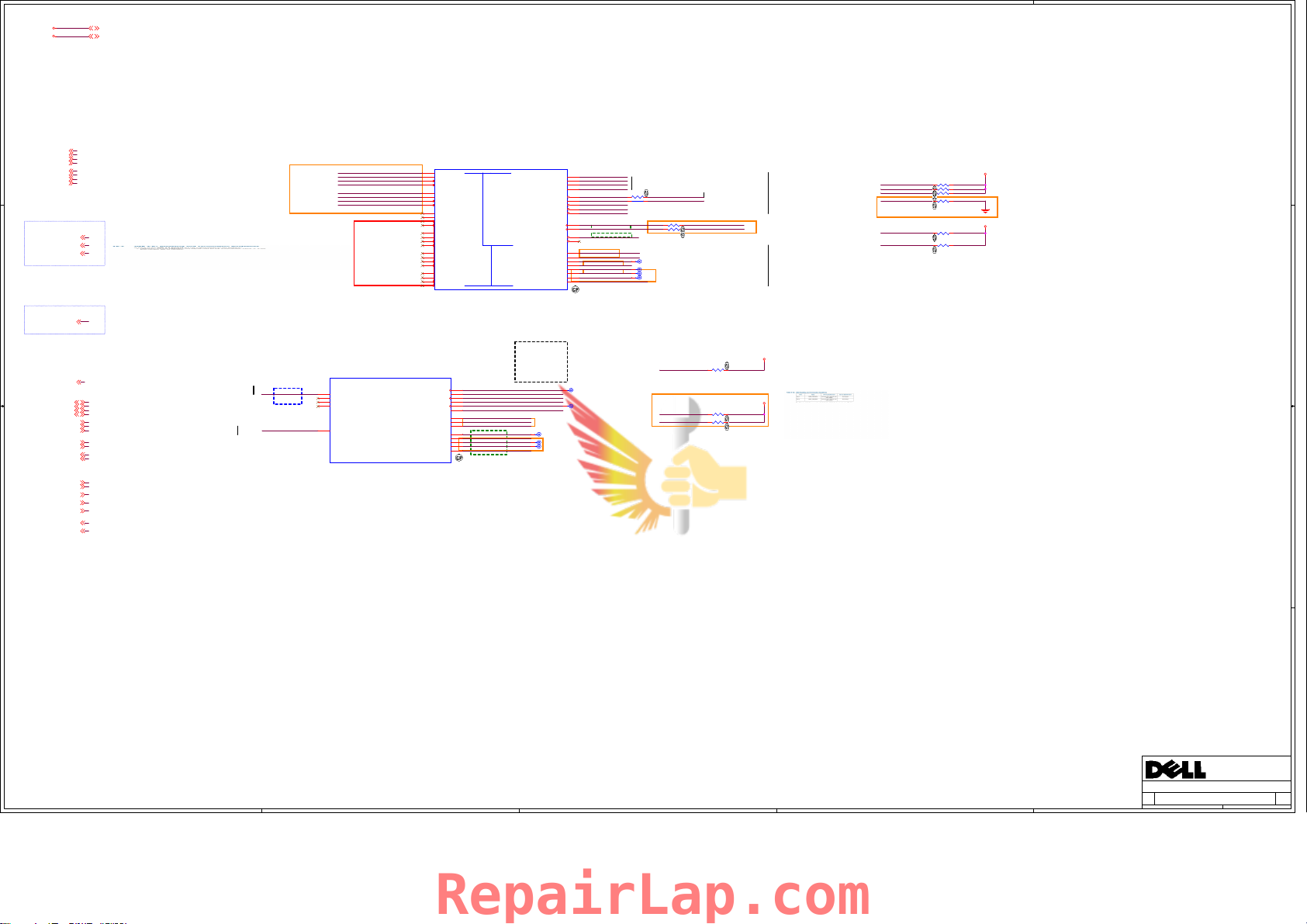

V_CPU_IO

RepairLap.com

5

V_CPU_IO 4,7,8,9,48,99

4

3

2

1

Already SWAP

3 OF 12

PEG_TXP0

PEG_TXN0

PEG_TXP1

PEG_TXN1

PEG_TXP2

PEG_TXN2

PEG_TXP3

PEG_TXN3

PEG_TXP4

PEG_TXN4

PEG_TXP5

PEG_TXN5

PEG_TXP6

PEG_TXN6

PEG_TXP7

PEG_TXN7

PEG_TXP8

PEG_TXN8

PEG_TXP9

PEG_TXN9

PEG_TXP10

PEG_TXN10

PEG_TXP11

PEG_TXN11

PEG_TXP12

PEG_TXN12

PEG_TXP13

PEG_TXN13

PEG_TXP14

PEG_TXN14

PEG_TXP15

PEG_TXN15

DMI_TXP0

DMI_TXN0

DMI_TXP1

DMI_TXN1

DMI_TXP2

DMI_TXN2

DMI_TXP3

DMI_TXN3

A5

A6

B4

B5

C3

C4

D2

D3

E1

E2

F2

F3

G1

G2

H2

H3

J1

J2

K2

K3

L1

L2

M2

M3

N1

N2

P2

P3

R2

R1

T2

T3

AC2

AC1

AD3

AD2

AE2

AE1

AF2

AF3

PEG_C_TXP7

PEG_C_TXN7

PEG_C_TXP6

PEG_C_TXN6

PEG_C_TXP5

PEG_C_TXN5

PEG_C_TXP4

PEG_C_TXN4

PEG_C_TXP3

PEG_C_TXN3

PEG_C_TXP2

PEG_C_TXN2

PEG_C_TXP1

PEG_C_TXN1

PEG_C_TXP0

PEG_C_TXN0

DMI_MT_IR_DP0

DMI_MT_IR_DN0

DMI_MT_IR_DP1

DMI_MT_IR_DN1

DMI_MT_IR_DP2

DMI_MT_IR_DN2

DMI_MT_IR_DP3

DMI_MT_IR_DN3

06/24 Allen add

PEG_C_TXN7

PEG_C_TXN6

PEG_C_TXN5

PEG_C_TXN4

PEG_C_TXN3

PEG_C_TXN2

PEG_C_TXN1

PEG_C_TXN0

PEG_C_TXP7

PEG_C_TXP6

PEG_C_TXP5

PEG_C_TXP4

PEG_C_TXP3

PEG_C_TXP2

PEG_C_TXP1

PEG_C_TXP0

NOTE.

If PEG is not implemented, the RX&TX pairs can be left as No Connect

1 2

C11898 SCD22U10V2KX-2-GP(G_)

1 2

C11895 SCD22U10V2KX-2-GP(G_)

1 2

C11900 SCD22U10V2KX-2-GP(G_)

1 2

C11902 SCD22U10V2KX-2-GP(G_)

1 2

C11904 SCD22U10V2KX-2-GP(G_)

1 2

C11905 SCD22U10V2KX-2-GP(G_)

1 2

C11907 SCD22U10V2KX-2-GP(G_)

1 2

C11908 SCD22U10V2KX-2-GP(G_)

1 2

C12138 SCD22U10V2KX-2-GP(G_)

1 2

C12139 SCD22U10V2KX-2-GP(G_)

1 2

C12140 SCD22U10V2KX-2-GP(G_)

1 2

C12141 SCD22U10V2KX-2-GP(G_)

1 2

C12142 SCD22U10V2KX-2-GP(G_)

1 2

C12143 SCD22U10V2KX-2-GP(G_)

1 2

C12144 SCD22U10V2KX-2-GP(G_)

1 2

C12145 SCD22U10V2KX-2-GP(G_)

PEG_TXN7

PEG_TXN6

PEG_TXN5

PEG_TXN4

PEG_TXN3

PEG_TXN2

PEG_TXN1

PEG_TXN0

PEG_TXP7

PEG_TXP6

PEG_TXP5

PEG_TXP4

PEG_TXP3

PEG_TXP2

PEG_TXP1

PEG_TXP0

PEG_TXN[7..0] 76

PEG_TXP[7..0] 76

B8

B7

C7

C6

D6

D5

E5

E4

F6

F5

G5

G4

H6

H5

J5

J4

K6

K5

L5

L4

M6

M5

N5

N4

P6

P5

R5

R4

T6

T5

U5

U4

L7

Y3

Y4

AA4

AA5

AB4

AB3

AC4

AC5

CPU1C

PEG_RXP0

PEG_RXN0

PEG_RXP1

PEG_RXN1

PEG_RXP2

PEG_RXN2

PEG_RXP3

PEG_RXN3

PEG_RXP4

PEG_RXN4

PEG_RXP5

PEG_RXN5

PEG_RXP6

PEG_RXN6

PEG_RXP7

PEG_RXN7

PEG_RXP8

PEG_RXN8

PEG_RXP9

PEG_RXN9

PEG_RXP10

PEG_RXN10

PEG_RXP11

PEG_RXN11

PEG_RXP12

PEG_RXN12

PEG_RXP13

PEG_RXN13

PEG_RXP14

PEG_RXN14

PEG_RXP15

PEG_RXN15

PEG_RCOMP

DMI_RXP0

DMI_RXN0

DMI_RXP1

DMI_RXN1

DMI_RXP2

DMI_RXN2

DMI_RXP3

DMI_RXN3

SKYLAKE

LGA1151

DMI

D D

C C

DMI_IT_MR_DP[0..3]17

DMI_IT_MR_DN[0..3]17

DMI_MT_IR_DP[0..3]17

DMI_MT_IR_DN[0..3]17

CHECK PCIEX8 swap ?????

PEG_RXN[7..0]76

PEG_RXN7

PEG_RXN6

PEG_RXN5

PEG_RXN4

PEG_RXN3

PEG_RXN2

PEG_RXN1

PEG_RXN0

PEG_RXP[7..0]76

PEG_RXP7

PEG_RXP6

PEG_RXP5

PEG_RXP4

PEG_RXP3

PEG_RXP2

PEG_RXP1

PEG_RXP0

V_CPU_IO

12

R63

24D9R2F-L-GP

PEG_RXP7

PEG_RXN7

PEG_RXP6

PEG_RXN6

PEG_RXP5

PEG_RXN5

PEG_RXP4

PEG_RXN4

PEG_RXP3

PEG_RXN3

PEG_RXP2

PEG_RXN2

PEG_RXP1

PEG_RXN1

PEG_RXP0

PEG_RXN0

PEG_COMP

DMI_IT_MR_DP0

DMI_IT_MR_DN0

DMI_IT_MR_DP1

DMI_IT_MR_DN1

DMI_IT_MR_DP2

DMI_IT_MR_DN2

DMI_IT_MR_DP3

DMI_IT_MR_DN3

B B

SKYLAKE-1

Sandy Bridge Socket

SKT1

A A

5

4

Load Plate

(22.78003.021)

SKT2

Back Plate

(22.78006.031)

SKT3

CPU Cover

(42.3EQ28.011)

3

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

005_CPU_PCIE

005_CPU_PCIE

005_CPU_PCIE

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

COLORADO MLK SKYLAKE-S

C

COLORADO MLK SKYLAKE-S

C

COLORADO MLK SKYLAKE-S

C

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

5 107

5 107

1

5 107

-2

-2

-2

5

RepairLap.com

4

3

2

1

M10

M12

M15

M17

M19

M21

M23

M25

M27

M29

M35

M37

M39

N33

R33

U33

W33

D40

K39

L13

L32

P35

P37

P39

T35

T37

T39

V35

V37

V39

W3

W6

Y35

Y37

B38

K4

K7

L3

L6

L9

M1

M4

M7

N3

N6

N8

P1

P4

R3

R6

R8

T1

T4

U3

U6

V1

V8

Y5

A4

C2

CPU1L

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS_NCTF

VSS_NCTF

VSS_NCTF

VSS_NCTF

SKYLAKE-1

SKYLAKE

LGA1151

12 OF 12

6 OF 12

CPU1F

A11

VSS

AA33

AB39

AC33

AC34

AC35

AD33

AD36

AD37

AD38

AD39

AD40

AE33

AE36

AF33

AF36

AF37

AF40

AG33

AG36

AH33

AH36

AH37

AH38

AH39

AH40

AJ31

AJ32

AJ33

AJ34

AJ35

AJ36

AK10

AK12

AK13

AK15

AK16

AK17

AK18

AK19

AK20

AK23

AK25

AK26

AK28

AA3

AA8

AB5

AC3

AC6

AD1

AD4

AD6

AD7

AD8

AE3

AE5

AE8

AF1

AF5

AF8

AG1

AG2

AG3

AG4

AG5

AG8

AH5

AH8

A13

A15

A17

A24

A7

AJ1

AJ4

AJ5

AJ8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SKYLAKE-1

D D

C C

B B

SKYLAKE

LGA1151

AK29

VSS

AK30

VSS

AK36

VSS

AK37

VSS

AK40

VSS

AK5

VSS

AK6

VSS

AK7

VSS

AK8

VSS

AK9

VSS

AL1

VSS

AL11

VSS

AL14

VSS

AL2

VSS

AL21

VSS

AL24

VSS

AL27

VSS

AL3

VSS

AL30

VSS

AL36

VSS

AL4

VSS

AL5

VSS

AM11

VSS

AM14

VSS

AM17

VSS

AM19

VSS

AM24

VSS

AM27

VSS

AM30

VSS

AM31

VSS

AM32

VSS

AM33

VSS

AM34

VSS

AM35

VSS

AM36

VSS

AM37

VSS

AM38

VSS

AM39

VSS

AM40

VSS

AM5

VSS

AN1

VSS

AN10

VSS

AN11

VSS

AN14

VSS

AN16

VSS

AN19

VSS

AN22

VSS

AN23

VSS

AN24

VSS

AN27

VSS

AN30

VSS

AN36

VSS

AN4

VSS

AN5

VSS

AN6

VSS

AN7

VSS

AN8

VSS

AN9

VSS

AP11

VSS

AP14

VSS

AP24

VSS

AP27

VSS

AP30

VSS

AP36

VSS

AP37

VSS

AP40

VSS

AP5

VSS

AR1

VSS

AR11

VSS

AR14

VSS

AR16

VSS

AR17

VSS

AR18

VSS

AR19

VSS

AR2

VSS

AR20

VSS

AR21

VSS

AR24

AR27

AR30

AR31

AR32

AR33

AR34

AR35

AR36

AT10

AT11

AT12

AT13

AT14

AT17

AT24

AT25

AT26

AT27

AT28

AT29

AT30

AT31

AT32

AT34

AT36

AT37

AT38

AT39

AT40

AU25

AU30

AU34

AV26

AV28

AV30

AV34

AV38

AW3

AW30

AW32

AW34

AW36

AW5

AW9

AY27

AY30

AR3

AR4

AR5

AT5

AT6

AT7

AT8

AT9

AU1

AU4

AU5

AU7

AV2

AV5

AV9

AY5

AY7

AY9

B24

B26

B28

B30

B6

C12

C14

C16

C18

C20

C22

C24

C31

C33

C35

CPU1K

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SKYLAKE-1

SKYLAKE

LGA1151

11 OF 12

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C37

C5

C8

C10

D24

D26

D28

D30

D37

D39

D4

D7

E11

E13

E15

E17

E19

E21

E23

E3

E31

E33

E35

E37

E6

E9

F1

F10

F22

F26

F28

F30

F4

F40

F7

G11

G13

G15

G17

G19

G22

G3

G31

G33

G6

H1

H21

H24

H26

H28

H30

H35

H37

H39

H4

H7

H9

J10

J12

L11

J16

J18

J20

J3

J32

J34

J6

K1

K14

K15

K17

K19

K22

K24

K26

K28

K30

K33

K35

K37

A A

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

6 107

6 107

1

6 107

-2C

-2C

-2C

5

4

Title

Title

Title

006_CPU_ (VSS)

006_CPU_ (VSS)

006_CPU_ (VSS)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

COLORADO MLK SKYLAKE-S

COLORADO MLK SKYLAKE-S

COLORADO MLK SKYLAKE-S

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

V_CPU_C ORE

RepairLap.com

V_CPU_G T

V1P0_P CH_S5

V_CPU_S T_PLL

V_CPU_S A

V_CPU_I O

V_SM

DCBATO UT

V_CPU_CORE:VR12.5

D D

VCCSA_ SENSE47

VCCIO_ SENSE48

VSS_SA _IO_SE NSE47,48

VCORE_ VCC_SE N44

VCORE_ VSS_SE N44

VCCGT_ VCC_SE N44

VCCGT_ VSS_SE N44

PCH_2_C PU_TRIGG ER22

CPU_2_P CH_TRIGG ER22

C C

SLP_S4 _N

5

V_CPU_C ORE 9,24,44 ,45

V_CPU_G T 9,44 ,46

V1P0_P CH_S5 15,21,51,9 9

V_CPU_S T_PLL 4,44,99

V_CPU_S A 9,4 7,48

V_CPU_I O 4,5 ,8,9,48,99

V_SM 9,12 ,13,15,50 ,86

DCBATO UT 24,2 6,28,42,4 3,45,46,4 7,48,49,50 ,51,53,55 ,58,59,86 ,88

V_CPU_C ORE

CPU1G

SKYLAKE

A25

VCC_A25

A26

VCC_A26

A27

VCC_A27

A28

VCC_A28

A29

VCC_A29

A30

VCC_A30

B25

VCC_B25

B27

VCC_B27

B29

VCC_B29

B31

VCC_B31

B32

VCC_B32

B33

VCC_B33

B34

VCC_B34

B35

VCC_B35

B36

VCC_B36

B37

VCC_B37

LGA1151

C25

VCC_C25

C26

VCC_C26

C27

VCC_C27

C28

VCC_C28

C29

VCC_C29

C30

VCC_C30

C32

VCC_C32

C34

VCC_C34

C36

VCC_C36

D25

VCC_D25

D27

VCC_D27

D29

VCC_D29

D31

VCC_D31

D32

VCC_D32

D33

VCC_D33

D34

VCC_D34

D35

VCC_D35

D36

VCC_D36

E24

VCC_E24

E25

VCC_E25

E26

VCC_E26

E27

VCC_E27

E28

VCC_E28

E29

VCC_E29

E30

VCC_E30

E32

VCC_E32

E34

VCC_E34

E36

VCC_E36

F23

VCC_F23

F24

VCC_F24

F25

VCC_F25

F27

VCC_F27

F29

VCC_F29

F31

VCC_F31

G30

VCC_G30

G32

VCC_G32

H22

VCC_H22

H23

VCC_H23

H25

VCC_H25

H27

VCC_H27

H29

VCC_H29

H31

VCC_H31

AJ11

VCC_AJ11

AJ13

VCC_AJ13

AJ15

VCC_AJ15

AJ17

VCC_AJ17

AJ19

VCC_AJ19

AJ21

VCC_AJ21

VCC_SENSE

VSS_SENSE

SKYLAKE -1

1 2

(R_)

R79788 49D9R2F

IF power not support 4 4e

+VCCGTX

Wait for SPEC

V_CPU_C ORE

7 OF 12

H32

VCC_H32

J21

VCC_J21

F32

VCC_F32

F33

VCC_F33

F34

VCC_F34

G23

VCC_G23

G24

VCC_G24

G25

VCC_G25

G26

VCC_G26

G27

VCC_G27

G28

VCC_G28

G29

VCC_G29

J22

VCC_J22

J23

VCC_J23

J24

VCC_J24

J25

VCC_J25

J26

VCC_J26

J27

VCC_J27

J28

VCC_J28

J29

VCC_J29

J30

VCC_J30

J31

VCC_J31

K16

VCC_K16

K18

VCC_K18

K20

VCC_K20

K21

VCC_K21

K23

VCC_K23

K25

VCC_K25

K27

VCC_K27

K29

VCC_K29

K31

VCC_K31

L14

VCC_L14

L15

VCC_L15

L16

VCC_L16

L17

VCC_L17

L18

VCC_L18

L19

VCC_L19

L20

VCC_L20

L21

VCC_L21

L22

VCC_L22

L23

VCC_L23

L24

VCC_L24

L25

VCC_L25

L26

VCC_L26

L27

VCC_L27

L28

VCC_L28

L29

VCC_L29

L30

VCC_L30

M13

VCC_M13

M14

VCC_M14

M16

VCC_M16

M18

VCC_M18

M20

VCC_M20

M22

VCC_M22

M24

VCC_M24

M26

VCC_M26

M28

VCC_M28

M30

VCC_M30

AJ12

VCC_AJ12

AJ14

VCC_AJ14

AJ16

VCC_AJ16

AJ18

VCC_AJ18

AJ20

VCC_AJ20

AJ22

VCC_AJ22

VCORE_ VCC_SE N

C38

VCORE_ VSS_SE N

D38

VCORE_ VSS_SE NVCORE_ VCC_SE N

To VR Controller

+VCORE POWER SENSE

V_CPU_G T

07/17 Allen modify

B B

4

SKYLAKE

LGA1151

VCCGT_SENSE

VSSGT_SENSE

VCCGTX_SENSE

VSSGTX_SENSE

VCCGTX_F35

VCCGTX_G34

VCCGTX_G35

VCCGTX_H33

VCCGTX_H34

VCCGTX_J33

VCCGTX_J35

VCCGTX_K32

VCCGTX_K34

VCCGTX_L31

VCCGTX_L33

VCCGTX_M32

8 OF 12

CPU1H

AA34

VCCGT

AA35

VCCGT

AA36

VCCGT

AA37

VCCGT

AA38

VCCGT

AB33

VCCGT

AB34

VCCGT

G36

VCCGT

G37

VCCGT

G38

VCCGT

G39

VCCGT

G40

VCCGT

H36

VCCGT

H38

VCCGT

H40

VCCGT

J36

VCCGT

J37

VCCGT

J38

VCCGT

J39

VCCGT

J40

VCCGT

K36

VCCGT

K38

VCCGT

K40

VCCGT

L34

VCCGT

L35

VCCGT

L36

VCCGT

L37

VCCGT

L38

VCCGT

L39

VCCGT

L40

VCCGT

M33

VCCGT

M34

VCCGT

M36

VCCGT

M38

VCCGT

M40

VCCGT

N34

VCCGT

N35

VCCGT

N36

VCCGT

N37

VCCGT

N38

VCCGT

N39

VCCGT

N40

VCCGT

P33

VCCGT

P34

VCCGT

P36

VCCGT

P38

VCCGT

P40

VCCGT

R34

VCCGT

R35

VCCGT

R36

VCCGT

R37

VCCGT

R38

VCCGT

R39

VCCGT

R40

VCCGT

T33

VCCGT

T34

VCCGT

T36

VCCGT

T38

VCCGT

T40

VCCGT

U34

VCCGT

U35

VCCGT

U36

VCCGT

U37

VCCGT

U38

VCCGT

U39

VCCGT

U40

VCCGT

V33

VCCGT

V34

VCCGT

V36

VCCGT

V38

VCCGT

V40

VCCGT

W34

VCCGT

W35

VCCGT

W36

VCCGT

W37

VCCGT

W38

VCCGT

Y33

VCCGT

Y34

VCCGT

Y36

VCCGT

Y38

VCCGT

SKYLAKE -1

V_CPU_G TX V_SM

F35

G34

08/28 Allen modify

G35

H33

H34

J33

J35

K32

K34

L31

L33

M32

+VCCFUSEPRG HAS NO PWR SOURCE ON CRB

V_CPU_C ORE

R1823

0R2J-2-G P

V_CPU_S T_PLL

R1824 0R040 2-PAD-2-G P

06/24 Allen add

1A015 04/14 Allen modify

VCCGT_ VCC_SE N

F39

VCCGT_ VSS_SE N

F38

VCCGTX _SENSE

F37

VSSGTX _SENSE

F36

1

For 44e

1 2

(R_)

1 2

+VCCFUSE PRG

+VCCFUSE PRG_R

1

1

V_CPU_S A

TP227TPA D28

V_CPU_I O

Jeffrey 0617

V_CPU_S T_PLL

+VCCFUSE PRG

1 2

R1822 0R0603-PAD

SB002 09/29 Allen modify

+VCCGT SENSE PIN

TP228TPAD 28

+VCCGTX SENSE PIN

TP229TPAD 28

CPU1I

AA7

AB6

AB7

AB8

AC7

AC8

N7

P7

R7

T7

U7

Y6

Y7

Y8

W7

V7

AA6

AK11

AK14

AK24

AJ23

M8

P8

T8

U8

W8

V5

V6

V4

SKYLAKE -1

08/28 Allen modify

DCBATO UT

12

R1988

100KR2 J-1-GP

SLP_S4 _N_SFR_ 1

12

R1990

100KR2 J-1-GP

6

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCST_V5

VCCST_V6

VCCPLL

Q1233

2N7002E DW-2-GP

(75.2700 2.F7C)

SKYLAKE

LGA1151

VSSOPC_EOPIO_SENSE

2345

1

3

VDDQ_AT18

VDDQ_AT21

VDDQ_AU13

VDDQ_AU15

VDDQ_AU19

VDDQ_AU23

VDDQ_AV11

VDDQ_AV17

VDDQ_AV21

VDDQ_AW10

VDDQ_AW14

VDDQ_AW25

VDDQ_AY12

VDDQ_AY16

VDDQ_AY18

VDDQ_AY23

VCCPLL_OC

VCCOPC_AJ30

VCCOPC_AJ27

VCCOPC_AJ28

VCCOPC_AJ29

VCCOPC_AK27

VCCEOPIO

VCCEOPIO

VCC_OPC_1P8_AB37

VCC_OPC_1P8_AB38

VCCSA_SENSE

VCCIO_SENSE

VSS_SAIO_SENSE

VCCOPC_SENSE

VCCEOPIO_SENSE

2

9 OF 12

AT18

AT21

AU13

AU15

AU19

AU23

AV11

AV17

AV21

AW10

Note: Place resistors son backside under socket cavity

AW14

AW25

AY12

AY16

AY18

AY23

AJ9

AJ30

AJ27

AJ28

AJ29

AK27

AJ25

AJ26

AB37

AB38

AD5

AF4

AE4

AK21

AJ24

AK22

+VCCPLL _OC_R

R64 0R0402-P AD

OPC_1P 8_AB37

VCCSA_ SENSE

VCCIO_ SENSE

VSS_SA _IO_SE NSE

VCCOPC _SENSE

VCCEOP IO_SENS E

VSS_OP C_EOPI O_SENSE

09/12 Allen modify

For 44e

Have No Pwr Source

1 2

R65

1 2

0R2J-2-G P(R_)

+VCCSA SENSE PIN

+VCCIO SENSE PIN

1

1

1

+VCCPLL _OC

TP250TPA D28

TP249TPA D28

TP248TPA D28

V_SM

1

V_CPU_O PC

1

V_CPU_E OPIO

09/12 Allen modify

08/28 Allen modify

Have No Pwr Source for our

1.2V 1A

For 44e

TP253TPA D28

1

TP251TPA D28

TP226TPAD 28

TO PCH

Have No Pwr Source ON CRB

+OPC_FUS EPRG

1

TP252TPA D28

09/12 Allen modify

08/08 Allen modify

R66 20R2J-3-G P

TP12TPAD28

TP14TPAD28

TP16TPAD28

TP17TPAD28

TP20TPAD28

TP21TPAD28

TP182TPAD28

TP181TPAD28

TP178TPAD28

TP180TPAD28

TP177TPAD28

TP179TPAD28

1 2

TP261TPAD28

TP262TPAD28

SB022 10/06 Allen add

1

1

1

1

1

1

1

1

1

1

1

1

PCH_2_C PU_TRIGG ER

CPU_2_P CH_TRIGG ER_RCPU_2_P CH_TRIGG ER

TP_CPU_ L12

1

TP_CPU_ K12

1

TP_CPU_ J8

TP_CPU_ J7

TP_CPU_ L8

TP_CPU_ K8

TP_CPU_ AV1

TP_CPU_ AW2

TP_CPU_ K10

TP_CPU_ L10

TP_CPU_ J17

TP_CPU_ B39

TP_CPU_ J19

TP_CPU_ C40

J8

J7

L8

K8

AV1

AW2

H8

K10

L10

J17

B39

J19

C40

G8

AY3

D1

B3

L12

K12

CPU1J

RSVD_TP_J8

RSVD_TP_J7

RSVD_TP_L8

RSVD_TP_K8

RSVD_TP_AV1

RSVD_TP_AW2

RSVD_H8

RSVD_K10

RSVD_L10

RSVD_J17

RSVD_B39

RSVD_J19

RSVD_C40

RSVD_G8

RSVD_AY3

PROC_TRIGIN

PROC_TRIGOUT

RSVD_L12

RSVD_K12

SKYLAKE -1

SKYLAKE

LGA1151

1

RSVD_TP_H11

RSVD_TP_H12

RSVD_TP_AW38

RSVD_TP_AV39

RSVD_AU39

RSVD_AU40

VSS_AT15

VSS_AR23

VSS_AR22

RSVD_J15

RSVD_J14

RSVD_AU9

RSVD_AU10

RSVD_J13

RSVD_K13

RSVD_J11

RSVD_D15

RSVD_K11

10 OF 12

TP_CPU_ H11

H11

H12

AW38

AV39

AU39

AU40

AT15

AR23

AR22

J15

J14

AU9

AU10

J13

K13

J11

D15

K11

TP_CPU_ H12

TP_CPU_ AW38

TP_CPU_ AV39

TP_CPU_ AU39

TP_CPU_ AU40

TP_CPU_ J15

TP_CPU_ J14

TP_CPU_ AU9

TP_CPU_ AU10

TP_CPU_ J13

TP_CPU_ K13

TP_CPU_ J11

TP_CPU_ D15

TP_CPU_ K11

12

1

1

1

1

1

1

1

1

1

1

1

1

1

1

(R_)

R1996

560R2J -3-GP

TP13 TPAD28

TP15 TPAD28

TP149 T PAD28

TP19 TPAD28

TP183 T PAD28

TP184 T PAD28

TP185 T PAD28

TP186 T PAD28

TP187 T PAD28

TP188 T PAD28

TP191 T PAD28

TP192 T PAD28

TP189 T PAD28

TP190 T PAD28

09/12 Allen del

V1P0_P CH_S5

DS

Q1234

AO3404 AL-GP

07/07 Allen add

SC032 12/18 Allen modify

12

R152

4K7R2J -2-GP

V1P0_P CH_S5 V_CPU_S T_PLL

1 2

R68 0R3J-L1-G P

(R_)

V_CPU_S T_PLL

12

12

(R_)

(R_)

C12057

C12056

DCBATO UT

12

R1989

47KR2J -2-GP

10KR2J -3-GP

12

R1991

100KR2 J-1-GP

R1992

1 2

SLP_S4 _N_SFR_ GSLP_S4_N_S FR_2

12

C12059

SCD1U50 V3KX-DL -GP

12

(R_)

C12058

SCD1U50 V3KX-DL -GP

G

SLP_S4 _N SLP_S4 _N_SFR

A A

5

4

1 2

R1683 0R040 2-PAD

12

(R_)

C12060

SCD1U50 V3KX-DL -GP

SC10U10V5KX-2DLGP

SCD1U16V2KX-3DLGP

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, S ec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, S ec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, S ec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 22 1, Taiwan, R.O.C.

Taipei Hsien 22 1, Taiwan, R.O.C.

Title

Title

Title

007_CP U_(VCC_C ORE/TP)

007_CP U_(VCC_C ORE/TP)

007_CP U_(VCC_C ORE/TP)

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

D

D

D

COLORADO MLK SKYLAKE-S

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

1

Taipei Hsien 22 1, Taiwan, R.O.C.

7 1 07

7 1 07

7 1 07

-2

-2

-2

5

RepairLap.com

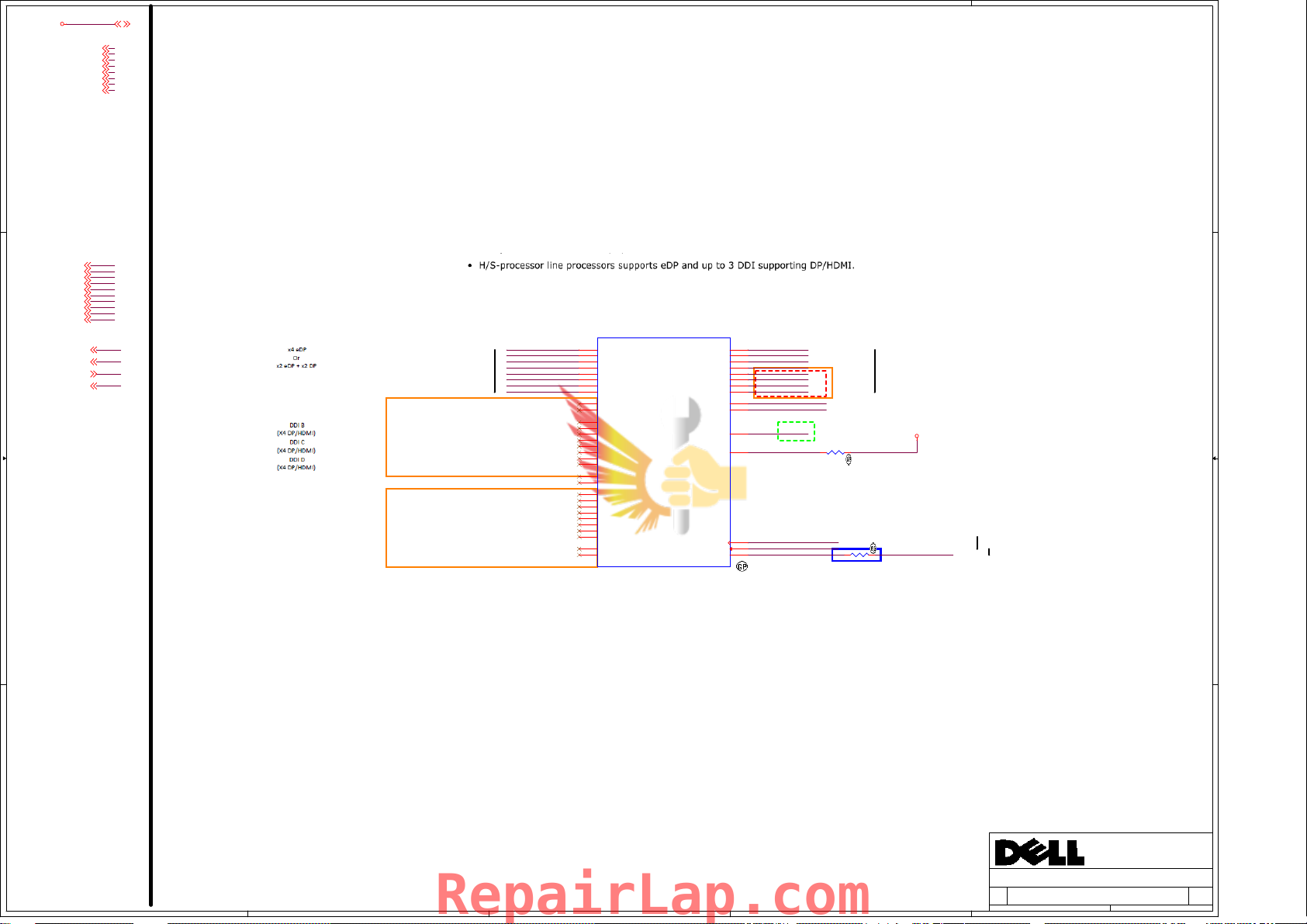

V_CPU_IO

HDMI PORT B

DDSP_B_TX_DN_056

DDSP_B_TX_DP_056

DDSP_B_TX_DN_156

DDSP_B_TX_DP_156

DDSP_B_TX_DN_256

DDSP_B_TX_DP_256

DDSP_B_TX_DN_356

DDSP_B_TX_DP_356

D D

eDISPLAY PORT E

DPD_LANE0P55

DPD_LANE0N55

DPD_LANE1P55

DPD_LANE1N55

DPD_LANE2P55

DPD_LANE2N55

DPD_LANE3P55

DPD_LANE3N55

DPD_AUXN55

DPD_AUXP55

AUDIO

C C

AUD_AZACPU_SCLK15

AUD_AZACPU_SDO15

AUD_AZACPU_SDI_R15

DISP_UTIL_CPU55

B B

V_CPU_IO 4,5,7,9,48,99

4

PORT B

PORT C

09/10 Allen remove

07/03 Allen remove

In CRB,

DDI1 for DP

DDI2 dor HDMI

DDI3 for DP HDMI combo

DDI4 for eDP

DDSP_B_TX_DP_0

DDSP_B_TX_DN_0

DDSP_B_TX_DP_1

HDMI

DDSP_B_TX_DN_1

DDSP_B_TX_DP_2

DDSP_B_TX_DN_2

DDSP_B_TX_DP_3

DDSP_B_TX_DN_3

C21

D21

D22

E22

B23

A23

C23

D23

B13

C13

B18

A18

D18

E18

C19

D19

D20

E20

A12

B12

B14

A14

C15

B15

B16

A16

C17

B17

B11

C11

3

CPU1D

DDI1_TXP0

DDI1_TXN0

DDI1_TXP1

DDI1_TXN1

DDI1_TXP2

DDI1_TXN2

DDI1_TXP3

DDI1_TXN3

DDI1_AUXP

DDI1_AUXN

DDI2_TXP0

DDI2_TXN0

DDI2_TXP1

DDI2_TXN1

DDI2_TXP2

DDI2_TXN2

DDI2_TXP3

DDI2_TXN3

DDI2_AUXP

DDI2_AUXN

DDI3_TXP0

DDI3_TXN0

DDI3_TXP1

DDI3_TXN1

DDI3_TXP2

DDI3_TXN2

DDI3_TXP3

DDI3_TXN3

DDI3_AUXP

DDI3_AUXN

SKYLAKE-1

SKYLAKE

LGA1151

4 OF 12

EDP_TXP0

EDP_TXN0

EDP_TXP1

EDP_TXN1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXP

EDP_AUXN

EDP_DISP_UTIL

EDP_RCOMP

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

2

DPD_LANE0P

E10

DPD_LANE0N

D10

DPD_LANE1P

D9

DPD_LANE1N

C9

DPD_LANE2N

H10

DPD_LANE2P

G10

DPD_LANE3N

G9

DPD_LANE3P

F9

D12

E12

D14

M9

DPD_AUXP

DPD_AUXN

Jeffrey 0619

DISP_UTIL_CPU

DP_RCOMP

08/28 Allen modfiy

TO DP LVDS

1 2

R71 24D9R2F-L-GP

Note: Place ra inside cpu cavity

AUD_AZACPU_SCLK

V3

AUD_AZACPU_SDO

V2

AUD_AZACPU_SDI AUD_AZACPU_SDI_R

U1

1 2

R72

20R2F-GP

SB007 09/30 Allen modfiy

eDP

V_CPU_IO

From PCH

TO PCH

1

A A

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

8 107

8 107

1

8 107

-2

-2

-2

5

4

Title

Title

Title

008_CPU_(DDI/EDP)

008_CPU_(DDI/EDP)

008_CPU_(DDI/EDP)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

COLORADO MLK SKYLAKE-S

C

COLORADO MLK SKYLAKE-S

C

COLORADO MLK SKYLAKE-S

C

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

V_CPU_C ORE

RepairLap.com

V_SM

V_CPU_G T

V_CPU_S A

V_CPU_I O

5

V_CPU_C ORE 7,24,44 ,45

V_SM 7,12 ,13,15,50 ,86

V_CPU_G T 7,44 ,46

V_CPU_S A 7,4 7,48

V_CPU_I O 4 ,5,7,8,48,9 9

4

3

2

1

D D

C C

B B

V_CPU_C ORE

PLACE ALL 0805 CAPS ON TOP SIDE OF CPU CAVITY

12

C24

SC22U6D 3V5MX-2DL GP

C16

SC22U6D 3V5MX-2DL GP

12

12

(R_)

C11

SC22U6D 3V5MX-2DL GP

C17

SC22U6D 3V5MX-2DL GP

C12

SC22U6D 3V5MX-2DL GP

12

C18

SC22U6D 3V5MX-2DL GP

PLACE ALL 0805 CAPS ON BOTTOM SIDE NEAR CPU SOCKET

12

12

C28

SC22U6D 3V5MX-2DL GP

C22

SC22U6D 3V5MX-2DL GP

PLACE SIZE 0805 CAPS FOR DIMM

12

12

C41

C42

SC22U6D 3V5MX-2DL GP

SC22U6D 3V5MX-2DL GP

(R_)

(R_)

C48

SC22U6D 3V5MX-2DL GP

PLACE CAPS ON TOP SIDE

SOCKET CAVITY

12

C55

SC22U6D 3V5MX-2DL GP

(R_)

12

C49

SC22U6D 3V5MX-2DL GP

PLACE CAPS ON BACKSIDE

UNDER SOCKET CAVITY

12

C61

SC22U6D 3V5MX-2DL GP

PLACE CAPS AT SOCKET EDGE

6 ON TOP & 6 ON BOTTOM

12

C70

SC22U6D 3V5MX-2DL GP

(R_)

C47

SC22U6D 3V5MX-2DL GP

V_CPU_G T

12

V_CPU_C ORE

12

C27

SC22U6D 3V5MX-2DL GP

V_SM

12

C37

SC22U6D 3V5MX-2DL GP

V_SM

12

12

(R_)

12

12

C23

SC22U6D 3V5MX-2DL GP

12

C43

SC22U6D 3V5MX-2DL GP

12

12

C56

SC22U6D 3V5MX-2DL GP

12

(R_)

12

C13

SC22U6D 3V5MX-2DL GP

(R_)

SC032 12/16 Allen modifySC032 12/16 Allen modifySC032 12/16 Allen modify

12

C19

SC22U6D 3V5MX-2DL GP

(R_)

12

C31

SC22U6D 3V5MX-2DL GP

(R_)

C50

SC22U6D 3V5MX-2DL GP

12

C62

SC22U6D 3V5MX-2DL GP

C71

SC22U6D 3V5MX-2DL GP

12

C14

SC22U6D 3V5MX-2DL GP

12

C20

SC22U6D 3V5MX-2DL GP

12

C44

SC22U6D 3V5MX-2DL GP

(R_)

12

C51

SC22U6D 3V5MX-2DL GP

12

C57

SC22U6D 3V5MX-2DL GP

12

12

C72

SC22U6D 3V5MX-2DL GP

(R_)

(R_)

12

12

C32

SC22U6D 3V5MX-2DL GP

C63

SC22U6D 3V5MX-2DL GP

12

C73

SC22U6D 3V5MX-2DL GP

(R_)

SC032 12/16 Allen modifySC032 12/16 Allen modify

12

C15

SC22U6D 3V5MX-2DL GP

C26

SC22U6D 3V5MX-2DL GP

12

12

C33

SC22U6D 3V5MX-2DL GP

V_SM

PLACE SIZE 0603 CAPS IN SOCKET EDGE TOP

12

12

C38

SC22U6D 3V3MX-1-DL -GP

CRB: 5*22U 0805,4*22U 0603, 5*22U 0805{reserve)

Our: 5*22U 0805,4*22U 0603, 5*22U 0805{reserve)

C58

SC22U6D 3V5MX-2DL GP

12

C64

SC47U6D 3V5MX-1DL -GP

(R_)

12

(R_)

12

C59

SC22U6D 3V5MX-2DL GP

12

C74

SC22U6D 3V5MX-2DL GP

12

PLACE ALL 0603 CAPS ON TOP SIDE OF CPU CAVITY

V_CPU_C ORE

12

12

C4

SC22U6D 3V3MX-1-DL -GP

(R_)

(R_)

V_CPU_C ORE

C5

SC22U6D 3V3MX-1-DL -GP

12

(R_)

PLACE ALL 0805 CAPS AT TOP SOCKET EDGE

(R_)

12

C29

SC22U6D 3V5MX-2DL GP

12

12

C35

C34

SC22U6D 3V5MX-2DL GP

C39

SC22U6D 3V3MX-1-DL -GP

C12444

SC22U6D 3V5MX-2DL GP

12

C75

SC22U6D 3V5MX-2DL GP

(R_)

12

12

(R_)

SC22U6D 3V5MX-2DL GP

C40

SC22U6D 3V3MX-1-DL -GP

C60

SC47U6D 3V5MX-1DL -GP

12

C12445

SC22U6D 3V5MX-2DL GP

12

C76

SC22U6D 3V5MX-2DL GP

(R_)

PLACE CAPS AT SOCKET EDGE

6 ON TOP & 6 ON BOTTOM

C25

SC22U6D 3V5MX-2DL GP

12

C45

SC22U6D 3V3MX-1-DL -GP

PLACE CAPS IN SOCKET EDGE TOP

12

C52

SC47U6D 3V5MX-1DL -GP

(R_)

12

C67

SC47U6D 3V5MX-1DL -GP

(R_)

12

C77

SC22U6D 3V5MX-2DL GP

(R_)

12

C6

SC22U6D 3V3MX-1-DL -GP

(R_)

(R_)

12

C30

SC22U6D 3V5MX-2DL GP

CRB: 27*22U 0805,6*22U 0603

Our:27*22U 0805,6*22U 0603

12

C53

SC47U6D 3V5MX-1DL -GP

(R_)

12

C68

SC47U6D 3V5MX-1DL -GP

(R_)

12

C78

SC22U6D 3V5MX-2DL GP

(R_)

C7

SC22U6D 3V3MX-1-DL -GP

(R_)

12

CRB:1*22U 0603

OUR:1*22U 0603

12

(R_)

12

(R_)

12

(R_)

12

C8

SC22U6D 3V3MX-1-DL -GP

(R_)

C10

SC22U6D 3V5MX-2DL GP

SC032 12/16 Allen modify

C54

SC47U6D 3V5MX-1DL -GP

SC032 12/16 Allen modify

C69

SC47U6D 3V5MX-1DL -GP

C79

SC22U6D 3V5MX-2DL GP

SC032 12/16 Allen modify

12

C9

SC22U6D 3V3MX-1-DL -GP

(R_)

(R_)

C36

SC22U6D 3V5MX-2DL GP

(R_)

12

C21

SC22U6D 3V5MX-2DL GP

12

09/12 Allen del

CRB:18*47U 0805,12*22U 0805

Our:18*47U 0805,12*22U 0805

12

12

C80

C81

SC22U6D 3V5MX-2DL GP

(R_)

SC22U6D 3V5MX-2DL GP

(R_)

SC032 12/16 Allen modify

SC032 12/16 Allen modify

PLACE CAPS AT TOP SOCKET EDGE

A A

V_CPU_G T

2-008

12

C82

SC22U6D 3V5MX-2DL GP

(R_)

CRB:1*22U 0805,1*1U 0402

Our:1*22U 0805,1*1U 0402

5

12

C83

SC1U10V 2KX-1DL GP

12

C84

SC22U6D 3V3MX-1-DL -GP

CRB:2*22U 0603

Our:2*22U 0603

12

C85

SC22U6D 3V3MX-1-DL -GP

4

V_CPU_I OV_CPU_S A

12

C86

SC22U6D 3V5MX-2DL GP

0805 SIZE

12

C87

SC22U6D 3V5MX-2DL GP

12

C88

SC22U6D 3V5MX-2DL GP

12

C89

SC22U6D 3V5MX-2DL GP

3

12

C90

SC22U6D 3V5MX-2DL GP

12

C91

SC22U6D 3V5MX-2DL GP

CRB:1*22U 0805,:5*22U 0603

Our:1*22U 0805,:5*22U 0603

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, S ec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, S ec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, S ec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 22 1, Taiwan, R.O.C.

Taipei Hsien 22 1, Taiwan, R.O.C.

Title

Title

Title

009_CPU_(POWER CAP1)

009_CPU_(POWER CAP1)

009_CPU_(POWER CAP1)

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

COLORA DO MLK SKYL AKE-S -2

D

COLORA DO MLK SKYL AKE-S -2

D

COLORA DO MLK SKYL AKE-S -2

D

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

1

Taipei Hsien 22 1, Taiwan, R.O.C.

9 1 07

9 1 07

9 1 07

5

RepairLap.com

For 44e

4

For 44e

3

2

1

For 44e

GTTX

CRB:4*22U 0603,10*47U 0805

D D

C C

V_CPU_OPC

CRB:6*22U 0603

V_CPU_EOPIO

CRB:7*22U 0603

B B

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

A A

Title

Title

Title

010_CPU_(POWER CAP2)

010_CPU_(POWER CAP2)

010_CPU_(POWER CAP2)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

A

A

COLORADO MLK SKYLAKE-S

COLORADO MLK SKYLAKE-S

COLORADO MLK SKYLAKE-S

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

2

Taipei Hsien 221, Taiwan, R.O.C.

10 107

10 107

10 107

1

-2

-2

-2

5

RepairLap.com

D D

C C

4

3

2

1

B B

A A

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

COLORA DO MLK SKYL AKE-S

D

COLORA DO MLK SKYL AKE-S

D

COLORA DO MLK SKYL AKE-S

D

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, S ec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, S ec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, S ec.1, Hsin Tai W u Rd., Hsichih,