5

4

3

2

1

Goodyear

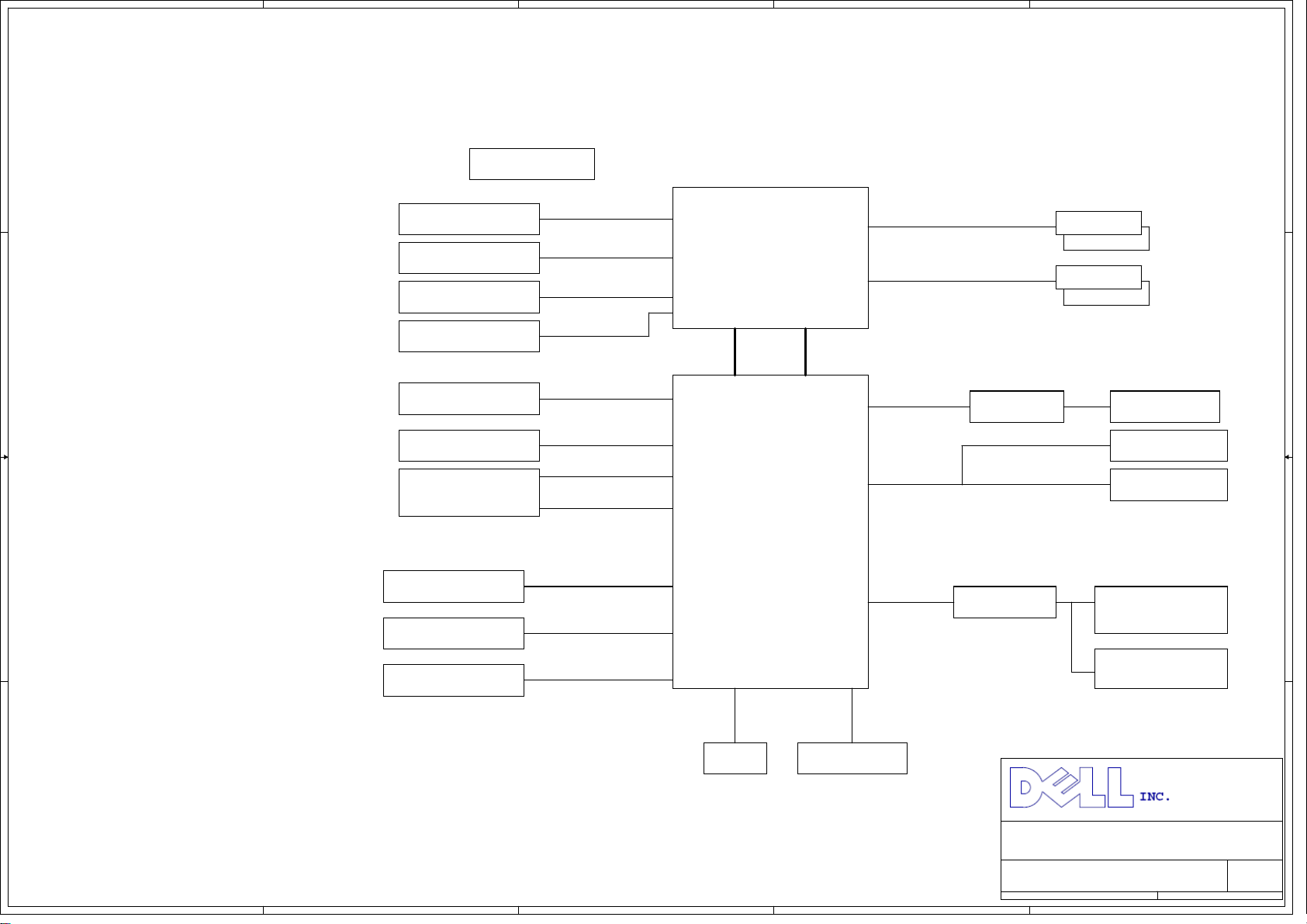

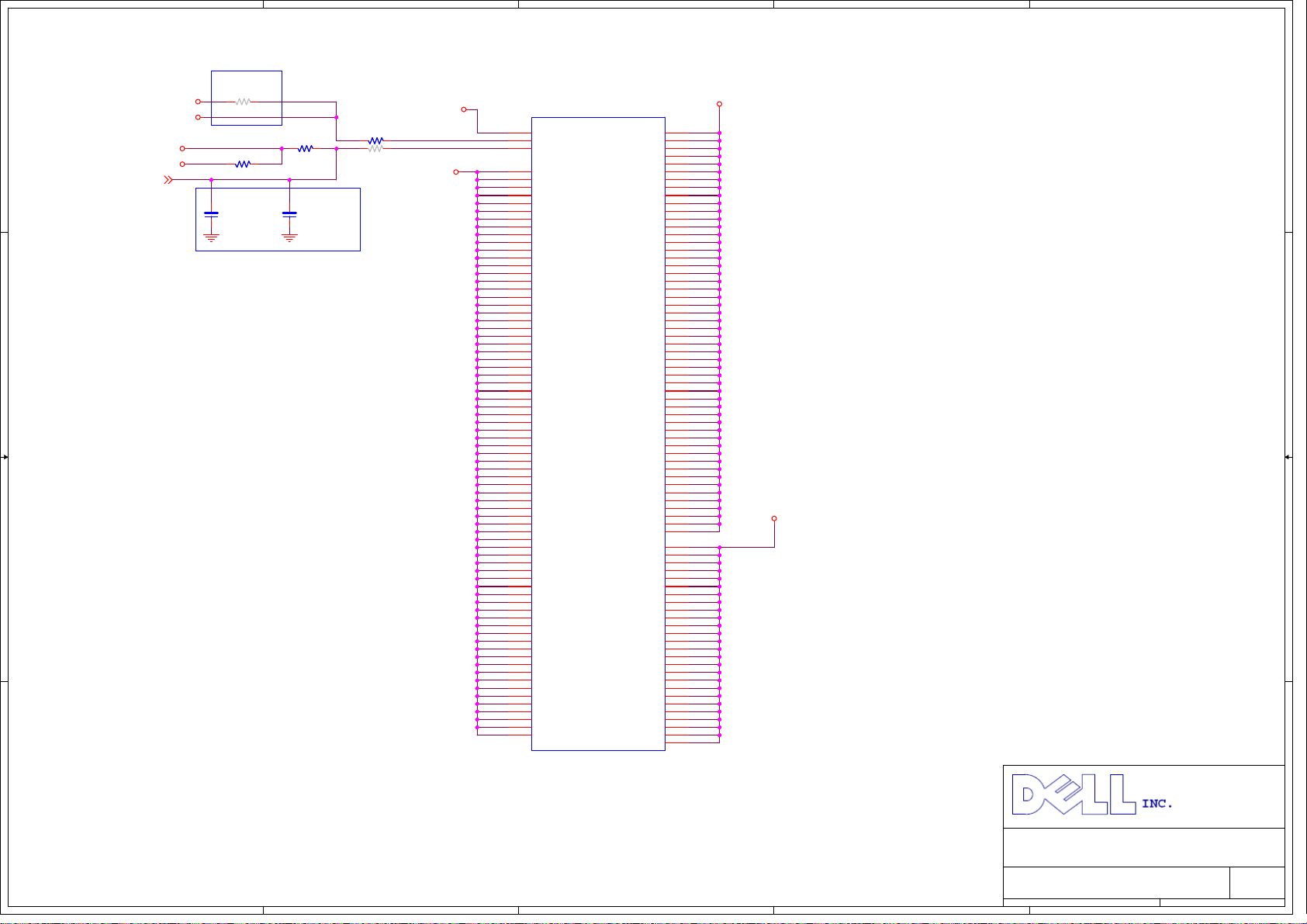

1. Index / Block diagram

D D

C C

B B

A A

2. SMBus MAP

3. Clock Distribution

4. Power Delivery Map

5. Power On Sequence

6. Reset / Power Good Map

7. Strap/IRQ/IDSel Table

8. GPIO Table

9-14. CPU

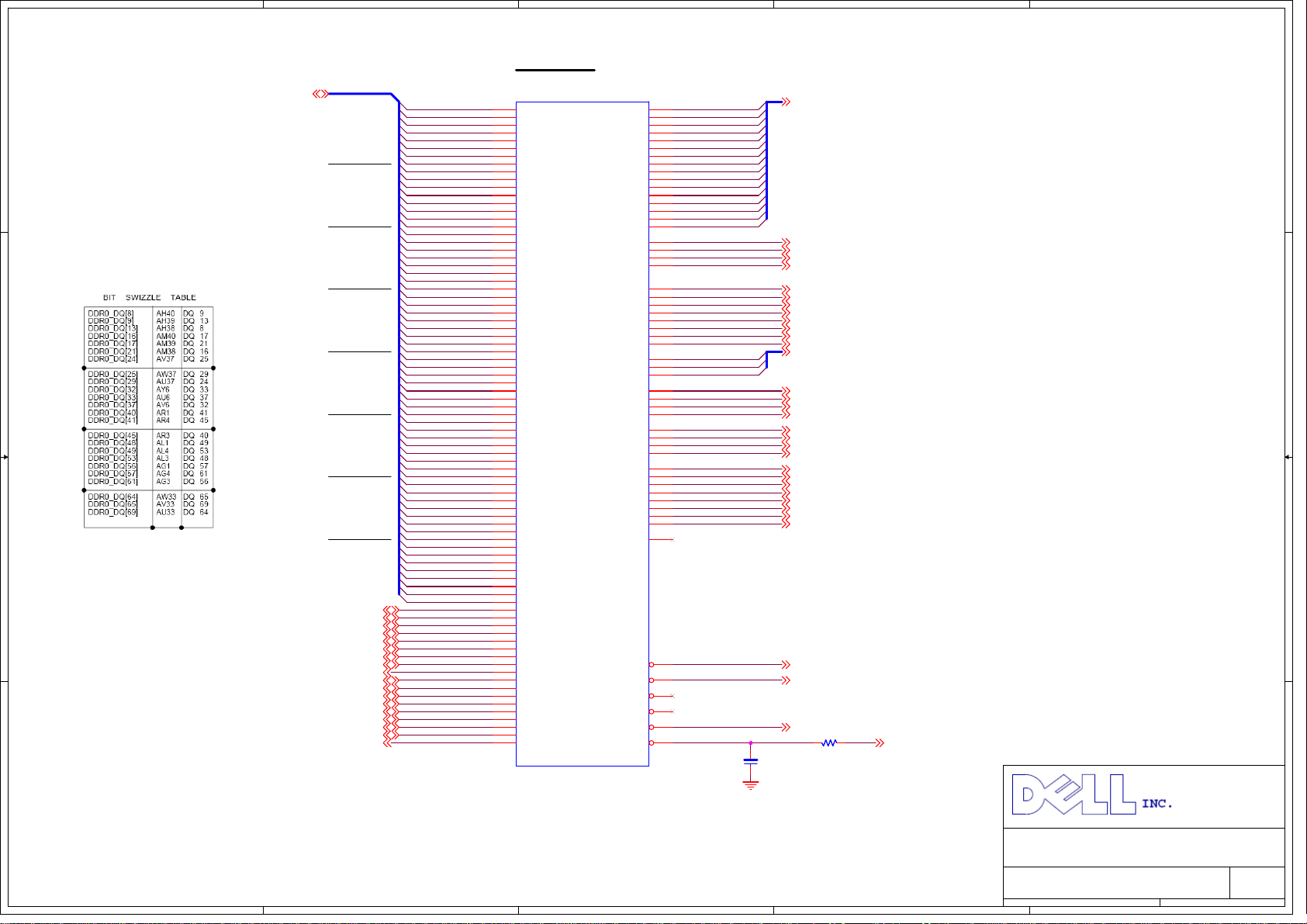

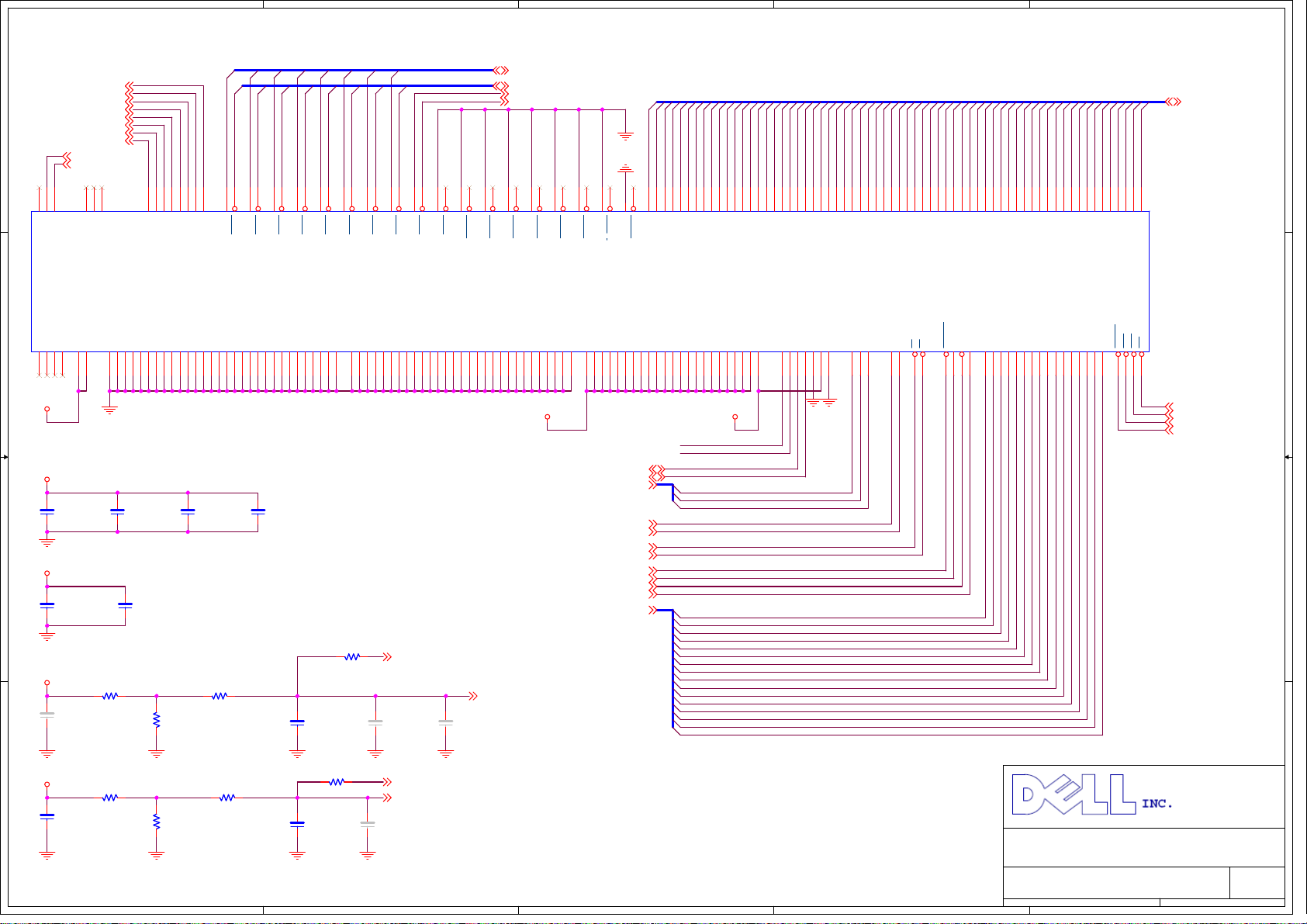

15-16. DDR3 Conn: CHA

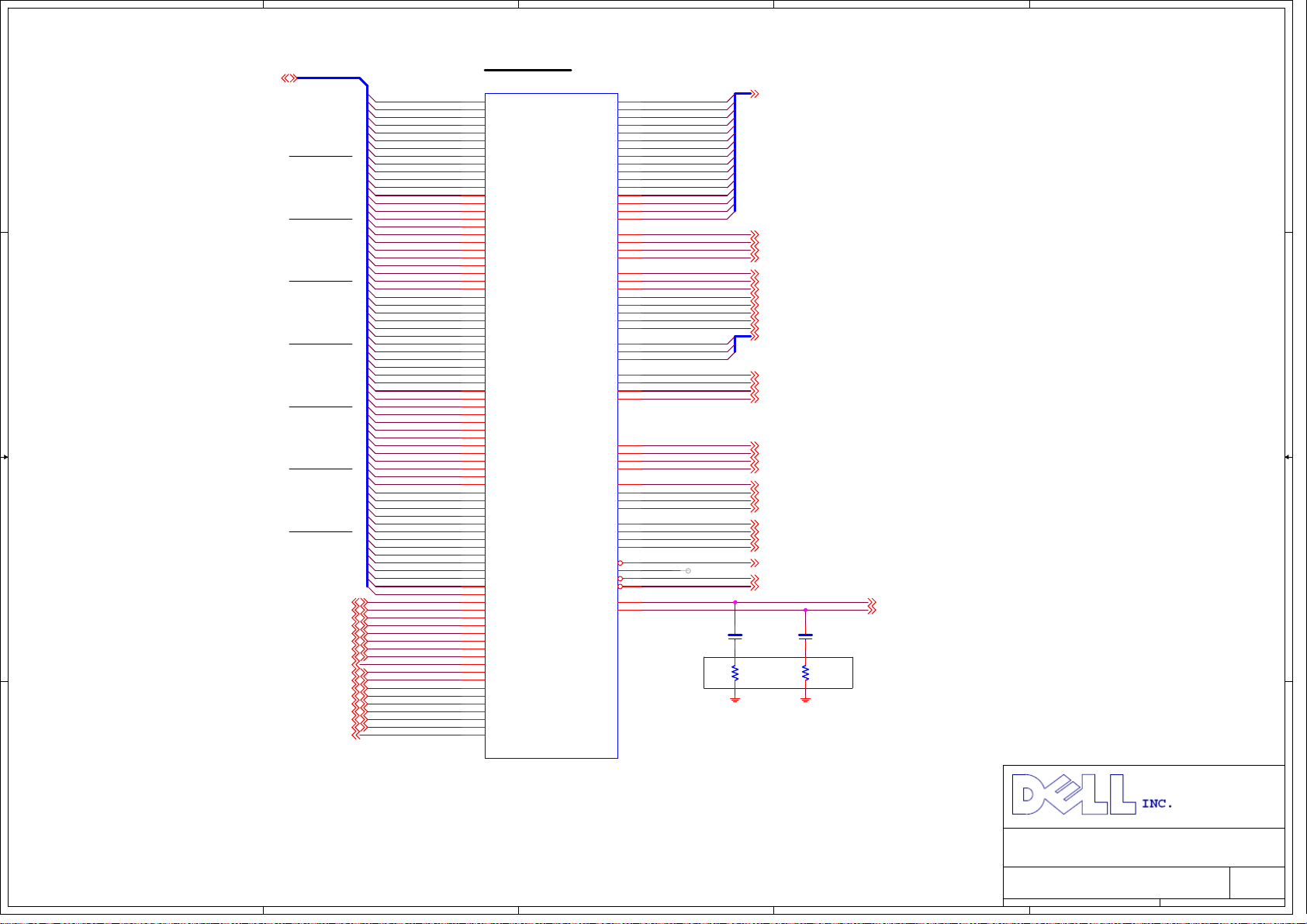

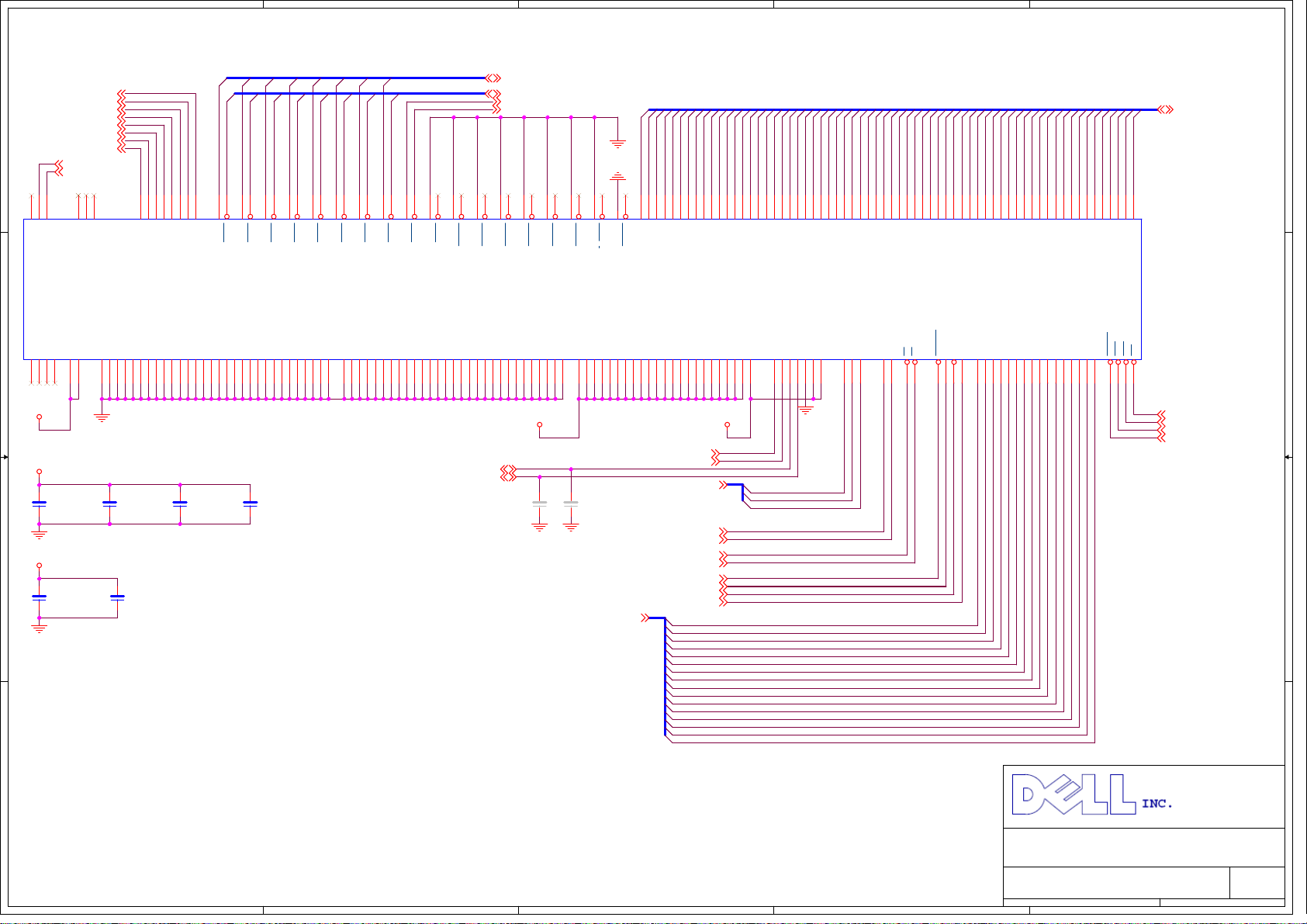

17-18. DDR3 Conn: CHB

19. Label

20. TBD

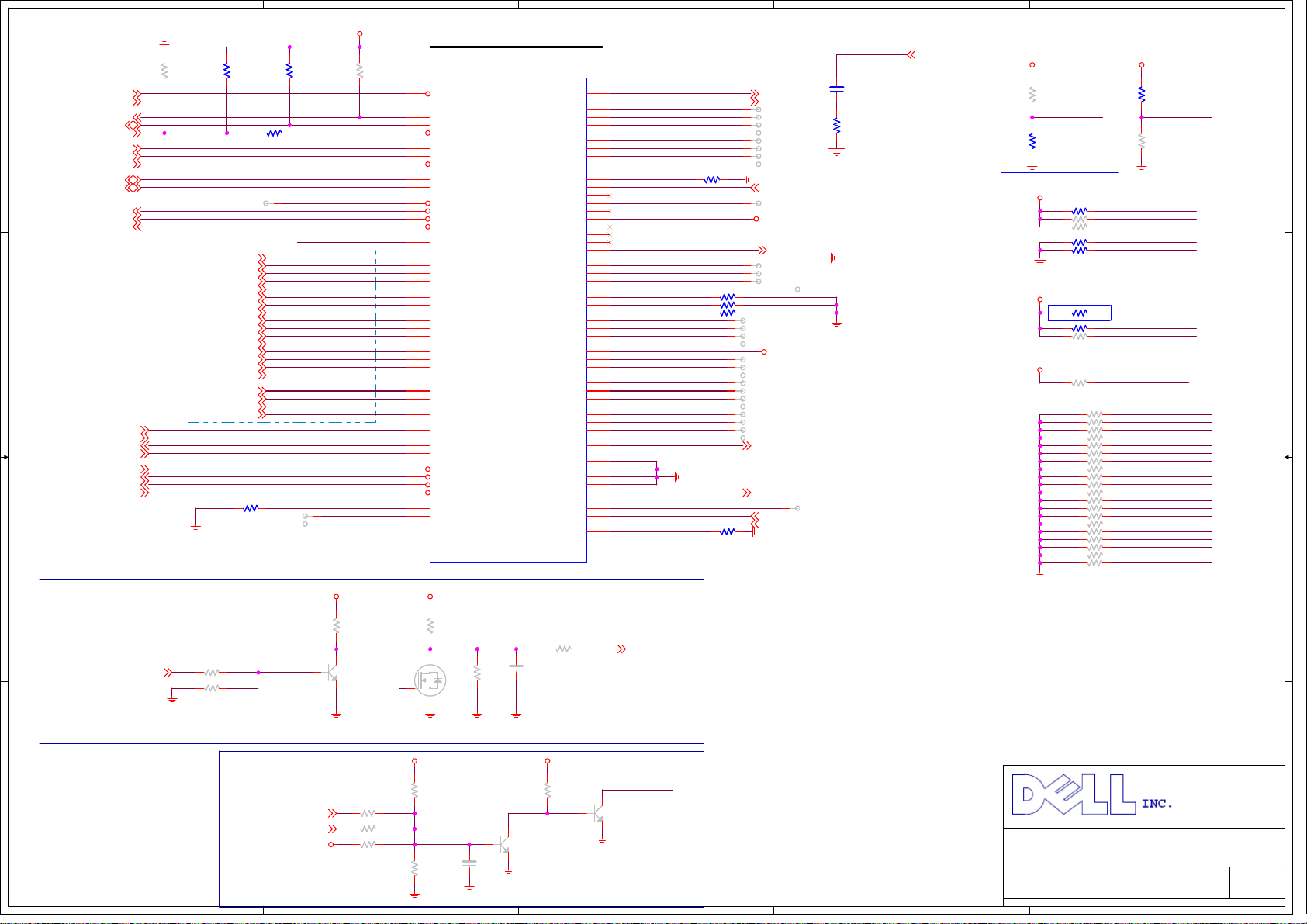

21-28. PCH

29-30.SIO-IT8772E

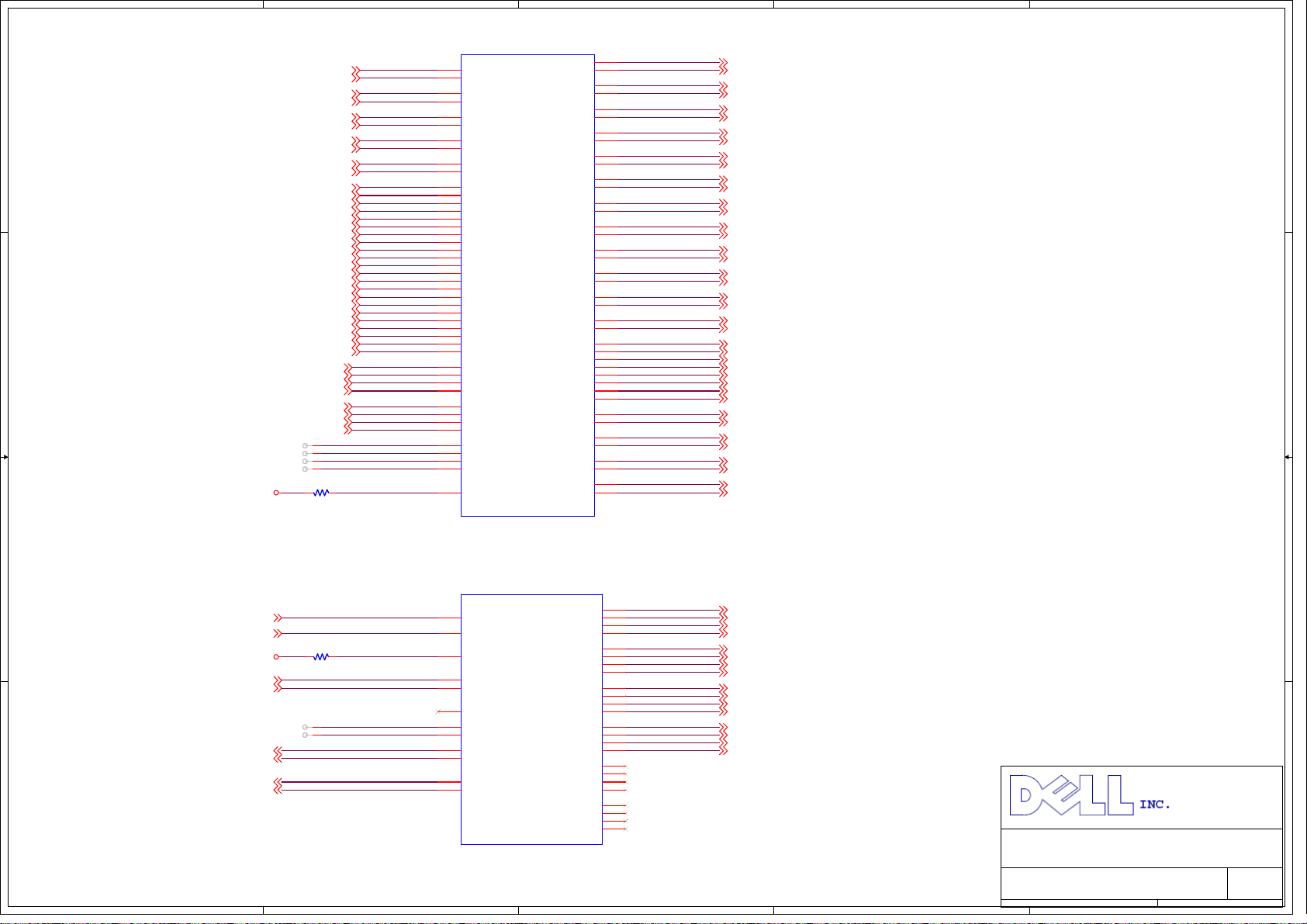

31-32. LAN: RTL8111G

33-34. Audio:ALC3861

35. Slot1 : PCIe 16X

36. Mini PCIe

37. HDMI

38.Display port

39. SATA+mSATA

40. RearUSB3

41. FAN

42. Serial / PS2 port

43. SPI-LPC DBG

44. XDP

45.EMI

46.Front_Panel

47. Slot4: PCIe 4x

48. Slot2 ,3: PCIe 1x

49. Front USB

50. Power Conn

51. Power Sequence

52. Power-1: Linear Power-1

53. Power-2: Linear Power-2

54.Power-4: Vcore PWM

55. Power-5: Vcore Driver

56. Power-6: DDR3

57. +5V_DUAL/+5V_DUAL_USBKB

Page 52 ~ 57

VRD12.5 / VRM / Linear

HDMI

Disply Port

PCIe 16x slot X1

XDP

PCIe 4x Slot4

PCIe 1x Slot2 ,3

Mini-PCIe Slot x1

SATA 3.0 CONN X5

mSATA 3.0 CONN X1

XDP

TMDS Link

Page 37

DP Link

Page 38

PCIe Gen3 16x

Page 35

Page 44

PCIe Gen2 2x

Page 47

PCIe Gen2 1x

Page 48

PCIe Gen2 1x

Page 36

USB 2.0

Page 36

SATA Port 0/1/2/3/4

Page 39

SATA Port 5

Page 39

Page 44

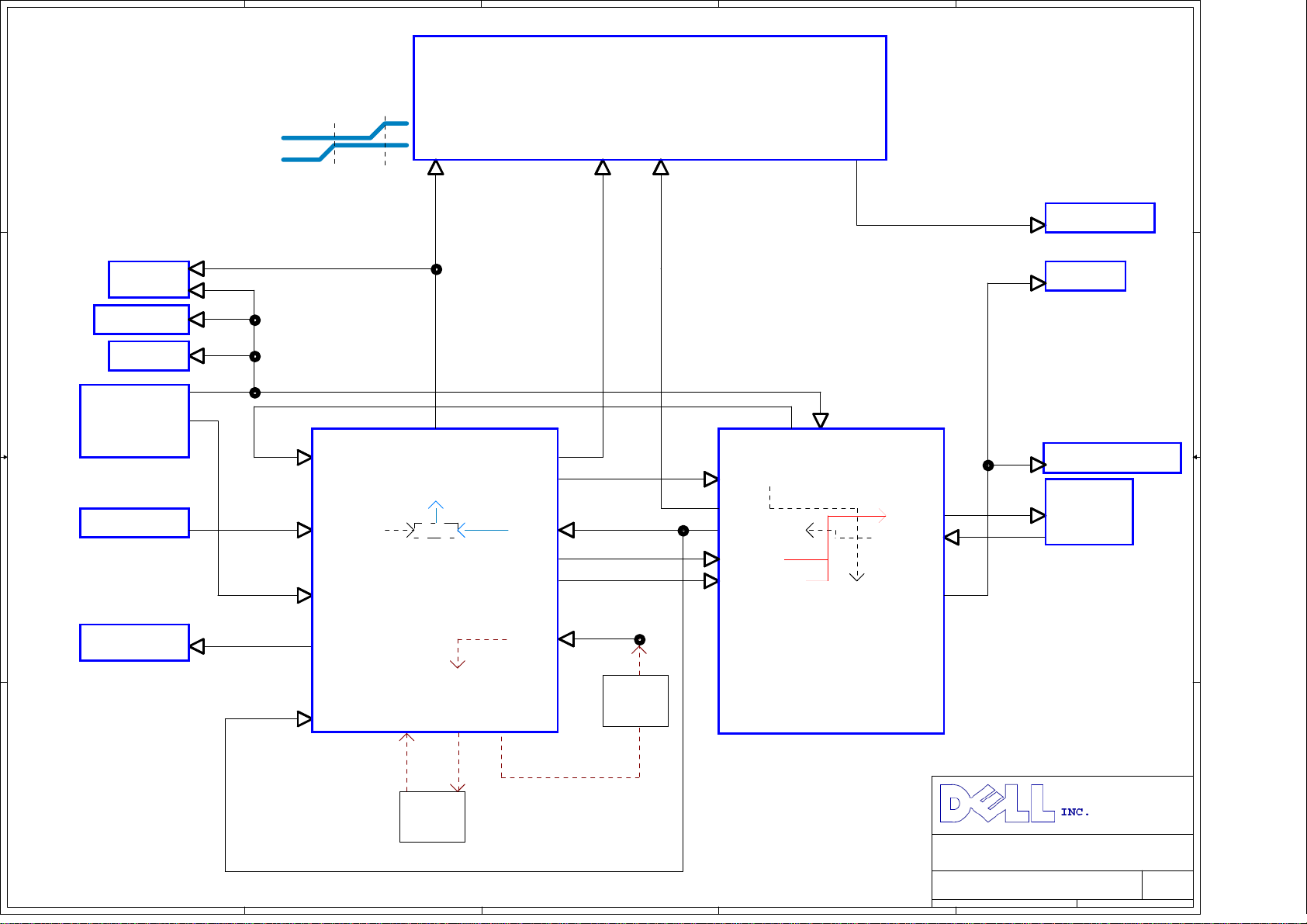

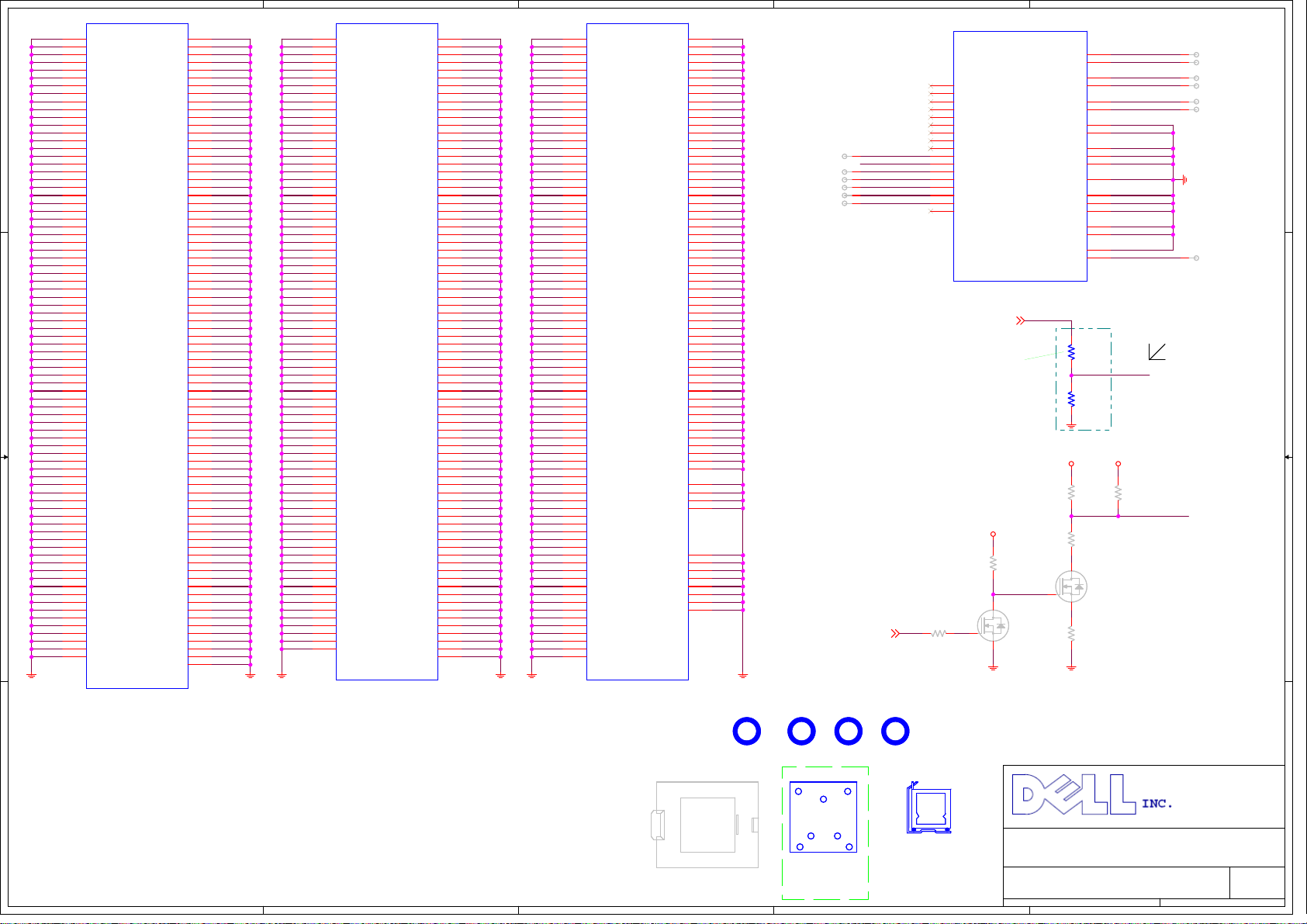

Intel PROCESSOR

HASWELL

LGA1150

Page 9-14

FDI

DMI

Intel

Lynx Point

Page 21-28

SPI

SPI BIOS

Page 43

ITE8772

CHANNEL A DDR3 SDRAM (1600/1333)

Page 15, 16

CHANNEL B DDR3 SDRAM (1600/1333)

Page 17, 18

PCIe 1x

Page 31

RTL8111G-CG

Page 32

USB 2.0/3.0

HDA

Page 33

ALC3861-CG

Page 29

DDR3 DIMM 1

DDR3 DIMM 3

DDR3 DIMM 2

DDR3 DIMM 4

Page 40

Page 49

Giga lan port

Rear USB Ports X 6

(2.0*2, 3.0*4)

Front USB Ports X 4

(Front 3.0*2, Top 2.0*2)

Rear Audio CONN

7.1 channel

Page 34

Front Audio CONN

HP Out/ MIC In

Page 34

Title

Title

Title

Index / Block diagram

Index / Block diagram

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Index / Block diagram

Goodyear

Goodyear

Goodyear

157星期三, 二月 20, 2013

157星期三, 二月 20, 2013

157星期三, 二月 20, 2013

1

A00

A00

A00

of

of

of

5

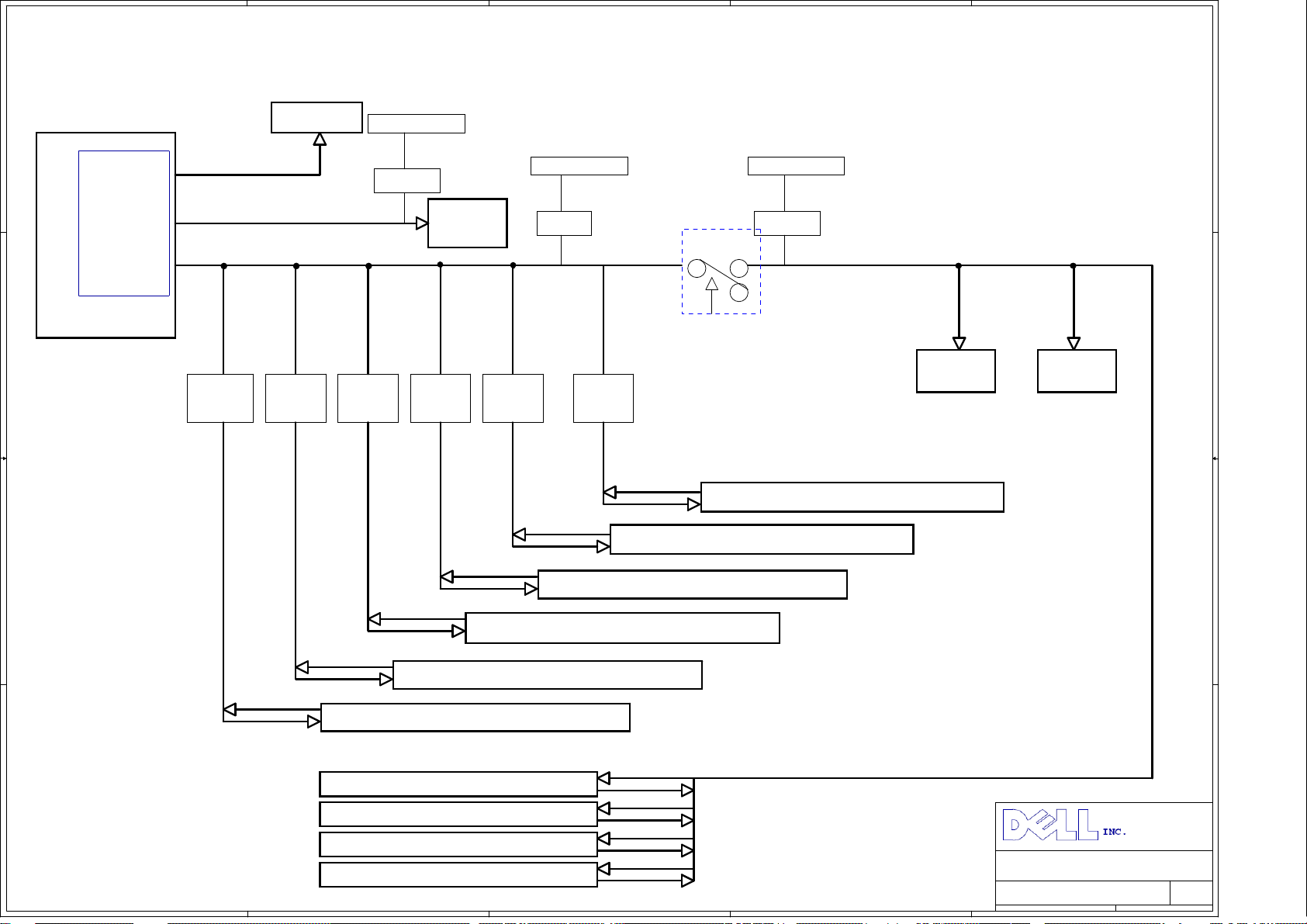

SMBUS DIAGRAM

4

3

2

1

D D

SMLINK0

Pull-up to +3V_S5

Pull-up to +3V_S5

Pull-up to +3V_S5

Pull-up to +3V

RS89 RS90

SMBus

Controller

SMLINK1

(S_SMLINK1_CLK/S_SMLINK1_DATA)

RESUME SMBUS

(S_SMBCLK_PCI/S_SMBDATA_PCI) (S_SMBCLK_MAIN/S_SMBDATA_MAIN)

SIO

IT8772

S_SMLINK1_CLK

S_SMLINK1_DATA

RNX6

SMdata1

SMdclk1

RNX6

BUS Switch

Main SMBUS

PCH

C C

RX7

RX12

RU37

RU38

RU35

RU36

RU53

RU54

RX9

RX10

CPU-XDP

X2R16

X2R10

PCH-XDP

mSATA

Mini-PCIe 1x

B B

PCI EXPRESS 16x

SLOT 1

PCIE 16x SMBUS

PCIE 4x SMBUS

PCIE 1x SMBUS

PCIE 1x SMBUS

A A

PCI EXPRESS 4x(2 Lans)

DIMM SLOTS

5

PCI EXPRESS 1x

DDR3 DIMM1 CHA

DDR3 DIMM3 CHA

DDR3 DIMM2 CHB

DDR3 DIMM4 CHB

4

PCI EXPRESS 1x

SLOT 3

SLOT 4

Address : 0 X00

Address : 0 X02

Address : 0 X04

Address : 0 X06

3

SLOT 2

Title

Title

Title

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Goodyear

Goodyear

Goodyear

1

A00

A00

A00

of

257星期三, 二月 20, 2013

of

257星期三, 二月 20, 2013

of

257星期三, 二月 20, 2013

5

4

3

2

1

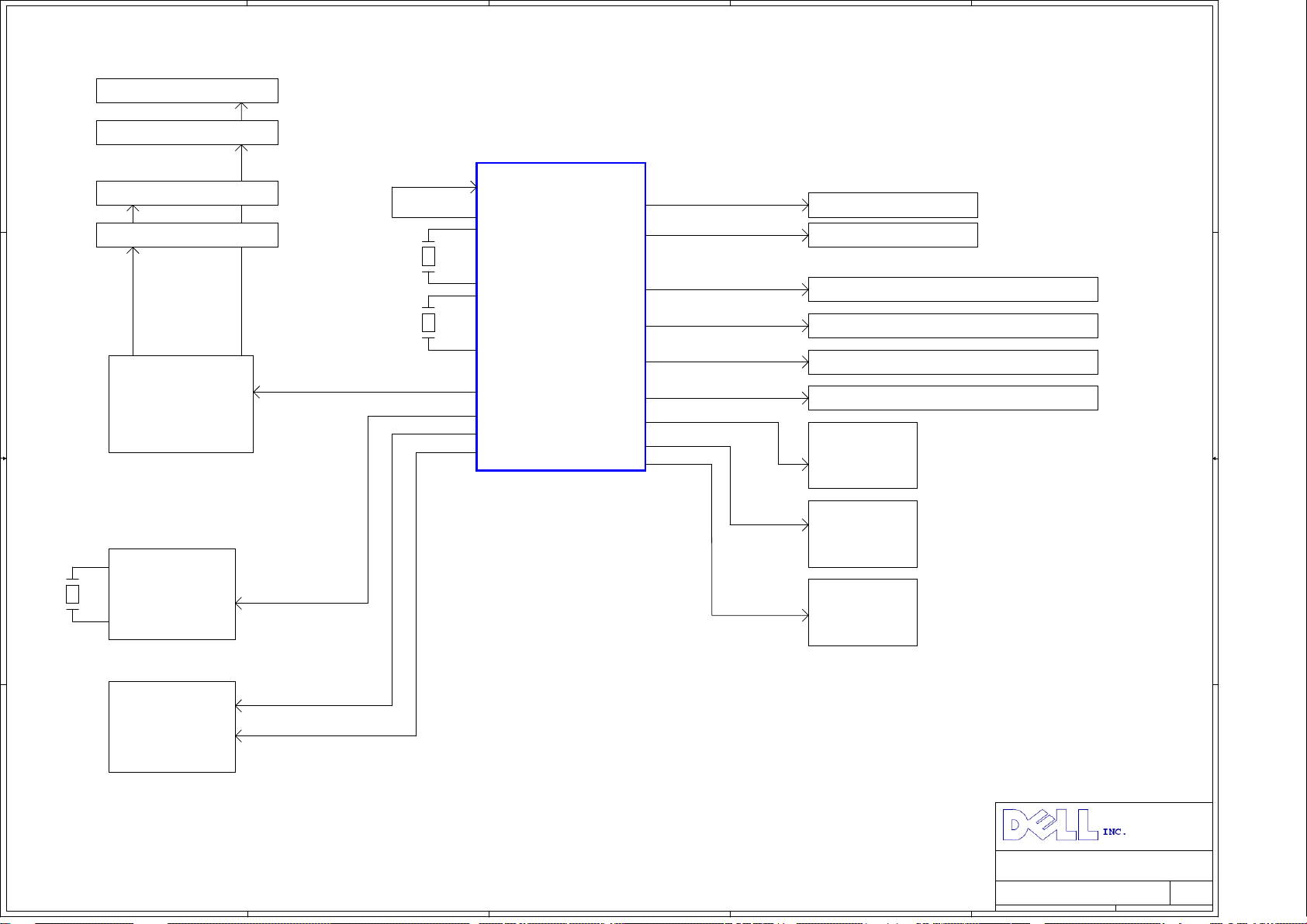

DIMM 2

D D

Channel B

DIMM 4

DIMM 1

Channel A

DIMM 3

C_PCI_SB

C_PCIEX1_1/C_PCIEX1#_1

MINI PCIe

C_MPCIE7_PCI/C_MPCIE7_PCI#

mSATA

25 MHZ

C_PCIEX16_1/C_PCIEX16#_1

PCI EXPRESS X16

32.768 KHZ

PCH

C C

D3_MA_CLK/CLK#[0:3]

D3_MB_CLK/CLK#[0:3]

C_PCIEX1_2/C_PCIEX1#_2

PCI EXPRESS X1

C_PCIEX1_3/C_PCIEX1#_3

PCI EXPRESS X1

C_PE_100M_MCP/C_PE_100M_MCP#

CPU

C_PCIEX1_4/C_PCIEX1#_4

C_PCH_ITP/C_PCH_ITP#

C_SRC1_PCH/C_SRC1_PCH#

PCI EXPRESS X4(2 Lans)

SLOT 1

SLOT 2

SLOT 3

SLOT 4

CPU XDP

PCH XDP

B B

25 MHZ

RTL8111G-CG

C_PCIE_L1/C_PCIE_L1#

C_LPC_TPM

LPC HEADER

C_LPC_SIO

SUPER IO

A A

5

C_48M_SIO

Title

Title

Title

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

Clock Distribution

Clock Distribution

Clock Distribution

Goodyear

Goodyear

Goodyear

1

A00

A00

A00

of

357星期三, 二月 20, 2013

of

357星期三, 二月 20, 2013

of

357星期三, 二月 20, 2013

5

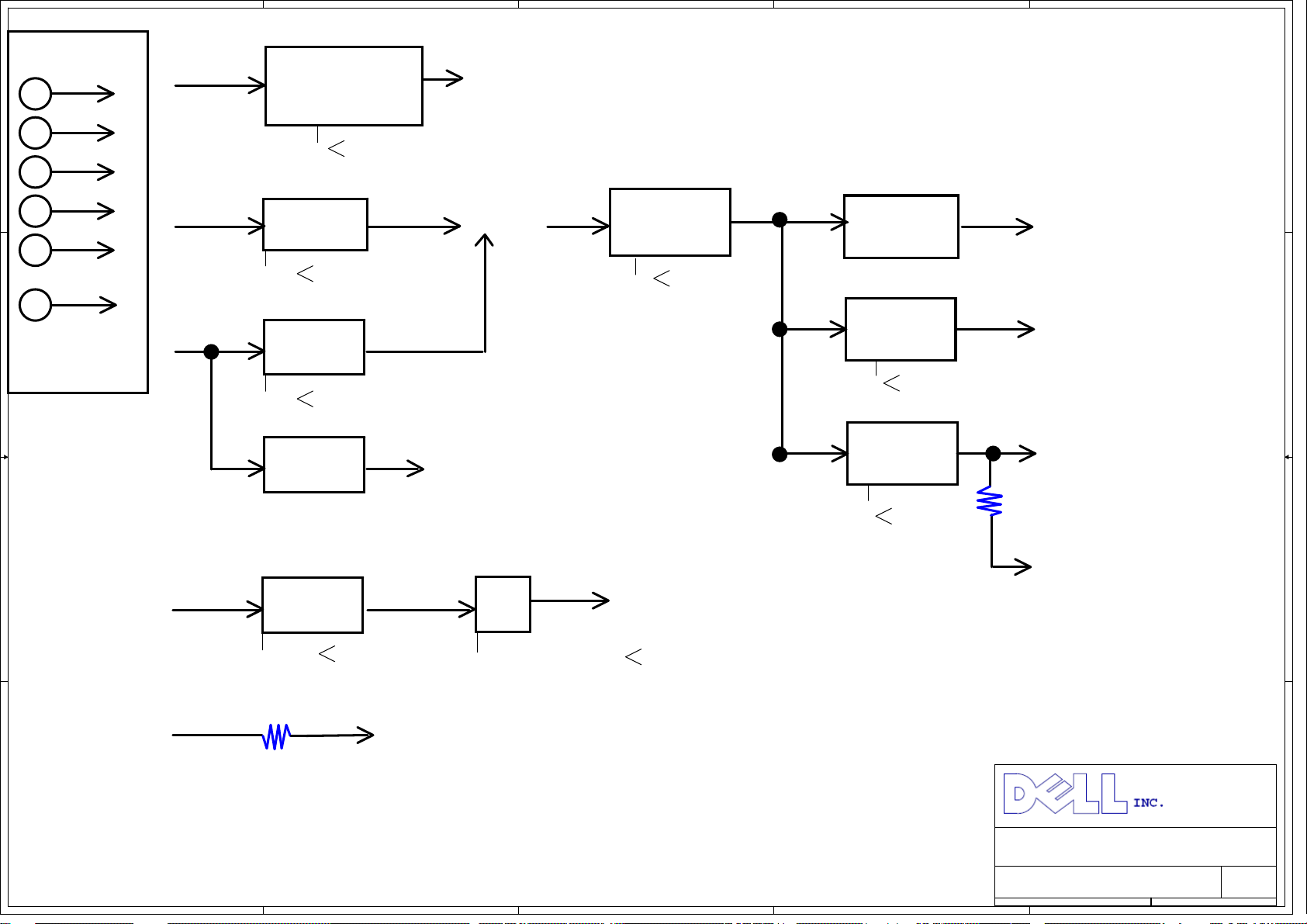

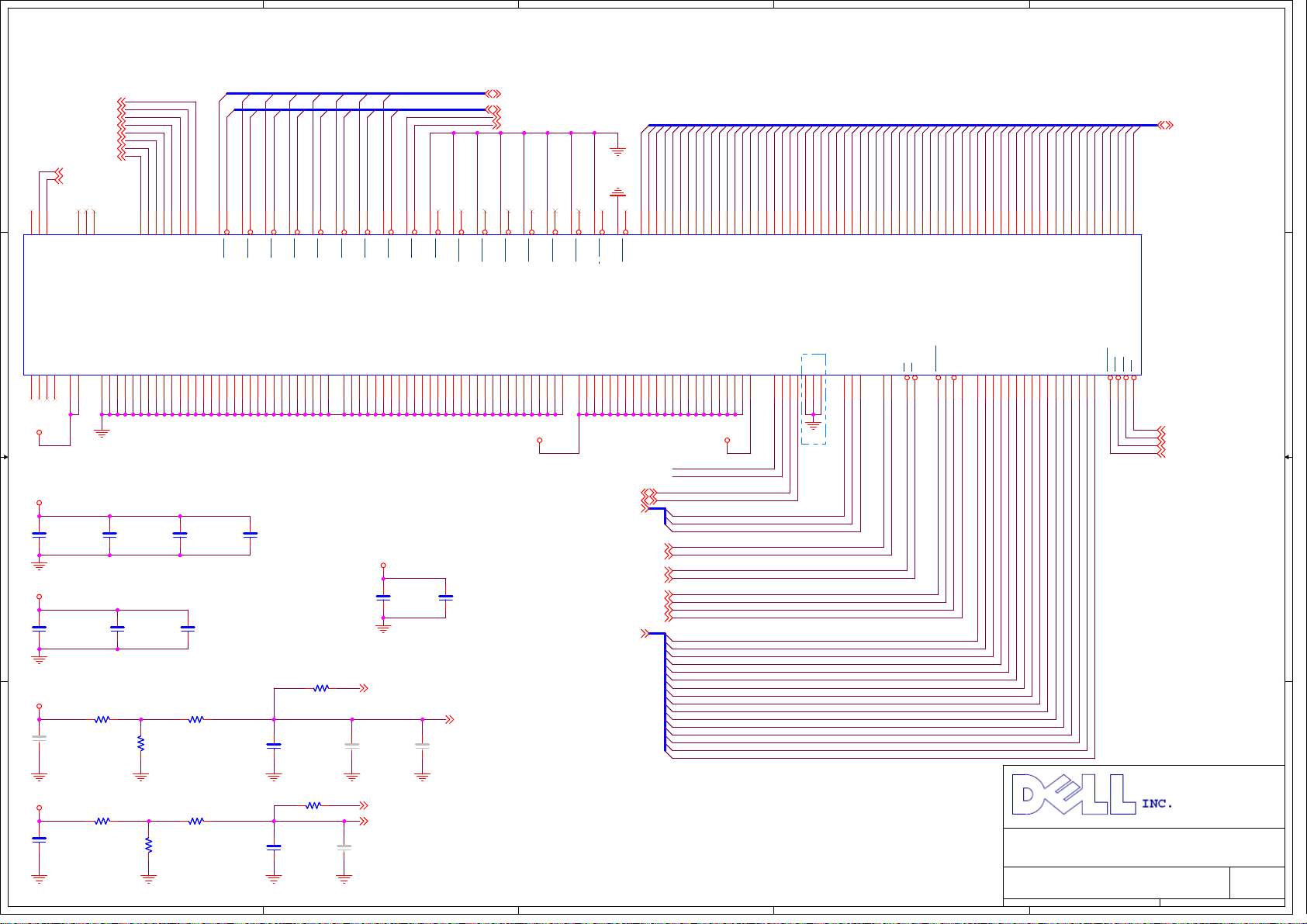

POWER DELIVERY MAP

4

3

2

1

PSU

2X12

S0

+5V

5V

D D

-12V

5VSB

3V

12V

+3V

+12V

-12V

+5VSB

S0

S0

S0

S0,S3,S4,S5,DSW

2X2

+12V_CPU

12V

C C

S0

+12V_CPU

+5V

+5VSB

S0

S0,S3,S4,S5,DSW

VCC_CORE

Richtek RT8884B+RT9611A

VRD12.5 switcher, 3ph

S0

SVID

LL = 1.5m ohms

+3V

N-FET

AOD452AL

Switch

P-FET

AP2305GN

Switch

LDO

AZ1084D

3.3V,3A

H=Power on

L=Power off

H=Power off

L=Power on

3VSBSW#

3VSBSW#

H=Power on

L=Power off

+3V_DUAL

+VCORE

+5VDUAL

S0,S3,S4,S5,DSW

S0

S0,S3

DDR3

ANPEC APW7120

Switcher, 1ph

1.508V,25A

+/- 5% DC+ AC

S_SLP_S4#

OR+3V

H=Power on

L=Power off

+1P5V_SM

S0,S3

DDR3 Vtt

Richtek RT9045

Linear

0.75V, 1.1A TDC

+/- 5% DC+ AC

PCH IO

N-FET AMP2306

1.5V, 0.35A Imax

+/- 5% DC+ AC

H=Power on

+3V

L=Power off

PCH Core

Linear OP LM358

1.05V, 5A Imax

+/- 5% DC+ AC

+1P5V_SM_VTT

+1P5V_PCH

+1P05V_PCH

S0

S0

S0

H=Power on

+3V

L=Power off

B B

P-FET

AP2305GN

Switch

S_SLP_SUS#

Resistor, 0ohm

+3V_S5

Deep Sleep : Off

Default S0,S3,S4,S5

H=Power on

L=Power off

+3V_BG

P-FET

AP2305GN

Switch

S_SLP_S4#

S0

4

S0=1.5A,

S3=0.45A

S_PCIAUX_GATEOR

+3V_PCIAUX

Deep Sleep : Off

Default S0,S3

H=Power on

L=Power off

3

2

+3V

S0,S3,S4,S5,DSW

S0

+3V_DUAL

A A

5

RNP 0ohm resistor

+1P05V_ME

Default S0

Title

Title

Title

Power Delivery Map

Power Delivery Map

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet

Date: Sheet

Power Delivery Map

Goodyear

Goodyear

Goodyear

1

457星期三, 二月 20, 2013

457星期三, 二月 20, 2013

457星期三, 二月 20, 2013

A00

A00

A00

of

of

of

5

4

3

2

1

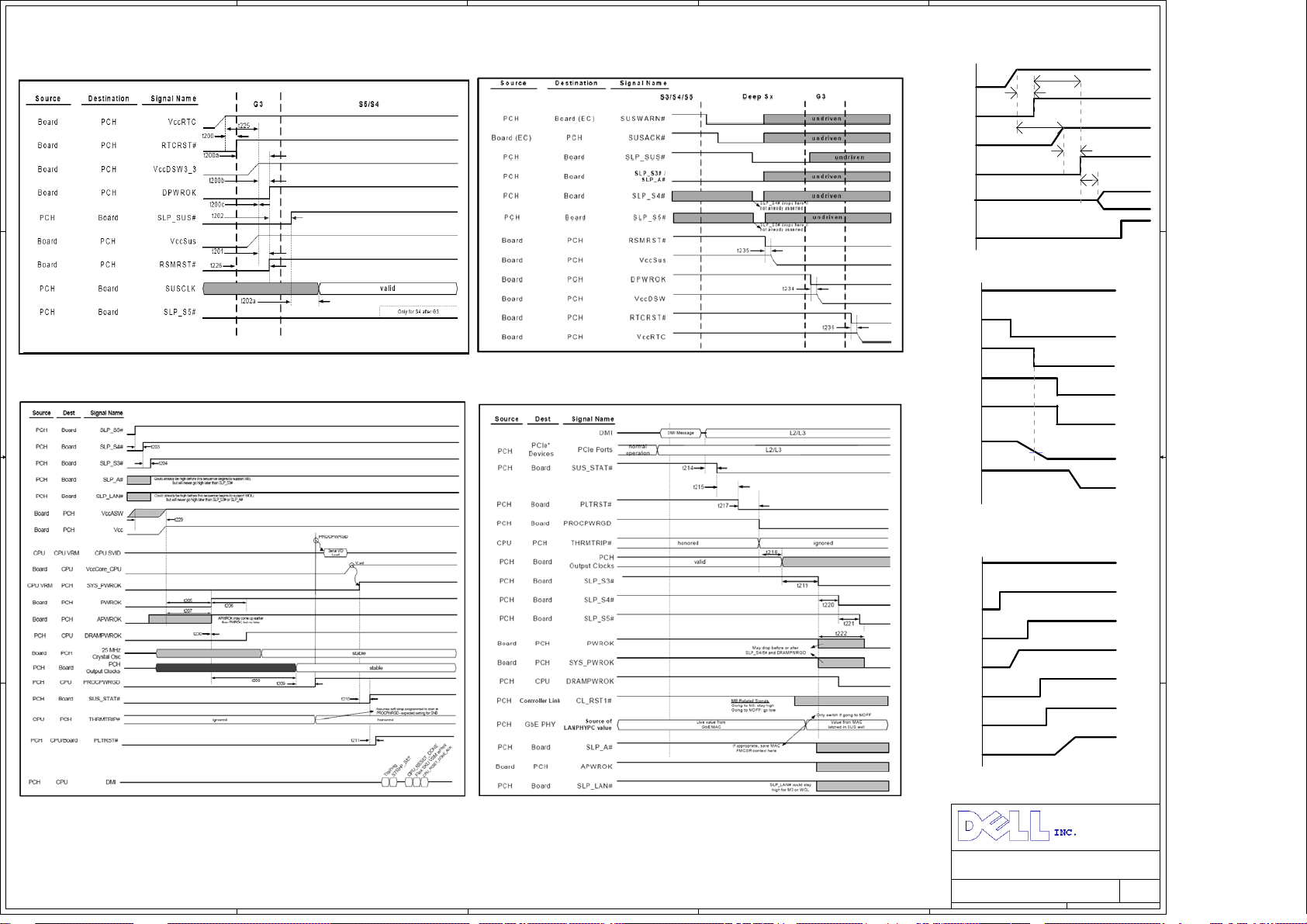

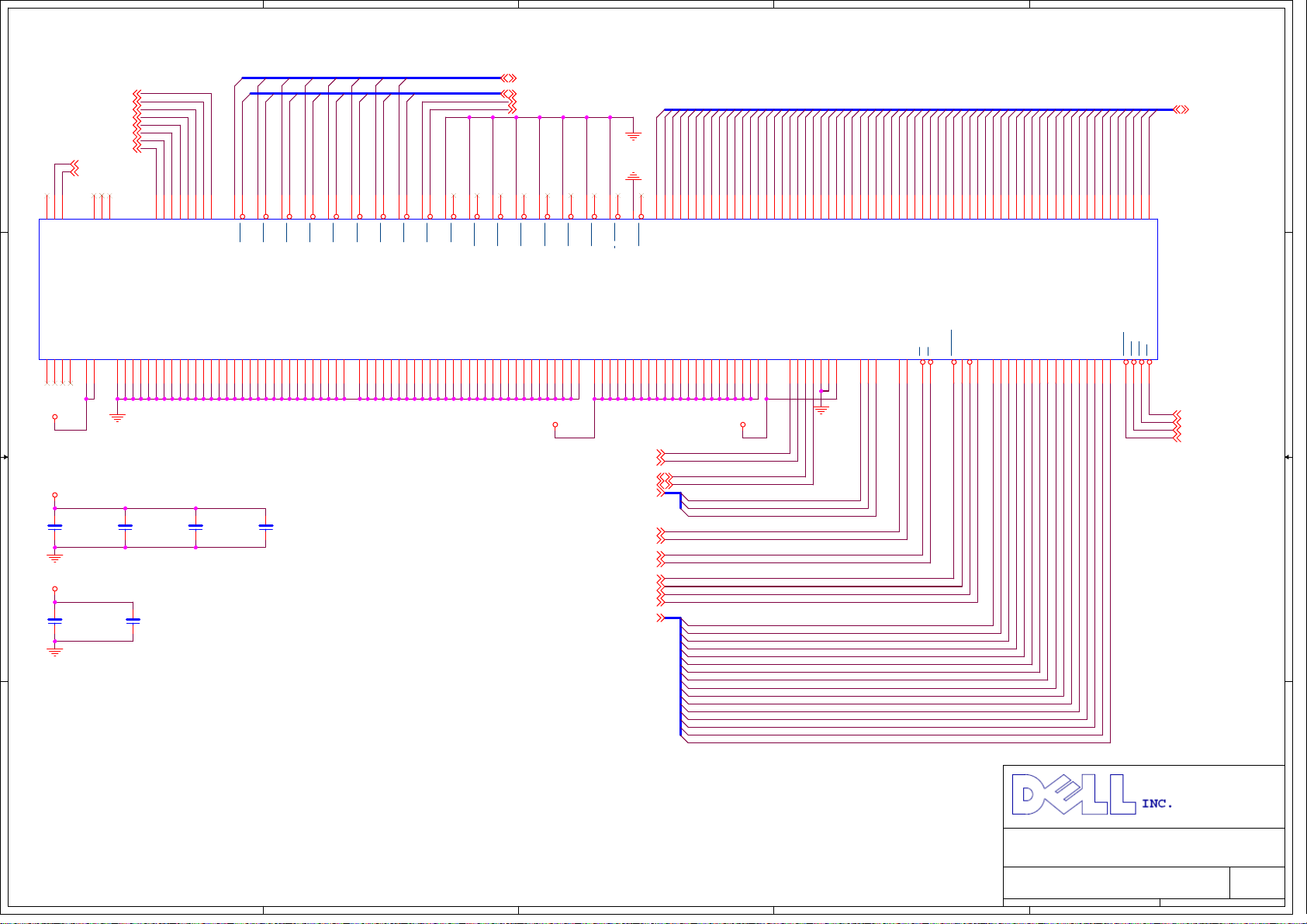

POWER ON Timing Diagram

G3 to S4/S5 Timing Diagram

G3 --> S4/S5 (with Deep Sleep support) Sx --> Deep S4/S5 -->G3

VccRTC

D D

RTCRST#

VCCSUS

RSMRST#

SUSCLK

SLP_S5#

t200

t226

t225

t201

t202

Deep Sleep Entry

DPWROK

C C

SUSWARN#

SUS_PWR_ACK

S5 --> S0 S0 --> S5

SLP_SUS#

RSMRST#

+5VDUAL

1.05V

+5V_S5/+3V_S5

Deep Sleep Exit

B B

DPWROK

SLP_SUS#

RSMRST#

+5V_S5/+3V_S5

SUSWARN#

SUS_PWR_ACK

+5VDUAL

A A

Title

Title

Title

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet of

5

4

3

2

Date: Sheet of

Power On Sequence

Power On Sequence

Power On Sequence

Goodyear

Goodyear

Goodyear

1

A00

A00

A00

of

557星期三, 二月 20, 2013

557星期三, 二月 20, 2013

557星期三, 二月 20, 2013

5

4

3

2

1

RESET / Power Good MAP

Sequence Signal Name:

O_PWRBTN#IN

(1)

S_SLP_S4# S_SLP_S3#

(2)

O_PSON#

(3)

D D

B_ATX_PWROK

(4)

PCH_MEPWRGD

(5)

S_PCH_SYSPWROK P_VR_READY

(6)

PWRGD_3V

(7)

H_DRAMPWRGD

(8)

H_PWRGD

(9)

S_PLTRST#

(10)

X_PLTRST_PCIE_SLOT# K_PCIRST#_SLOT

(11)

A_Z_RST#

(12)

D3_RESET#

H_RESET#_R S_PLTRST#_R

S_SLP_M#

PROCPWRGD

PWROK

> 1ms

UNCOREPWRGOOD

(9)

CPU-Haswell LGA1150

SM_DRAMPWROK

RESET*

(10)

SM_DRAMRST*

(9)

CPU-XDP

(1)

Deep Sleep Exit MAP

Sequence Signal Name:

O_PWRBTN#IN

(D1)

S_SLP_SUS#

(D2)

S_RSMRST#

(D3)

S_SUSWARN#

(D4)

S_SUS_PWR_ACK#

(D5)

(8)

(11)

DDRIII Slots

D3_RESET#

LAN

PE_RST_N

PCH-XDP

F_TP_XDP_RST

C C

APS DEBUG

Front Panel

O_PWRBTN#IN

FP_RST#

VRD 12

VR_RDY

B B

(1)

(1.1)

(D1)

(6)

PWRBTN#

SYS_PWROK

SYS_RESET#

PROCPWRGD

AND

PCH

DRAMPWROK

PLTRST# LRESET#

(8)

(10)

PCIRST#3

(7)

PWROK

(2)

SLP_S4# SLP_S4_S5#

(2)

PWRGD_3V

SLP_S3#SLP_S3#

(2)

(1)

PANSWH#

S_PWRBTN#

PS_ON#

PWRGD_PS

PCIRST#2

(4)

(11)

(3)

Mini-PCIe

PERST#

ATX Power

PSON

PWROK

HD Audio

RESET#

(12)

HDA_RST#

RSMRST#

SIO-ITE IT8772

(D3)

Sequence

Logic

(5)

APWROK

A A

SUSACK#

Sequence

SUSWARN#

(D4)(D5)

SLP_SUS#

(D2)

Circuit

Logic

Circuit

Title

Title

Title

Reset / Power Good Map

Reset / Power Good Map

Reset / Power Good Map

DWG NO Rev

DWG NO Rev

DWG NO Rev

Goodyear

Goodyear

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Goodyear

657星期三, 二月 20, 2013

657星期三, 二月 20, 2013

657星期三, 二月 20, 2013

1

A00

A00

A00

of

of

of

5

4

3

2

1

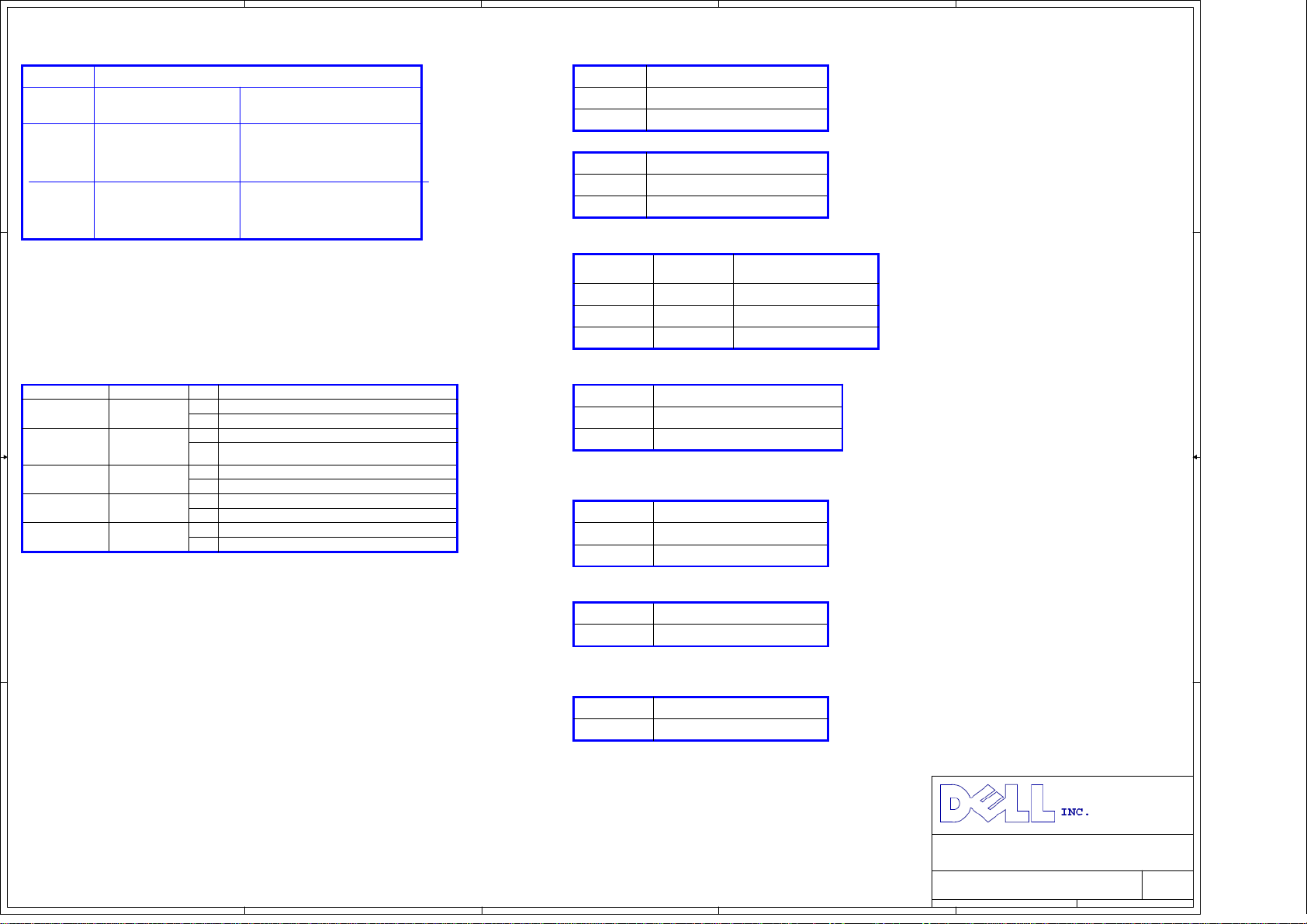

STRAPPING Table

PCH

CPU side

CFG[19:0] Description

D D

C C

[2]

[3]

[6:5]

PCI Express static x16

lane numbering reversal

PCI Express* Static x4 Lane

Numbering Reversal

PCI Express Bifurcation

1: normal

0: lane numbers reversed

1 = Normal operation

0 = Lane numbers reversed

00: 1x8, 2x4 PCI Express

01: reserved

10: 2x8 PCI Express

11: 1x16 PCI Express

Default

Default

Default

No Reboot Mode

SPKR

(IN-PD)

High

Low

Topblock Swap Mode

GPIO55

(IN-PU)

High

Low

Boot BIOS Destination Selection

GPIO51

(IN-PU)

Low

High

High

Description

No reboot mode: Enable

No reboot mode: Disable

Description

Topblock swap mode: Disable

Topblock swap mode: Enable

SATA1GP/GP19

(IN-PU)

Low

Low

High

DEFAULT

DEFAULT

Description

Flash cycle routed to LPC

Flash cycle routed to PCI

Flash cycle routed to SPI

SIO IT8772E/EX

PIN NAME

JP1

Pin23

JP2

Pin57

JP4

Pin61

JP3

Pin59

JP8

Pin30

B B

A A

NET

JP1

O_RTS1#_R

O_DTR1#_R

O_TXD1_R

S_SLP_S3#

Strapping description

EUP

1

DSW

0

Disable WDT to reset PWRGD

1

0

Enable WDT to reset PWRGD

Disable K8 power sequence function

1

Enable K8 power sequence function

0

The default value of EC Index 63h/6Bh/73h is 80h

1

The default value of EC Index 63h/6Bh/73h is 00h

0

RSMRST# output detected by 3VSB

1

RSMRST# output detected by SYS_3VSB

0

DEFAULT

DEFAULT

DEFAULT

DEFAULT

DEFAULT

ME Disable (Flash overide)

HDA_SDO

High

Low

TLS Confidentiality

SAAT3GP/

GPIO37

High

Low

On-Die PLL Voltage Regulator

GPIO62/SUSCLK

(IN-PU)

High

DMI Rx Termination

GPIO36

(IN-PD)

Low DMI Rx Termination Voltage

Description

ME Disable (Flash overide): Enable

ME Disable (Flash overide): Disable

Description

ME Crypto TLS cipher suite

with confidentiality

ME Crypto TLS cipher suite

with no confidentiality

Description

Regulator is enabled. DEFAULT

Description

DEFAULT

DEFAULT

Title

Title

Title

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

GPIO/IRQ/IDSEL Table

GPIO/IRQ/IDSEL Table

GPIO/IRQ/IDSEL Table

Goodyear

Goodyear

Goodyear

757星期三, 二月 20, 2013

757星期三, 二月 20, 2013

757星期三, 二月 20, 2013

1

A00

A00

A00

of

of

of

5

D D

C C

4

3

2

1

B B

A A

Title

Title

Title

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

GPIO Table

GPIO Table

GPIO Table

Goodyear

Goodyear

Goodyear

1

A00

A00

A00

of

857星期三, 二月 20, 2013

of

857星期三, 二月 20, 2013

of

857星期三, 二月 20, 2013

5

4

3

2

1

DDR3 CH-A

D3_DQ_A[63..0]15,16

D D

C C

Bit Swap for layout

B B

D3_DQS_A015,16

D3_DQS_A115,16

D3_DQS_A215,16

D3_DQS_A315,16

D3_DQS_A415,16

D3_DQS_A515,16

D3_DQS_A615,16

D3_DQS_A715,16

ECC

ECC

A A

D3_DQS_A815,16

D3_DQS_A#015,16

D3_DQS_A#115,16

D3_DQS_A#215,16

D3_DQS_A#315,16

D3_DQS_A#415,16

D3_DQS_A#515,16

D3_DQS_A#615,16

D3_DQS_A#715,16

D3_DQS_A#815,16

D3_DQ_A0

D3_DQ_A1

D3_DQ_A2

D3_DQ_A3

D3_DQ_A4

D3_DQ_A5

D3_DQ_A6

D3_DQ_A7

D3_DQ_A9

D3_DQ_A13

D3_DQ_A10

D3_DQ_A11

D3_DQ_A12

D3_DQ_A8

D3_DQ_A14

D3_DQ_A15

D3_DQ_A17

D3_DQ_A21

D3_DQ_A18

D3_DQ_A19

D3_DQ_A20

D3_DQ_A16

D3_DQ_A22

D3_DQ_A23

D3_DQ_A25

D3_DQ_A29

D3_DQ_A26

D3_DQ_A27

D3_DQ_A28

D3_DQ_A24

D3_DQ_A30

D3_DQ_A31

D3_DQ_A33

D3_DQ_A37

D3_DQ_A34

D3_DQ_A35

D3_DQ_A36

D3_DQ_A32

D3_DQ_A38

D3_DQ_A39

D3_DQ_A41

D3_DQ_A45

D3_DQ_A42

D3_DQ_A43

D3_DQ_A44

D3_DQ_A40

D3_DQ_A46

D3_DQ_A47

D3_DQ_A49

D3_DQ_A53

D3_DQ_A50

D3_DQ_A51

D3_DQ_A52

D3_DQ_A48

D3_DQ_A54

D3_DQ_A55

D3_DQ_A57

D3_DQ_A61

D3_DQ_A58

D3_DQ_A59

D3_DQ_A60

D3_DQ_A56

D3_DQ_A62

D3_DQ_A63

UH1A

UH1A

AD38

SA_DQ[0]

AD39

SA_DQ[1]

AF38

SA_DQ[2]

AF39

SA_DQ[3]

AD37

SA_DQ[4]

AD40

SA_DQ[5]

AF37

SA_DQ[6]

AF40

SA_DQ[7]

AH40

SA_DQ[8]

AH39

SA_DQ[9]

AK38

SA_DQ[10]

AK39

SA_DQ[11]

AH37

SA_DQ[12]

AH38

SA_DQ[13]

AK37

SA_DQ[14]

AK40

SA_DQ[15]

AM40

SA_DQ[16]

AM39

SA_DQ[17]

AP38

SA_DQ[18]

AP39

SA_DQ[19]

AM37

SA_DQ[20]

AM38

SA_DQ[21]

AP37

SA_DQ[22]

AP40

SA_DQ[23]

AV37

SA_DQ[24]

AW37

SA_DQ[25]

AU35

SA_DQ[26]

AV35

SA_DQ[27]

AT37

SA_DQ[28]

AU37

SA_DQ[29]

AT35

SA_DQ[30]

AW35

SA_DQ[31]

AY6

SA_DQ[32]

AU6

SA_DQ[33]

AV4

SA_DQ[34]

AU4

SA_DQ[35]

AW6

SA_DQ[36]

AV6

SA_DQ[37]

AW4

SA_DQ[38]

AY4

SA_DQ[39]

AR1

SA_DQ[40]

AR4

SA_DQ[41]

AN3

SA_DQ[42]

AN4

SA_DQ[43]

AR2

SA_DQ[44]

AR3

SA_DQ[45]

AN2

SA_DQ[46]

AN1

SA_DQ[47]

AL1

SA_DQ[48]

AL4

SA_DQ[49]

AJ3

SA_DQ[50]

AJ4

SA_DQ[51]

AL2

SA_DQ[52]

AL3

SA_DQ[53]

AJ2

SA_DQ[54]

AJ1

SA_DQ[55]

AG1

SA_DQ[56]

AG4

SA_DQ[57]

AE3

SA_DQ[58]

AE4

SA_DQ[59]

AG2

SA_DQ[60]

AG3

SA_DQ[61]

AE2

SA_DQ[62]

AE1

SA_DQ[63]

AE39

SA_DQS[0]

AJ39

SA_DQS[1]

AN39

SA_DQS[2]

AV36

SA_DQS[3]

AV5

SA_DQS[4]

AP3

SA_DQS[5]

AK3

SA_DQS[6]

AF3

SA_DQS[7]

AV32

SA_DQS[8]

AE38

SA_DQS#[0]

AJ38

SA_DQS#[1]

AN38

SA_DQS#[2]

AU36

SA_DQS#[3]

AW5

SA_DQS#[4]

AP2

SA_DQS#[5]

AK2

SA_DQS#[6]

AF2

SA_DQS#[7]

AU32

SA_DQS#[8]

PE115027-4041-0DF

PE115027-4041-0DF

1 OF 10

1 OF 10

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

SA_ODT[0]

SA_ODT[1]

SA_ODT[2]

SA_ODT[3]

SA_ECC_CB[0]

SA_ECC_CB[1]

SA_ECC_CB[2]

SA_ECC_CB[3]

SA_ECC_CB[4]

SA_ECC_CB[5]

SA_ECC_CB[6]

SA_ECC_CB[7]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CKE[0]

SA_CKE[1]

SA_CKE[2]

SA_CKE[3]

SA_CS#[0]

SA_CS#[1]

SA_CS#[2]

SA_CS#[3]

SA_CK[0]

SA_CK#[0]

SA_CK[1]

SA_CK#[1]

SA_CK[2]

SA_CK#[2]

SA_CK[3]

SA_CK#[3]

RSVD_46

SA_RAS#

SA_WE#

RSVD_47

RSVD_48

SA_CAS#

SM_DRAMRST#

AU13

AV16

AU16

AW17

AU17

AW18

AV17

AT18

AU18

AT19

AW11

AV19

AU19

AY10

AT20

AU21

AW10

AY8

AW9

AU8

AW33

AV33

AU31

AV31

AT33

AU33

AT31

AW31

AV12

AY11

AT21

AV22

AT23

AU22

AU23

AU14

AV9

AU10

AW8

AY15

AY16

AW15

AV15

AV14

AW14

AW13

AY13

AW12

AU12

AU11

AV20

AW27

AU9

AK22

D3_MAA0

D3_MAA1

D3_MAA2

D3_MAA3

D3_MAA4

D3_MAA5

D3_MAA6

D3_MAA7

D3_MAA8

D3_MAA9

D3_MAA10

D3_MAA11

D3_MAA12

D3_MAA13

D3_MAA14

D3_MAA15

D3_BAA0

D3_BAA1

D3_BAA2

D3_SM_DRAMRST#

CH3

CH3

*

*

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

D3_MAA[15..0] 15,16

D3_ODT_A0 15

D3_ODT_A1 15

D3_ODT_A2 16

D3_ODT_A3 16

D3_SA_ECC_CB1 15,16

D3_SA_ECC_CB5 15,16

D3_SA_ECC_CB2 15,16

D3_SA_ECC_CB3 15,16

D3_SA_ECC_CB4 15,16

D3_SA_ECC_CB0 15,16

D3_SA_ECC_CB6 15,16

D3_SA_ECC_CB7 15,16

D3_BAA[2..0] 15,16

D3_CKE_A0 15

D3_CKE_A1 15

D3_CKE_A2 16

D3_CKE_A3 16

D3_SCS_A#0 15

D3_SCS_A#1 15

D3_SCS_A#2 16

D3_SCS_A#3 16

D3_MA_CLK0 15

D3_MA_CLK#0 15

D3_MA_CLK1 15

D3_MA_CLK#1 15

D3_MA_CLK2 16

D3_MA_CLK#2 16

D3_MA_CLK3 16

D3_MA_CLK#3 16

D3_RASA# 15,16

D3_WEA# 15,16

D3_CASA# 15,16

R30 0

R30 0

*

*

+/-5%

+/-5%

ECC

D3_RESET# 15,16,17,18

Title

Title

Title

CPU-1: DDR3_CHA

CPU-1: DDR3_CHA

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

CPU-1: DDR3_CHA

Goodyear

Goodyear

Goodyear

1

X02

X02

X02

of

957星期三, 二月 20, 2013

of

957星期三, 二月 20, 2013

of

957星期三, 二月 20, 2013

5

4

3

2

1

D3_DQ_B[63..0]17,18

D3_DQ_B0

D3_DQ_B1

D3_DQ_B2

D D

C C

B B

D3_DQS_B017,18

D3_DQS_B117,18

D3_DQS_B217,18

D3_DQS_B317,18

D3_DQS_B417,18

D3_DQS_B517,18

D3_DQS_B617,18

D3_DQS_B717,18

ECC

ECC

D3_DQS_B817,18

D3_DQS_B#017,18

D3_DQS_B#117,18

D3_DQS_B#217,18

D3_DQS_B#317,18

D3_DQS_B#417,18

D3_DQS_B#517,18

D3_DQS_B#617,18

D3_DQS_B#717,18

D3_DQS_B#817,18

D3_DQ_B3

D3_DQ_B4

D3_DQ_B5

D3_DQ_B6

D3_DQ_B7

D3_DQ_B8

D3_DQ_B9

D3_DQ_B10

D3_DQ_B11

D3_DQ_B12

D3_DQ_B13

D3_DQ_B14

D3_DQ_B15

D3_DQ_B17

D3_DQ_B21

D3_DQ_B19

D3_DQ_B23

D3_DQ_B20

D3_DQ_B16

D3_DQ_B18

D3_DQ_B22

D3_DQ_B25

D3_DQ_B28

D3_DQ_B27

D3_DQ_B30

D3_DQ_B24

D3_DQ_B29

D3_DQ_B26

D3_DQ_B31

D3_DQ_B32

D3_DQ_B33

D3_DQ_B34

D3_DQ_B35

D3_DQ_B36

D3_DQ_B37

D3_DQ_B38

D3_DQ_B39

D3_DQ_B45

D3_DQ_B41

D3_DQ_B47

D3_DQ_B43

D3_DQ_B44

D3_DQ_B40

D3_DQ_B46

D3_DQ_B42

D3_DQ_B52

D3_DQ_B53

D3_DQ_B50

D3_DQ_B55

D3_DQ_B48

D3_DQ_B49

D3_DQ_B54

D3_DQ_B51

D3_DQ_B61

D3_DQ_B60

D3_DQ_B59

D3_DQ_B63

D3_DQ_B56

D3_DQ_B57

D3_DQ_B58

D3_DQ_B62

DDR3 CH-B

UH1B

UH1B

AE34

SB_DQ[0]

AE35

SB_DQ[1]

AG35

SB_DQ[2]

AH35

SB_DQ[3]

AD34

SB_DQ[4]

AD35

SB_DQ[5]

AG34

SB_DQ[6]

AH34

SB_DQ[7]

AL34

SB_DQ[8]

AL35

SB_DQ[9]

AK31

SB_DQ[10]

AL31

SB_DQ[11]

AK34

SB_DQ[12]

AK35

SB_DQ[13]

AK32

SB_DQ[14]

AL32

SB_DQ[15]

AN34

SB_DQ[16]

AP34

SB_DQ[17]

AN31

SB_DQ[18]

AP31

SB_DQ[19]

AN35

SB_DQ[20]

AP35

SB_DQ[21]

AN32

SB_DQ[22]

AP32

SB_DQ[23]

AM29

SB_DQ[24]

AM28

SB_DQ[25]

AR29

SB_DQ[26]

AR28

SB_DQ[27]

AL29

SB_DQ[28]

AL28

SB_DQ[29]

AP29

SB_DQ[30]

AP28

SB_DQ[31]

AR12

SB_DQ[32]

AP12

SB_DQ[33]

AL13

SB_DQ[34]

AL12

SB_DQ[35]

AR13

SB_DQ[36]

AP13

SB_DQ[37]

AM13

SB_DQ[38]

AM12

SB_DQ[39]

AR9

SB_DQ[40]

AP9

SB_DQ[41]

AR6

SB_DQ[42]

AP6

SB_DQ[43]

AR10

SB_DQ[44]

AP10

SB_DQ[45]

AR7

SB_DQ[46]

AP7

SB_DQ[47]

AM9

SB_DQ[48]

AL9

SB_DQ[49]

AL6

SB_DQ[50]

AL7

SB_DQ[51]

AM10

SB_DQ[52]

AL10

SB_DQ[53]

AM6

SB_DQ[54]

AM7

SB_DQ[55]

AH6

SB_DQ[56]

AH7

SB_DQ[57]

AE6

SB_DQ[58]

AE7

SB_DQ[59]

AJ6

SB_DQ[60]

AJ7

SB_DQ[61]

AF6

SB_DQ[62]

AF7

SB_DQ[63]

AF35

SB_DQS[0]

AL33

SB_DQS[1]

AP33

SB_DQS[2]

AN28

SB_DQS[3]

AN12

SB_DQS[4]

AP8

SB_DQS[5]

AL8

SB_DQS[6]

AG7

SB_DQS[7]

AN25

SB_DQS[8]

AF34

SB_DQS#[0]

AK33

SB_DQS#[1]

AN33

SB_DQS#[2]

AN29

SB_DQS#[3]

AN13

SB_DQS#[4]

AR8

SB_DQS#[5]

AM8

SB_DQS#[6]

AG6

SB_DQS#[7]

AN26

SB_DQS#[8]

PE115027-4041-0DF

PE115027-4041-0DF

SB_ECC_CB[0]

SB_ECC_CB[1]

SB_ECC_CB[2]

SB_ECC_CB[3]

SB_ECC_CB[4]

SB_ECC_CB[5]

SB_ECC_CB[6]

SB_ECC_CB[7]

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

2 OF 10

2 OF 10

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

SB_ODT[0]

SB_ODT[1]

SB_ODT[2]

SB_ODT[3]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CKE[0]

SB_CKE[1]

SB_CKE[2]

SB_CKE[3]

SB_CS#[0]

SB_CS#[1]

SB_CS#[2]

SB_CS#[3]

SB_CK[0]

SB_CK#[0]

SB_CK[1]

SB_CK#[1]

SB_CK[2]

SB_CK#[2]

SB_CK[3]

SB_CK#[3]

SB_CAS#

RSVD_49

SB_RAS#

SB_WE#

AL19

AK23

AM22

AM23

AP23

AL23

AY24

AV25

AU26

AW25

AP18

AY25

AV26

AR15

AV27

AY28

AM17

AL16

AM16

AK15

AM26

AM25

AP25

AP26

AL26

AL25

AR26

AR25

AK17

AL18

AW28

AW29

AY29

AU28

AU29

AP17

AN15

AN17

AL15

AM20

AM21

AP22

AP21

AN20

AN21

AP19

AP20

AP16

AL20

AM18

AK16

AB39

H_CPU_DIMM_VREF_A

AB40

H_CPU_DIMM_VREF_B

D3_MAB0

D3_MAB1

D3_MAB2

D3_MAB3

D3_MAB4

D3_MAB5

D3_MAB6

D3_MAB7

D3_MAB8

D3_MAB9

D3_MAB10

D3_MAB11

D3_MAB12

D3_MAB13

D3_MAB14

D3_MAB15

D3_BAB0

D3_BAB1

D3_BAB2

TPH4TPH4

CRB 0.7

CH79

CH79

22nF

22nF

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

RH113

RH113

*

*

24.9

24.9

+/-1%

+/-1%

D3_MAB[15..0] 17,18

D3_ODT_B0 17

D3_ODT_B1 17

D3_ODT_B2 18

D3_ODT_B3 18

D3_SB_ECC_CB4 17,18

D3_SB_ECC_CB5 17,18

D3_SB_ECC_CB6 17,18

D3_SB_ECC_CB7 17,18

D3_SB_ECC_CB0 17,18

D3_SB_ECC_CB1 17,18

D3_SB_ECC_CB2 17,18

D3_SB_ECC_CB3 17,18

D3_BAB[2..0] 17,18

D3_CKE_B0 17

D3_CKE_B1 17

D3_CKE_B2 18

D3_CKE_B3 18

D3_SCS_B#0 17

D3_SCS_B#1 17

D3_SCS_B#2 18

D3_SCS_B#3 18

D3_MB_CLK0 17

D3_MB_CLK#0 17

D3_MB_CLK1 17

D3_MB_CLK#1 17

D3_MB_CLK2 18

D3_MB_CLK#2 18

D3_MB_CLK3 18

D3_MB_CLK#3 18

D3_CASB# 17,18

D3_RASB# 17,18

D3_WEB# 17,18

CH80

CH80

22nF

22nF

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

RH114

RH114

*

*

24.9

24.9

+/-1%

+/-1%

ECC

H_CPU_DIMM_VREF_A 15

H_CPU_DIMM_VREF_B 17

A A

Title

Title

Title

CPU-2: DDR3_CHB

CPU-2: DDR3_CHB

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

CPU-2: DDR3_CHB

Goodyear

Goodyear

Goodyear

1

A00

A00

A00

of

10 57星期三, 二月 20, 2013

of

10 57星期三, 二月 20, 2013

of

10 57星期三, 二月 20, 2013

5

H_CPU_VCCIO_RIGHT

RH4

RH4

*

*

100 Ohm

100 Ohm

+/-1%

+/-1%

Dummy

C_PE_100M_DMI#24

C_PE_100M_DMI24

D D

C C

H_VIDSCLK54

H_VIDSOUT54

H_VIDALERT#54

H_DRAM_PWRGD23

H_PWRGOOD23,44,51

H_RESET#22,29,44

H_PM_SYNC22

H_PECI22,29

H_PROCHOT#54

H_THERMTRIP#22

H_SKTOCC#23

Intel XDP_CPU required

H_TCK44

H_TDI44

H_TDO44

H_TMS44

H_TRST#44

H_PRDY#44

H_PREQ#44

FP_RST#23,43,44,46

Dummy

RH77

RH77

*

*

75

75

+/-1%

+/-1%

RH8 44.2Ohm

RH8 44.2Ohm

TPH64TPH64

H_CFG044

H_CFG144

H_CFG244

H_CFG344

H_CFG444

H_CFG544

H_CFG644

H_CFG744

H_CFG844

H_CFG944

H_CFG1044

H_CFG1144

H_CFG1244

H_CFG1344

H_CFG1444

H_CFG1544

H_CFG1744

H_CFG1644

H_CFG1944

H_CFG1844

RH63 49.9

RH63 49.9

*

*

+/-1%

+/-1%

*

*

+/-1%

+/-1%

TPH5TPH5

TPH6TPH6

*

*

RH78

RH78

110Ohm

110Ohm

+/-1%

+/-1%

H_VIDALERT#_R

H_PWRGOOD

H_RESET#

H_CATERR#

H_PROCHOT#

H_THERMTRIP#

H_SM_VREF

H_CFG0

H_CFG1

H_CFG2

H_CFG3

H_CFG4

H_CFG5

H_CFG6

H_CFG7

H_CFG8

H_CFG9

H_CFG10

H_CFG11

H_CFG12

H_CFG13

H_CFG14

H_CFG15

H_CFG17

H_CFG16

H_CFG19

H_CFG18

H_PRDY#

FP_RST#

H_TESTLOW

H_TP_RSVD_K8

H_TP_RSVD_J10

CPU REST CIRCUITRY

EnsuretimingsandedgeratesaremetonPLTRST#goingtoprocessor.

B B

RH58

RH58

*

*

1K

1K

+/-5%

+/-5%

Dummy

Dummy

S_RST_CPU#_G S_RST_CPU#_O

+/-5%Dummy

+/-5%Dummy

+/-5%Dummy

+/-5%Dummy

S_RST_CPU#

RH61 10K

RH61 10K

*

S_PLTRST#21,29,31,35,43,44

*

RH71 5.1K Ohm

RH71 5.1K Ohm

*

*

B

QH3

QH3

MMBT3904-7-F

MMBT3904-7-F

E C

Dummy

Dummy

*

*

RH76

RH76

91 Ohm

91 Ohm

+/-1%

+/-1%

Dummy

Dummy

4

MCP - VID,CTRL, MSIC

UH1E

UH1E

V4

BCLK#

V5

BCLK

C38

VIDSCLK

C37

VIDSOUT

B37

VIDALERT#

AK21

SM_DRAMPWROK

AB35

PWRGOOD

M39

RESET#

P36

PM_SYNC

N37

PECI

M36

CATERR#

K38

PROCHOT#

F37

THERMTRIP#

D38

SKTOCC#

AB38

SM_VREF

AA37

CFG[0]

Y38

CFG[1]

AA36

CFG[2]

W38

CFG[3]

V39

CFG[4]

U39

CFG[5]

U40

CFG[6]

V38

CFG[7]

T40

CFG[8]

Y35

CFG[9]

AA34

CFG[10]

V37

CFG[11]

Y34

CFG[12]

U38

CFG[13]

W34

CFG[14]

V35

CFG[15]

Y36

CFG[17]

Y37

CFG[16]

V36

CFG[19]

W36

CFG[18]

D39

TCK

F38

TDI

F39

TDO

E39

TMS

E37

TRST#

L39

PRDY#

L37

PREQ#

G40

DBR#

N5

TESTLOW_N5

K8

RSVD_TP_18

J10

RSVD_TP_20

5 OF 10

QH4

QH4

2N7002

2N7002

Dummy

Dummy

5 OF 10

*

*

RH62

RH62

75

75

+/-1%

+/-1%

Dummy

Dummy

PE115027-4041-0DF

PE115027-4041-0DF

+3V+3V_DUAL

*

*

DS

G

RH59

RH59

178 Ohm

178 Ohm

+/-1%

+/-1%

Dummy

Dummy

TESTLOW_P6

RSVD_TP_19

RSVD_TP_21

PWR_DEBUG

RSVD_TP_7

RSVD_TP_8

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

RSVD_TP_9

RSVD_TP_10

VCOMP_OUT

VCC_SENSE

VSS_SENSE

DPLL_REF_CLK#

DPLL_REF_CLK

CFG_RCOMP

RH74 0 +/-5%

RH74 0 +/-5%

*

*

CH38

CH38

100pF

100pF

50V, NPO, +/-5%

50V, NPO, +/-5%

Dummy

Dummy

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

RSVD_3

RSVD_4

RSVD_6

RSVD_7

RSVD_8

RSVD_9

VCC_1

RSVD_10

VSS_1

VSS_480

VSS_479

RSVD_15

RSVD_16

RSVD_18

RSVD_19

RSVD_50

RSVD_20

RSVD_21

RSVD_22

RSVD_23

RSVD_24

RSVD_25

RSVD_26

RSVD_27

VSS_3

VSS_4

VSS_5

VSS_6

RSVD28

*

*

Dummy

Dummy

G39

J39

G38

H37

H38

J38

K39

K37

T35

M38

P6

K9

H15

J9

H14

M8

AV2

J16

H16

N40

N39

V7

AB6

K13

J8

R1

P1

R2

AB36

AW2

AV1

AC8

P4

U8

AB33

T8

Y8

M10

L10

M11

L12

W8

R33

P33

E40

N33

J11

M9

J7

F40

N35

W6

W5

H40

3

H_TP_BPM#2

H_TP_BPM#3

H_TP_BPM#4

H_TP_BPM#5

H_TP_BPM#6

H_TP_BPM#7

H_TP_RSVD_T35

H_TP_RSVD_M38

H_TESTLOW_2

H_VCCSTH_PECI

H_TP_RSVD_J9

H_PWR_DEBUG

H_TP_RSVD_V7

H_TP_RSVD_AB6

H_TP_RSVD_K13

H_TP_RSVD_J8

H_SM_RCOMP_0

H_SM_RCOMP_1

H_SM_RCOMP_2

H_TP_RSVD_AB36

H_TP_RSVD_AW2

H_TP_RSVD_AV1

H_TP_RSVD_AC8

H_TP_RSVD_U8

H_TP_RSVD_AB33

H_TP_RSVD_T8

H_TP_RSVD_Y8

H_TP_RSVD_M10

H_TP_RSVD_L10

H_TP_RSVD_M11

H_TP_RSVD_L12

H_TP_RSVD_W8

H_TP_RSVD_R33

H_TP_RSVD_P33

H_TP_RSVD_N35

H_TP_CFG_RCOMP

H_RESET# 22,29,44

RH14 49.9

RH14 49.9

H_BPM#0 44

H_BPM#1 44

TPH65TPH65

TPH66TPH66

TPH67TPH67

TPH68TPH68

TPH69TPH69

TPH70TPH70

TPH7TPH7

*

*

*

*

*

*

TPH17TPH17

TPH18TPH18

TPH19TPH19

TPH20TPH20

TPH21TPH21

TPH22TPH22

TPH23TPH23

TPH24TPH24

TPH25TPH25

TPH26TPH26

TPH27TPH27

TPH28TPH28

TPH29TPH29

TPH30TPH30

TPH31TPH31

*

*

+/-1%

+/-1%

TPH8TPH8

H_VCCST 13

TPH10TPH10

+VCORE

H_PWR_DEBUG 44

TPH14TPH14

TPH62TPH62

TPH63TPH63

VCOMP_OUT_CPU

VCORE_VCC_SEN 54

VCORE_VSS_SEN 54

C_DPNS# 24

C_DPNS 24

*

*

+/-1%

+/-1%

RH27 100 Ohm +/-1%

RH27 100 Ohm +/-1%

RH29 75 +/-1%

RH29 75 +/-1%

RH31 100 Ohm +/-1%

RH31 100 Ohm +/-1%

RH73 49.9

RH73 49.9

2

H_SM_VREF

CH81

CH81

22nF

22nF

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

RH115

RH115

*

*

24.9

24.9

+/-1%

+/-1%

TPH15TPH15

20120413: Delete RH57, CH39 and add

TPH39TPH39

TPH39, follow CRB1.0

H_SM_VREF 15,17

20120413: Add RH13,

follow CRB1.0

1

Check can ne removed ?

H_CPU_VCCIO_RIGHT

*

*

RH12

RH12

51 Ohm

51 Ohm

Dummy

Dummy

H_PWRGOOD

RH13

RH13

*

*

10K

10K

+/-5%

+/-5%

H_CPU_VCCIO_RIGHT

RH10 51 Ohm

RH10 51 Ohm

*

*

RH82 51 Ohm Dummy

RH82 51 Ohm Dummy

*

*

RH83 51 Ohm Dummy

RH83 51 Ohm Dummy

*

*

RH85 51 Ohm

RH85 51 Ohm

*

*

RH84 51 Ohm

RH84 51 Ohm

*

*

RH72 Close to XDP Conn

Need Close to CPU

+1P05V_PCH

RH18 1K

RH18 1K

*

*

RH72 51 Ohm

RH72 51 Ohm

*

*

RH11 1K Dummy

RH11 1K Dummy

*

*

20120326: RH72, RH9 pull-up to +1P05V_PCH

20120413: RH18 change to 1k and stuffed, follow CRB1.0

+3V_S5

RH81 220 +/-5%

RH81 220 +/-5%

*

*

RH21 1K+/-5% Dummy

RH21 1K+/-5% Dummy

RH22 1K+/-5% Dummy

RH22 1K+/-5% Dummy

RH23 1K+/-5% Dummy

RH23 1K+/-5% Dummy

RH24 1K+/-5% Dummy

RH24 1K+/-5% Dummy

RH25 1K+/-5% Dummy

RH25 1K+/-5% Dummy

RH26 1K+/-5% Dummy

RH26 1K+/-5% Dummy

RH28 1K+/-5% Dummy

RH28 1K+/-5% Dummy

RH30 1K+/-5% Dummy

RH30 1K+/-5% Dummy

RH32 1K+/-5% Dummy

RH32 1K+/-5% Dummy

RH33 1K+/-5% Dummy

RH33 1K+/-5% Dummy

RH34 1K+/-5% Dummy

RH34 1K+/-5% Dummy

RH37 1K+/-5% Dummy

RH37 1K+/-5% Dummy

RH38 1K+/-5% Dummy

RH38 1K+/-5% Dummy

RH39 1K+/-5% Dummy

RH39 1K+/-5% Dummy

RH41 1K+/-5% Dummy

RH41 1K+/-5% Dummy

RH42 1K+/-5% Dummy

RH42 1K+/-5% Dummy

RH44 1K+/-5% Dummy

RH44 1K+/-5% Dummy

RH46 1K+/-5% Dummy

RH46 1K+/-5% Dummy

RH56 1K+/-5% Dummy

RH56 1K+/-5% Dummy

RH60 1K+/-5% Dummy

RH60 1K+/-5% Dummy

Dummy

Dummy

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

+1P05V_PCH

RH19

RH19

*

*

150

150

+/ -1%

+/ -1%

H_PWR_DEBUG

RH20

RH20

*

*

10K

10K

+/-5%

+/-5%

Dummy

Dummy

H_PROCHOT#

H_TDI

H_TMS

H_TCK

H_TRST#

H_THERMTRIP#

H_TDO

H_PECI

FP_RST#

H_CFG10

H_CFG11

H_CFG12

H_CFG13

H_CFG14

H_CFG15

H_CFG17

H_CFG16

H_CFG19

H_CFG18

H_CFG0

H_CFG1

H_CFG2

H_CFG3

H_CFG4

H_CFG5

H_CFG6

H_CFG7

H_CFG8

H_CFG9

If RS71 pop, CPU RESET CIRCUIT need to Dummy

CheckwithIntelforthiscircuitnecessary??

A A

H_TAPPWRGOOD44

P_VR_READY23,44,51,54

5

+VCORE

RH40 10K

RH40 10K

RH43 10K

RH43 10K

RH64 10K

RH64 10K

+3V +3V

RH35

RH35

*

*

10K

10K

+/-5%

+/-5%

Dummy

*

*

*

*

*

*

Dummy

+/-5%Dummy

+/-5%Dummy

+/-5%Dummy

+/-5%Dummy

+/-5%Dummy

+/-5%Dummy

*

*

RH51

RH51

0

0

+/-5%

+/-5%

Dummy

Dummy

4

B

*

*

CH36

CH36

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

Dummy

Dummy

QH1

QH1

MMBT3904-7-F

MMBT3904-7-F

E C

Dummy

Dummy

*

*

RH36

RH36

10K

10K

+/-5%

+/-5%

Dummy

Dummy

B

H_PWR_DEBUG

QH2

QH2

MMBT3904-7-F

MMBT3904-7-F

E C

Dummy

Dummy

Title

Title

Title

CPU-3: VID/MISC

CPU-3: VID/MISC

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet

3

2

Date: Sheet

CPU-3: VID/MISC

Goodyear

Goodyear

Goodyear

1

A00

A00

A00

of

11 57星期三, 二月 20, 2013

of

11 57星期三, 二月 20, 2013

of

11 57星期三, 二月 20, 2013

5

X_1X16_RXP035

X_1X16_RXN035

X_1X16_RXP135

X_1X16_RXN135

D D

C C

VCOMP_OUT_CPU

X_1X16_RXP235

X_1X16_RXN235

X_1X16_RXP335

X_1X16_RXN335

X_1X16_RXP435

X_1X16_RXN435

X_1X16_RXP535

X_1X16_RXN535

X_1X16_RXP635

X_1X16_RXN635

X_1X16_RXP735

X_1X16_RXN735

X_1X16_RXP835

X_1X16_RXN835

X_1X16_RXP935

X_1X16_RXN935

X_1X16_RXP1035

X_1X16_RXN1035

X_1X16_RXP1135

X_1X16_RXN1135

X_1X16_RXP1235

X_1X16_RXN1235

X_1X16_RXP1335

X_1X16_RXN1335

X_1X16_RXP1435

X_1X16_RXN1435

X_1X16_RXP1535

X_1X16_RXN1535

H_DMI_RXP021

H_DMI_RXN021

H_DMI_RXP121

H_DMI_RXN121

H_DMI_RXP221

H_DMI_RXN221

H_DMI_RXP321

H_DMI_RXN321

TPH32TPH32

TPH33TPH33

TPH34TPH34

TPH35TPH35

RH2 24.9

RH2 24.9

*

*

+/-1%

+/-1%

4

H_TP_RSVD_D1

H_TP_RSVD_C2

H_TP_RSVD_B3

H_TP_RSVD_A4

H_PEG_RCOMP

UH1C

UH1C

E15

PEG_RX[0]

F15

PEG_RX#[0]

D14

PEG_RX[1]

E14

PEG_RX#[1]

E13

PEG_RX[2]

F13

PEG_RX#[2]

D12

PEG_RX[3]

E12

PEG_RX#[3]

E11

PEG_RX[4]

F11

PEG_RX#[4]

F10

PEG_RX[5]

G10

PEG_RX#[5]

E9

PEG_RX[6]

F9

PEG_RX#[6]

F8

PEG_RX[7]

G8

PEG_RX#[7]

D3

PEG_RX[8]

D4

PEG_RX#[8]

E4

PEG_RX[9]

E5

PEG_RX#[9]

F5

PEG_RX[10]

F6

PEG_RX#[10]

G4

PEG_RX[11]

G5

PEG_RX#[11]

H5

PEG_RX[12]

H6

PEG_RX#[12]

J4

PEG_RX[13]

J5

PEG_RX#[13]

K5

PEG_RX[14]

K6

PEG_RX#[14]

L4

PEG_RX[15]

L5

PEG_RX#[15]

U3

DMI_RX[0]

T3

DMI_RX#[0]

U1

DMI_RX[1]

V1

DMI_RX#[1]

W2

DMI_RX[2]

V2

DMI_RX#[2]

Y3

DMI_RX[3]

W3

DMI_RX#[3]

D1

RSVD_TP_1

C2

RSVD_TP_2

B3

RSVD_TP_3

A4

RSVD_TP_4

P3

PEG_RCOMP

PE115027-4041-0DF

PE115027-4041-0DF

3 OF 10

3 OF 10

PEG_TX[0]

PEG_TX#[0]

PEG_TX[1]

PEG_TX#[1]

PEG_TX[2]

PEG_TX#[2]

PEG_TX[3]

PEG_TX#[3]

PEG_TX[4]

PEG_TX#[4]

PEG_TX[5]

PEG_TX#[5]

PEG_TX[6]

PEG_TX#[6]

PEG_TX[7]

PEG_TX#[7]

PEG_TX[8]

PEG_TX#[8]

PEG_TX[9]

PEG_TX#[9]

PEG_TX[10]

PEG_TX#[10]

PEG_TX[11]

PEG_TX#[11]

PEG_TX[12]

PEG_TX#[12]

PEG_TX[13]

PEG_TX#[13]

PEG_TX[14]

PEG_TX#[14]

PEG_TX[15]

PEG_TX#[15]

DMI_TX[0]

DMI_TX#[0]

DMI_TX[1]

DMI_TX#[1]

DMI_TX[2]

DMI_TX#[2]

DMI_TX[3]

DMI_TX#[3]

A12

B12

B11

C11

C10

D10

B9

C9

C8

D8

B7

C7

A6

B6

B5

C5

E1

E2

F2

F3

G1

G2

H2

H3

J1

J2

K2

K3

M2

M3

L1

L2

AA4

AA5

AB3

AB4

AC5

AC4

AC1

AC2

3

X_1X16_TXP0 35

X_1X16_TXN0 35

X_1X16_TXP1 35

X_1X16_TXN1 35

X_1X16_TXP2 35

X_1X16_TXN2 35

X_1X16_TXP3 35

X_1X16_TXN3 35

X_1X16_TXP4 35

X_1X16_TXN4 35

X_1X16_TXP5 35

X_1X16_TXN5 35

X_1X16_TXP6 35

X_1X16_TXN6 35

X_1X16_TXP7 35

X_1X16_TXN7 35

X_1X16_TXP8 35

X_1X16_TXN8 35

X_1X16_TXP9 35

X_1X16_TXN9 35

X_1X16_TXP10 35

X_1X16_TXN10 35

X_1X16_TXP11 35

X_1X16_TXN11 35

X_1X16_TXP12 35

X_1X16_TXN12 35

X_1X16_TXP13 35

X_1X16_TXN13 35

X_1X16_TXP14 35

X_1X16_TXN14 35

X_1X16_TXP15 35

X_1X16_TXN15 35

H_DMI_TXP0 21

H_DMI_TXN0 21

H_DMI_TXP1 21

H_DMI_TXN1 21

H_DMI_TXP2 21

H_DMI_TXN2 21

H_DMI_TXP3 21

H_DMI_TXN3 21

2

1

B B

UH1D

UH1D

S_FDI_CSYNC24

S_FDI_INT24

*

*

+/-1%

+/-1%

H_DP_COMP

H_TP_RSVD_K11

H_TP_RSVD_J12

4

RH3 24.9

VCOMP_OUT_CPU

C_OUT_DP#24

C_OUT_DP24

S_FDI_TX0_N24

S_FDI_TX0_P24

S_FDI_TX1_N24

A A

5

S_FDI_TX1_P24

RH3 24.9

TPH37TPH37

TPH38TPH38

D16

FDI_CSYNC

D18

FDI_INT

R4

DP_COMP

U5

SSC_DPLL_REF_CLK#

U6

SSC_DPLL_REF_CLK

E16

EDP_DISP_UTIL

K11

RSVD_TP_5

J12

RSVD_TP_6

B14

FDI0_TX0#[0]

A14

FDI0_TX0[0]

C13

FDI0_TX0#[1]

B13

FDI0_TX0[1]

PE115027-4041-0DF

PE115027-4041-0DF

4 OF 10

4 OF 10

DDIB_TXB[0]

DDIB_TXB#[0]

DDIB_TXB[1]

DDIB_TXB#[1]

DDIB_TXB[2]

DDIB_TXB#[2]

DDIB_TXB[3]

DDIB_TXB#[3]

DDIC_TXC[0]

DDIC_TXC#[0]

DDIC_TXC[1]

DDIC_TXC#[1]

DDIC_TXC[2]

DDIC_TXC#[2]

DDIC_TXC[3]

DDIC_TXC#[3]

DDID_TXD[0]

DDID_TXD#[0]

DDID_TXD[1]

DDID_TXD#[1]

DDID_TXD[2]

DDID_TXD#[2]

DDID_TXD[3]

DDID_TXD#[3]

E17

F17

F18

G18

G19

H19

F20

G20

D19

E19

C20

D20

D21

E21

C22

D22

B15

C15

A16

B16

B17

C17

A18

B18

3

V_DDSP_B_DP_0_DP 38

V_DDSP_B_DP_0_DN 38

V_DDSP_B_DP_1_DP 38

V_DDSP_B_DP_1_DN 38

V_DDSP_B_DP_2_DP 38

V_DDSP_B_DP_2_DN 38

V_DDSP_B_DP_3_DP 38

V_DDSP_B_DP_3_DN 38

V_DDSP_C_DP_0_DP 37

V_DDSP_C_DP_0_DN 37

V_DDSP_C_DP_1_DP 37

V_DDSP_C_DP_1_DN 37

V_DDSP_C_DP_2_DP 37

V_DDSP_C_DP_2_DN 37

V_DDSP_C_DP_3_DP 37

V_DDSP_C_DP_3_DN 37

Display Port

HDMI

2

Title

Title

Title

CPU-4: FDI/PCIe/DMI/DP

CPU-4: FDI/PCIe/DMI/DP

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet

Date: Sheet

CPU-4: FDI/PCIe/DMI/DP

Goodyear

Goodyear

Goodyear

12 57星期三, 二月 20, 2013

12 57星期三, 二月 20, 2013

12 57星期三, 二月 20, 2013

1

A00

A00

A00

of

of

of

5

4

3

2

1

CRB 1.0 update

C31

C33

L16

L15

J35

H33

H35

J21

J22

J23

J24

J25

J26

J27

J28

J29

J30

J32

J34

K19

K21

K23

K25

K27

K29

K31

M13

K33

K35

L19

L20

L21

L22

L23

L24

L25

L26

L27

L28

L29

L30

L32

L33

M17

M15

M19

M21

M23

M25

M27

M29

M33

AJ12

AJ13

AJ15

AJ17

AJ20

AJ21

AJ24

AJ25

AJ28

AJ29

AJ9

AT17

AT22

AU15

AU20

AU24

AV10

AV11

AV13

AV18

AV23

AV8

AW16

AY12

AY14

AY9

+VCORE

+1P5V_SM

RH89 0

RH89 0

*

RH66 0

RH66 0

CH82

CH82

0.1uF

0.1uF

*

*

10V, X5R, +/-10%

10V, X5R, +/-10%

*

*

*

Dummy

Dummy

RH88 0

RH88 0

*

*

CH83

CH83

*

*

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

+/-5%

+/-5%

RH87 0

RH87 0

*

*

RH65 0

RH65 0

*

*

Dummy

Dummy

+VCORE

H_VCCIO_OUT

H_VCCIO2PCH

+VCORE

UH1F

UH1F

P8

VCC_2

L40

VCCIO_OUT

AB8

VCCIO2PCH

L31

VCC_3

L18

VCC_4

L17

VCC_5

J33

VCC_6

A24

VCC_7

A25

VCC_8

A26

VCC_9

A27

VCC_10

A28

VCC_11

A29

VCC_12

A30

VCC_13

G33

VCC_14

B25

VCC_15

B27

VCC_16

B29

VCC_17

B31

VCC_18

J31

VCC_19

B33

VCC_20

G31

VCC_21

B35

VCC_22

C24

VCC_23

C25

VCC_24

C26

VCC_25

C27

VCC_26

C28

VCC_27

C29

VCC_28

C30

VCC_29

C32

VCC_30

C34

VCC_31

C35

VCC_32

D25

VCC_33

D27

VCC_34

D29

VCC_35

D31

VCC_36

E33

VCC_37

D33

VCC_38

E31

VCC_39

D35

VCC_40

E24

VCC_41

E25

VCC_42

E26

VCC_43

E27

VCC_44

E28

VCC_45

E29

VCC_46

E30

VCC_47

E32

VCC_48

E34

VCC_49

F23

VCC_50

F25

VCC_51

F27

VCC_52

F29

VCC_53

F31

VCC_54

E35

VCC_55

F33

VCC_56

F35

VCC_57

G22

VCC_58

G23

VCC_59

G24

VCC_60

G25

VCC_61

G26

VCC_62

G27

VCC_63

G28

VCC_64

G29

VCC_65

G30

VCC_66

G32

VCC_67

G34

VCC_68

G35

VCC_69

H23

VCC_70

H25

VCC_71

H27

VCC_72

H29

VCC_73

H31

VCC_74

L34

VCC_75

PE115027-4041-0DF

PE115027-4041-0DF

6 OF 10

6 OF 10

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

VCC_81

VCC_82

VCC_83

VCC_84

VCC_85

VCC_86

VCC_87

VCC_88

VCC_89

VCC_90

VCC_91

VCC_92

VCC_93

VCC_94

VCC_95

VCC_96

VCC_97

VCC_98

VCC_99

VCC_100

VCC_101

VCC_102

VCC_103

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

VCC_110

VCC_111

VCC_112

VCC_113

VCC_114

VCC_115

VCC_116

VCC_117

VCC_118

VCC_119

VCC_120

VCC_121

VCC_122

VCC_123

VCC_124

VCC_125

VCC_126

VCC_127

VDDQ_1

VDDQ_2

VDDQ_3

VDDQ_4

VDDQ_5

VDDQ_6

VDDQ_7

VDDQ_8

VDDQ_9

VDDQ_10

VDDQ_11

VDDQ_12

VDDQ_13

VDDQ_14

VDDQ_15

VDDQ_16

VDDQ_17

VDDQ_18

VDDQ_19

VDDQ_20

VDDQ_21

VDDQ_22

VDDQ_23

VDDQ_24

VDDQ_25

VDDQ_26

+1P05V_PCH

D D

H_CPU_VCCIO_RIGHT

+VCCIO2PCH

+1P05V_PCH

H_VCCST11

CRB 1.0 update

20120413: Add CH82, CH83 ; RH88 change connect to RH65.1 and RH66.2 ; add net H_VCCIO2PCH ; RH65

and RH66 change to 0402 size, follow CRB1.0

20120413: Add RH87, RH89 ; Net H_VCCIO_OUT, follow CRB1.0

C C

B B

A A

Title

Title

Title

CPU-5: Vcore

CPU-5: Vcore

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

CPU-5: Vcore

Goodyear

Goodyear

Goodyear

A00

A00

A00

of

13 57星期三, 二月 20, 2013

of

13 57星期三, 二月 20, 2013

of

13 57星期三, 二月 20, 2013

1

5

UH1H

UH1G

UH1G

A13

VSS_7

A15

VSS_8

A17

VSS_9

A23

VSS_10

A11

VSS_11

AA3

VSS_12

AA33

VSS_13

AA35

VSS_14

AA38

VSS_15

AA6

VSS_16

AA7

VSS_17

D D

C C

B B

AA8

VSS_18

A5

VSS_19

AB34

VSS_20

AB37

VSS_21

AB5

VSS_22

AB7

VSS_23

AC3

VSS_24

AC33

VSS_25

AC34

VSS_26

AC35

VSS_27

AC36

VSS_28

AC37

VSS_29

AC38

VSS_30

AC39

VSS_31

AC40

VSS_32

AC6

VSS_33

AC7

VSS_34

A7

VSS_35

AD1

VSS_36

AD2

VSS_37

AD3

VSS_38

AD33

VSS_39

AD36

VSS_40

AD4

VSS_41

AD5

VSS_42

AD6

VSS_43

AD7

VSS_44

AD8

VSS_45

AE33

VSS_46

AE36

VSS_47

AE37

VSS_48

AE40

VSS_49

AE5

VSS_50

AE8

VSS_51

AF1

VSS_52

AF33

VSS_53

AF36

VSS_54

AF4

VSS_55

AF5

VSS_56

AF8

VSS_57

AG33

VSS_58

AG36

VSS_59

AG37

VSS_60

AG38

VSS_61

AG39

VSS_62

AG40

VSS_63

AG5

VSS_64

AG8

VSS_65

AH1

VSS_66

AH2

VSS_67

AH3

VSS_68

AH33

VSS_69

AH36

VSS_70

AH4

VSS_71

AH5

VSS_72

AH8

VSS_73

AJ11

VSS_74

AJ14

VSS_75

AJ16

VSS_76

AJ18

VSS_77

AJ19

VSS_78

AJ22

VSS_79

AJ23

VSS_80

AJ26

VSS_81

AJ27

VSS_82

AJ30

VSS_83

AJ31

VSS_84

AJ32

VSS_85

AJ33

VSS_86

PE115027-4041-0DF

PE115027-4041-0DF

7 OF 10

7 OF 10

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

AJ34

AJ35

AJ36

AJ37

AJ40

AJ5

AJ8

AK1

AK10

AK11

AK12

AK13

AK14

AK18

AK19

AK24

AK25

AK26

AK27

AK28

AK29

AK30

AK36

AK4

AK5

AK6

AK7

AK8

AK9

AL11

AL14

AL17

AL21

AL22

AL24

AL27

AL30

AL36

AL37

AL38

AL39

AL40

AL5

AM1

AM11

AM14

AM15

AM19

AM2

AM24

AM27

AM3

AM30

AM31

AM32

AM33

AM34

AM35

AM36

AM4

AM5

AN10

AN11

AN14

AN16

AN18

AN19

AN22

AN23

AN24

AN27

AN30

AN36

AN37

AN40

AN5

AN6

AN7

AN8

AN9

AP1

UH1H

AP11

VSS_168

AP14

VSS_169

AP15

VSS_170

AP24

VSS_171

AP27

VSS_172

AP30

VSS_173

AP36

VSS_174

AP4

VSS_175

AP5

VSS_176

AR11

VSS_177

AR14

VSS_178

AR16

VSS_179

AR17

VSS_180

AR18

VSS_181

AR19

VSS_182

AR20

VSS_183

AR21

VSS_184

AR22

VSS_185

AR23

VSS_186

AR24

VSS_187

AR27

VSS_188

AR30

VSS_189

AR31

VSS_190

AR32

VSS_191

AR33

VSS_192

AR34

VSS_193

AR35

VSS_194

AR36

VSS_195

AR37

VSS_196

AR38

VSS_197

AR39

VSS_198

AR40

VSS_199

AR5

VSS_200

AT1

VSS_201

AT10

VSS_202

AT11

VSS_203

AT12

VSS_204

AT13

VSS_205

AT14

VSS_206

AT15

VSS_207

AT16

VSS_208

AT2

VSS_209

AT24

VSS_210

AT25

VSS_211

AT26

VSS_212

AT27

VSS_213

AT28

VSS_214

AT29

VSS_215

AT3

VSS_216

AT30

VSS_217

AT32

VSS_218

AT34

VSS_219

AT36

VSS_220

AT38

VSS_221

AT39

VSS_222

AT4

VSS_223

AT5

VSS_224

AT6

VSS_225

AT7

VSS_226

AT8

VSS_227

AT9

VSS_228

AU2

VSS_229

AU25

VSS_230

AU3

VSS_231

AU30

VSS_232

AU34

VSS_233

AU38

VSS_234

AU5

VSS_235

AU7

VSS_236

AV21

VSS_237

AV28

VSS_238

AV3

VSS_239

AV30

VSS_240

AV34

VSS_241

AV38

VSS_242

AV7

VSS_243

AW26

VSS_244

AW3

VSS_245

AW30

VSS_246

PE115027-4041-0DF

PE115027-4041-0DF

4

8 OF 10

8 OF 10

VSS_247

VSS_248

VSS_249

VSS_250

VSS_251

VSS_252

VSS_253

VSS_254

VSS_255

VSS_256

VSS_257

VSS_258

VSS_259

VSS_260

VSS_261

VSS_262

VSS_263

VSS_264

VSS_265

VSS_266

VSS_267

VSS_268

VSS_269

VSS_270

VSS_271

VSS_272

VSS_273

VSS_274

VSS_275

VSS_276

VSS_277

VSS_278

VSS_279

VSS_280

VSS_281

VSS_282

VSS_283

VSS_284

VSS_285

VSS_286

VSS_287

VSS_288

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

VSS_297

VSS_298

VSS_299

VSS_300

VSS_301

VSS_302

VSS_303

VSS_304

VSS_305

VSS_306

VSS_307

VSS_308

VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_314

VSS_315

VSS_316

VSS_317

VSS_318

VSS_319

VSS_320

VSS_321

VSS_322

VSS_323

VSS_324

VSS_325

VSS_326

AW32

AW34

AW36

AW7

AY17

AY23

AY26

AY27

AY30

AY5

AY7

B24

B26

B28

B30

B34

B36

B4

B8

C4

C6

C12

C14

C16

C18

C19

C21

C23

C36

B10

B23

C3

D9

D11

D13

D15

D17

D2

D23

D24

D26

D28

D30

D34

D36

D37

D5

D6

D7

E7

E8

E10

E18

E3

E20

E22

E23

E36

E38

B32

E6

F1

F32

F12

F14

F16

F19

F21

F22

F24

F26

F28

F30

F34

F36

F4

D32

F7

G9

G11

UH1I

UH1I

G12

VSS_327

G13

VSS_328

G14

VSS_329

G16

VSS_330

H11

VSS_331

G17

VSS_332

G21

VSS_333

G3

VSS_334

H13

VSS_335

H22

VSS_336

H32

VSS_337

G36

VSS_338

G37

VSS_339

G6

VSS_340

G7

VSS_341

G15

VSS_342

H1

VSS_343

H10

VSS_344

H17

VSS_345

H18

VSS_346

H20

VSS_347

H21

VSS_348

H24

VSS_349

H26

VSS_350

H28

VSS_351

H30

VSS_352

H34

VSS_353

H36

VSS_354

H39

VSS_355

H4

VSS_356

H7

VSS_357

H8

VSS_358

H9

VSS_359

J19

VSS_360

J20

VSS_361

J3

VSS_362

J18

VSS_363

K10

VSS_364

K14

VSS_365

J36

VSS_366

J37

VSS_367

J6

VSS_368

K1

VSS_369

K18

VSS_370

K20

VSS_371

K22

VSS_372

K24

VSS_373

K26

VSS_374

K28

VSS_375

K30

VSS_376

K34

VSS_377

K36

VSS_378

K4

VSS_379

K40

VSS_380

K7

VSS_381

L7

VSS_382

L8

VSS_383

L9

VSS_384

L11

VSS_385

L3

VSS_386

L13

VSS_387

L14

VSS_388

L35

VSS_389

L38

VSS_390

L6

VSS_391

M1

VSS_392

K17

VSS_393

M12

VSS_394

M14

VSS_395

M18

VSS_396

M16

VSS_397

M20

VSS_398

M22

VSS_399

M24

VSS_400

M26

VSS_401

M28

VSS_402

M30

VSS_403

M32

VSS_404

M34

VSS_405

M37

VSS_406

PE115027-4041-0DF

PE115027-4041-0DF

9 OF 10

9 OF 10

3

VSS_407

VSS_408

VSS_409

VSS_410

VSS_411

VSS_412

VSS_413

VSS_414

VSS_415

VSS_416

VSS_417

VSS_418

VSS_419

VSS_420

VSS_421

VSS_422

VSS_423

VSS_424

VSS_425

VSS_426

VSS_427

VSS_428

VSS_429

VSS_430

VSS_431

VSS_432

VSS_433

VSS_434

VSS_435

VSS_436

VSS_437

VSS_438

VSS_439

VSS_440

VSS_441

VSS_442

VSS_443

VSS_444

VSS_445

VSS_446

VSS_447

VSS_448

VSS_449

VSS_450

VSS_451

VSS_452

VSS_453

VSS_454

VSS_455

VSS_456

VSS_457

VSS_458

VSS_459

VSS_460

VSS_461

VSS_462

VSS_463

VSS_464

VSS_465

VSS_466

VSS_NCTF_1

VSS_NCTF_2

VSS_NCTF_3

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_8

M4

M40

M5

M6

M7

K15

K16

N1

N2

N3

N7

N34

N4

N6

K32

P2

P34

P38

P5

P7

N8

R3

L36

R35

R40

R5

R6

R7

T1

T2

T33

M35

T39

T4

T5

T6

T7

R8

U2

U33

U34

U37

U4

U7

P35

V3

V33

V40

V6

V8

W1

W33

W35

W37

W4

W7

Y33

Y4

Y5

Y6

AU40

AV39

AW38

AY3

B38

B39

C40

D40

2

UH1J

UH1J

AY18

RSVD_29

AW24

RSVD_30

AW23

RSVD_31

AV29

RSVD_32

AV24

RSVD_33

AU39

RSVD_34

AU27

RSVD_35

AU1

RSVD_36

AT40

RSVD_37

TPH48TPH48

TPH49TPH49

TPH50TPH50

TPH51TPH51

TPH53TPH53

TPH54TPH54

dummy RO3, RH5 10K change to 11.8K

H_TP_RSVD_AK20

H_RSVD_Y7

H_TP_RSVD_T34

H_TP_RSVD_R34

H_TP_RSVD_J40

H_TP_RSVD_J17

H_TP_RSVD_J15

20120413: Change RH5 to 6.04k, RH6 to 2.67k,

follow CRB1.0

PWRGD_3V22,23,29,44

AK20

T34

R34

J40

J17

J15

H12

R195 0

R195 0

*

*

Dummy

Dummy

RSVD_38

Y7

RSVD_39

RSVD_40

RSVD_41

RSVD_42

RSVD_43

RSVD_44

RSVD_45

PE115027-4041-0DF

PE115027-4041-0DF

PWRGD_3V22,23,29,44

G

10 OF 10

10 OF 10

RH5 :6.04K

RH6 :2.67K Ohm

+5VSB

RH17

RH17

*

*

6.04K

6.04K

+/-1%

+/-1%

Dummy

Dummy

DS

QH10

QH10

2N7002

2N7002

Dummy

Dummy

RSVD_TP_12

RSVD_TP_13

RSVD_TP_14

RSVD_TP_15

RSVD_TP_16

RSVD_TP_17

RSVD_TP_11

G

K12

J13

P37

N38

R36

C39

U35

VSS_467

P40

VSS_468

R38

VSS_469

T37

VSS_470

V34

VSS_471

R39

VSS_472

T38

VSS_473

U36

VSS_474

P39

VSS_475

T36

VSS_476

R37

VSS_477

J14

VSS_478

N36

RH5

RH5

*

*

11.8K

11.8K

+/-1%

+/-1%

RH6

RH6

*

*

6.04K

6.04K

+/-1%

+/-1%

+1P05V_PCH +3V

RH7

RH7

*

*

10K

10K

Dummy

Dummy

RH15

RH15

*

*

0

0

+/-5%

+/-5%

Dummy

Dummy

DS

QH9

QH9

2N7002

2N7002

Dummy

Dummy

RH9

RH9

*

*

2.67K Ohm

2.67K Ohm

+/-1%

+/-1%

Dummy

Dummy

1

H_TP_RSVD_K12

H_TP_RSVD_J13

H_TP_RSVD_R37

H_TP_RSVD_N38

H_TP_RSVD_R36

H_TP_RSVD_C39

H_TP_RSVD_N36

This pin voltage is

1.05V for 2014 CPU

H_RSVD_Y7

RH16

RH16

*

*

6.04K

Dummy

6.04K

Dummy

+/-1%

+/-1%

H_RSVD_Y7

RH16 :6.04K

RH6 :2.67K Ohm

solution 1

R195, QH10, RH17, QH9, Rh16, RH6

TPH56TPH56

TPH57TPH57

TPH55TPH55

TPH59TPH59

TPH60TPH60

TPH58TPH58

TPH61TPH61

Dummy

Dummy

UH1_C

UH1_C

A A

LGA115X_CPU_COVER

LGA115X_CPU_COVER

MLH1MLH1

CPU_Plastic Cover (DIP)

5

4

3

MLH2MLH2

UH1_1

UH1_1

Retention Module

Retention Module

Same CPPB

MLH3MLH3

MLH4MLH4

UH1_B

UH1_B

LGA 115X ILM

LGA 115X ILM

2

Title

Title

Title

CPU-6: GND

CPU-6: GND

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet

Date: Sheet

CPU-6: GND

Goodyear

Goodyear

Goodyear

14 57星期三, 二月 20, 2013

14 57星期三, 二月 20, 2013

14 57星期三, 二月 20, 2013

1

A00

A00

A00

of

of

of

5

CHANNEL A BANK 1

SMB ADDRESS:000

4

3

2

1

D3_SA_ECC_CB79,16

D3_SA_ECC_CB69,16

D D

C C

B B

D3_SA_ECC_CB59,16

D3_SA_ECC_CB49,16

D3_SA_ECC_CB39,16

D3_SA_ECC_CB29,16

D3_SA_ECC_CB19,16

D3_SA_ECC_CB09,16

79

195

ODT177ODT0

RSVD

FREE1

FREE2

FREE349FREE4

48

198

187

+1P5V_SM_VTT

+1P5V_SM

CD1

CD1

*

*

1uF

1uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

+1P5V_SM_VTT

CD8

CD8

*

*

4.7uF

4.7uF

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

+1P5V_SM

*

*

CD11

CD11

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

Dummy

Dummy

D3_ODT_A1 9

D3_ODT_A0 9

68

167

53

NC/TEST4

NC/PAR_IN

NC/ERR_OUT

VSS

VSS

VTT

VTT

239

235

120

240

*

*

*

*

RD1 1K

RD1 1K

*

*

CB<0>39CB<1>40CB<2>45CB<3>46CB<4>

VSS

VSS

VSS

VSS

VSS

232

229

226

223

220

217

CD2

CD2

1uF

1uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

CD9

CD9

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

RD10 0

RD10 0

+/-1%

+/-1%

*

*

RD2

RD2

1K

1K

+/-1%

+/-1%

VSS

158

VSS

214

211

*

*

159

164

165

CB<5>

CB<6>

CB<7>

VSS

VSS

VSS

VSS

208

205

202

199

CD3

CD3

1uF

1uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

CD10

CD10

*

*

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

D3_DQS_A0

DQS07DQS0

VSS

VSS

VSS

166

163

D3_DQS_A#1

D3_DQS_A1

D3_DQS_A#0

15

6

DQS116DQS1

VSS

VSS

VSS

VSS

160

157

154

151

148

*

*

D3_DQS_A#3

D3_DQS_A3

D3_DQS_A2

D3_DQS_A#2

33

24

DQS334DQS3

DQS225DQS2

VSS

VSS

VSS

VSS

VSS

145

142

139

136

133

CD4

CD4

1uF

1uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

RD6 2.2Ohm

RD6 2.2Ohm

CD12

CD12

*

*

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

D3_DQS_A4

DQS485DQS4

VSS

VSS

VSS

130

127

D3_DQS_A#5

D3_DQS_A5

D3_DQS_A#4

93

84

DQS594DQS5

VSS

VSS

VSS

124

121

116

113

*

*

+/-1%

+/-1%

*

*

D3_DQS_A#7

D3_DQS_A7

D3_DQS_A6

D3_DQS_A#6

112

103

111

102

DQS7

DQS7

DQS6

DQS6

VSS

VSS

VSS

VSS

VSS

VSS98VSS95VSS92VSS89VSS86VSS83VSS80VSS47VSS44VSS41VSS38VSS35VSS32VSS29VSS26VSS23VSS20VSS17VSS14VSS11VSS8VSS5VSS2VDDQ

110

107

104

101

+3V

CD6

CD6

*

*

1uF

1uF

16V, X5R, +/-10%

16V, X5R, +/-10%

H_CPU_DIMM_VREF_A 10

D3_DQ_VREF_A

CD52

CD52

0.1uF

0.1uF

Dummy

Dummy

16V, X7R, +/-10%

16V, X7R, +/-10%

125

42

DQS843DQS8

DM0/DQS9

CD53

CD53

*

*

0.1uF

0.1uF

Dummy

Dummy

16V, X7R, +/-10%

16V, X7R, +/-10%

134

126

DQS9

DM1/DQS10

CD7

CD7

*

*

1uF

1uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

135

D3_DQS_A[7..0] 9,16

D3_DQS_A#[7..0] 9,16

D3_DQS_A8 9,16

D3_DQS_A#8 9,16

152

143

153

144

DQS12

DQS11

DQS10

DM3/DQS12

DM2/DQS11

D3_DQ_VREF_A 16

212

203

204

DQS13

DM4/DQS13

+1P5V_SM

221

222

213

DQS14

DM6/DQS15

DM5/DQS14

197

S_SMBCLK_MAIN16,17,18,29,44

S_SMBDATA_MAIN16,17,18,29,44

DQS15

VDDQ

194

D3_BAA[2..0]9,16

D3_MAA[15..0]9,16

230

231

NC/DQS16

DM7/DQS16

VDDQ

VDDQ

VDDQ

191

189

186

D3_CKE_A19

D3_CKE_A09

D3_SCS_A#19

D3_SCS_A#09

D3_MA_CLK#19

D3_MA_CLK19

D3_MA_CLK#09

D3_MA_CLK09

161

162

DQS17

DM8/DQS17

VDDQ

VDDQ

VDDQ

183

182

179

D3_DQ_A9

D3_DQ_A8

D3_DQ_A7

D3_DQ_A6

D3_DQ_A5

D3_DQ_A4

D3_DQ_A3

D3_DQ_A2

D3_DQ_A1

D3_DQ_A0

122

123

128

129

13

DQ03DQ14DQ29DQ310DQ4

DQ5

DQ6

DQ7

DQ812DQ9

DDRIII

DDRIII

VDDQ

VDDQ

VDDQ

VDD78VDD75VDD72VDD69VDD66VDD65VDD62VDD60VDD57VDD54VDD51VDDSPD

176

173

170

D3_CA_VREF_A

D3_DQ_VREF_A

D3_BAA2

D3_BAA1

D3_BAA0

D3_MAA0

D3_MAA1

D3_MAA2

D3_MAA3

D3_MAA4

D3_MAA5

D3_MAA6

D3_MAA7

D3_MAA8

D3_MAA9

D3_MAA10

D3_MAA11

D3_MAA12

D3_MAA13

D3_MAA14

D3_MAA15

D3_DQ_A13

D3_DQ_A12

D3_DQ_A11

D3_DQ_A10

131

132

DQ1018DQ1119DQ12

+3V

D3_DQ_A16

D3_DQ_A15

D3_DQ_A14

137

138

DQ13

DQ14

DQ15

DQ1621DQ1722DQ1827DQ1928DQ20

236

D3_DQ_A20

D3_DQ_A19

D3_DQ_A18

D3_DQ_A17

140

VREFDQ1SCL

VREFCA

67

118

238

D3_DQ_A23

D3_DQ_A22

D3_DQ_A21

141

146

147

DQ21

DQ22

DQ23

SA2

SDA

SA1

SA0

119

237

117

000

D3_DQ_A27

D3_DQ_A26

D3_DQ_A25

D3_DQ_A24

DQ2430DQ2531DQ2636DQ2737DQ28

BA2

52

190

D3_DQ_A31

D3_DQ_A30

D3_DQ_A29

D3_DQ_A28

149

150

155

156

DQ29

DQ30

BA071BA1

169

D3_DQ_A35

D3_DQ_A34

D3_DQ_A33

D3_DQ_A32

DQ31

DQ3281DQ3382DQ3487DQ3588DQ36

CKE050CKE1

S176CK1/NU64CK1/NU63CK0*

193

D3_DQ_A38

D3_DQ_A37

D3_DQ_A36

200

201

206

DQ37

S0

D3_DQ_A41

D3_DQ_A40

D3_DQ_A39

207

DQ38

DQ39

DQ4090DQ4191DQ4296DQ4397DQ44

185

184A0188A1181

D3_DQ_A44

D3_DQ_A43

D3_DQ_A42

209

CK0

D3_DQ_A48

D3_DQ_A47

D3_DQ_A46

D3_DQ_A45

210

215

216

DQ45

DQ46

DQ47

A261A3

A459A558A6

180

D3_DQ_A51

D3_DQ_A50

D3_DQ_A49

100

105

106

DQ4899DQ49

DQ50

DQ51

A756A9

A8

178

177

D3_DQ_A55

D3_DQ_A54

D3_DQ_A53

D3_DQ_A52

218

219

224

225

DQ52

DQ53

DQ54

A10/AP70A1155A12

175

174

D3_DQ_A58

D3_DQ_A57

D3_DQ_A56

108

109