Page 1

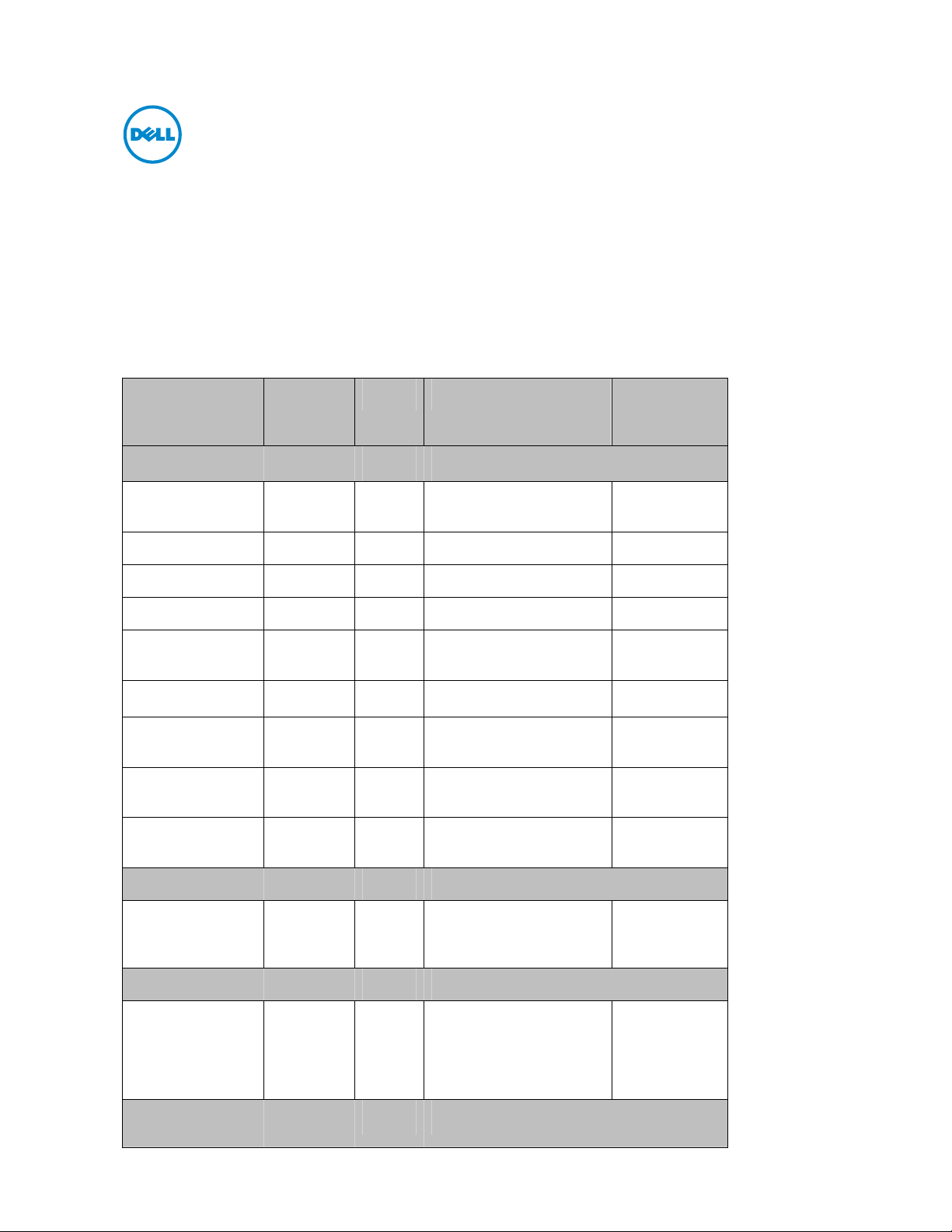

Statement of Volatility – Dell DX6112-SN

Dell DX6112-SN contains both volatile and non-volatile (NV) components. Volatile components lose their data

immediately upon removal of power from the component. Non-volatile components continue to retain their data

even after the pow er h as b ee n removed from the compo n en t. C omponents chosen as us er - de f i na bl e

configuration op t i ons (t h o s e no t so l de re d to t he m o t h er b o ar d) ar e n ot incl u d ed in t he St atement of Volatility.

Configuration option information (pertinent to options such as microprocessors, remote access controllers, and

storage controllers) is available by component separately. The following NV components are present in the

DX6112-SN system.

Item Non-

Volatile or

Volatile

Planer

PCH Internal CMOS

RAM

BIOS SPI Flash Non-Volatile 1 U_SPI_BIOS 8 MB

iDRAC SPI Flash Non-Volatile 1 U_IDRAC_SPI 4 MB

BMC EMMC Non-Volatile 1 U_EMMC 4 GB

CPU Vcore and VSA

Regulators

System CPLD RAM Volatile 1 U_CPLD 1 KB

System Memory Volatile Up to 12

Internal USB Key Non-Volatile Up to 1 N/A Varies (not

Trusted Platform

Module (TPM)

Non-Volatile 1 U_PCH 256 Bytes

Non-Volatile 2 U11, U12 4.25 KB

Non-Volatile 1 U_TPM 128 Bytes

Quantity Reference Designator Size

CPU<2:1>_CH<3:0>_D<2:0> Up to 32G B pe r

per CPU

DIMM

factory installed)

Power Supplies

PSU FW Non-Volatile 1 per

PSU

8x2.5" Backplane

SEP internal flash Non-Volatile 1 U_SEP Flash:32KB+4KB

2x2.5" Backplane

02 - 2013

Varies by part number Up to 2MB.

Varies by part

number

EEPROM: 1KB

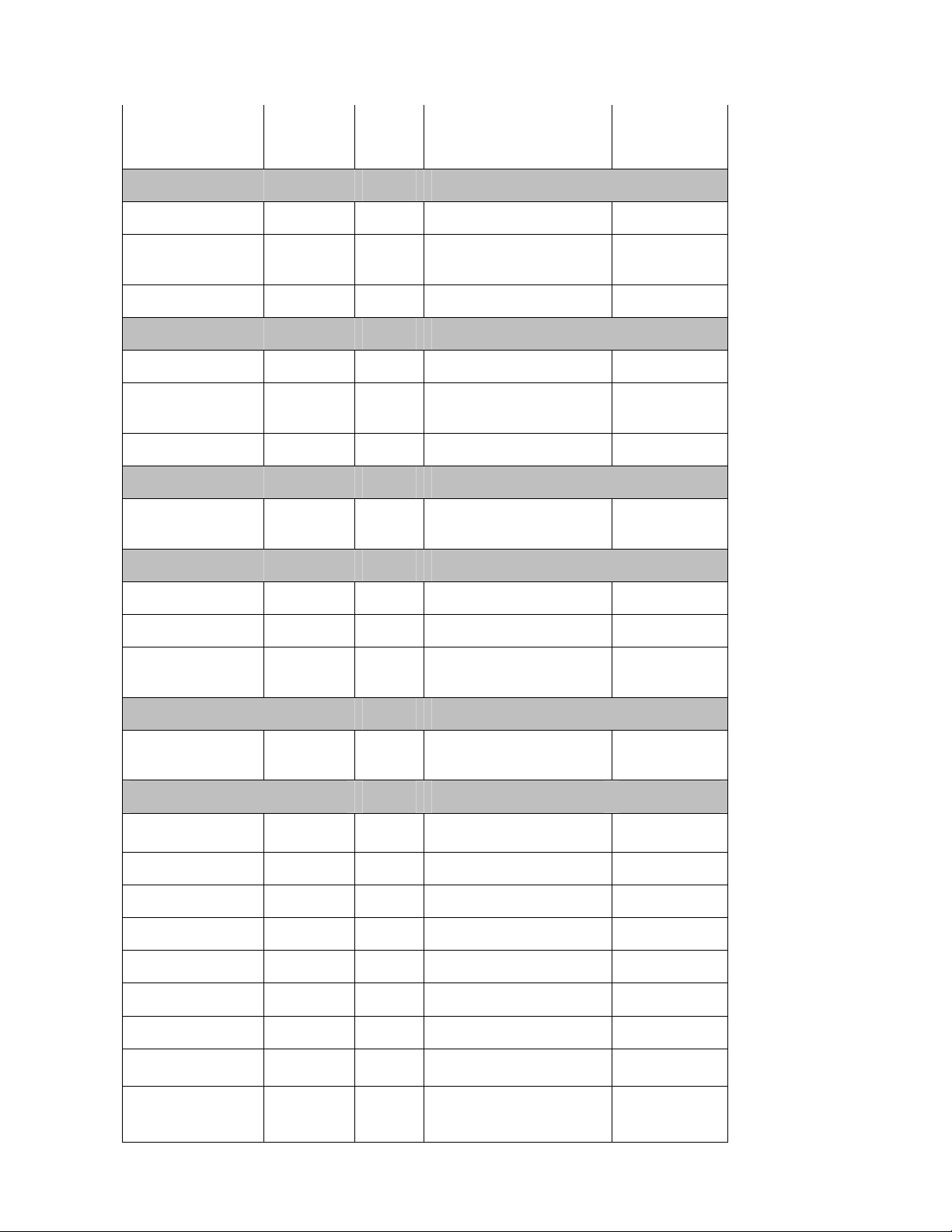

Page 2

SEP internal flash Non-Volatile 1 U_SEP Flash:32KB+4KB

EEPROM: 1KB

24x2.5" Backplane

Flash memory Non-Volatile 1 U33 32 Mb

Expander FRU

image

BP FRU image Non-Volatile 1 U_BP_EEPROM 256 Bytes

16x2.5" Backplane

Flash memory Non-Volatile 1 U33 32 Mb

Expander FRU

image

BP FRU image Non-Volatile 1 U_BP_EEPROM 256 Bytes

8x3.5" Backplane

SEP internal flash Non-Volatile 1 U_SEP Flash:32KB+4KB

12x3.5" Backplane

Flash memory Non-Volatile 1 U_FLASH 32 Mb

BP FRU image Non-Volatile 1 U_BP_FRU 256 Bytes

Expander FRU

image

Non-Volatile 1 U_EXP_EEPROM 512 Bytes

Non-Volatile 1 U_EXP_EEPROM 512 Bytes

EEPROM: 1KB

Non-Volatile 1 U_EXP_FRU 512 Bytes

PCIe SSD Backplane

SEP internal flash Non-Volatile 1 U_SEP1 Flash:32K B +4KB

EEPROM: 1KB

H710, H810, H710M PERCs

NVSRAM Non-volatile 1 U1033 128KB

FRU Non-volatile 1 U1019 256B

1-Wire EEPROM Non-volatile 1 U1004 128B

SPD Non-volatile 1 U22 256B

SBR Non-volatile 1 U1020 8KB

SPI Flash Non-volatile 1 U1055 2MB

Flash Non-volatile 1 U1031 16MB

ONFI Backup Flash Non-volatile 1 U4 4GB

SDRAM Volatile 5 U1043-U1047 512MB/1GB

Page 3

H310, H310M PERCs

NVSRAM Non-volatile 1 U500 128KB

FRU Non-volatile 1 U504 256B

1-Wire EEPROM Non-volatile 1 U15 128B

SBR Non-volatile 1 U503 8KB

Flash Non-volatile 1 U3 16MB

PCIe SSD Extension Card

Switch Configuration

EEPROM

IDSDM

SPI Flash Non-Volatile 1 U9 8MB

MCU Non-Volatile 1 U7 256KB

Item Type (e.g. Flash

Planer

PCH Internal CMOS RAM Battery-backed CMOS

BIOS SPI Flash SPI Flash No

iDRAC SPI Flash SPI Flash No

BMC EMMC eMMC NAND Flash No

Non-Volatile 1 U2 256B

Can user programs or operating

PROM, EEPROM)

RAM

system write data to it during normal

operation?

No

CPU Vcore and VSA

Regulators

System CPLD RAM RAM No

System Memory RAM Yes

Internal USB Key Flash Yes

Trusted Platform Module

(TPM)

Power Supplies

PSU FW Embedded

OTP(one time

programmable)

EEPROM Yes

microcontroller flash

No

No

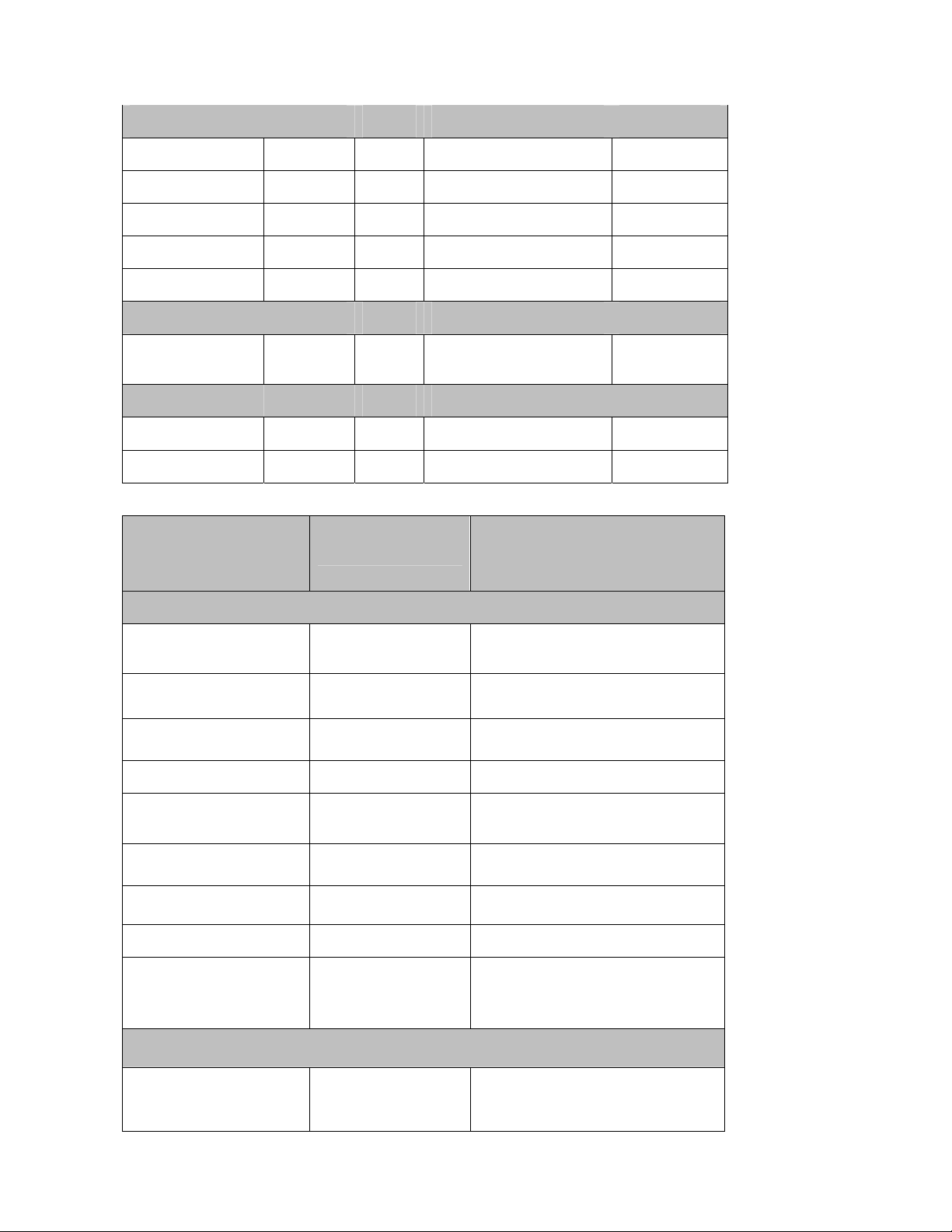

Page 4

8x2.5" Backplane

SEP internal flash Integrated

Flash+EEPROM

2x2.5" Backplane

SEP internal flash Integrated

Flash+EEPROM

24x2.5" Backplane

Flash memory Flash No

Expander FRU image I2C EEPROM No

BP FRU image I2C EEPROM No

16x2.5" Backplane

Flash memory Flash No

Expander FRU image I2C EEPROM No

BP FRU image I2C EEPROM No

8x3.5" Backplane

SEP internal flash Integrated

Flash+EEPROM

No

No

No

12x3.5" Backplane

Flash memory Flash No

BP FRU image I2C EEPROM No

Expander FRU image I2C EEPROM No

PCIe SSD Backplane

SEP internal flash Integrated

Flash+EEPROM

H710, H810, H710M PERCs

NVSRAM NVSRAM No

FRU FRU No

1-Wire EEPROM 1-Wire EEPROM No

SPD SPD No

SBR SBR No

SPI Flash SPI Flash No

Flash Flash No

No

ONFI Backup Flash ONFI Backup Flash No

SDRAM SDRAM No

Page 5

H310, H310M PERCs

NVSRAM NVSRAM No

FRU FRU No

1-Wire EEPROM 1-Wire EEPROM No

SBR SBR No

Flash Flash No

PCIe SSD Extension Card

Switch Configuration

SPI Flash EEPROM No (requires specialized SW)

EEPROM

IDSDM

SPI Flash SPI Flash No

MCU Embedded Flash FW can be updated via Linux and DOS

Item Purpose? (e.g. boot code) How is data input to this memory?

Planer

PCH Internal CMOS

RAM

BIOS SPI Flash Boot code, system configuration

Real-time clock and BIOS

configuration settings

BIOS

SPI interface via iDRAC

information, UEFI environment,

Flash descriptor, ME

iDRAC SPI Flash iDRAC Uboot (bootloader),

SPI interface via iDRAC

server management persistent

store (i.e. IDRAC MAC Address,

iDRAC boot variables), life cycle

log cache, virtual planar FRU and

EPPID, rac log, system event

log, JobStore, iDRAC Secure

boot code,

BMC EMMC Operati on a l iDRAC FW, Life cycle

NAND Flash interface via iDRAC

Controller (LC) USC partition, LC

service diags, LC OS drivers,

USC firmware

CPU Vcore and VSA

Regulators

Operational parameters Once values are loaded into register

space a command writes to NVMEM.

System CPLD RAM Not utilized Not utilized

System Memory System OS RAM System OS

Internal USB Key General purpose USB key drive USB interface via PCH. Accessed via

system OS

Trusted Platform Storage of encryption keys Using TPM Enabled operating systems

Page 6

Module (TPM)

Power Supplies

PSU FW Power Supply operation, power

management data and fault

behaviors

8x2.5" Backplane

SEP internal flash Firmware + FRU I2C interface via iDRAC

2x2.5" Backplane

SEP internal flash Firmware + FRU I2C interface via iDRAC

24x2.5" Backplane

Flash memory Firmware Common Flash memory Interface (CFI)

Expander FRU

image

BP FRU image FRU I2C interface via iDRAC

16x2.5" Backplane

Flash memory Firmware Common Flash memory Interface (CFI)

Expander FRU

image

FRU I2C interface via iDRAC

FRU I2C interface via iDRAC

Different vendors have differen t utilities

and tools to load the data to memory. It

can also be loaded by Dell Update

Package from LC or OS (Windows and

Linux)

BP FRU image FRU I2C interface via iDRAC

8x3.5" Backplane

SEP internal flash Firmware + FRU I2C interface via iDRAC

12x3.5" Backplane

Flash memory Firmware Common Flash memory Interface (CFI)

BP FRU image FRU I2C interface via iDRAC

Expander FRU

image

PCIe SSD Backplane

SEP internal flash Firmware + FRU I2C interface via iDRAC

H710, H810, H710M PERCs

NVSRAM Configuration data ROC writes configuration data to

FRU Card manufacturing information Programmed at ICT during production.

1-Wire EEPROM Holds default controller

FRU I2C interface via iDRAC

NVSRAM

ROC writes data to this memory

properties/settings

Page 7

SPD Memory configuration data Pre-programmed before assembly

SBR Bootloader Pre-programmed before assembly

SPI Flash FPGA configuration data Pre-programmed before assembly. Can

be updated using Dell/LSI tools

Flash Card firmware Pre-programmed before assembly. Can

be updated using Dell/LSI tools

ONFI Backup Flash Holds cache data during power

loss

SDRAM Cache for HDD I/O ROC writes to this memory - using it as

H310, H310M PERCs

NVSRAM Configuration data ROC writes configuration data to

FRU Card manufacturing information Programmed at ICT during production

1-Wire EEPROM Holds default controller

properties/settings

SBR Bootloader Pre-programmed before assembly

Flash Card firmware Pre-programmed before assembly. Can

PCIe SSD Extension Card

Switch Configuration

EEPROM

Configuration for PLX PCIe

switch, setting registers

FPGA backs up DDR data to this

device in case of a power failure

cache for data IO to HDDs

NVSRAM

ROC writes data to this memory

be updated using Dell/LSI tools

The EEPROM image is pre-loaded at

factory before assembly. Once

assembled on the card, dat a can be

entered via PLX Device Editor or PLX

EEP DOS based tool.

IDSDM

SPI Flash Exclusively used by the controller SPI interface via iDRAC

MCU Firmware USB interface via PCH

Page 8

Item How is this memory write

How is the memory cleared?

protected?

Planer

PCH Internal CMOS

RAM

N/A – BIOS only control 1) Set NVRAM_CLR jumper to clear

BIOS configuration settings at boot

and reboot system; 2) AC power off

system, rem o ve coin cell bat t e ry for

30 seconds, replace battery and

power back on; 3) restore default

configuration in F2 system setup

menu.

BIOS SPI Flash Software write protected Not possible with any utilities or

applications and system is not

functional if corrupted/removed.

iDRAC SPI Flash Embedded iDRAC subsystem

firmware actively controls sub area

based write protection as needed.

Not completely user clearable;

however, user data, lifecycle log

and archive, SEL, fw image

repository can be cleared via Delete

Configuration and Retire System,

accessible in Lifecycle Controller

interface

BMC EMMC Embedded FW write protected Not completely user clearable;

however, user data, lifecycle log

and archive, SEL, fw image

repository can be cleared via Delete

Configuration and Retire System,

accessible in Lifecycle Controller

interface

CPU Vcore and VSA

Regulators

There are passwords for different

sections of the register space

Not user clearable

System CPLD RAM Not access ible Not accessible

System Memory OS Control Reboot or power down system

Internal USB Key No write protect Can be cleared in system OS

Trusted Platform

SW write protected F2 Setup option

Module (TPM)

Power Supplies

PSU FW Protected by the embedded

Not clearable

microcontroller. Special keys are

used by special vendor provided

utilities to unlock the ROM with

various CRC checks during load.

8x2.5" Backplane

SEP internal flash Program write protect bit Not user clearable

Page 9

2x2.5" Backplane

SEP internal flash Program write protect bit Not user clearable

24x2.5" Backplane

Flash memory Hardware strapping Not user clearable

Expander FRU

Hardware strapping Not user clearable

image

BP FRU image Hardware strapping Not user clearable

16x2.5" Backplane

Flash memory Hardware strapping Not user clearable

Expander FRU

Hardware strapping Not user clearable

image

BP FRU image Hardware strapping Not user clearable

8x3.5" Backplane

SEP internal flash Program write protect bit Not user clearable

12x3.5" Backplane

Flash memory Hardware strapping Not user clearable

BP FRU image Hardware strapping Not user clearable

Expander FRU

Hardware strapping Not user clearable

image

PCIe SSD Backplane

SEP internal flash Program write protect bit Not user clearable

H710, H810, H710M PERCs

NVSRAM Not WP. Not visible to Host

Processor

Cannot be cleared with existing

tools available to the custom er

FRU Not WP Cannot be cleared with existing

tools available to the custom er

1-Wire EEPROM Not WP. Not visible to Host

Processor

SPD Not WP. Not vis i b le to Ho s t

Processor

SBR Not WP. Not vis i b le to Ho s t

Processor

SPI Flash Not WP. Not visible to Host

Processor

Flash Not WP. Not visible to Host

Processor

Cannot be cleared with existing

tools available to the custom er

Cannot be cleared with existing

tools available to the custom er

Cannot be cleared with existing

tools available to the custom er

Cannot be cleared with existing

tools available to the custom er

Cannot be cleared with existing

tools available to the custom er

Page 10

ONFI Backup Flash Not WP. Not visible to Host

Processor

Flash can be cleared by powering

up the card and allowing the

controller to flush the contents to

VDs. If the VDs are no longer

available, cache can be cleared by

going into controller bios and

selecting Discard Preserved Cache.

SDRAM Not WP. Not visible to Host

Processor

Cache can be cleared by powering

off the card

H310, H310M PERCs

NVSRAM Not WP. Not visible to Host

Processor

Cannot be cleared with existing

tools available to the customer

FRU Not WP Cannot be cleared with existing

tools available to the customer

1-Wire EEPROM Not WP. Not visible to Host

Processor

SBR Not WP. Not visible to Host

Processor

Flash Not WP. Not visible to Host

Processor

Cannot be cleared with existing

tools available to the customer

Cannot be cleared with existing

tools available to the customer

Cannot be cleared with existing

tools available to the customer

PCIe SSD Extension Card

Switch Configuration

EEPROM

Device can be write protected via

hardware pin. Alternatively, device

System is not functional as intended

if corrupted/removed.

contents can be write protected via

WPEN bit in status register.

IDSDM

SPI Flash Hardware stra ppi ng Not user clearable

MCU N/A Not user clearable

NOTE:

For any information that you may need, direct your questions to your Dell Marketing contact.

______________

© 2013 Dell Inc.

Trademarks used in this text: Dell™ and the DELL logo are trademarks of De ll Inc.

Loading...

Loading...