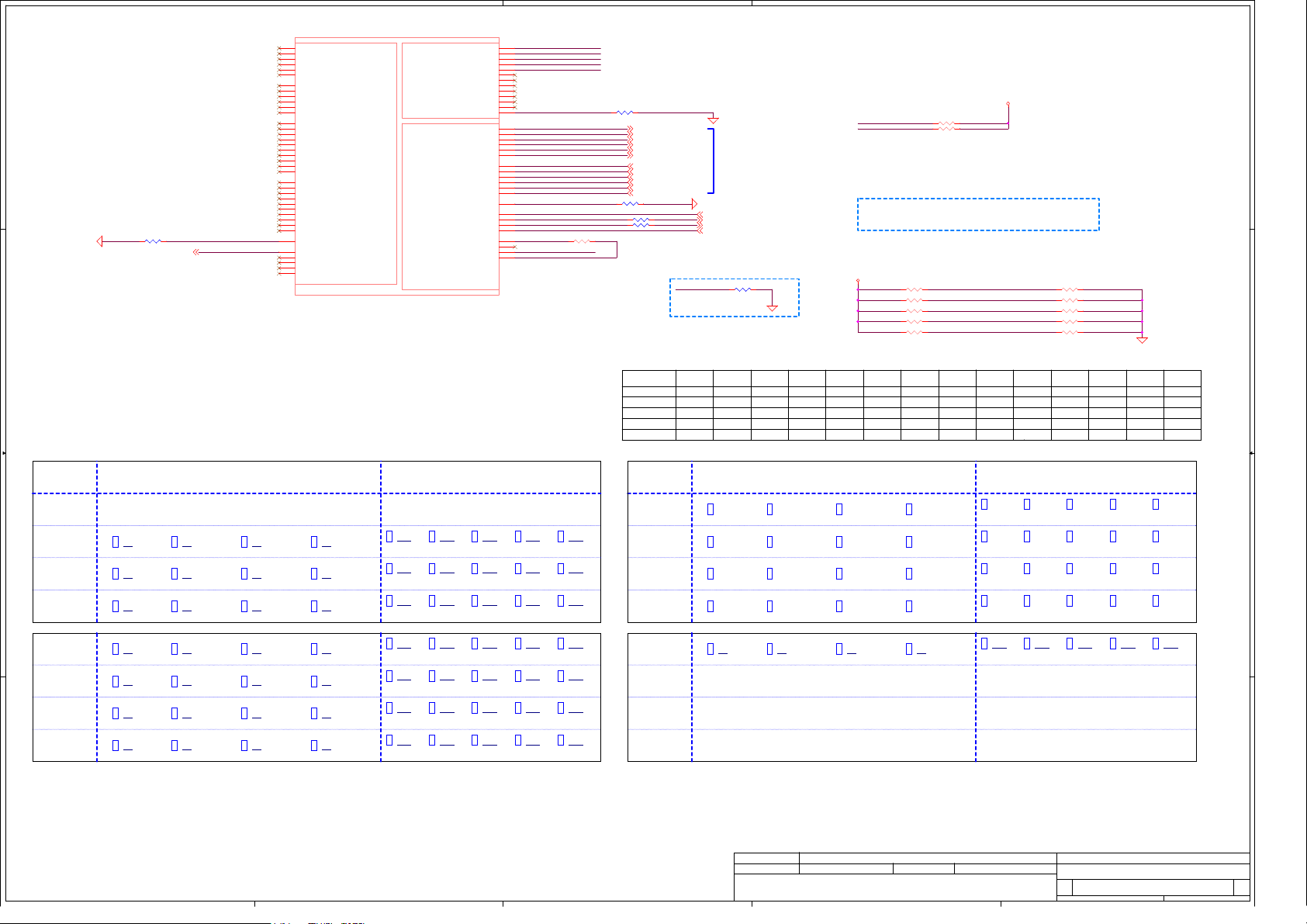

Dell Latitude XPS 13 9000 Schematics

A

B

C

D

E

MODEL NAME :

PCB NO :

LA-H811P

BOM P/N :

1 1

ZZZ LA-H811P

Modena

451AHT31L01 ~ L32

Dell/Compal Confidential

2 2

Schematic Document

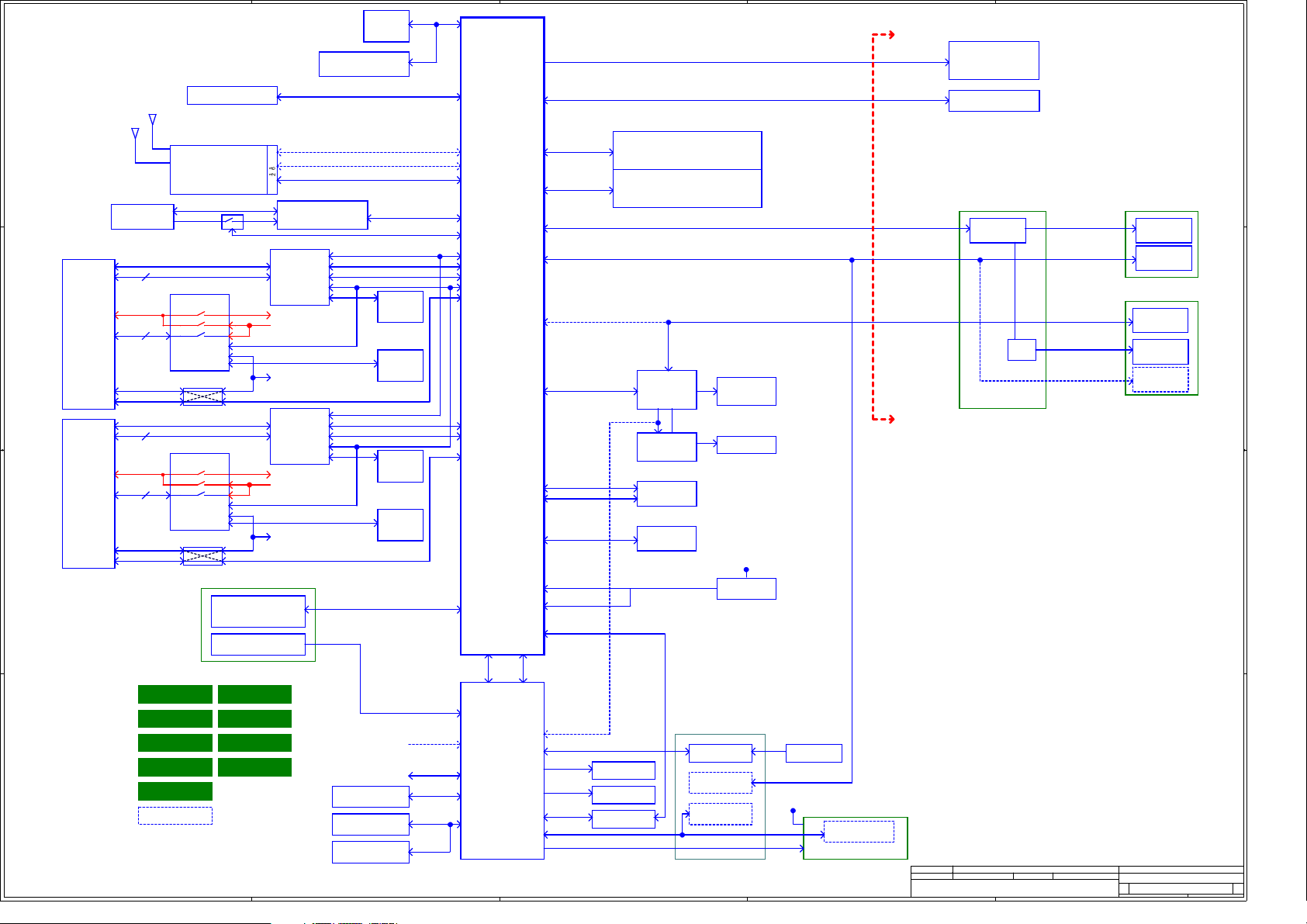

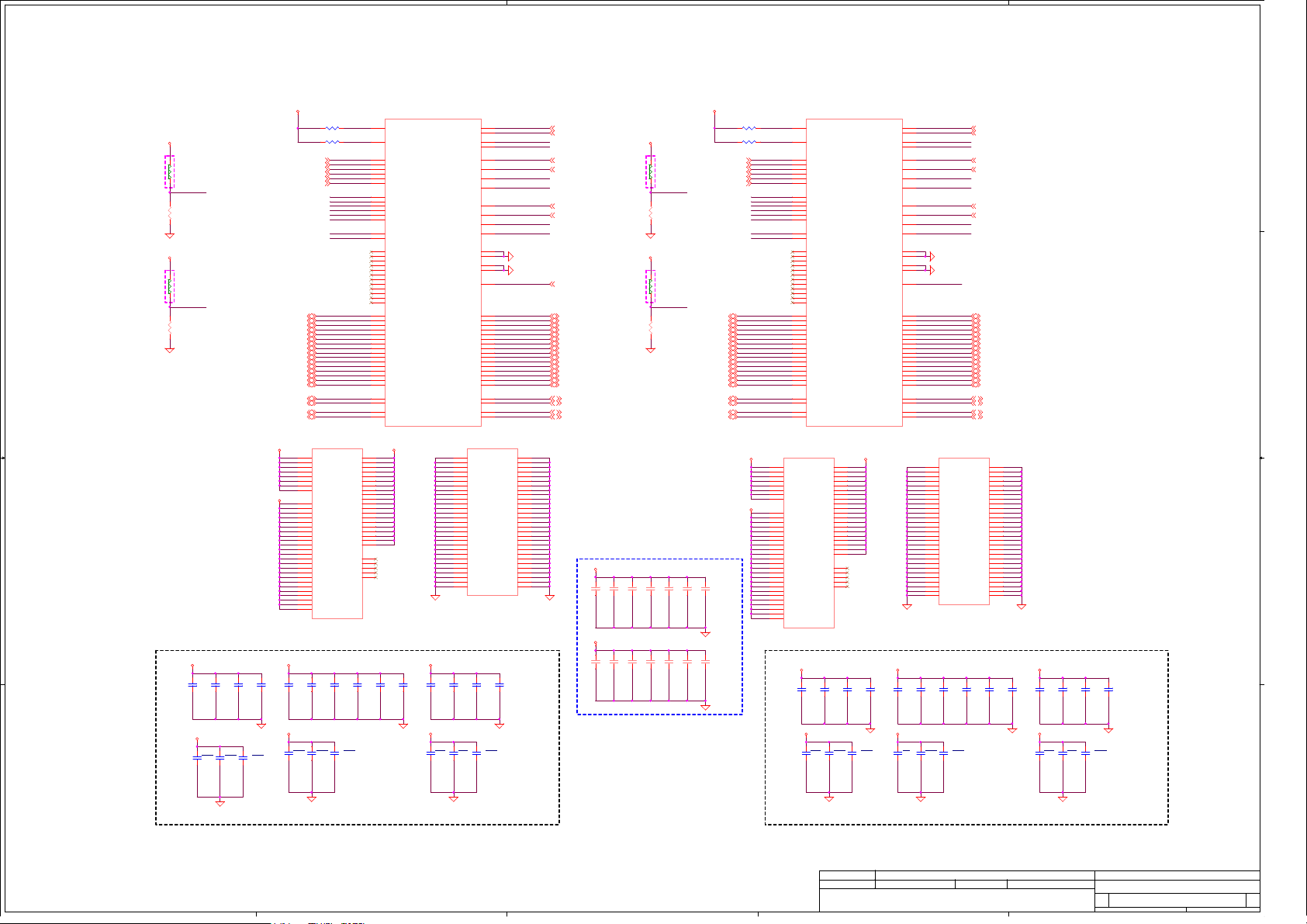

CPU Option

UC1

SRG0S@

SA0000CTD2L

ICE LAKE SRG0S I3 32EUs

UC1

SRGKL@

SA0000CTB2L

ICE LAKE SRGKL I5 32EUs

UC1

SRG0N@

SA0000CT62L

ICE LAKE SRG0N I7 64EUs

(MODENA ICE Lake U)

3 3

TBT Option

URT1

SA0000CAH3L

JHL8040R QURW

PD Option

UPD1

SA0000CM71L

SN1806026RSHR

WLAN Option

UWL1

4 4

PK29S009L0L

KILLER1650S.01

BB@

MP@

CNV@

URT2

BB@

SA0000CAH3L

JHL8040R QURW

UPD2

MP@

SA0000CM71L

SN1806026RSHR

UWL1

DAR@

PK29S00B60L

WBQ76QOUS01

TPM Option

U712

ST@

SA0000C5G10

ST33HTPH2032AHC1_VQFN32_5X5

2019-12-16

Rev: 1.0 (A00)

EC Option

UE1

5105@

SA00009GL30

MEC5105_WFBGA169_11X11

UE1

5106C@

SA0000C5D00

MEC5106K-D2-TN-TR

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2020/10/01 2018/10/01

2020/10/01 2018/10/01

2020/10/01 2018/10/01

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

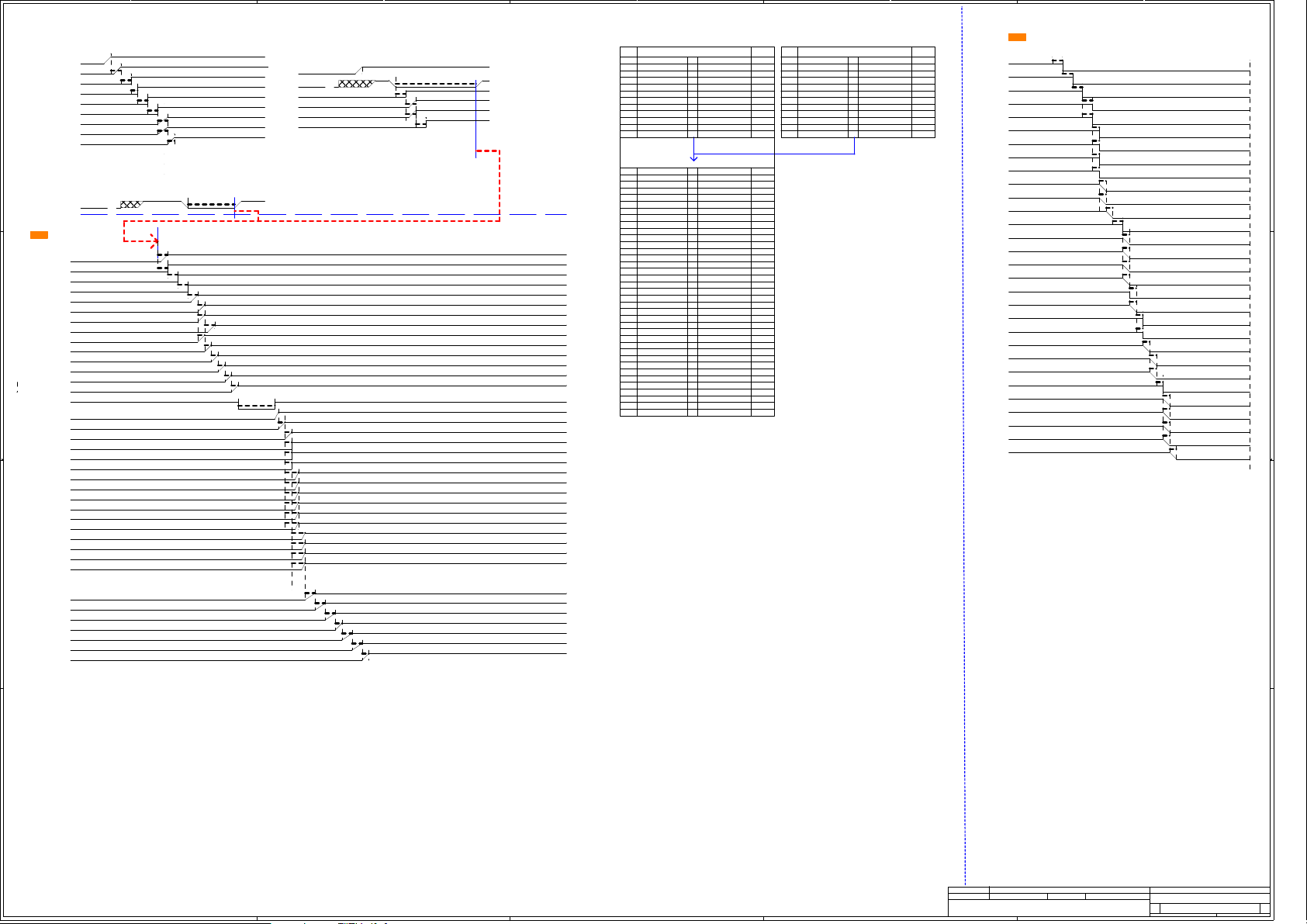

P001 - Cover

P001 - Cover

P001 - Cover

Document Number Re v

Document Number Re v

Document Number Re v

LA-H811P

LA-H811P

LA-H811P

E

1 100Tuesday, December 24, 2019

1 100Tuesday, December 24, 2019

1 100Tuesday, December 24, 2019

0.1 (X00)

0.1 (X00)

0.1 (X00)

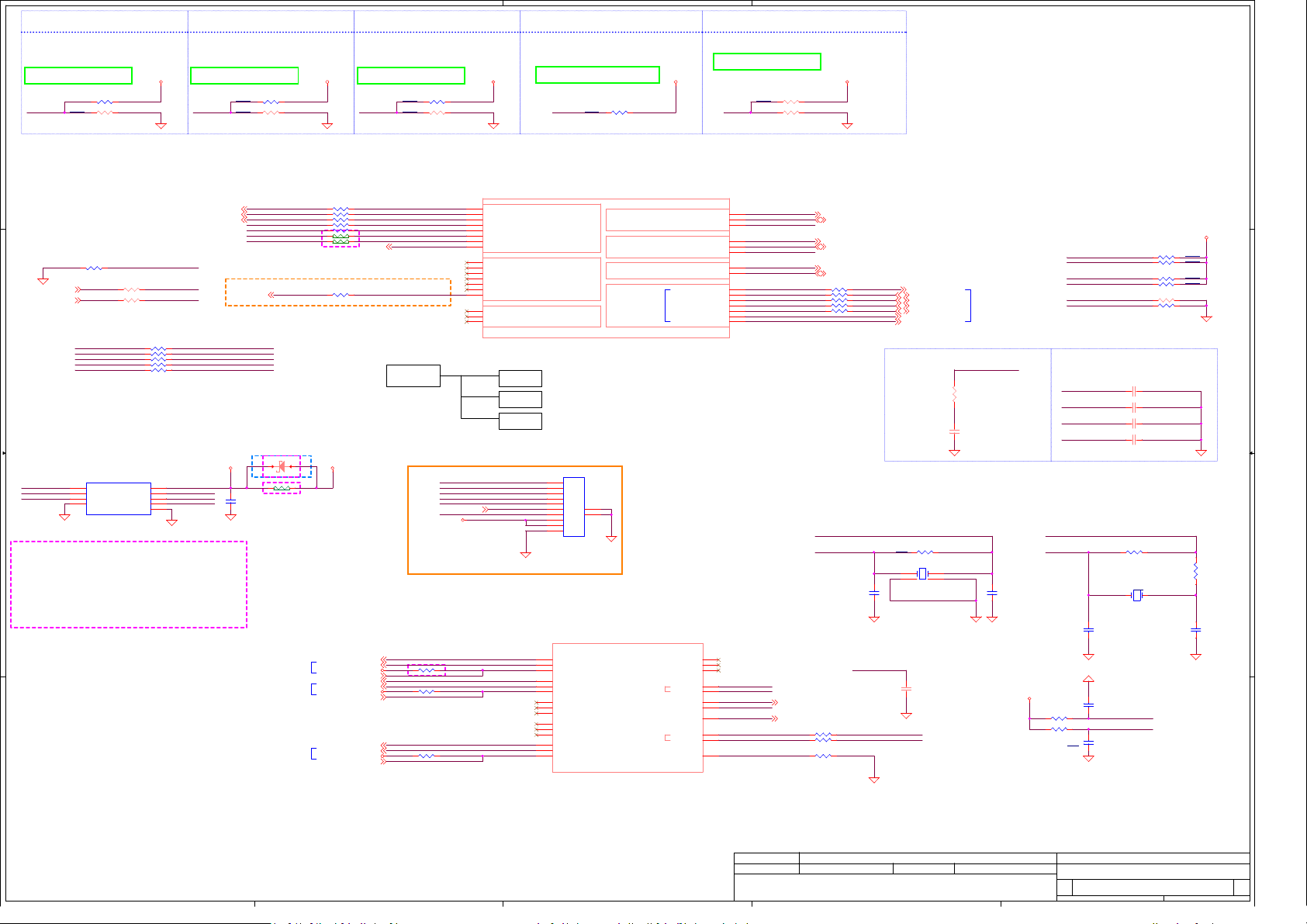

A

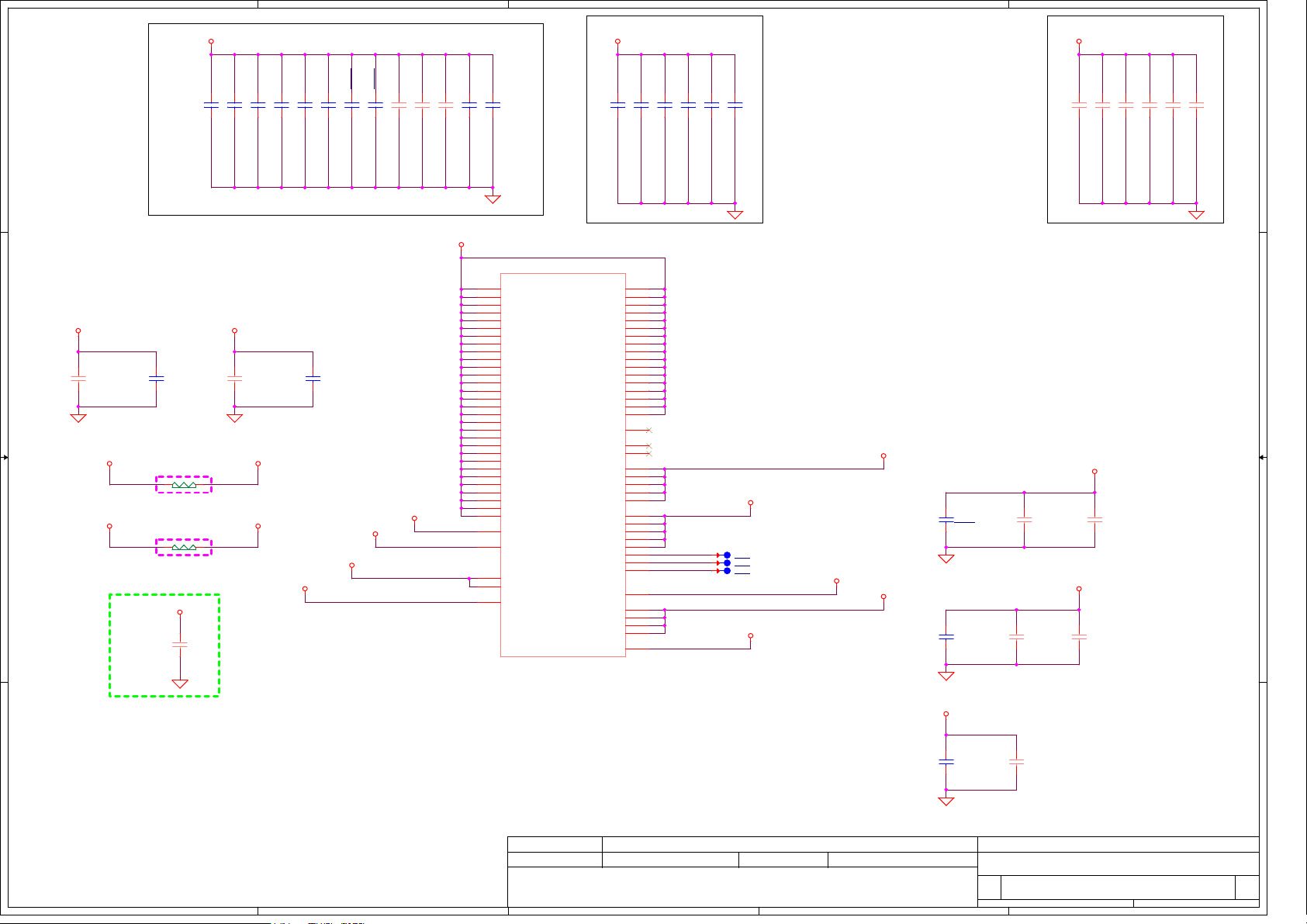

TPM2.0

ST/Nuvoton TPM chip

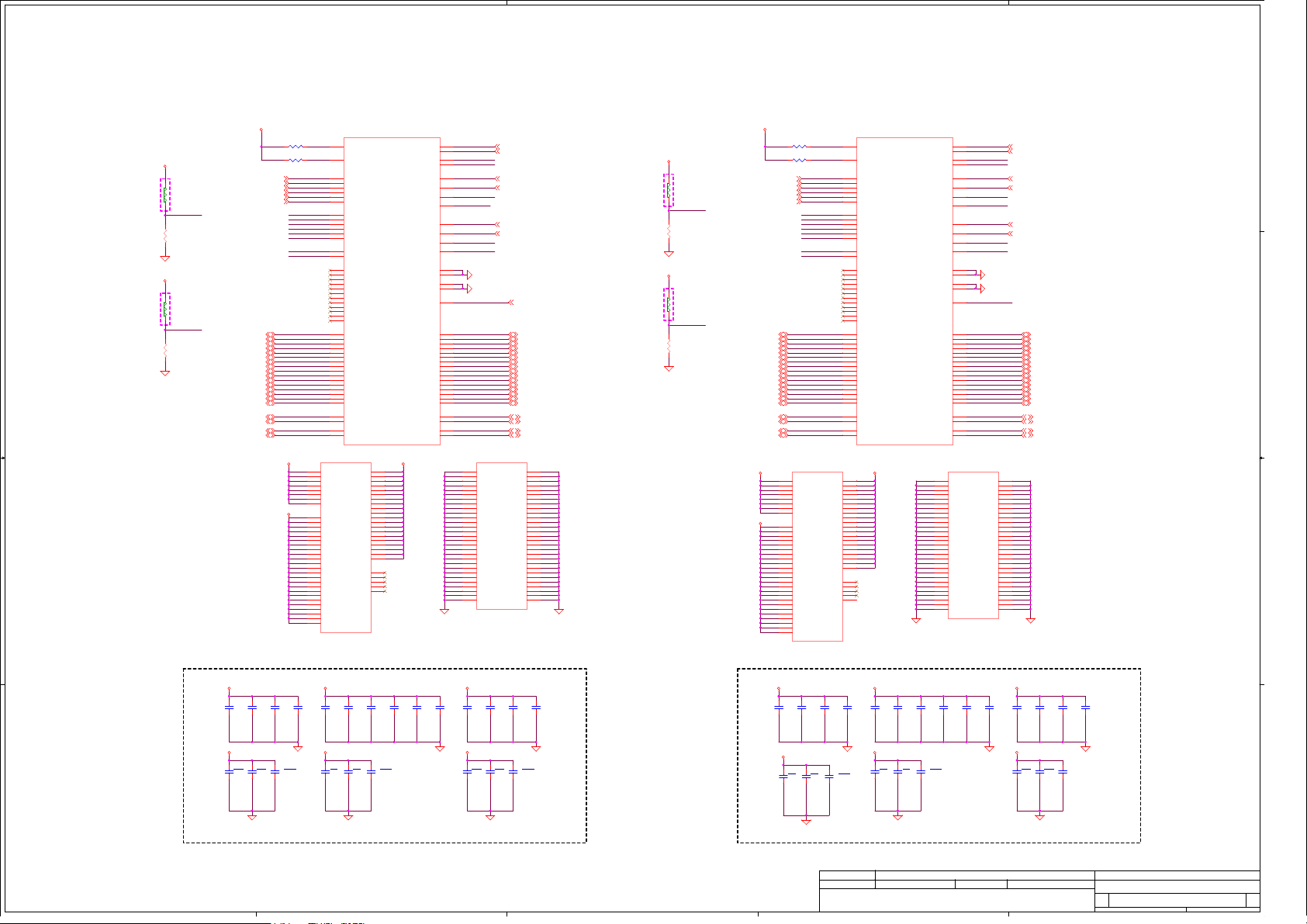

M.2 SSD-Key M

1 1

WLAN/BT 5.1 Solder down

Killer 1650-S 1216 SIP

uSD Connector

SD4.0/SDXC

SD_WP

p.67

1 6

1 2

p.52

Card Reader 4.0

RealTek

RTS5242 PCIe to SD

GPIO (BIOS Controlled )

TBT

2SBU

TPS65987-DD J

VBUS

PP_HV1

PP_HV2

CC

2CC VCONN

p.42

USB2/I2C MUXES_L

p.50

2SBU

TPS65987-DD J

VBUS

PP_HV1

PP_HV2

CC

VCONN2CC

p.44

USB2/I2C MUXES_R

p.50

Fingerprint module

I2C2

I2C1

SPI

I2C2

I2C1

SPI

Fingerprint Controller

GOODIX GF5288+HT32

p.43

VBUS

USB (Top)

USB (Bottom)

USB Type-C

TBT with PD

2 2

(Left)

TBT

p.45

VBUS

USB (Top)

USB (Bottom)

USB Type-C

TBT with PD

(Right)

3 3

EC UART Debug/80 port

SPI Programmer

PD Programmer/I2C

BIOS UART Debug

DCI Debug

4 4

RT Programmer

I2C

I2C

USB

I2C

I2C

USB

Power Button

MIPI60 Debug

APS Debug

JESPI Debug

Burnside Bridge

TBT Re-Timer

CHRG_IN

5VALW

to EC

Burnside Bridge

TBT Re-Timer

CHRG_IN

5VALWB

to EC

p.77

p.77

p.46,47

p.48,49

PWRBTN#

to PD & USB2/I2C MUXES

Coin Cell

A

B

PCH SPI

Flash ROM

32M

p.70p.70

SMBUS

TBT

LSx / AUX

I2C

RT SPI

Flash ROM

1M

PD SPI

Flash ROM

1M

SMBUS

TBT

LSx / AUX

I2C

RT SPI

Flash ROM

1M

PD SPI

Flash ROM

1M

to Battery Gauge FPC

VCCIN Controller

MP2940 AGRT

Charger

ISL9538B

Battery Connector

B

SPI

p.9

p.66

SPI#0

DDI#A

PCIe Gen3 x 4lanes PCIe#9,10, 11,12

PCIe Gen2 x 1lane

USB2.0

CNVi Gen2

PCIe Gen2 x 1lane

p.46

PCIe#3

USB2#3

CNVi Gen2

PCIe#16

SML#0

TBT#0

LSx / AUX

SML#1

USB2#8

USB2#9

ISH_I2C#1

IceLake-U

USB2.0

4+2

TBT#2

LSx / AUX

USB2#4

USB2#5

GPP_D13

GPP_D14

SMBUS

SMB#03 eSPI

GPIO

GPIO

EC

MEC5106D

SMB#04

SMB#05

SMB#10

p.58

USB2#1

USB3#2

SMB

GPIO 1 61

(VCI_IN2#)

eSPI

SMB#01

BCM#1

PWM#0

PWM#1

SMB#00

p.42

p.48

p.44

BATBTN#

SMBUS

SMBUS

p.91

SMBUS

p.83

p.82

Hinge Down

I2C#0

DMIC

HDA

I2C#1

eSPI

GPIO

PS/2

LEDs

C

eDP x4 lanes

I2C

LPDDR4 4GB X32x4 Memory Down

LPDDR4x 8/16/32 GB X32x4 Memory Down

Memory Bus

(LPDDR4/ x)

Dual Channel

3733MHz

Memory Bus

(LPDDR4/ x)

Dual Channel

3733MHz

LPDDR4/x - ChA

LPDDR4/x - ChB

USB2.0

ISH_I2C

DMIC

DMIC

HDA

USB2.0

USB3.1

SMB

Audio Codec

ALC3281 -CG

I2S

I2C

SPK Amp

TI TAS2770

USB DCI Debug

MIPI60 Debug

Universal

Headset Jack

p.56

p.57

p.79

p.79

NB_LID#

I2C

KB Transfer Board

BC Bus

PWM

PWM

PS/2

SMBUS

Fan 1

Fan 2

Touchpad

p.77

p.77

p.63

C

KB Controller

ECE111 7

Acceleromet er

LNG2D MTR

Acceleromet er

MCube MC3451

p.23,24

p.23,24

2xSpeaker

+3VLP

Hall Sensor

YB825 1

D

E

Hinge up

13.3" FHD+/UHD+ Panel

eDP v1.4b

Touch Screen Controller

Middle Board

RGBIR Camera

Contrlller

p.57

p.57

Keyboard

+3VLP

Battery Gauge

Acceleromet er

MCube MC3451

p.63

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D

2020/10/01 2018/10/01

2020/10/01 2018/10/01

2020/10/01 2018/10/01

p.38

p.38

enable

IR SW

p.39

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

CAM module

CSI

RGBIR Camera

ALS

DMIC FPC

DMIC

2xDMIC

IR LED

P-sensor

Title

Title

Title

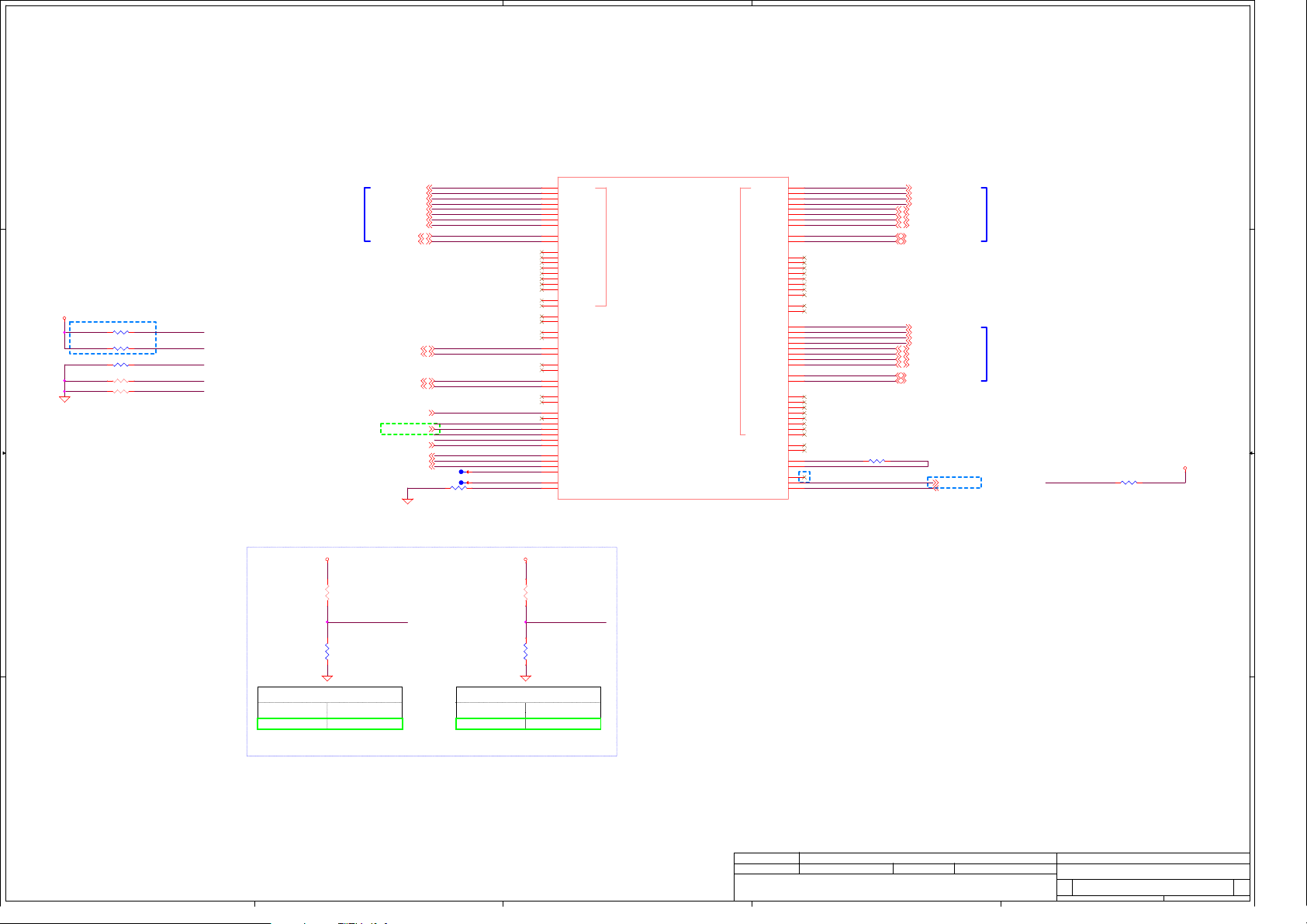

P002 - Bl ock Diagra m

P002 - Bl ock Diagra m

P002 - Bl ock Diagra m

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

LA-H811P

LA-H811P

LA-H811P

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

Compal El ectronics, I nc.

Compal El ectronics, I nc.

Compal El ectronics, I nc.

2 100Tuesday, December 24, 2019

2 100Tuesday, December 24, 2019

2 100Tuesday, December 24, 2019

0.1 (X00)

0.1 (X00)

0.1 (X00)

A

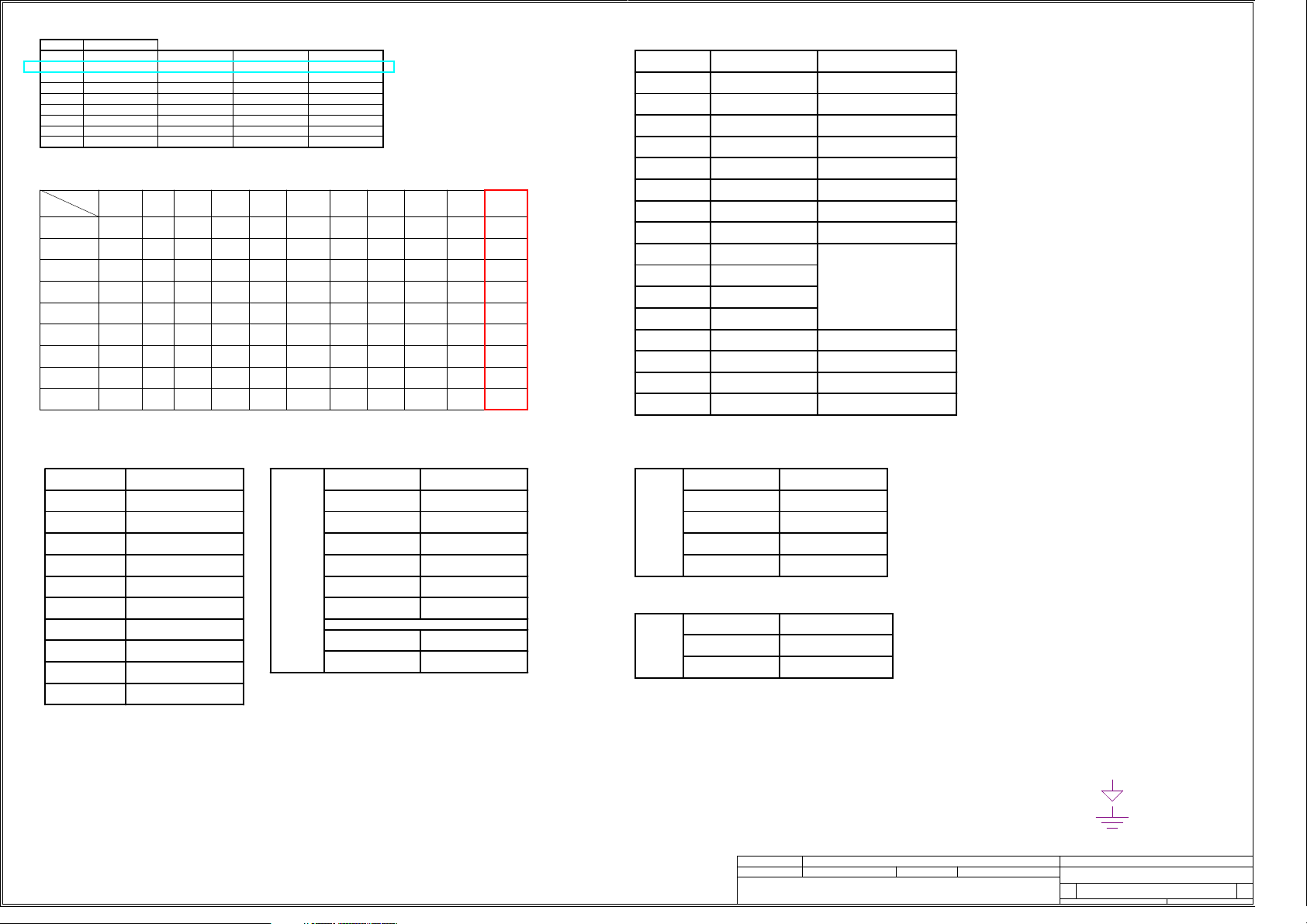

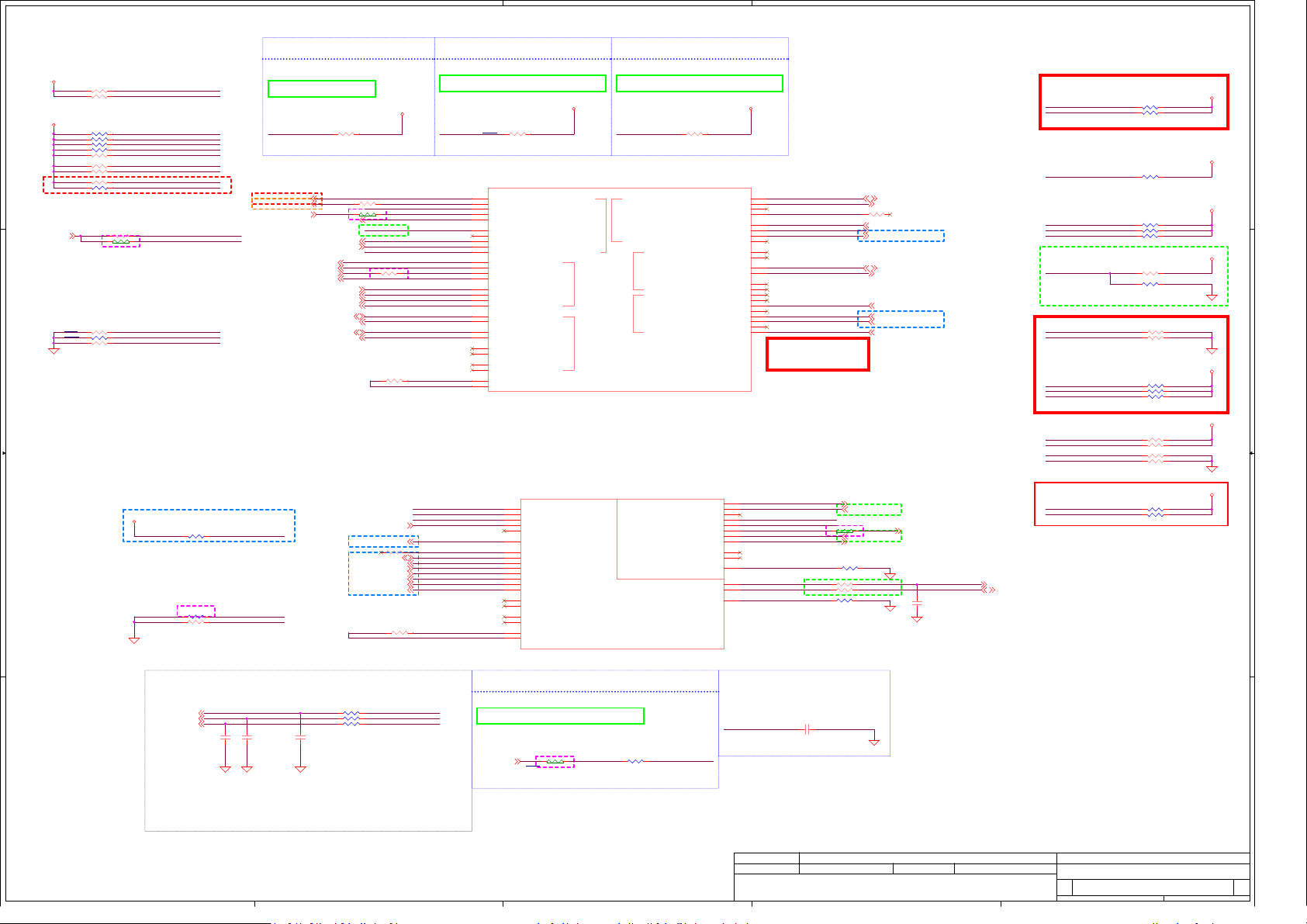

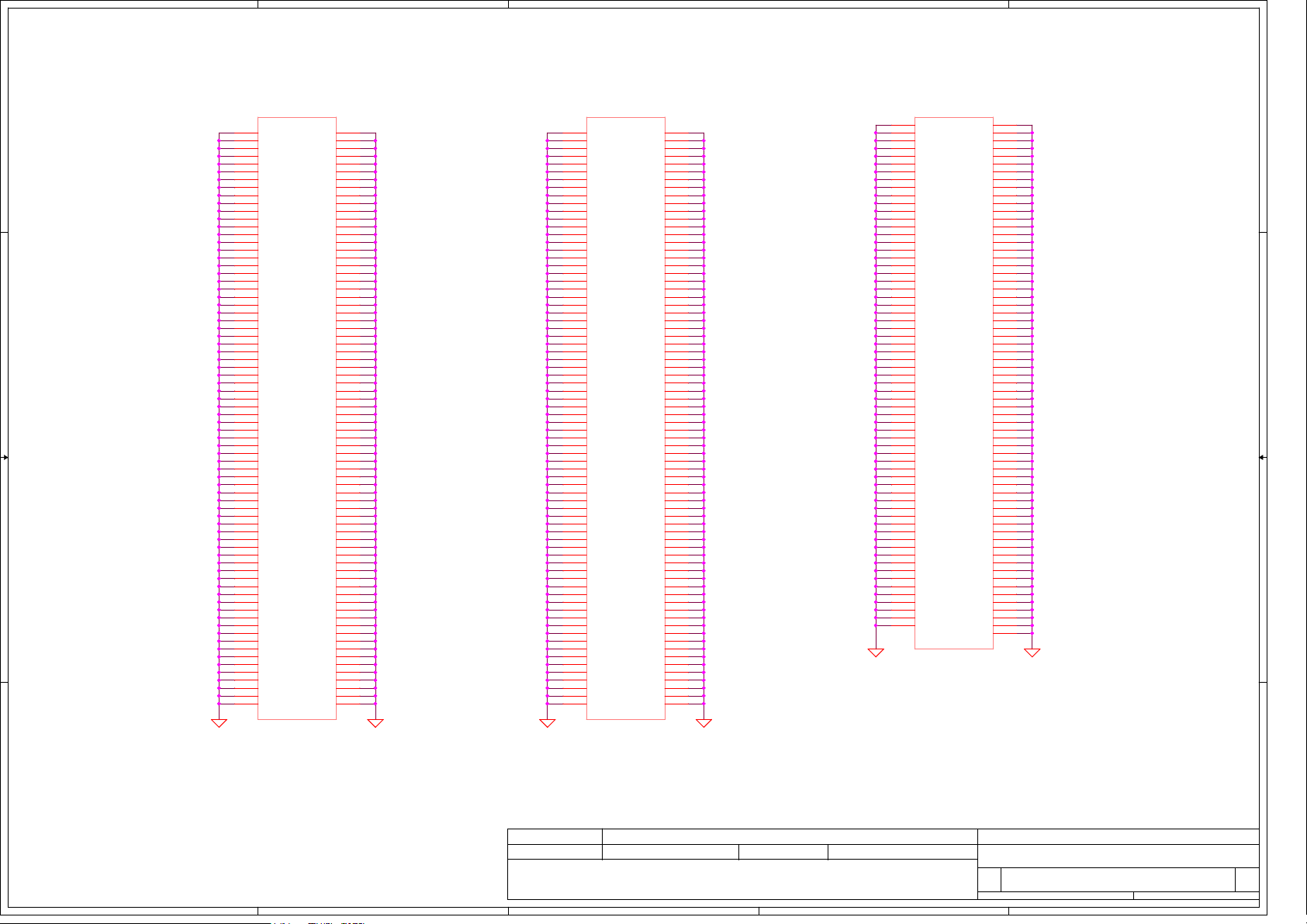

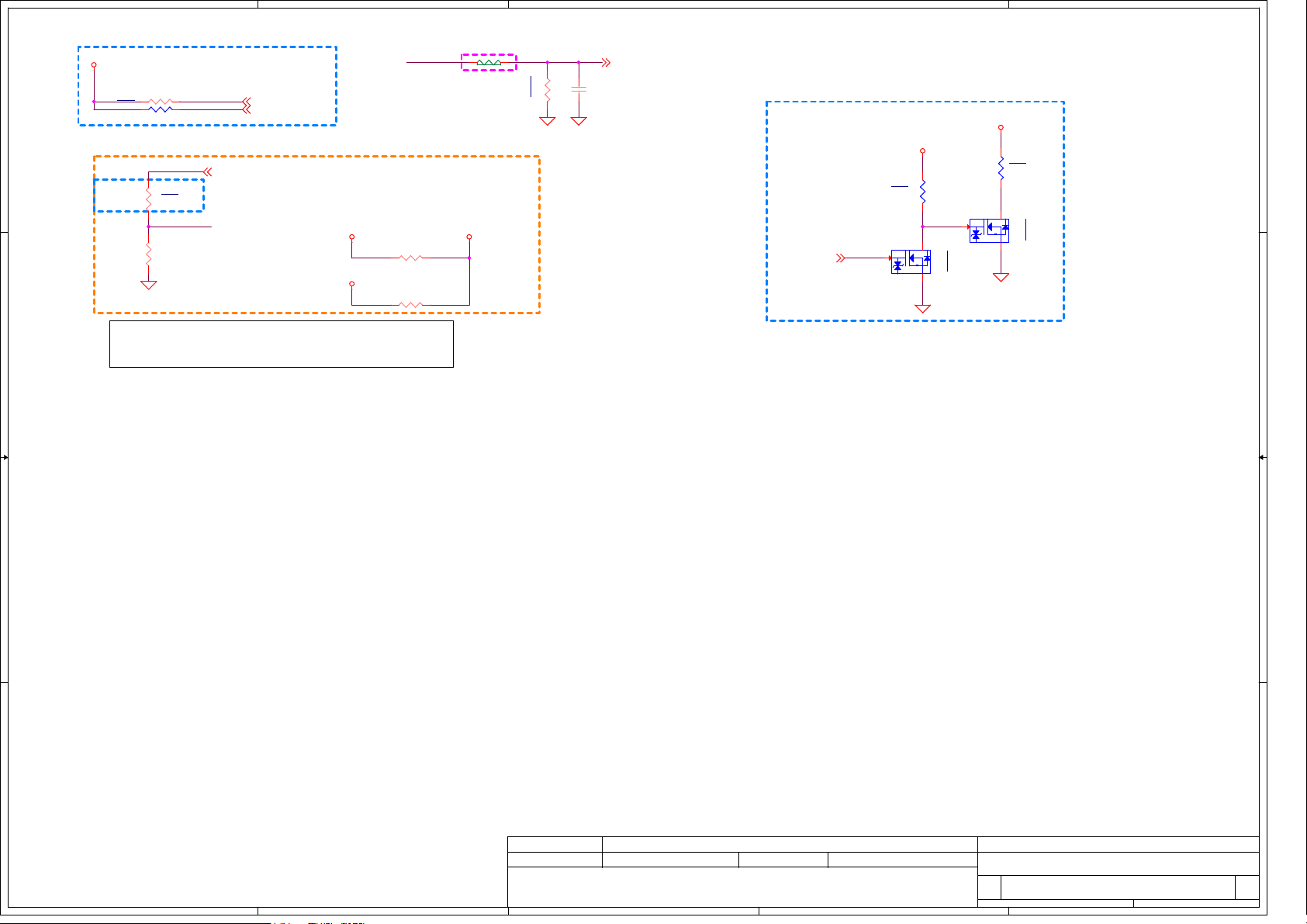

Board ID Table

3.3V +/- 5%Vcc

Board ID

0

1

2

3

4

5

6

7

R

240K +/- 1% 4700p

130K +/- 5%

62K +/- 5%

33K +/- 5%

8.2K +/- 5%

4.3K +/- 5%

2K +/- 5%

1K +/- 5% 4700p

SMBUS Control Table

SOURCE

PCH_SML0CL K

PCH_SML0DATA

PCH_SML1CL K

PCH_SML1DATA

SMBCLK

SMBDATA

EC_SMB03_CLK

EC_SMB03_DAT

EC_SMB04_CLK

EC_SMB04_DAT

EC_SMB05_CLK

EC_SMB05_DAT

EC_SMB10_CLK

EC_SMB10_DAT

EC_SMB00_CLK

EC_SMB00_DAT

EC_SMB01_CLK

EC_SMB01_DAT

1 1

USB 2.0

PCH

PCH

PCH

MEC5106

MEC5106

MEC5106

MEC5106

MEC5106

MEC5106

DESTINATIONUSB 2.0 PORT#

1

2

3

4

5

6

7

8

9

10

USB DCI Debug

None

None

Type-C_R

FPR

None

None

Type-C_L

CAM

BT

4700p

4700p

4700p

4700p

4700p

4700p

C

REV

X00

X01

X02

N/A

PCB Revision

0.1

0.2

0.3

N/A

Check

BATT

PCH

Connec tor

Charger

VCCIN

Control lerPDControl ler

V

MIPI6 0

USB/I2C

MUX

BurnSid e

Bridge

Reserve

V

Accel

TI Amp.

V

V

V

Reserve

V

V

V

V

V

CLK

DESTINATIONDIFFERENTIAL

WLAN

M.2 SSD

None

None

Card Reader

None

EC eSPI

CLK

CLKOUT_PCIE 0

CLKOUT_PCIE 1

CLKOUT_PCIE 2

CLKOUT_PCIE 3

CLKOUT_PCIE 4

CLKOUT_PCIE 5

FLEX CLOCKS DESTINATION

ESPI_CLK

PCIE/USB3.1

Flexible I/O

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Interface DESTINATION

PCI-E#1 / USB 3.1#1

PCI-E#2 / USB 3.1#2

PCI-E#3 / USB 3.1#3

PCI-E#4 / USB 3.1#4

PCI-E#5 / USB 3.1#5

PCI-E#6 / USB 3.1#6

PCI-E#7

PCI-E#8

PCI-E#9

PCI-E#10

PCI-E#11 / SATA#0

PCI-E#12 / SATA#1a

PCI-E#13

PCI-E#14

PCI-E#15 / SATA#1b

PCI-E#16 / SATA#2

Thunderbolt

TBT PORT# DESTINATION

0

TBT

1

2

3

Displayport

DDI PORT# DESTINATION

DDI

A

B

None

USB DCI Debug

WLAN PCIe Gen2

None

None

None

None

None

M.2 SSD

None

None

None

Card Reader PCIE GEN2

USB Type-C_L

None

USB Type-C_R

None

4 Lane eDP

None

Symbol Note :

: means de-po p

@

: means Digital Ground

: means Analog Ground

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

A

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

2020/10/01 2018/10/01

2020/10/01 2018/10/01

2020/10/01 2018/10/01

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

P003 - Notes List

P003 - Notes List

P003 - Notes List

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

LA-H811P

LA-H811P

LA-H811P

Date : Sheet of

Date : Sheet of

Date : Sheet of

3 100Tuesday, December 24, 2019

3 100Tuesday, December 24, 2019

3 100Tuesday, December 24, 2019

0.1 (X00)

0.1 (X00)

0.1 (X00)

5

4

3

2

1

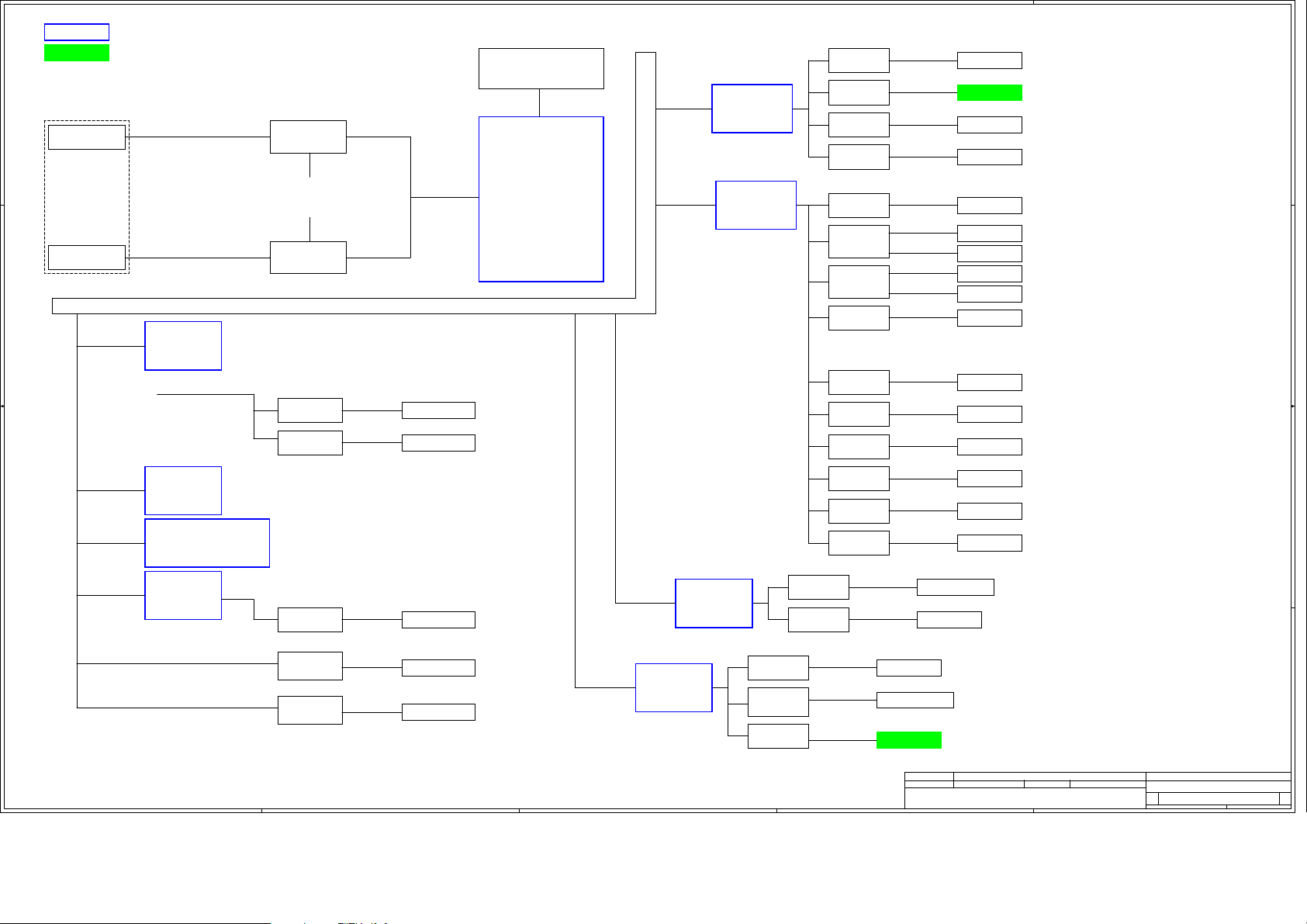

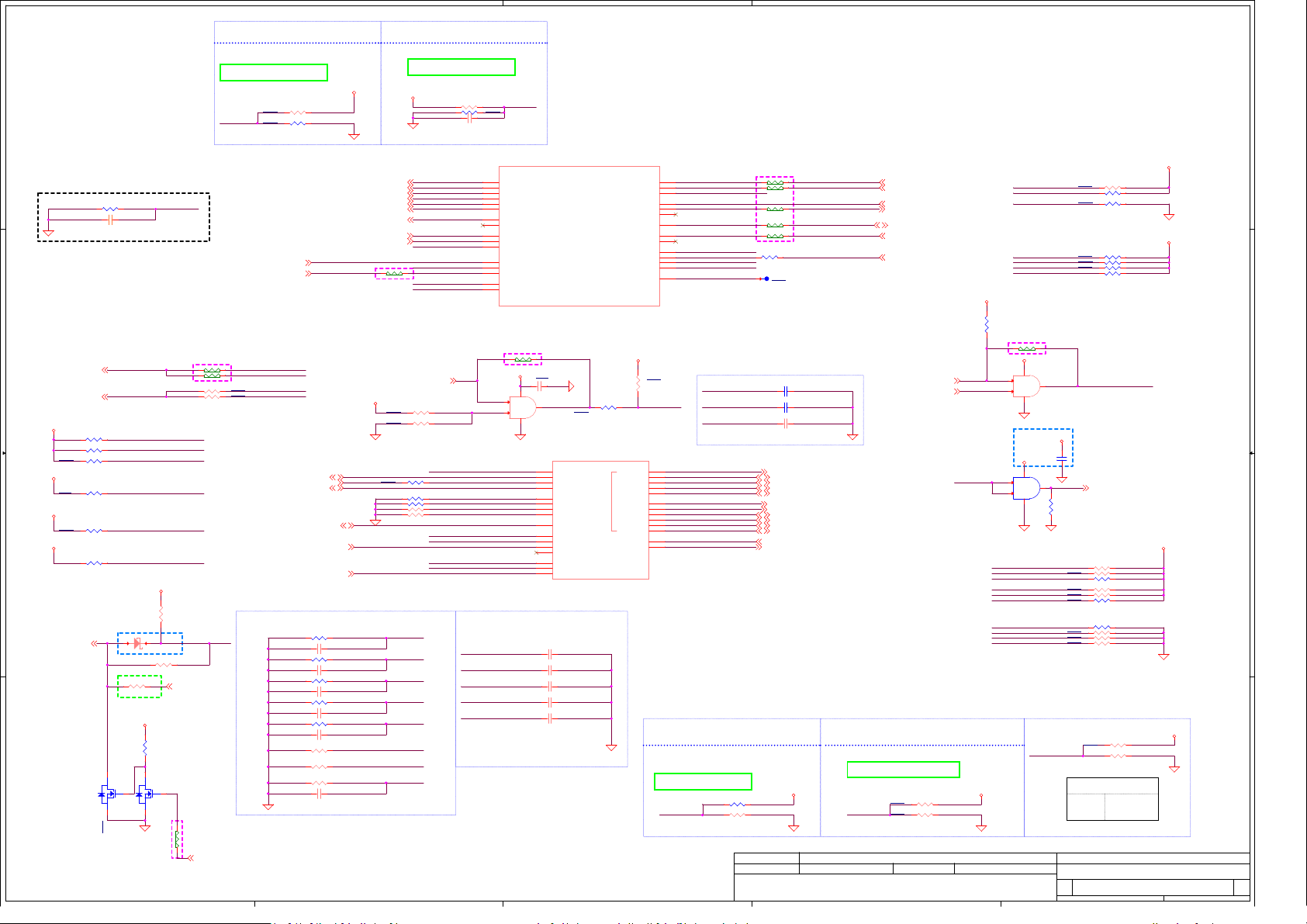

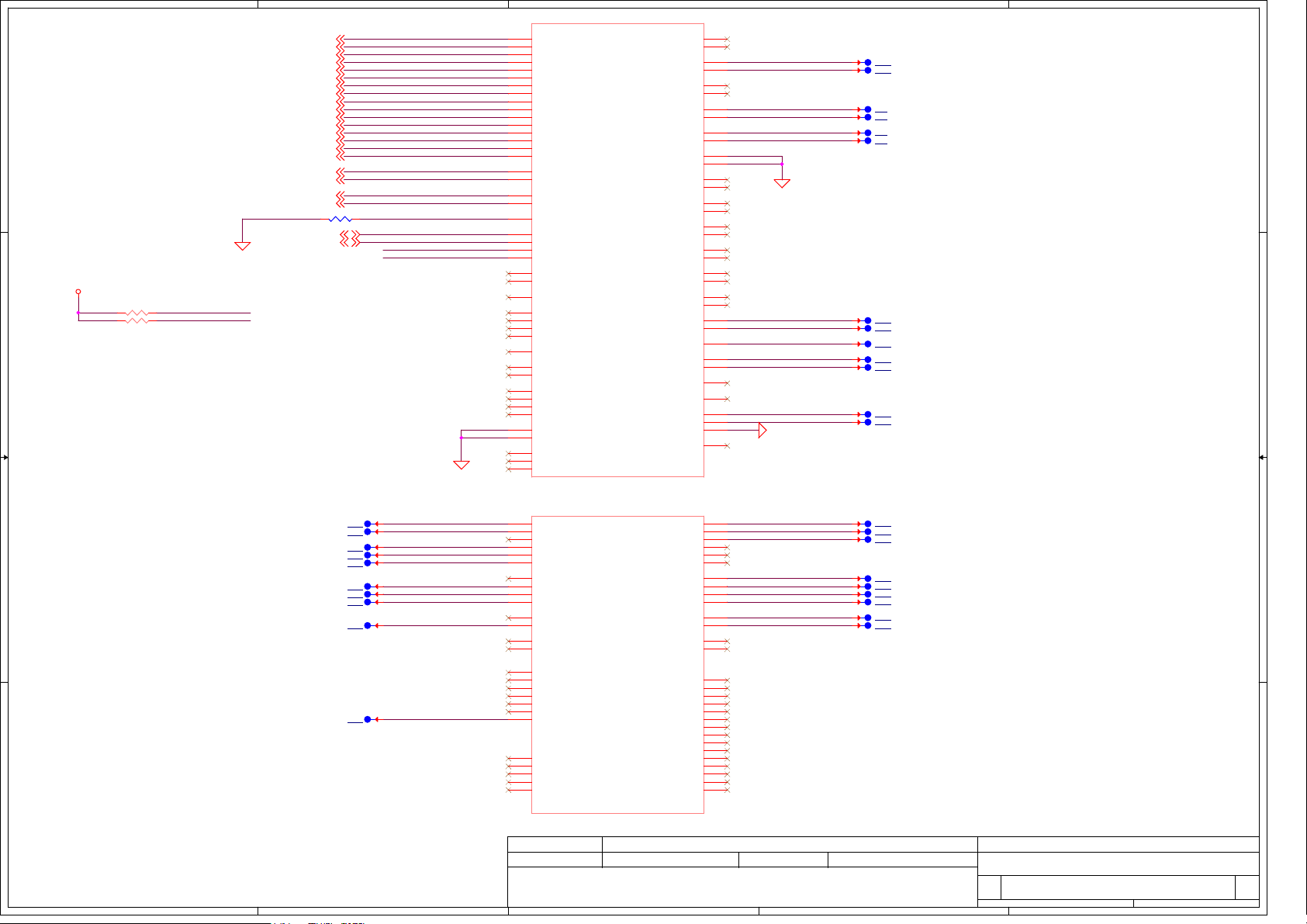

Power Rail

Audio Power Rail

D D

Type-C Port-L

Type-C Port-R

C C

VCCIN

IMVP_VR_ON _EN

1.8V_PRIM_P G

B B

0.6V_VDDQ_EN _P

1.1V_MEM_EN

PL2 TDC 36A

Peak Current 62A

(MP294 0A)

Page: 91,9 2,93

+VCC1.05_OUT_FET

VCCIN_AUX

TDC 10A

Peak Current 26A

(MP29 41)

Page: 89,90

+0.6V_VDDQ (LPDDR4X only)

TDC 0.5A

Peak C urrent 0.72A

(NB691)

Page:8 7

+1.1V_MEM

TDC 4.2A

Peak Current 6A

(RT6243B )

Page:8 6

PD1

Controller

TPS65987D H

EC_I2C

EC_I2C

PD2

Controller

TPS65987D H

UC13

AOZ1334DI-01

UC12

AOZ1334DI-01

UC27

AOZ1334DI-01

VCCST_EN

VCCSTG_EN

VCC_SFR_OC_E N

Modena POWER BLOCK DIAGRAM

B+B+

+VCCST_CPU

+VCCSTG_CPU

+VCC_SFR_OC

2S2P Battery

51W

Buck-boost

Charger

ISL9538B

(NVDC)

Page: 83

B+

B+

B+

B+

ALWON_5VALW

PCH_PRIM_E N

ALWON_3VALW

+5VALW

TDC 5.1A

Peak Current 7.3A

(NB502)

Page:8 5

+1.8VPRIM

TDC 1.9A

Peak Current 2.8A

(NB691)

Page:8 8

+3VALW

TDC 7.4A

Peak C urrent 10.5A

(NB502)

Page:8 4

UPD1

TPS65987D H

UC28

AOZ1336DI

UC22

AOZ1334DI-01

UC25

AOZ1336DI

UC24

AOZ1336DI

UC23

AOZ1334DI-01

U7

SY628 8

U31

AOZ1331DI

U34

AOZ1331DI

UC30

AOZ1336DI

US1

AOZ1336D I

UC31

SY6288

UT1

AOZ1336D I

UT2

AOZ1336D I

U713

AOZ1336DI

U55

SY6288

RUN_ON_P

CPU_C10_GATE#

AUD_PW R_EN

RUN_ON_P

SUS_ON_P

ENVDD

VCCDSW_EN_GPIO

VCCDSW_EN_GPIO

WLAN_PW R_EN

TS_EN_R

RUN_ON_P

RUN_ON_P_R

SD_PWR_EN

3.3V_TBT_L_EN

3.3V_TBT_R _EN

TP_EN

3.3V_CAM_EN

+5VALWB_L_TBT

+5VS

+VCC1P8A

+1.8VS_AUDIO

+1.8VS

+1.8V_MEM

+LCDVDD

+3V_PRIM

+3VALW_DSW

+3VS_WLAN

+3VS_TS

+3VS

+3VS_SSD

+3VS_CR

+3.3V_TBT_ L

+3.3V_TBT_R

+3VS_TP

+CAM_PWR

Q15

SI3457BDV

A A

5

QZ10

SI3457BDV

EN_INVPWR

IRCAM_EN

+INV_PWR_SRC

B+_CAM

4

ALWON_5VALWB

+5VALWB

TDC 3.5A

Peak Current 5A

(NB502)

Page:8 5

3

U60

AOZ1336DI

UPD2

TPS65987D H

U36

AOZ1336DI

RUN_ON_P

AUD_PW R_EN

+5VBS

+5VALWB_R_TBT

+5VS_AUDIO

Security C lassification

Security C lassification

Security C lassification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

2020/10/01 2018/10/01

2020/10/01 2018/10/01

2020/10/01 2018/10/01

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

P004 - Power MAP

P004 - Power MAP

P004 - Power MAP

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

LA-H811P

LA-H811P

LA-H811P

Date: S heet of

Date: S heet of

Date: S heet of

1

4 100Tuesday, December 24, 2019

4 100Tuesday, December 24, 2019

4 100Tuesday, December 24, 2019

0.1 (X00)

0.1 (X00)

0.1 (X00)

5

[AC in] for VBU_L/VBU_R

TBT_VBUS

+3V_LDO

+CHG_VIN_20V

B+

ACAV_INEC Input

ALWON

+3VALW

+5VALW (+5VALWB)

ALW_PWRGD_3V_5V

POWER_SW_IN#

Ta

Tb

Tc

Td

Te

Tf

Tg Tg

Th

200ms < Th

PD Output

PD Output

CHR Output

D D

EC Output

VR Output

VR Output

VR Output

EC Input

[Battery only, AC absent]

CHR Output

B+

PWR_SW_IN#

EC Output

ALWON

VR Output

+3VALW

VR Output

+5VALW (+5VALWB)

VR Output

ALW_PWRGD_3V_5V

EC pay attention timing

VCCDSW_EN_GPIO

+3VALW_DSW/+3V_PRIM(U31 )

EC Output

PCH_DPWROK

PCH Output

SIO_SLP_SUS#

VR Output

+1.8V_PRIM(PU500)

PCH Output

+VCC1.05_OUT _PCH

PCH Output

+VCC1.05_OUT _FET

+VCCST_CPU(U C13)

VR Output

C C

B B

1.8V_PRIM_PG

+VCCIN_AUX( PU900)

PCH Output

VR Output

VCCIN_AUX_VR_PG

PCH_RSMRS T#

EC Output

PCH Output

ESPI_RESET#

EC Output AC_PRES ENT

POWER_SW_IN# 16ms < T < 4s

PCH Output

SIO_SLP_S5#

PCH Output

SIO_SLP_S4#

PCH Output

SIO_SLP_S3#

PCH Output

CPU_C10_GATE#

PCH Output

SIO_SLP_S0#

RUN_ON_ECEC Output

VR Output

+1.1V_MEM(PU700)

+0.6V_VDDQ( PU800)

VR Output

+1.8V_MEM(U C23)

+VCCSTG_CPU (UC12)

+VCC1P8A(UC2 2)

+VCC_SFR_OC( UC27)

+3VS(UC30 )

+1.8VS(UC24)

+5VS(UC28)/+5VBS(U60)

+3VS_SSD(US1)

RUNPWROK(ALL_SYS_PWRGD)EC Input

EC Output

IMVP_VR_ON_P(VCCST_PWRGD)

VR Output

+VCCIN(PU1100)

VR Output

PCH_PWROK_P

CPUPWRGD

EC Output

SYS_PWROK

PCH_PLTRST #_ECPCH Output

T1

T2

T3

T4

T5

T6

T7

T8

T9

T10

T11

T12

T13

T14

T15

T16

T17

T18

T19

T20

T21

T22

T23

T24

T25

T26

T27

T28

T29

T30

4

200ms < Th

Td

Te

Tf

T31

T32

T33

T34

T35

3

Power On Sequence

ITEM

Ta

Tb

Tc

Td

Te

Tf

Tg

Th

ITEM

T1

T2

T3

T4

T5

T6

T7

T8

T9

T10

T11

T12

T13

T14

T15

T16

T17

T18

T19

T20

T21

T22

T23

T24

T25

T26

T27

T28

T29

T30

T31

T32

T33

T34

T35

T36

T37

TBT_VBUS

+3V_LDO

+CHG_VIN_2 0V

B+

ALWON

ALWON

+3VALW

Measure Point

VCCDSW_EN_GPIO

+3VALW_DSW/+3V_PR IM

PCH_DPWROK

SIO_SLP_SUS#

+1.8V_PRIM

+1.8V_PRIM

+VCC1.05_OUT_ FET

+1.8V_PRIM

1.8V_PRIM_PG

+VCCIN_AUX

VCCIN_AUX_VR_P G

PCH_RSMRS T#

ESPI_RESET#

SIO_SLP_S5#

SIO_SLP_S4#

SIO_SLP_S4#

SIO_SLP_S4#

SIO_SLP_S4#

SIO_SLP_S4#

SIO_SLP_S4#

SIO_SLP_S4#

SIO_SLP_S4#

SIO_SLP_S4#

SIO_SLP_S4#

RUN_ON_EC

RUN_ON_EC

RUN_ON_EC

RUN_ON_EC

RUN_ON_EC

RUN_ON_EC

+3VS

RUNPWR OK

IMVP_VR_ON_P

+VCCIN

PCH_PWROK_P

CPUPWR GD

SYS_PWRO K

[AC in]

+3V_LDO

To

+CHG_VIN_2 0V

To

B+

To

ACAV_IN

To

ALWONACAV_IN

To

+3VALW

To

+5VALW ( +5VALWB) ALWON

To

ALW_PWRGD_3V_5V

To

+3VALW_DSW/+3V_P RIM

To

PCH_DPWROK

To

SIO_SLP_SUS#

To

+1.8V_PRIM

To

+VCC1.05_OUT_ PCH

To

+VCC1.05_OUT_ FET

To

+VCCST_CPU

To

1.8V_PRIM_PG

To

+VCCIN_AUX

To

VCCIN_AUX_VR_P G

To

PCH_RSMRS T#

To

ESPI_RESET#

To

AC_PRESENT

To

SIO_SLP_S4#

To

SIO_SLP_S3#

To

CPU_C10_GATE #

To

SIO_SLP_S0#

To

RUN_ON_EC

To

+1.1V_MEM

To

+0.6V_VDDQ

To

+1.8V_MEM

To

+1.8V_MEM

To

+VCC1P8A

To

+VCC_SFR_OC

To

+3VS

To

+1.8VS

To

+5VS/+5V BS

To

+3.3VDX_SSD

To

+SSD_PWR2

To

+SSD_PWR3

To

RUNPWR OK

To

IMVP_VR_ON_P

To

+VCCIN

To

PCH_PWROK_P

To

CPUPWR GD

To

SYS_PWRO K

To

PCH_PLTRST#_E C

To

TimeMeasure Point

Time

[Battery only, AC absent]

ITEM

Measure Point

B+

Tc

POWER_SW_IN# Low pluse width

Th

POWER_SW_IN#

Td

ALWON +3VALW

Te

Tf

+3VALW ALW_PWRGD_3V_5V

Tg

To

To

To

To

To

2

POWER_SW_IN#

ALWON

+5VALW ( +5VALWB)

1

Power Down Sequence

EC pay attention timing

Time

PCH_PLTRST#

CPUPWRGD

PCH_CLK_OUTP UTS

SIO_SLP_S3#

CPU_C10_GATE#

SYS_PWROK

PCH_PWROK_P

IMVP_VR_ON_P(VCCST_PWRGD)

RUNPWROK(ALL_SYS_PWRGD)

+VCCIN

3VS/+1.8VS/+5V S/+5VBS

+VCCSTG_CPU

SIO_SLP_S4#

+1.1V_MEM

+0.6V_VDDQ

+1.8V_MEM

+VCC_SFR_OC

SIO_SLP_S5#

+VCC1P05_OUTPUT_PLL

PCH_RSMRS T#

PCH_DPWROK

+3VALW_DSW/+3 V_PRIM

SIO_SLP_SUS#

ESPI_RESET#

SIO_SLP_S0#

+1.8V_PRIM

+VCC1.05_OUT _PCH

+VCCIN_AUX

+VCCST_CPU

SUSCLK

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

2

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Compal Secret Data

Compal Secret Data

Compal Secret Data

2020/10 /01 2018/10 /01

2020/10 /01 2018/10 /01

2020/10 /01 2018/10 /01

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

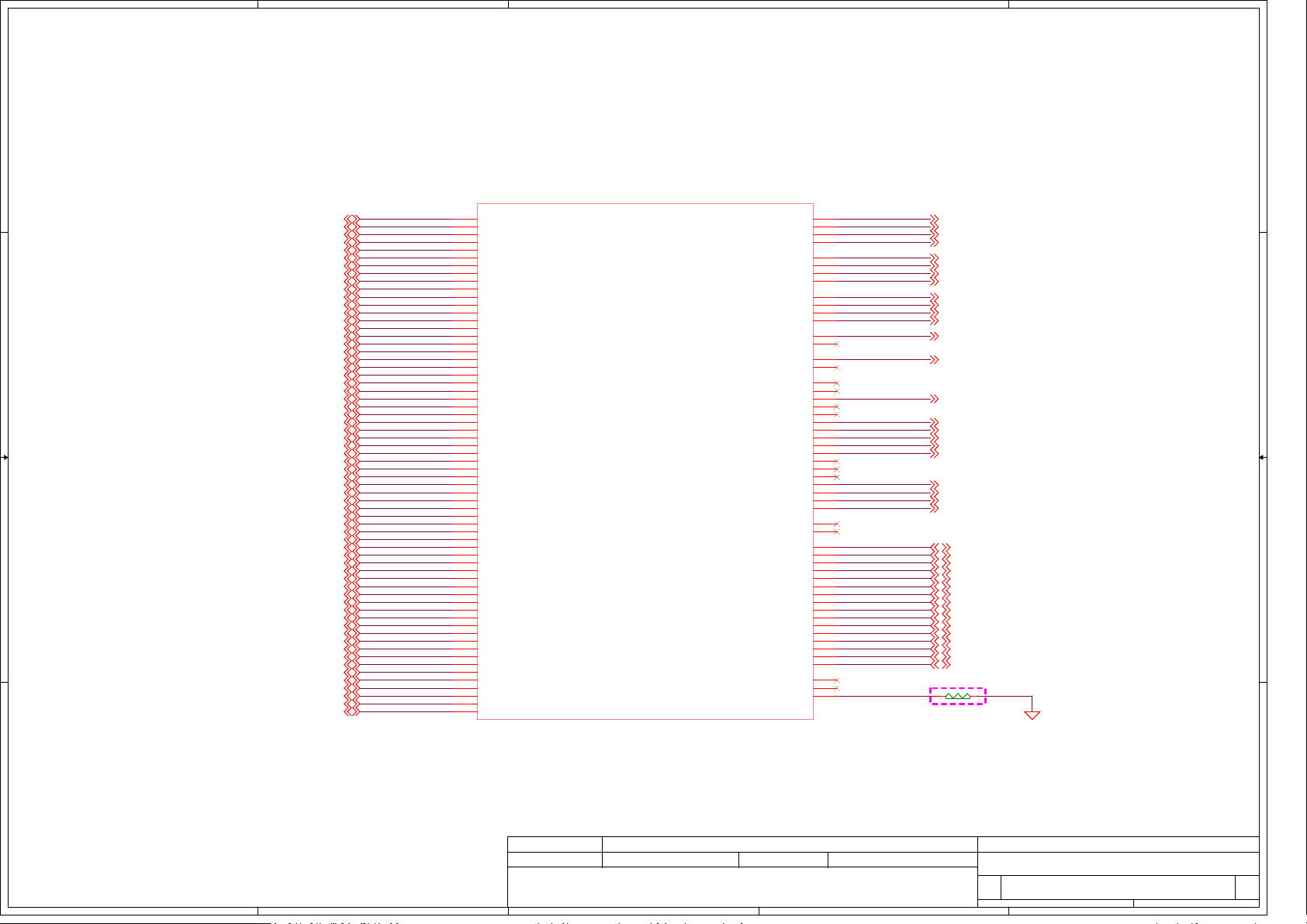

P005 - Power Sequence

P005 - Power Sequence

P005 - Power Sequence

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

LA-H811P

LA-H811P

LA-H811P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

0.1 (X00)

0.1 (X00)

0.1 (X00)

5 100Tuesday, December 24, 2019

5 100Tuesday, December 24, 2019

5 100Tuesday, December 24, 2019

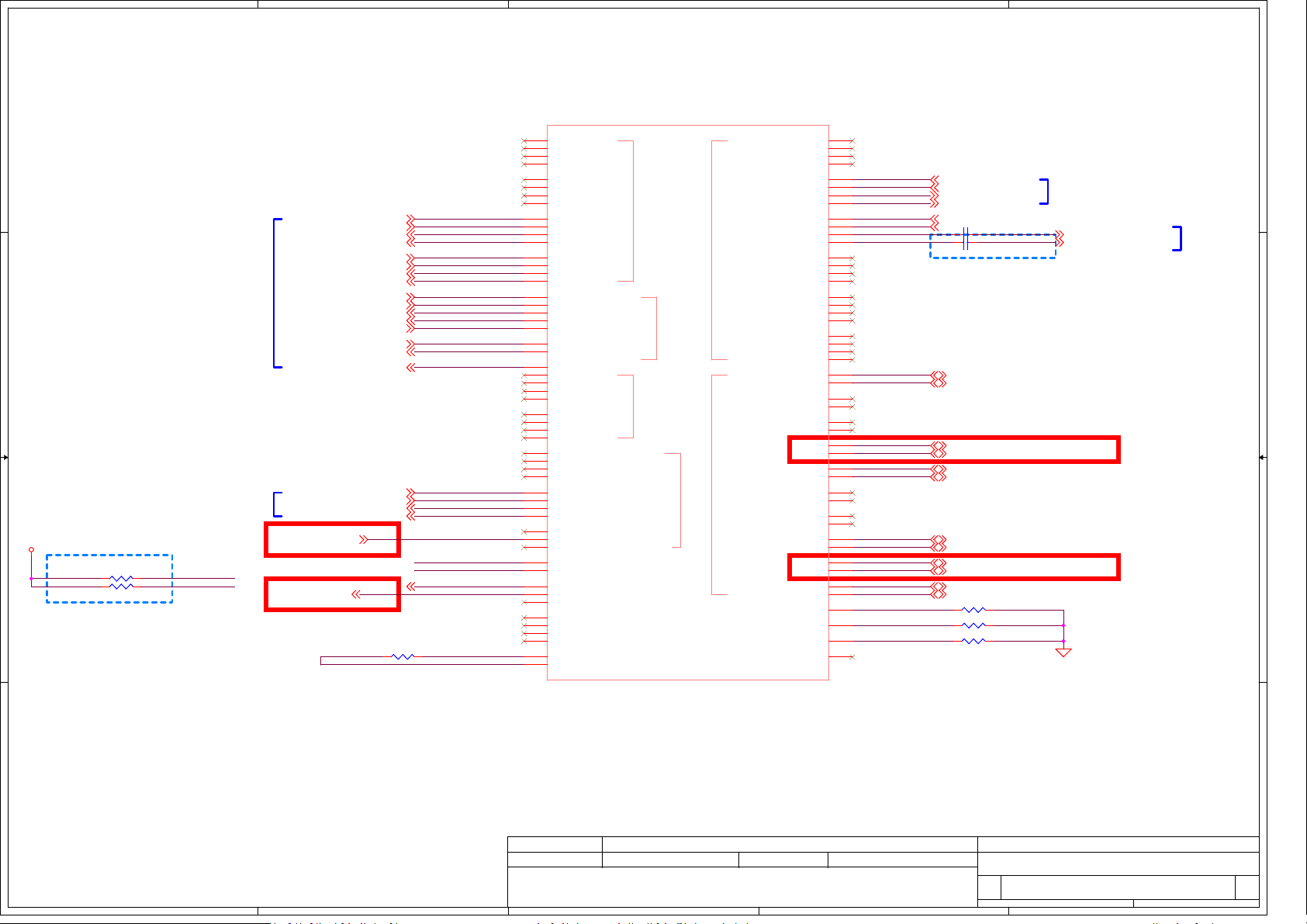

5

D D

+3V_PRIM

C C

DVT1_5 7

RH74210K_0201_5%

12

RH60310K_0201_5%

12

RH675100K_0201_5%

12

RH717100K_0201_5% @

12

RH718100K_0201_5% @

12

USB_OC1#

USB_OC2#

EDP_HPD

CPU_TCP0_HPD

USB_OC1#

eDP

4

UC1A

EDP_TXN0<38>

EDP_TXP0<38>

EDP_TXN1<38>

EDP_TXP1<38>

EDP_TXN2<38>

EDP_TXP2<38>

EDP_TXN3<38>

EDP_TXP3<38>

EDP_AUXN<38>

EDP_AUXP<38>

TBT_0_LSX_TX<46>

TBT_0_LSX_RX<46>

TBT_2_LSX_TX<48>

TBT_2_LSX_RX<48>

EDP_HPD<38,58>

TS_DET#<38>

TS_INT#<38>

ENVDD_PCH<38>

PANEL_BKLEN<10,38>

EDP_BIA_PWM<38>

TP99

TP69

TBT_0_LSX_RX

TBT_2_LSX_RX

EDP_HPD

CPU_TCP0_HPD

USB_OC1#

USB_OC2#

PAD~D

1

PAD~D

1

RC3150_0201_1%

12

TP@

TP@

Y5

DDIA_TXN_0

Y3

DDIA_TXP_0

Y1

DDIA_TXN_1

Y2

DDIA_TXP_1

V2

DDIA_TXN_2

V1

DDIA_TXP_2

V3

DDIA_TXN_3

V5

DDIA_TXP_3

W4

DDIA_AUX_N

W3

DDIA_AUX_P

AE3

DDIB_TXN_0

AE5

DDIB_TXP_0

AE2

DDIB_TXN_1

AE1

DDIB_TXP_1

AC5

DDIB_TXN_2

AC3

DDIB_TXP_2

AC1

DDIB_TXN_3

AC2

DDIB_TXP_3

AD3

DDIB_AUX_N

AD4

DDIB_AUX_P

DP15

GPP_E22/DDPA_CTRLCLK/PCIE_LNK_DOWN

DJ17

GPP_E23/DDPA_CTRLDATA/BK4/SBK4

DL40

GPP_H16/DDPB_CTRLCLK

DP42

GPP_H17/DDPB_CTRLDATA

DL17

GPP_E18/DDP1_CTRLCLK/TBT_LSX0_TXD

DK17

GPP_E19/DDP1_CTRLDATA/TBT_LSX0_RXD

DN17

GPP_E20/DDP2_CTRLCLK/TBT_LSX1_TXD

DP17

GPP_E21/DDP2_CTRLDATA/TBT_LSX1_RXD

DK34

GPP_D9/ISH_SPI_CS_N/DDP3_CTRLCLK/GSPI2_CS0_N/TBT_LSX2_TXD

DL34

GPP_D10/ISH_SPI_CLK/DDP3_CTRLDATA/GSPI2_CLK/TBT_LSX2_RXD

DN33

GPP_D11/ISH_SPI_MISO/DDP4_CTRLCLK/GSPI2_MISO/TBT_LSX3_TXD

DL33

GPP_D12/ISH_SPI_MOSI/DDP4_CTRLDATA/GSPI2_MOSI/TBT_LSX3_RXD

DW11

GPP_E14/DPPE_HPDA/DISP_MISCA

CV42

GPP_A18/DDSP_HPDB/DISP_MISCB

CV39

GPP_A19/DDSP_HPD1/DISP_MISC1

CY43

GPP_A20/DDSP_HPD2/DISP_MISC2

CR41

GPP_A14/USB_OC1_N/DDSP_HPD3/DISP_MISC3

CT41

GPP_A15/USB_OC2_N/DDSP_HPD4/DISP_MISC4

DV14

GPP_E17

DN21

EDP_VDDEN

DL19

EDP_BKLTEN

DU19

J3

D2

R2

ICL-U_BGA1526

@

EDP_BKLTCTL

RSVD_1

DISP_UTILS

DISP_RCOMP

RSVD_1

DISP_UTILS KB_DET#

DP_RCOMP

3

BB5

TCP0_TX_N0

BB6

TCP0_TX_P0

AV6

TCP0_TX_N1

AV5

TCP0_TX_P1

BH2

TCP0_TXRX_N0

BH1

TCP0_TXRX_P0

BF1

TCP0_TXRX_N1

BF2

TCP0_TXRX_P1

AY5

TCP0_AUX_N

AY6

TBT / USB / DP

GPP_A17/DISP_MISCC

TCP0_AUX_P

TCP1_TX_N0

TCP1_TX_P0

TCP1_TX_N1

TCP1_TX_P1

TCP1_TXRX_N0

TCP1_TXRX_P0

TCP1_TXRX_N1

TCP1_TXRX_P1

TCP1_AUX_N

TCP1_AUX_P

TCP2_TX_N0

TCP2_TX_P0

TCP2_TX_N1

TCP2_TX_P1

TCP2_TXRX_N0

TCP2_TXRX_P0

TCP2_TXRX_N1

TCP2_TXRX_P1

TCP2_AUX_N

TCP2_AUX_P

TCP3_TX_N0

TCP3_TX_P0

TCP3_TX_N1

TCP3_TX_P1

TCP3_TXRX_N0

TCP3_TXRX_P0

TCP3_TXRX_N1

TCP3_TXRX_P1

TCP3_AUX_N

TCP3_AUX_P

TC_RCOMP_N

TC_RCOMP_P

GPP_A21

GPP_A22

AR5

AR6

AL5

AL3

BD2

BD1

BB1

BB2

AN3

AN5

BF6

BF5

BJ5

BJ6

BL1

BL2

BM2

BM1

BG6

BG5

BP6

BP5

BV5

BV6

BR1

BR2

BT2

BT1

BT6

BT5

TCRCOMP_DN

AY1

TCRCOMP_DP

AY2

CT38

DVT1_42 : remove RTC

CV43

CV41

DDI

1 0f 19

2

RC1 150_0201_1%

1 2

TBT_0_TTX_DRX_N0<46>

TBT_0_TTX_DRX_P0<46>

TBT_0_TTX_DRX_N1<46>

TBT_0_TTX_DRX_P1<46>

TBT_0_TRX_DTX_N0<46>

TBT_0_TRX_DTX_P0<46>

TBT_0_TRX_DTX_N1<46>

TBT_0_TRX_DTX_P1<46>

TBT_0_AUXN <46>

TBT_0_AUXP <46>

TBT_2_TTX_DRX_N0<48>

TBT_2_TTX_DRX_P0<48>

TBT_2_TTX_DRX_N1<48>

TBT_2_TTX_DRX_P1<48>

TBT_2_TRX_DTX_N0<48>

TBT_2_TRX_DTX_P0<48>

TBT_2_TRX_DTX_N1<48>

TBT_2_TRX_DTX_P1<48>

TBT_2_AUXN <48>

TBT_2_AUXP <48>

DVT1_31, DVT1_67

3.3V_CAM_EN <71>

KB_DET# <63>

TBT_L

TBT_R

1

RH672 10K_0201_5%

1 2

+3V_PRIM

B B

TBT LSX #0 PINS VCCIO CONFIGURATION

+3V_PRIM +3V_PRIM

12

R6172

@

4.7K_0201_5%

TBT_0_LSX_RX TBT_2_LSX_RX

RC691

20K_0201_5%

1 2

HIGH

LOW

3.3V

1.8V

12

R6174

@

4.7K_0201_5%

RC693

20K_0201_5%

1 2

TBT LSX #2 PINS VCCIO CONFIGURATION

HIGH

LOW

3.3V

1.8V

PLACE CLOSE TO THE SIGNAL TO AVOID STUB

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

2020/10/01 2018/10/01

2020/10/01 2018/10/01

2020/10/01 2018/10/01

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

P006 - ICL-U(1/13)TCSS,EDP

P006 - ICL-U(1/13)TCSS,EDP

P006 - ICL-U(1/13)TCSS,EDP

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

LA-H811P

LA-H811P

LA-H811P

Date : Sheet of

Date : Sheet of

Date : Sheet of

1

6 100Tuesday, December 24, 2019

6 100Tuesday, December 24, 2019

6 100Tuesday, December 24, 2019

0.1 (X00)

0.1 (X00)

0.1 (X00)

5

4

3

2

1

Memory connection refer 573975 Rev1P1

D D

UC1B

LP4(NIL) / DDR4(NIL) LP4(NIL) / DDR4(NIL)

DDR_A_D0_0<23>

DDR_A_D0_1<23>

DDR_A_D0_2<23>

DDR_A_D0_3<23>

DDR_A_D0_4<23>

DDR_A_D0_5<23>

DDR_A_D0_6<23>

DDR_A_D0_7<23>

DDR_A_D1_0<23>

DDR_A_D1_1<23>

DDR_A_D1_2<23>

DDR_A_D1_3<23>

DDR_A_D1_4<23>

DDR_A_D1_5<23>

DDR_A_D1_6<23>

DDR_A_D1_7<23>

DDR_A_D2_0<23>

DDR_A_D2_1<23>

DDR_A_D2_2<23>

DDR_A_D2_3<23>

C C

B B

A A

DDR_A_D2_4<23>

DDR_A_D2_5<23>

DDR_A_D2_6<23>

DDR_A_D2_7<23>

DDR_A_D3_0<23>

DDR_A_D3_1<23>

DDR_A_D3_2<23>

DDR_A_D3_3<23>

DDR_A_D3_4<23>

DDR_A_D3_5<23>

DDR_A_D3_6<23>

DDR_A_D3_7<23>

DDR_B_D0_0<23>

DDR_B_D0_1<23>

DDR_B_D0_2<23>

DDR_B_D0_3<23>

DDR_B_D0_4<23>

DDR_B_D0_5<23>

DDR_B_D0_6<23>

DDR_B_D0_7<23>

DDR_B_D1_0<23>

DDR_B_D1_1<23>

DDR_B_D1_2<23>

DDR_B_D1_3<23>

DDR_B_D1_4<23>

DDR_B_D1_5<23>

DDR_B_D1_6<23>

DDR_B_D1_7<23>

DDR_B_D2_0<23>

DDR_B_D2_1<23>

DDR_B_D2_2<23>

DDR_B_D2_3<23>

DDR_B_D2_4<23>

DDR_B_D2_5<23>

DDR_B_D2_6<23>

DDR_B_D2_7<23>

DDR_B_D3_0<23>

DDR_B_D3_1<23>

DDR_B_D3_2<23>

DDR_B_D3_3<23>

DDR_B_D3_4<23>

DDR_B_D3_5<23>

DDR_B_D3_6<23>

DDR_B_D3_7<23>

DDR_COMP_0

RC12100_0201_1%

12

DDR_COMP_1

RC13100_0201_1%

12

DDR_COMP_2

RC14100_0201_1%

12

CA48

DDRA_DQ0_0/DDR0_DQ0_0

CA47

DDRA_DQ0_1/DDR0_DQ0_1

CA49

DDRA_DQ0_2/DDR0_DQ0_2

BV49

DDRA_DQ0_3/DDR0_DQ0_3

CA45

DDRA_DQ0_4/DDR0_DQ0_4

BV47

DDRA_DQ0_5/DDR0_DQ0_5

BV45

DDRA_DQ0_6/DDR0_DQ0_6

BV48

DDRA_DQ0_7/DDR0_DQ0_7

CC42

DDRA_DQ1_0/DDR0_DQ1_0

CC39

DDRA_DQ1_1/DDR0_DQ1_1

CC43

DDRA_DQ1_2/DDR0_DQ1_2

CE38

DDRA_DQ1_3/DDR0_DQ1_3

CC38

DDRA_DQ1_4/DDR0_DQ1_4

CE39

DDRA_DQ1_5/DDR0_DQ1_5

CE42

DDRA_DQ1_6/DDR0_DQ1_6

CE43

DDRA_DQ1_7/DDR0_DQ1_7

BT48

DDRA_DQ2_0/DDR0_DQ2_0

BT47

DDRA_DQ2_1/DDR0_DQ2_1

BT49

DDRA_DQ2_2/DDR0_DQ2_2

BN49

DDRA_DQ2_3/DDR0_DQ2_3

BT45

DDRA_DQ2_4/DDR0_DQ2_4

BN47

DDRA_DQ2_5/DDR0_DQ2_5

BN45

DDRA_DQ2_6/DDR0_DQ2_6

BN48

DDRA_DQ2_7/DDR0_DQ2_7

BV42

DDRA_DQ3_0/DDR0_DQ3_0

BV39

DDRA_DQ3_1/DDR0_DQ3_1

BV43

DDRA_DQ3_2/DDR0_DQ3_2

BW38

DDRA_DQ3_3/DDR0_DQ3_3

BV38

DDRA_DQ3_4/DDR0_DQ3_4

BW39

DDRA_DQ3_5/DDR0_DQ3_5

BW42

DDRA_DQ3_6/DDR0_DQ3_6

BW43

DDRA_DQ3_7/DDR0_DQ3_7

AY48

DDRB_DQ0_0/DDR0_DQ4_0

AY47

DDRB_DQ0_1/DDR0_DQ4_1

AY49

DDRB_DQ0_2/DDR0_DQ4_2

AU45

DDRB_DQ0_3/DDR0_DQ4_3

AY45

DDRB_DQ0_4/DDR0_DQ4_4

AU47

DDRB_DQ0_5/DDR0_DQ4_5

AU48

DDRB_DQ0_6/DDR0_DQ4_6

AU49

DDRB_DQ0_7/DDR0_DQ4_7

AY42

DDRB_DQ1_0/DDR0_DQ5_0

AY38

DDRB_DQ1_1/DDR0_DQ5_1

AY43

DDRB_DQ1_2/DDR0_DQ5_2

BB39

DDRB_DQ1_3/DDR0_DQ5_3

AY39

DDRB_DQ1_4/DDR0_DQ5_4

BB38

DDRB_DQ1_5/DDR0_DQ5_5

BB42

DDRB_DQ1_6/DDR0_DQ5_6

BB43

DDRB_DQ1_7/DDR0_DQ5_7

AR48

DDRB_DQ2_0/DDR0_DQ6_0

AR47

DDRB_DQ2_1/DDR0_DQ6_1

AR49

DDRB_DQ2_2/DDR0_DQ6_2

AM45

DDRB_DQ2_3/DDR0_DQ6_3

AR45

DDRB_DQ2_4/DDR0_DQ6_4

AM47

DDRB_DQ2_5/DDR0_DQ6_5

AM48

DDRB_DQ2_6/DDR0_DQ6_6

AM49

DDRB_DQ2_7/DDR0_DQ6_7

AT42

DDRB_DQ3_0/DDR0_DQ7_0

AT39

DDRB_DQ3_1/DDR0_DQ7_1

AR43

DDRB_DQ3_2/DDR0_DQ7_2

AT38

DDRB_DQ3_3/DDR0_DQ7_3

AR38

DDRB_DQ3_4/DDR0_DQ7_4

AR39

DDRB_DQ3_5/DDR0_DQ7_5

AR42

DDRB_DQ3_6/DDR0_DQ7_6

AT43

DDRB_DQ3_7/DDR0_DQ7_7

D47

DDR_RCOMP_0

E46

DDR_RCOMP_1

C47

DDR_RCOMP_2

ICL-U_BGA1526

@

2 of 19

DDRA_CLK_N/DDR0_CLK_N_0

DDRA_CLK_P/DDR0_CLK_P_0

DDRB_CLK_N/DDR0_CLK_N_1

DDRB_CLK_P/DDR0_CLK_P_1

DDRA_CKE0/DDR0_CKE0

DDRA_CKE1/NC

DDRB_CKE0/NC

DDRB_CKE1/DDR0_CKE1

DDRA_CS_0/DDR0_CS#0

DDRA_CS_1/NC

DDRB_CS_0/NC

DDRB_CS_1/DDR0_CS#1

DDRB_CA4/DDR0_BA0

NC/DDR0_BA1

DDRA_CA5/DDR0_BG0

NC/DDR0_BG1

NC/DDR0_MA0

NC/DDR0_MA1

DDRB_CA5/DDR0_MA2

NC/DDR0_MA3

NC/DDR0_MA4

DDRA_CA0/DDR0_MA5

DDRA_CA2/DDR0_MA6

DDRA_CA4/DDR0_MA7

DDRA_CA3/DDR0_MA8

DDRA_CA1/DDR0_MA9

NC/DDR0_MA10

NC/DDR0_MA11

NC/DDR0_MA12

DDRB_CA0/DDR0_MA13

DDRB_CA2/DDR0_MA14WE#

DDRB_CA1/DDR0_MA15CAS#

DDRB_CA3/DDR0_MA16RAS#

NC/DDR0_ODT_0

NC/DDR0_ODT_1

DDRA_DQSN_0/DDR0_DQSN_0

DDRA_DQSP_0/DDR0_DQSP_0

DDRA_DQSN_1/DDR0_DQSN_1

DDRA_DQSP_1/DDR0_DQSP_1

DDRA_DQSN_2/DDR0_DQSN_2

DDRA_DQSP_2/DDR0_DQSP_2

DDRA_DQSN_3/DDR0_DQSN_3

DDRA_DQSP_3/DDR0_DQSP_3

DDRB_DQSN_0/DDR0_DQSN_4

DDRB_DQSP_0/DDR0_DQSP_4

DDRB_DQSN_1/DDR0_DQSN_5

DDRB_DQSP_1/DDR0_DQSP_5

DDRB_DQSN_2/DDR0_DQSN_6

DDRB_DQSP_2/DDR0_DQSP_6

DDRB_DQSN_3/DDR0_DQSN_7

DDRB_DQSP_3/DDR0_DQSP_7

NC/DDR0_PAR

NC/DDR0_ACT#

NC/DDR0_ALERT#

DDR0_VREF_CA

DDR1_VREF_CA

DDR_VTT_CTL

DRAM_RESET#

RSVD_73

BL48

BL47

BF42

BF43

BG49

BJ47

BF38

BF41

BM38

BM42

BP42

BG42

BM43

BG39

BB49

BD47

BB48

BL49

BG38

BL45

BJ46

BG48

BE45

BG45

BG47

BE47

BJ38

BB47

BE48

BM39

BG43

BJ42

BM41

BJ39

BB45

BY47

BY46

CC41

CE41

BR47

BR46

BV41

BW41

AV46

AV47

AY41

BB41

AN46

AN47

AR41

AT41

BF39

BF39,BE49 SDS CRB P.8 NC

BE49

M_0_ALERT_N

BD46

M38

C44

M38,C44,B45 SDS CRB P.8 NC

B45

M39

DK47

DDR_DRAMRST#

DDR_A_CLK# <23>

DDR_A_CLK <23>

DDR_B_CLK# <23>

DDR_B_CLK <23>

DDR_A_CKE0 <23>

DDR_A_CKE1 <23>

DDR_B_CKE0 <23>

DDR_B_CKE1 <23>

DDR_A_CS#0 <23>

DDR_A_CS#1 <23>

DDR_B_CS#0 <23>

DDR_B_CS#1 <23>

DDR_B_CA4 <23>

DDR_A_CA5 <23>

DDR_B_CA5 <23>

DDR_A_CA0 <23>

DDR_A_CA2 <23>

DDR_A_CA4 <23>

DDR_A_CA3 <23>

DDR_A_CA1 <23>

DDR_B_CA0 <23>

DDR_B_CA2 <23>

DDR_B_CA1 <23>

DDR_B_CA3 <23>

DDR_A_DQS#0 <23>

DDR_A_DQS0 <23>

DDR_A_DQS#1 <23>

DDR_A_DQS1 <23>

DDR_A_DQS#2 <23>

DDR_A_DQS2 <23>

DDR_A_DQS#3 <23>

DDR_A_DQS3 <23>

DDR_B_DQS#0 <23>

DDR_B_DQS0 <23>

DDR_B_DQS#1 <23>

DDR_B_DQS1 <23>

DDR_B_DQS#2 <23>

DDR_B_DQS2 <23>

DDR_B_DQS#3 <23>

DDR_B_DQS3 <23>

RH11 0_0201_5%@

1 2

M39 (DDR_VTT_CTL) is DDR4 System Memory Power Gate

Control Buf f er use , L PDDR4/x don' t use.

Processor EDS Rev0p7 P.118,119 #572795

SDS CRB NC

C44(DDR0_VREF_CA),B45(DDR1_VREF_CA) for DDR4 used only

LPDDR4/4x has all Vref Internal inside the DRAMS

Rev.0.91 PDG P.112 #572907

+1.1V_MEM

1 2

RH42 0_0201_5%@

RH12

470_0201_1%

1 2

DDR_DRAMRST#_R < 23,24>

1

CC740

@

0.1U_0201_10V6K

2

Security Classification

Security Classification

Security Classification

2020/10/ 01 2018/10/ 01

2020/10/ 01 2018/10/ 01

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

2020/10/ 01 2018/10/ 01

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Num ber Re v

Size Document Num ber Re v

Size Document Num ber Re v

Date : Sheet of

Date : Sheet of

2

Date : Sheet of

Compal Electronics, Inc.

P007 - ICL-U(2/13)LPDDR4/x

P007 - ICL-U(2/13)LPDDR4/x

P007 - ICL-U(2/13)LPDDR4/x

LA-H811P

LA-H811P

LA-H811P

7 100Tuesday, December 24, 2019

7 100Tuesday, December 24, 2019

7 100Tuesday, December 24, 2019

1

0.1 (X00)

0.1 (X00)

0.1 (X00)

5

D D

4

3

2

1

Memory connection refer 573975 Rev1P1

UC1C

LP4(NIL) / DDR4(NIL)

DDR_C_D0_0<24>

DDR_C_D0_1<24>

DDR_C_D0_2<24>

DDR_C_D0_3<24>

DDR_C_D0_4<24>

DDR_C_D0_5<24>

DDR_C_D0_6<24>

DDR_C_D0_7<24>

DDR_C_D1_0<24>

DDR_C_D1_1<24>

DDR_C_D1_2<24>

DDR_C_D1_3<24>

DDR_C_D1_4<24>

DDR_C_D1_5<24>

DDR_C_D1_6<24>

DDR_C_D1_7<24>

C C

B B

DDR_C_D2_0<24>

DDR_C_D2_1<24>

DDR_C_D2_2<24>

DDR_C_D2_3<24>

DDR_C_D2_4<24>

DDR_C_D2_5<24>

DDR_C_D2_6<24>

DDR_C_D2_7<24>

DDR_C_D3_0<24>

DDR_C_D3_1<24>

DDR_C_D3_2<24>

DDR_C_D3_3<24>

DDR_C_D3_4<24>

DDR_C_D3_5<24>

DDR_C_D3_6<24>

DDR_C_D3_7<24>

DDR_D_D0_0<24>

DDR_D_D0_1<24>

DDR_D_D0_2<24>

DDR_D_D0_3<24>

DDR_D_D0_4<24>

DDR_D_D0_5<24>

DDR_D_D0_6<24>

DDR_D_D0_7<24>

DDR_D_D1_0<24>

DDR_D_D1_1<24>

DDR_D_D1_2<24>

DDR_D_D1_3<24>

DDR_D_D1_4<24>

DDR_D_D1_5<24>

DDR_D_D1_6<24>

DDR_D_D1_7<24>

DDR_D_D2_0<24>

DDR_D_D2_1<24>

DDR_D_D2_2<24>

DDR_D_D2_3<24>

DDR_D_D2_4<24>

DDR_D_D2_5<24>

DDR_D_D2_6<24>

DDR_D_D2_7<24>

DDR_D_D3_0<24>

DDR_D_D3_1<24>

DDR_D_D3_2<24>

DDR_D_D3_3<24>

DDR_D_D3_4<24>

DDR_D_D3_5<24>

DDR_D_D3_6<24>

DDR_D_D3_7<24>

AK48

DDRC_DQ0_0/DDR1_DQ0_0

AK45

DDRC_DQ0_1/DDR1_DQ0_1

AK49

DDRC_DQ0_2/DDR1_DQ0_2

AG47

DDRC_DQ0_3/DDR1_DQ0_3

AK47

DDRC_DQ0_4/DDR1_DQ0_4

AG45

DDRC_DQ0_5/DDR1_DQ0_5

AG48

DDRC_DQ0_6/DDR1_DQ0_6

AG49

DDRC_DQ0_7/DDR1_DQ0_7

AJ38

DDRC_DQ1_0/DDR1_DQ1_0

AL39

DDRC_DQ1_1/DDR1_DQ1_1

AJ39

DDRC_DQ1_2/DDR1_DQ1_2

AL43

DDRC_DQ1_3/DDR1_DQ1_3

AL38

DDRC_DQ1_4/DDR1_DQ1_4

AJ42

DDRC_DQ1_5/DDR1_DQ1_5

AL42

DDRC_DQ1_6/DDR1_DQ1_6

AJ43

DDRC_DQ1_7/DDR1_DQ1_7

AB49

DDRC_DQ2_0/DDR1_DQ2_0

AB48

DDRC_DQ2_1/DDR1_DQ2_1

AE49

DDRC_DQ2_2/DDR1_DQ2_2

AE47

DDRC_DQ2_3/DDR1_DQ2_3

AE48

DDRC_DQ2_4/DDR1_DQ2_4

AB47

DDRC_DQ2_5/DDR1_DQ2_5

AB45

DDRC_DQ2_6/DDR1_DQ2_6

AE45

DDRC_DQ2_7/DDR1_DQ2_7

AD38

DDRC_DQ3_0/DDR1_DQ3_0

AD39

DDRC_DQ3_1/DDR1_DQ3_1

AE39

DDRC_DQ3_2/DDR1_DQ3_2

AE43

DDRC_DQ3_3/DDR1_DQ3_3

AE38

DDRC_DQ3_4/DDR1_DQ3_4

AD43

DDRC_DQ3_5/DDR1_DQ3_5

AD42

DDRC_DQ3_6/DDR1_DQ3_6

AE42

DDRC_DQ3_7/DDR1_DQ3_7

J48

DDRD_DQ0_0/DDR1_DQ4_0

J45

DDRD_DQ0_1/DDR1_DQ4_1

J49

DDRD_DQ0_2/DDR1_DQ4_2

G47

DDRD_DQ0_3/DDR1_DQ4_3

J47

DDRD_DQ0_4/DDR1_DQ4_4

G45

DDRD_DQ0_5/DDR1_DQ4_5

G48

DDRD_DQ0_6/DDR1_DQ4_6

E48

DDRD_DQ0_7/DDR1_DQ4_7

J38

DDRD_DQ1_0/DDR1_DQ5_0

G39

DDRD_DQ1_1/DDR1_DQ5_1

G38

DDRD_DQ1_2/DDR1_DQ5_2

G42

DDRD_DQ1_3/DDR1_DQ5_3

J39

DDRD_DQ1_4/DDR1_DQ5_4

J42

DDRD_DQ1_5/DDR1_DQ5_5

G43

DDRD_DQ1_6/DDR1_DQ5_6

J43

DDRD_DQ1_7/DDR1_DQ5_7

B43

DDRD_DQ2_0/DDR1_DQ6_0

D43

DDRD_DQ2_1/DDR1_DQ6_1

A43

DDRD_DQ2_2/DDR1_DQ6_2

C40

DDRD_DQ2_3/DDR1_DQ6_3

C43

DDRD_DQ2_4/DDR1_DQ6_4

D40

DDRD_DQ2_5/DDR1_DQ6_5

B40

DDRD_DQ2_6/DDR1_DQ6_6

A40

DDRD_DQ2_7/DDR1_DQ6_7

B35

DDRD_DQ3_0/DDR1_DQ7_0

D35

DDRD_DQ3_1/DDR1_DQ7_1

A35

DDRD_DQ3_2/DDR1_DQ7_2

D38

DDRD_DQ3_3/DDR1_DQ7_3

C35

DDRD_DQ3_4/DDR1_DQ7_4

C38

DDRD_DQ3_5/DDR1_DQ7_5

B38

DDRD_DQ3_6/DDR1_DQ7_6

A38

DDRD_DQ3_7/DDR1_DQ7_7

ICL-U_BGA1526

@

3 of 19

LP4(NIL) / DDR4(NIL)

DDRC_CLK_N/DDR1_CLK_N_0

DDRC_CLK_P/DDR1_CLK_P_0

DDRD_CLK_N/DDR1_CLK_N_1

DDRD_CLK_P/DDR1_CLK_P_1

DDRC_CKE0/DDR1_CKE0

DDRC_CKE1/NC

DDRD_CKE0/NC

DDRD_CKE1/DDR1_CKE1

DDRC_CS_0/DDR1_CS#0

DDRC_CS_1/NC

DDRD_CS_0/NC

DDRD_CS_1/DDR1_CS#1

DDRD_CA4/DDR1_BA0

NC/DDR1_BA1

DDRC_CA5/DDR1_BG0

NC/DDR1_BG1

NC/DDR1_MA0

NC/DDR1_MA1

DDRD_CA5/DDR1_MA2

NC/DDR1_MA3

NC/DDR1_MA4

DDRC_CA0/DDR1_MA5

DDRC_CA2/DDR1_MA6

DDRC_CA4/DDR1_MA7

DDRC_CA3/DDR1_MA8

DDRC_CA1/DDR1_MA9

NC/DDR1_MA10

NC/DDR1_MA11

NC/DDR1_MA12

DDRD_CA0/DDR1_MA13

DDRD_CA2/DDR1_MA14WE#

DDRD_CA1/DDR1_MA15CAS#

DDRD_CA3/DDR1_MA16RAS#

NC/DDR1_ODT_0

NC/DDR1_ODT_1

DDRC_DQSN_0/DDR1_DQSN_0

DDRC_DQSP_0/DDR1_DQSP_0

DDRC_DQSN_1/DDR1_DQSN_1

DDRC_DQSP_1/DDR1_DQSP_1

DDRC_DQSN_2/DDR1_DQSN_2

DDRC_DQSP_2/DDR1_DQSP_2

DDRC_DQSN_3/DDR1_DQSN_3

DDRC_DQSP_3/DDR1_DQSP_3

DDRD_DQSN_0/DDR1_DQSN_4

DDRD_DQSP_0/DDR1_DQSP_4

DDRD_DQSN_1/DDR1_DQSN_5

DDRD_DQSP_1/DDR1_DQSP_5

DDRD_DQSN_2/DDR1_DQSN_6

DDRD_DQSP_2/DDR1_DQSP_6

DDRD_DQSN_3/DDR1_DQSN_7

DDRD_DQSP_3/DDR1_DQSP_7

NC/DDR1_PAR

NC/DDR1_ACT#

NC/DDR1_ALERT#

Y48

Y47

M43

M42

U45

V46

M41

P43

V42

V39

Y39

T39

T38

T42

R45

N47

P42

Y49

U48

Y45

U47

R49

U49

M47

M45

R47

P39

N46

R48

Y41

V41

Y42

V47

V43

V38

AH46

AH47

AJ41

AL41

AC47

AC46

AE41

AD41

H47

H46

G41

J41

C42

D42

D36

C36

P38

M48

M49

P38,M48 SSD CRB NC

M_1_ALERT_N

RH13 0_0201_5%@

DDR_C_CLK# <24>

DDR_C_CLK <24>

DDR_D_CLK# <24>

DDR_D_CLK <24>

DDR_C_CKE0 <24>

DDR_C_CKE1 <24>

DDR_D_CKE0 <24>

DDR_D_CKE1 <24>

DDR_C_CS#0 <24>

DDR_C_CS#1 <24>

DDR_D_CS#0 <24>

DDR_D_CS#1 <24>

DDR_D_CA4 <24>

DDR_C_CA5 <24>

DDR_D_CA5 <24>

DDR_C_CA0 <24>

DDR_C_CA2 <24>

DDR_C_CA4 <24>

DDR_C_CA3 <24>

DDR_C_CA1 <24>

DDR_D_CA0 <24>

DDR_D_CA2 <24>

DDR_D_CA1 <24>

DDR_D_CA3 <24>

DDR_C_DQS#0 <24>

DDR_C_DQS0 <24>

DDR_C_DQS#1 <24>

DDR_C_DQS1 <24>

DDR_C_DQS#2 <24>

DDR_C_DQS2 <24>

DDR_C_DQS#3 <24>

DDR_C_DQS3 <24>

DDR_D_DQS#0 <24>

DDR_D_DQS0 <24>

DDR_D_DQS#1 <24>

DDR_D_DQS1 <24>

DDR_D_DQS#2 <24>

DDR_D_DQS2 <24>

DDR_D_DQS#3 <24>

DDR_D_DQS3 <24>

12

A A

Security Classification

Security Classification

Security Classification

2020/10/ 01 2018/10/ 01

2020/10/ 01 2018/10/ 01

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

2020/10/ 01 2018/10/ 01

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Num ber Re v

Size Document Num ber Re v

Size Document Num ber Re v

Date : Sheet of

Date : Sheet of

2

Date : Sheet of

Compal Electronics, Inc.

P008 - ICL-U(3/13)LPDDR4/x

P008 - ICL-U(3/13)LPDDR4/x

P008 - ICL-U(3/13)LPDDR4/x

LA-H811P

LA-H811P

LA-H811P

8 100Tuesday, December 24, 2019

8 100Tuesday, December 24, 2019

8 100Tuesday, December 24, 2019

1

0.1 (X00)

0.1 (X00)

0.1 (X00)

5

BOOT HALT

SPI0_MOSI(NO INTERNAL PU/PD)

0 = Enable

1 = Disable

RH643 100K_0201_5%

1 2

RH641 4.7K_0201_5%@

D D

1 2

CONSENT STRAP

SPI0_IO2(NO INTERNAL P U/PD)

0 = Enable

1 = Disable

RH141 100K_0201_5%

1 2

RH142 4.7K_0201_5%@

1 2

+V3.3A_1.8A_PCH_SPI +V3.3A_1.8A_PCH_SPI+V3.3A_1.8A_PCH_SPI

4

A0 PERSONALITY STRAP

SPI0_I O3

0 = Enable

1 = Disable

RH635 100K_0201_5%

1 2

RH636 100K_0201_5%@

1 2

3

TLS CONFIDENTIALITY

GPP_C2/SMBALERT#(INTERNAL PD 20K)

0 = TLS CONFIDENTIALITY DISABLE

1 = TLS CONFIDENTIALITY ENABLE

GPP_C2

RH692 4.7K_0201_5%

1 2

2

ESPI OR EC LESS

GPP_C5 (Internal 20 K internal Pull Down): SML0ALERT#

0 = Enable eSPI. (Default)

1 = Disable eSPI.

RH666 4.7K_0201_5%@

GPP_C5SOC_SPI_0_D2 SOC_SPI_0_D3SOC_SPI_0_D0

RH98 20K_0 201_5%@

1 2

1 2

+3V_PRIM+3V_PRIM

1

SOC_SPI_0_CLK

SOC_SPI_0_D0

SOC_SPI_0_D1

SOC_SPI_0_D2

SOC_SPI_0_D3

SOC_SPI_0_CS#0

SOC_SPI_0_CS#1

SOC_SPI_0_CS#2

SECURE_BIOS_BIO

RH687 100K_0201_5%

MIPI60_SPI0_MOSI<7 9>

MIPI60_SPI0_IO2<79>

1 2

1 2

MIPI60@

1 2

MIPI60@

RH6401K_0201_5%

RH6341K_0201_5%

SOC_SPI_0_CLK

SOC_SPI_0_D0

SOC_SPI_0_D2

SOC_SPI_0_CLK_R

RH719 4.99_0201_1%

SOC_SPI_0_CLK_R<66>

SOC_SPI_0_D0_R<66>

SOC_SPI_0_D1_R<66>

SOC_SPI_0_D0_R

SOC_SPI_0_D1_R

SOC_SPI_0_D2_R

SOC_SPI_0_D3_R

SOC_SPI_0_CS#0_R

SOC_SPI_0_CS#1_R

1 2

RH720 4.99_0201_1%

1 2

RH721 4.99_0201_1%

1 2

RH722 4.99_0201_1%

1 2

RH723 4.99_0201_1%

1 2

RH736 0_0201_5%@

1 2

RH735 0_0201_5%@

1 2

SOC_SPI_0_CS#2<66>

DVT2_04

RH750 0_0201_5%

S_BIO<39>

1 2

NO support C-Link

C C

SPI_0_D0_ROM

SPI_0_CLK_ROM

SPI_0_D1_ROM

SPI_0_D2_ROM

SPI_0_D3_ROM

Closed to ROM

RH23 49.9_02 01_1%

1 2

RH24 49.9_02 01_1%

1 2

RH25 49.9_02 01_1%

1 2

RH26 49.9_02 01_1%

1 2

RH27 49.9_02 01_1%

1 2

SOC_SPI_0_D0_R

SOC_SPI_0_CLK_R

SOC_SPI_0_D1_R

SOC_SPI_0_D2_R

SOC_SPI_0_D3_R

Serial Peripheral Interface (SPI) Topology Guidelines

PCH SPI

NPI pop D20

MP pop RC745

DVT1_23

PVT_05

D20

SPI ROM ( 32MByte )

ROM is Quad SPI

SOC_SPI_0_CS#0_R

SPI_0_D1_ROM SPI_0_D3_ROM

SPI_0_D2_ROM SPI_0_CLK_ROM

UH8

1

CS#

2

DO

3

IO2

4

GND

ThemalPad

W25Q256JVEIQ_WSON8_8X6

8

VCC

7

IO3

6

CLK

SPI_0_D0_ROM

5

DI

9

+3V_SPI

PVT_04

B B

A A

RB751S40T1G_SOD523-2

1

CH35

0.1U_0201_10V6K

2

@

21

@

12

RC7450_040 2_5%

WLAN--->

SSD-->

Card Reader--->

+3V_PRIM

CLK_PCIE_N0<52>

CLK_PCIE_P0<52>

RH40 10K_0 201_5%DAR@

1 2

+3VS

CLKREQ_PCIE#0<52>

CLK_PCIE_N1<67>

CLK_PCIE_P1<67>

RH727 10K_0201_5%

1 2

+3VS

CLKREQ_PCIE#1<67>

CLK_PCIE_N4<70>

CLK_PCIE_P4<70>

RH39 10K_0 201_5%

1 2

+3VS

CLKREQ_PCIE#4<70>

UC1E

DB42

SPI0_CLK

DD43

Strap Pin

SPI0_MOSI

DF43

SPI0_MISO

DF42

Strap Pin

SPI0_IO2

DD41

Strap Pin

SPI0_IO3

DB43

SPI0_CS0#

DF41

SPI0_CS1#

DB41

SPI0_CS2#

DV16

GPP_E11/SPI1_CLK/BK1/SBK1

DT16

GPP_E13/SPI1_MOSI/BK3/SBK3

DU18

GPP_E12/SPI1_MISO/BK2/SBK2

DT18

GPP_E1/SPI1_IO2

DW18

GPP_E2/SPI1_IO3

DW16

GPP_E10/SPI1_CS_N/BK0/SBK0

DU16

GPP_E8/SATALED#/SPI1_CS1#

DV19

CL_CLK

DW19

CL_DATA

DT19

CL_RST#

ICL-U_BGA1526

@

TPM

JSPI

SOC_SPI_0_CS#1_R

SOC_SPI_0_D0_R

SOC_SPI_0_D1_R

SOC_SPI_0_CLK_R

SOC_SPI_0_CS#0_R

PROM_BIOS_R<78>

SOC_SPI_0_D3_R

+3V_SPI

ACES_50521-01041-P01_10P

Follow Pebble Creek MLK

DK33

DN34

DP34

DP36

DN40

JSPI1

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

CONN@

UC1J

CJ3

CLKOUT_PCIE_N0

CJ5

CLKOUT_PCIE_P0

GPP_D5/SRCCLKREQ0#

CL2

CLKOUT_PCIE_N1

CL1

CLKOUT_PCIE_P1

GPP_D6/SRCCLKREQ1#

CL3

CLKOUT_PCIE_N2

CL5

CLKOUT_PCIE_P2

GPP_D7/SRCCLKREQ2#

CK3

CLKOUT_PCIE_N3

CK4

CLKOUT_PCIE_P3

GPP_D8/SRCCLKREQ3#

CJ2

CLKOUT_PCIE_N4

CJ1

CLKOUT_PCIE_P4

GPP_H10/SRCCLKREQ4#

ICL-U_BGA1526

@

SMBUS

SPI 0

SML 0

GPP_C6/SML1CLK/SUSWARN_N/SUSPWRDNACK

SML1

SPI 1

eSPI

MLINK

5 of 19

11

G1

12

G2

GPP_H11/SRCCLKREQ5#

RTC

XTAL

10 of 19

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C7/SML1DATA/SUSACK#

GPP_A5/ESPI_CLK

GPP_A0/ESPI_IO0

GPP_A1/ESPI_IO1

GPP_A2/ESPI_IO2

GPP_A3/ESPI_IO3

GPP_A4/ESPI_CS#

GPP_A6/ESPI_RESET#

RTCX1

RTCX2

RTCRST#

SRTCRST#

GPD8/SUSCLK

XTAL_IN

XTAL_OUT

XCLK_BIASREF

CF5

CF3

DP40

DL48

DL49

DT47

DK46

DF49

DW8

DU8

DU6

CLKOUT_PCIE_N5

CLKOUT_PCIE_P5

DK27

DP24

GPP_C2

DL24

SML0_SMBCLK

DK24

SML0_SMBDATA

DJ24

GPP_C5

DP22

SML1_SMBCLK

DN22

SML1_SMBDATA

DL22

ESPI_CLK

CR47

ESPI_IO0_R

CN45

ESPI_IO1_R

CN48

ESPI_IO2_R

CN49

ESPI_IO3_R

CN47

ESPI_CS#

CT45

ESPI_RESET#

CR46

PCH_RTCX1

PCH_RTCX2

PCH_RTCRST#

SRTCRST#

SUSCLK

XTAL_38P4M_IN_CPU

XTAL_38P4M_OUT_CPU

CLK_BIASREF

SMB_CLK <79>

SMB_DATA <79>

SML0_SMBCLK <46,48>

SML0_SMBDATA <46,48>

SML1_SMBCLK <42,44,46,48>

SML1_SMBDATA <42,44,46,48>

RC569 49.9_0201_1%

RC336 10_0201_1%

1 2

RC367 10_0201_1%

1 2

RC368 10_0201_1%

1 2

RC369 10_0201_1%

1 2

XTAL_38P4M_IN

XTAL_38P4M_OUT

10P_0201_50V8J

PCH_RTCRST# <63,79>

SUSCLK <52,67>

RH14 0_0201 _5%

1 2

RH15 0_0201 _5%

1 2

RH475 60.4_0201_1%

1 2

MIPI60

BB_L&BB_R

(For support Vpro)

BB_L&BB_R

12

CH10

PD_L&PD_R

ESPI_CLK_5105<58,79>

ESPI_IO0 <58,79>

ESPI_IO1 <58,79>

ESPI_IO2 <58,79>

ESPI_IO3 <58,79>

ESPI_CS# <5 8,79>

ESPI_RESET# <58,79>

RH17 200K _0201_1%

1 2

YH1

123

2

38.4MHZ_10PF_8Y38420005

1

Intel SPEC :

CL = Specified Crystal Capacitive Load = 10 pF

Series Resistance < or = 30 Ω

Frequency Tolerance < or 100 PPM

Aging ± 3 PPM

SUSCLK

1

CH49

@EMI@

0.1U_0201_10V6K

2

XTAL_38P4M_IN

XTAL_38P4M_OUT

4

EMI Request

SOC_SPI_0_CLK

12

RC734

33_0201_5%

1

CC659

33P_0201_50V8J

2

ESPI 1.8V

@EMI@

@EMI@

2

CH11

10P_0201_50V8J

1

SML0_SMBDATA

SML0_SMBCLK

SML1_SMBCLK

SML1_SMBDATA

ESPI_CS#

ESPI_RESET#

SMB_CLK

CC655 33P_0201_50V8J

SML0_SMBCLK

CC656 33P_0201_50V8J

SML1_SMBCLK

CC657 33P_0201_50V8J

ESPI_CLK_5105

CC658 33P_0201_50V8J

PCH_RTCX2

PCH_RTCX1

15P_0201_50V8J

+RTCVCC_R

1U_0201_6.3V6K

1 2

RH573 20K_0201_5%

1 2

RH572 20K_0201_5%

1U_0201_6.3V6K

PDG_An RC delay circuit with a t i me delay i n t he

range of 18– 25 ms should be provided. The circuit

should be connected to VCCRTC.

1

CH12

2

1

CH47

2

1

CH46

2

RH16 10M_0201_1%

32.768KHZ_12.5PF_9H03200042

CRB XTAL ESR = 50K MAX

RF Request

@RF@

1 2

@RF@

1 2

@RF@

1 2

@RF@

1 2

1 2

YC1

1 2

PCH_RTCRST#

SRTCRST#

1 2

1 2

1 2

1 2

1 2

1 2

PCH_RTCX2_R

RH144499_0201_1%

RH143499_0201_1%

RH6061K_0201_5%

RH6071K_0201_5%

RC71275K_0201_1% @

RC71175K_0201_1%

+3V_PRIM

RH637

0_0201_5%

1 2

1

CH13

15P_0201_50V8J

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE C USTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

2020/10/01 2018/10/01

2020/10/01 2018/10/01

2020/10/01 2018/10/01

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

P009 - ICL-U(4/13)SPI,SMB,ESPI

P009 - ICL-U(4/13)SPI,SMB,ESPI

P009 - ICL-U(4/13)SPI,SMB,ESPI

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

LA-H811P

LA-H811P

LA-H811P

Date : Sheet of

Date : Sheet of

Date : Sheet of

1

9 100Tuesday, December 24, 2019

9 100Tuesday, December 24, 2019

9 100Tuesday, December 24, 2019

0.1 (X00)

0.1 (X00)

0.1 (X00)

5

4

3

2

1

NO REBOOT

+3V_PRIM

RC682 10K_0201_5%@

1 2

RH646 100K_0201_5%@

1 2

D D

+3VS

RC222 49.9K_0201_1%

12

RC223 49.9K_0201_1%

12

RC655 49.9K_0201_1%

12

RC656 49.9K_0201_1%

12

RH713 100K_0201_5%@

1 2

RC339 10K_0201_5%@

1 2

RC338 10K_0201_5%@

1 2

RC748 10K_0201_5%@

1 2

RC749 10K_0201_5%

1 2

check 1.8VS or 3.3VS

RC254 0_0201_5%@

TPM_PIRQ#_R<66>

1 2

RC255 0_0201_5%@

1 2

MEDIACARD_IRQ#

PCH_TBT_PERST#

UART_2_CRXD_DTXD

UART_2_CTXD_DRXD

UART_2_CRTS_DCTS

UART_2_CCTS_DRTS

PCH_TBT_PERST#

TPM_GPP_B17_SMI#_NMI

TPM_PIRQ#

P_SENSOR_PWR_SAVE#

P_DET#

TPM_GPP_B17_SMI#_NMI

TPM_PIRQ#

DVT2_14

For TS lid open reques t

RW53 10K_0201_5%@

1 2

RH300 10K_0201_5%

1 2

RH688 100K_0201_5%@

C C

1 2

WAKE_BT

PCH_TBT_PERST#

HDA_BIT_CLK

DVT1_05 : CAM_DET# pull high 100k ohm

+3VS

RH747 100K_0201_5%

1 2

B B

PVT_17

RH11475K_0201_5% CNV@

12

RH72810K_0201_5% @

12

SPCE p.30 PU or PD 100K-180K

PDG define only JFP need to PD 10K.

HDA for AUDIO

HDA_BIT_CLK_R<56>

HDA_SYNC_R<56>

HDA_SDOUT_R<56>

A A

1

2

@RF@

GPP_B18/GSPI0_MOS (Internal 20 K Pull Down)

0 = REBOOT ENABLED

1 = NO REBOOT

NRB_BIT

RH621 4.7K_0201_5%@

1 2

Check follow CRB 573129

SSD_PWR_EN<67>

BT_RADIO_DIS#<52,58>

MEDIACARD_IRQ#_R<70>

P_SENSOR_PWR_SAVE#<39>

TS

TP

CAM_DET#

DVT1_36, DVT1_40,DVT1_69

CNV_RF_RESET#

CLKREQ_CNV#

1

CH50

CH51

2

56P_0201_25V8J

56P_0201_25V8J

@RF@

RH751 0_0201_5%@

RH645 0_0201_5%@

SPKR<56>

Remove 0 ohm

PCH_3.3V_TS_EN<71>

P_DET#<3 9>

PCH_TBT_PERST#<46,48>

SBIOS_TX<7 9>

PANEL_BKLEN<6,38>

UART_2_CRXD_DTXD< 79>

UART_2_CTXD_DRXD< 79>

UART_2_CRTS_DCTS<79>

UART_2_CCTS_DRTS<79>

I2C_0_SDA<38>

I2C_0_SCL<38>

I2C_1_SDA<63>

I2C_1_SCL<63>

DVT1_69

RH113 33_0201_1%

RH111 33_0201_1%

RH112 33_0201_1%

1

CH40

2

@

22P_0201_50V8J

PVT_09

0_0201_5%

1 2

1 2

1 2

1 2

1 2

PCH_TBT_PERST#

RH732 0_0201_5%@

RH715 0_0201_5%@

CNV_RF_RESET#<52>

+3VS

TPM_GPP_B17_SMI#_NMI

TPM_PIRQ#

P_DET#

GPP_B23

1 2

UART_2_CRXD_DTXD

UART_2_CTXD_DRXD

UART_2_CRTS_DCTS

UART_2_CCTS_DRTS

@

12

HDA_SDIN0<56>

PCM_CLK<52>

1 2

PCM_SYNC<52>

PCM_IN<5 2>

PCM_OUT<52>

CAM_DET#<39, 58>

TS_RST#<38>

CLKREQ_CNV#<52>

HDA_BIT_CLK

HDA_SYNC

HDA_SDOUT

CPUNSSC CLOCK FREQ

GPP_B23 (Internal 20 K Pull Down)

0 = 38.4 MHz clock (direct from crystal) (default)

1 = 19.2 MHz clock (from internal divider)

GPP_B23

RH647 4.7K_0201_5%@

1 2

UC1F

CH48

NRB_BIT

MEDIACARD_IRQ#

ENBKL_TS

GPP_H8

RH714

GPP_H9

HDA_BIT_CLK

HDA_SYNC

HDA_SDOUT

HDA_SDIN0

GPP_A23

CNV_RF_RESET#

GPP_S4

RH7160_0201_5% @

12

GPP_S5

Reserved for debug

GPP_B16/GSPI0_CLK

CF48

Strap Pin

GPP_B18/GSPI0_MOSI

CF47

GPP_B17/GSPI0_MISO

CH49

GPP_B15/GSPI0_CS0#

CH47

GPP_B14/SPKR/TIME_SYNC1/GSPI0_CS1#

CL47

GPP_B20/GSPI1_CLK

CK47

GPP_B22/GSPI1_MOSI

CK46

GPP_B21/GSPI1_MISO

CH45

GPP_B19/GSPI1_CS0#

CL48

Strap Pin

GPP_B23/SML1ALERT#/PCHHOT#/GSPI1_CS1#

DP21

GPP_C8/UART0_RXD

DK21

GPP_C9/UART0_TXD

DL21

GPP_C10/UART0_RTS#

DJ22

GPP_C11/UART0_CTS#

DT22

GPP_C20/UART2_RXD

DW22

GPP_C21/UART2_TXD

DV22

GPP_C22/UART2_RTS#

DU22

GPP_C23/UART2_CTS#

DT24

GPP_C16/I2C0_SDA

DT23

GPP_C17/I2C0_SCL

DW23

GPP_C18/I2C1_SDA

DU23

GPP_C19/I2C1_SCL

DU41

GPP_H4/I2C2_SDA

DV41

GPP_H5/I2C2_SCL

DW41

GPP_H6/I2C3_SDA

DT41

GPP_H7/I2C3_SCL

DT40

GPP_H8/I2C4_SDA/CNV_MFUART2_RXD

DW40

GPP_H9/I2C4_SCL/CNV_MFUART2_TXD

ICL-U_BGA1526

@

UC1G

CY46

GPP_R0/HDA_BCLK/I2S0_SCLK

CV49

GPP_R1/HDA_SYNC/I2S0_SFRM

CY47

GPP_R2/HDA_SDO/I2S0_TXD

CV45

GPP_R3/HDA_SDI0/I2S0_RXD

DA47

GPP_R4/HDA_RST#

DP33

GPP_D19/I2S_MCLK

DC45

GPP_A23/I2S1_SCLK

DA49

GPP_R5/HDA_SDI1/I2S1_SFRM

DA45

GPP_R6/I2S1_TXD

DA48

GPP_R7/I2S1_RXD

CT49

GPP_A7/I2S2_SCLK

CT48

GPP_A8/I2S2_SFRM/CNV_RF_RESET#

CV47

GPP_A10/I2S2_RXD

CT47

GPP_A9/I2S2_TXD/MODEM_CLKREQ

CY39

GPP_S0/SNDW1_CLK

CY38

GPP_S1/SNDW1_DATA

DB39

GPP_S2/SNDW2_CLK

DD38

GPP_S3/SNDW2_DATA

DF38

GPP_S4/SNDW3_CLK/DMIC_CLK1

DD39

GPP_S5/SNDW3_DATA/DMIC_DATA1

ICL-U_BGA1526

@

FLASH DESCRIPTOR SECURITY OVERRIDE

GPP_R2/HDA_SDO (Internal 20 K Pull Down)

0 = ENABLE (DEFAULT)

1 = DISABLE (ME can update)

ME_FWP<58>

TOP SWAP OVERRIDE

GPP_B14 / SPKR (Internal 20 K Pull Down)

0 = Disable " Top Swap" mode. (Default)

+3V_PRIM +3V_PRIM

@

1 2

RH218 0_0201_5%

1 = Enable "Top Swap" mode.

RH667 8.2K_0201_5%@

SPKR

GPP_D15/ISH_UART0_RTS_N/GSPI2_CS1_N/IMGCLKOUT5

GPP_D16/ISH_UART0_CTS_N/CNV_WCEN

UART

GSPI

UART

I2C

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

I2C / ISH

6 of 19

GPP_H1/SD_PWR_EN_N/CNV_BT_I2S_SDO

7 of 19

1 2

RH217 1K_0201_1%

GPP_B9/I2C5_SDA/ISH_I2C2_SDA

GPP_B10/I2C5_SCL/ISH_I2C2_SCL

ISH

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G0/SD_CMD

SD3.0

GPP_H0/CNV_BT_I2S_SDO

GPP_S6/SNDW4_CLK/DMIC_CLK0

GPP_S7/SNDW4_DATA/DMIC_DATA0

AUDIO

1 2

GPP_D13/ISH_UART0_RXD

GPP_D14/ISH_UART0_TXD

GPP_B5/ISH_I2C0_SDA

GPP_B6/ISH_I2C0_SCL

GPP_B7/ISH_I2C1_SDA

GPP_B8/ISH_I2C1_SCL

GPP_D0/ISH_GP0

GPP_D1/ISH_GP1

GPP_D2/ISH_GP2

GPP_D3/ISH_GP3

GPP_D17/ISH_GP4

GPP_D18/ISH_GP5

GPP_E15/ISH_GP6

GPP_E16/ISH_GP7

GPP_G7/SD_WP

SD3_RCOMP

SNDW_RCOMP

CE46

CC48

CC49

CC47

CF45

CC45

CF49

CE47

DK38

DG38

CJ43

DG36

DG34

CV38

GPP_G6/SD_CLK

GPP_G5/SD_CD#

RF Request. Place near CPU side

HDA_SDIN0

HDA_SDOUTME_FWP_PCH

SML0B_SMBDATA

DV33

SML0B_SMBCLK

DW33

DT33

DU33

SML0BALERT#

SIO_EXT_WAKE# SIO_EXT_WAKE#

DK22

DW24

DV24

DU24

CN43

CN42

ISH_I2C_1_SDA

CN41

ISH_I2C_1_SCL

CL43

CL41

CJ39

DU36

DV36

ACC1_INT2#

DW36

DT36

ISH_TABLE_MODE#

DU34

P_INT#

DW34

DT14

DU14

ISH_GP2 for 2nd Acc elerometer INT2#

ISH_GP4 for ISH_TABLE_MODE#

ISH_GP5 for P_INT#

ISH_GP7 for A LS_ALERT#

DDR_CHA_EN

DDR_CHB_EN

CNVI_EN#_R

SD3_RCOMP

WOV_DMIC_CLK0

WOV_DMIC_DATA0

SNDW_RCOMP

RH729 0_0201_5%@

1 2

RC20 200_0201_1%

RH705 33_0201_5%@

1 2

RH706 33_0201_5%@

1 2

RC16 200_0201_1%

1 2

@RF@

CC727 2.2P_0201_50V8B

1 2

SML0B_SMBDATA< 58>

SML0B_SMBCLK <58>

RC727 0_0201_5%@

1 2

SIO_EXT_WAKE#<58>

DBC_EN <38>

WAKE_BT <52>

DVT1_25 : reserve GPIO between WLAN and CPU

ISH_I2C_1_SDA <39,63>

ISH_I2C_1_SCL< 39,63>

ACC1_INT2# <63 >

ISH_TABLE_MODE# <58>

P_INT# <39>

ALS_ALERT# <39>

AUD_PWR_EN <7 1>

SPK2_DET# <57>

SPK1_DET# <57>

HOST_SD_WP# <70>

1 2

EC

ALS/G-sensor/P-se nsor

DVT1_11,DVT1_79

CNVI_EN# <52,71>

Intel DMIC for WOV function

1

CC654

@

27P_0201_25V8

2

PCH_DMIC_CLK12 <39>

PCH_DMIC_DATA12 <39>

ISH_I2C_1_SDA

ISH_I2C_1_SCL

HOST_SD_WP#

SML0B_SMBDATA

SML0B_SMBCLK

ISH_TABLE_MODE#

0= table mode

1= exit table mode

P_INT#

ACC1_INT2#

P_INT#

ACC1_INT2#

ALS_ALERT#

DDR_CHA_EN

DDR_CHB_EN

DDR_CHA_EN

DDR_CHB_EN

SPK1_DET#

SPK2_DET#

RC667 1K_0201_5%

RC668 1K_0201_5%

RC717 10K_0201_5%

RC671 10K_0201_5%

RC672 1K_0201_5%