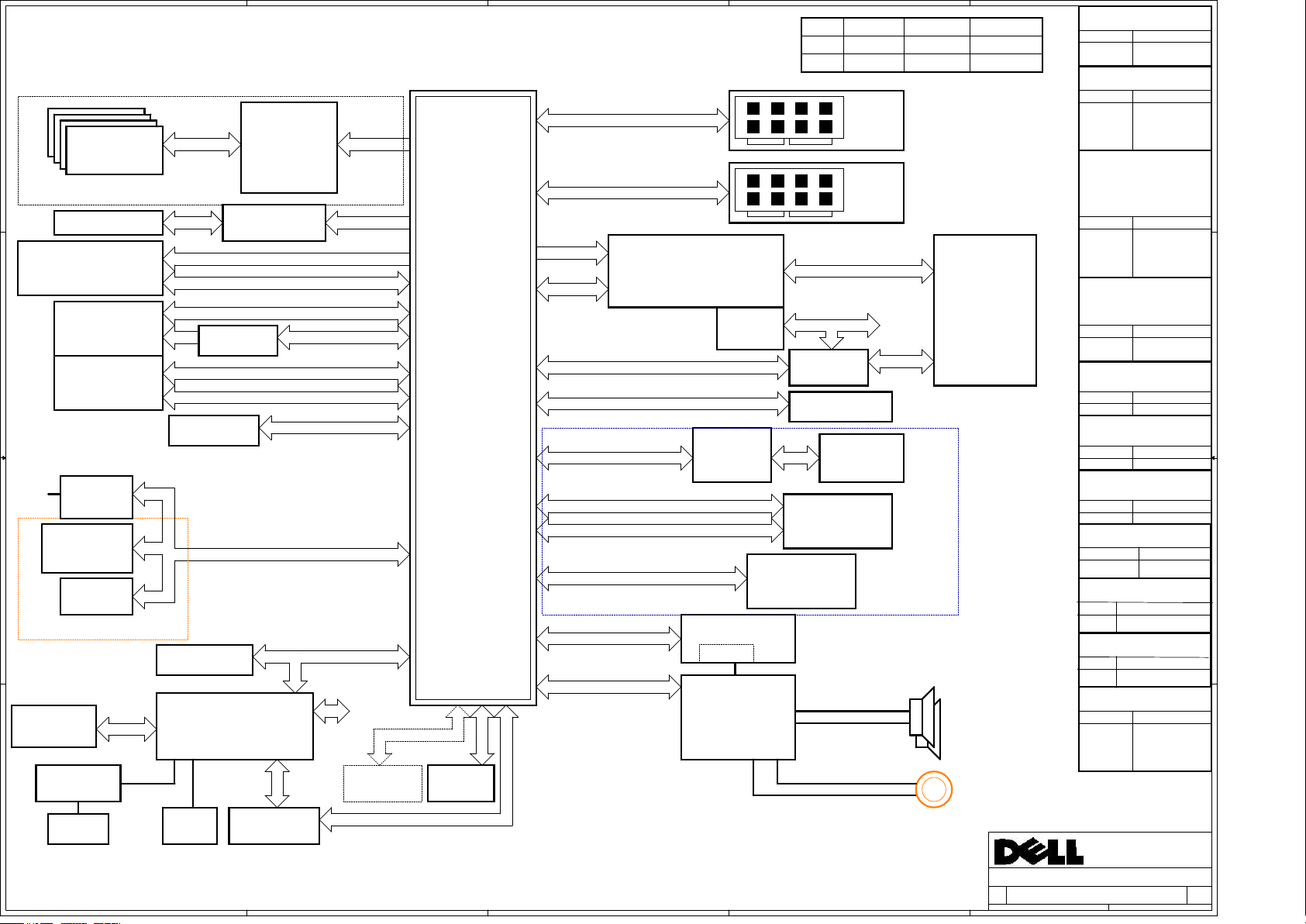

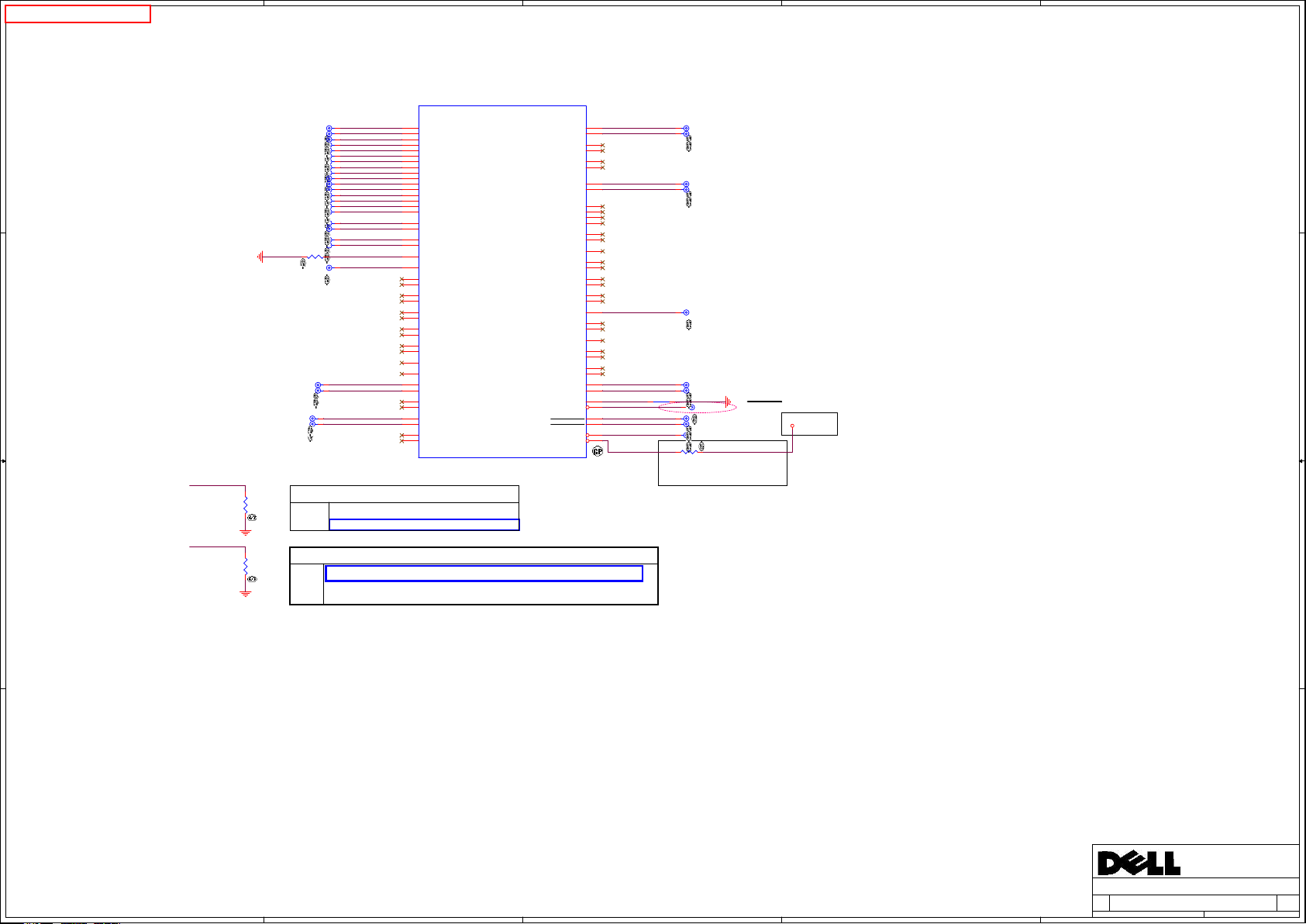

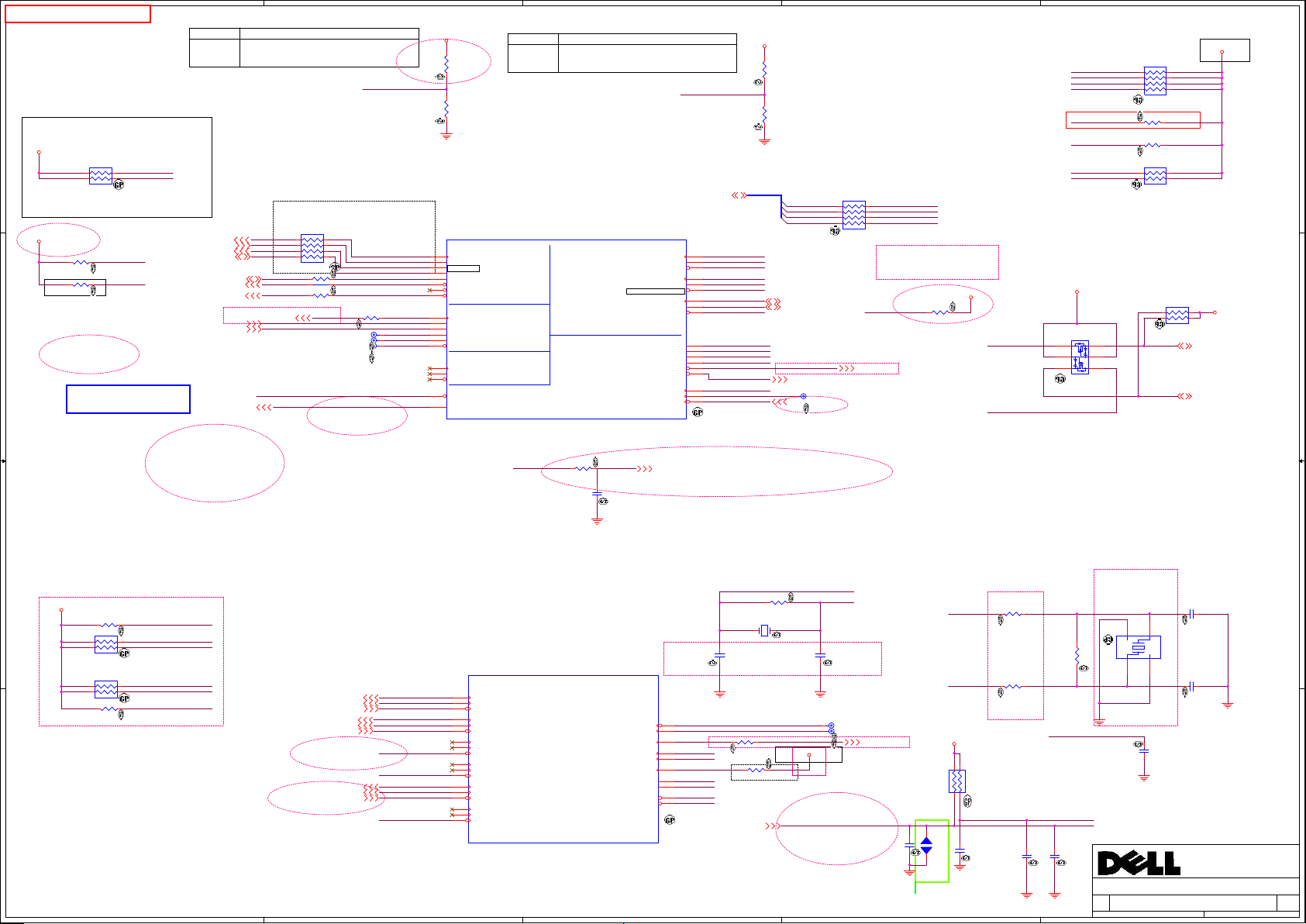

Dell Inspiron 5379, Inspiron 5579, Inspiron 7773 Schematics

5

D D

4

3

2

1

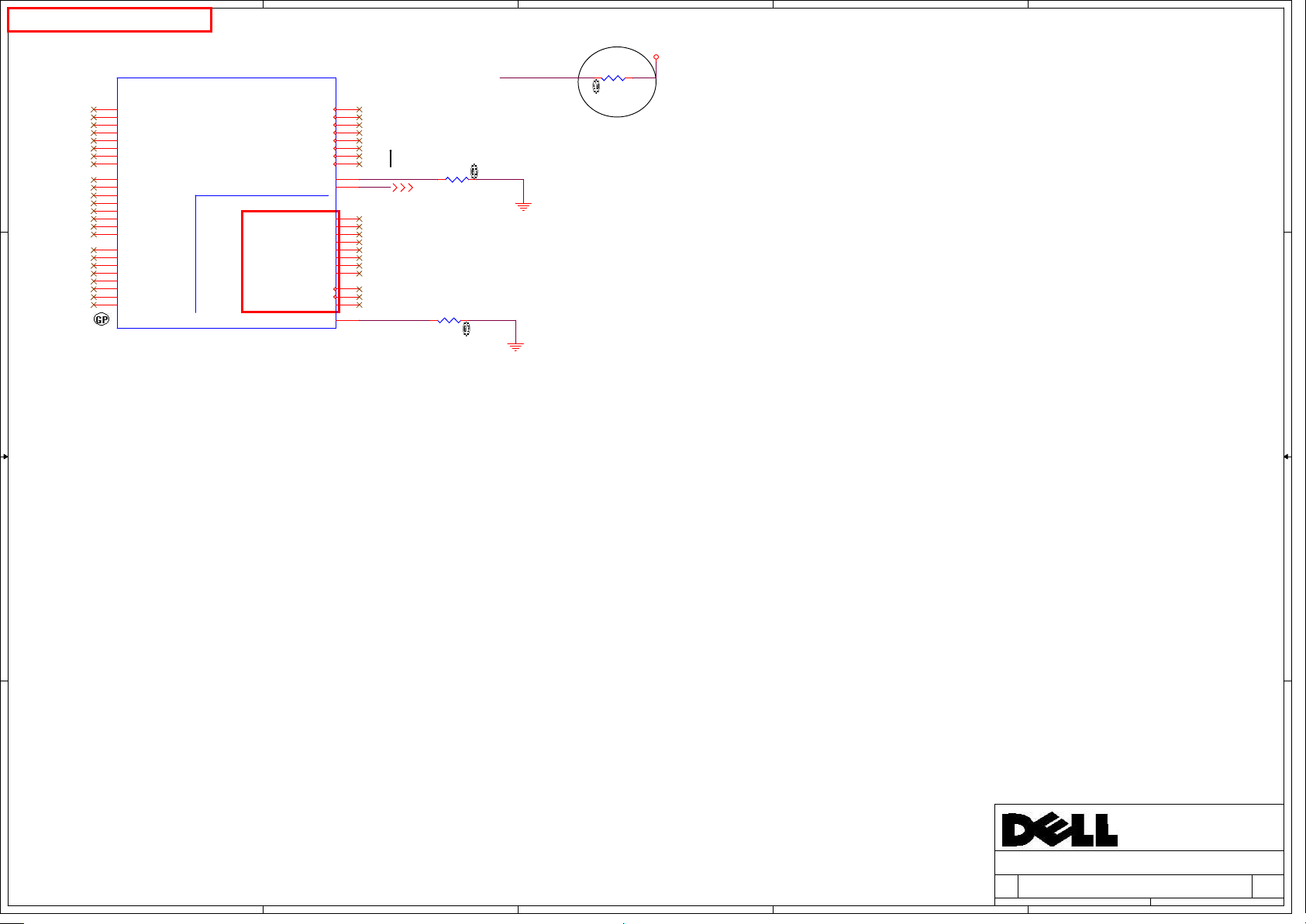

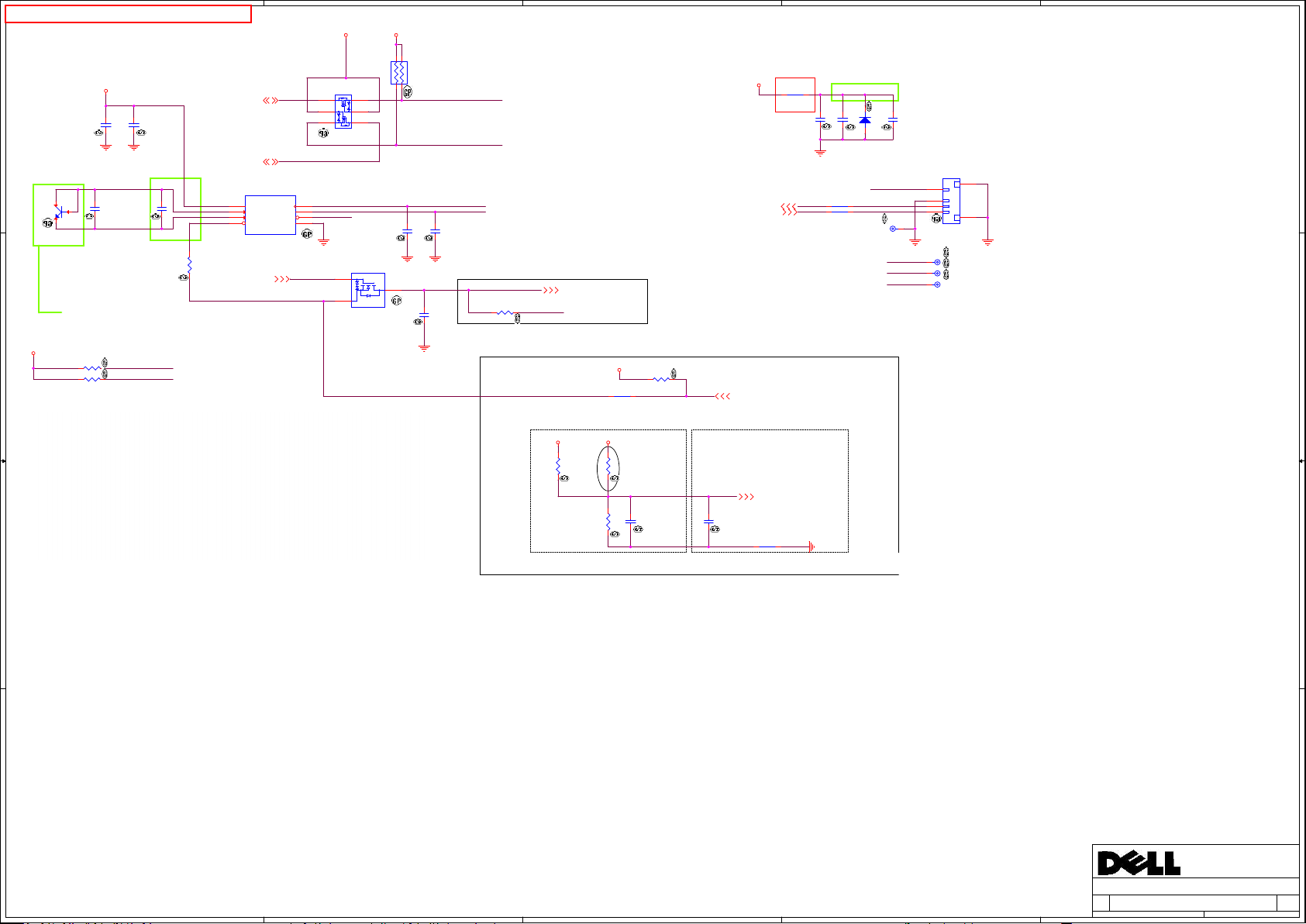

Starlord KBL_Refresh Schematics

KabyLake-R

C C

2017-05-25

REV : A00

B B

DY : None Installed

A A

UMA: UMA only installed

OPS: DISCRTE OPTIMUS installed

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

W

W

W

i

i

i

stron Corporation

stron Corporation

stron Corporation

2

2

2

1

1

1

F, 88, Sec.1, Hsin T ai Wu Rd., Hsichih,

F, 88, Sec.1, Hsin T ai Wu Rd., Hsichih,

F, 88, Sec.1, Hsin T ai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C .

Taipei Hsien 221, Taiwan, R.O.C .

Taipei Hsien 221, Taiwan, R.O.C .

T

tle

Title

Title

i

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A

A

A

3

3

3

Monday, August 2 8, 2017

Monday, August 2 8, 2017

Monday, August 2 8, 2017

Date: Sheet

Date: Sheet

Date: Sheet

C

C

C

er Page

er Page

er Page

ov

ov

ov

S

S

S

t

t

t

arlord KBL-R

arlord KBL-R

arlord KBL-R

1 1

1 1

1 1

1

o

o

o

f

f

f

A

A

A

0

0

0

06

06

06

0

0

0

Project code: 4PD0CF010001(SL13_R)

WWW.AliSaler.Com

5

4PD0CG010001(SL15_R)

4PD0CH010001(SL17_B)

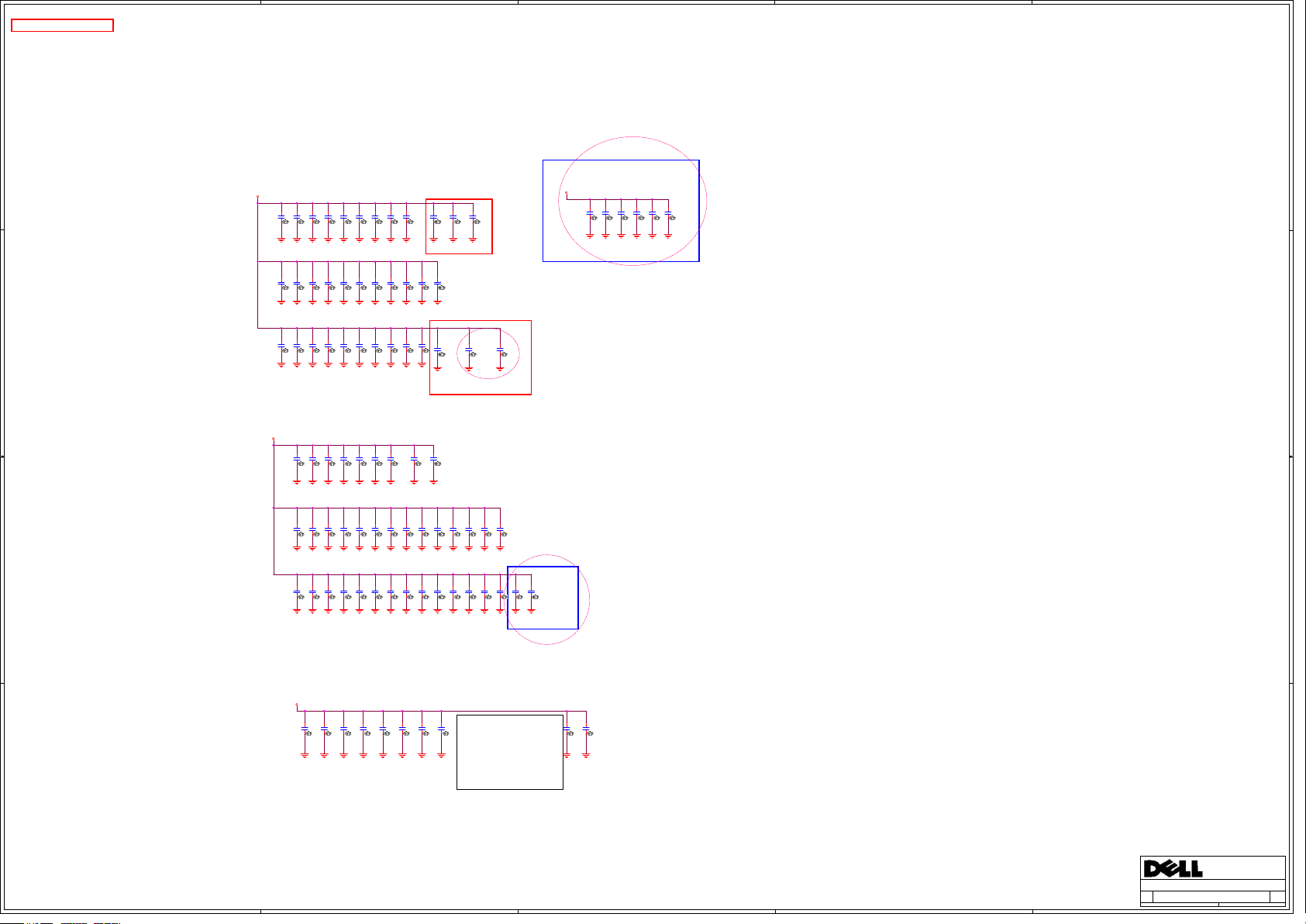

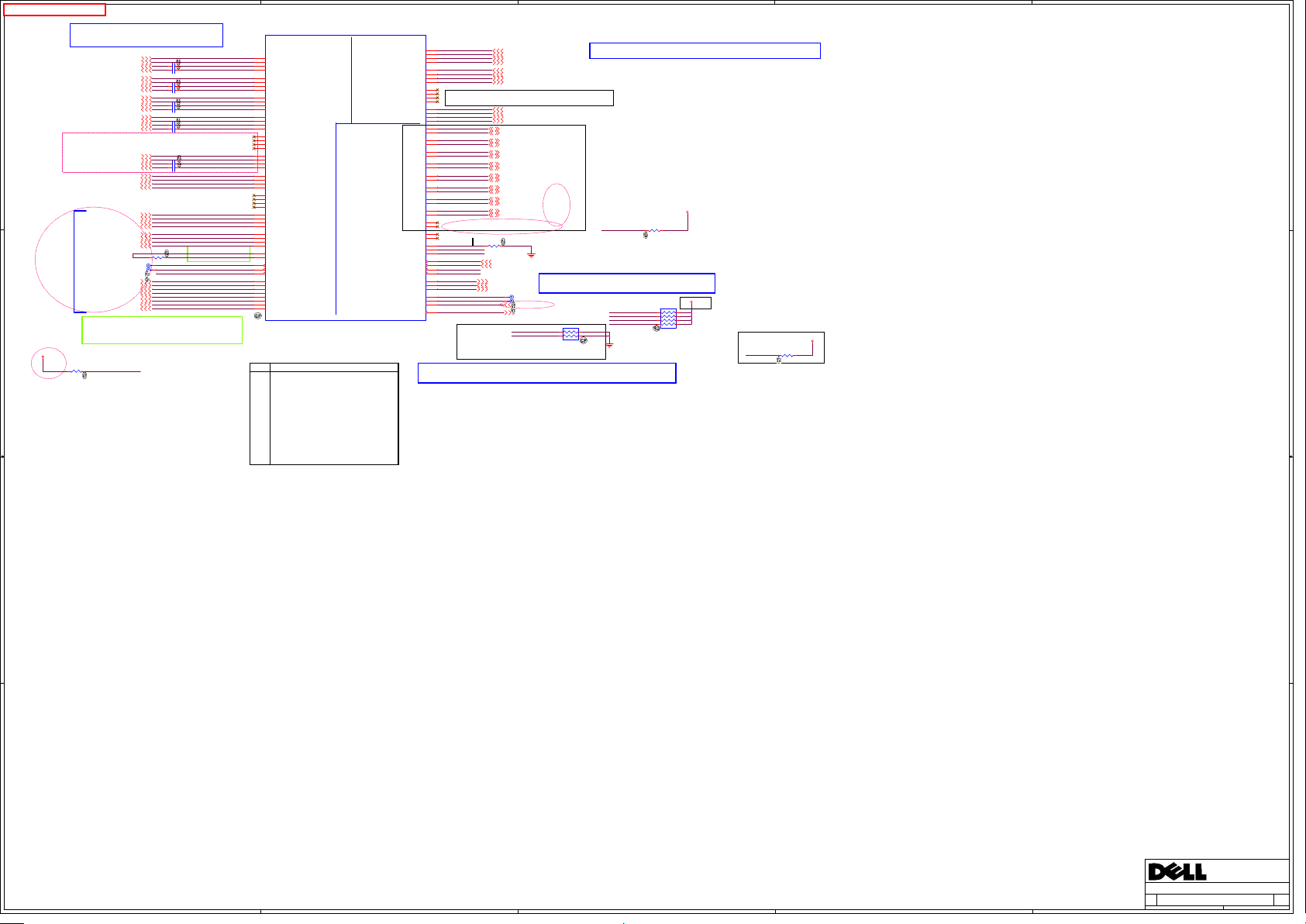

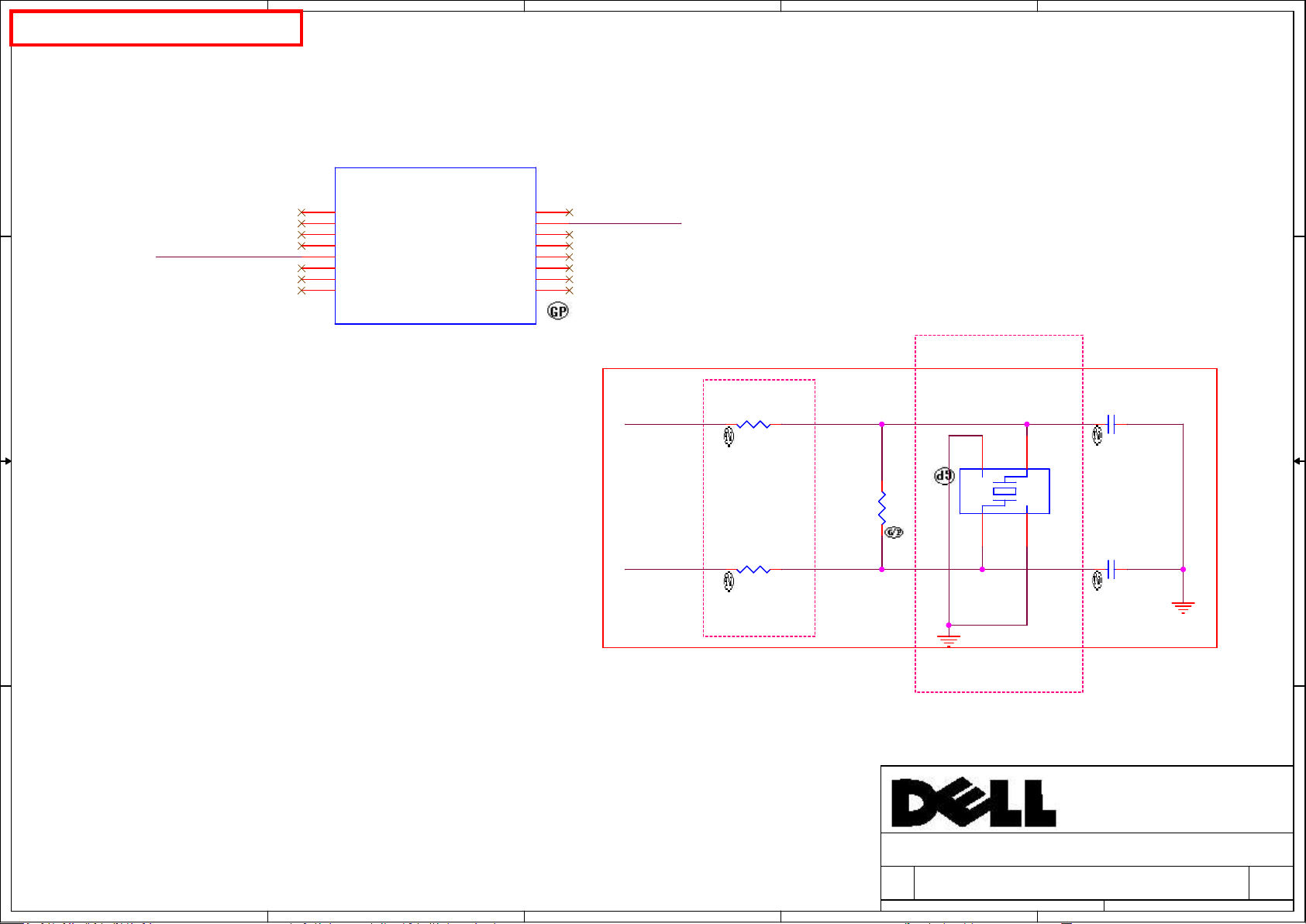

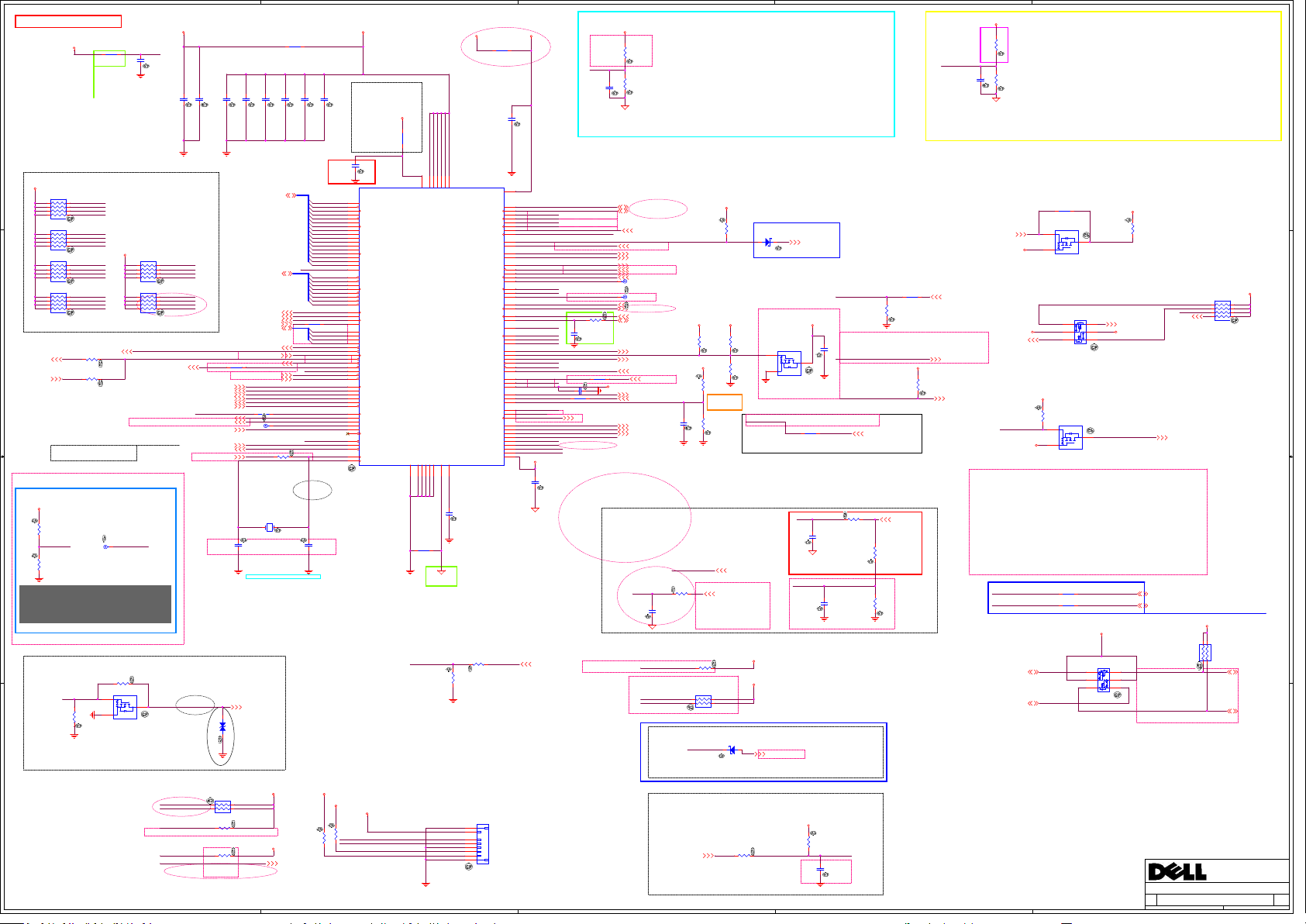

Star lord KBL Block Diagram

PCB P/N: 16888

Revision: A00

D D

RA

M(GDDR5) *4

V

2GB/4GB

G

DDR5

GPU

NVDIA

N17S-G1

18W

GPU BOARD

HDMI V1.4

HDMI

57

13.3"/15.6"/17.3"

(HD/FHD)

ouc

h panel

T

USB3.0 Port2

owe

C C

P

r share

5

5

USB PowerShare

34

USB3.0 Port3

ROR only

35

7mm HDD

Free fall

INT2

B B

Sensor BD

on Panel side

Gsensor

ST

LNG2DMTR

E-compass

ST

LIS3MDLTR

yr

o

G

ST

LSM6DS3USTR

70

eSPI debug port

Thermal

NUVOTON

NCT7718W

SMBUS

26

Fan Control

A A

PWM

FAN

Int.

KB

5

DM

H

TI

TPS2544RTER

68

KBC

SMSC

1416

EC

M

I Level Shifter

PS2

ouc

h PAD

T

Image sensor

57

USB2.0

USB3.0

USB2.0

USB3.0

USB2.0

eSPI

24

4

PCIE x 4

PCIE Lane1~Lane4

HDMI

eDP

U

SB2.0 LANE7

U

SB3.0 LANE1

USB2.0 LANE1

USB3.0 LANE3

USB2.0 LANE2

SATA

2C

I

(To CCG4

I2C

& USB2.0/I2C MUX)

TPM

NUVOTON

NPCT650JB2YX

4

SPI

Flash ROM

I2C

nt

el CPU

I

KBL/KBL-R

U22 / U42

10 USB 2.0/1.1 ports

SB 3.0 ports

U

6

ig

h Definition Audio

H

3 SATA ports

6 PCIE ports

LPC I/F

I 5.0

CP

A

SPI

16MB

Quad Read

3

Channel A

Channel B

DP

MUX and Redriver

TI

USB3.0

USB3.0 LANE4

USB2.0

USB2.0 LANE4

SATA/PCIex2/PCIEx4(Optane)

TUSB546-DCI

CCG4

CYPRESS

CYPD4125

3

8

37

USB2.0/I2C MUX

M.2 SSD

CardReader

USB2.0 LANE8

USB2.0

USB2.0 x 1

USB2.0 LANE5

HDA

USB2.0 x 1

PCIE LANE5

USB2.0 LANE6

USB2.0 LANE3

SD 3.0

Realtak

RTS5176E

PCIe

USB2.0

Camera (HD/IR)

D-MIC

HDA

NGFF WLAN

USB2.0 Port4

55

CODEC

Realtek

ALC3253

2526

3

27

MIC_IN/GND

HP_R/L

2

SENSOR IO MB

ROR

17A18-SA 17A17-SA 17810-1

BBY

DDR4

IMM A

OD

S

12

DDR4

OD

IMM B

S

13

DP/USB 3.0

I2C

TI

TS3DS10224

(To KBC)

USB2.0/I2C

3

8

63

SD Card Slot

IO Board

2CH SPEAKER

(2CH 2W/4ohm)

ni

U

2

USB3.0 type c

Port1

BBY only

versal Jack

1

C

HARGER

ISL88739

NPUTS

I

AD+

16888-117A16-SA17A18-SA

38

<Core Design>

<Core Design>

<Core Design>

T

T

T

le

le

le

it

it

it

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

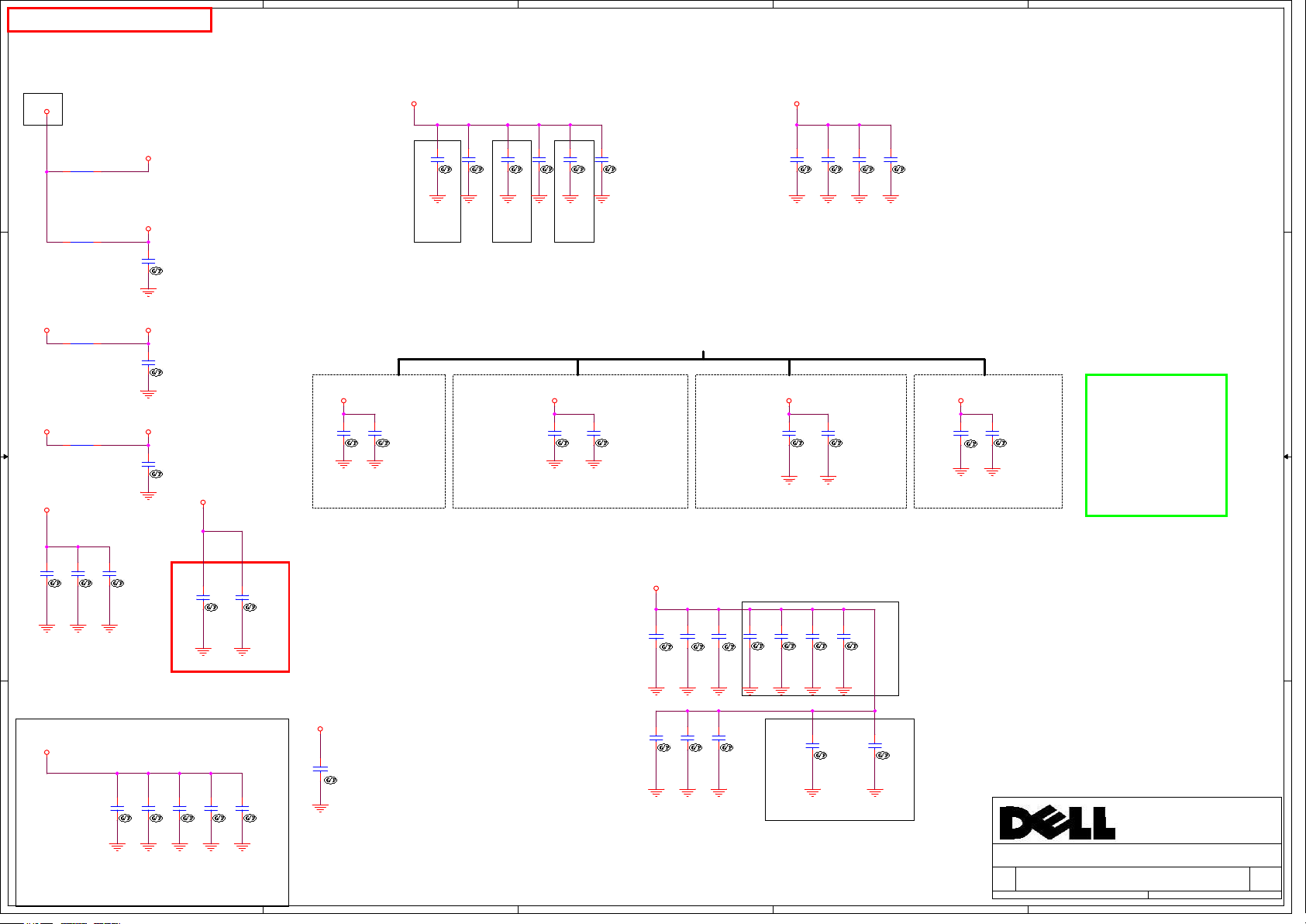

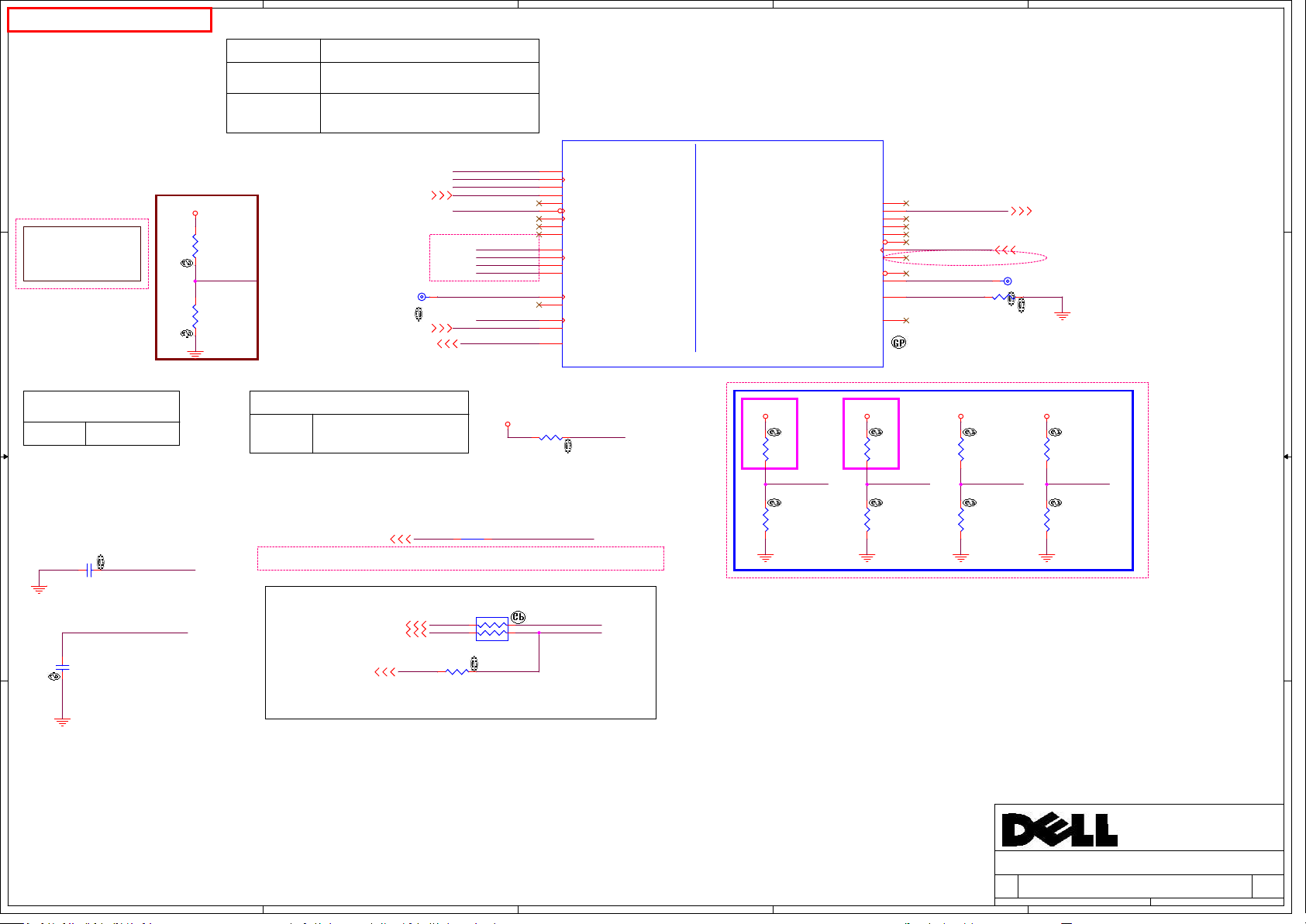

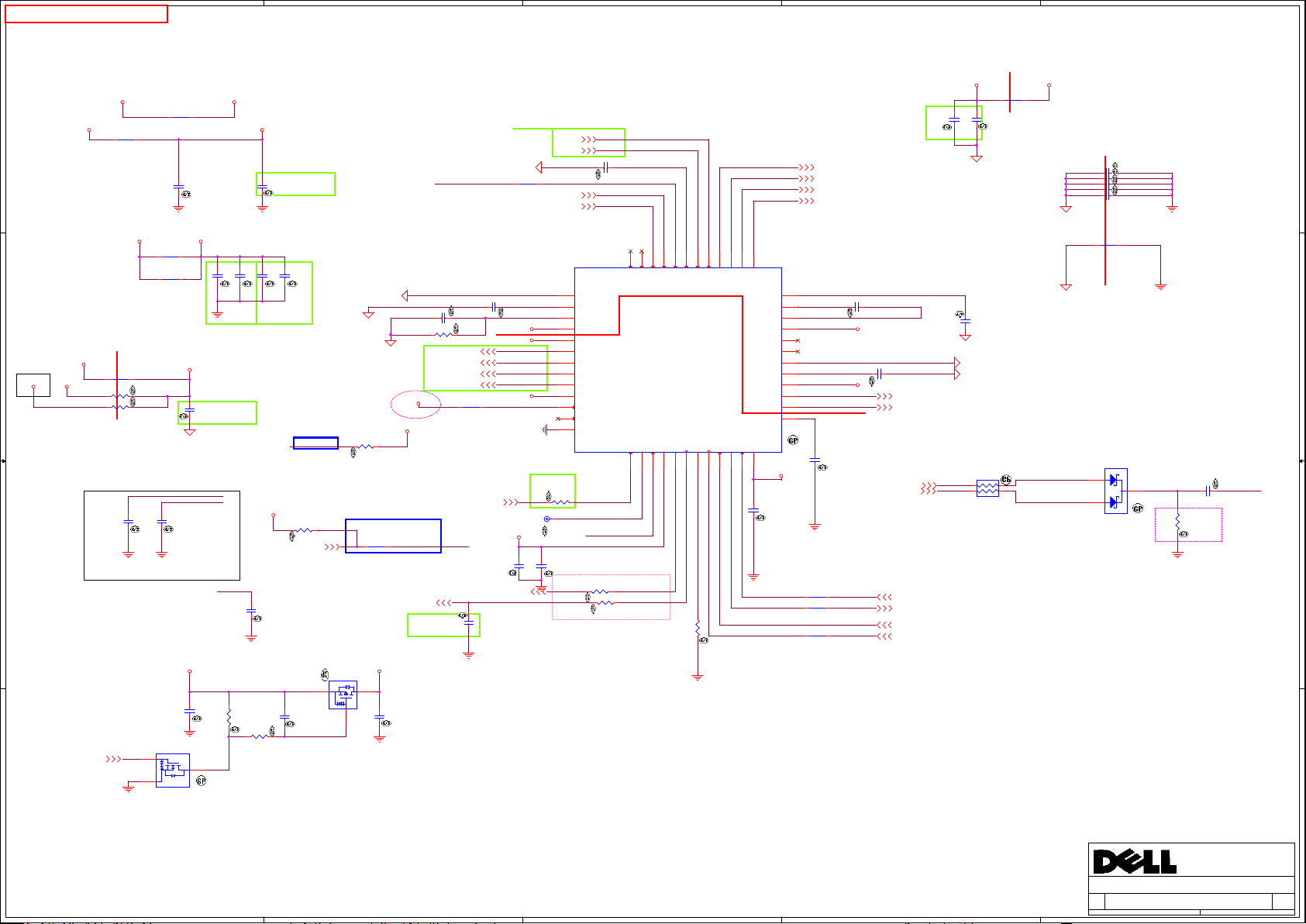

BT+

S

YSTEM DC/DC

SY8288CRAC-GP

NPUTS

I

DCBATOUT

C

PU Core Power

NCP81208MNTXG-GP

NCP81382MNTXG-1-GP

NCP81382MNTXG-1-GP

NCP81253MNTBG-GP

NPUTS

I

DCBATOUT

DCBATOUT +VCCGT

D

DR4

SY8288RAC-GP

APL5338XAI-TRG-GP

NPUTS OUTPUTS

I

DCBATOUT

C

PU DCDC-V1D00A

AOZ1268QI-02-GP

NPUTS OUTPUTS

I

DCBATOUT

L

DO-V1D5V

S-1339D15-M5001-GP

3D3V_S5

L

DO-V1D8V

APL5930KAI-TRG-GP

NPUTS OUTPUTS

I

3D3V_S5

5

G5016KD1U

NPUTS

I

5V_S5

M5938ARD1U-GP-U

INPUTS

1D0V_S5

TPS22965DSGR-GP-U

INPUTS

1D0V_S5

S

YSTEM DC/DC

TPS51225RUKR-GP

NPUTS

I

DCBATOUT

W

W

W

2

2

2

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

B

B

B

k Diagram

k Diagram

k Diagram

loc

loc

loc

rlord KBL-R

rlord KBL-R

rlord KBL-R

ta

ta

ta

S

S

S

1

UTPUTS

O

DCBATOUT

UTPUTS

O

PWR_5V

5V_S5

5V_AUX_S5

UTPUTS

O

VCC_CORE

+VCCSA_VRDCBATOUT

1D2V_S3

0D675V_S0

1D0V_S5

UTPUTSINPUTS

O

1D5V_S0

1D8V_S5

V/3V S0

OUTPUTS

5V_S0

3D3V_S03D3V_S5

V

CCSTG

UTPUTS

O

+VCCSTG

V

CCST

UTPUTS

O

+V1.00U_CPU

UTPUTS

O

3D3V_AUX_S5

3D3V_S5

PWR_3D3V

tron Corporation

tron Corporation

tron Corporation

is

is

is

, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

1F

1F

1F

2

2

2

44

45

46~50

3

3

51

52

54

54

40

40

40

45

00

00

00

A

A

A

o

o

o

f

10

f

10

f

10

6Monday, August 28, 2017

6Monday, August 28, 2017

6Monday, August 28, 2017

5

4

3

2

1

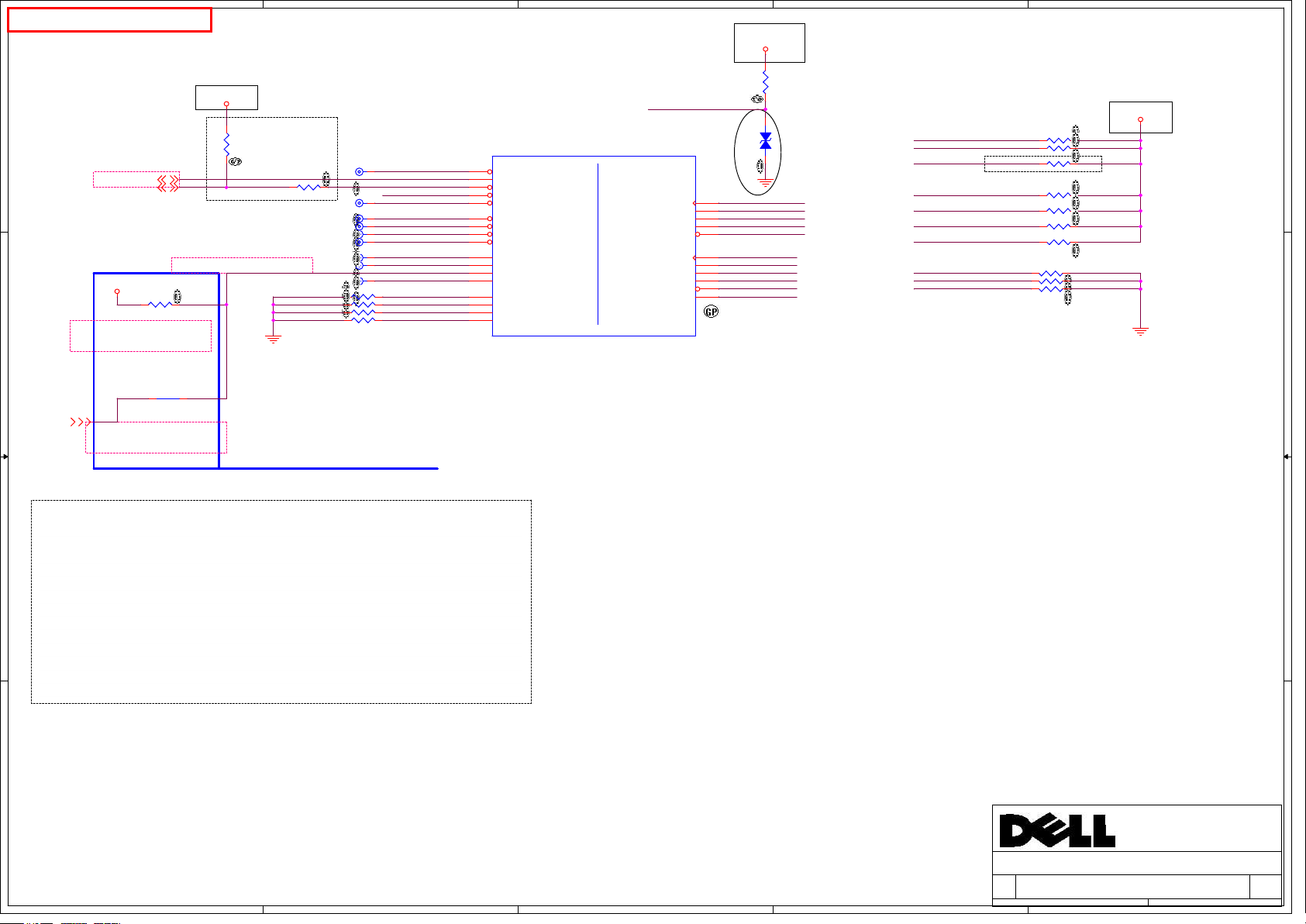

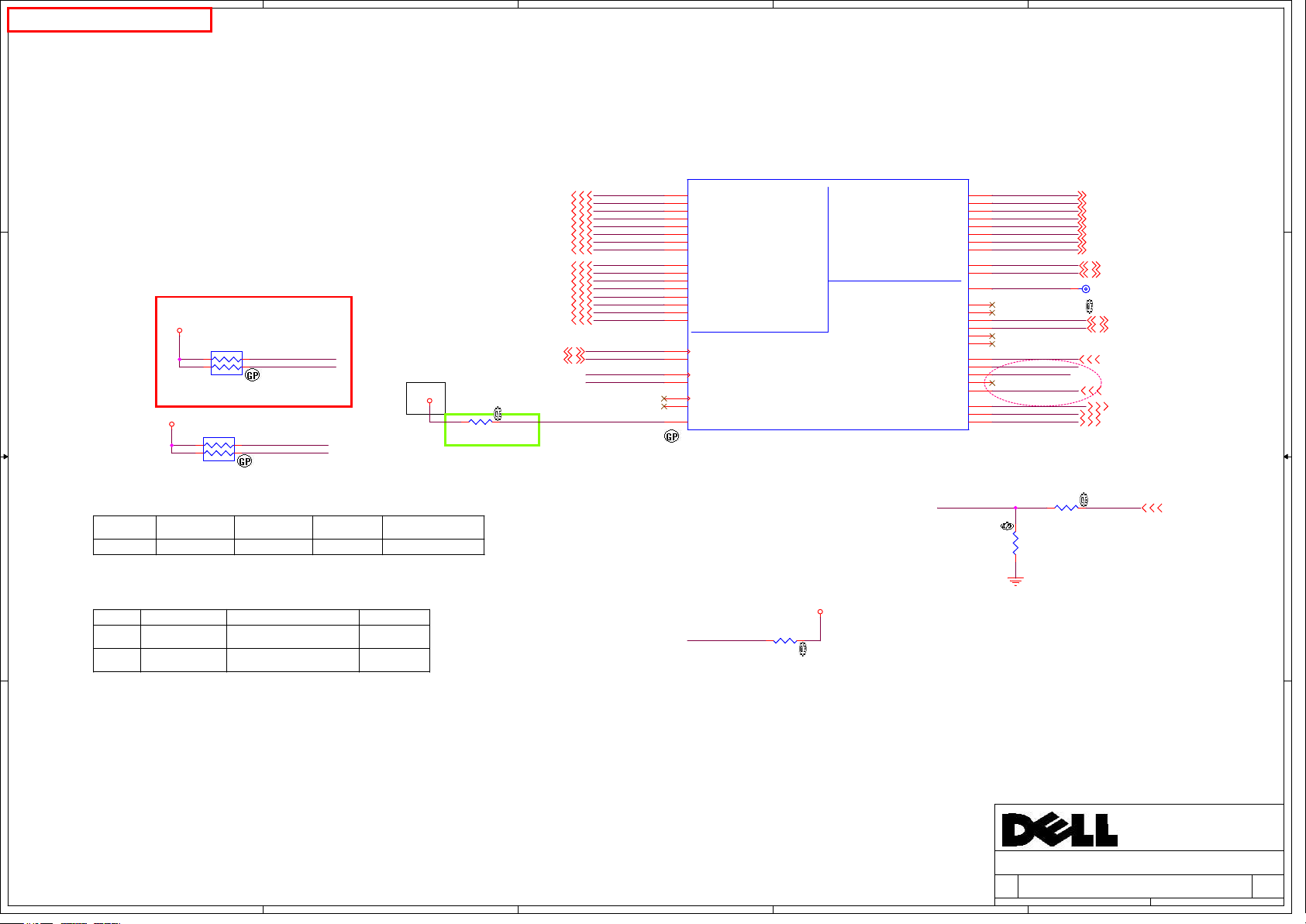

SSID = CPU

D D

C C

(Blanking)

B B

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

W

W

W

i

i

i

stron Corporation

stron Corporation

stron Corporation

2

2

2

1

1

1

F, 88, Sec.1, Hsin T ai Wu Rd., Hsichih,

F, 88, Sec.1, Hsin T ai Wu Rd., Hsichih,

F, 88, Sec.1, Hsin T ai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C .

Taipei Hsien 221, Taiwan, R.O.C .

Taipei Hsien 221, Taiwan, R.O.C .

T

tle

Title

Title

i

(

(

(

eserved)

eserved)

eserved)

R

R

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Date: Sheet

Date: Sheet

Date: Sheet

R

A

A

A

3

3

3

S

S

S

arlord KBL-R

arlord KBL-R

arlord KBL-R

t

t

t

3 1

3 1

3 1

1

o

o

o

f

f

f

0

0

0

0

0

0

A

A

A

06Monday, August 2 8, 2017

06Monday, August 2 8, 2017

06Monday, August 2 8, 2017

5

WWW.AliSaler.Com

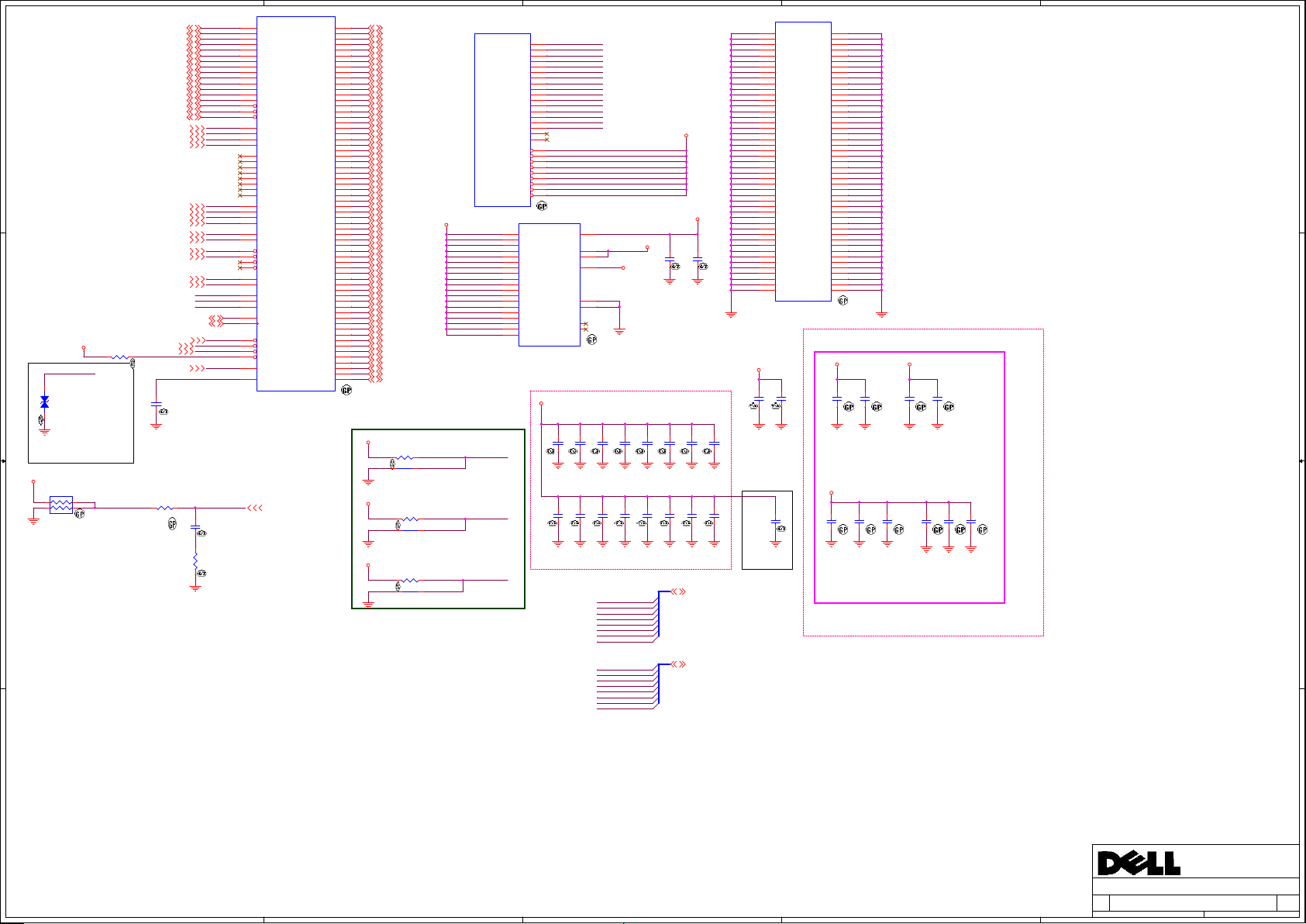

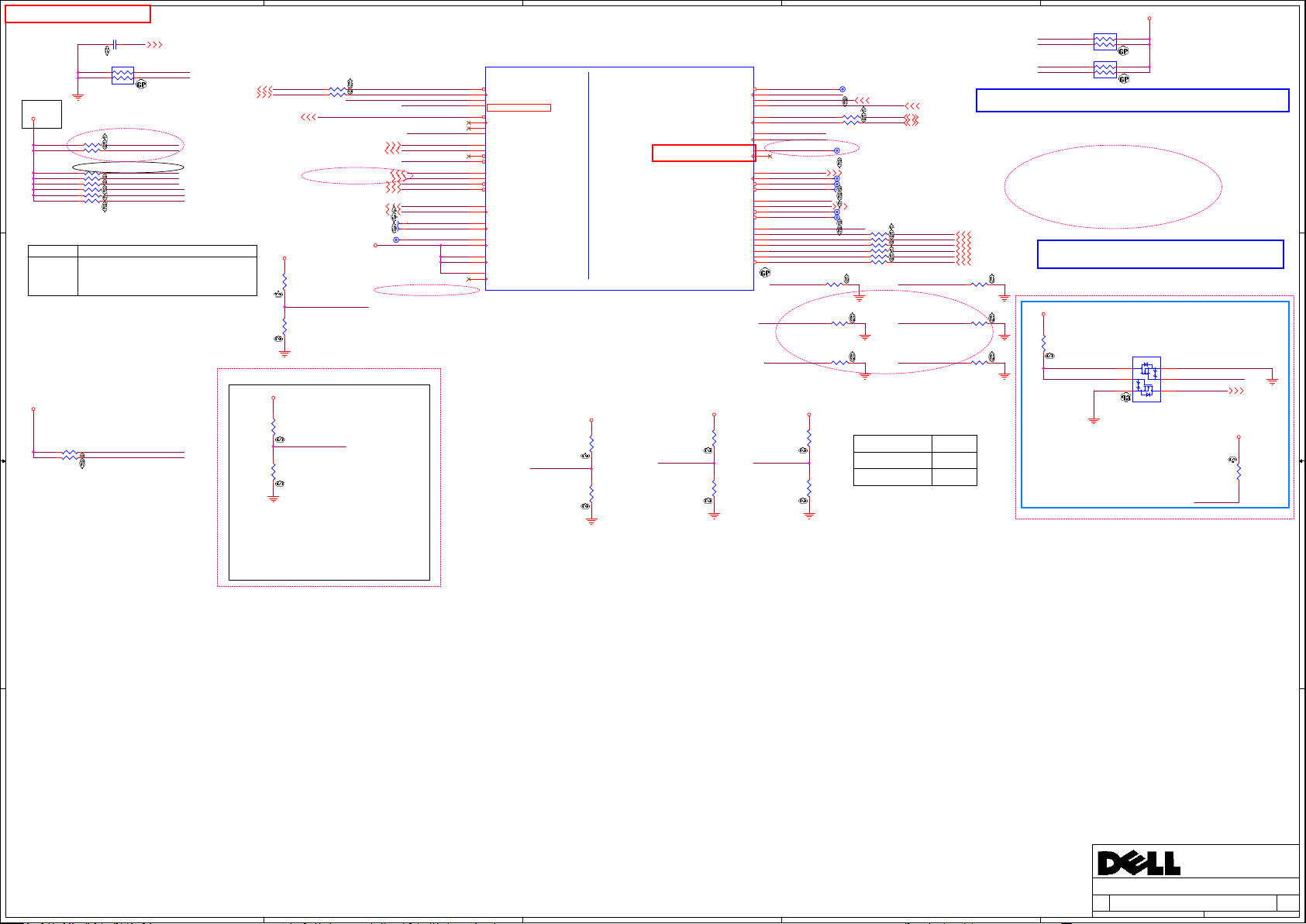

SSID = CPU

+

CSTG

VC

D D

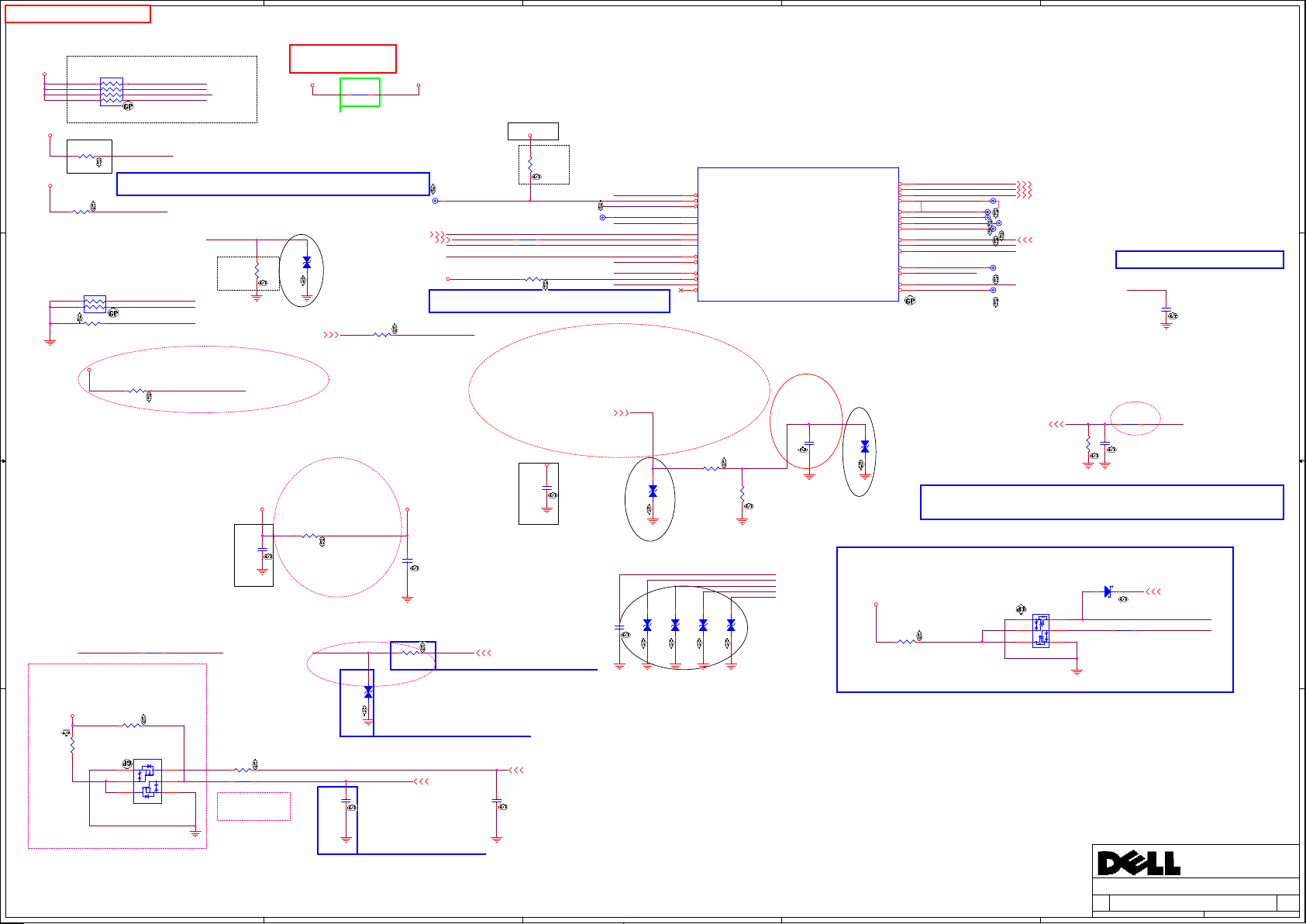

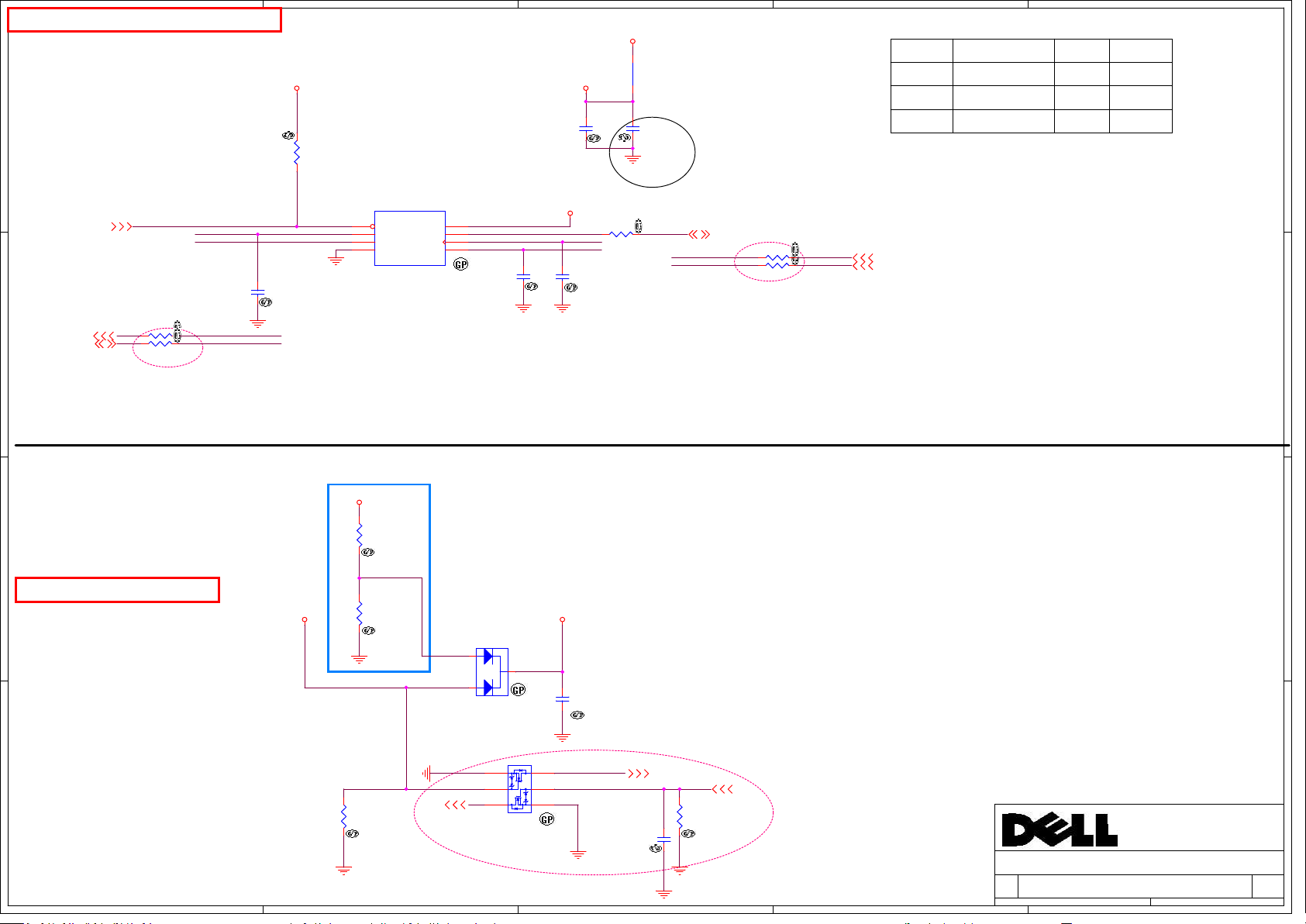

[PECI] and [PRO CHOT#]

Impedance contr ol: 50 ohm

Vince,20170106

H

_P

ECI_CPU[24]

H

ROCHOT#[24,44,46]

_P

Rb

Vince,20161107

3

D3

V_S5_PC H

R

4

40

1 2

Vince,20161031

C C

Vince,20161031

T

WAK E_KBC#

P_

DY

100KR2J -1-GP

1 2

R

0

41

0R0402-P AD

+VCCSTG = 1.0 V +VCCSTG = 1.0 V

12

R

1

40

1KR2J-1-G P

1 2

R

TPAD14-O P-GP

TPAD14-O P-GP

TPAD14-O P-GP

TPAD14-O P-GP

TPAD14-O P-GP

TPAD14-O P-GP

TPAD14-O P-GP

TPAD14-O P-GP

40

Ra

3499R2F-2 -GP

T

TPAD14-O P-GP

T

P4

T

P4

T

P4

T

P4

T

P4

T

P4

T

P4

T

P4

4

3

2

1

#544669 CRB Rev 0.52

+

CST_CPU

VC

12

R

41

9

1KR2J-1-G P

P

_THERMT RIP#

CH

C

1D

P4

01

H

1

ATERR#

_C

H

ROCHOT# _R

_P

P

_THERMT RIP#

CH

1

S

OCC#

KT

02

X

1

_BPM0

DP

05

X

1

_BPM1

DP

06

X

1

_BPM2

DP

07

X

1

DP

_BPM3

08

1

03

1

09

1

04

R

41

249D9R2F -GP

R

349D9R2F -GP

41

R

449D9R2F -GP

41

R

549D9R2F -GP

41

T

OU

CH_PAD_ INTR#

C

12

PU

P

12

CH

E

12

DR

E

12

OP

C

_EN#

AM

T

CH_PANE L_INTR#

OU

T

CH_PANE L_PD#

OU

_POPIRCOM P

_POPIRCOM P

AM_OPIO_R COMP

IO_RCOMP

D63

A54

C65

C63

A65

C55

D55

B54

C56

BA5

AY5

AT16

AU16

H66

H65

A6

A7

PU

C

AT

ERR#

P

I

EC

P

RO

CHOT#

T

HE

RMTRIP#

S

KT

OCC#

B

#[0]

PM

B

#[1]

PM

B

PM

#[2]

B

PM

#[3]

G

_E3/CPU_GP0

PP

G

PP

_E7/CPU_GP1

G

PP

_B3/CPU_GP2

G

_B4/CPU_GP3

PP

P

RO

C_POPIRCOMP

P

_OPIRCOMP

CH

O

E_RCOMP

PC

O

PC

_RCOMP

SKYLAKE-U-GP

SKYLAKE_ULT

CPU MISC

JTAG

P

RO

P

_JTAG_TCK

CH

P

CH

P

CH

_JTAG_TDO

P

_JTAG_TMS

CH

P

4

OF 20

P

RO

C_TCK

P

C_TDI

RO

P

C_TDO

RO

P

C_TMS

RO

C_TRST#

_JTAG_TDI

CH

_TRST#

J

TA

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

GX

X

_TCLK

DP

X

DP

_TDI

X

_TDO_CP U

DP

X

_TMS

DP

X

_TRST#

DP

P

_JTAG_T CK

CH

P

_JTAG_T DI

CH

P

CH

_JTAG_T DO

P

_JTAG_T MS

CH

X

DP

_TRST#

X

_TCK_JT AGX

DP

12

01

D4

E

DY

E

MI DVT1 0210

AZ5725-01FDR7G-GP

X

DP

X

DP

X

DP

P

CH

P

CH

P

CH

X

DP

X

DP

X

DP

P

CH

_TMS

_TDI

_TDO_CP U

_JTAG_T DI

_JTAG_T DO

_JTAG_T MS

_TCK_JT AGX

_TRST#

_TCLK

_JTAG_T CK

1 2

DY

1 2

DY

1 2

DY

PH in P.99

1 2

1 2

1 2

1 2

DY

R

1 2

40

2 51R2J-2-G P

DY

1 2

R

6 51R2J-2-G P

40

1 2

R

7 51R2J-2-G P

40

DY

+

VC

CSTG

R

42

151R2J-2-G P

R

42

251R2J-2-G P

R

351R2J-2-G P

42

R

851R2J-2-G P

40

R

951R2J-2-G P

40

R

651R2J-2-G P

41

R

71 KR2J-1-GP

41

Add resistor by NON DS3 function

(#543016) PROCHOT# Routing Guidelines

B B

M1,2,3,4,5: <3 inches

M6: 1-11 inches

MCPU: 0.3-1.5 i nches

Mt <0.3 mils

Main route(M1+M 2+M3+M4+M5+M6+ MCPU): 1-12 i nches

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

W

W

W

is

is

is

tron Corporation

tron Corporation

tron Corporation

2

2

2

, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

1F

1F

1F

Taipei Hsien 221, Taiwan, R.O.C .

Taipei Hsien 221, Taiwan, R.O.C .

Taipei Hsien 221, Taiwan, R.O.C .

T

le

Title

Title

it

C

C

C

PU

PU

PU

_(JTAG/CPU SIDE BAND)

_(JTAG/CPU SIDE BAND)

_(JTAG/CPU SIDE BAND)

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A

A

A

3

3

3

Date: Sheet

Date: Sheet

Date: Sheet

S

S

S

rlord KBL-R

rlord KBL-R

rlord KBL-R

ta

ta

ta

4 10

4 10

4 10

1

o

o

o

f

f

f

00

00

00

A

A

A

6Friday, December 08, 201 7

6Friday, December 08, 201 7

6Friday, December 08, 201 7

SSID = CPU

5

4

3

2

1

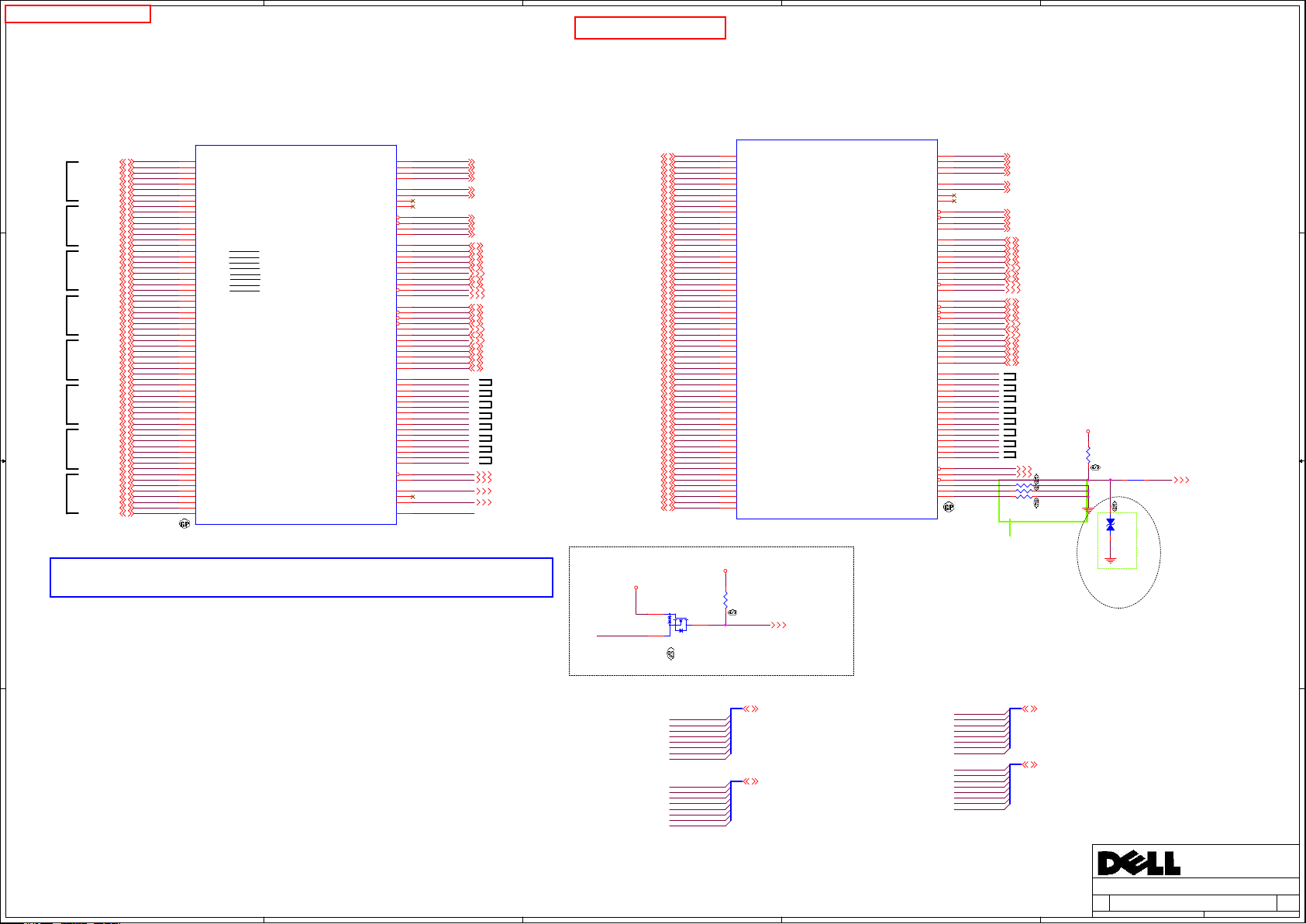

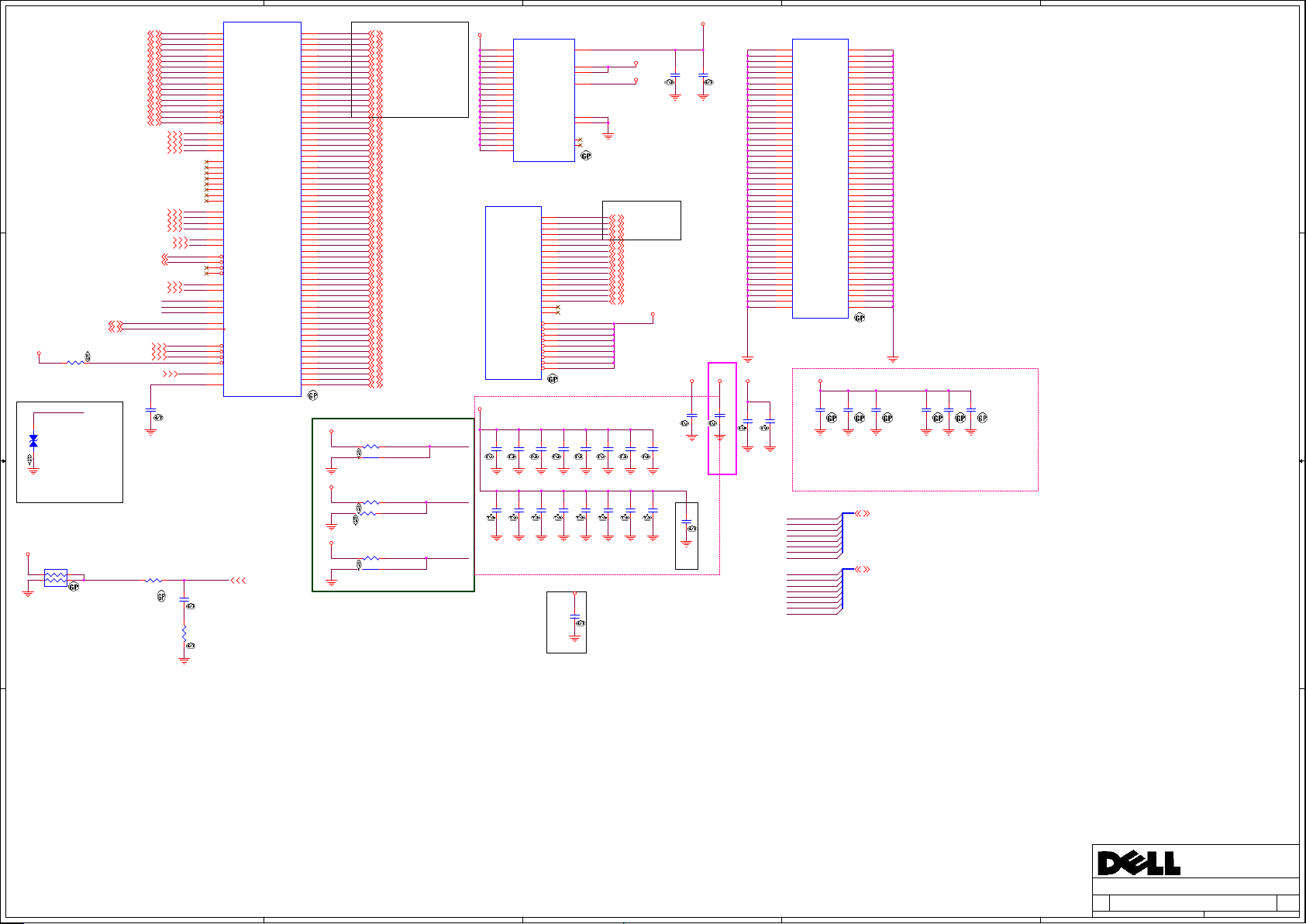

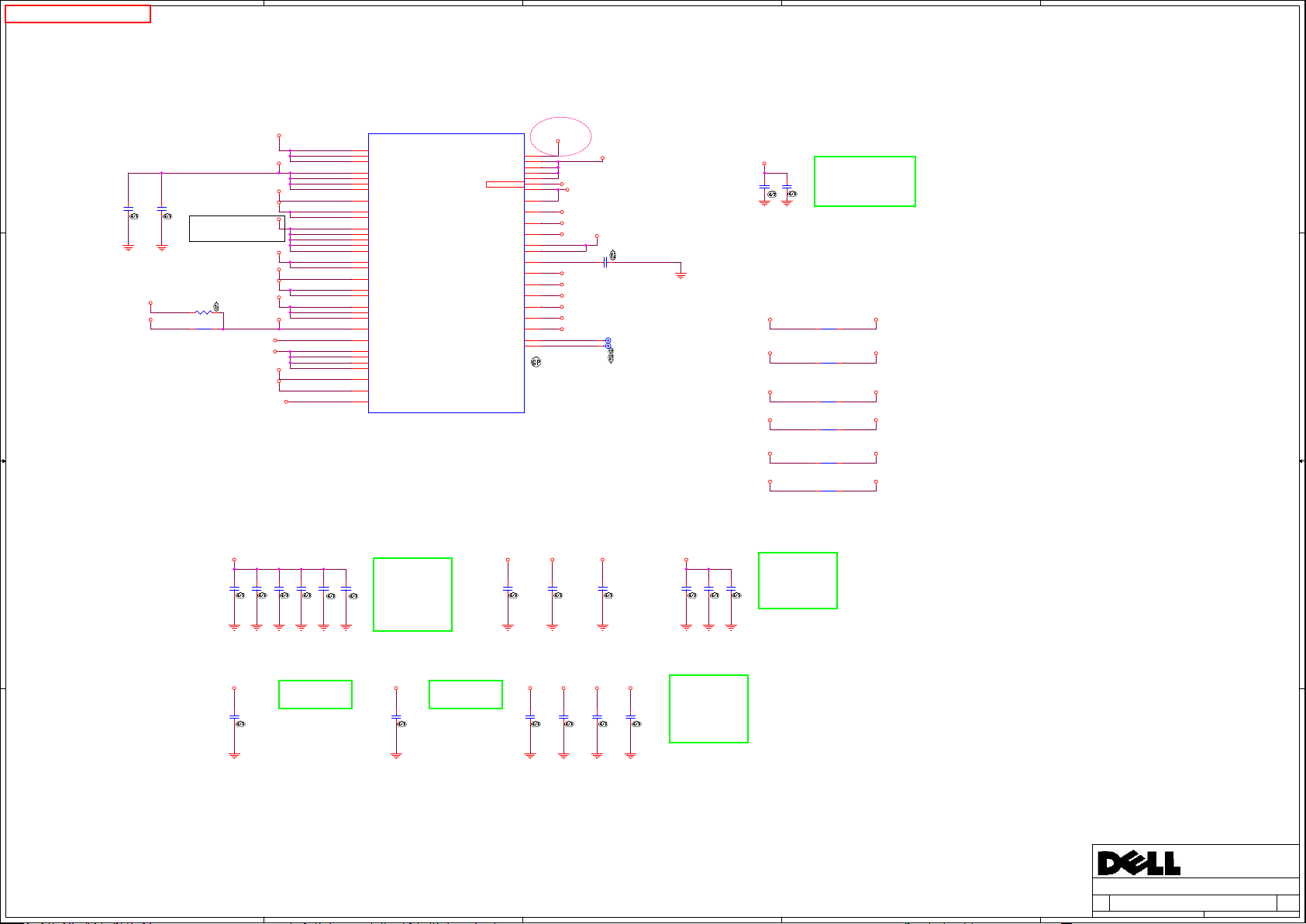

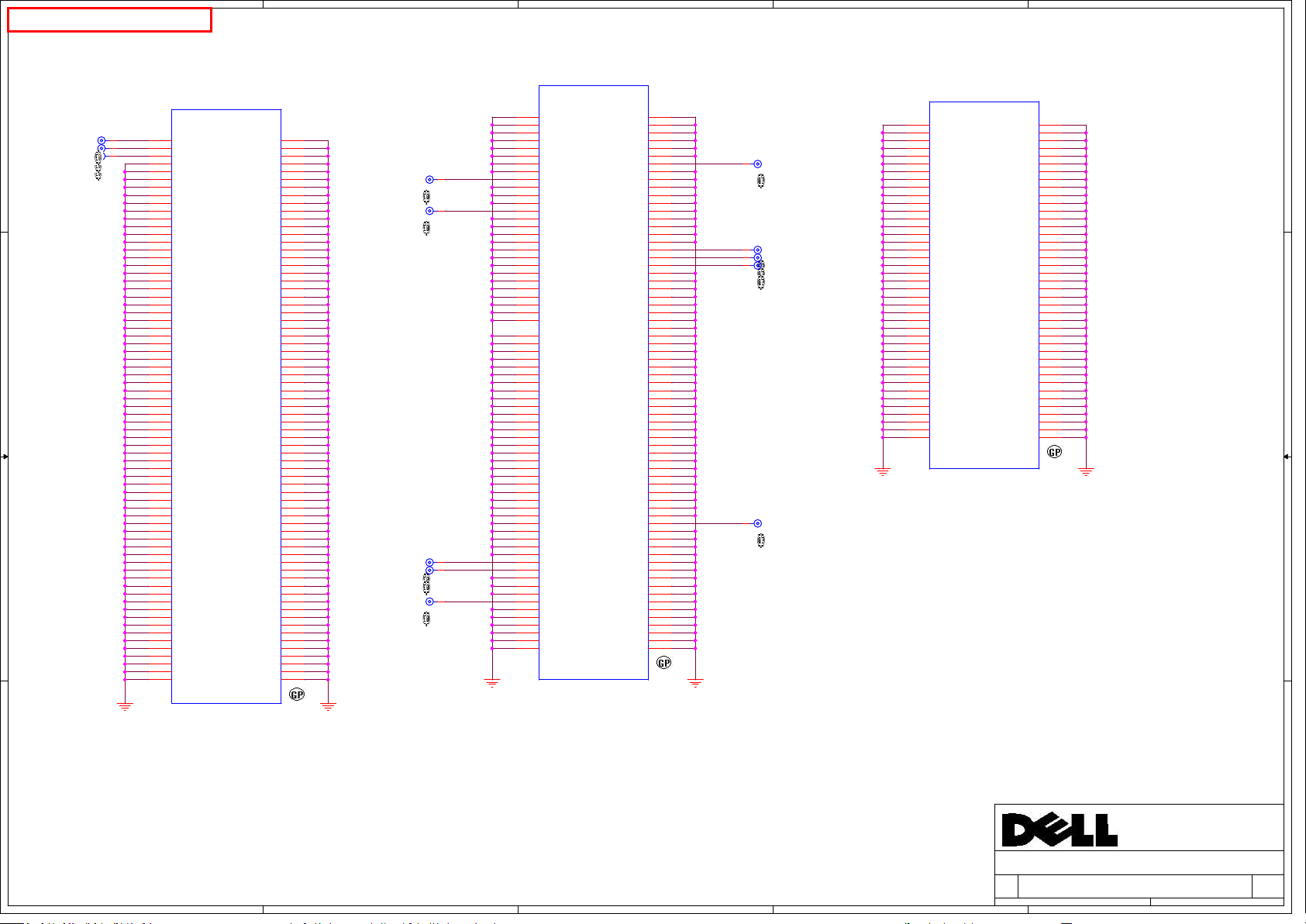

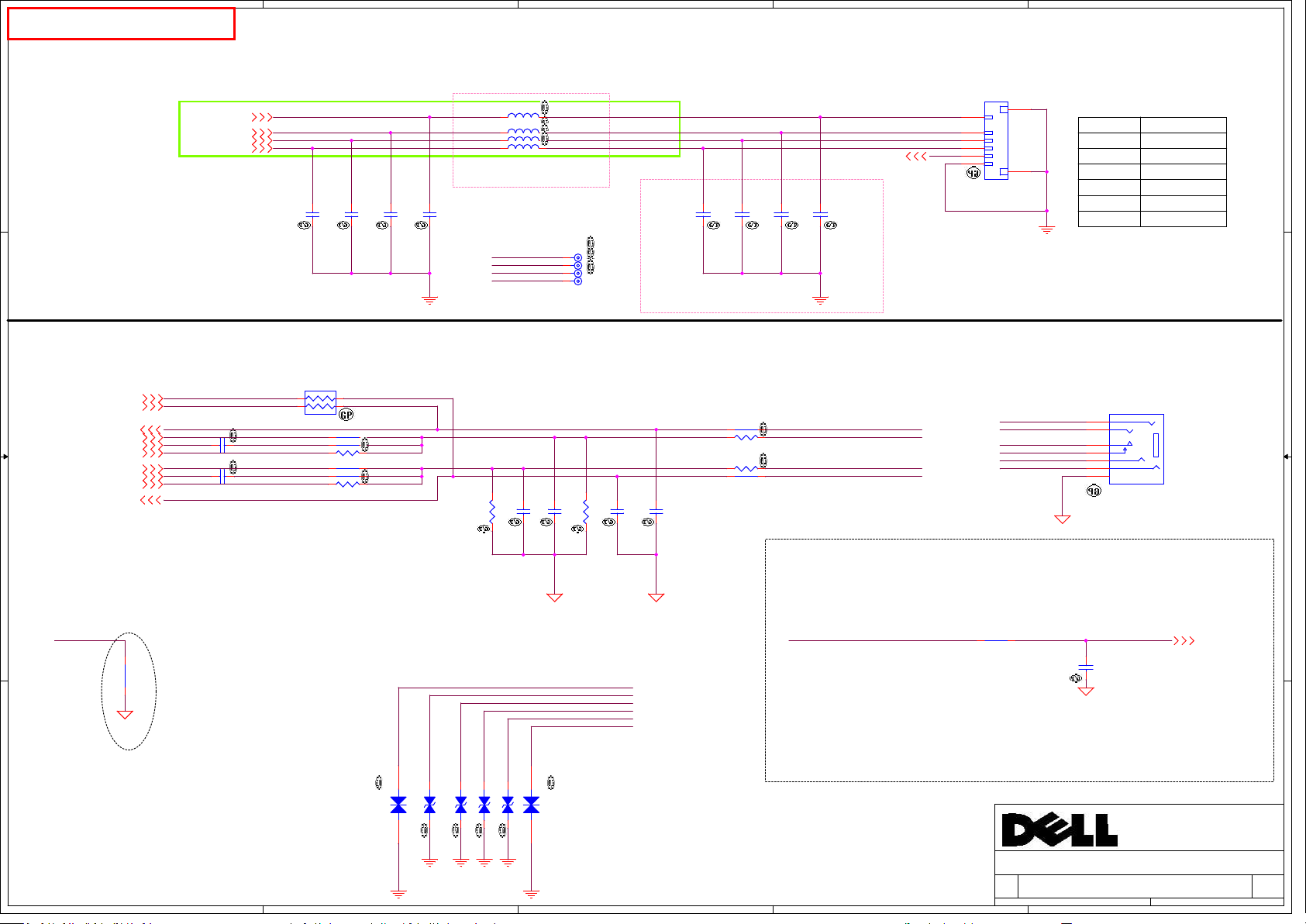

DDR4 ball type: Interleaved Type

D D

P

U1B

C

A_DQ0

_

AL71

M

A_DQ0[12]

_

M

_

A_DQ1[12]

M

A_DQ2[12]

_

M

_

A_DQ3[12]

M_A_DQ[0:7]

M_A_DQ[8:15]

M_B_DQ[0:7]

M_B_DQ[8:15]

C C

M_A_DQ[16:23]

M_A_DQ[24:31]

M_B_DQ[16:23]

M_B_DQ[24:31]

B B

M

_

A_DQ4[12]

M

A_DQ5[12]

_

M

_

A_DQ6[12]

M

A_DQ7[12]

_

M

_

A_DQ8[12]

M

A_DQ9[12]

_

M

_

A_DQ10[12]

M

_

A_DQ11[12]

M

A_DQ12[12]

_

M

_

A_DQ13[12]

M

A_DQ14[12]

_

M

_

A_DQ15[12]

M

B_DQ0[13]

_

M

_

B_DQ1[13]

M

_

B_DQ2[13]

M

B_DQ3[13]

_

M

_

B_DQ4[13]

M

B_DQ5[13]

_

M

_

B_DQ6[13]

M

_

B_DQ7[13]

M

B_DQ8[13]

_

M

_

B_DQ9[13]

M

B_DQ10[13]

_

M

_

B_DQ11[13]

M

_

B_DQ12[13]

M

B_DQ13[13]

_

M

_

B_DQ14[13]

M

B_DQ15[13]

_

M

_

A_DQ16[12]

M

_

A_DQ17[12]

M

A_DQ18[12]

_

M

_

A_DQ19[12]

M

A_DQ20[12]

_

M

_

A_DQ21[12]

M

A_DQ22[12]

_

M

A_DQ23[12]

_

M

_

A_DQ24[12]

M

A_DQ25[12]

_

M

_

A_DQ26[12]

M

A_DQ27[12]

_

M

_

A_DQ28[12]

M

_

A_DQ29[12]

M

A_DQ30[12]

_

M

_

A_DQ31[12]

M

B_DQ16[13]

_

M

_

B_DQ17[13]

M

B_DQ18[13]

_

M

_

B_DQ19[13]

M

_

B_DQ20[13]

M

B_DQ21[13]

_

M

_

B_DQ22[13]

M

B_DQ23[13]

_

M

_

B_DQ24[13]

M

B_DQ25[13]

_

M

B_DQ26[13]

_

M

_

B_DQ27[13]

M

B_DQ28[13]

_

M

_

B_DQ29[13]

M

B_DQ30[13]

_

M

_

B_DQ31[13]

M

DQ Bit Swapping is allowed w ithin the same byte, and Byte Swapping is allowed within t he same channel.

Clock (CLK and CLK#) and Str obe (DQS and DQS#) differentia l signal swapping within a p air is not allowed. Also dif ferential

clock pair to clock pair swa pping within a channel is not allowed.

_

A_DQ1

M

_

A_DQ2

M

A_DQ3

_

M

_

A_DQ4

M

A_DQ5

_

M

_

A_DQ6

M

A_DQ7

_

M

A_DQ8

_

M

_

A_DQ9

M

A_DQ10

_

M

_

A_DQ11

M

A_DQ12

_

M

_

A_DQ13

M

_

A_DQ14

M

A_DQ15

_

M

_

B_DQ0

M

B_DQ1

_

M

_

B_DQ2

M

_

B_DQ3

M

B_DQ4

_

M

_

B_DQ5

M

B_DQ6

_

M

_

B_DQ7

M

B_DQ8

_

M

_

B_DQ9

M

_

B_DQ10

M

B_DQ11

_

M

_

B_DQ12

M

B_DQ13

_

M

_

B_DQ14

M

_

B_DQ15

M

A_DQ16

_

M

_

A_DQ17

M

A_DQ18

_

M

_

A_DQ19

M

_

A_DQ20

M

A_DQ21

_

M

_

A_DQ22

M

A_DQ23

_

M

_

A_DQ24

M

A_DQ25

_

M

_

A_DQ26

M

_

A_DQ27

M

A_DQ28

_

M

_

A_DQ29

M

A_DQ30

_

M

_

A_DQ31

M

_

B_DQ16

M

B_DQ17

_

M

_

B_DQ18

M

B_DQ19

_

M

_

B_DQ20

M

_

B_DQ21

M

B_DQ22

_

M

_

B_DQ23

M

B_DQ24

_

M

_

B_DQ25

M

B_DQ26

_

M

_

B_DQ27

M

_

B_DQ28

M

B_DQ29

_

M

_

B_DQ30

M

B_DQ31

_

M

AN68

AN69

AL70

AL69

AN70

AN71

AR70

AR68

AU71

AU68

AR71

AR69

AU70

AU69

AF65

AF64

AK65

AK64

AF66

AF67

AK67

AK66

AF70

AF68

AH71

AH68

AF71

AF69

AH70

AH69

BB65

AW65

AW63

AY63

BA65

AY65

BA63

BB63

BA61

AW61

BB59

AW59

BB61

AY61

BA59

AY59

AT66

AU66

AP65

AN65

AN66

AP66

AT65

AU65

AT61

AU61

AP60

AN60

AN61

AP61

AT60

AU60

AL68

SKYLAKE-U-GP

D

R0_DQ[0]

D

R0_DQ[1]

D

D

D

R0_DQ[2]

D

D

R0_DQ[3]

D

R0_DQ[4]

D

D

D

R0_DQ[5]

D

R0_DQ[6]

D

D

D

R0_DQ[7]

D

D

R0_DQ[8]

D

R0_DQ[9]

D

D

D

R0_DQ[10]

D

R0_DQ[11]

D

D

D

R0_DQ[12]

D

D

R0_DQ[13]

D

R0_DQ[14]

D

D

D

R0_DQ[15]

D

R1_DQ[0]/DDR0_DQ[8]

D

D

D

R1_DQ[1]/DDR0_DQ[9]

D

R1_DQ[2]/DDR0_DQ[10]

D

D

D

R1_DQ[3]/DDR0_DQ[11]

D

D

R1_DQ[4]/DDR0_DQ[12]

D

R1_DQ[5]/DDR0_DQ[13]

D

D

D

R1_DQ[6]/DDR0_DQ[14]

D

R1_DQ[7]/DDR0_DQ[15]

D

D

D

R1_DQ[8]/DDR0_DQ[24]

D

D

R1_DQ[9]/DDR0_DQ[25]

D

R1_DQ[10]/DDR0_DQ[26]

D

D

D

R1_DQ[11]/DDR0_DQ[27]

D

R1_DQ[12]/DDR0_DQ[28]

D

D

D

R1_DQ[13]/DDR0_DQ[29]

D

R1_DQ[14]/DDR0_DQ[30]

D

D

R1_DQ[15]/DDR0_DQ[31]

D

D

D

R0_DQ[16]/DDR0_DQ[32]

D

R0_DQ[17]/DDR0_DQ[33]

D

D

D

R0_DQ[18]/DDR0_DQ[34]

D

R0_DQ[19]/DDR0_DQ[35]

D

D

D

R0_DQ[20]/DDR0_DQ[36]

D

D

R0_DQ[21]/DDR0_DQ[37]

D

R0_DQ[22]/DDR0_DQ[38]

D

D

D

R0_DQ[23]/DDR0_DQ[39]

D

R0_DQ[24]/DDR0_DQ[40]

D

D

D

R0_DQ[25]/DDR0_DQ[41]

D

D

R0_DQ[26]/DDR0_DQ[42]

D

R0_DQ[27]/DDR0_DQ[43]

D

D

D

R0_DQ[28]/DDR0_DQ[44]

D

R0_DQ[29]/DDR0_DQ[45]

D

D

D

R0_DQ[30]/DDR0_DQ[46]

D

R0_DQ[31]/DDR0_DQ[47]

D

D

D

R1_DQ[16]/DDR0_DQ[48]

D

D

R1_DQ[17]/DDR0_DQ[49]

D

R1_DQ[18]/DDR0_DQ[50]

D

D

D

R1_DQ[19]/DDR0_DQ[51]

D

R1_DQ[20]/DDR0_DQ[52]

D

D

D

R1_DQ[21]/DDR0_DQ[53]

D

D

R1_DQ[22]/DDR0_DQ[54]

D

R1_DQ[23]/DDR0_DQ[55]

D

D

D

R1_DQ[24]/DDR0_DQ[56]

D

R1_DQ[25]/DDR0_DQ[57]

D

D

D

R1_DQ[26]/DDR0_DQ[58]

D

D

R1_DQ[27]/DDR0_DQ[59]

D

R1_DQ[28]/DDR0_DQ[60]

D

D

D

R1_DQ[29]/DDR0_DQ[61]

D

R1_DQ[30]/DDR0_DQ[62]

D

D

D

R1_DQ[31]/DDR0_DQ[63]

D

SKYLAKE_ULT

D

DR0_DQ[16]

D

D

DDR0_DQ[17]

D

DDR0_DQ[18]

D

DDR0_DQ[19]

D

DDR0_DQ[20]

D

DDR0_DQ[21]

R0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

D

D

DDR0_DQ[22]

D

R0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

D

DDR0_DQ[23]

D

D

D

D

R0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

D

D

D

D

D

D

D

D

D

D

R0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

D

D

D

D

DDR CH - A

D

R0_MA[5]/DDR0_CAA[0]/DDR0_MA[ 5]

R0_MA[9]/DDR0_CAA[1]/DDR0_MA[ 9]

D

D

R0_MA[6]/DDR0_CAA[2]/DDR0_MA[ 6]

R0_MA[8]/DDR0_CAA[3]/DDR0_MA[ 8]

D

D

R0_MA[7]/DDR0_CAA[4]/DDR0_MA[ 7]

D

R0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

R0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

R0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

R0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

R0_WE#/DDR0_CAB[2]/DD R0_MA[14]

D

R0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

R0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

D

R0_MA[2]/DDR0_CAB[5]/DDR0_MA[ 2]

D

D

R0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

D

R0_MA[1]/DDR0_CAB[8]/DDR0_MA[ 1]

R0_MA[0]/DDR0_CAB[9]/DDR0_MA[ 0]

D

D

D

D

D

D

D

D

D

R0_DQSN[2]/DDR0_DQSN[4]

D

D

D

R0_DQSP[2]/DDR0_DQSP[4]

D

D

R0_DQSN[3]/DDR0_DQSN[5]

D

R0_DQSP[3]/DDR0_DQSP[5]

D

D

D

R1_DQSN[2]/DDR0_DQSN[6]

D

R1_DQSP[2]/DDR0_DQSP[6]

D

D

D

R1_DQSN[3]/DDR0_DQSN[7]

D

D

R1_DQSP[3]/DDR0_DQSP[7]

D

PDG: DDR/ODT

OF 20

2

D

R0_CKN[0]

D

R0_CKP[0]

D

D

D

R0_CKN[1]

D

D

R0_CKP[1]

D

D

R0_CKE[0]

D

R0_CKE[1]

D

D

D

R0_CKE[2]

D

D

R0_CKE[3]

D

D

R0_CS#[0]

D

R0_CS#[1]

D

D

D

R0_ODT[0]

D

D

R0_ODT[1]

D

D

R0_MA[3]

D

D

R0_MA[4]

D

D

R0_DQSN[0]

D

R0_DQSP[0]

D

D

D

R0_DQSN[1]

D

D

R0_DQSP[1]

D

R1_DQSN[0]/DDR0_DQ[2]

R1_DQSP[0]/DDR0_DQ[2]

R1_DQSN[1]/DDR0_DQ[3]

R1_DQSP[1]/DDR0_DQ[3]

D

R0_ALERT#

D

R0_PAR

D

D

D

R_VREF_CA

D

R0_VREF_DQ

D

D

D

R1_VREF_DQ

D

D

R_VTT_CNTL

D

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

AH66

AH65

AG69

AG70

BA64

AY64

AY60

BA60

AR66

AR65

AR61

AR60

AW50

AT52

AY67

AY68

BA67

AW67

A_A5

_

M

_

A_A9

M

A_A6

_

M

_

A_A8

M

_

A_A7

M

_

A_A12

M

A_A11

_

M

_

A_A13

M

A_A15

_

M

_

A_A14

M

A_A16

_

M

_

A_A2

M

_

A_A10

M

A_A1

_

M

_

A_A0

M

_

A_A3

M

A_A4

_

M

A_DQS_DN0

_

M

_

A_DQS_DP0

M

A_DQS_DN1

_

M

_

A_DQS_DP1

M

_

B_DQS_DN0

M

B_DQS_DP0

_

M

_

B_DQS_DN1

M

B_DQS_DP1

_

M

_

A_DQS_DN2

M

_

A_DQS_DP2

M

A_DQS_DN3

_

M

_

A_DQS_DP3

M

B_DQS_DN2

_

M

_

B_DQS_DP2

M

_

B_DQS_DN3

M

B_DQS_DP3

_

M

S

_PGCNTL

M

_

A_CLK#0 [12]

M

A_CLK0 [12]

_

M

_

A_CLK#1 [12]

M

_

A_CLK1 [12]

M

_

A_CKE0 [12]

M

A_CKE1 [12]

_

M

_

A_CS#0 [12]

M

A_CS#1 [12]

_

M

_

A_DIMA_ODT0 [12]

M

A_DIMA_ODT1 [12]

_

M

M

M

M

M

M

_

M

_

M

_

M

A_ACT_N [12]

_

M

_

A_BG1 [12]

M

_

M

_

M

_

M

_

M

_

M

M

_

M

_

M

M

M

M

M

M_A_DQS0

M_A_DQS1

M_B_DQS0

M_B_DQS1

M_A_DQS2

M_A_DQS3

M_B_DQS2

M_B_DQS3

M

M

V

V

_

A_A5 [12]

A_A9 [12]

_

_

A_A6 [12]

_

A_A8 [12]

A_A7 [12]

_

A_BG0 [12]

A_A12 [12]

A_A11 [12]

A_A13 [12]

A_A15 [12]

A_A14 [12]

A_A16 [12]

A_BA0 [12]

A_A2 [12]

_

A_BA1 [12]

A_A10 [12]

_A_A1 [12]

_

A_A0 [12]

A_A3 [12]

_

_

A_A4 [12]

A_ALERT_N [12]

_

_

A_PARITY [12]

SM_VREF_CNTA [ 12]

_

SM_VREF_CNTB [ 13]

_

M_A_DQ[32:39]

M_A_DQ[40:47]

M_B_DQ[32:39]

M_B_DQ[40:47]

M_A_DQ[48:55]

M_A_DQ[56:63]

M_B_DQ[48:55]

M_B_DQ[56:63]

M

A_DQ33[12]

_

M

_

A_DQ34[12]

M

A_DQ35[12]

_

M

_

A_DQ36[12]

M

_

A_DQ37[12]

M

A_DQ38[12]

_

M

_

A_DQ39[12]

M

A_DQ40[12]

_

M

_

A_DQ41[12]

M

A_DQ42[12]

_

M

_

A_DQ43[12]

M

_

A_DQ44[12]

M

A_DQ45[12]

_

M

_

A_DQ46[12]

M

A_DQ47[12]

_

M

_

B_DQ32[13]

M

B_DQ33[13]

_

M

_

B_DQ34[13]

M

_

B_DQ35[13]

M

B_DQ36[13]

_

M

_

B_DQ37[13]

M

B_DQ38[13]

_

M

_

B_DQ39[13]

M

_

B_DQ40[13]

M

B_DQ41[13]

_

M

_

B_DQ42[13]

M

B_DQ43[13]

_

M

_

B_DQ44[13]

M

_

B_DQ45[13]

M

B_DQ46[13]

_

M

_

B_DQ47[13]

M

A_DQ48[12]

_

M

_

A_DQ49[12]

M

_

A_DQ50[12]

M

A_DQ51[12]

_

M

_

A_DQ52[12]

M

A_DQ53[12]

_

M

_

A_DQ54[12]

M

A_DQ55[12]

_

M

A_DQ56[12]

_

M

_

A_DQ57[12]

M

A_DQ58[12]

_

M

_

A_DQ59[12]

M

A_DQ60[12]

_

M

_

A_DQ61[12]

M

_

A_DQ62[12]

M

A_DQ63[12]

_

M

_

B_DQ48[13]

M

B_DQ49[13]

_

M

_

B_DQ50[13]

M

B_DQ51[13]

_

M

_

B_DQ52[13]

M

_

B_DQ53[13]

M

B_DQ54[13]

_

M

_

B_DQ55[13]

M

B_DQ56[13]

_

M

_

B_DQ57[13]

M

B_DQ58[13]

_

M

B_DQ59[13]

_

M

_

B_DQ60[13]

M

B_DQ61[13]

_

M

_

B_DQ62[13]

M

B_DQ63[13]

_

M

D

2V_S3

1

_PGCNTL

M

S

G

S

PJA138KA-GP

A_DQ33

_

M

_

A_DQ34

M

_

A_DQ35

M

A_DQ36

_

M

_

A_DQ37

M

A_DQ38

_

M

_

A_DQ39

M

A_DQ40

_

M

A_DQ41

_

M

_

A_DQ42

M

A_DQ43

_

M

_

A_DQ44

M

A_DQ45

_

M

_

A_DQ46

M

_

A_DQ47

M

B_DQ32

_

M

_

B_DQ33

M

B_DQ34

_

M

_

B_DQ35

M

_

B_DQ36

M

B_DQ37

_

M

_

B_DQ38

M

B_DQ39

_

M

_

B_DQ40

M

B_DQ41

_

M

_

B_DQ42

M

_

B_DQ43

M

B_DQ44

_

M

_

B_DQ45

M

B_DQ46

_

M

_

B_DQ47

M

_

A_DQ48

M

A_DQ49

_

M

_

A_DQ50

M

A_DQ51

_

M

_

A_DQ52

M

_

A_DQ53

M

A_DQ54

_

M

_

A_DQ55

M

A_DQ56

_

M

_

A_DQ57

M

A_DQ58

_

M

_

A_DQ59

M

_

A_DQ60

M

A_DQ61

_

M

_

A_DQ62

M

A_DQ63

_

M

_

B_DQ48

M

_

B_DQ49

M

B_DQ50

_

M

_

B_DQ51

M

B_DQ52

_

M

_

B_DQ53

M

_

B_DQ54

M

B_DQ55

_

M

_

B_DQ56

M

B_DQ57

_

M

_

B_DQ58

M

B_DQ59

_

M

_

B_DQ60

M

_

B_DQ61

M

B_DQ62

_

M

_

B_DQ63

M

01

5

Q

D

_

A_DQ32

M

_

A_DQ32[12]

AY39

AW39

AY37

AW37

BB39

BA39

BA37

BB37

AY35

AW35

AY33

AW33

BB35

BA35

BA33

BB33

AU40

AT40

AT37

AU37

AR40

AP40

AP37

AR37

AT33

AU33

AU30

AT30

AR33

AP33

AR30

AP30

AY31

AW31

AY29

AW29

BB31

BA31

BA29

BB29

AY27

AW27

AY25

AW25

BB27

BA27

BA25

BB25

AU27

AT27

AT25

AU25

AP27

AN27

AN25

AP25

AT22

AU22

AU21

AT21

AN22

AP22

AP21

AN21

D

3V_S0

3

12

P

U1C

C

R0_DQ[32]/DDR1_DQ[0]

D

D

D

R0_DQ[33]/DDR1_DQ[1]

D

R0_DQ[34]/DDR1_DQ[2]

D

D

D

R0_DQ[35]/DDR1_DQ[3]

D

D

R0_DQ[36]/DDR1_DQ[4]

D

R0_DQ[37]/DDR1_DQ[5]

D

D

D

R0_DQ[38]/DDR1_DQ[6]

D

R0_DQ[39]/DDR1_DQ[7]

D

D

D

R0_DQ[40]/DDR1_DQ[8]

D

D

R0_DQ[41]/DDR1_DQ[9]

D

R0_DQ[42]/DDR1_DQ[10]

D

D

D

R0_DQ[43]/DDR1_DQ[11]

D

R0_DQ[44]/DDR1_DQ[12]

D

D

D

R0_DQ[45]/DDR1_DQ[13]

D

D

R0_DQ[46]/DDR1_DQ[14]

D

R0_DQ[47]/DDR1_DQ[15]

D

D

D

R1_DQ[32]/DDR1_DQ[16]

D

R1_DQ[33]/DDR1_DQ[17]

D

D

D

R1_DQ[34]/DDR1_DQ[18]

D

R1_DQ[35]/DDR1_DQ[19]

D

D

D

R1_DQ[36]/DDR1_DQ[20]

D

D

R1_DQ[37]/DDR1_DQ[21]

D

R1_DQ[38]/DDR1_DQ[22]

D

D

D

R1_DQ[39]/DDR1_DQ[23]

D

R1_DQ[40]/DDR1_DQ[24]

D

D

D

R1_DQ[41]/DDR1_DQ[25]

D

D

R1_DQ[42]/DDR1_DQ[26]

D

R1_DQ[43]/DDR1_DQ[27]

D

D

D

R1_DQ[44]/DDR1_DQ[28]

D

R1_DQ[45]/DDR1_DQ[29]

D

D

D

R1_DQ[46]/DDR1_DQ[30]

D

R1_DQ[47]/DDR1_DQ[31]

D

D

R0_DQ[48]/DDR1_DQ[32]

D

D

D

R0_DQ[49]/DDR1_DQ[33]

D

R0_DQ[50]/DDR1_DQ[34]

D

D

D

R0_DQ[51]/DDR1_DQ[35]

D

R0_DQ[52]/DDR1_DQ[36]

D

D

D

R0_DQ[53]/DDR1_DQ[37]

D

D

R0_DQ[54]/DDR1_DQ[38]

D

R0_DQ[55]/DDR1_DQ[39]

D

D

D

R0_DQ[56]/DDR1_DQ[40]

D

R0_DQ[57]/DDR1_DQ[41]

D

D

D

R0_DQ[58]/DDR1_DQ[42]

D

D

R0_DQ[59]/DDR1_DQ[43]

D

R0_DQ[60]/DDR1_DQ[44]

D

D

D

R0_DQ[61]/DDR1_DQ[45]

D

R0_DQ[62]/DDR1_DQ[46]

D

D

D

R0_DQ[63]/DDR1_DQ[47]

D

R1_DQ[48]

D

D

D

R1_DQ[49]

D

D

R1_DQ[50]

D

R1_DQ[51]

D

D

D

R1_DQ[52]

D

R1_DQ[53]

D

D

D

R1_DQ[54]

D

D

R1_DQ[55]

D

R1_DQ[56]

D

D

D

R1_DQ[57]

D

R1_DQ[58]

D

D

D

R1_DQ[59]

D

D

R1_DQ[60]

D

R1_DQ[61]

D

D

D

R1_DQ[62]

D

R1_DQ[63]

D

D

SKYLAKE-U-GP

06

5

R

220KR2F-GP

_PGCNTL_R [51]

M

S

SKYLAKE_ULT

R1_MA[5]/DDR1_CAA[0]/DDR1_MA[ 5]

D

D

D

R1_MA[9]/DDR1_CAA[1]/DDR1_MA[ 9]

D

R1_MA[6]/DDR1_CAA[2]/DDR1_MA[ 6]

D

D

D

R1_MA[8]/DDR1_CAA[3]/DDR1_MA[ 8]

D

R1_MA[7]/DDR1_CAA[4]/DDR1_MA[ 7]

D

D

D

R1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

D

D

R1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

D

R1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

D

D

D

R1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

D

R1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

D

D

D

R1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

D

R1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

D

D

D

R1_WE#/DDR1_CAB[2]/DD R1_MA[14]

D

R1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

D

D

D

R1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

D

R1_MA[2]/DDR1_CAB[5]/DDR1_MA[ 2]

D

D

R1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

D

D

D

R1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

D

R1_MA[1]/DDR1_CAB[8]/DDR1_MA[ 1]

D

D

D

R1_MA[0]/DDR1_CAB[9]/DDR1_MA[ 0]

D

R0_DQSN[4]/DDR1_DQSN[0]

D

D

D

R0_DQSP[4]/DDR1_DQSP[0]

D

R0_DQSN[5]/DDR1_DQSN[1]

D

D

D

R0_DQSP[5]/DDR1_DQSP[1]

D

D

R1_DQSN[4]/DDR1_DQSN[2]

D

R1_DQSP[4]/DDR1_DQSP[2]

D

D

D

R1_DQSN[5]/DDR1_DQSN[3]

D

R1_DQSP[5]/DDR1_DQSP[3]

D

D

D

R0_DQSN[6]/DDR1_DQSN[4]

D

R0_DQSP[6]/DDR1_DQSP[4]

D

D

D

R0_DQSN[7]/DDR1_DQSN[5]

D

D

R0_DQSP[7]/DDR1_DQSP[5]

D

DDR CH - B

Design Guideline:

SM_RCOMP keep routing length less than 500 mils.

D

D

D

D

D

D

D

D

D

D

D

D

D

R1_CKN[0]

D

D

R1_CKN[1]

R1_CKP[0]

D

D

D

R1_CKP[1]

D

R1_CKE[0]

D

D

D

R1_CKE[1]

D

R1_CKE[2]

D

D

D

R1_CKE[3]

D

R1_CS#[0]

D

D

D

R1_CS#[1]

D

R1_ODT[0]

D

D

R1_ODT[1]

D

D

D

D

R1_DQSN[6]

D

D

R1_DQSP[6]

R1_DQSN[7]

D

D

R1_DQSP[7]

R1_ALERT#

D

D

AM_RESET#

R

D

R_RCOMP[0]

D

R_RCOMP[1]

R_RCOMP[2]

D

OF 20

3

R1_MA[3]

R1_MA[4]

D

R1_PAR

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

BA38

AY38

AY34

BA34

AT38

AR38

AT32

AR32

BA30

AY30

AY26

BA26

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

_

M

M

S

M

S

M

S

M

S

#543016

B_A5

B_A9

B_A6

B_A8

B_A7

B_A12

B_A11

B_ACT_N

B_A13

B_A15

B_A14

B_A16

B_A2

B_A10

B_A1

B_A0

B_A3

B_A4

A_DQS_DN4

A_DQS_DP4

A_DQS_DN5

A_DQS_DP5

B_DQS_DN4

B_DQS_DP4

B_DQS_DN5

B_DQS_DP5

A_DQS_DN6

A_DQS_DP6

A_DQS_DN7

A_DQS_DP7

B_DQS_DN6

B_DQS_DP6

B_DQS_DN7

B_DQS_DP7

_DRAMRST#

_RCOMP_0

_RCOMP_1

_RCOMP_2

B_CLK#0 [13]

_

M

_

B_CLK#1 [13]

M

B_CLK0 [13]

_

M

_

B_CLK1 [13]

M

B_CKE0 [13]

_

M

_

B_CKE1 [13]

M

_B_CS#0 [13]

M

_

B_CS#1 [13]

M

B_DIMB_ODT0 [13]

_

M

_

B_DIMB_ODT1 [13]

M

B_A5 [13]

_

M

_

B_A9 [13]

M

B_A6 [13]

_

M

_

B_A8 [13]

M

_

B_A7 [13]

M

_

B_BG0 [13]

M

_

B_A12 [13]

M

B_A11 [13]

_

M

_

B_ACT_N [13]

M

B_BG1 [13]

_

M

_

B_A13 [13]

M

B_A15 [13]

_

M

_

B_A14 [13]

M

_

B_A16 [13]

M

_

B_BA0 [13]

M

_

B_A2 [13]

M

_

B_BA1 [13]

M

_

B_A10 [13]

M

B_A1 [13]

_

M

_B_A0 [13]

M

_

B_A3 [13]

M

B_A4 [13]

_

M

M_A_DQS4

M_A_DQS5

M_B_DQS4

M_B_DQS5

M_A_DQS6

M_A_DQS7

M_B_DQS6

M_B_DQS7

_

M

_

M

1 2

01 121R2F -GP

5

R

1 2

5

02 80D6R2 F-L-GP

R

1 2

5

03 100R2F -L1-GP-U

R

Layout Note:

1

B_ALERT_N [13]

B_PARITY [13]

2V_S3

D

12

5

05

R

470R2F-GP

1 2

close to CPU

1 2

5

04

R

0R0402-PAD

D

501

E

AZ5725-01FDR7G-GP

D

R4_DRAMRST# [12,13]

D

2015/11/18 Modify

A_DQS_DN[7:0] [12]

_

A_DQS_DN0

_

M

_

A_DQS_DN1

M

A_DQS_DN2

_

M

_

A_DQS_DN3

M

A_DQS_DN4

_

M

_

A_DQS_DN5

M

_

A_DQS_DN6

M

A_DQS_DN7

_

M

_

A_DQS_DP0

M

_

A_DQS_DP1

M

A_DQS_DP2

_

M

_

A_DQS_DP3

A A

5

4

M

A_DQS_DP4

_

M

_

A_DQS_DP5

M

_

A_DQS_DP6

M

_

A_DQS_DP7

M

3

M

_

A_DQS_DP[7:0] [12]

M

2

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

_

B_DQS_DN0

B_DQS_DN1

_

_

B_DQS_DN2

B_DQS_DN3

_

_

B_DQS_DN4

B_DQS_DN5

_

_

B_DQS_DN6

_

B_DQS_DN7

B_DQS_DP0

_

_

B_DQS_DP1

B_DQS_DP2

_

_

B_DQS_DP3

_

B_DQS_DP4

B_DQS_DP5

_

_

B_DQS_DP6

B_DQS_DP7

_

B_DQS_DN[7:0] [13]

_

M

_

B_DQS_DP[7:0] [13]

M

<Core Design>

<Core Design>

<Core Design>

stron Corporation

stron Corporation

stron Corporation

i

i

i

W

W

W

1

1

1

F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

2

2

2

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

i

tle

Title

Title

T

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

2

2

2

A

A

A

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

U_(DDR)

U_(DDR)

U_(DDR)

P

P

P

C

C

C

arlord KBL-R

arlord KBL-R

arlord KBL-R

t

t

t

S

S

S

1

5 1

5 1

5 1

f

f

f

o

o

o

0

0

0

A

A

A

06Friday, December 08, 2017

06Friday, December 08, 2017

06Friday, December 08, 2017

0

0

0

5

WWW.AliSaler.Com

4

3

2

1

Main Func = CPU

PU

1S

C

D D

C C

PCH strap pin:

FG

3

C

C

B B

12

60

R

1KR2J-1-GP

DY

4

FG

12

60

R

1KR2J-1-GP

P6

T

P6

T

P6

T

P6

T

P6

T

P6

T

P6

T

P6

T

P6

T

P6

T

P6

T

P6

T

P6

T

P6

T

P6

T

P6

T

P6

T

P6

T

P6

T

P6

T

P6

T

01TPAD14-OP-GP

P6

T

P6

02TPAD14-OP-GP

T

P6

12TPAD14-OP-GP

T

P6

13TPAD14-OP-GP

T

[BDW Only]PHYSICAL_DEBUG_ENA BLED (DFX PRIVACY)

4

CFG[3]

(#543016)

DISPLAY PORT PRESENCE STRAP

5

CFG[4]

0

FG

18TPAD14-OP-GP

1

C

FG

1

19TPAD14-OP-GP

1

C

2

FG

20TPAD14-OP-GP

1

C

FG

3

21TPAD14-OP-GP

1

C

FG

4

22TPAD14-OP-GP

1

C

5

FG

23TPAD14-OP-GP

1

C

FG

6

24TPAD14-OP-GP

1

C

7

FG

25TPAD14-OP-GP

1

C

FG

8

26TPAD14-OP-GP

1

C

9

FG

27TPAD14-OP-GP

1

C

FG

10

28TPAD14-OP-GP

1

C

FG

11

29TPAD14-OP-GP

1

C

12

FG

30TPAD14-OP-GP

1

C

FG

13

31TPAD14-OP-GP

1

C

14

FG

32TPAD14-OP-GP

1

C

FG

15

33TPAD14-OP-GP

1

C

16

FG

34TPAD14-OP-GP

1

C

FG

17

35TPAD14-OP-GP

1

C

FG

18

36TPAD14-OP-GP

1

C

19

FG

37TPAD14-OP-GP

1

C

FG

C

149D9R2F-GP

60

12

R

TP

_PMODE

I

38TPAD14-OP-GP

1

SV

R

1

SV

R

1

SV

R

1

SV

R

1

0 : ENABLED

SET DFX ENABLED BIT IN DEBU G INTERFACE MSR

1 : DISABLED

0 : ENABLED

An external Display Port dev ice is connected to the Embedd ed Display Port.

1 : DISABLED (Default)

No Physical Display Port att ached to Embedded DisplayPort* . No connect for disable.

_RCOMP

D_TP_BA70

D_TP_BA68

D_F65

D_G65

E68

B67

D65

D67

E70

C68

D68

C67

F71

G69

F70

G68

H70

G71

H69

G70

E63

F63

E66

F66

E60

E8

AY2

AY1

D1

D3

K46

K45

AL25

AL27

C71

B70

F60

A52

BA70

BA68

J71

J68

F65

G65

F61

E61

[0]

FG

C

FG

[1]

C

FG

[2]

C

[3]

FG

C

FG

[4]

C

[5]

FG

C

FG

[6]

C

[7]

FG

C

FG

[8]

C

FG

[9]

C

[10]

FG

C

FG

[11]

C

[12]

FG

C

FG

[13]

C

FG

[14]

C

[15]

FG

C

[16]

FG

C

FG

[17]

C

[18]

FG

C

FG

[19]

C

FG

_RCOMP

C

TP

_PMODE

I

D_AY2

SV

R

SV

D_AY1

R

SV

D_D1

R

SV

D_D3

R

SV

D_K46

R

D_K45

SV

R

D_AL25

SV

R

D_AL27

SV

R

D_C71

SV

R

SV

D_B70

R

SV

D_F60

R

D_A52

SV

R

D_TP_BA70

SV

R

SV

D_TP_BA68

R

D_J71

SV

R

SV

D_J68

R

SS

_F65

V

_G65

SS

V

SV

D_F61

R

D_E61

SV

R

SKYLAKE-U-GP

RESERVED SIGNALS-1

SKYLAKE_ULT

SVD_TP_AW71

R

RSVD_TP_AW70

R

R

R

R

P

SV

SV

SV

SV

R

R

R

R

R

R

R

R

R

R

R

R

C_SELECT#

RO

9 OF 20

1

D_TP_BB68

D_TP_BB69

D_TP_AK13

D_TP_AK12

SV

D_BB2

D_BA3

SV

SV

D_D5

R

D_D4

SV

R

SV

D_B2

R

D_C2

SV

R

SV

D_B3

R

D_A3

SV

R

D_AW1

SV

D_E1

SV

R

SV

D_E2

R

D_BA4

SV

SV

D_BB4

SV

D_A4

R

SV

D_C4

R

SV

D_A69

R

D_B69

SV

R

SV

D_AY3

SV

D_D71

D_C70

SV

SV

D_C54

D_D54

SV

_AY71

SS

V

Z

SV

D_AW71

D_AW70

SV

M

SV

D_TP_BB68

BB68

R

D_TP_BB69

SV

BB69

R

AK13

AK12

BB2

BA3

P5

_AU5

U5

A

T

P5

T

T

T

T

T

VM

SM

_AT5

P6

A

T5

T

P6

D5

D4

B2

C2

B3

A3

AW1

E1

E2

BA4

BB4

A4

C4

_BB5

P4

T

B

B5

P4

A69

B69

AY3

D71

C70

C54

D54

P1

_AY4

T

Y4

A

P1

_BB3

P2

T

B

B3

P2

SS

_AY71

V

AY71

AR56

VM

#

Z

#

D_TP_AW71

SV

R

AW71

SV

D_TP_AW70

R

AW70

AP56

SM

M

#

C64

RO

P

1 2

#

C_SELECT#

60

2

R

0R0402-PAD

1

1

1

1

1

1

1

1

1

1

1

1 2

60

3

R

100KR2J-1-GP

03 TPAD14-OP-GP

P6

T

P6

04 TPAD14-OP-GP

T

07 TPAD14-OP-GP

P6

T

P6

08 TPAD14-OP-GP

T

P6

09 TPAD14-OP-GP

T

10 TPAD14-OP-GP

P6

T

P6

11 TPAD14-OP-GP

T

P6

T

P6

14 TPAD14-OP-GP

T

P6

15 TPAD14-OP-GP

T

P6

17 TPAD14-OP-GP

T

DY

16 TPAD14-OP-GP

#54469 CRB.

Vince,20161027

VC

CST_CPU

+

2016/01/11 modify

SKL(#543016):

Processor strap CFG[4] should be pulled low to enable embedded DisplayPort*

A A

<Core Design>

<Core Design>

<Core Design>

tron Corporation

tron Corporation

tron Corporation

is

is

is

W

W

W

1F

1F

1F

, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

, 88, Sec.1, Hsin Tai Wu R d., Hsichih,

2

2

2

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

_(RESERVED)

_(RESERVED)

_(RESERVED)

PU

PU

PU

C

C

C

rlord KBL-R

rlord KBL-R

rlord KBL-R

ta

ta

ta

S

S

S

1

6 10

6 10

6 10

f

f

f

o

o

o

A

A

A

5

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

2

2

2

A

A

A

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

00

00

00

6Friday, December 08, 2017

6Friday, December 08, 2017

6Friday, December 08, 2017

SSID = CPU

5

4

3

2

1

CCGT

V

+

CCSTG

V

+

CGT_SENSE[46]

C

V

S

SGT_SENSE[46]

V

For U22 & U42

T

_CORE

G

V

CCGT

+

T

_CORE

G

V

CCGT

+

T

_CORE

G

7

12

R

22_POWER_K52

U

12

DY

V

CCGT

+

0R2J-2-GP

22 only

U

C

U1M

P

CPU POWER 2 OF 4

A48

CCGT

A53

C

CGT

V

A58

CGT

C

V

A62

C

CGT

V

A66

CGT

C

V

AA63

C

CGT

V

AA64

CGT

C

V

AA66

C

CGT

V

AA67

CGT

C

V

AA69

C

CGT

V

AA70

CGT

C

V

AA71

CCGT

V

AC64

C

CGT

V

AC65

CGT

C

V

AC66

CGT

C

V

AC67

CCGT

V

AC68

C

CGT

V

AC69

CGT

C

V

AC70

C

CGT

V

AC71

CGT

C

V

J43

C

CGT

V

J45

CGT

C

V

J46

CCGT

V

J48

CGT

C

V

J50

C

CGT

V

J52

CGT

C

V

J53

CCGT

V

J55

C

CGT

V

J56

CGT

C

V

J58

C

CGT

V

J60

CGT

C

V

K48

C

CGT

V

K50

CGT

C

V

K52

C

CGT

V

K53

CGT

C

V

K55

C

CGT

V

K56

CGT

C

V

K58

CCGT

V

K60

C

CGT

V

L62

CGT

C

V

L63

C

CGT

V

L64

CCGT

V

L65

C

CGT

V

L66

CGT

C

V

L67

C

CGT

V

L68

CGT

C

V

L69

C

CGT

V

L70

CGT

C

V

L71

CCGT

V

M62

CGT

C

V

N63

C

CGT

V

N64

CGT

C

V

N66

CCGT

V

N67

C

CGT

V

N69

V

CGT

C

V

J70

CGT_SE NSE

C

J69

V

S

SGT_SE NSE

V

SKYLAKE-U-GP

D

2V_S3

1

SKYLAKE_ULT

C

S

V

V

V

CSTG_G 20

C

V

C

CC_G33

V

C

V

C

V

C

V

C

V

C

V

C

V

C

V

C

V

C

V

C

V

CC_K35

V

C

V

C

V

C

V

CC_K42

V

C

V

V

C_SENSE

S_SENSE

DALERT #

I

DSOUT

I

V

1

C_G32

C_G35

C_G37

C_G38

C_G40

C_G42

C_K33

C_K37

C_K38

C_K40

C_K43

IDSCK

V

2 OF 20

C_J30

C_J33

C_J37

C_J40

C

C_CORE

V

G32

G33

G35

G37

G38

G40

G42

J30

J33

J37

J40

K33

K35

K37

K38

K40

K42

K43

E32

E33

B63

A63

D64

G20

_

CPU_SVIDALRT#

H

_

CPU_SVIDCLK

H

CPU_SVIDDAT

_

H

V

CCFUSEPRG

+

C_SENSE [46]

C

V

S

S_SENSE [46]

V

1 2

0R0603-PAD

7

03

R

C

C

C_CORE

V

D D

701TPAD14-OP-GP

CCCOREG0

P

V

1

T

+

707TPAD14-OP-GP

CCCOREG1

P

V

1

T

+

Vince,20161012

Vince,20161012

C C

A30

A34

A39

A44

AK33

AK35

AK37

AK38

AK40

AL33

AL37

AL40

AM32

AM33

AM35

AM37

AM38

G30

K32

AK32

AB62

P62

V62

H63

G61

AC63

AE63

AE62

AG62

AL63

AJ62

U1L

P

C_A30

C

CC_A34

V

C

C_A39

V

C_A44

C

V

C

C_AK33

V

C_AK35

C

V

C

C_AK37

V

C_AK38

C

V

C

C_AK40

V

C_AL33

C

V

C

C_AL37

V

C_AL40

C

V

CC_AM32

V

C

C_AM33

V

C_AM35

C

V

C_AM37

C

V

CC_AM38

V

C

C_G30

V

V

C

CG0

SVD_K32

R

V

C

CG1

RSVD_AK32

V

CCOPC_ AB62

COPC_P 62

C

V

C

COPC_V 62

V

V

CC_OPC _1P8_H6 3

V

C_OPC_ 1P8_G6 1

C

V

COPC_S ENSE

C

S

SOPC_S ENSE

V

V

C

CEOPIO

CEOPIO

C

V

V

CEOPIO _SENSE

C

SSEOPI O_SENSE

V

V

SKYLAKE-U-GP

CPU POWER 1 OF 4

2016/02/16 modify

SKYLAKE_ULT

#544669 CRB.

7

05

R

1 2

0R0805-PAD

CCGTX_ AK42

C

CGTX_A K43

V

CGTX_A K45

C

V

C

CGTX_A K46

V

CGTX_A K48

C

V

C

CGTX_A K50

V

CGTX_A K52

C

V

C

CGTX_A K53

V

CGTX_A K55

C

V

C

CGTX_A K56

V

CGTX_A K58

C

V

CCGTX_ AK60

V

C

CGTX_A K70

V

CGTX_A L43

C

V

C

CGTX_A L46

V

CCGTX_ AL50

V

C

CGTX_A L53

V

CGTX_A L56

C

V

C

CGTX_A L60

V

CGTX_A M48

C

V

C

CGTX_A M50

V

CGTX_A M52

C

V

CCGTX_ AM53

V

CGTX_A M56

C

V

C

CGTX_A M58

V

CGTX_A U58

C

V

CCGTX_ AU63

V

C

CGTX_B B57

V

V

CGTX_B B66

C

V

CGTX_S ENSE

C

V

S

SGTX_S ENSE

V

V

+

3 OF 20

1

CGT

C

CCGT

V

C

CGT

V

CGT

C

V

C

CGT

V

CGT

C

V

C

CGT

V

CGT

C

V

C

CGT

V

CGT

C

V

C

CGT

V

CGT

C

V

CCGT

V

C

CGT

V

CGT

C

V

CGT

C

V

CCGT

V

C

CGT

V

CGT

C

V

C

CGT

V

CGT

C

V

C

CGT

V

CGT

C

V

CCGT

V

CGT

C

V

V

DDQ_CPU_CLK

V

N70

N71

R63

R64

R65

R66

R67

R68

R69

R70

R71

T62

U65

U68

U71

W63

W64

W65

W66

W67

W68

W69

W70

W71

Y62

AK42

AK43

AK45

AK46

AK48

AK50

AK52

AK53

AK55

AK56

AK58

AK60

AK70

AL43

AL46

AL50

AL53

AL56

AL60

AM48

AM50

AM52

AM53

AM56

AM58

AU58

AU63

BB57

BB66

AK62

AL61

CCGT

+

Vince,20170202

T

X_CORE

G

Follow Kyloren 13" SCH

T

X_CORE

G

T

X_CORE

G

For U42 only

C_CORE

C

V

7

07

R

1 2

U42

D0002R5J-GP-U

C

C_CORE

V

08

7

R

1 2

U42

D0002R5J-GP-U

T

_CORE

G

T

X_CORE

G

SCD1U16V2KX-3DLGP

SCD1U16V2KX-3DLGP

Vince,20170622

CCGT

V

+

7

06

R

1 2

U22

D0002R5J-GP-U

D

2V_S3

1

12

19

7

C

SC1U10V2KX-1GP

DDQ_CPU_CLK

V

+

15SC10U6D3V3MX-GP

7

12

C

V

CCST_CPU

+

16SC1U10V2KX-1GP

7

12

C

V

CCSTG

+

17SC1U10V2KX-1GP

7

12

C

DY

2V_S3

D

1

7

18

12

C

V

CCSFR

+

12

7

20

C

C

C_CORE

V

12

7

19

R

100R2F-L1-GP-U

12

7

20

R

100R2F-L1-GP-U

CCGT

V

+

12

21

7

R

100R2F-L1-GP-U

12

22

7

R

100R2F-L1-GP-U

C

P

U1N

AU23

DQ_AU23

D

AU28

DQ_AU28

D

V

AU35

DDQ_AU3 5

V

AU42

D

DQ_AU42

V

BB23

DQ_BB2 3

D

V

BB32

D

DQ_BB3 2

V

BB41

DQ_BB4 1

D

V

BB47

D

DQ_BB4 7

V

BB51

DQ_BB5 1

D

V

V

AM40

D

DQC

V

A18

CCST

0.04 A

V

A22

CSTG_A 22

C

V

AL23

CPLL_O C

C

V

K20

CPLL_K 20

C

K21

C

CPLL_K 21

V

V

0.12 A

12

7

21

C

S

C

D1U16V2KX-3DLGP

SKYLAKE-U-GP

C_SENSE [46]

C

V

S

S_SENSE [46]

V

Layout Note:

1. Place close to CPU

2. VCC_SENSE/ VSS_SENSE

impedance=50 ohm

3. Length match<25mil

CGT_SENSE [46]

C

V

S

SGT_SENSE [46]

V

CPU POWER 3 OF 4

SKYLAKE_ULT

CIO_SE NSE

C

SSIO_S ENSE

V

V

SSA_SE NSE

S

C

CSA_SE NSE

V

V

V

CCIO

+

4 OF 20

1

CIO

C

CIO

C

V

CCIO

V

C

CIO

V

CIO

C

V

C

CIO

V

CIO

C

V

V

CSA

C

CCSA

V

CSA

C

V

C

CSA

V

CSA

C

V

CCSA

V

C

CSA

V

CSA

C

V

C

CSA

V

CSA

C

V

C

CSA

V

CSA

C

V

C

CSA

V

CSA

C

V

V

CSA_SENSE

C

V

S

SSA_SENSE

V

VCCIO(ICCMAX.=2.73A

+

AK28

AK30

AL30

AL42

AM28

AM30

AM42

V

CCSA

+

AK23

AK25

G23

G25

G27

G28

J22

J23

J27

K23

K25

K27

K28

K30

AM23

AM22

H21

H20

CCSA

V

+

12

35

7

R

100R2F-L1-GP-U

12

7

34

R

100R2F-L1-GP-U

SSA_SENSE [46]

S

V

C

CSA_SENSE [46]

V

Layout Note:

SVID DATA

CCST_CPU

V

+

12

CLOSE TO CPU

B B

_

CPU_SVIDDAT

H

SVID CLOCK

CPU_SVIDCLK

_

H

_

CPU_SVIDALRT#

H

A A

5

220R2J-L2-GP

The total Length of Data and Clock (from CPU to each VR) must be equal (±0.1 inch).

Route the Alert signal betwee n the Clock and the Data si gnals.

#544669

7

26

R

100R2F-L1-GP-U

7

09

1 2

R

0R0402-PAD

V

CCST_CPU

+

12

7

R

54D9R2F-L1-GP

DY

32

7

1 2

R

0R0402-PAD

V

CCST_CPU

+

#544669

12

CLOSE TO CPU

7

27

R

56R2J-4-GP

28

7

R

12

4

23

R

_SVID_ALERT# [46]

V

#544669

CLOSE TO VR

_SVID_DATA [46]

R

V

_SVID_CLK [46]

R

V

SVID_543016:

3

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

1

1

1

A

A

A

Friday, December 08, 2017

Friday, December 08, 2017

Friday, December 08, 2017

Date: Sheetof

Date: Sheetof

2

Date: Sheetof

1

W

W

W

1

1

1

F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

2

2

2

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

P

P

P

U(VCC_CORE)

U(VCC_CORE)

U(VCC_CORE)

C

C

C

arlord KBL-R

arlord KBL-R

arlord KBL-R

t

t

t

S

S

S

i

i

i

stron Corporation

stron Corporation

stron Corporation

7 1

7 1

7 1

A

A

A

06

06

06

0

0

0

0

0

0

5

WWW.AliSaler.Com

4

3

2

1

SSID = CPU

D D

C

1A

PU

H

I_DATA2#[57]

DM

H

DM

I_DATA2[57]

H

DM

I_DATA1#[57]

H

DM

I_DATA1[57]

H

DM

HDMI

Dummy, Vendor suggest

20141117

3

D3

V_S0

D3

V_S0

SRN2K2J -1-GP

1

DY

2 3

R

N8

R

N8

1

2 3

SRN2K2J -1-GP

C

4

_DP1_CT RL_DATA

PU

C

_DP1_CT RL_CLK

PU

01

03

C

4

PU

_DP2_CT RL_DATA

C

_DP2_CT RL_CLK

PU

C C

3

DP and DP to VGA

HDMI

+

VC

Check

CIO

R

80

1 2

24D9R2F -L-GP

C

1

I_DATA0#[57]

H

DM

I_DATA0[57]

H

I_CLK#[57]

DM

H

DM

I_CLK[57]

P

CH

_DPC_N0[38]

P

_DPC_P0[38]

CH

P

CH

_DPC_N1[38]

P

CH

_DPC_P1[38]

P

CH

_DPC_N2[38]

P

_DPC_P2[38]

CH

P

CH

_DPC_N3[38]

P

_DPC_P3[38]

CH

C

PU_DP1_ CTRL_CLK[57]

_DP1_CT RL_DATA[57]

PU

C

PU

_DP2_CT RL_CLK

C

PU

_DP2_CT RL_DATA

E

DP

_COMP

E55

D

DI

1_TXN[0]

F55

D

DI

1_TXP[0]

E58

D

1_TXN[1]

DI

F58

D

1_TXP[1]

DI

F53

D

1_TXN[2]

DI

G53

D

DI

1_TXP[2]

F56

D

DI

1_TXN[3]

G56

D

1_TXP[3]

DI

C50

D

DI

2_TXN[0]

D50

D

DI

2_TXP[0]

C52

D

2_TXN[1]

DI

D52

D

DI

2_TXP[1]

A50

D

DI

2_TXN[2]

B50

D

2_TXP[2]

DI

D51

D

2_TXN[3]

DI

C51

D

DI

2_TXP[3]

L13

G

_E18/DDPB_CTRLCLK

PP

L12

G

_E19/DDPB_CTRLDATA

PP

N7

G

PP

_E20/DDPC_CTRLCLK

N8

G

PP

_E21/DDPC_CTRLDATA

N11

G

_E22/DDPD_CTRLCLK

PP

N12

G

_E23/DDPD_CTRLDATA

PP

E52

E

DP

_RCOMP

SKYLAKE-U-GP

(#543016) The S kylake U/Y pro cessor supports only two DDI ports - Port 1 and Port 2.

SKYLAKE_ULT

DDI

DISPLAY SIDEBANDS

EDP

G

G

G

G

(#543016) eDP_RCOMP Guideline

Signal Trace

Width

eDP_RCOMP 20 mils 25 mils 24.9 Ω ±1%

B B

(#543016) DDI Disabling and Termination Guidelines

Port Strap Enable Port Disable Port

Port 1

DDPB_CTRLDATA

Port 2

DDPC_CTRLDATA

Isolation

Spacing

PU to 3.3 V wit h 2.2-k

±5% resistor

PU to 3.3 V wit h 2.2-k

±5% resistor

Resistor

Value

Length

Max = 100 mils

NC

NC

S

IO

_EXT_SM I#

1 2

R

80

2 1 0KR2J-3-GP

3

D3

V_S0

E

DP

E

DP

E

DP

E

DP

E

DP

E

DP

E

DP

E

DP

E

DP

E

DP

E

DP

_DISP_UTIL

D

DI

D

DI

D

DI

D

DI

D

DI

D

DI

_E13/DDPB_HPD0

PP

PP

_E14/DDPC_HPD1

PP

_E15/DDPD_HPD2

PP

_E16/DDPE_HPD3

G

PP

_E17/EDP_HPD

E

_BKLTEN

DP

E

DP

_BKLTCTL

E

DP

1

OF 20

_TXN[0]

_TXP[0]

_TXN[1]

_TXP[1]

_TXN[2]

_TXP[2]

_TXN[3]

_TXP[3]

_AUXN

_AUXP

1_AUXN

1_AUXP

2_AUXN

2_AUXP

3_AUXN

3_AUXP

_VDDEN

C

PU

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

_DP2_HP D

TypeC

E

DP

_DISP_UTIL

C

_DP2_HP D

PU

S

IO

_EXT_SM I#

1 2

R

80

4 0R2J-2-GP

TypeC

R

80

3

100KR2J -1-GP

1 2

E

DP

_TX0_DN [55 ]

E

_TX0_DP [55]

DP

E

_TX1_DN [55 ]

DP

E

DP

_TX1_DP [55]

E

DP

_TX2_DN [55 ]

E

_TX2_DP [55]

DP

E

DP

_TX3_DN [55 ]

E

_TX3_DP [55]

DP

E

_AUX_DN [55]

DP

E

_AUX_DP [55]

DP

1

T

01 TPAD1 4-OP-GP

P8

D

PB_AUXN [38]

D

PB

C

_DP1_HP D [57]

PU

Vince,20161018

E

_HPD [55]

DP

L

L

_B

KLT_CTR L [55]

E

_VDD_EN [55]

DP

_AUXP [38]

_B

KLT_EN [24,55]

C

PU

_DP_HPD _R [37,38 ,57]

A A

Design Guidelin e:

Skylake process or signal eDP_ RCOMP should be connected to the VCCIO rai l via a single 24.9 ±1% Ω res istor.

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

W

W

W

is

is

is

tron Corporation

tron Corporation

tron Corporation

2

2

2

1F

1F

1F

, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C .

Taipei Hsien 221, Taiwan, R.O.C .

Taipei Hsien 221, Taiwan, R.O.C .

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A

A

A

3

3

3

Date: Sheet

Date: Sheet

Date: Sheet

C

C

C

PU

PU

PU

_(DISPLAY)

_(DISPLAY)

_(DISPLAY)

S

S

S

ta

ta

ta

rlord KBL-R

rlord KBL-R

rlord KBL-R

8 10

8 10

8 10

1

o

o

o

f

f

f

00

00

00

A

A

A

6Friday, December 08, 2017

6Friday, December 08, 2017

6Friday, December 08, 2017

5

4

3

2

1

Main Func = CPU

D D

C C

(Blanking)

B B

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

W

W

W

i

i

i

stron Corporation

stron Corporation

stron Corporation

2

2

2

1

1

1

F, 88, Sec.1, Hsin T ai Wu Rd., Hsichih,

F, 88, Sec.1, Hsin T ai Wu Rd., Hsichih,

F, 88, Sec.1, Hsin T ai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C .

Taipei Hsien 221, Taiwan, R.O.C .

Taipei Hsien 221, Taiwan, R.O.C .

T

tle

Title

Title

i

(

(

(

eserved)

eserved)

eserved)

R

R

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Date: Sheet

Date: Sheet

Date: Sheet

R

A

A

A

3

3

3

S

S

S

t

t

t

arlord KBL-R

arlord KBL-R

arlord KBL-R

9 1

9 1

9 1

1

o

o

o

f

f

f

0

0

0

0

0

0

A

A

A

06Monday, August 2 8, 2017

06Monday, August 2 8, 2017

06Monday, August 2 8, 2017

SSID = CPU

WWW.AliSaler.Com

5

4

3

2

1

D D

CORE

U-line 23e 28W

IccMax current-10ms max = 34 A

22U 0603 x 35(5 DY)

CC

_CORE

V

002

C1

P

12

C1

011

P

12

022

C1

P

C C

12

005

004

003

C1

C1

C1

P

P

P

12

12

12

S

C2

2U6D3V3MX-1-GP

S

C2

2U6D3V3MX-1-GP

S

C2

2U6D3V3MX-1-GP