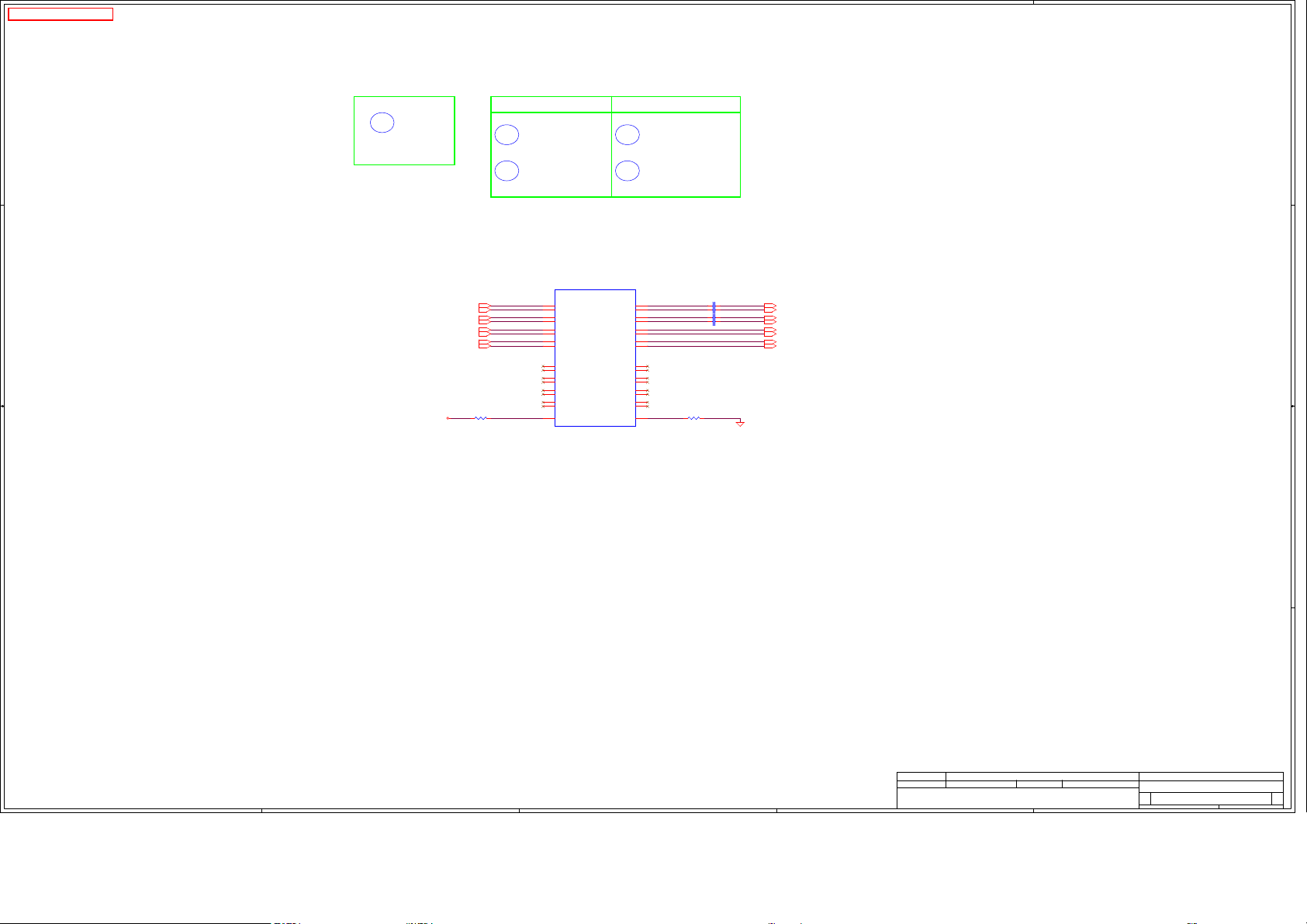

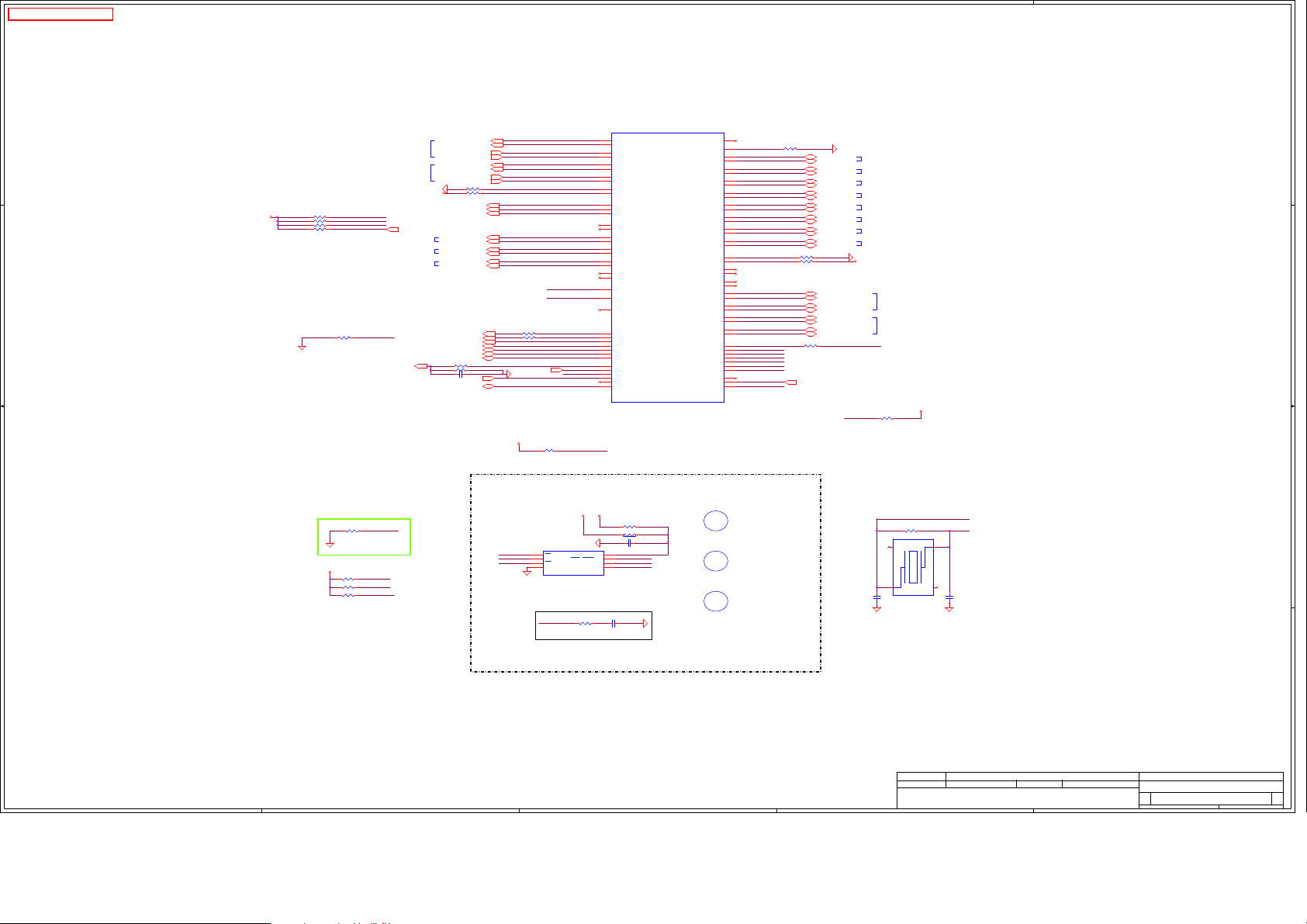

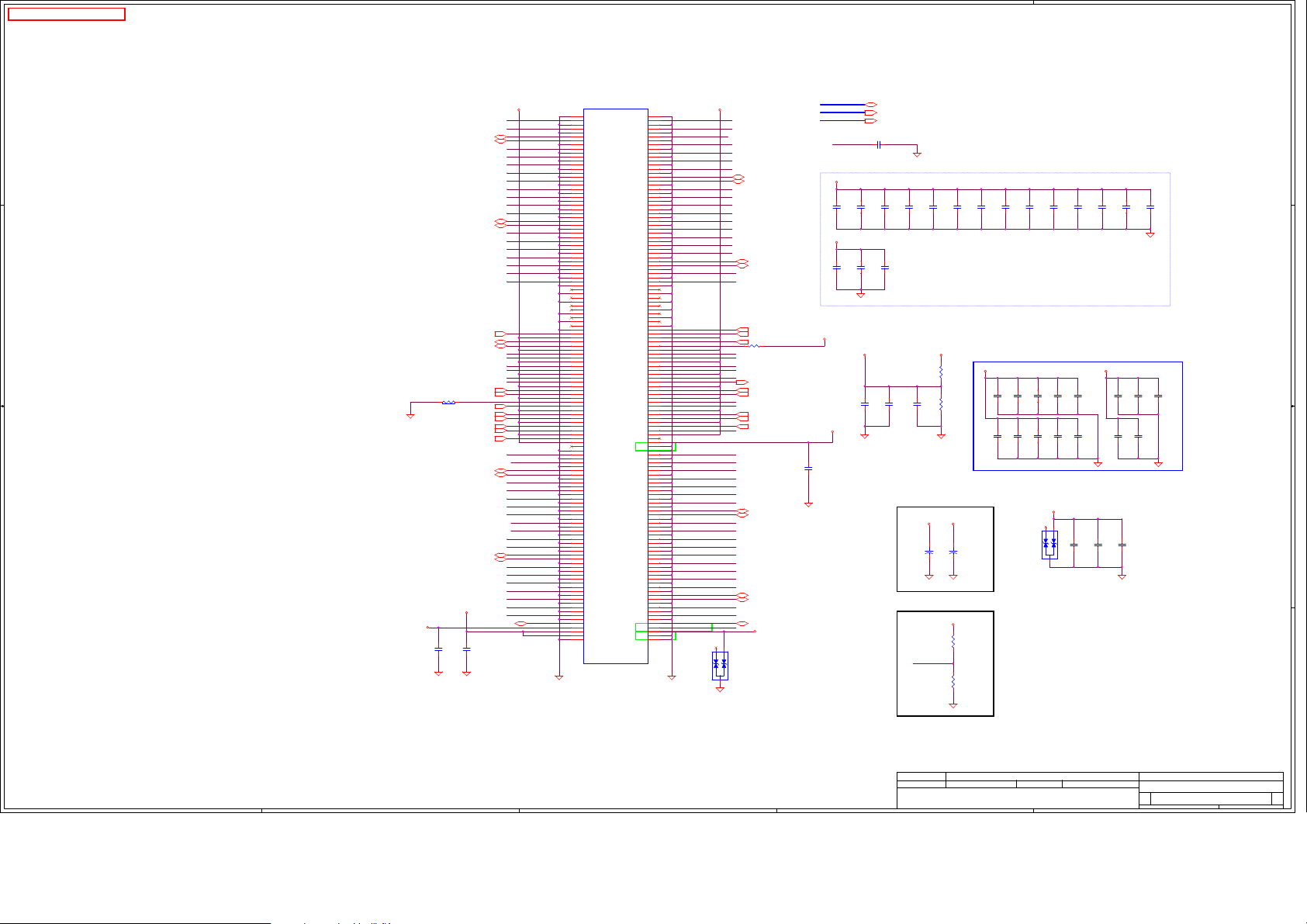

Dell Inspiron 3493 Schematics

5

PROJECT NAME : LA-H872P

PCB NO : DA60026R000

D D

C C

4

3

2

1

Dell / Compal Confidential

Schematic Document

AMD Stoney Ridge

2018-05-21 Rev: 1.0 (A00)

B B

A A

Security C lassification

Security C lassification

Security C lassification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

2016/01/07 2017/01/07

2016/01/07 2017/01/07

2016/01/07 2017/01/07

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

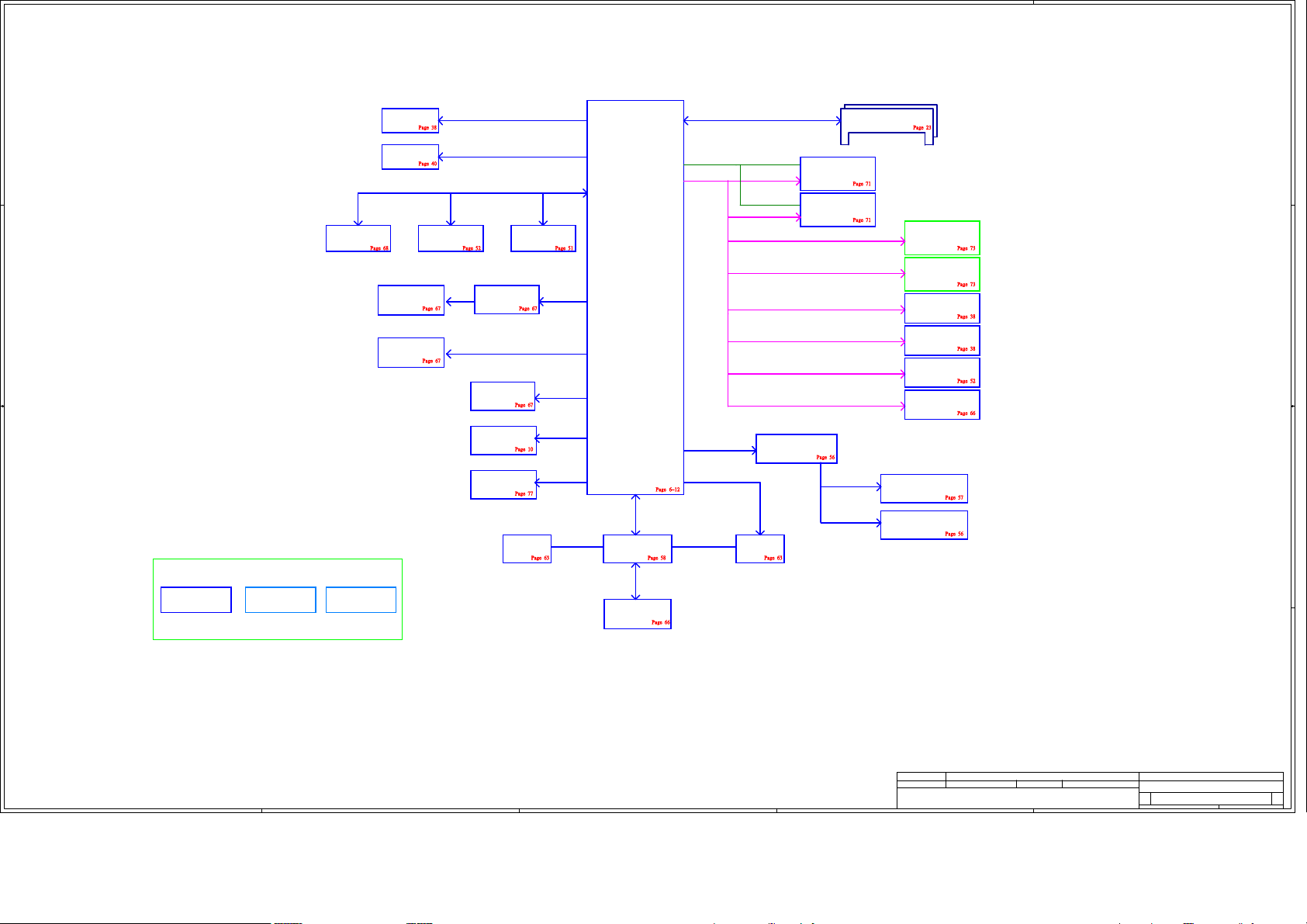

Cover Page

Cover Page

Cover Page

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

LA-H872P

LA-H872P

LA-H872P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

1 102Wednes day, June 05, 2 019

1 102Wednes day, June 05, 2 019

1 102Wednes day, June 05, 2 019

1.0(A00)

1.0(A00)

1.0(A00)

5

4

3

2

1

USB 3.0

USB 2.0

USB 3.0

USB 2.0

Page 56

Max DDR Rate: 2133 MHz

DDR4-DIMM x1

1.2V DDR4

JUSB1

Page 71

JUSB2

Page 71

Headphone Jack

Int. Speaker R / L

Page 23

Card Reader

(IO/B)

USB 2.0

JIOB1

(IO/B)

Touch Screen

Digital Camera

(With DMIC)

NGFF 2230

WiFi/BT4.0

Finger Printer

Page 57

Page 56

Page 73

Page 73

Page 38

Page 38

Page 52

Page 66

D D

eDP Conn.

HDMI Conn.

x2 Lane

SSD

Class 35 RTS514 4

Page 68

Page 38

Page 40

Port 1Port 2,3

NGFF 2230

WiFi/BT4.0

DDI-DP0

DDI-DP1

x1 Lane

Page 52

Port 0

LAN 10/1 00

Giga (Reserve)

GEN3 GEN1

SATA HDD

Page 67

C C

Connector

Port 0

SATA Redr iver

PS8527 C

DP1.2

HDMI1.4b

(w/o 4K2K support)

PCI-E

25 MHz

x1 Lane

Page 51

GEN1

SATA3.0

Page 67

AMD

Stoney FT4

Processor

BGA 769

TDP 15W

L2 Cache: 1M

Memory Bus

Slave Address: 000

USB 3.0

USB2.0

Support 1 Channel

Port 1

Port 5

Port 2

Port 6

Port 0

Port 1

Port 2

Core Count: 2

Port 3

Port 4

Port 7

Audio Codec

ALC3204-C G

Touch Pad

Page 63

Page 67

Page 10

Page 77

Page 63

SATA1.0

SMBUS

PWM

KSI/KSO

SPI

32.768 KHz

48 MHz

LPC Bus

32.768 KHz (@)

ENE KBC

KB9542Q-E

Page 58

Page 6~12

HDA

I2C

PS/2

SATA ODD

Connector

Page 67

Port 1

FFS (Reserve)

SPI ROM

16MB

FAN Conn.

B B

SUB-BOARDS

Int. KB

with KBBL

SMBus

IO/B (AMD) PWR/B

LS-H871PR1 0 LS-F114PR1 0 LS-F122PR1 0

A A

5

ODD/B (AMD)

Thermal Sensor

G781(0 x9A)

4

Page 66

Security C lassification

Security C lassification

Security C lassification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

2016/01/07 2017/01/07

2016/01/07 2017/01/07

2016/01/07 2017/01/07

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

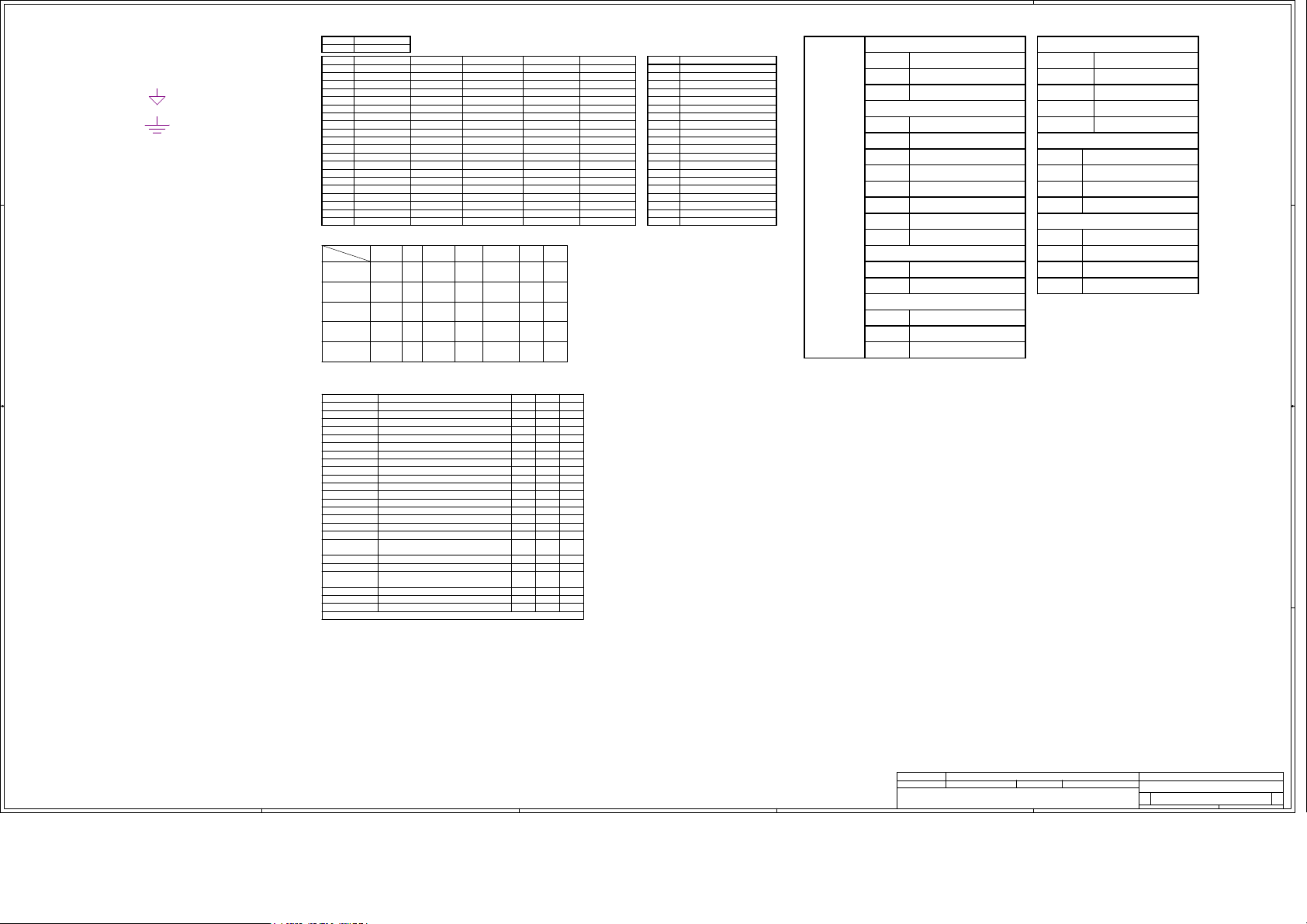

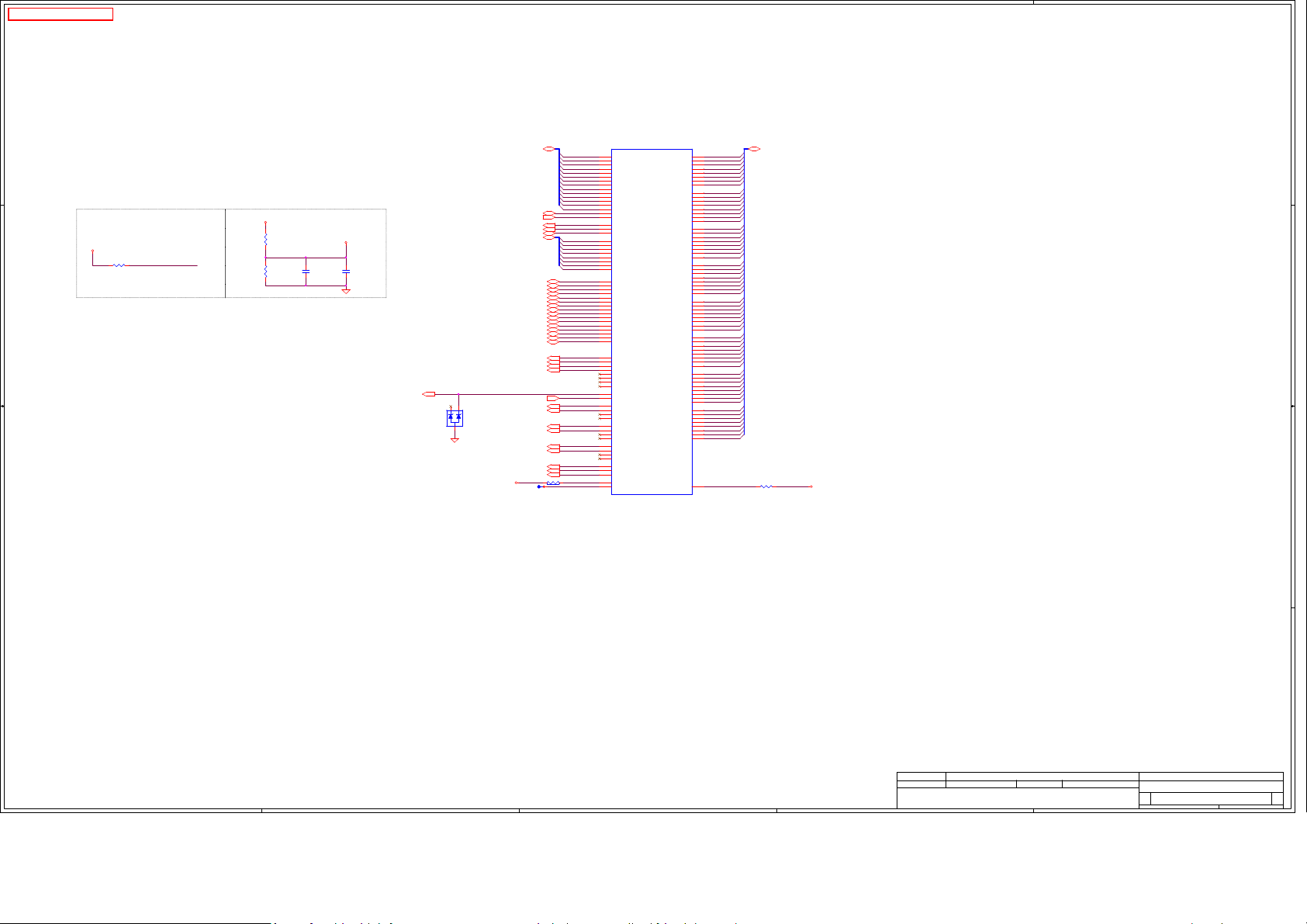

Block Diagram

Block Diagram

Block Diagram

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

LA-H872P

LA-H872P

LA-H872P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

2 102Wednes day, June 05, 2 019

2 102Wednes day, June 05, 2 019

2 102Wednes day, June 05, 2 019

1.0(A00)

1.0(A00)

1.0(A00)

5

Board ID Table for AD Channel:

Vcc 3.3V +/- 1%

Board ID Board ID

Symbol Note :

D D

: Means Digital Ground

: Means Analog Ground

0

1

2

3

4

5

6

7 56K +/- 1%

8

9

10

11

12

13

14

15 330K +/- 1%

16

17

18

19 N C

SMBUS Control Table:

EC_SMB_CK1

EC_SMB_DA1

EC_SMB_CK2

C C

EC_SMB_DA2

TP_CLK

TP_DATA

APU_SCLK0

APU_SDATA0

APU_SIC

APU_SID

4

100K +/- 1%Ra(RE5)

Rb(RE9) V

0 ohm 0.000 V

12K +/- 1%

15K +/- 1%

20K +/- 1%

27K +/- 1%

33K +/- 1%

43K +/- 1%

75K +/- 1% 1.398 V

100K +/- 1%

160K +/- 1%

200K +/- 1%

240K +/- 1%

270K +/- 1%

430K +/- 1%

560K +/- 1%

750K +/- 1%

SOURCE

KB9542Q

KB9542Q

KB9542Q

BATT

V

APU

APU

AD_BID

0.347 V

0.423V

0.541 V

0.691 V

0.807 V

0.978 V 0.9 92V

1.169 V

1.634 V

1.849 V 1.8 65V

2.015 V

2.185 V

2.316 V

2.395 V 2.4 08V

2.521 V

2.667 V

2.791 V

2.905 V 2.9 12V

3.000 V

Charger

V

min

V typ

Thermal

Sensor

V

V

Touch Pad

DIMM

V

AD_BID

0.360 V

0.438 V

0.559 V

0.713 V

0.831 V

1.006 V

1.200 V

1.667 V

1.881 V130K +/- 1%

2.046 V

2.215 V

2.343 V

2.421 V

2.544 V

2.687 V

2.808 V

2.919 V

3.300 V

AD_BID

0.000 V 0.300 V

0.354 V

0.430 V

0.550 V

0.702 V

0.819 V

1.185 V

1.414 V 1.430 V

1.650 V

2.031 V

2.200 V

2.329 V

2.533 V

2.677 V

2.800 V

3.300 V

V

V

3

max

EC AD3

0x00 - 0x13

0x14 - 0x1E

0x1F - 0x25

0x26 - 0x30

0x31 - 0x3A

0x3B - 0x45

0x46 - 0x54

0x55 - 0x64

0x65 - 0x76

0x77 - 0x87

0x88 - 0x96

0x97 - 0xA4

0xA5 - 0xAF

0xB0 - 0xB7

0xB8 - 0xBF

0xC0 - 0xC9

0xCA - 0xD4

0xD5 - 0xDD

0xDE - 0xF0

0xF1 - 0xFF

FFS

BOARD ID Table:

0

N3V3 MLK STR UMA <EVT>

1

N3V3 MLK STR UMA <DVT1>

2

N3V3 MLK STR UMA <DVT2>

3

N3V3 MLK STR UMA <PVT>

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

Definition

N/A

N/A

N/A

N/A

N/A

N/A

N/A

N/A

N/A

N/A

N/A

N/A

N/A

N/A

N/A

N/A

HS I/O

2

USB3.0

Port 0

---

USB3 Connector Port 1

Port 1

USB3 Connector Port 2

Port 2

USB2.0

Port 0

Card Reader (IO/B)

Port 1

USB2 Connector Port (IO/B)

Port 2

Touch Screen

Camera

Port 3

WLAN

Port 4

Port 5

USB2 Connector Port 1

Port 6

USB2 Connector Port 2

Finger Printer

Port 7

SATA

HDD

Port 0

Port 1

ODD

GFX_CLK

GPP_CLK0

GPP_CLK1

GPP_CLK2

GPP_CLK3

Lane 0

Lane 1

Lane 2

Lane 3

Lane 0

Lane 1

Lane 2

Lane 3

1

Clock Signal

---

LAN

WLAN

NVMe SSD

---

PCI Express(GFX)

---

---

---

---

PCI Express(GPP)

LAN

WLAN

NVMe SSD

NVMe SSD

Display(DP)

Port 0

V

eDP (Lan0/Lan1)

Port 1

HDMI (Lan0/Lan1/Lan2/Lan3)

Port 2

---

Voltage Rails

+19V_VIN

+17.4V_BATT++

+19VB

+5VALW

+3VALW

+1.8V_ALW

+0.95VALW

+0.775VALW

+1.2V_DDR

+0.6V_DDR_VTT

+2.5V_MEM

+5VS

B B

+3VS

+1.8VS

+0.95VS

+APU_CORE

+APU_CORE_NB

+VDDCR_FCH_ ALW

+3VLP

+RTCVCC

+0.95VS_APU_G FX

+3VS_APU

Adapter power supply

Battery power supply

AC or DC for power circuit

System +5VALW power rail

System +3VALW power rail

System +1.8VALW power rail

System +0.95VALW power rail

System +0.775VALW power rail

DDR4 +1.2V power rail

DDR4 +0.6V power rail

DDR4 +2.5V power rail

System +5VS power rail

System +3VS power rail

System +1.8VS power rail

System +0.95VS power rail

Core voltage for APU

Core NB voltage for APU

S5 supply voltage for the FCH core logic

+19VB to +3VLP power rail for suspend power

RTC power

PCIe GPP, PCIe GFX, DP and SATA PHY logic power

rail for APU

+3VS power rail for APU

S0 S3 S4/S5Power Plane Description

N/A

N/A

N/A

N/A

N/A

N/A

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

OFF OFF

ON

OFF OFF

ON

OFF OFF

ON

OFF OFF

ON

OFF OFF

ON

OFF OFF

ON

OFF OFF

ON

ONON

ON ON ON

OFF OFF

ON

OFF OFF

ON

N/A

N/A

N/A

ON*

ON*

ON*

ON*

ON*

OFF

OFFOFF

OFF

ON

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF

A A

Security C lassification

Security C lassification

Security C lassification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

2016/01/07 2017/01/07

2016/01/07 2017/01/07

2016/01/07 2017/01/07

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

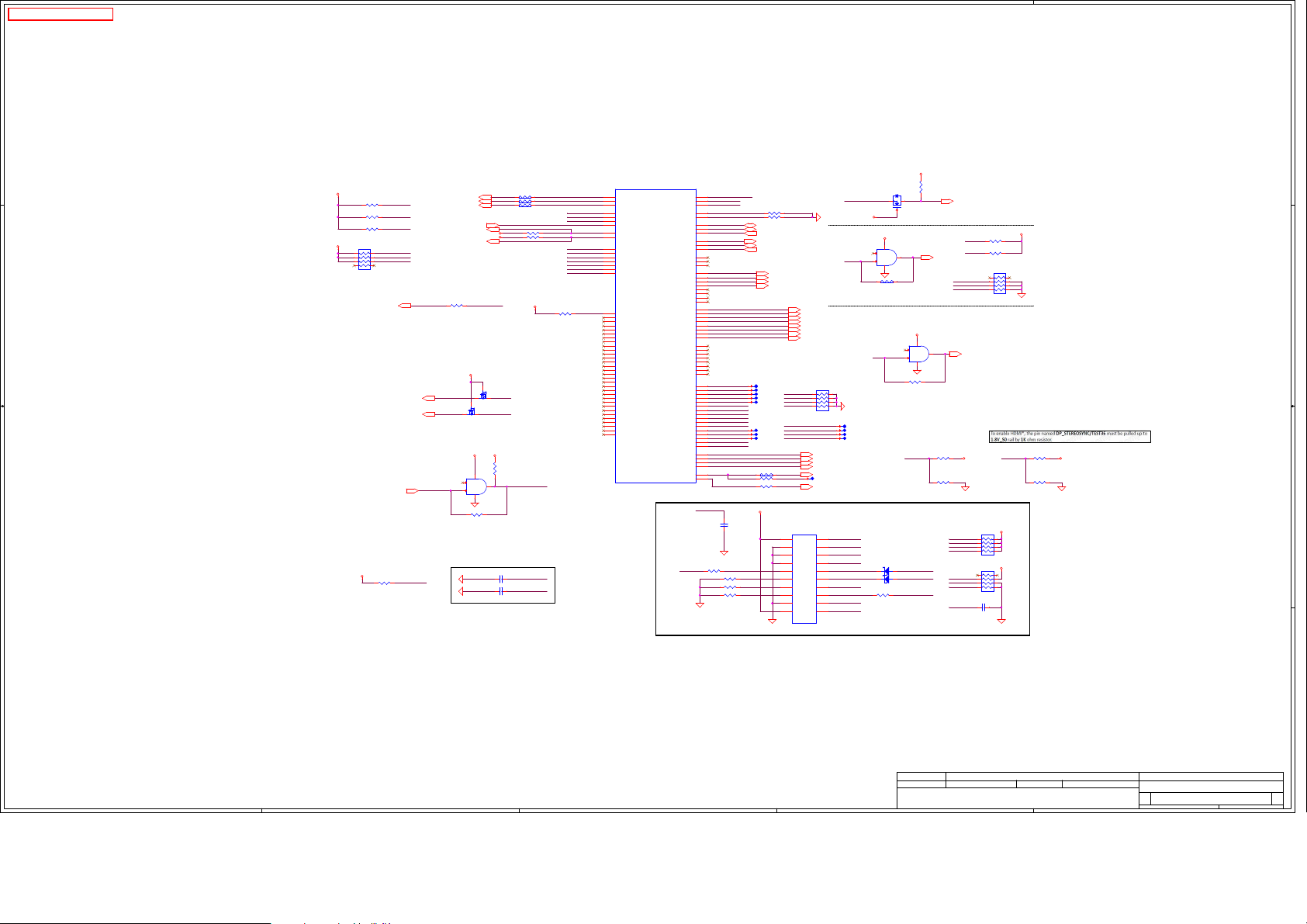

Notes List

Notes List

Notes List

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

LA-H872P

LA-H872P

LA-H872P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

3 102Wednes day, June 05, 2 019

3 102Wednes day, June 05, 2 019

3 102Wednes day, June 05, 2 019

1.0(A00)

1.0(A00)

1.0(A00)

5

4

3

2

1

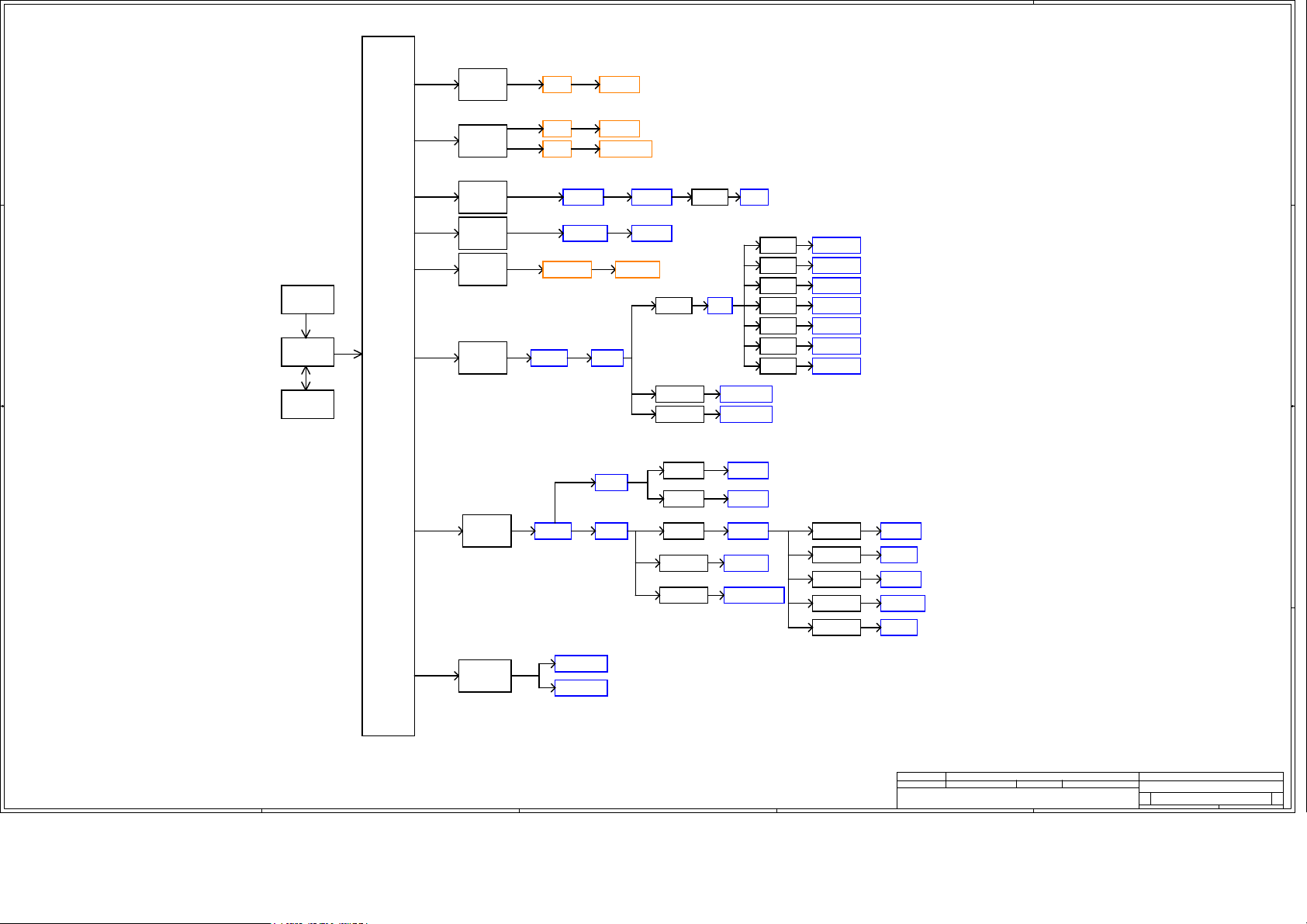

PU2501

PWM

D D

CPU PWR

Peripheral Device PWR

C C

ADAPTER

PUB01

CHARGER

ISL95522HRZ-T

+PWR_SRC

(+19VB)

RT6226AGQUF

PUM01

PWM

RT8207PGQW

PU1801

PWM

RT8061AZQW

PUH01

PWM

RT6226AGQUF

PU800

PWM

G2992F1U

PU501

PWM

SY8288CRAC

BATTERY

B B

PU301

PWM

SY8286BRAC

P.86

P.86

P.87

P.87

P.91

P.85

P.85

SYSON

+2.5VP

SYSON

+1.2VP +1.2V_DDR

SUSP#

+0.6VSP +0.6V_DDR_VTT

0.95_1.8VAL W_PWRE N

0.95_1.8VAL W_PWRE N

0.775PW_EN#

VDDCR_FCH_S5

EN_5V

+5VALWP +5VALW

EN_3V

+3VALWP

PJP250 2

PJPM0 2

PJPM0 3

+1.8VALWP

+0.95VALWP

PJP50 2

PJP30 2

+2.5V_MEM

PJP80 2

+3VLP

+3VALW

PJP180 2

PJPH02

+1.8V_ALW

+0.95VALW

+0.775VALW

SUSP#

USB_EN#

USB_EN#

SUSP#

WOL_EN

WLAN_EN

SUSP# J3

U3

EM5209 VF

J1

J2

U2

EM5209 VF

UU1

SY6288 D20A AC

UU2

SY6288 D20A AC

RE2

0_0603_5%

+5VS

JP2 +CHGRTC

J4

U2

EM5209 VF

UL2

SY6288C20AAC

UW1

SY6288C20AAC

+1.8VS

+5V_USB_PWR1

+5V_USB_PWR2

+3VALW_EC

+3VS

+LAN_VDD33

+3VS_WLAN_NGF F

R20

0_0603_5%

+VDD_TOUCH

FV2

RA1

0_0805_5%

RA34

0_0603_5%

F3

JP3 +5V_HDD

ENVDD

SY6288C20AAC

+5V_HDMI

+5V_PVDD

+5V_AVDD

+5VS_KBL

+5VS_ODDJP4

RC122

0_0402_5%

UV1

RA33

0_0402_5%

R27

0_0603_5%

+3VS_APU

+LCDVDD

+3V_DVDD

+3VS_TOUCH

+3VS_SSDJP5

PLZ02

PUZ01

P.89

PWM

ISL62771HRTZ-T

A A

5

4

VR_ON

PLZ04

+APU_CORE_NB

+APU_CORE

Security C lassification

Security C lassification

Security C lassification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

2016/01/07 2017/01/07

2016/01/07 2017/01/07

2016/01/07 2017/01/07

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Power Map

Power Map

Power Map

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

LA-H872P

LA-H872P

LA-H872P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

4 102Wednes day, June 05, 2 019

4 102Wednes day, June 05, 2 019

4 102Wednes day, June 05, 2 019

1.0(A00)

1.0(A00)

1.0(A00)

5

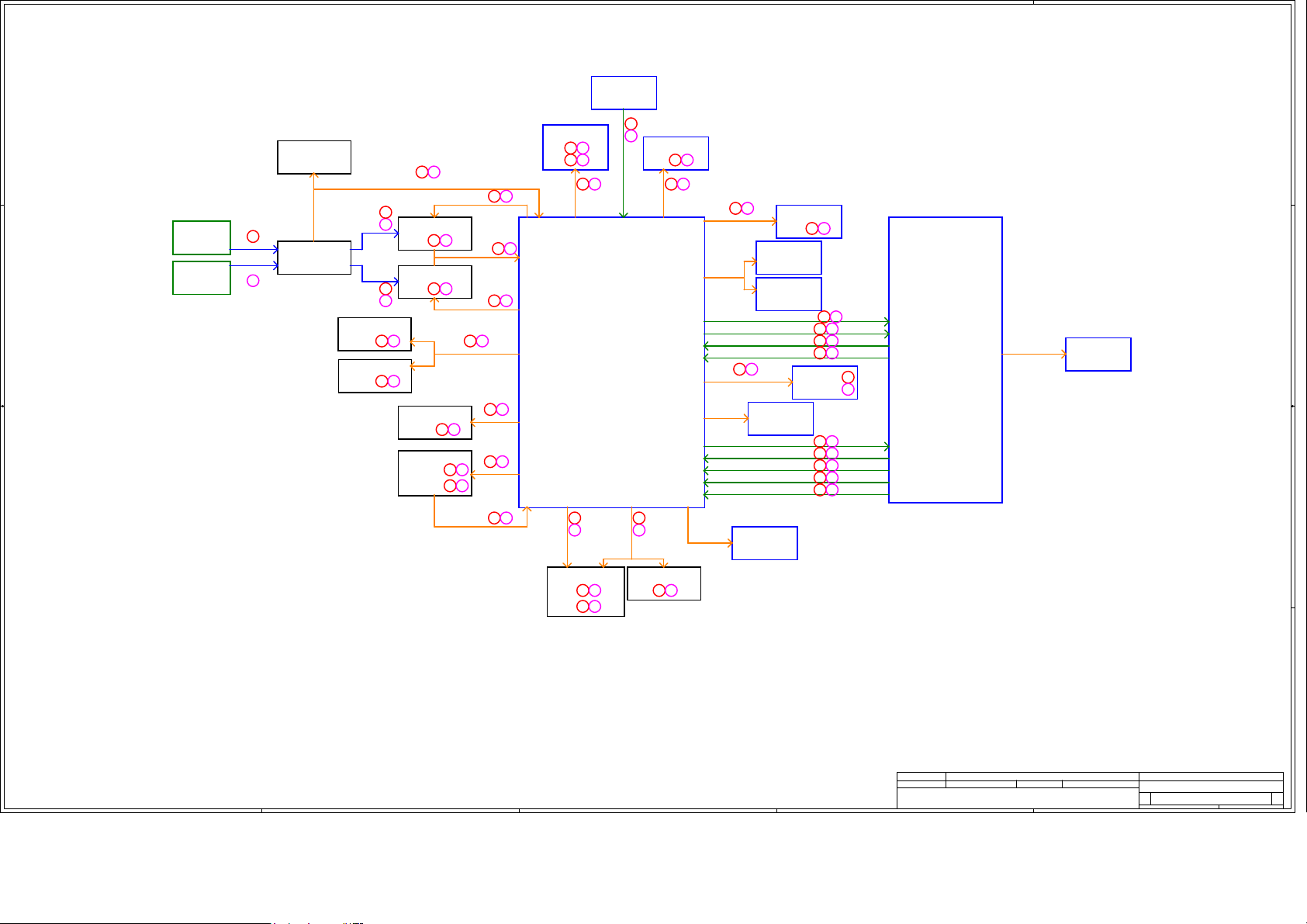

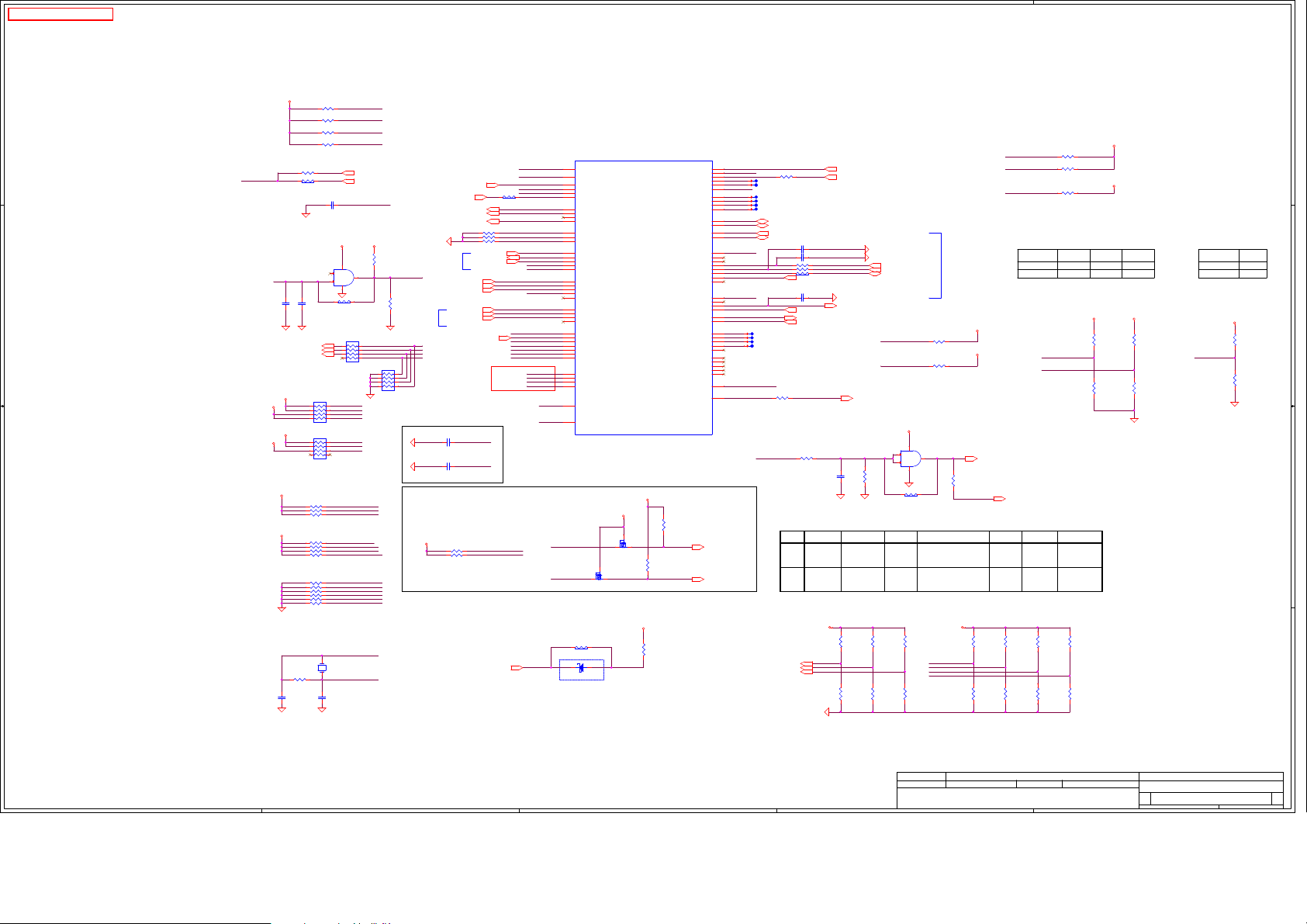

Platform Power Sequence

LA-H872P

4

3

2

1

2019/4/26

D D

U2 (3/5V)

EM5209VF

PU900 (SMOKE)

AZV3002

A2

B2

AC Mode

(PJPDC1)

DC Mode

(PBATT1)

C C

B B

A1

+19V_VIN

+17.4V_BATT+

B1

PUB01 (Charger)

ISL95522

+19VB

+19VB

PU1801 (1. 8V)

RT806 1

A8

+1.8V_ALW

PUH01 (0.95V)

RT622 6

A9

+0.95VALW

A2

B2

A3

HW_ACAV_IN

PU301 (3V)

SY8286

+3VALW

PU501 (5V)

SY8288

+5VALW

B9

B10

PU800 (0 .775V)

APL533 6

+0.775VALW

PUZ01 (CORE)

ISL62771

+APU_CORE

+APU_CORE_NB

B3

B5

A5

B5

A5

0.95_1.8VALW_PWREN

B12

A11

A28

A28

B28

B28

EC_ON

EC_ON

A7

VGATE

A4

A6

POK

A4

B7

A10

B11

0.775PW_EN#

B27

A27

VR_ON

A29

+3VS

+5VS

B4

B6

B4

B29

PUM01 (0. 6/1.2V)

RT820 7

+1.2VP

+0.6VSP

JPWR1

Power Button

A12

B8

B23

A23

B24

A24

A20 A20

SUSP#

ON/OFF#

B20 B20

UE1

KB9542Q-E

LQFP128

14X14

A20

B20

SUSP#

A18

A21

A17

B17

SYSON

PU2501 (2. 5V)

RT905 9

B18

+2.5VP

B21

U3 (1.8V)

EM5209VF

+1.8VS

SUSP#

B19

A19

B22

A22

B25

A25

0.95VS_PWR_EN#

USB_EN#

0.95_1.8VALW_PWREN

WOL_EN

B30

A30

UL2 (LAN_VDD )

SY6288

+LAN_VDD3 3

U4 (0.95V)

EMB04N03 G

+0.95VS

UU1 (USB)

SY62 88D

+5V_USB_PWR1

UU2 (USB IO/B)

SY6288 D

+5V_USB_PWR2

EC_RSMRST#

PBTN_OUT#

PM_SLP_S5#

PM_SLP_S3#

U6 (+VDDCR)

EM5028V

+VDDCR_FCH_ALW

APU_FCH_POK

APU_PWRGD

PLT_RST#

APU_PCIE_RST#

APU_RST#

B26

A26

B14

A14

B13

A13

B15

A15

B16

A16

A31

B31

B32

A32

B33

A33

B34

A34

B35

A35

B36

A36

UC1

Stoney FT4

15W

ENVDD

UV1 (LCDVDD)

SY6288

+LCDVDD

All sequence is complete.

UW1 (WLAN_VDD)

WLAN_EN

SY6288

+3VS_WLAN_NGFF

A A

Security C lassification

Security C lassification

Security C lassification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

2016/01/07 2017/01/07

2016/01/07 2017/01/07

2016/01/07 2017/01/07

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Power Sequence Diagram

Power Sequence Diagram

Power Sequence Diagram

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

LA-H872P

LA-H872P

LA-H872P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

5 102Wednes day, June 05, 2 019

5 102Wednes day, June 05, 2 019

5 102Wednes day, June 05, 2 019

1.0(A00)

1.0(A00)

1.0(A00)

Main Func = CPU

5

4

3

2

1

D D

C C

B B

ZZZ

X4E@

SMT EMC STR EE UMA AH872 FDI52

X4EAI931L01

+0.95VS_ APU_GF X

PCIE_A RX_DTX _P0[51]

PCIE_A RX_DTX _N0[51]

PCIE_A RX_DTX _P1[52]

PCIE_A RX_DTX _N1[52]

PCIE_A RX_DTX _P2[68]

PCIE_A RX_DTX _N2[68]

PCIE_A RX_DTX _P3[68]

PCIE_A RX_DTX _N3[68]

LAN LAN

WLAN WLAN

SSD SSD

EMC X4E for BOM control:

2019/02/12: Change to D Mark P/N

UC1

S IC A6-9225 AM9225AYN23AC 2.6G APU S

UC1

S IC A9-9425 AM9425AYN23AC 3.1G APU S

PCIE_A RX_DTX _P0

PCIE_A RX_DTX _N0

PCIE_A RX_DTX _P1

PCIE_A RX_DTX _N1

PCIE_A RX_DTX _P2

PCIE_A RX_DTX _N2

PCIE_A RX_DTX _P3

PCIE_A RX_DTX _N3

1 2

RC1 196_0402_1 %

15W APU R1 P/N 15W APU R3 P/N

(NPI used D Mark P/N)

SA0000BGT2L

A6_R1@

(NPI used D Mark P/N)

SA0000BGS2L

A9_R1@

UC1B

U4

P_GPP_RXP0

U5

P_GPP_RXN0

R8

P_GPP_RXP1

R10

P_GPP_RXN1

R5

P_GPP_RXP2

R4

P_GPP_RXN2

N4

P_GPP_RXP3

N5

P_GPP_RXN3

L5

P_GFX_RXP0

L4

P_GFX_RXN0

J5

P_GFX_RXP1

J4

P_GFX_RXN1

G5

P_GFX_RXP2

G4

P_GFX_RXN2

D7

P_GFX_RXP3

E7

P_GFX_RXN3

U8

P_ZVDDP

2D3201 AJN23AC _BGA7 69~D

UC1

S IC A6-9225 AM9225AYN23AC 2.6G APU A31!

UC1

S IC A9-9425 AM9425AYN23AC 3.1G APU A31!

Note: Cap place on the TX side, and AMD spec define the length need to >= 500mils

PCIE

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

P_ZVSS

FT4 REV 1 .01

@

SA0000BGT1L

A6_R3@

SA0000BGS1L

A9_R3@

0.1uF is for PCIE Gen2

0.22uF is for PCIE Gen2 & 3

CL13/CL14: Place near APU

CC1/CC2: Place near APU

PCIE_A TX_DRX _P0

D2

PCIE_A TX_DRX _N0

D1

PCIE_A TX_DRX _P1

C2

PCIE_A TX_DRX _N1

C1

PCIE_A TX_DRX _P2

B2

PCIE_A TX_DRX _N2

B1

PCIE_A TX_DRX _P3

A3

PCIE_A TX_DRX _N3

B3

A4

B4

A5

B5

A6

B6

A7

B7

P_ZVSSP_ZVDD P

1 2

W8

RC2 196_0402_1 %

1 2

CL13 0.1U_0 201_1 0V6K

1 2

CL14 0.1U_0 201_1 0V6K

1 2

CC1 0.1U_0 201_10 V6K

1 2

CC2 0.1U_0 201_10 V6K

PCIE_A TX_C_D RX_P0 [51]

PCIE_A TX_C_D RX_N0 [51 ]

PCIE_A TX_C_D RX_P1 [52]

PCIE_A TX_C_D RX_N1 [52 ]

PCIE_A TX_DRX _P2 [68]

PCIE_A TX_DRX _N2 [68]

PCIE_A TX_DRX _P3 [68]

PCIE_A TX_DRX _N3 [68]

A A

Security C lassification

Security C lassification

Security C lassification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

2014/06/10 2015/06/30

2014/06/10 2015/06/30

2014/06/10 2015/06/30

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

FP4 PCIE/UMI

FP4 PCIE/UMI

FP4 PCIE/UMI

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

LA-H872P

LA-H872P

LA-H872P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

6 102Wednes day, June 05, 2 019

6 102Wednes day, June 05, 2 019

6 102Wednes day, June 05, 2 019

1.0(A00)

1.0(A00)

1.0(A00)

5

4

3

2

1

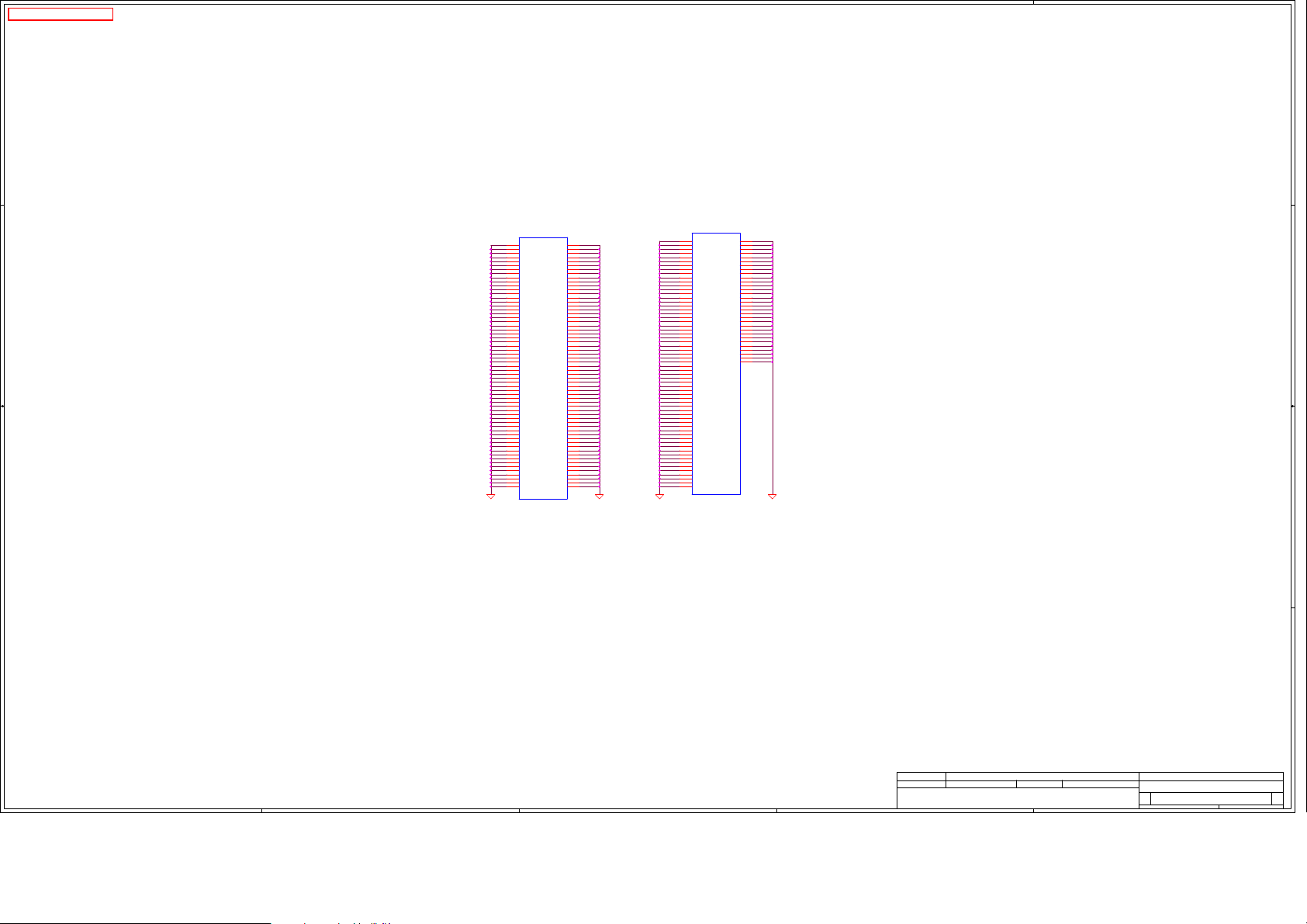

Main Func = CPU

D D

DDR_A_ ADD[13..0 ][23]

DDR_A_ BG1[23]

+MEM_VREF

DDR_A_ ACT#[23]

DDR_A_ BA0[23 ]

DDR_A_ BA1[23 ]

DDR_A_ BG0[23]

DDR_A_ DM[7..0][23]

DDR_A_ DQS0[23]

DDR_A_ DQS#0[23]

DDR_A_ DQS1[23]

DDR_A_ DQS#1[23]

DDR_A_ DQS2[23]

DDR_A_ DQS#2[23]

DDR_A_ DQS3[23]

DDR_A_ DQS#3[23]

DDR_A_ DQS4[23]

DDR_A_ DQS#4[23]

DDR_A_ DQS5[23]

DDR_A_ DQS#5[23]

DDR_A_ DQS6[23]

DDR_A_ DQS#6[23]

DDR_A_ DQS7[23]

DDR_A_ DQS#7[23]

DDR_A_ EVENT#[23]

EVENT# pull high 0.6V reference voltage

+1.2V_DD R

1 2

RC6 1K _0402_ 5%

C C

B B

DDR_A_ EVENT#

+1.2V_DD R

1 2

1 2

RC5

1K_040 2_1%

RC7

1K_040 2_1%

1

CC3

1000P_ 0402_5 0V7K

2

+MEM_VREF

15mil

1

CC4

0.1U_020 1_10V6 K

2

DDR_A_ RST#[23]

2

3

DC1

CEST52 3NC5VB 3 P C/A SOT -523

@ESD@

1

DDR_A_ ADD0

DDR_A_ ADD1

DDR_A_ ADD2

DDR_A_ ADD3

DDR_A_ ADD4

DDR_A_ ADD5

DDR_A_ ADD6

DDR_A_ ADD7

DDR_A_ ADD8

DDR_A_ ADD9

DDR_A_ ADD10

DDR_A_ ADD11

DDR_A_ ADD12

DDR_A_ ADD13

DDR_A_ BG1

DDR_A_ ACT#

DDR_A_ BG0

DDR_A_ DM0

DDR_A_ DM1

DDR_A_ DM2

DDR_A_ DM3

DDR_A_ DM4

DDR_A_ DM5

DDR_A_ DM6

DDR_A_ DM7

DDR_A_ CLK0[23]

DDR_A_ CLK#0[2 3]

DDR_A_ CLK1[23]

DDR_A_ CLK#1[2 3]

DDR_A_ CKE0[23]

DDR_A_ CKE1[23]

DDR_A_ ODT0[23]

DDR_A_ ODT1[23]

DDR_A_ CS0#[23]

DDR_A_ CS1#[23]

DDR_A_ RAS#[23]

DDR_A_ CAS#[23]

DDR_A_ WE#[23]

1 2

RC3 0_0402_5%@

DDR_A_ VREFDQ

T1

AG38

W35

W38

W34

U38

U37

U34

R35

R38

N38

AG34

R34

N37

AN35

L38

L35

AJ38

AG35

N34

B35

D40

K40

T41

AE41

AL40

AU40

BA37

B36

A36

E40

D41

L40

K41

U41

U40

AF41

AE40

AM40

AM41

AV40

AV41

BA36

AY36

AC35

AC34

AA34

AA32

AE38

AE37

AA37

AA38

G38

AA41

J38

J34

L34

J37

AN37

AU38

AL34

AN34

AL35

AR37

AJ34

AR38

AJ37

AN38

AL38

AA40

Y41

15mil

UC1A

MEMORY

M_ADD0

M_ADD1

M_ADD2

M_ADD3

M_ADD4

M_ADD5

M_ADD6

M_ADD7

M_ADD8

M_ADD9

M_ADD10

M_ADD11

M_ADD12

M_ADD13

M_ADD14/M_BG1

M_ADD15/M_ACT_L

M_BANK0

M_BANK1

M_BANK2/M_BG0

M_DM0

M_DM1

M_DM2

M_DM3

M_DM4

M_DM5

M_DM6

M_DM7

M_DQS_H0

M_DQS_L0

M_DQS_H1

M_DQS_L1

M_DQS_H2

M_DQS_L2

M_DQS_H3

M_DQS_L3

M_DQS_H4

M_DQS_L4

M_DQS_H5

M_DQS_L5

M_DQS_H6

M_DQS_L6

M_DQS_H7

M_DQS_L7

M_CLK_H0

M_CLK_L0

M_CLK_H1

M_CLK_L1

M_CLK_H2

M_CLK_L2

M_CLK_H3

M_CLK_L3

M_RESET_L

M_EVENT_L

M0_CKE0

M0_CKE1

M1_CKE0

M1_CKE1

M0_ODT0

M0_ODT1

M1_ODT0

M1_ODT1

M0_CS_L0

M0_CS_L1

M1_CS_L0

M1_CS_L1

M_RAS_L/M_RAS_L_ADD16

M_CAS_L/M_CAS_L_ADD15

M_WE_L/M_WE_L_ADD14

M_VREF

M_VREFDQ

FT4 REV 1 .01

2D3201 AJN23AC _BGA7 69~D

Place them close to APU within 1"

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

M_ZVDDIO_MEM_S3

A34

B34

A38

B38

A33

B33

A37

B37

B41

C40

F41

G40

A40

B40

E41

F40

J40

J41

N40

N41

H40

H41

M40

M41

R40

T40

W40

Y40

P40

P41

V40

V41

AD41

AD40

AH41

AH40

AB40

AC40

AF40

AG40

AK41

AK40

AP41

AP40

AJ41

AJ40

AN41

AN40

AT40

AU41

AY40

BA40

AR40

AT41

AW40

AY41

BA38

AY37

BA34

BA33

AY39

AY38

AY35

AY34

AB41

@

DDR_A_ DQ0

DDR_A_ DQ1

DDR_A_ DQ2

DDR_A_ DQ3

DDR_A_ DQ4

DDR_A_ DQ5

DDR_A_ DQ6

DDR_A_ DQ7

DDR_A_ DQ8

DDR_A_ DQ9

DDR_A_ DQ10

DDR_A_ DQ11

DDR_A_ DQ12

DDR_A_ DQ13

DDR_A_ DQ14

DDR_A_ DQ15

DDR_A_ DQ16

DDR_A_ DQ17

DDR_A_ DQ18

DDR_A_ DQ19

DDR_A_ DQ20

DDR_A_ DQ21

DDR_A_ DQ22

DDR_A_ DQ23

DDR_A_ DQ24

DDR_A_ DQ25

DDR_A_ DQ26

DDR_A_ DQ27

DDR_A_ DQ28

DDR_A_ DQ29

DDR_A_ DQ30

DDR_A_ DQ31

DDR_A_ DQ32

DDR_A_ DQ33

DDR_A_ DQ34

DDR_A_ DQ35

DDR_A_ DQ36

DDR_A_ DQ37

DDR_A_ DQ38

DDR_A_ DQ39

DDR_A_ DQ40

DDR_A_ DQ41

DDR_A_ DQ42

DDR_A_ DQ43

DDR_A_ DQ44

DDR_A_ DQ45

DDR_A_ DQ46

DDR_A_ DQ47

DDR_A_ DQ48

DDR_A_ DQ49

DDR_A_ DQ50

DDR_A_ DQ51

DDR_A_ DQ52

DDR_A_ DQ53

DDR_A_ DQ54

DDR_A_ DQ55

DDR_A_ DQ56

DDR_A_ DQ57

DDR_A_ DQ58

DDR_A_ DQ59

DDR_A_ DQ60

DDR_A_ DQ61

DDR_A_ DQ62

DDR_A_ DQ63

DDR_A_ ZVDDIO

DDR_A_ DQ[63..0] [23]

1 2

RC4 39.2_0402_ 1%

+1.2V_DD R

A A

Security C lassification

Security C lassification

Security C lassification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

2014/06/10 2015/06/30

2014/06/10 2015/06/30

2014/06/10 2015/06/30

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

FT4 DDR4 MEMORY

FT4 DDR4 MEMORY

FT4 DDR4 MEMORY

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

LA-H872P

LA-H872P

LA-H872P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

7 102Wednes day, June 05, 2 019

7 102Wednes day, June 05, 2 019

7 102Wednes day, June 05, 2 019

1.0(A00)

1.0(A00)

1.0(A00)

A

B

C

D

E

Main Func = CPU

1 1

+1.8VS

1

NC

2

A

1 2

INVTPW M_R

1 2

1 2

1 2

HDT@

QC1

S

G

5

@

P

Y

G

TC7SZ0 7FU_SSO P5

3

SA0000 4G200

@

RC23 0_0 402_5 %

HDT@

HDT@

+3VS

RC8

2.2K_04 02_5%

D

1 2

123

BSS138 W 1N SOT -323-3

4

+1.8VS

5

UC10

1

P

NC

Y

2

A

G

TC7SZ0 7FU_SSO P5

3

SA0000 4G200

12

@

APU_TES T41

APU_PW RGD

APU_RST #

APU_DBR EQ#

ENVDD [38]

4

1 2

@

RC25

1K_040 2_5%

1 2

@

RC27

1K_040 2_5%

PANEL_B KLEN [38,58]

ENVDD

RC19 4.7K_0 402_5 %

INVTPW M

RC20 4.7K_0 402_5 %

INVTPW M_R

ENVDD_R

PANEL_B KLEN_AP U

INVTPW M [38]

+1.8VS

APU_TCK

1 8

APU_TMS

2 7

APU_TDI

3 6

APU_DBR EQ#

4 5

1 8

APU_TRS T#

2 7

APU_TES T19

3 6

APU_TES T18

4 5

APU_TRS T#

1 2

CH2 0.01 U_0402 _16V7K

1 2

@

1 2

RPC2

100K_0 804_8P 4R_5%

HDMI output (Very important):

APU_TES T36

+1.8VS

RPH1

1K_080 4_8P4R _5%

HDT@

+1.8VS

RPH2

1K_080 4_8P4R _5%

HDT@

@

+3VS

18

27

36

45

1 2

+1.8VS

RC24

1K_040 2_5%

1 2

@

RC28

1K_040 2_5%

SVT(RC9) :

+1.8VS

+1.8VS

2 2

3 3

1 2

@

RC11 1K_0 402_5%

1 2

@

RC14 1K_0 402_5%

1 2

@

RC16 1K_0 402_5%

RPC1

1K_080 4_8P4R _5%

APU_PW RGD_EC[58]

+1.8VS

RC33 1K_0402 _5%

18

27

36

45

APU_RST #_EC[58]

1 2

APU_SVT

APU_SVC

APU_SVD

APU_SIC

APU_SID

APU_ALE RT#

EC_SMB_ CK2[58,66]

EC_SMB_ DA2[58,66]

APU_RST #_EC

H_PROCHO T#

APU_SVT[88]

APU_SVC[88]

APU_SVD[88]

H_PROCHO T#[9,58,82,8 4,88]

APU_PW RGD[9,88]

APU_RST #[9]

12

@

RC127 0_0402_5 %

+1.8VS

EC_SMB_ CK2

G

EC_SMB_ DA2

6 1

D

QC2B ME2N7002F1KW -G 2N SO T-363-6

PU at EC side

+3VALW _EC

UC11

1

NC

2

A

RC32 0_04 02_5%

Place close to Power IC

1 2

RC9 0_0402_5%@

1 2

RC10 0_0 402_5%@

1 2

RC12 0_0 402_5%@

SVC,SVD (RC10, RC12) :

Place close to APU side

3 4

2

S

5

3

@

1 2

RC17 300_ 0402_5 %

+1.8VS

1 2

RC18 300_ 0402_5 %

+1.8VS

APU_PW RGDAPU_PW RGD_EC

5

APU_SIC

SGD

QC2A ME2N7002F1KW -G 2N SO T-363-6

APU_SID

+1.8VS

12

RC26

4.7K_04 02_5%@

@

P

G

4

Y

TC7SZ0 7FU_SSO P5

SA0000 4G200

12

@ESD@

1 2

CC5 0.1U_0201_1 0V6K

@ESD@

1 2

CC6 0.1U_0201_1 0V6K

APU_RST #

APU_RST #

APU_PW RGD

+3VALW

RC22 100 K_040 2_5%

APU_SVT _R

APU_SVC _R

APU_SVD _R

1 2

@

APU_SIC

APU_SID

APU_ALE RT#

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRS T#

APU_DBR DY

APU_DBR EQ#

APU_PW RGD

APU_RST #

APU_RST #

CORETYP E

UC1C

H27

SVT

E27

SVC

D27

SVD

B30

SIC

B29

SID

A30

ALERT_L

A31

PROCHOT_L

G25

PWROK

D29

RESET_L

B25

TDI

A27

TDO

B27

TCK

B26

TMS

A29

TRST_L

A26

DBRDY

A25

DBREQ_L

D9

RSVD_1

D11

RSVD_2

D13

RSVD_3

E4

RSVD_4

E31

RSVD_5

H11

RSVD_6

H13

RSVD_7

L11

RSVD_8

AE34

RSVD_9

AM15

RSVD_10

AM17

RSVD_11

AM19

RSVD_12

AN8

RSVD_13

AP13

RSVD_14

AP15

RSVD_15

AP17

RSVD_16

AR13

RSVD_17

AR15

RSVD_18

AR17

RSVD_19

AU4

RSVD_20

AU13

RSVD_21

AU15

RSVD_22

AU17

RSVD_23

AV7

RSVD_24

AV9

RSVD_25

AV11

RSVD_26

AV13

RSVD_27

AV15

RSVD_28

AV17

RSVD_29

AY3

RSVD_30

AY7

RSVD_31

2D3201 AJN23AC _BGA7 69~D

DISPLAY/S VI2/J TAG/T ES T

DP_STEREOSYNC/TEST36

VDDCR_CPU_SENSE

VDDCR_NB_SENSE

VDDIO_MEM_S3_SENSE

FT4 REV 1 .01

DP_BLON

DP_DIGON

DP_VARY_BL

DP_AUX_ZVSS

DP_ZVSS

DP0_AUXP

DP0_AUXN

DP0_HPD

DP1_AUXP

DP1_AUXN

DP1_HPD

DP2_AUXP

DP2_AUXN

DP2_HPD

DP0_TXP0

DP0_TXN0

DP0_TXP1

DP0_TXN1

DP0_TXP2

DP0_TXN2

DP0_TXP3

DP0_TXN3

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

DP2_TXP0

DP2_TXN0

DP2_TXP1

DP2_TXN1

DP2_TXP2

DP2_TXN2

DP2_TXP3

DP2_TXN3

TEST10

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST28_H

TEST28_L

TEST31

TEST41

VDDP_SENSE

VSS_SENSE_A

VSS_SENSE_B

APU_TRS T#

PANEL_B KLEN_AP U

B23

ENVDD_R

B24

INVTPW M_R

A24

DP_AUX_ ZVSS

D21

DP_ZVS S

B18

G15

H15

EDP_HPD

D15

G17

H17

D17

G19

H19

D19

A9

B9

A10

B10

A11

B11

A12

B12

A14

B14

A15

B15

A16

B16

A17

B17

A19

B19

A20

B20

A21

B21

A22

B22

H29

TEST4

G29

TEST5

H25

TEST6

R32

TEST9

N32

G21

H21

D23

E23

A28

B28

N8

N10

H31

D25

B31

D31

E33

D35

AM21

APU_VSS _SENSE_ A

D33

AM23

APU_VSS _SENSE_ B

@

APU_TRS T#_R

HDT@

1 2

RH1 33_0 402_5%HDT@

RH2 10K_ 0402_5 %HDT@

RH3 10K_ 0402_5 %HDT@

RH4 10K_ 0402_5 %HDT@

EDP_TX P0

EDP_TX N0

EDP_TX P1

EDP_TX N1

APU_DP1 _P0

APU_DP1 _N0

APU_DP1 _P1

APU_DP1 _N1

APU_DP1 _P2

APU_DP1 _N2

APU_DP1 _P3

APU_DP1 _N3

APU_TES T4

APU_TES T5

APU_TES T6

APU_TES T9

APU_TES T10

APU_TES T14

APU_TES T15

APU_TES T16

APU_TES T17

APU_TES T18

APU_TES T19

APU_TES T28_H

APU_TES T28_L

APU_TES T31

APU_TES T36

APU_TES T41

0.01U_0402_16V7K

1

CH1

2

APU_TRS T#_R

1 2

1 2

1 2

1 2

RC13 150_ 0402_1 %

1 2

RC15 2K_0 402_1%

EDP_AUX P [38]

EDP_AUX N [38]

EDP_HPD [38]

APU_DP1 _CTRL_ CLK [40]

APU_DP1 _CTRL_ DATA [40]

APU_DP1 _HPD [40]

EDP_TX P0 [38]

EDP_TX N0 [38]

EDP_TX P1 [38]

EDP_TX N1 [38]

Place near APU

T2

T3

APU_TES T15

T4

APU_TES T14

T5

APU_TES T16

T6

APU_TES T17

T7

T8

T9

1 2

RC29 0_0 402_5%@

1 2

RC30 0_0 402_5%@

1 2

@

RC31 0_0 402_5%

+1.8VS

11

13

15

17

19

VDD_3 3

APU_VDD _SEN

APU_VDD NB_SEN

APU_VDD IO_MEM_S 3_FB_ H

APU_VDD P_RUN_FB _H

HDT Debug

JHDT1

1

1

3

3

5

5

7

7

9

9

11

13

15

17

19

SAMTE_A SP-1364 46-07-B

HDMIVDD_3 3

eDP

APU_DP1 _P0 [40 ]

APU_DP1 _N0 [40]

APU_DP1 _P1 [40 ]

APU_DP1 _N1 [40]

APU_DP1 _P2 [40 ]

APU_DP1 _N2 [40]

APU_DP1 _P3 [40 ]

APU_DP1 _N3 [40]

RPC3

@

18

27

36

45

1K_080 4_8P4R _5%

APU_VDD _SEN [88]

APU_VDD NB_SEN [88 ]

APU_VDD IO_MEM_S 3_FB_ H [86]

APU_VDD P_RUN_FB _H [87]

APU_VDD _RUN_FB_ L [88 ]

T12

APU_VDD P_RUN_FB _L [8 7]

CONN@

APU_TCK

2

2

APU_TMS

4

4

APU_TDI

6

6

APU_TDO

8

8

APU_PW RGD_BUF

10

10

APU_RST #_BUF

12

12

APU_DBR DY

14

14

APU_DBR EQ#_R

16

16

APU_TES T19

18

18

APU_TES T18

20

20

PANEL_B KLEN_AP U

+1.8VS

UC9

ENVDD_R

RC21 0_0402 _5%

HDMI

T10

T11

T30

TP31: Place near the APU

T31

DH1 RB75 1V-40_S OD323 -2

DH2 RB75 1V-40_S OD323 -2

RH5 33_0402_5 %

4 4

Security C lassification

Security C lassification

Security C lassification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

C

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D

Compal Secret Data

Compal Secret Data

Compal Secret Data

2014/06/10 2015/06/30

2014/06/10 2015/06/30

2014/06/10 2015/06/30

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

FT4 DISP/MISC/HDT

FT4 DISP/MISC/HDT

FT4 DISP/MISC/HDT

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

LA-H872P

LA-H872P

LA-H872P

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

8 102Wednes day, June 05, 2 019

8 102Wednes day, June 05, 2 019

8 102Wednes day, June 05, 2 019

1.0(A00)

1.0(A00)

1.0(A00)

Main Func = CPU

A

B

C

D

E

APU_FCH_ PWRGD

APU_FCH_ PWRGD

+3VALW

+3VS

+1.8VS

+3VS

+3VALW

+3VALW

+3VS

RC38 0_04 02_5%@

RC40 0_04 02_5%@

0.1U_0201_10V6K

1

2

HDA_SDO UT_R[56]

HDA_BIT _CLK_R[56]

HDA_SYNC_R[56]

1 2

1

CC11

2

RC68 100 K_0402 _5%

RC69 100 K_0402 _5%

RC70 10K _0402_ 5%

RC71 1K_ 0402_5 %@

RC72 2.2K _0402_ 5%@

RC73 2.2K _0402_ 5%@

RC74 10K _0402_ 5%

RC75 10K _0402_ 5%@

RC87 10K _0402_ 5%@

RC86 10K _0402_ 5%@

RC83 10K _0402_ 5%

RC85 10K _0402_ 5%

RC84 10K _0402_ 5%@

1 1

2 2

3 3

32.768KHz CRYSTAL

RC97 20M_04 02_5%

18P_0402_50V8J

CC18

1

4 4

2

RC34 10K_ 0402_ 5%

RC130 10K_0402 _5%

RC36 10K_ 0402_ 5%

RC35 10K_ 0402_ 5%

12

@ESD@

CC7 100P_0402 _50V8 J

CC7 close to UC1

+3VALW _EC

UC12

1

NC

2

A

0.1U_0201_10V6K

1 2

CC12

RC54 0_0402_ 5%

RPC6

I2C_3_ SCL

18

I2C_3_ SDA

27

APU_SCL K0

36

APU_SDA TA0

45

2.2K_08 04_8P4 R_5%

RPC7

1 8

2 7

3 6

4 5

10K_08 04_8P4 R_5%

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

12

YC1

32.768K HZ 12.5PF 9H0320 0031

SJ1000 0HW00

12

22P_0402_50V8J

CC19

1

2

CAM_DET ECT#

12

CLKREQ _PCIE# 0

12

CLKREQ _PCIE# 1

12

CLKREQ _PCIE# 2

12

12

5

@

P

Y

G

TC7SZ0 7FU_SSO P5

3

SA0000 4G200

@

RPC4

1 8

2 7

3 6

4 5

33_080 4_8P4R _5%

EMI@

I2C_1_ SCL

I2C_1_ SDA

GATEA2 0

VGATE [58,88 ]

APU_FCH_ POK [58]

APU_FCH_ PWRGD

+3VALW

4.7K_0402_5%

12

@

4

HDA_SDO UT

HDA_BIT _CLK

HDA_SYNC

HDA_RST #

RPC5

1 8

2 7

3 6

4 5

1K_080 4_8P4R _5%

USB_OC0 #

USB_OC1 #

RTC_DE T#

APU_TES T1

APU_TES T0

APU_TES T2

PBTN_OUT #

EGPIO1 31

HDA_BIT _CLK

HDA_SDI N0

HDA_SDI N1

HDA_SDI N2

HVB_FUNCTI ON

32K_X1

32K_X2

RC48

APU_FCH_ PWRGD _R

100K_0402_5%

RC49

1 2

VDD_3 3_S5:

AD2,A F1,AE7

VDD_3 3_S5:

AB1,A A7

VDD_3 3_S5

PBTN_OUT #[58]

APU_PCI E_WAK E#[51,58,68 ]

PM_SLP_ S3#[58 ]

PM_SLP_ S5#[58,78]

S5_MUX_C TRL[78]

RC41 15K_ 0402_5 %

RC43 15K_ 0402_5 %

RC45 15K_ 0402_5 %

VDD_3 3_S5

CLKREQ _PCIE# 0[51]

CLKREQ _PCIE# 1[52]

CLKREQ _PCIE# 2[68]

USB_OC0 #[71] GATEA2 0 [58]

USB_OC1 #[73]

CAM_DET ECT#[38]

@ESD@

EC_RSMR ST#_R

1 2

CC14 0.1U_02 01_10 V6K

@ESD@

SYS_RES ET_L

1 2

CC15 0.1U_02 01_10 V6K

Reserve for 17" touch (I2C):

+1.8VS

1 2

R2 2.2K_040 2_5%

1 2

R3 2.2K_040 2_5%

APU_PCI E_RST# _C

VDD_3 3_S5

EC_RSMR ST#_R

APU_FCH_ PWRGD _R

SYS_RES ET_L

APU_PCI E_WAK E#_R

1 2

@

RC39 0_0402_ 5%

S5_MUX_C TRL

1 2

1 2

1 2

HDA_SDI N0[56]

APU_TES T0

APU_TES T1

APU_TES T2

FFS_INT 2[67 ]

WL_OF F#

RTC_DE T#

WL_OF F#[10,52]

APU_ID

RTC_DE T#[11]

SKU_ID

CLKREQ _PCIE# 0

CLKREQ _PCIE# 1

CLKREQ _PCIE# 2

EGPIO1 31

USB_OC0 #

USB_OC1 #

CAM_DET ECT#

HDA_BIT _CLK

HDA_SDI N0

HDA_SDI N1

HDA_SDI N2

HDA_RST #

HDA_SYNC

HDA_SDO UT

I2C_0_ SCL

For 17' Touch

I2C_0_ SDA

I2C_1_ SCL

VDD_18

I2C_1_ SDA

SW Programing as EGPIO

EC_RSMR ST#[58]

32K_X1

32K_X2

I2C0 and I2C1 for CZ only

1.8V_S0 level, nee d LS

I2C Not Implemented:

Used as EG PIO or configured with one of the following options:

1.PH 2.2K

2.PD 10K

I2C_0_ SCL

I2C_0_ SDA

EC_RS MRST#:

1.8V /EC p rogram to 1.8V OUTPUT

EC_RSMRST# EC Pin100 use Open-Drain output

EC_RSMR ST#

UC1D

AE4

PCIE_RST_L/EGPIO26

AG1

RSMRST_L

AD2

PWR_BTN_L/AGPIO0

AE2

PWR_GOOD

AF1

SYS_RESET_L/AGPIO1

AE7

WAKE_L/AGPIO2

AC2

SLP_S3_L

AG4

SLP_S5_L

AB1

S0A3_GPIO/AGPIO10

AA7

S5_MUX_CTRL/EGPIO42

AF2

TEST0

AE1

TEST1/TMS

AC8

TEST2

AH2

AC_PRES/USB_OC4_L/IR_RX0/AGPIO23

AA4

IR_TX0/USB_OC5_L/AGPIO13

AG8

IR_TX1/USB_OC6_L/AGPIO14

AL5

IR_RX1/AGPIO15

AE8

IR_LED_L/LLB_L/AGPIO12

AY32

CLK_REQ0_L/SATA_IS0_L/SATA_ZP0_L/AGPIO92

AY31

CLK_REQ1_L/AGPIO115

AV29

CLK_REQ2_L/AGPIO116

AP31

CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/EGPIO131

AV35

CLK_REQG_L/OSCIN/EGPIO132

AB2

USB_OC0_L/TRST_L/AGPIO16

AG2

USB_OC1_L/TDI/AGPIO17

AJ1

USB_OC2_L/TCK/AGPIO18

AH1

USB_OC3_L/TDO/AGPIO24

AY6

AZ_BITCLK/I2S_BCLK_MIC

BA6

AZ_SDIN0/I2S_DATA_MIC0

AY5

AZ_SDIN1/I2S_LR_PLAYBACK

BA5

AZ_SDIN2/I2S_DATA_PLAYBACK

AY4

AZ_RST_L/I2S_LR_MIC

BA3

AZ_SYNC/I2S_BCLK_PLAYBACK

BA4

AZ_SDOUT/I2S_DATA_MIC1

AY22

I2C0_SCL/EGPIO145

BA22

I2C0_SDA/EGPIO146

AU19

I2C1_SCL/EGPIO147

AV19

I2C1_SDA/EGPIO148

BA2

X32K_X1

AY2

X32K_X2

2D3201 AJN23AC _BGA7 69~D

I2C_0_ SCL I2C_0_ SCL_R

I2C_0_ SDA

1 2

@

RC93 0_0402 _5%

DC2

1 2

RB751V -40_SOD 323-2

RB751 Max Vf=0.37V

Q1B

L2N7002 DW1T1 G_SC8 8-6

5

Q1A

@

34

SGD

L2N7002 DW1T1 G_SC8 8-6

EC_RSMR ST#_R

@

ACPI/SD /AZ/GP IO/R TC/ MISC

UART1_CTS_L/BT_I2S_BCLK/EGPIO140

UART1_RXD/BT_I2S_SDI/EGPIO141

UART1_TXD/BT_I2S_SDO/EGPIO143

UART1_INTR/BT_I2S_LRCLK/AGPIO144

FT4 REV 1 .01

+3VS

+1.8VS

2

G

@

61

S

D

12

R4

@

4.7K_04 02_5%

+1.8V_AL W

12

RC96

22K_04 02_5%

SD_PWR_CTRL/AGPIO102

SD_DATA0/EGPIO97

SD_DATA1/EGPIO98

SD_DATA2/EGPIO99

SD_DATA3/EGPIO100

SCL0/I2C2_SCL/EGPIO113

SDA0/I2C2_SDA/EGPIO114

SCL1/I2C3_SCL/AGPIO19

SDA1/I2C3_SDA/AGPIO20

AGPIO6/LDT_RST_L

AGPIO7/LDT_PWROK

BLINK/USB_OC7_L/AGPIO11

GENINT2_L/AGPIO90

FANOUT0/AGPIO85

UART0_CTS_L/EGPIO135

UART0_RXD/EGPIO136

UART0_RTS_L/EGPIO137

UART0_TXD/EGPIO138

UART0_INTR/AGPIO139

UART1_RTS_L/EGPIO142

4.7K_0402_5%

12

R1

@

I2C_0_ SDA_R

SD_WP/EGPIO101

SD_CD/AGPIO25

SD_CLK/EGPIO95

SD_CMD/EGPIO96

SD_LED/EGPIO93

AGPIO3

AGPIO4

AGPIO5

AGPIO8

AGPIO9

AGPIO40

SPKR/AGPIO91

GA20IN/AGPIO126

FANIN0/AGPIO84

HVBEN_L

RTCCLK

KB_DET

BA28

RESERV E_2

AY29

AY13

AGPIO2 5

BA14

AY15

BA29

GPIO93

AY14

BA13

BA16

AY16

APU_SCL K0

AY33

APU_SDA TA0

BA32

I2C_3_ SCL

AC5

I2C_3_ SDA

AC4

MEM_VOLT _SEL

AJ7

AK2

AK1

APU_RST #_R

AL4

APU_PW RGD_R

AJ2

AJ4

AGPIO8

SATA_O DD_PRS NT#

AG5

AD1

AJ8

AGPIO1 1

AR29

AP29

AU35

BT_ON#

AV33

AU33

AP23

AP25

AR25

AV25

AU23

AP21

AV21

AP19

AV23

AR21

HVB_FUNCTI ON

AP27

RTC_CL K

AN4

@

I2C_0_ SCL_R [38]

I2C_0_ SDA_R [38]

1 2

RC37 0_0 402_5%@

T13

T14

T25

T16

T15

T17

APU_SCL K0 [2 3,67]

APU_SDA TA0 [23 ,67]

I2C_3_ SCL [63 ]

set to I2C

I2C_3_ SDA [63 ]

CC8: Close to UC1D

1 2

@

CC8 0.1U_0201_1 0V6K

1 2

@

CC9 0.1U_0201_1 0V6K

1 2

RC50 0_04 02_5%@

1 2

RC51 0_04 02_5%@

1 2

RC52 0_04 02_5%@

SATA_O DD_PRS NT# [58 ,67]

1 2

@

CC10 0.1U_02 01_10 V6K

BT_ON# [52 ]

FFS_INT 1 [67]

T26

T27

2019/01/18: Reserve UART signals for debug

T28

T29

1 2

@

RC62 22 +-5% 04 02

APU_PCIE_RST #: Reset PCIE dev ice on APU

APU_PCI E_RST# _C

1 2

RC63 33_ 0402_ 5%

LPC_FRAME#

SPI ROM

(DEFAULT)

H

LPC ROM

L

LPC_FR AME#[10,58]

LPC_CL K0_EC[10,58]

LPC_CL K1[10 ]

set to SMbus

SUSCLK_ WLAN

KB_DET [6 3]

H_PROCHO T# [8,58,82,84,8 8]

APU_RST #

APU_PW RGD

TP_I2C _INT#_A PU

APU_SPK R [56]

SUSCLK_ WLAN [52,58]

8.2K_0402_5%

150P_0402_50V8J

RC65

CC16

1

@

2

1 2

BOOT FAILTIMER

ENABLED

BOOT FAIL

TIMER

DISABLED

(DEFAULT)

10K_0402_5%

10K_0402_5%

12

12

RC76

@

2K_0402_5%

2K_0402_5%

12

12

RC88

@

VDD_3 3_S5

APU_RST # [8]

APU_PW RGD [8,88]

TP_I2C_INT#_APU [63]

FFS_INT 1

RC57 10K _0402_ 5%

FFS_INT 2

RC59 10K _0402_ 5%

AGPIO23 is VDD_33_S5

+3VALW

UC13

5

MC74VHC1 G08DFT 2G SC7 0 5P

2

P

B

Y

1

A

G

@

3

1 2

@

RC67 0_0402_ 5%

CLKGEN

ENABLE

(DEFAULT)

CLKGEN

DISABLED

10K_0402_5%

12

RC77

RC78

2K_0402_5%

12

RC94

RC89

@

VDD_3 3_S5:

AC5~A J8

+3VS

1 2

+3VALW

1 2

4

12

RC66

@

0_0402 _5%

PLT_RS T#

MEM_VOLT_SELLPC_CLK 1LPC_CLK0_EC

Enhanced Reset logic

(DEFAULT)

Traditional Reset logic

+3VALW+3VS

12

MEM_VOLT _SEL

RTC_CL K

SYS_RES ET_L

AGPIO1 1

12

@

AGPIO8

SATA_O DD_PRS NT#

GPIO93

APU_PCI E_RST# [51,52,68 ]

PLT_RS T# [10,51,52,5 8]

RTC_CLK

<INT PU>

COIN BATT

ON BOARD

(DEFAULT)

COIN BATT

NOT ON

BOARD

10K_0402_5%

10K_0402_5%

12

RC79

RC80

2K_0402_5%

2K_0402_5%

12

RC90

RC91

@

RC42 10K _0402_ 5%

RC44 10K _0402_ 5%

RC53 10K _0402_ 5%@

APU A6/A9

APU E2

AGPIO15 is VDD_33_S5

APU_ID

RESERV E_2

SYS_RST#

<INT PU>

NORMAL

RESET MODE

(DEFAULT)

SHORT RST

MODE

10K_0402_5%

12

RC81

2.2K_0402_5%

12

RC92

@

+3VALW

12

12

12

APU_ID

RESERVE _1

(AGPIO15)

(AGPIO4)

X

X

X X

X

BIOS don't care

+3VALW

RC55

10K_04 02_5%@

1 2

RC60

10K_04 02_5%@

1 2

BLINK/GPIO11

<INT PU>

LDT_RST#/PG

OUTPUT TO

APU

(DEFAULT)

OUTPUT

TO PADS

10K_0402_5%

12

RC82

2.2K_0402_5%

12

RC95

@

+3VS

RESERVE _2

(AGPIO102)

BIOS don't careBIOS don't care

+3VS

X

RC56

10K_04 02_5%@

1 2

RC61

10K_04 02_5%@

1 2

SKU_ID

MLK

Narrow Board

+3VALW

SKU_ID

(AGPIO12)

MLK@

NB@

RC132

10K_04 02_5%MLK@

1 2

RC133

10K_04 02_5%NB@

1 2

Security C lassification

Security C lassification

Security C lassification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

C

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D

Compal Secret Data

Compal Secret Data

Compal Secret Data

2014/06/10 2015/06/30

2014/06/10 2015/06/30

2014/06/10 2015/06/30

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

FT4 GPIO/AZ/MISC/STRAPS

FT4 GPIO/AZ/MISC/STRAPS

FT4 GPIO/AZ/MISC/STRAPS

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

LA-H872P

LA-H872P

LA-H872P

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

9 102Wednes day, June 05, 2 019

9 102Wednes day, June 05, 2 019

9 102Wednes day, June 05, 2 019

1.0(A00)

1.0(A00)

1.0(A00)

A

B

C

D

E

Main Func = CPU

(#55350 ) AGPIO Power Domain:

VDD_3.3_S5: Connect to +3VALW

1 1

+3VS

2 2

1 2

RC101 10K_0402 _5%@

1 2

RC99 10K_04 02_5%@

1 2

RC98 10K_04 02_5%@

1 2

RC104 10K_0402 _5%

SATA_A CT#

DEVSLP 0_HDD

DEVSLP 1_SSD

WL_OF F#

1 2

RC108 10 K_0402 _5%

LPCPD#

VDD_3.3_S0: Connect to +3VS

SATA_A TX_DRX _P0[67]

SATA_A TX_DRX _N0[67]

HDD

SATA_A RX_DTX _N0[67]

SATA_A RX_DTX _P0[67]

SATA_A TX_DRX _P1[67]

SATA_A TX_DRX _N1[67]

ODD

SATA_A RX_DTX _N1[67]

SATA_A RX_DTX _P1[67]

12

RC102 1K_0402 _1%

12

RC103 1K_0402 _1%

+0.95VS

SATA_A CT#[63,68]

DEVSLP 0_HDD[67]

DEVSLP 1_SSD[68]

WL_OF F# [9,5 2]

PLT_RS T#[9,51,52 ,58]

VDD_3 3_S5:

AC1/A A8

VDD_3 3_S0:

AY26, BA27,AV 27

LAN

WLAN

SSD

RC111 33_0402_ 5%

RC112 100K_0 402_5%

CC21 150 P_0402 _50V8 J

CLK_PC IE_P0[5 1]

CLK_PC IE_N0[51 ]

CLK_PC IE_P1[5 2]

CLK_PC IE_N1[52 ]

CLK_PC IE_P2[6 8]

CLK_PC IE_N2[68 ]

LPC_CL K0_EC[9 ,58]

LPC_CL K1[9]

LPC_FR AME#[9,58]

1 2

1 2

EC_SCI #[58]

LPC_AD 0[58]

LPC_AD 1[58]

LPC_AD 2[58]

LPC_AD 3[58]

12

SERIRQ[58]

SATA_A CT#

DEVSLP 0_HDD

DEVSLP 1_SSD

CLK_PC IE_P0

CLK_PC IE_N0

CLK_PC IE_P1

CLK_PC IE_N1

CLK_PC IE_P2

CLK_PC IE_N2

1 2

RC107 33_0402 _5%

1 2

RC109 33_0402 _5%EMI@

LPC_RS T_A#

CLKRUN#[58]

+1.8VS

RC114 10 K_0402 _5%

48M_X1

48M_X2

CLKRUN#

LPCPD#

12

SATA_Z VSS

SATA_Z VDD

APU_SPI _CS1#_ R

UC1E

BA10

SATA_TX0P

AY10

SATA_TX0N

AY12

SATA_RX0N

BA12

SATA_RX0P

AY9

SATA_TX1P

BA9

SATA_TX1N

BA8

SATA_RX1N

AY8

SATA_RX1P

AU11

SATA_ZVSS

AP11

SATA_ZVDDP

AY30

SATA_ACT_L/AGPIO130

AV31

DEVSLP0/EGPIO67

AU31

DEVSLP1/EGPIO70

H2

GFX_CLKP

H1

GFX_CLKN

M2

GPP_CLK0P

M1

GPP_CLK0N

L2

GPP_CLK1P

L1

GPP_CLK1N

K2

GPP_CLK2P

K1

GPP_CLK2N

J2

GPP_CLK3P

J1

GPP_CLK3N

F2

X48M_X1

F1

X48M_X2

AU27

X25M_48M_OSC

BA25

LPCCLK0/EGPIO74

BA24

LPCCLK1/EGPIO75

AY24

LFRAME_L

BA26

LAD0

AY28

LAD1

AY25

LAD2

AY23

LAD3

AY27

LPC_RST_L

AY26

LPC_CLKRUN_L/AGPIO88

AC1

LPC_PD_L/AGPIO21

AA8

LPC_PME_L/AGPIO22

BA27

LPC_SMI_L/AGPIO86

AV27

SERIRQ/AGPIO87

2D3201 AJN23AC _BGA7 69~D

CLK/SATA/USB/S PI/L PC

USBCLK/25M_48M_OSC

USB_ZVSS

USB_HSD0P

USB_HSD0N

USB_HSD1P

USB_HSD1N

USB_HSD2P

USB_HSD2N

USB_HSD3P

USB_HSD3N

USB_HSD4P

USB_HSD4N

USB_HSD5P

USB_HSD5N

USB_HSD6P

USB_HSD6N

USB_HSD7P

USB_HSD7N

USB_SS_ZVSS

USB_SS_ZVDDP

USB_SS_0TXP

USB_SS_0TXN

USB_SS_0RXP

USB_SS_0RXN

USB_SS_1TXP

USB_SS_1TXN

USB_SS_1RXP

USB_SS_1RXN

USB_SS_2TXP

USB_SS_2TXN

USB_SS_2RXP

USB_SS_2RXN

SPI_CLK/ESPI_CLK/EGPIO117

SPI_DO/ESPI_DAT0/EGPIO121

SPI_DI/ESPI_DAT1/EGPIO120

SPI_HOLD_L/ESPI_DAT3/EGPIO133

SPI_WP_L/ESPI_DAT2/EGPIO122

SPI_CS1_L/EGPIO118

SPI_TPM_CS_L/AGPIO76

ESPI_ALERT_L/LDRQ0_L

ESPI_RESET_L/KBRST_L/AGPIO129

SPI_CS2_L/ESPI_CS_L/EGPIO119

FT4 REV 1 .01

AL8

USB_ZVS S

AN7

AW1

AW2

AV1

AV2

AU1

AU2

AT1

AT2

AR1

AR2

AP1

AP2

AN1

AN2

AM1

AM2

W4

W5

T1

T2

V2

V1

R1

R2

W2

W1

P1

P2

Y2

Y1

AY17

AY20

BA17

BA18

BA20

AY21

BA21

AY18

BA30

AY19

@

USB20_P 0

USB20_N0

USB20_P 1

USB20_N1

USB20_P 2

USB20_N2

USB20_P 3

USB20_N3

USB20_P 4

USB20_N4

USB20_P 5

USB20_N5

USB20_P 6

USB20_N6

USB20_P 7

USB20_N7

USBSS_Z VSS

USBSS_Z VDD

USB3_AT X_DRX_ 0_P1

USB3_AT X_DRX_ 0_N1

USB3_AR X_DTX_ 0_P1

USB3_AR X_DTX_ 0_N1

USB3_AT X_DRX_ 0_P2

USB3_AT X_DRX_ 0_N2

USB3_AR X_DTX_ 0_P2

USB3_AR X_DTX_ 0_N2

APU_SPI _MOSI

APU_SPI _MISO

APU_SPI _HOLD#

APU_SPI _WP#

APU_SPI _CS1#

APU_SPI _TPMCS#

KB_RST #

APU_SPI _CS1#_ R

1 2

RC100 1 1.8K_04 02_1%

1 2

RC105 1K_040 2_1%

1 2

RC106 1K_040 2_1%

EMI@

RC110 33 _0402_ 5%

VDD_3 3_S0:

BA21, BA30

KB_RST # [58]

USB20_P 0 [73]

USB20_N0 [73]

USB20_P 1 [73]

USB20_N1 [73]

USB20_P 2 [38]

USB20_N2 [38]

USB20_P 3 [38]

USB20_N3 [38]

USB20_P 4 [52]

USB20_N4 [52]

USB20_P 5 [71]

USB20_N5 [71]

USB20_P 6 [71]

USB20_N6 [71]

USB20_P 7 [66]

USB20_N7 [66]

USB3_AT X_DRX_ 0_P1 [71]

USB3_AT X_DRX_ 0_N1 [71]

USB3_AR X_DTX_ 0_P1 [71]

USB3_AR X_DTX_ 0_N1 [71]

USB3_AT X_DRX_ 0_P2 [71]

USB3_AT X_DRX_ 0_N2 [71]

USB3_AR X_DTX_ 0_P2 [71]

USB3_AR X_DTX_ 0_N2 [71]

APU_SPI _CLKAPU_SPI _CLK_R

12

RC110: Place close to UC1

+3.3V S

KB_RST #

Card Reader

USB Conn IO PORT3

Touch Screen

Camera

WLAN

USB Conn MB PORT1

USB Conn MB PORT2

Finger Printer

+0.95VAL W

USB Conn PORT1

USB Conn PORT2

RC113 10K_04 02_5%

+3VS

12

16MB SPI ROM

3 3

APU_SPI _TPMCS#

12

@

RC115 1 0K_040 2_5%

UC14

APU_SPI _CS1#

1

APU_SPI _MISO

CS

2

APU_SPI _WP#

DO(IO1)

3

WP(IO2)

4

+SPI_VC C

4 4

A

12

RC119 1 0K_04 02_5%

12

RC120 1 0K_04 02_5%

12

RC121 1 0K_04 02_5%

APU_SPI _HOLD#

APU_SPI _WP#

APU_SPI _CS1#

B

GND

W25Q1 28FWS IQ_SO 8

Place close to UC14

APU_SPI _CLK

HOLD/RESET(IO3)

@EMI@

RC128

10_040 2_5%

+1.8V_AL W+1.8VS

1 2

RC117 0_0603_5 %@

1 2

RC118 0_0603_5 %@

1 2

CC22 0.1U_020 1_10V6 K

+SPI_VC C

8

APU_SPI _HOLD#

VCC

7

APU_SPI _CLK

6

APU_SPI _MOSI

CLK

5

DI(IO0)

@EMI@

12

1 2

CC121

10P_04 02_50V 8J

@

C

UC14

SA00009KY10

@

S IC FL 128M W25Q128FW SIQ SOIC 8P SPI

UC14

SA00009PH10

@

S IC FL 128M GD25LB128DSIGR SOP 8P SPI

UC14

SA00009KY30

@

S IC FL 128M W25Q128J WSIQ SOIC8P SPI ROM

48MHz CRYSTAL

48M_X2

1 2

RC116 1M_ 0402_5 %

2

2

334

1

C1

5.6P_04 02_50V 8D

2

Security C lassification

Security C lassification

Security C lassification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D

48M_X1

1

1

YC2

48MHZ 8PF +-20PPM 7V 48000 010

SJ1000 0JP00

4

1

C2

5.6P_04 02_50V 8D

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

2014/06/10 2015/06/30

2014/06/10 2015/06/30

2014/06/10 2015/06/30

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

FT4 SATA/CLK/USB/SPI

FT4 SATA/CLK/USB/SPI

FT4 SATA/CLK/USB/SPI

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

LA-H872P

LA-H872P

LA-H872P

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

10 10 2Wednesd ay, June 05, 20 19

10 10 2Wednesd ay, June 05, 20 19

10 10 2Wednesd ay, June 05, 20 19

1.0(A00)

1.0(A00)

1.0(A00)

A

B

C

D

E

Main Func = CPU

1 1

+APU_COR E

CC38 0.22U_0402_10V6K

CC95

1U_0201_6.3V6M

1

2

CC63 180P_0402_50V8J

CC101

0.22U_0402_10V6K

CC39 0.22U_0402_10V6K

1

2

CC64 180P_0402_50V8J

1

2

0.22U_0402_10V6K

1

2

CC113

1

2

CC40 180P_0402_50V8J

1

2

+1.2V_DD R

1

2

+VDDCR_ FCH_AL W

CC96

+0.95VAL W

10U_0402_6.3V6M

CC102

1

2

+0.95VS_ APU_GF X

0.22U_0402_10V6K

0.22U_0402_10V6K

CC114

1

2

+1.2V_DD R

extra 0.22uF, Follow AMD checklist 0.22uF*1pcs (CC97)

+RTC_AP U_R

0.5A

+1.8VS

0.2A

0.22U_0402_10V6K

CC103

1

2

0.22U_0402_10V6K

CC115

CC116

1

2

+1.2V_DD R

+APU_COR E

+VDDCR_ FCH_AL W

+0.95VAL W

+0.95VS_ APU_GF X

1 2

CC97 0.22U_0 402_10 V6K

1 2

RC123 0_0402_ 5%@

@ESD@

@

3

CEST23LC3V3B 3P C/A SOT-23

15W: 29A

UC1F

POWER

J35

VDDIO_MEM_S3_1

L32

VDDIO_MEM_S3_2

L37

AG32

AG37

+RTC_AP U_R

AM11

VDDIO_ AUDIO

AM13

RTC OF APU

12

RC126

10M_040 2_5%

VDDIO_MEM_S3_3

N35

VDDIO_MEM_S3_4

R37

VDDIO_MEM_S3_5

U32

VDDIO_MEM_S3_6

U35

VDDIO_MEM_S3_7

W32

VDDIO_MEM_S3_8