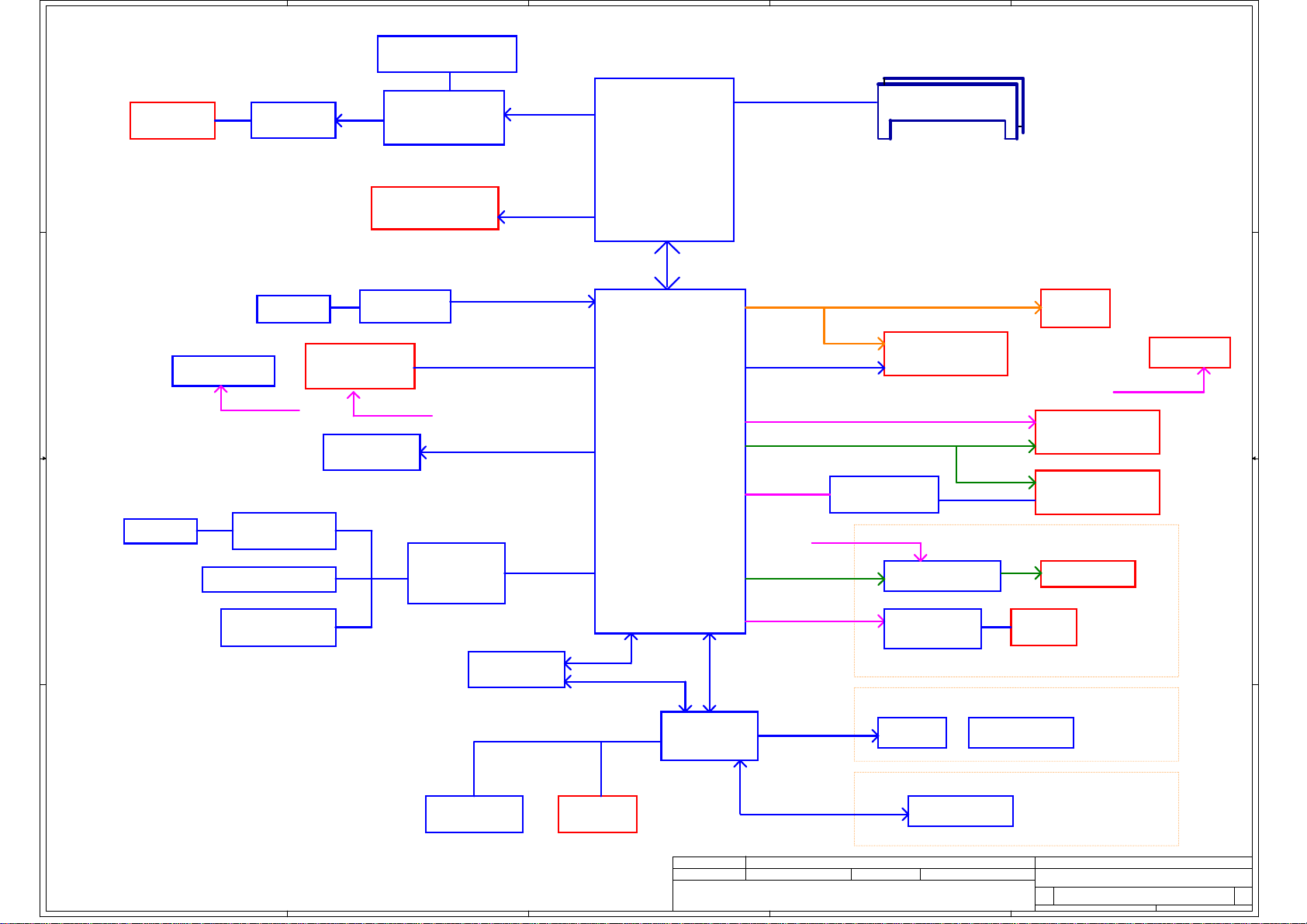

Dell Inspiron 15 Gaming 7567 Schematic

A

B

C

D

E

MODEL NAME :

PCB NO :

BOM P/N :

1

2

3

BBV00/ BBV10

LA-D993P

Dell/Compal Confidential

Schematic Document

KABYLAKE-H

2016-11-01

Rev: 1.0 (A00)

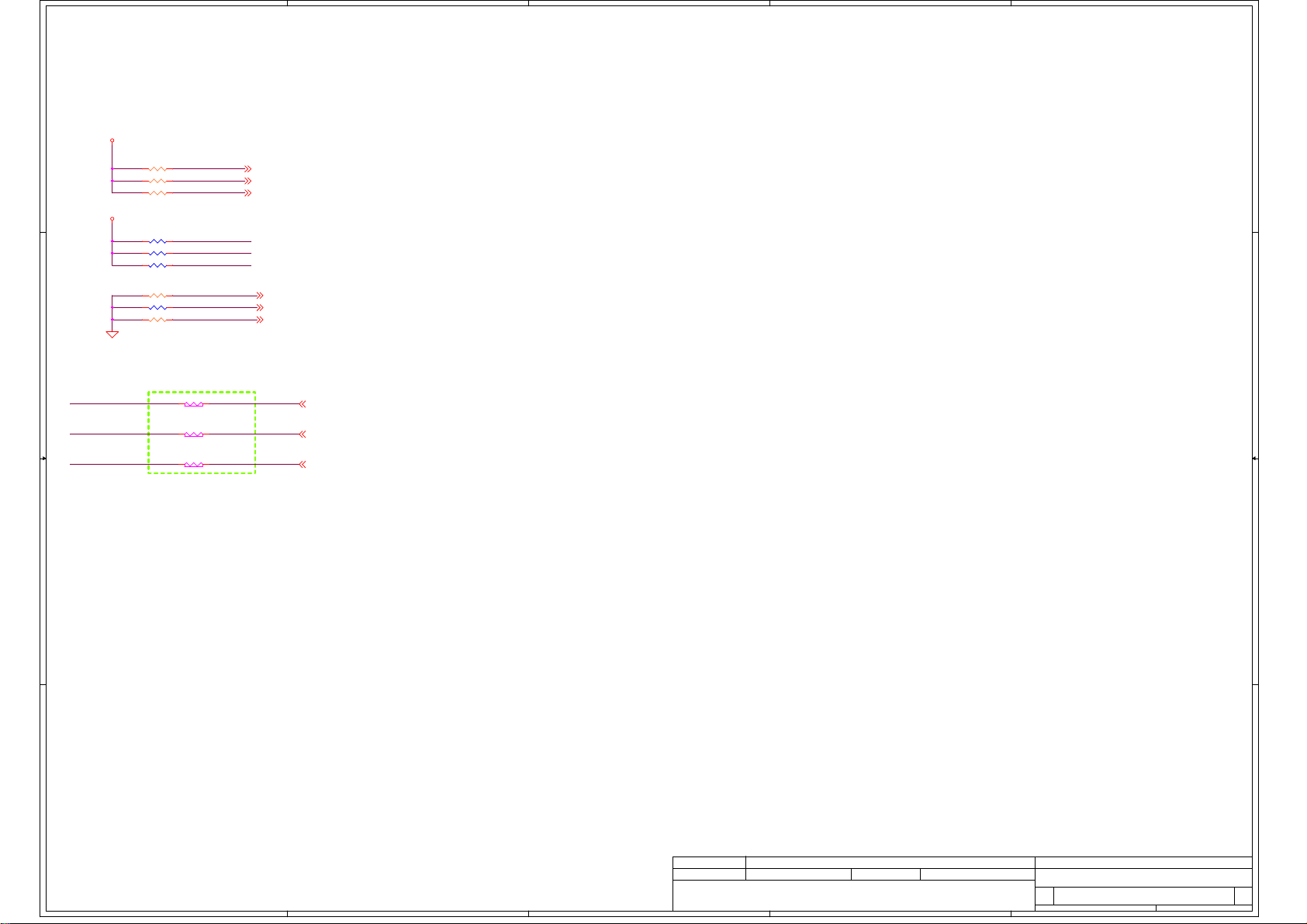

@ : Nopop Component

CONN@ : Connector Component

R1@ / R3@ : R1/R3 CPN for CPU, GPU, PCB

EMC@ : Pop of EMI parts

S4G@ : Samsung GDDR5 4G for GPU

M4G@ : Micron GDDR5 4G for GPU

H4G@ : Hynix GDDR5 4G for GPU

BreakDown@ : For measure power consumption

14G0@ : 14" N17P-G0

15G1@ : 15" N17P-G1

1

2

3

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONT AINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONT AINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONT AINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORM ATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORM ATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORM ATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WR ITTEN CONSENT OF COMPAL ELECTRONIC S, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WR ITTEN CONSENT OF COMPAL ELECTRONIC S, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WR ITTEN CONSENT OF COMPAL ELECTRONIC S, INC.

C

2011/08/25 2011/08/25

2011/08/25 2011/08/25

2011/08/25 2011/08/25

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

E

of

1 70Tuesday, November 08, 2016

of

1 70Tuesday, November 08, 2016

of

1 70Tuesday, November 08, 2016

0.1(X00)

0.1(X00)

0.1(X00)

4

A

B

C

D

E

128M*32 x4 =2G

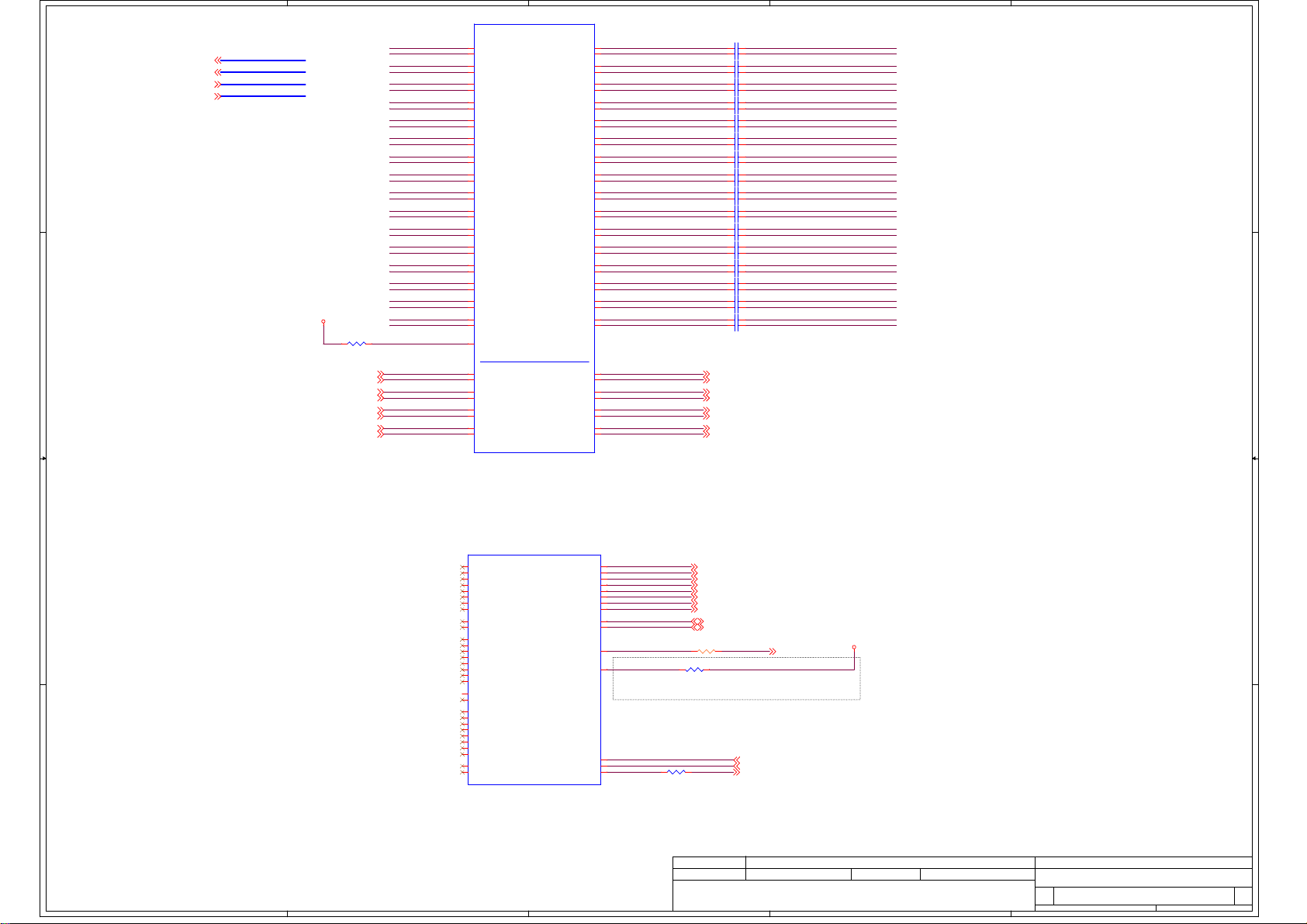

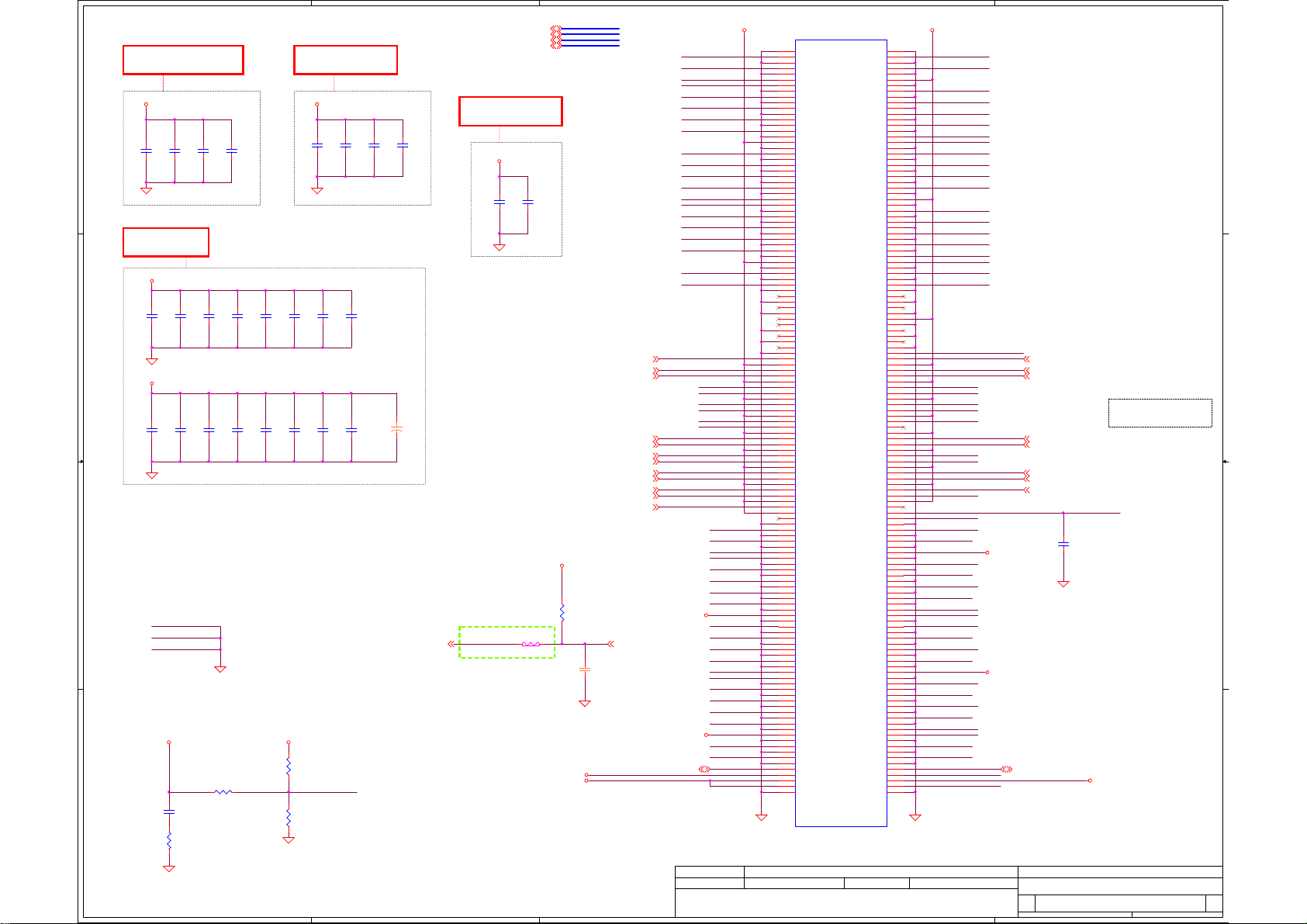

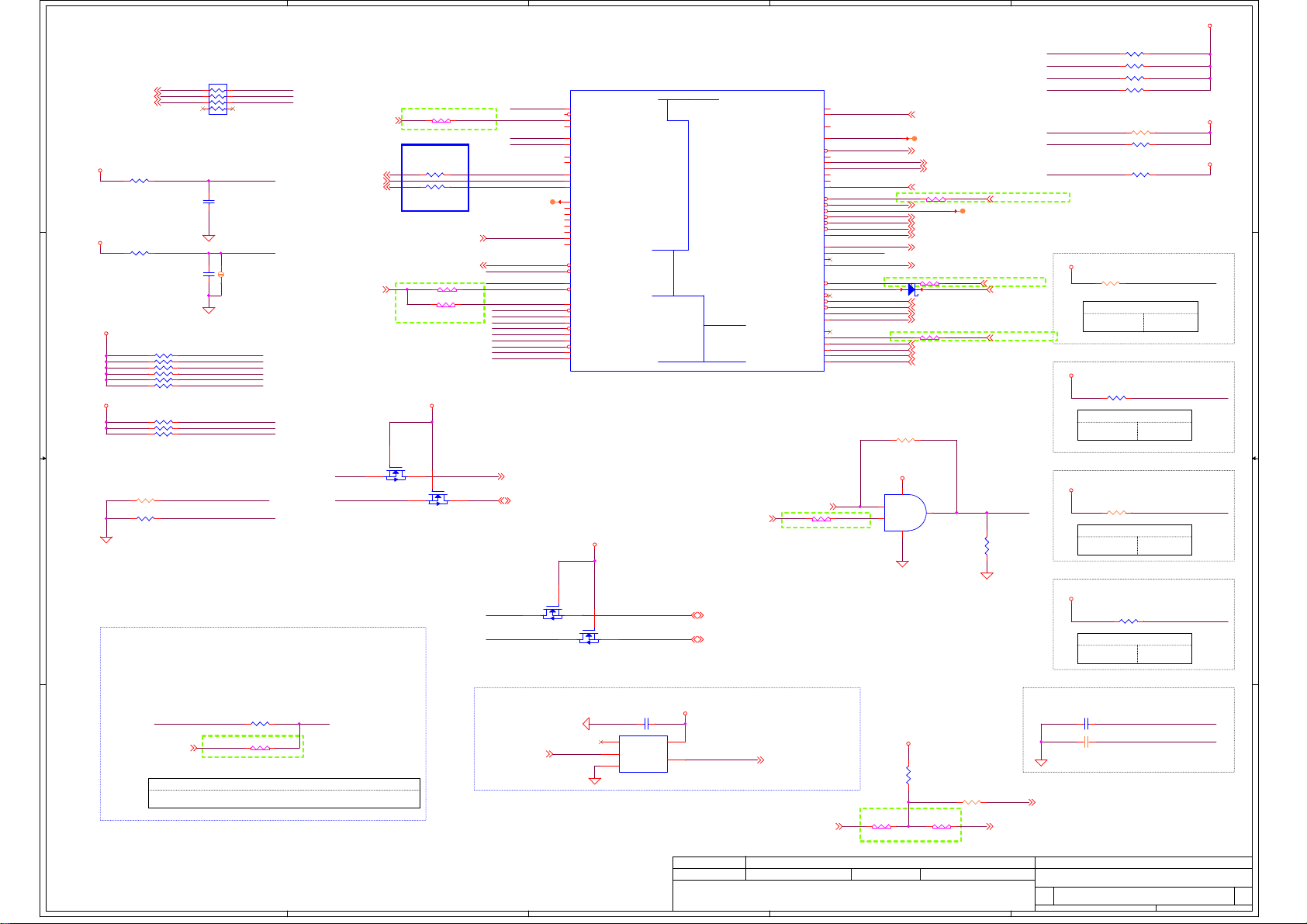

GPU

1

HDMI 2.0

Conn.

Retimer

PS8409A

IFP

P35P.36

N17PG0/ N17P-G1

40W/ 50W

256M*32 x4 =4G

VRAM * 4

GDDR5

GB4-128

P.28~30

P.23~27

PEG 3.0 x16

Intel

KBL-Lake-H

Memory Bus (DDR4)

Dual Channel

DDRIV-DIMM X2

1.2V DDR4 2400 MHz

P.14~15

32GB Max

1

Processor

45W

14.0'' / 15.6''

HD / FHD / UHD

RJ45

P.47

2

Digital Camera

Conn.

P.34

USB2.0

M.2 Slot A Key-E

(WLAN+BT4.0)

Port 12

LOM

RTL8111H

P.43

USB2.0

P.47

Port 4

SPI Flash

(BIOS 16MB)

Subwoofer

3

Subwoofer AMP

ALC1302

Main SPKR *2

P.39

P.38

P.17

HDA Codec

ALC3246

P.34

Port 5

Port 6

P.37

eDP 1.2 *4 lane

PCI-E x1

PCI-E x1

SPI

HD Audio

Universal

Audio Jack

P.38

Touch Pad

P.41

I2C

PS2

BGA

P.7~13

DMI x4

100MHz

5GB/s

Intel

KBL-H-PCH

BGA 837 Balls

P16~22

LPC Bus

33MHz

SATA3.0

PCI-E x4

USB2.0

USB 3.0

USB2.0

USB 3.0

USB2.0

Port 9~12

Port 1

Port 1

Port 2

USB Powershare

TPS2544

USB2.0

Port 3

Port 7

Port 1

Port 0

M.2 Slot C Key-M

(SATA/PCIe SSD)

Port 2

P.45

Port 3

USB 3.0 Re-driver

SN65LVPE50

Card Reader 2 in 1

RTS5176E SD / MS

P.44

HDD

Conn.

P.44

USB 3.0 Conn.

USB 3.0 Conn.

( USB Charger )

USB 3.0 Conn.

LED Board

USB2.0

P.46

P.46

IO Board

Touch Panel

Conn.

P.35

Port 9

2

3

SMSC 1404

SIO

4

A

B

Charger &

Battery

P.55

KB Conn.

P.40

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

C

P.48

Compal Secret Data

Compal Secret Data

2011/08/25 2011/08/25

2011/08/25 2011/08/25

2011/08/25 2011/08/25

Compal Secret Data

LED Hall Sensor

Power Button

Deciphered Date

Deciphered Date

Deciphered Date

D

Power Button Board

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

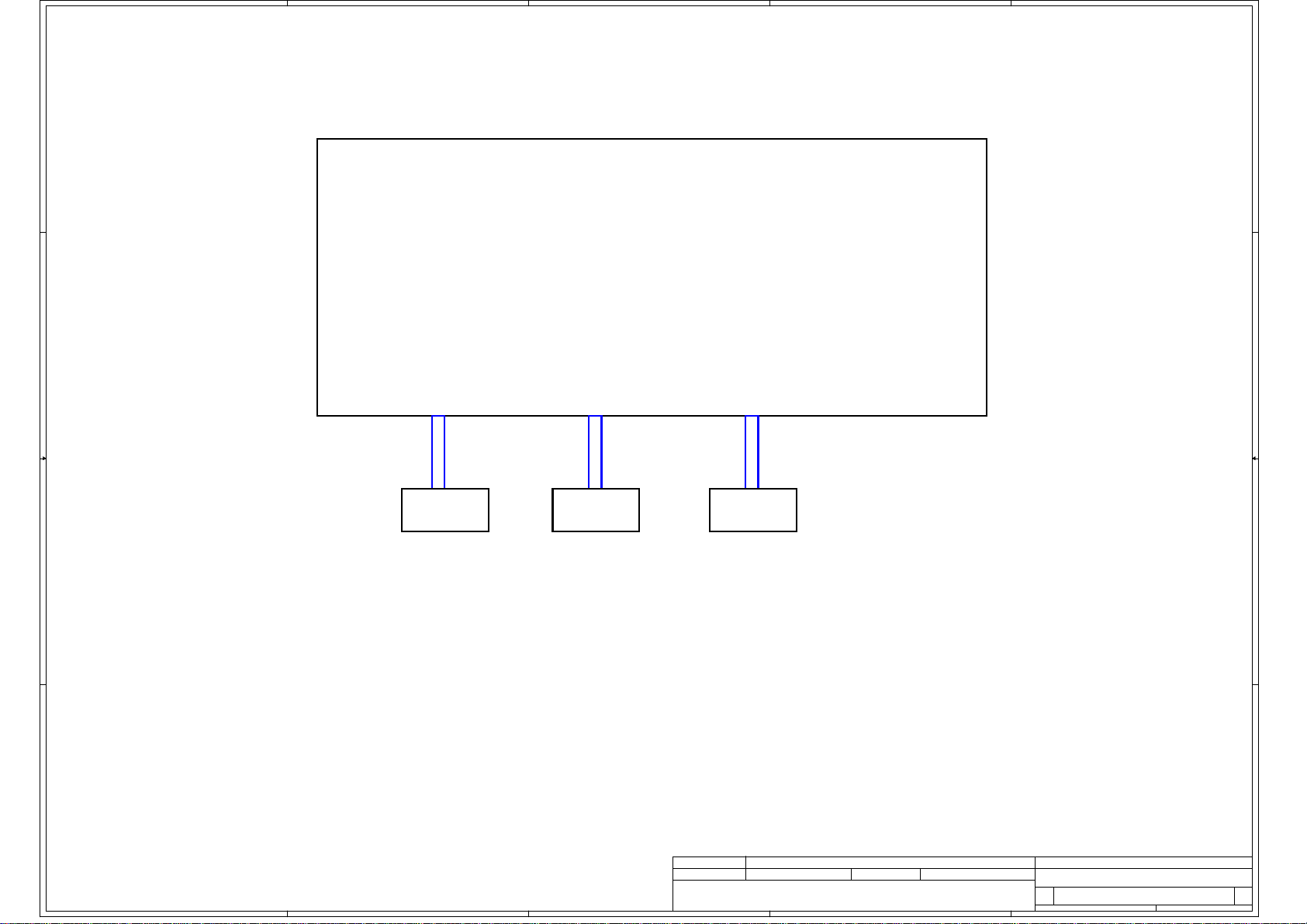

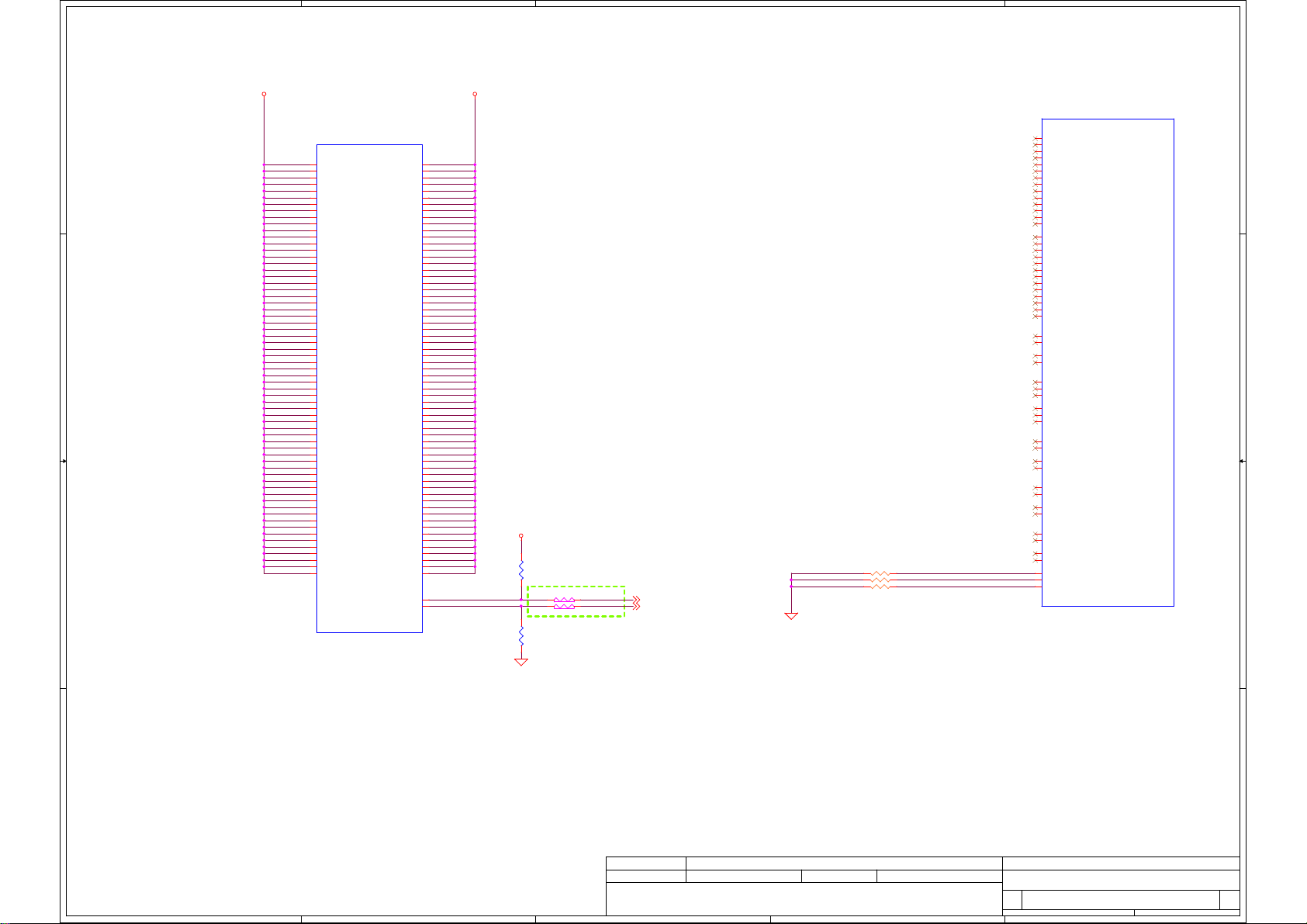

Block diagram

Block diagram

Block diagram

E

of

2 70Tuesday, November 08, 2016

of

2 70Tuesday, November 08, 2016

of

2 70Tuesday, November 08, 2016

0.1(X00)

0.1(X00)

0.1(X00)

4

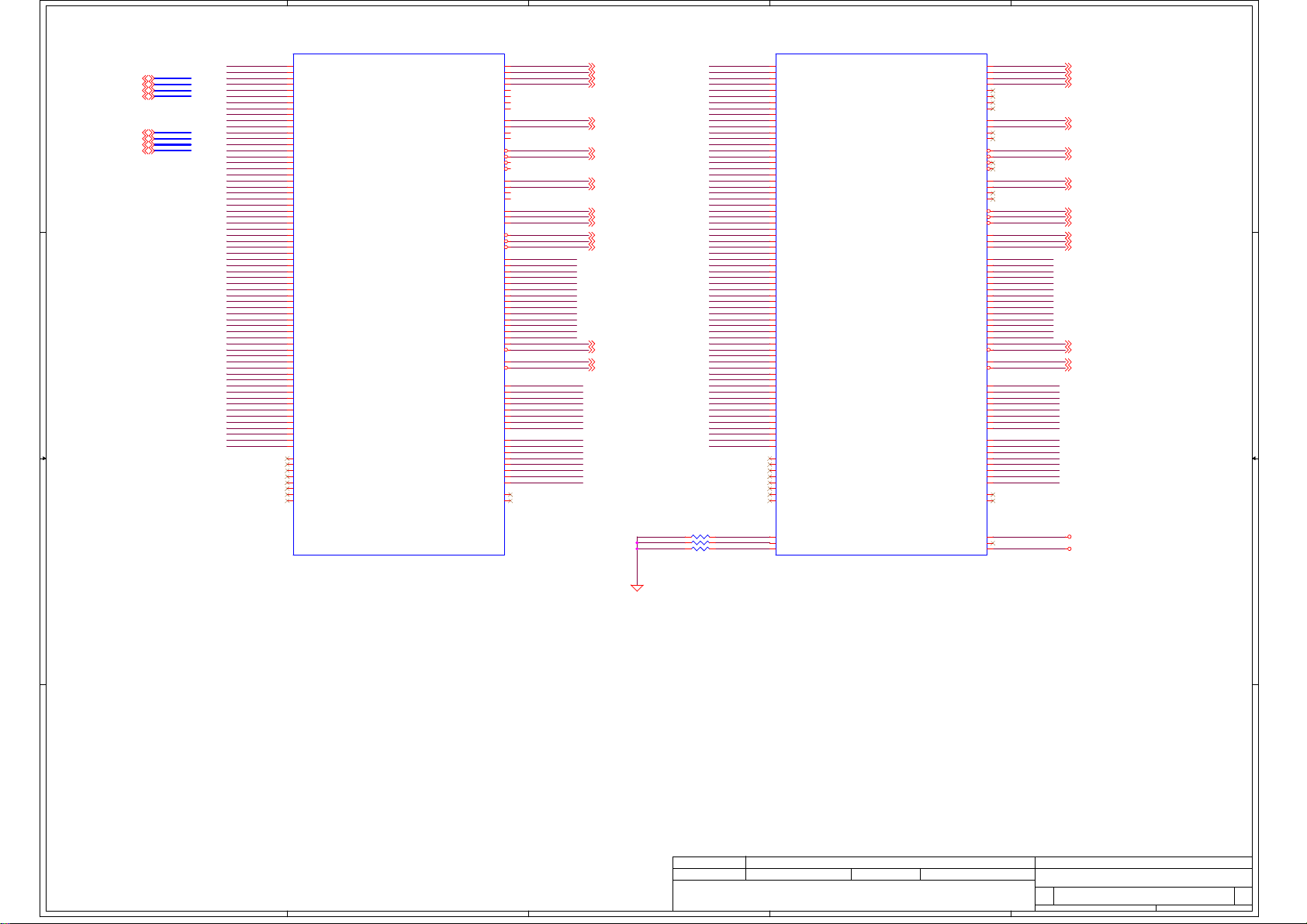

A

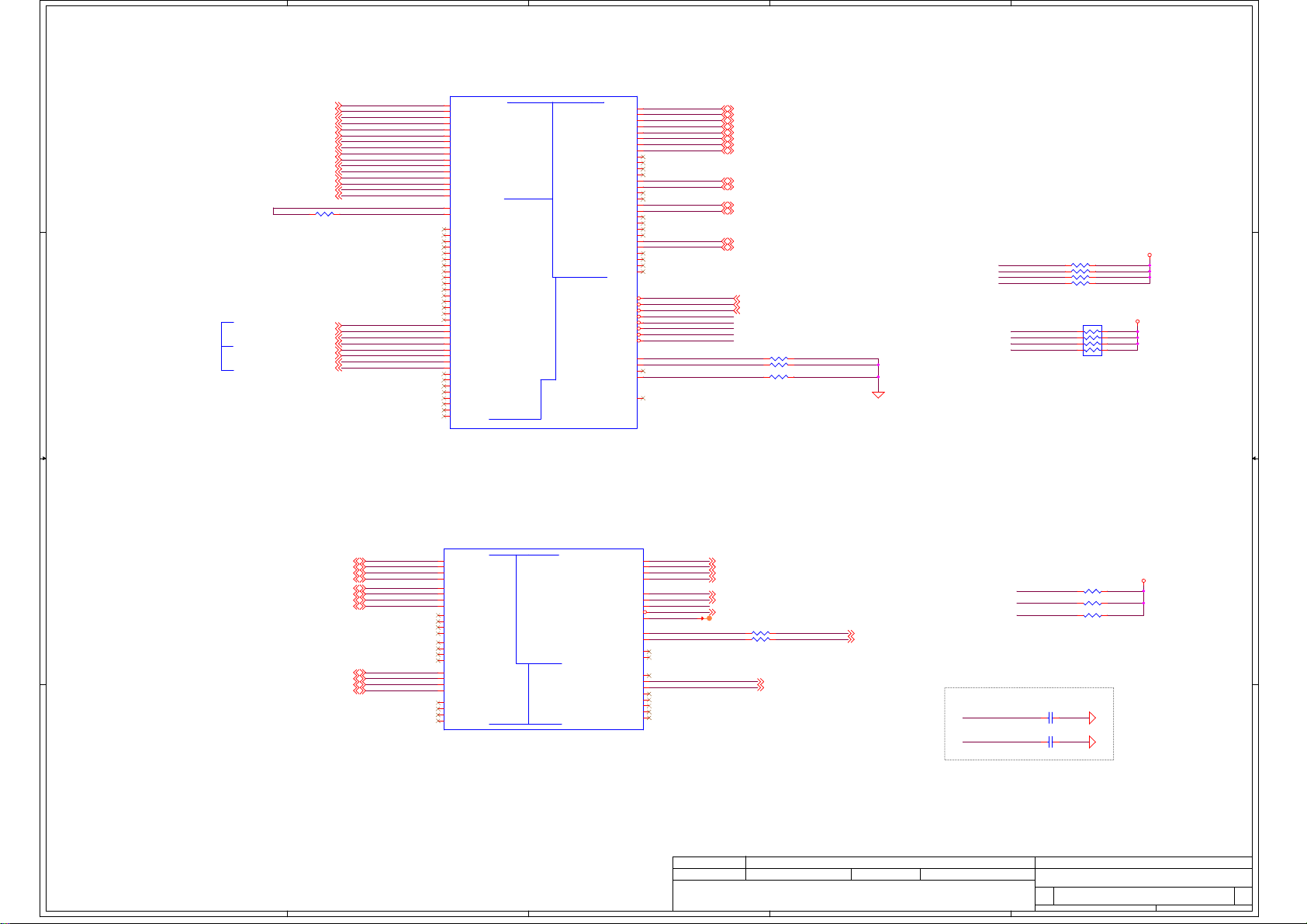

Compal Confidential

Project Code :

File Name :

B

C

D

E

1

1

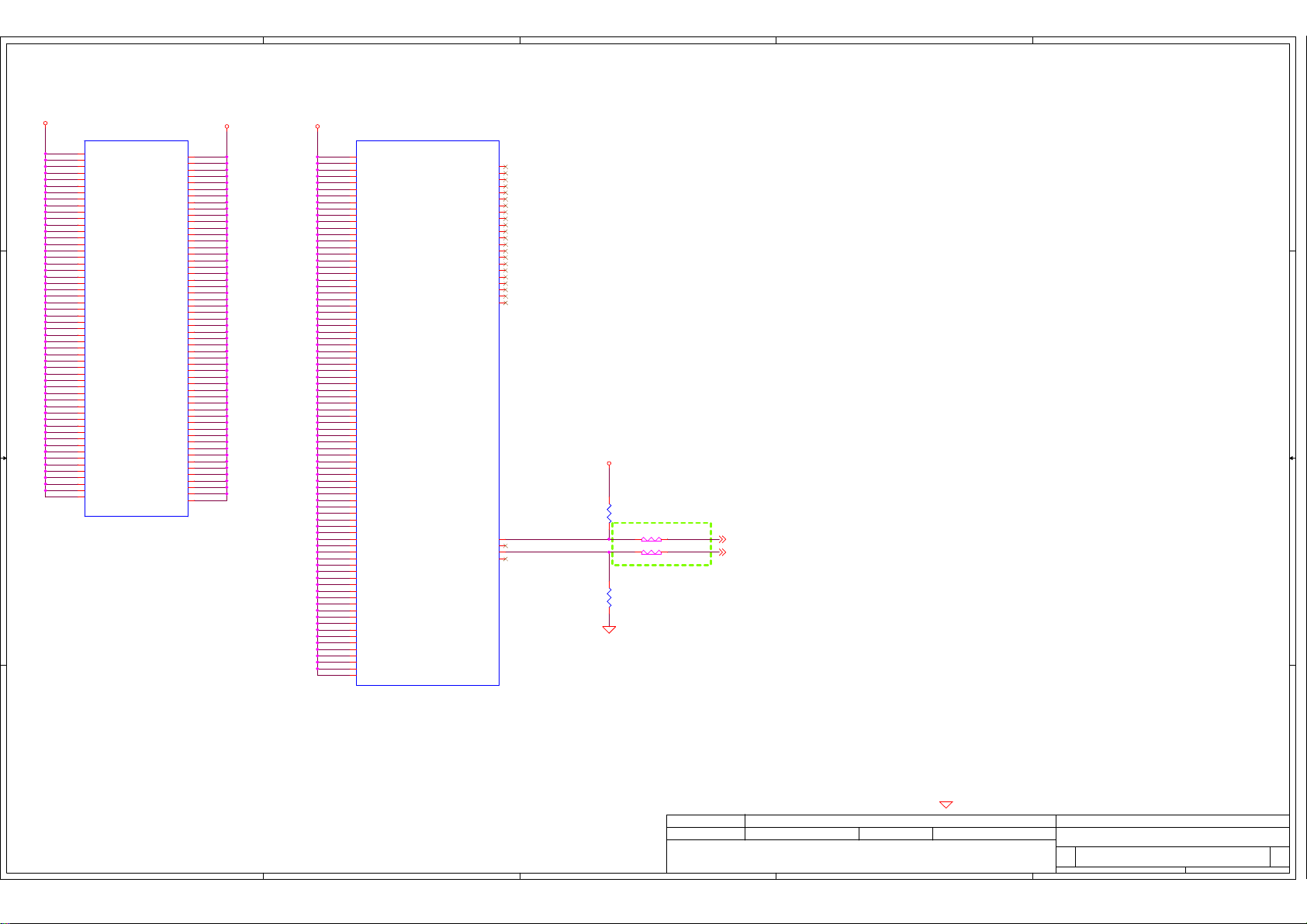

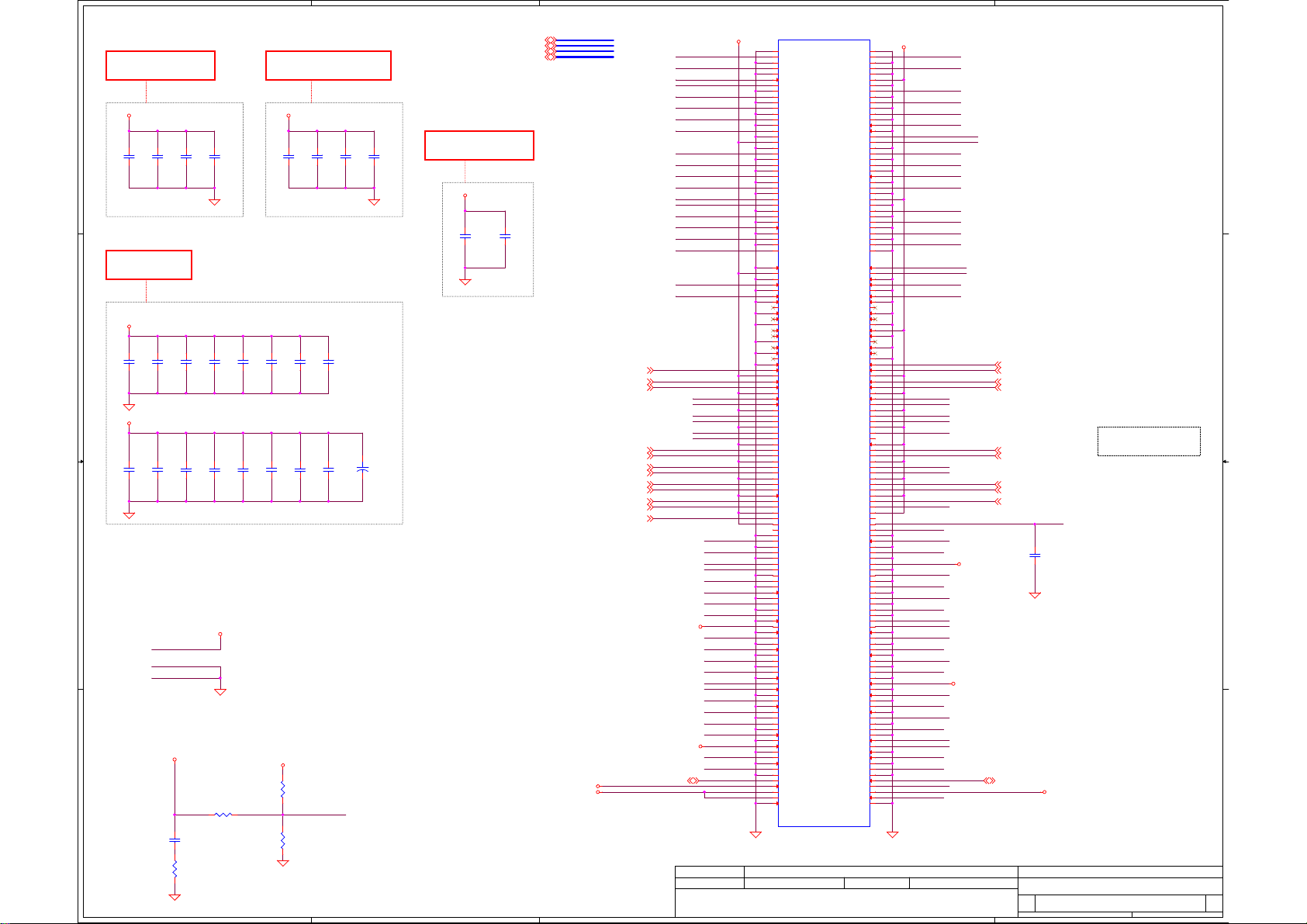

M/B

2

IO Board LED Board PWB Board

2

3

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

C

2011/08/25 2012/07/25

2011/08/25 2012/07/25

2011/08/25 2012/07/25

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

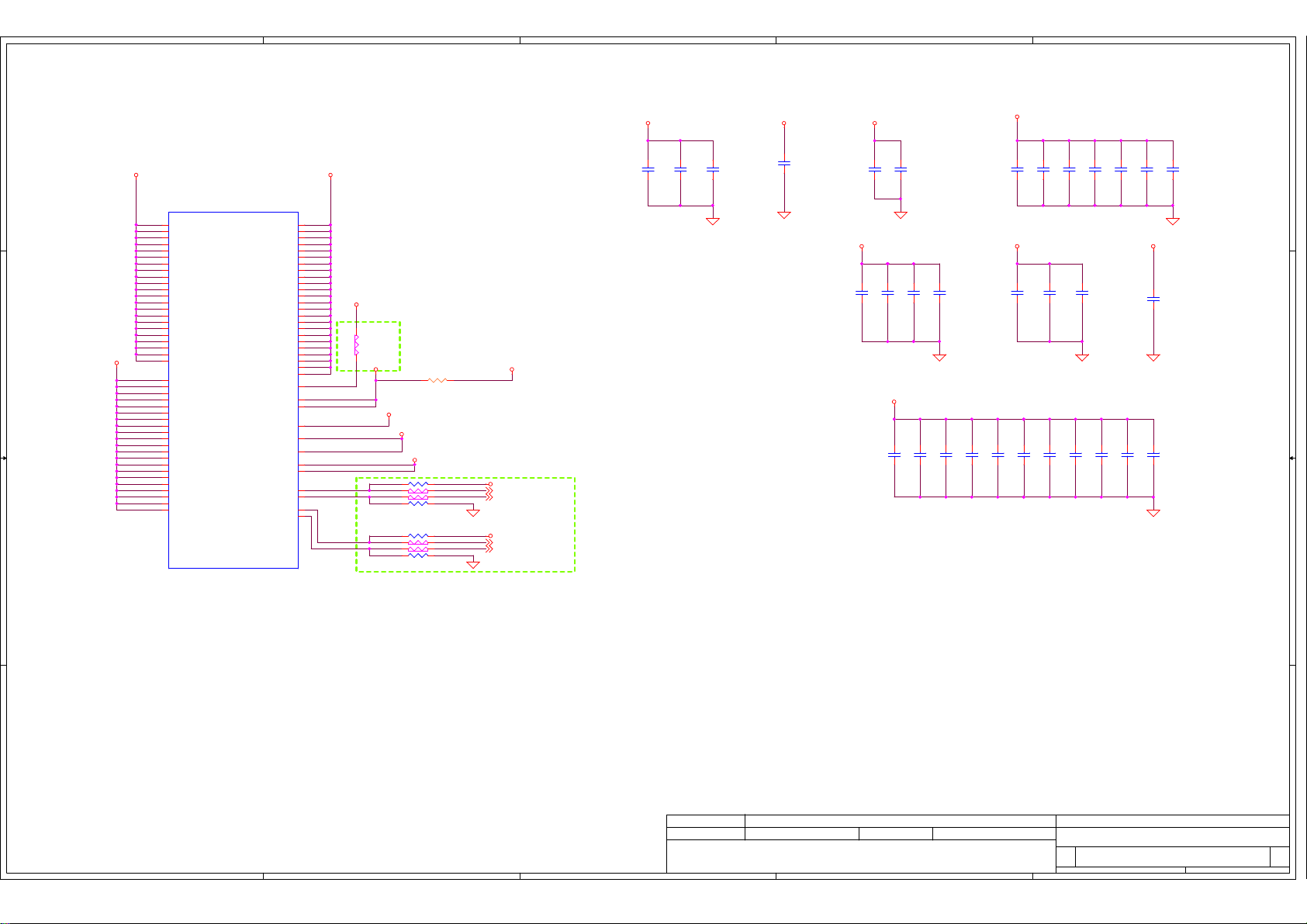

DB block diagram

DB block diagram

DB block diagram

E

of

3 70Tuesday, November 08, 2016

of

3 70Tuesday, November 08, 2016

of

3 70Tuesday, November 08, 2016

0.1(X00)

0.1(X00)

0.1(X00)

3

4

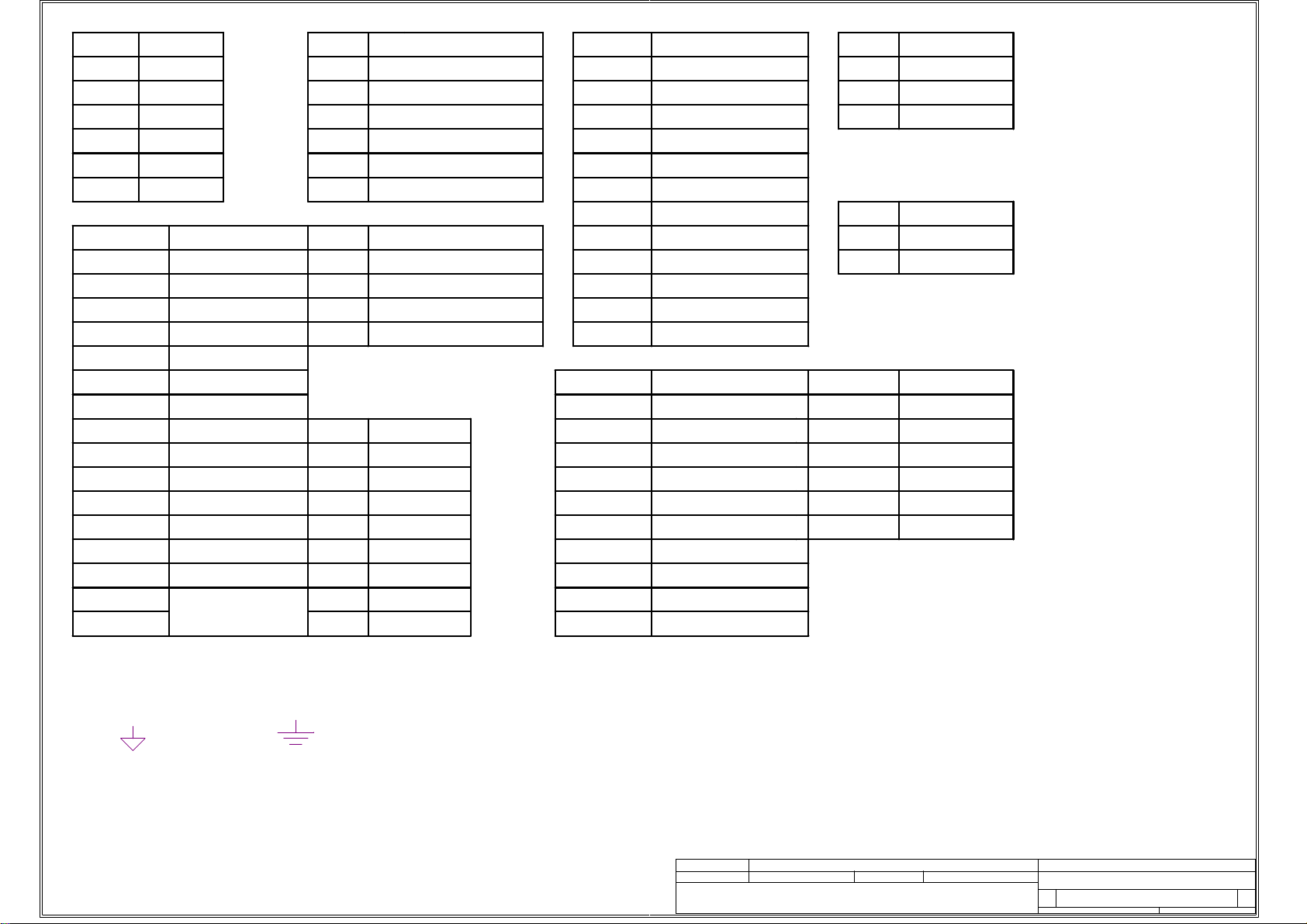

A

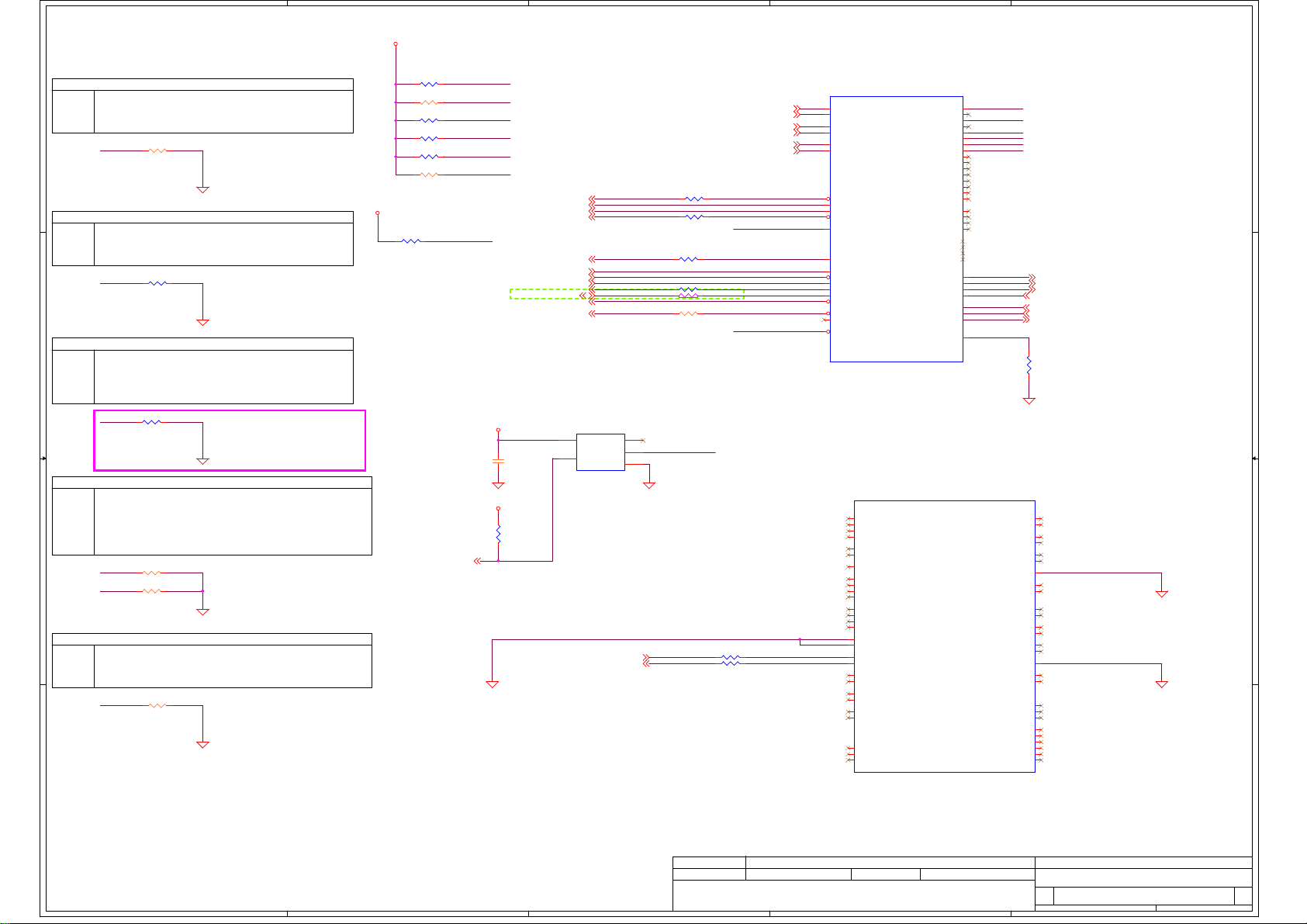

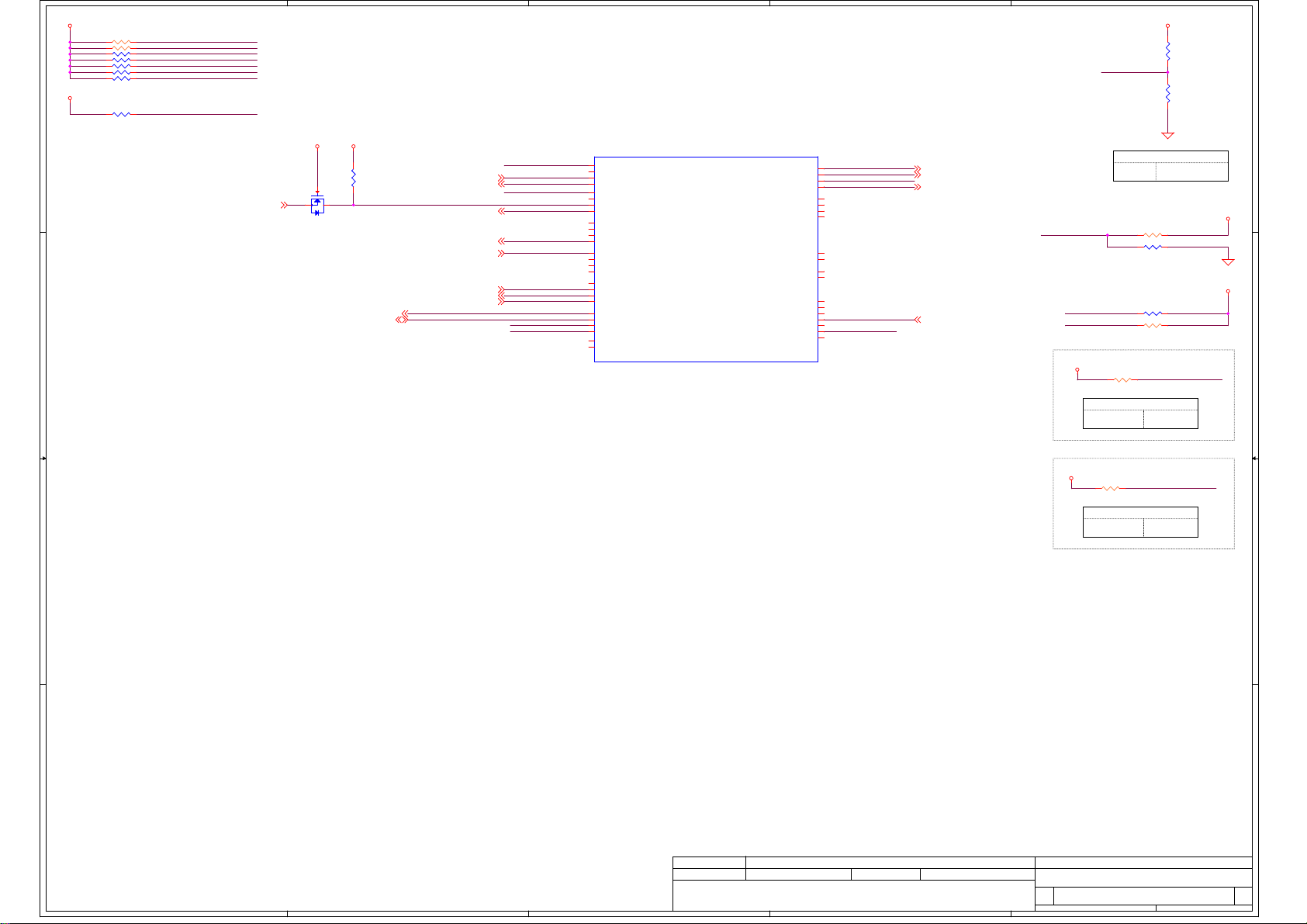

1

Board ID

X00

X01

X02

X03

X04

A00

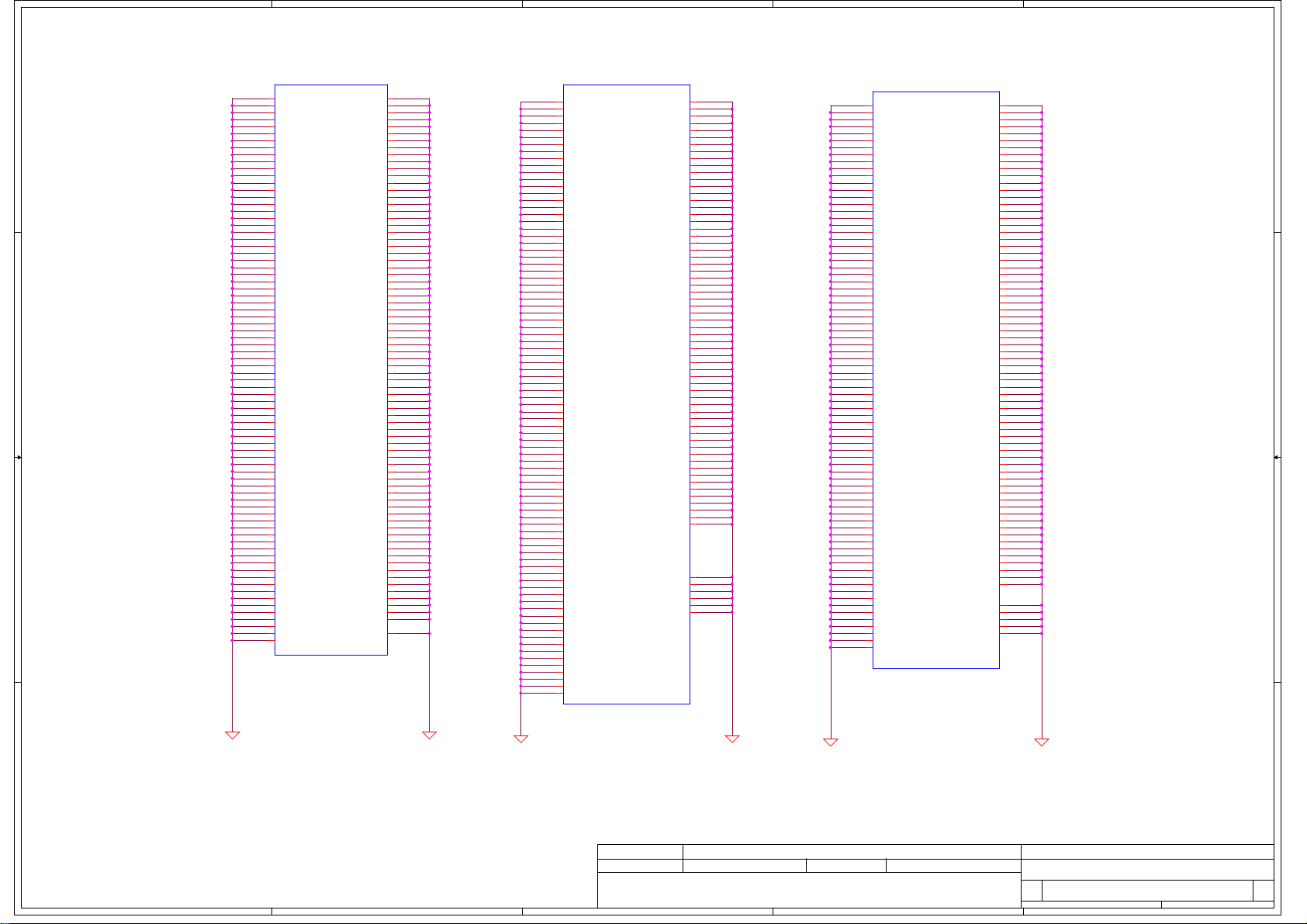

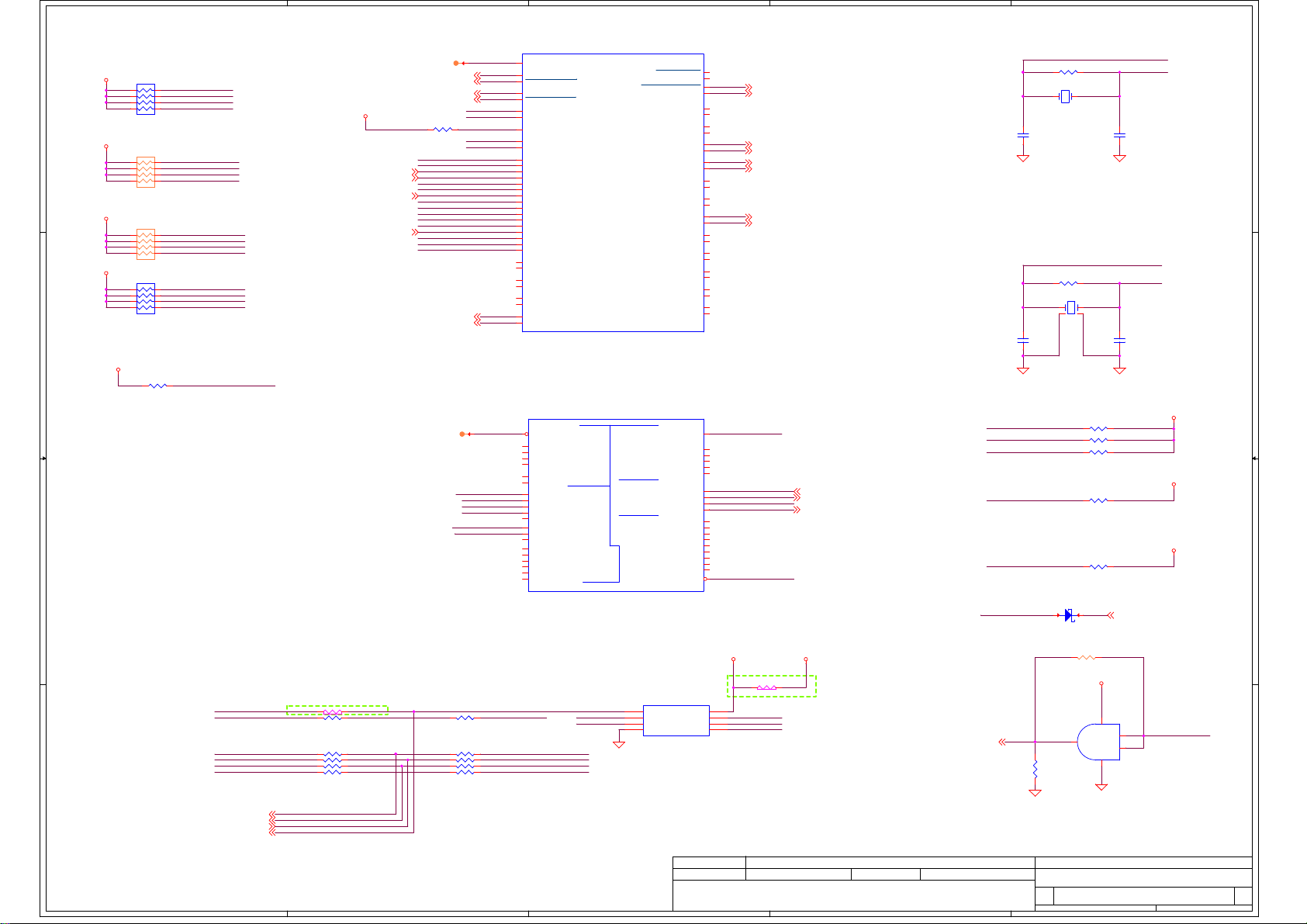

PCI EXPRESS

Lane 1

Lane 2

Lane 3

Lane 4

Lane 5

Lane 6

Lane 7

Lane 8 None

Lane 9

Lane 10

Lane 11

Lane 12

Lane 13

Lane 14

Lane 15

Lane 16

Resistor

N/A

22.1K

DESTINATION

NGFF-1 WLAN + BT

CARD READER

None

None

None

None

None

SSD

SSD

SSD

None

None

Alpine Ridge

USB31DESTINATION

USB Conn 1 (Right Side)

2

3

4

5

6

USB Conn 2 (Left Side)

None

None

None

None

DESTINATIONUSB3

7

8

9

10

SATA

0A

1A

N/A

N/A

0B

None

None

None

None

DESTINATION

SSD

N/ASSD

N/A

N/A

None

HDD1B

2

3

None

None

USB 2.0 DESTINATION

1

2

3

4

5

6

7

8

9

10

11

12

USB Conn 1 (Right Side)

USB Conn 2 (Left Side)

None None

NGFF-1 WLAN + BT

None

None

None

None

Touch screen

None

None

CAMERA

DESTINATIONCLKOUT_PCIE

0

1

2

3

4

None

None

None

NGFF-1 WLAN

CARD READER

Thunderbolt5

6

7

8

9

NGFF-2 SSD

GPU

None

None

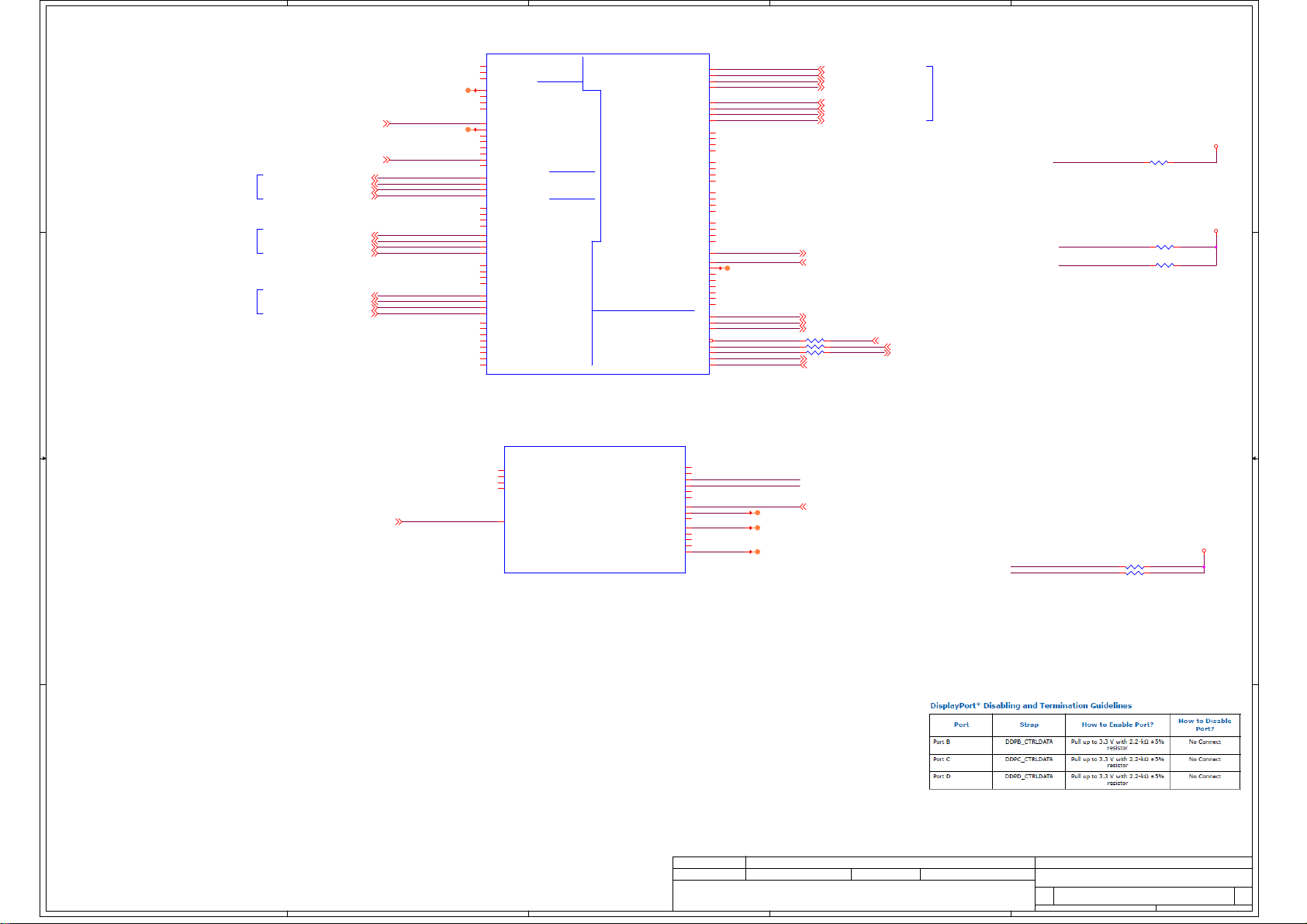

DDI

1

2

3

LPC

LPC1

CLKOUT_PCIE

10

11

12

13

14

15

DESTINATION

Alpine Ridge

Alpine Ridge

DESTINATION

MEC5085LPC0

DEBUG PORT

DESTINATION

None

None

None

None

None

None

1

Symbol Note :

: means Digital Ground : means Analog Ground

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

A

2011/08/25 2012/07/25

2011/08/25 2012/07/25

2011/08/25 2012/07/25

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

Notes List

Notes List

Notes List

LA-D991P

LA-D991P

LA-D991P

of

4 70Tuesday, November 08, 2016

of

4 70Tuesday, November 08, 2016

of

4 70Tuesday, November 08, 2016

0.1(X00)

0.1(X00)

0.1(X00)

5

4

3

2

1

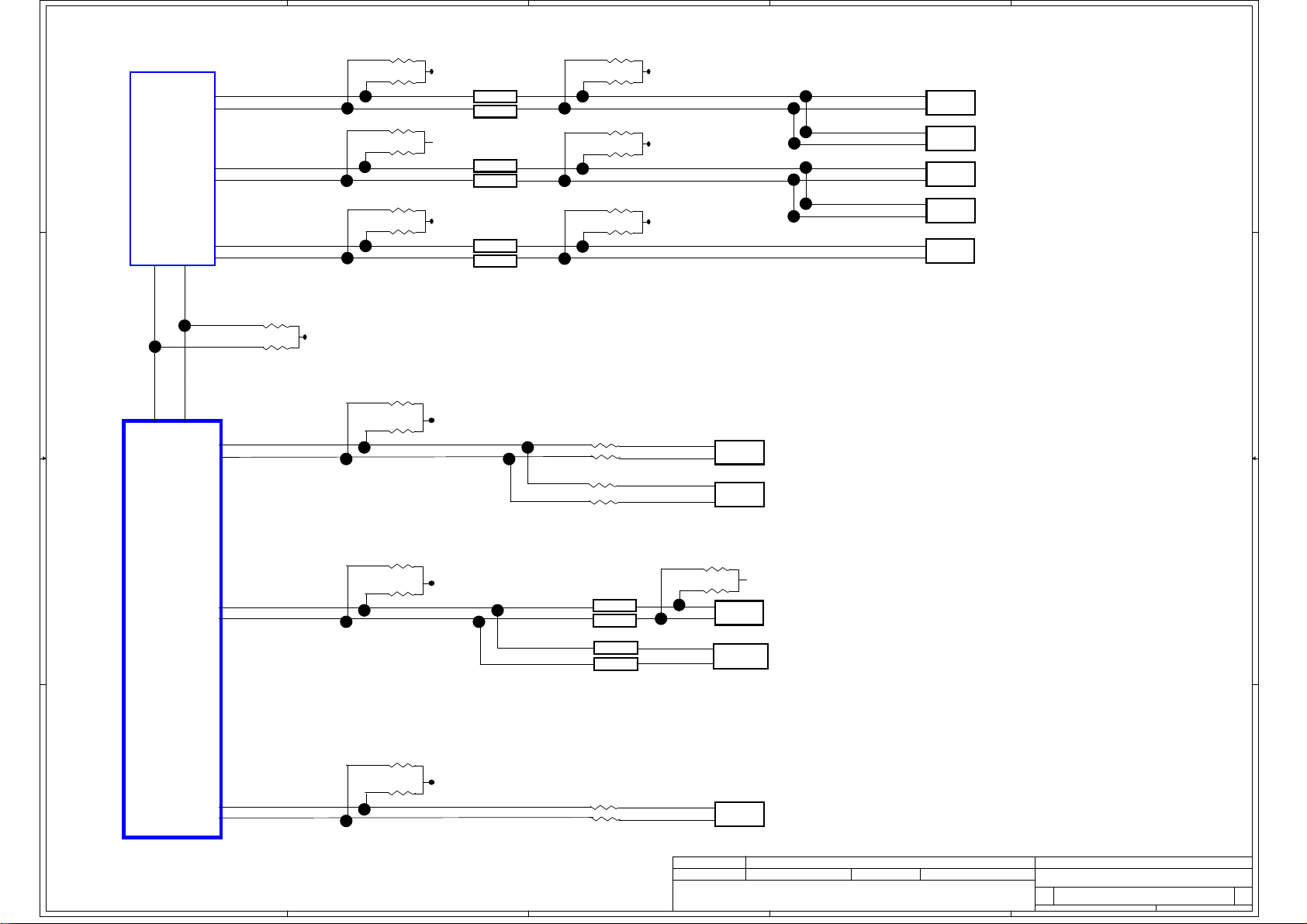

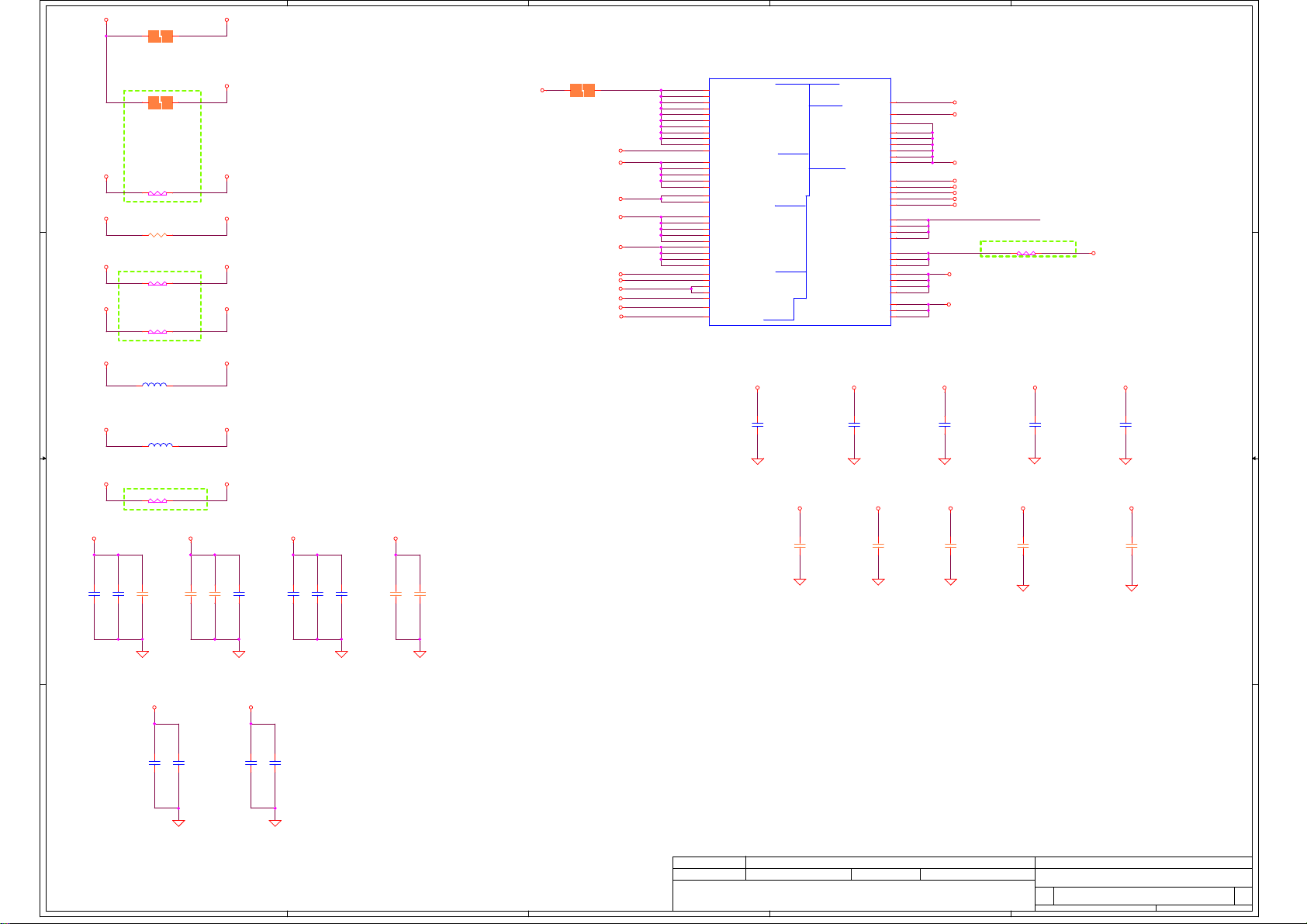

SMBUS Address [0x9a]

AW44

BB43

D

PCH

AW42

AW45

SMBCLK

SMBDATA

SML1_SMBCLK

SML1_SMBDAT

1K

1K

+3V_PCH

+3VS

DMN65D8L

+3V_PCH

DMN65D8L

+3V_PCH

DMN65D8L

1K

1K

DMN65D8L

4.7K

AR41

AR44

I2C1_SCK_TP

I2C1_SDA_TP

4.7K

AW42AW45

SML0_SMBCLK

C

SML0_SMBDATA

499

499

+3V_PCH

+3VS

+3VS

DMN65D8L

DMN65D8L

1K

1K

1K

1K

2.4K

2.4K

+3VS

+3VALW

+3VS_TP

DIMMA

D

DIMMB

Thermal

GPU

TP

C

4.7K

A5 B6

9

8

PBAT_CHG_SMBCLK

PBAT_CHG_SMBDAT

4.7K

2.2K

+3VALW_EC

100 ohm

100 ohm

BATT

0x16

0 ohm

0 ohm

Charger

MEC1404

B

12

11

GPU_THM_SMBCLK

GPU_THM_SMBDAT

2.2K

+3VALW_EC

DGPU_PEX_RST#

DMN66D0

DMN66D0

DMN66D0

DMN66D0

2.2K

5.1K

5.1K

+3.3V_GFX_AON

GPU

Thermal

B

0x9E

2.2K

4

+3VALW_EC

0 ohm

0 ohm

MCP23017

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

3

0x42

Compal Secret Data

Compal Secret Data

2011/08/25 2012/07/15

2011/08/25 2012/07/15

2011/08/25 2012/07/15

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Title

Title

Title

SMBus Block Diagram

SMBus Block Diagram

SMBus Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

1

of

5 70Tuesday, November 08, 2016

of

5 70Tuesday, November 08, 2016

of

5 70Tuesday, November 08, 2016

0.1(X00)

0.1(X00)

0.1(X00)

A

A

5

B4

A3

MCP23017_SMBCLK

MCP23017_SMBDAT

2.2K

5

4

3

2

1

D

C

+VCCST

+VCCSTG

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_JTAG_TDI

RH97

RH98

RH100

RH497

RH496

RH56

RH95

RH61

RH60

1

@

1

@

1

@

1

1

1

1

@

1

1

@

RH115 0_0402_5%@

RH492 0_0402_5%@

RH118 0_0402_5%@

2

51_0402_5%

2

51_0402_5%

2

51_0402_5%

2

51_0402_5%

2

51_0402_5%

2

51_0402_5%

2

51_0402_5%

2

51_0402_5%

2

51_0402_5%

1

1

1

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_JTAG_TDI

CPU_XDP_TDO

CPU_XDP_TMS

CPU_XDP_TDI

PCH_JTAG_TCK

CPU_XDP_TCK

CPU_XDP_TRST#

2

2

2

PCH_JTAG_TDO [18]

PCH_JTAG_TMS [18]

PCH_JTAG_TDI [18]

PCH_JTAG_TCK [18]

CPU_XDP_TCK [9,18]

CPU_XDP_TRST# [9,22]

CPU_XDP_TDO [9]

CPU_XDP_TMS [9]

CPU_XDP_TDI [9]

D

C

Pilot_05

B

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

3

2011/08/25 2012/07/25

2011/08/25 2012/07/25

2011/08/25 2012/07/25

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

XDP CONN

XDP CONN

XDP CONN

1

of

6 70Tuesday, November 08, 2016

of

6 70Tuesday, November 08, 2016

of

6 70Tuesday, November 08, 2016

0.1(X00)

0.1(X00)

0.1(X00)

B

A

5

PEG_HTX_C_GRX_P[0..15][23]

PEG_HTX_C_GRX_N[0..15][23]

PEG_GTX_C_HRX_P[0..15][23]

PEG_GTX_C_HRX_N[0..15][23]

D

C

PEG_HTX_C_GRX_P[0..15]

PEG_HTX_C_GRX_N[0..15]

PEG_GTX_C_HRX_P[0..15]

PEG_GTX_C_HRX_N[0..15]

+VCCIO

RH24

1

24.9_0402_1%

DMI_CRX_PTX_P0[19]

DMI_CRX_PTX_N0[19]

DMI_CRX_PTX_P1[19]

DMI_CRX_PTX_N1[19]

DMI_CRX_PTX_P2[19]

DMI_CRX_PTX_N2[19]

DMI_CRX_PTX_P3[19]

DMI_CRX_PTX_N3[19]

PEG_GTX_C_HRX_P15

PEG_GTX_C_HRX_N15

PEG_GTX_C_HRX_P14

PEG_GTX_C_HRX_N14

PEG_GTX_C_HRX_P13

PEG_GTX_C_HRX_N13

PEG_GTX_C_HRX_P12

PEG_GTX_C_HRX_N12

PEG_GTX_C_HRX_P11

PEG_GTX_C_HRX_N11

PEG_GTX_C_HRX_P10

PEG_GTX_C_HRX_N10

PEG_GTX_C_HRX_P9

PEG_GTX_C_HRX_N9

PEG_GTX_C_HRX_P8

PEG_GTX_C_HRX_N8

PEG_GTX_C_HRX_P7

PEG_GTX_C_HRX_N7

PEG_GTX_C_HRX_P6

PEG_GTX_C_HRX_N6

PEG_GTX_C_HRX_P5

PEG_GTX_C_HRX_N5

PEG_GTX_C_HRX_P4

PEG_GTX_C_HRX_N4

PEG_GTX_C_HRX_P3

PEG_GTX_C_HRX_N3

PEG_GTX_C_HRX_P2

PEG_GTX_C_HRX_N2

PEG_GTX_C_HRX_P1

PEG_GTX_C_HRX_N1

PEG_GTX_C_HRX_P0

PEG_GTX_C_HRX_N0

2

4

PEG_RCOMP

E25

D25

E24

F24

E23

D23

E22

F22

E21

D21

E20

F20

E19

D19

E18

F18

D17

E17

F16

E16

D15

E15

F14

E14

D13

E13

F12

E12

D11

E11

F10

E10

G2

D8

E8

E6

F6

D5

E5

J8

J9

UH1C

PEG_RXP[0]

PEG_RXN[0]

PEG_RXP[1]

PEG_RXN[1]

PEG_RXP[2]

PEG_RXN[2]

PEG_RXP[3]

PEG_RXN[3]

PEG_RXP[4]

PEG_RXN[4]

PEG_RXP[5]

PEG_RXN[5]

PEG_RXP[6]

PEG_RXN[6]

PEG_RXP[7]

PEG_RXN[7]

PEG_RXP[8]

PEG_RXN[8]

PEG_RXP[9]

PEG_RXN[9]

PEG_RXP[10]

PEG_RXN[10]

PEG_RXP[11]

PEG_RXN[11]

PEG_RXP[12]

PEG_RXN[12]

PEG_RXP[13]

PEG_RXN[13]

PEG_RXP[14]

PEG_RXN[14]

PEG_RXP[15]

PEG_RXN[15]

PEG_RCOMP

DMI_RXP[0]

DMI_RXN[0]

DMI_RXP[1]

DMI_RXN[1]

DMI_RXP[2]

DMI_RXN[2]

DMI_RXP[3]

DMI_RXN[3]

SKL-H_BGA1440

@

REV = 1

SKYLAKE_HALO

BGA1440

?

3 OF 14

PEG_TXP[0]

PEG_TXN[0]

PEG_TXP[1]

PEG_TXN[1]

PEG_TXP[2]

PEG_TXN[2]

PEG_TXP[3]

PEG_TXN[3]

PEG_TXP[4]

PEG_TXN[4]

PEG_TXP[5]

PEG_TXN[5]

PEG_TXP[6]

PEG_TXN[6]

PEG_TXP[7]

PEG_TXN[7]

PEG_TXP[8]

PEG_TXN[8]

PEG_TXP[9]

PEG_TXN[9]

PEG_TXP[10]

PEG_TXN[10]

PEG_TXP[11]

PEG_TXN[11]

PEG_TXP[12]

PEG_TXN[12]

PEG_TXP[13]

PEG_TXN[13]

PEG_TXP[14]

PEG_TXN[14]

PEG_TXP[15]

PEG_TXN[15]

DMI_TXP[0]

DMI_TXN[0]

DMI_TXP[1]

DMI_TXN[1]

DMI_TXP[2]

DMI_TXN[2]

DMI_TXP[3]

DMI_TXN[3]

B25

A25

B24

C24

B23

A23

B22

C22

B21

A21

B20

C20

B19

A19

B18

C18

A17

B17

C16

B16

A15

B15

C14

B14

A13

B13

C12

B12

A11

B11

C10

B10

B8

A8

C6

B6

B5

A5

D4

B4

?

3

PEG_HTX_GRX_P15

PEG_HTX_GRX_N15

PEG_HTX_GRX_P14

PEG_HTX_GRX_N14

PEG_HTX_GRX_P13

PEG_HTX_GRX_N13

PEG_HTX_GRX_P12

PEG_HTX_GRX_N12

PEG_HTX_GRX_P11

PEG_HTX_GRX_N11

PEG_HTX_GRX_P10

PEG_HTX_GRX_N10

PEG_HTX_GRX_P9

PEG_HTX_GRX_N9

PEG_HTX_GRX_P8

PEG_HTX_GRX_N8

PEG_HTX_GRX_P7

PEG_HTX_GRX_N7

PEG_HTX_GRX_P6

PEG_HTX_GRX_N6

PEG_HTX_GRX_P5

PEG_HTX_GRX_N5

PEG_HTX_GRX_P4

PEG_HTX_GRX_N4

PEG_HTX_GRX_P3

PEG_HTX_GRX_N3

PEG_HTX_GRX_P2

PEG_HTX_GRX_N2

PEG_HTX_GRX_P1

PEG_HTX_GRX_N1

PEG_HTX_GRX_P0

PEG_HTX_GRX_N0

1

2

CH5 0.22U_0201_6.3V6M

1

2

CH6 0.22U_0201_6.3V6M

1

2

CH7 0.22U_0201_6.3V6M

1

2

CH8 0.22U_0201_6.3V6M

1

2

CH9 0.22U_0201_6.3V6M

1

2

CH10 0.22U_0201_6.3V6M

1

2

CH11 0.22U_0201_6.3V6M

1

2

CH12 0.22U_0201_6.3V6M

1

2

CH13 0.22U_0201_6.3V6M

1

2

CH14 0.22U_0201_6.3V6M

1

2

CH15 0.22U_0201_6.3V6M

1

2

CH16 0.22U_0201_6.3V6M

1

2

CH17 0.22U_0201_6.3V6M

1

2

CH18 0.22U_0201_6.3V6M

1

2

CH19 0.22U_0201_6.3V6M

1

2

CH20 0.22U_0201_6.3V6M

1

2

CH21 0.22U_0201_6.3V6M

1

2

CH22 0.22U_0201_6.3V6M

1

2

CH23 0.22U_0201_6.3V6M

1

2

CH24 0.22U_0201_6.3V6M

1

2

CH25 0.22U_0201_6.3V6M

1

2

CH26 0.22U_0201_6.3V6M

1

2

CH27 0.22U_0201_6.3V6M

1

2

CH28 0.22U_0201_6.3V6M

1

2

CH29 0.22U_0201_6.3V6M

1

2

CH30 0.22U_0201_6.3V6M

1

2

CH31 0.22U_0201_6.3V6M

1

2

CH32 0.22U_0201_6.3V6M

1

2

CH33 0.22U_0201_6.3V6M

1

2

CH34 0.22U_0201_6.3V6M

1

2

CH35 0.22U_0201_6.3V6M

1

2

CH36 0.22U_0201_6.3V6M

DMI_CTX_PRX_P0 [19]

DMI_CTX_PRX_N0 [19]

DMI_CTX_PRX_P1 [19]

DMI_CTX_PRX_N1 [19]

DMI_CTX_PRX_P2 [19]

DMI_CTX_PRX_N2 [19]

DMI_CTX_PRX_P3 [19]

DMI_CTX_PRX_N3 [19]

PEG_HTX_C_GRX_P15

PEG_HTX_C_GRX_N15

PEG_HTX_C_GRX_P14

PEG_HTX_C_GRX_N14

PEG_HTX_C_GRX_P13

PEG_HTX_C_GRX_N13

PEG_HTX_C_GRX_P12

PEG_HTX_C_GRX_N12

PEG_HTX_C_GRX_P11

PEG_HTX_C_GRX_N11

PEG_HTX_C_GRX_P10

PEG_HTX_C_GRX_N10

PEG_HTX_C_GRX_P9

PEG_HTX_C_GRX_N9

PEG_HTX_C_GRX_P8

PEG_HTX_C_GRX_N8

PEG_HTX_C_GRX_P7

PEG_HTX_C_GRX_N7

PEG_HTX_C_GRX_P6

PEG_HTX_C_GRX_N6

PEG_HTX_C_GRX_P5

PEG_HTX_C_GRX_N5

PEG_HTX_C_GRX_P4

PEG_HTX_C_GRX_N4

PEG_HTX_C_GRX_P3

PEG_HTX_C_GRX_N3

PEG_HTX_C_GRX_P2

PEG_HTX_C_GRX_N2

PEG_HTX_C_GRX_P1

PEG_HTX_C_GRX_N1

PEG_HTX_C_GRX_P0

PEG_HTX_C_GRX_N0

2

1

D

C

UH1D

K36

DDI1_TXP[0]

B

A

5

K37

DDI1_TXN[0]

J35

DDI1_TXP[1]

J34

DDI1_TXN[1]

H37

DDI1_TXP[2]

H36

DDI1_TXN[2]

J37

DDI1_TXP[3]

J38

DDI1_TXN[3]

D27

DDI1_AUXP

E27

DDI1_AUXN

H34

DDI2_TXP[0]

H33

DDI2_TXN[0]

F37

DDI2_TXP[1]

G38

DDI2_TXN[1]

F34

DDI2_TXP[2]

F35

DDI2_TXN[2]

E37

DDI2_TXP[3]

E36

DDI2_TXN[3]

F26

DDI2_AUXP

E26

DDI2_AUXN

C34

DDI3_TXP[0]

D34

DDI3_TXN[0]

B36

DDI3_TXP[1]

B34

DDI3_TXN[1]

F33

DDI3_TXP[2]

E33

DDI3_TXN[2]

C33

DDI3_TXP[3]

B33

DDI3_TXN[3]

A27

DDI3_AUXP

B27

DDI3_AUXN

SKL-H_BGA1440

@

4

REV = 1

BGA1440

4 OF 14

EDP_TXP[0]

EDP_TXN[0]

EDP_TXP[1]

EDP_TXN[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXP

EDP_AUXN

EDP_DISP_UTIL

EDP_RCOMP

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

D29

E29

F28

E28

B29

A29

B28

C28

C26

B26

A33

EDP_DISP_UTIL

D37

EDP_COMP

G27

G25

G29

?

Close to CPU

3

EDP_TXP0 [34]

EDP_TXN0 [34]

EDP_TXP1 [34]

EDP_TXN1 [34]

EDP_TXN2 [34]

EDP_TXP2 [34]

EDP_TXN3 [34]

EDP_TXP3 [34]

EDP_AUXP [34]

EDP_AUXN [34]

1

RH20 0_0402_5%@

RH30 24.9_0402_1%

1

RH145 20_0402_5%

2

1

2

EDP_COMP

CAD Note:Trace width=20 mils ,Spacing=25mil,

Max length=100 mils.

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

BIA_PWM_PCH [16,34]

AUD_AZA_CPU_SCLK [18]

AUD_AZA_CPU_SDO [18]

AUD_AZA_CPU_SDI_R [18]

2011/08/25 2012/07/25

2011/08/25 2012/07/25

2011/08/25 2012/07/25

+VCCIO

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Title

Title

Title

PROCESSOR(1/7) DMI,FDI,PEG

PROCESSOR(1/7) DMI,FDI,PEG

PROCESSOR(1/7) DMI,FDI,PEG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

1

of

7 70Tuesday, November 08, 2016

of

7 70Tuesday, November 08, 2016

of

7 70Tuesday, November 08, 2016

0.1(X00)

0.1(X00)

0.1(X00)

B

A

?

SKYLAKE_HALO

Interleave

5

4

3

2

1

?

REV = 1

SKYLAKE_HALO

BGA1440

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

1 OF 14

DDR0_CKP[0]

DDR0_CKN[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CLKP[2]

DDR0_CLKN[2]

DDR0_CLKP[3]

DDR0_CLKN[3]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_CS#[2]

DDR0_CS#[3]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_ODT[2]

DDR0_ODT[3]

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

DDR0_ALERT#

DDR0_DQSN[0]

DDR0_DQSN[1]

DDR0_DQSP[0]

DDR0_DQSP[1]

DDR0_DQSP[8]

DDR0_DQSN[8]

?

AG1

AG2

AK1

AK2

AL3

AK3

AL2

AL1

AT1

AT2

AT3

AT5

AD5

AE2

AD2

AE5

AD3

AE4

AE1

AD4

AH5

AH1

AU1

AH4

AG4

AD1

AH3

AP4

AN4

AP5

AP2

AP1

AP3

AN1

AN3

AT4

AH2

AN2

AU4

AE3

AU2

AU3

AG3

AU5

BR5

BL3

BG3

BD3

AB3

V3

R3

M3

BP5

BK3

BF3

BC3

AA3

U3

P3

L3

AY3

BA3

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

M_CLK_DDR0 [14]

M_CLK_DDR#0 [14]

M_CLK_DDR#1 [14]

M_CLK_DDR1 [14]

DDR_CKE0_DIMMA [14]

DDR_CKE1_DIMMA [14]

DDR_CS0_DIMMA# [14]

DDR_CS1_DIMMA# [14]

M_ODT0 [14]

M_ODT1 [14]

DDR_A_BS0 [14]

DDR_A_BS1 [14]

DDR_A_BG0 [14]

DDR_A_RAS# [14]

DDR_A_WE# [14]

DDR_A_CAS# [14]

DDR_A_BG1 [14]

DDR_A_ACT# [14]

DDR_A_PAR [14]

DDR_A_ALERT# [14]

RH148 121_0402_1%

RH149 75_0402_1%

RH150 100_0402_1%

DDR_B_D0

DDR_B_D1

DDR_B_D6

DDR_B_D2

DDR_B_D4

DDR_B_D5

DDR_B_D3

DDR_B_D7

DDR_B_D12

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D14

DDR_B_D11

DDR_B_D13

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D21

DDR_B_D19

DDR_B_D18

DDR_B_D22

DDR_B_D20

DDR_B_D23

DDR_B_D26

DDR_B_D24

DDR_B_D31

DDR_B_D25

DDR_B_D28

DDR_B_D30

DDR_B_D29

DDR_B_D27

DDR_B_D34

DDR_B_D38

DDR_B_D32

DDR_B_D36

DDR_B_D35

DDR_B_D39

DDR_B_D37

DDR_B_D33

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D47

DDR_B_D46

DDR_B_D48

DDR_B_D51

DDR_B_D50

DDR_B_D52

DDR_B_D53

DDR_B_D55

DDR_B_D49

DDR_B_D54

DDR_B_D58

DDR_B_D57

DDR_B_D59

DDR_B_D61

DDR_B_D62

DDR_B_D60

DDR_B_D56

DDR_B_D63

1

2

1

2

1

2

DDR1_DQ[0]/DDR0_DQ[16]

BR11

DDR1_DQ[1]/DDR0_DQ[17]

BT8

DDR1_DQ[2]/DDR0_DQ[18]

BR8

DDR1_DQ[3]/DDR0_DQ[19]

BP11

DDR1_DQ[4]/DDR0_DQ[20]

BN11

DDR1_DQ[5]/DDR0_DQ[21]

BP8

DDR1_DQ[6]/DDR0_DQ[22]

BN8

DDR1_DQ[7]/DDR0_DQ[23]

BL12

DDR1_DQ[8]/DDR0_DQ[24]

BL11

DDR1_DQ[9]/DDR0_DQ[25]

BL8

DDR1_DQ[10]/DDR0_DQ[26]

BJ8

DDR1_DQ[11]/DDR0_DQ[27]

BJ11

DDR1_DQ[12]/DDR0_DQ[28]

BJ10

DDR1_DQ[13]/DDR0_DQ[29]

BL7

DDR1_DQ[14]/DDR0_DQ[30]

BJ7

DDR1_DQ[15]/DDR0_DQ[31]

BG11

DDR1_DQ[16]/DDR0_DQ[48]

BG10

DDR1_DQ[17]/DDR0_DQ[49]

BG8

DDR1_DQ[18]/DDR0_DQ[50]

BF8

DDR1_DQ[19]/DDR0_DQ[51]

BF11

DDR1_DQ[20]/DDR0_DQ[52]

BF10

DDR1_DQ[21]/DDR0_DQ[53]

BG7

DDR1_DQ[22]/DDR0_DQ[54]

BF7

DDR1_DQ[23]/DDR0_DQ[55]

BB11

DDR1_DQ[24]/DDR0_DQ[56]

BC11

DDR1_DQ[25]/DDR0_DQ[57]

BB8

DDR1_DQ[26]/DDR0_DQ[58]

BC8

DDR1_DQ[27]/DDR0_DQ[59]

BC10

DDR1_DQ[28]/DDR0_DQ[60]

BB10

DDR1_DQ[29]/DDR0_DQ[61]

BC7

DDR1_DQ[30]/DDR0_DQ[62]

BB7

DDR1_DQ[31]/DDR0_DQ[63]

AA11

DDR1_DQ[32]/DDR1_DQ[16]

AA10

DDR1_DQ[33]/DDR1_DQ[17]

AC11

DDR1_DQ[34]/DDR1_DQ[18]

AC10

DDR1_DQ[35]/DDR1_DQ[19]

AA7

DDR1_DQ[36]/DDR1_DQ[20]

AA8

DDR1_DQ[37]/DDR1_DQ[21]

AC8

DDR1_DQ[38]/DDR1_DQ[22]

AC7

DDR1_DQ[39]/DDR1_DQ[23]

W8

DDR1_DQ[40]/DDR1_DQ[24]

W7

DDR1_DQ[41]/DDR1_DQ[25]

V10

DDR1_DQ[42]/DDR1_DQ[26]

V11

DDR1_DQ[43]/DDR1_DQ[27]

W11

DDR1_DQ[44]/DDR1_DQ[28]

W10

DDR1_DQ[45]/DDR1_DQ[29]

V7

DDR1_DQ[46]/DDR1_DQ[30]

V8

DDR1_DQ[47]/DDR1_DQ[31]

R11

DDR1_DQ[48]

P11

DDR1_DQ[49]

P7

DDR1_DQ[50]

R8

DDR1_DQ[51]

R10

DDR1_DQ[52]

P10

DDR1_DQ[53]

R7

DDR1_DQ[54]

P8

DDR1_DQ[55]

L11

DDR1_DQ[56]

M11

DDR1_DQ[57]

L7

DDR1_DQ[58]

M8

DDR1_DQ[59]

L10

DDR1_DQ[60]

M10

DDR1_DQ[61]

M7

DDR1_DQ[62]

L8

DDR1_DQ[63]

AW11

DDR1_ECC[0]

AY11

DDR1_ECC[1]

AY8

DDR1_ECC[2]

AW8

DDR1_ECC[3]

AY10

DDR1_ECC[4]

AW10

DDR1_ECC[5]

AY7

DDR1_ECC[6]

AW7

DDR1_ECC[7]

G1

DDR_RCOMP[0]

H1

DDR_RCOMP[1]

J2

DDR_RCOMP[2]

SKL-H_BGA1440

@

DDR CHANNEL B

UH1B

BT11

DDR_A_D0

DDR_A_D1

DDR_A_D[0..63][14]

DDR_A_MA[0..13][14]

DDR_A_DQS#[0..7][14]

DDR_A_DQS[0..7][14]

D

C

B

DDR_B_D[0..63][15]

DDR_B_MA[0..13][15]

DDR_B_DQS#[0..7][15]

DDR_B_DQS[0..7][15]

DDR_A_D2

DDR_A_D7

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D3

DDR_A_D9

DDR_A_D13

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D8

DDR_A_D14

DDR_A_D15

DDR_A_D20

DDR_A_D16

DDR_A_D23

DDR_A_D19

DDR_A_D21

DDR_A_D17

DDR_A_D22

DDR_A_D18

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D44

DDR_A_D45

DDR_A_D43

DDR_A_D47

DDR_A_D41

DDR_A_D40

DDR_A_D42

DDR_A_D46

DDR_A_D53

DDR_A_D51

DDR_A_D49

DDR_A_D55

DDR_A_D52

DDR_A_D54

DDR_A_D48

DDR_A_D50

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D63

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D59

DDR0_DQ[0]

BT6

DDR0_DQ[1]

BP3

DDR0_DQ[2]

BR3

DDR0_DQ[3]

BN5

DDR0_DQ[4]

BP6

DDR0_DQ[5]

BP2

DDR0_DQ[6]

BN3

DDR0_DQ[7]

BL4

DDR0_DQ[8]

BL5

DDR0_DQ[9]

BL2

DDR0_DQ[10]

BM1

DDR0_DQ[11]

BK4

DDR0_DQ[12]

BK5

DDR0_DQ[13]

BK1

DDR0_DQ[14]

BK2

DDR0_DQ[15]

BG4

DDR0_DQ[16]/DDR0_DQ[32]

BG5

DDR0_DQ[17]/DDR0_DQ[33]

BF4

DDR0_DQ[18]/DDR0_DQ[34]

BF5

DDR0_DQ[19]/DDR0_DQ[35]

BG2

DDR0_DQ[20]/DDR0_DQ[36]

BG1

DDR0_DQ[21]/DDR0_DQ[37]

BF1

DDR0_DQ[22]/DDR0_DQ[38]

BF2

DDR0_DQ[23]/DDR0_DQ[39]

BD2

DDR0_DQ[24]/DDR0_DQ[40]

BD1

DDR0_DQ[25]/DDR0_DQ[41]

BC4

DDR0_DQ[26]/DDR0_DQ[42]

BC5

DDR0_DQ[27]/DDR0_DQ[43]

BD5

DDR0_DQ[28]/DDR0_DQ[44]

BD4

DDR0_DQ[29]/DDR0_DQ[45]

BC1

DDR0_DQ[30]/DDR0_DQ[46]

BC2

DDR0_DQ[31]/DDR0_DQ[47]

AB1

DDR0_DQ[32]/DDR1_DQ[0]

AB2

DDR0_DQ[33]/DDR1_DQ[1]

AA4

DDR0_DQ[34]/DDR1_DQ[2]

AA5

DDR0_DQ[35]/DDR1_DQ[3]

AB5

DDR0_DQ[36]/DDR1_DQ[4]

AB4

DDR0_DQ[37]/DDR1_DQ[5]

AA2

DDR0_DQ[38]/DDR1_DQ[6]

AA1

DDR0_DQ[39]/DDR1_DQ[7]

V5

DDR0_DQ[40]/DDR1_DQ[8]

V2

DDR0_DQ[41]/DDR1_DQ[9]

U1

DDR0_DQ[42]/DDR1_DQ[10]

U2

DDR0_DQ[43]/DDR1_DQ[11]

V1

DDR0_DQ[44]/DDR1_DQ[12]

V4

DDR0_DQ[45]/DDR1_DQ[13]

U5

DDR0_DQ[46]/DDR1_DQ[14]

U4

DDR0_DQ[47]/DDR1_DQ[15]

R2

DDR0_DQ[48]/DDR1_DQ[32]

P5

DDR0_DQ[49]/DDR1_DQ[33]

R4

DDR0_DQ[50]/DDR1_DQ[34]

P4

DDR0_DQ[51]/DDR1_DQ[35]

R5

DDR0_DQ[52]/DDR1_DQ[36]

P2

DDR0_DQ[53]/DDR1_DQ[37]

R1

DDR0_DQ[54]/DDR1_DQ[38]

P1

DDR0_DQ[55]/DDR1_DQ[39]

M4

DDR0_DQ[56]/DDR1_DQ[40]

M1

DDR0_DQ[57]/DDR1_DQ[41]

L4

DDR0_DQ[58]/DDR1_DQ[42]

L2

DDR0_DQ[59]/DDR1_DQ[43]

M5

DDR0_DQ[60]/DDR1_DQ[44]

M2

DDR0_DQ[61]/DDR1_DQ[45]

L5

DDR0_DQ[62]/DDR1_DQ[46]

L1

DDR0_DQ[63]/DDR1_DQ[47]

BA2

DDR0_ECC[0]

BA1

DDR0_ECC[1]

AY4

DDR0_ECC[2]

AY5

DDR0_ECC[3]

BA5

DDR0_ECC[4]

BA4

DDR0_ECC[5]

AY1

DDR0_ECC[6]

AY2

DDR0_ECC[7]

DDR CHANNEL A

SKL-H_BGA1440

@

UH1A

BR6

REV = 1

?

SKYLAKE_HALO

BGA1440

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSP[5]/DDR1_DQSP[3]

2 OF 14

DDR1_CKP[0]

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[1]

DDR1_CLKP[2]

DDR1_CLKN[2]

DDR1_CLKP[3]

DDR1_CLKN[3]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_CS#[2]

DDR1_CS#[3]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_ODT[2]

DDR1_ODT[3]

DDR1_MA[3]

DDR1_MA[4]

DDR1_PAR

DDR1_ALERT#

DDR1_DQSN[6]

DDR1_DQSN[7]

DDR1_DQSP[6]

DDR1_DQSP[7]

DDR1_DQSP[8]

DDR1_DQSN[8]

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

?

AM9

AN9

AM8

AM7

AM11

AM10

AJ10

AJ11

AT8

AT10

AT7

AT11

AF11

AE7

AF10

AE10

AF7

AE8

AE9

AE11

AH10

AH11

AF8

AH8

AH9

AR9

AJ9

AK6

AK5

AL5

AL6

AM6

AN7

AN10

AN8

AR11

AH7

AN11

AR10

AF9

AR7

AT9

AJ7

AR8

BP9

BL9

BG9

BC9

AC9

W9

R9

M9

BR9

BJ9

BF9

BB9

AA9

V9

P9

L9

AW9

AY9

BN13

BP13

BR13

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

M_CLK_DDR2 [15]

M_CLK_DDR#2 [15]

M_CLK_DDR#3 [15]

M_CLK_DDR3 [15]

DDR_CKE2_DIMMB [15]

DDR_CKE3_DIMMB [15]

DDR_CS2_DIMMB# [15]

DDR_CS3_DIMMB# [15]

M_ODT2 [15]

M_ODT3 [15]

DDR_B_RAS# [15]

DDR_B_WE# [15]

DDR_B_CAS# [15]

DDR_B_BS0 [15]

DDR_B_BS1 [15]

DDR_B_BG0 [15]

DDR_B_BG1 [15]

DDR_B_ACT# [15]

DDR_B_PAR [15]

DDR_B_ALERT# [15]

+V_DDR_REFA_R

+V_DDR_REFB_R

D

C

B

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

3

2011/08/25 2012/07/25

2011/08/25 2012/07/25

2011/08/25 2012/07/25

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

Title

Title

PROCESSOR(3/7) DDRIII

PROCESSOR(3/7) DDRIII

PROCESSOR(3/7) DDRIII

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

1

of

8 70Tuesday, November 08, 2016

of

8 70Tuesday, November 08, 2016

of

8 70Tuesday, November 08, 2016

0.1(X00)

0.1(X00)

0.1(X00)

A

5

CFG Straps for Processor

Stall reset sequence after CPU PLL lock until de-asserted

CFG0

D

PCI EXPRESS STATIC LANE REVERSAL FOR ALL PEG PORTS

CFG2

Display Port Presence Strap

C

CFG4

PCIE Port Bifurcation Straps

CFG[6:5]

B

PEG DEFER TRAINING

CFG7

A

1 = (Default) Normal Operation; No stall.

*

0 = Stall.

1

CFG0

1: Normal Operation; Lane # definition matches

socket pin map definition

0:Lane Reversed

*

CFG2

1 : Disabled; No Physical Display Port

attached to Embedded Display Port

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

*

CFG4

RH185 1K_0402_5%

11: (Default) x16 - Device 1 functions 1 and 2 disabled

*

10: x8, x8 - Device 1 function 1 enabled ; function 2

disabled

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

CFG5

RH186 1K_0402_5%

CFG6

RH187 1K_0402_5%

1: (Default) PEG Train immediately following xxRESETB

de assertion

*

2

@

RH183 1K_0402_5%

1

2

RH184 1K_0402_5%

Enable because PS175(DP to HDMI Converter)

1

2

1

2

@

1

2

@

0: PEG Wait for BIOS for training

1

CFG7

2

@

RH188 1K_0402_5%

4

+VCCST

RH163 1K_0402_5%

RH156 51_0402_5%

RH164 1K_0402_5%

RH151 100_0402_5%

RH152 56.2_0402_1%

RH144 49.9_0402_1%

+VCCSTG

1

RH165 1K_0402_5%

3

1

2

H_THERMTRIP#_R

1

2

XDP_PREQ#

@

1

2

H_VCCST_PWRGD

1

2

VR_SVID_DATA

1

2

VR_SVID_ALERT#

1

2

H_CATERR#

@

1

RH153 220_0402_5%

1

RH158 499_0402_1%

1

RH154 60.4_0402_1%

1

RH155 20_0402_5%

1

RH190 0_0402_5%@

1

RH89 0_0402_5%@

DDR_VTT_PG_CTRL

PCH_TRIGGER

CPU_TRIGGER

2

SM_PG_CTRL[57]

H_PROCHOT#

Pilot_05

+1.2V_DDR

+3VS

1

@

CH197

0.1U_0402_10V7K

2

1

RH93

220K_0402_5%

2

VR_SVID_ALERT#[63]

VR_SVID_CLK[63]

VR_SVID_DATA[63]

H_PROCHOT#[48,54,55,63]

H_VCCST_PWRGD[18]

H_CPUPWRGD[18]

PLTRST_CPU#[16]

H_PM_SYNC_R[16]

H_PM_DOWN[16]

PECI_EC[16,48]

H_THERMTRIP#_R[16]

PROC_DETECT#[16]

VR_SVID_ALERT#

VR_SVID_DATA

H_PROCHOT#

H_VCCST_PWRGD

H_PM_DOWN

UC1

5

VCC

4

Y

GND

74AUP1G07GW_TSSOP5

PCH_TRIGGER[22]

CPU_TRIGGER[22]

1

NC

2

A

3

PCH_CPU_BCLK_P[17]

PCH_CPU_BCLK_N[17]

PCH_CPU_PCIBCLK_P[17]

PCH_CPU_PCIBCLK_N[17]

CPU_24MHZ_P[17]

CPU_24MHZ_N[17]

2

VR_SVID_ALERT#_R

2

H_PROCHOT#_R

DDR_VTT_PG_CTRL

2

2

2

2

RH167 30_0402_5%

RH192 30_0402_5%

1

1

VCCST_PWRGD_CPU

PLTRST_CPU#

H_PM_SYNC_R

H_PM_DOWN_R

PECI_EC_R

H_THERMTRIP#_R

H_CATERR#

2

2

PCH_TRIGGER_R

CPU_TRIGGER_R

BH31

BH32

BH29

BR30

BT13

BT31

BP35

BM34

BP31

BT34

BR33

BM30

B31

A32

D35

C36

E31

D31

H13

J31

BN1

UH1E

BCLKP

BCLKN

PCI_BCLKP

PCI_BCLKN

CLK24P

CLK24N

VIDALERT#

VIDSCK

VIDSOUT

PROCHOT#

DDR_VTT_CNTL

VCCST_PWRGD

PROCPWRGD

RESET#

PM_SYNC

PM_DOWN

PECI

THERMTRIP#

SKTOCC#

PROC_SELECT#

CATERR#

SKL-H_BGA1440

@

D1

E1

E3

E2

BR1

BT2

BN35

J24

H24

BN33

BL34

N29

R14

AE29

AA14

A36

A37

H23

J23

F30

E30

B30

C30

G3

J3

BR35

BR31

BH30

SKYLAKE_HALO

BGA1440

REV = 1

UH1K

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

PROC_TRIGIN

PROC_TRIGOUT

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

SKL-H_BGA1440

@

2

?

5 OF 14

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST#

PROC_PREQ#

PROC_PRDY#

CFG_RCOMP

SKYLAKE_HALO

BGA1440

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[17]

CFG[16]

CFG[19]

CFG[18]

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

?

11 OF 14

1

BN25

CFG0

BN27

BN26

CFG2

BN28

BR20

CFG4

BM20

CFG5

BT20

CFG6

BP20

CFG7

BR23

BR22

BT23

BT22

BM19

BR19

BP19

BT19

BN23

BP23

BP22

BN22

BR27

BT27

BM31

BT30

BT28

CPU_XDP_TDO

BL32

CPU_XDP_TDI

BP28

CPU_XDP_TMS

BR28

CPU_XDP_TCK

BP30

CPU_XDP_TRST#

BL30

XDP_PREQ#

BP27

XDP_PRDY#

BT25

?

CFG_RCOMP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

CPU_XDP_TDO [6]

CPU_XDP_TDI [6]

CPU_XDP_TMS [6]

CPU_XDP_TCK [6,18]

CPU_XDP_TRST# [6,22]

XDP_PREQ# [22]

XDP_PRDY# [22]

1

RH59

49.9_0402_1%

2

BM33

BL33

BJ14

BJ13

BK28

RSVD

BJ28

RSVD

BJ18

VSS

BJ16

BK16

BK24

BJ24

BK21

RSVD

BJ21

RSVD

BT17

RSVD

BR17

RSVD

BK18

VSS

BJ34

BJ33

G13

RSVD

AJ8

RSVD

BL31

RSVD

B2

NCTF

B38

NCTF

BP1

NCTF

BR2

NCTF

C1

NCTF

C38

NCTF

?REV = 1

D

C

B

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF C OMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSF ERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITH ER THIS SHEET NOR THE IN FORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

3

2011/08/25 2012/07/25

2011/08/25 2012/07/25

2011/08/25 2012/07/25

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Title

Title

Title

PROCESSOR(4/7) RSVD,CFG

PROCESSOR(4/7) RSVD,CFG

PROCESSOR(4/7) RSVD,CFG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

1

of

9 70Tuesday, November 08, 2016

of

9 70Tuesday, November 08, 2016

of

9 70Tuesday, November 08, 2016

0.1(X00)

0.1(X00)

0.1(X00)

5

4

3

2

1

V32

V33

V34

V35

V36

V37

V38

W13

W14

W29

W30

W31

W32

W35

W36

W37

W38

Y29

Y30

Y31

Y32

Y33

Y34

Y35

Y36

L14

P29

P30

P31

P32

P33

P34

P35

P36

R13

R31

R32

R33

R34

R35

R36

R37

R38

T29

T30

T31

T32

T35

T36

T37

T38

U29

U30

U31

U32

U33

U34

U35

U36

V13

V14

V31

P14

AG37

AG38

+VCC_CORE

+VCC_CORE

1

2

1

2

RH197

100_0402_1%

1

RH198 0_0402_5%@

1

RH28 0_0402_5%@

RH29

100_0402_1%

2

2

Pilot_05

VCC_SENSE [63]

VSS_SENSE [63]

1

RH166 49.9_0402_1%@

RH57 49.9_0402_1%@

1

1

RH58 49.9_0402_1%@

UH1J

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCCOPC_SENSE

VSSOPC_SENSE

RSVD

RSVD

VCCEOPIO

VCCEOPIO

VCCEOPIO

RSVD

RSVD

RSVD

VCCEOPIO_SENSE

VSSEOPIO_SENSE

RSVD

RSVD

VCC_OPC_1P8

VCC_OPC_1P8

RSVD

RSVD

ZVM#

MSM#

ZVM2#

MSM2#

OPC_RCOMP

OPCE_RCOMP

OPCE_RCOMP2

SKL-H_BGA1440

REV = 1

@

BGA1440

10 OF 14

?

BJ17

BJ19

BJ20

BK17

BK19

BK20

BL16

BL17

BL18

BL19

BL20

BL21

BM17

BN17

BJ23

BJ26

BJ27

BK23

BK26

BK27

BL23

BL24

BL25

BL26

BL27

BL28

BM24

BL15

BM16

BL22

BM22

BP15

BR15

BT15

BP16

BR16

BT16

BN15

BM15

BP17

BN16

BM14

BL14

BJ35

BJ36

AT13

AW13

AU13

AY13

2

2

2

BT29

BR25

BP25

D

C

B

?

SKYLAKE_HALO

+VCC_CORE

D

UH1G

AA13

VCC

AA31

VCC

AA32

VCC

AA33

VCC

AA34

VCC

AA35

VCC

AA36

VCC

AA37

VCC

AA38

VCC

AB29

VCC

AB30

VCC

AB31

VCC

AB32

VCC

AB35

VCC

AB36

VCC

AB37

VCC

AB38

VCC

AC13

VCC

AC14

VCC

AC29

VCC

AC30

VCC

AC31

VCC

AC32

VCC

AC33

VCC

AC34

VCC

AC35

VCC

AC36

VCC

AD13

VCC

C

B

AD14

AD31

AD32

AD33

AD34

AD35

AD36

AD37

AD38

AE13

AE14

AE30

AE31

AE32

AE35

AE36

AE37

AE38

AF35

AF36

AF37

AF38

K13

K14

L13

N13

N14

N30

N31

N32

N35

N36

N37

N38

P13

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

SKL-H_BGA1440

@

?

SKYLAKE_HALO

BGA1440

REV = 1 ?

7 OF 14

VCC_SENSE

VSS_SENSE

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/08/25 2012/07/25

2011/08/25 2012/07/25

2011/08/25 2012/07/25

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

PROCESSOR(5/7) PWR,BYPASS

PROCESSOR(5/7) PWR,BYPASS

PROCESSOR(5/7) PWR,BYPASS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

1

of

10 70Tuesday, November 08, 2016

of

10 70Tuesday, November 08, 2016

of

10 70Tuesday, November 08, 2016

0.1(X00)

0.1(X00)

0.1(X00)

A

5

4

3

2

1

+VCCIO

10U_0603_6.3V6M

D

+VCCSA

?

SKYLAKE_HALO

UH1I

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

SKL-H_BGA1440

@

BGA1440

9 OF 14

VCCPLL_OC

VCCPLL_OC

VCCSA_SENSE

VSSSA_SENSE

VCCIO_SENSE

VSSIO_SENSE

J30

K29

K30

K31

K32

K33

K34

K35

L31

L32

L35

L36

L37

L38

M29

M30

M31

M32

M33

M34

AG12

M35

M36

G15

G17

G19

G21

H15

H16

H17

H19

H20

H21

H26

H27

J15

J16

J17

J19

J20

J21

J26

J27

C

B B

+VCCIO

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQC

VCCST

VCCSTG

VCCSTG

VCCPLL

VCCPLL

+1.2V_DDR

AA6

AE12

AF5

AF6

AG5

AG9

AJ12

AL11

AP6

AP7

AR12

AR6

AT12

AW6

AY6

J5

J6

K12

K6

L12

L6

R6

T6

W6

Y12

BH13

G11

H30

H29

G30

H28

J28

M38

M37

H14

J14

?REV = 1

+1.2V_DDR

Pilot_05

1

RH34

@

0_0402_5%

2

+1.2V_VCCPLL_OC

+VCCST

RH201 100_0402_1%

RH202 0_0402_5%@

RH31 0_0402_5%@

RH41 100_0402_1%

RH515 100_0402_1%

RH514 0_0402_5%@

RH513 0_0402_5%@

RH516 100_0402_1%

1

RH107 0_0402_5%@

+VCCSTG

+VCCST

1

1

1

1

1

1

1

1

+1.2V_DDR

2

2

2

2

2

2

2

2

2

+VCCSA

VCCSA_SENSE [63]

VSSSA_SENSE [63]

+VCCIO

VCCIO_SENSE [59]

VSSIO_SENSE [59]

Pilot_05

10U_0603_6.3V6M

CH102

1

2

10U_0603_6.3V6M

CH103

CH104

1

1

2

2

+VCCSTG

1

2

1U_0402_6.3V6K

CH106

+VCCST

+1.2V_DDR

1

2

1U_0402_6.3V6K

CH110

1

2

22U_0603_6.3V6M

1

CH129

2

+1.2V_DDR

1U_0402_6.3V6K

CH204

1

2

22U_0603_6.3V6M

22U_0603_6.3V6M

22U_0603_6.3V6M

1

1

CH130

CH131

CH132

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

CH124

CH121

CH118

1

1

1

2

2

2

+VCCSA

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

CH111

1

1

2

2

+VCCSA

1U_0402_6.3V6K

CH133

1

1

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

CH120

1

2

10U_0603_6.3V6M

CH119

CH122

1

2

1

1

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

CH113

CH112

1U_0402_6.3V6K

10U_0603_6.3V6M

CH114

1

1

1

2

2

2

1U_0402_6.3V6K

CH135

CH134

1

2

10U_0603_6.3V6M

10U_0603_6.3V6M

CH123

CH126

CH125

1

1

1

2

2

2

CH115

10U_0603_6.3V6M

1

2

+VCCSA

CH127

10U_0603_6.3V6M

10U_0603_6.3V6M

CH117

CH116

1

2

47U_0603_6.3V6M

CH136

1

2

10U_0603_6.3V6M

CH128

1

2

D

C

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/08/25 2012/07/25

2011/08/25 2012/07/25

2011/08/25 2012/07/25

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Title

Title

Title

PROCESSOR(6/7) PWR

PROCESSOR(6/7) PWR

PROCESSOR(6/7) PWR

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

1

of

11 70Tuesday, November 08, 2016

of

11 70Tuesday, November 08, 2016

of

11 70Tuesday, November 08, 2016

0.1(X00)

0.1(X00)

0.1(X00)

5

4

3

2

1

+VCCGT

?

SKYLAKE_HALO

UH1H

D

C

B B

BG34

BG35

BG36

BH33

BH34

BH35

BH36

BH37

BH38

BJ37

BJ38

BL36

BL37

BM36

BM37

BN36

BN37

BN38

BP37

BP38

BR37

BT37

BE38

BF13

BF14

BF29

BF30

BF31

BF32

BF35

BF36

BF37

BF38

BG29

BG30

BG31

BG32

BG33

BC36

BC37

BC38

BD13

BD14

BD29

BD30

BD31

BD32

BD33

BD34

BD35

BD36

BE31

BE32

BE37

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

SKL-H_BGA1440

@

BGA1440

REV = 1

8 OF 14

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

+VCCGT

AV29

AV30

AV31

AV32

AV33

AV34

AV35

AV36

AW14

AW31

AW32

AW33

AW34

AW35

AW36

AW37

AW38

AY29

AY30

AY31

AY32

AY35

AY36

AY37

AY38

BA13

BA14

BA29

BA30

BA31

BA32

BA33

BA34

BA35

BA36

BB13

BB14

BB31

BB32

BB33

BB34

BB35

BB36

BB37

BB38

BC29

BC30

BC31

BC32

BC35

BE33

BE34

BE35

BE36

?

+VCCGT

AJ29

AJ30

AJ31

AJ32

AJ33

AJ34

AJ35

AJ36

AK31

AK32

AK33

AK34

AK35

AK36

AK37

AK38

AL13

AL29

AL30

AL31

AL32

AL35

AL36

AL37

AL38

AM13

AM14

AM29

AM30

AM31

AM32

AM33

AM34

AM35

AM36

AN13

AN14

AN31

AN32

AN33

AN34

AN35

AN36

AN37

AN38

AP13

AP14

AP29

AP30

AP31

AP32

AP35

AP36

AP37

AP38

AR29

AR30

AR31

AR32

AR33

AR34

AR35

AR36

AT14

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AU14

AU29

AU30

AU31

AU32

AU35

AU36

AU37

AU38

UH1N

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT