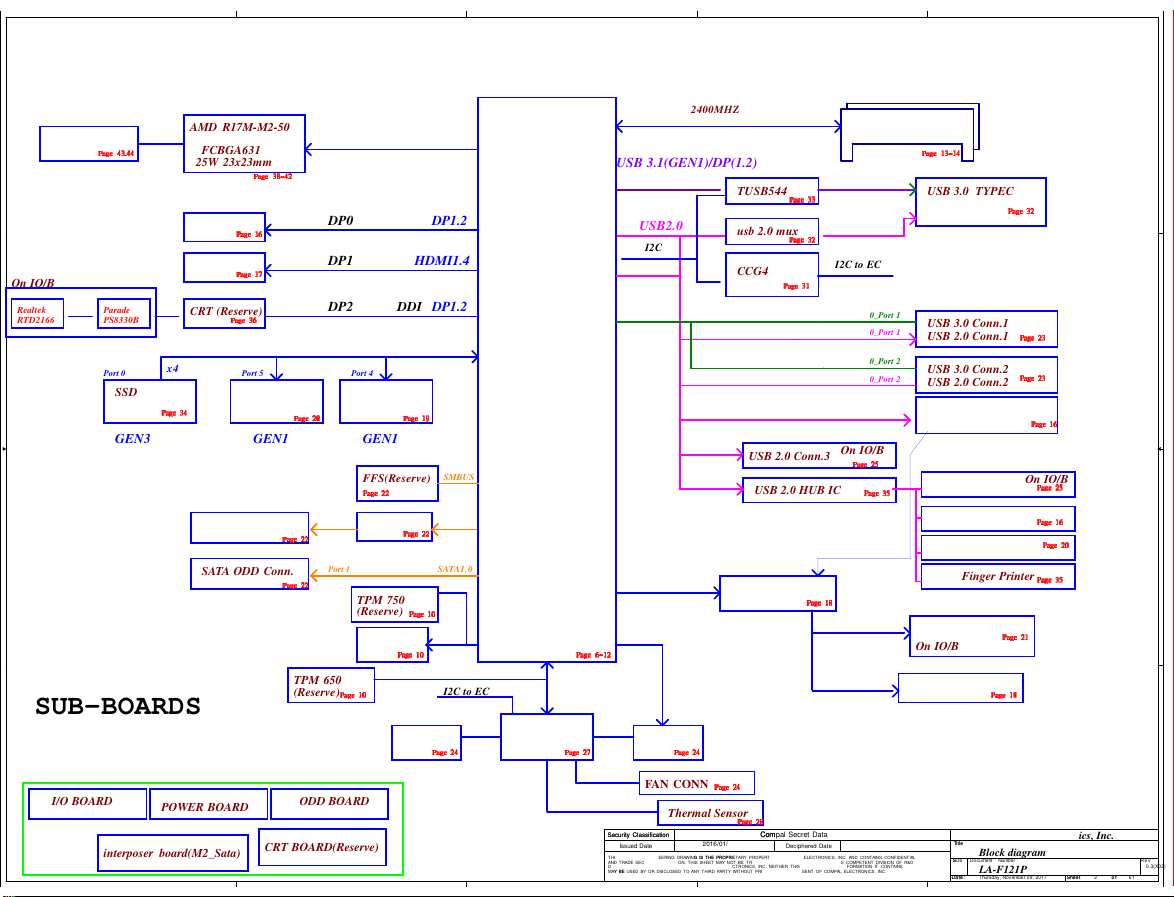

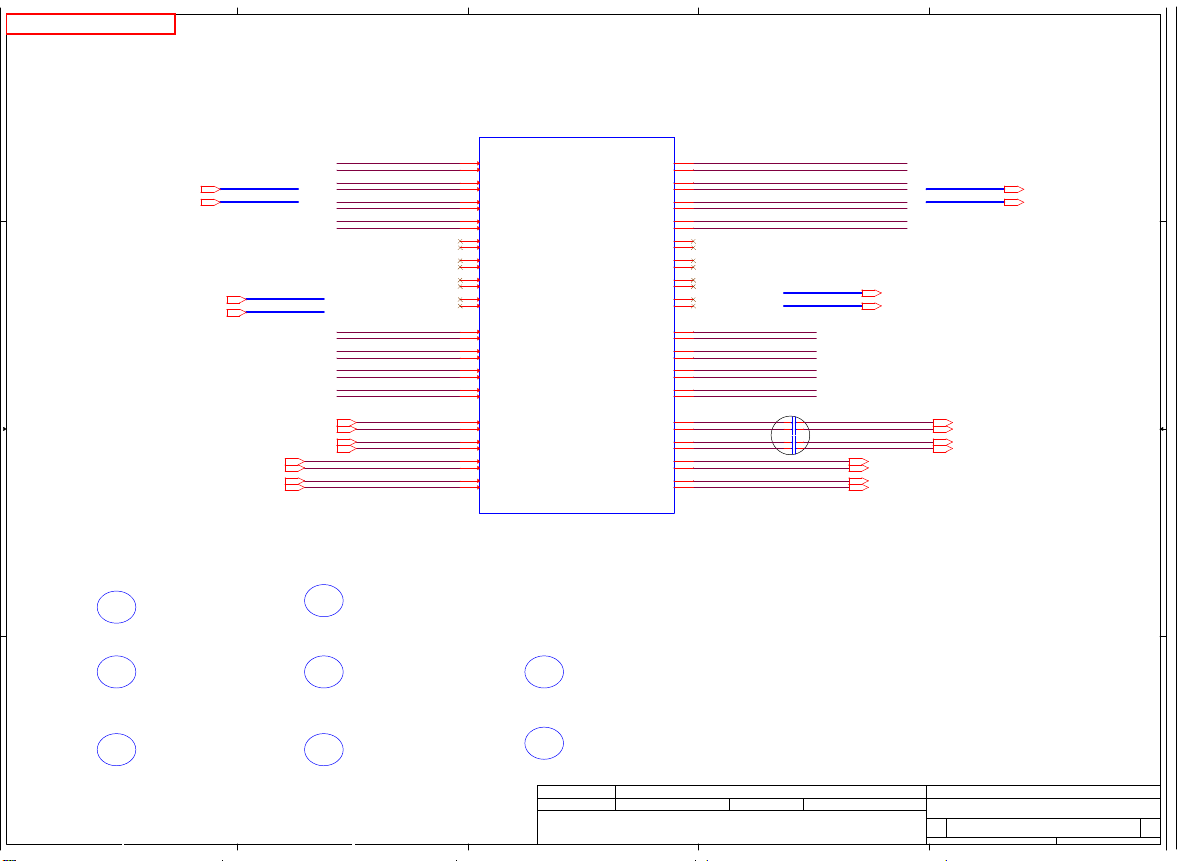

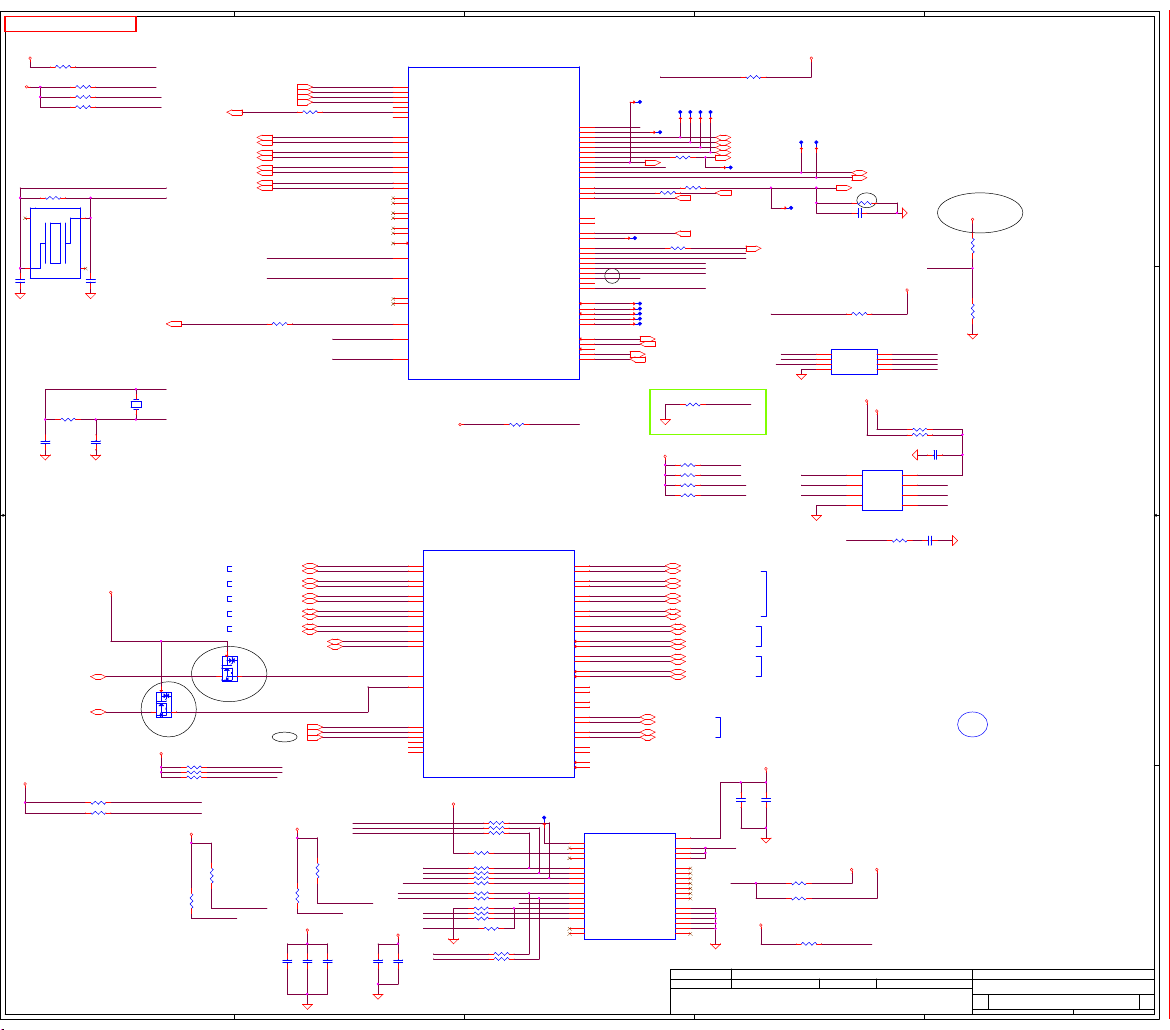

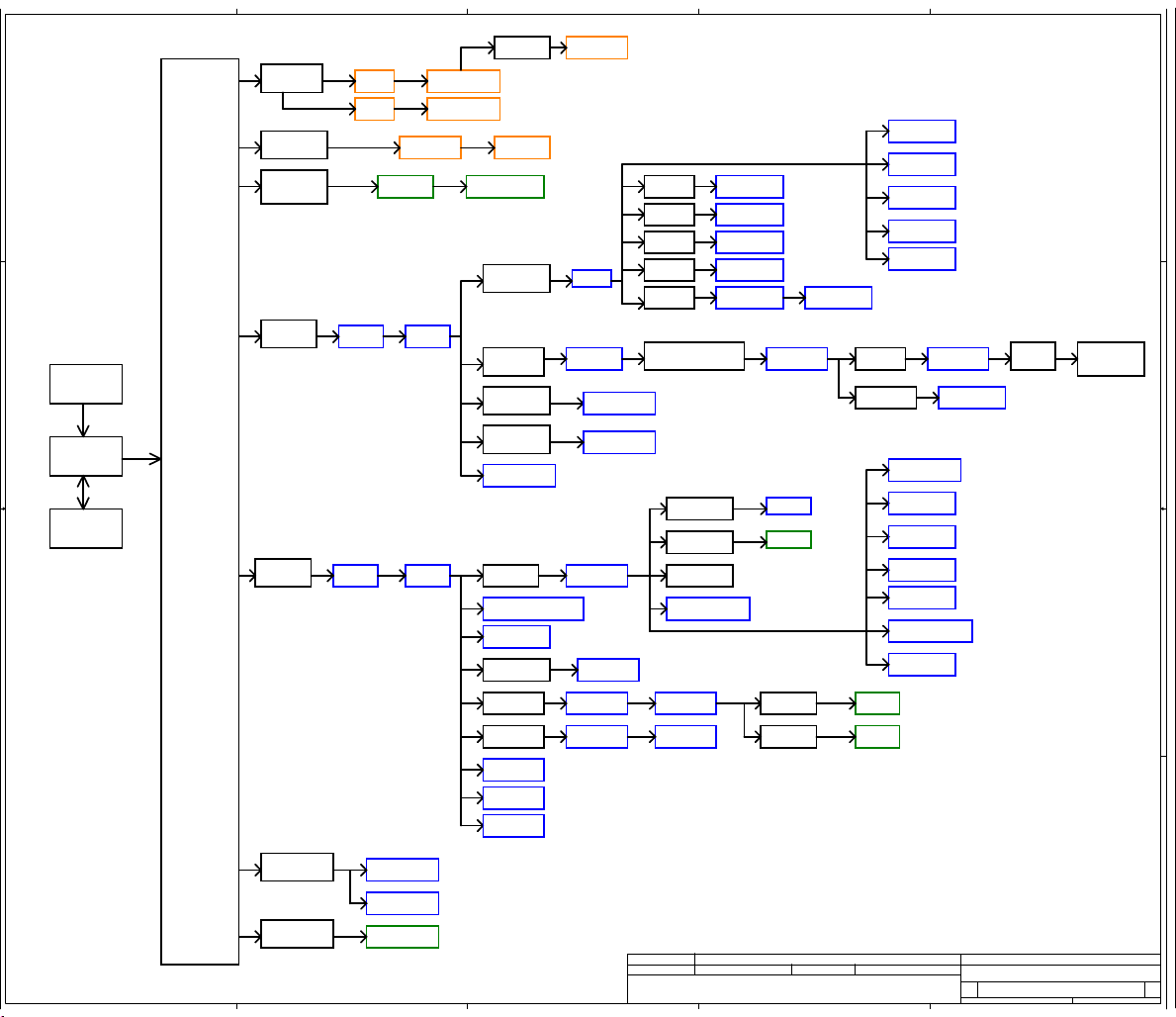

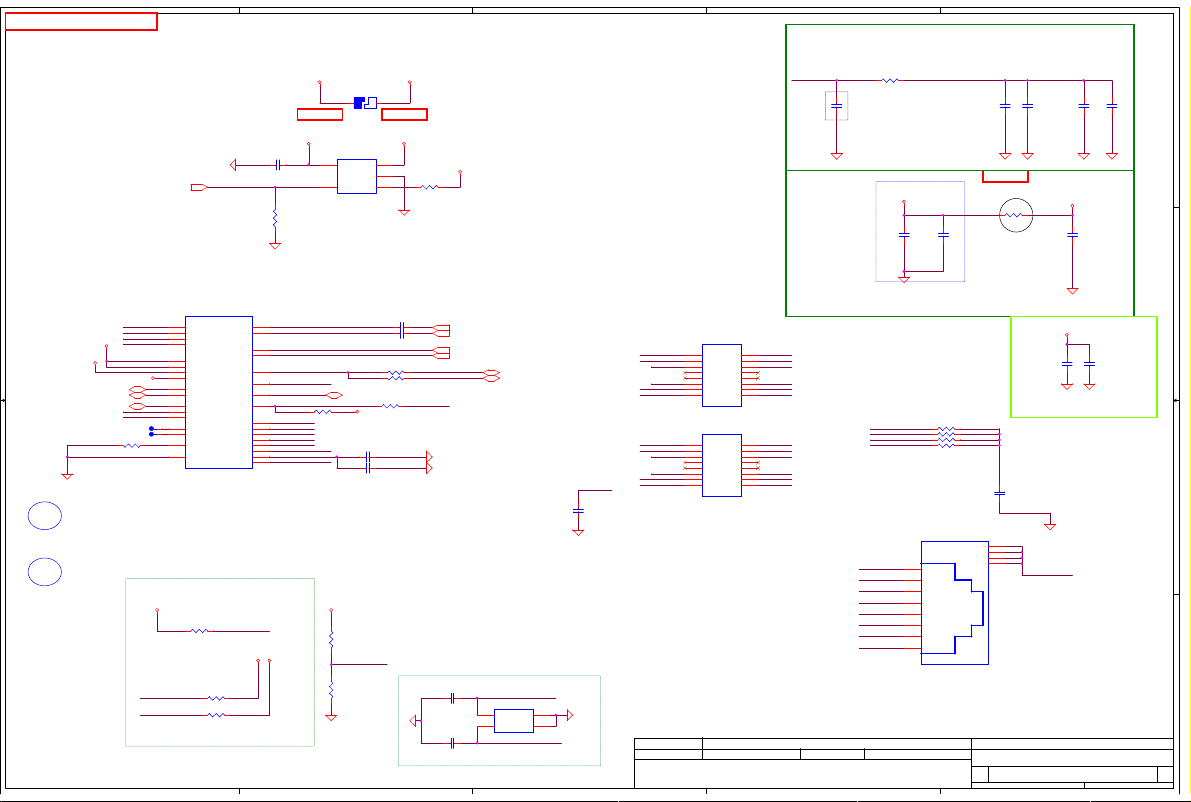

Dell Inspiron 15 5575 Schematics

5

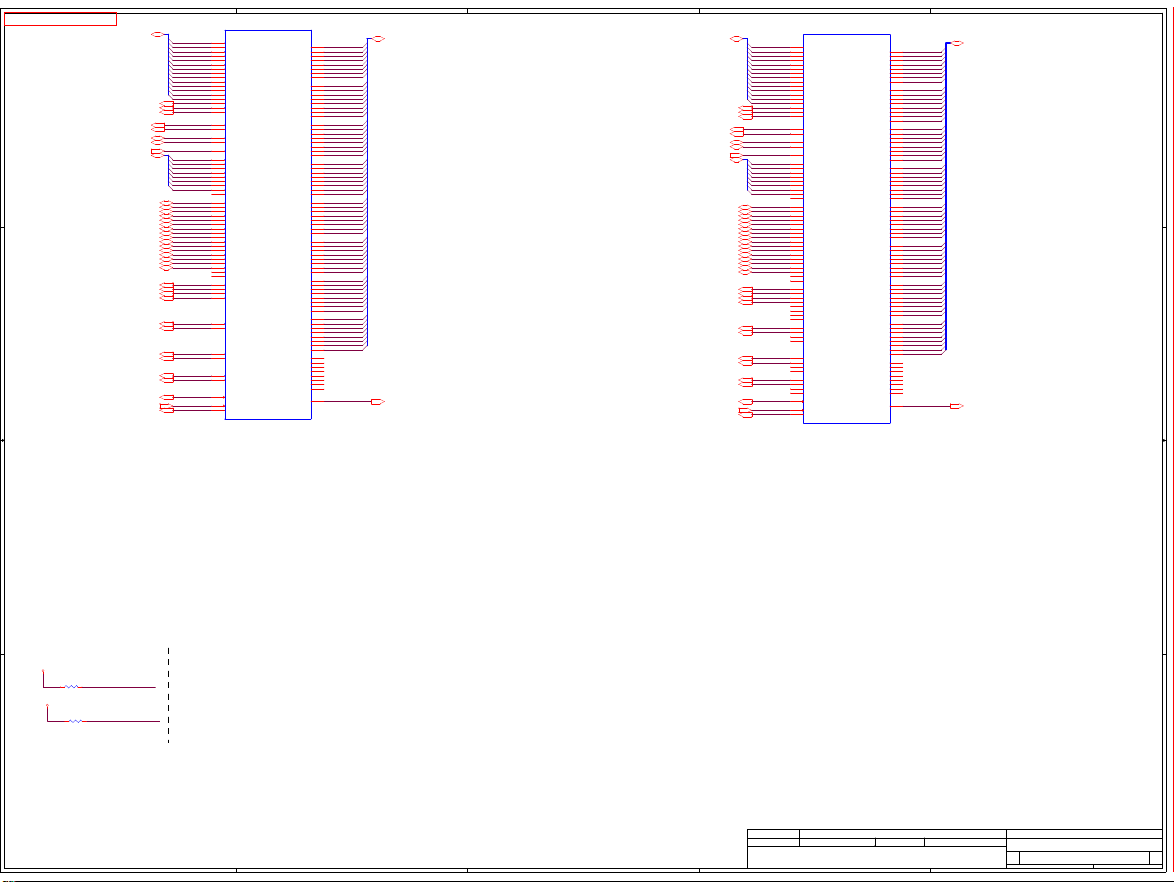

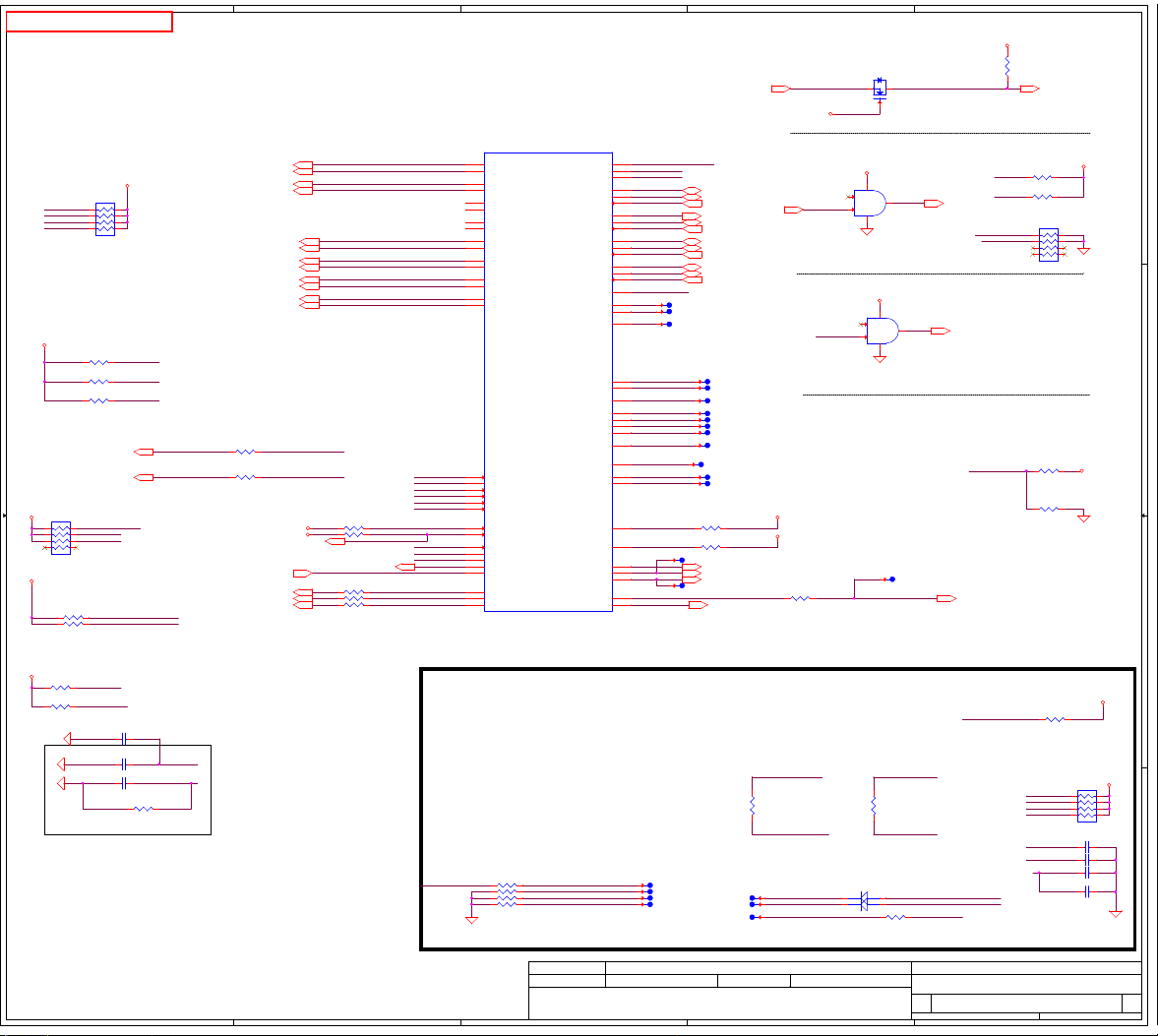

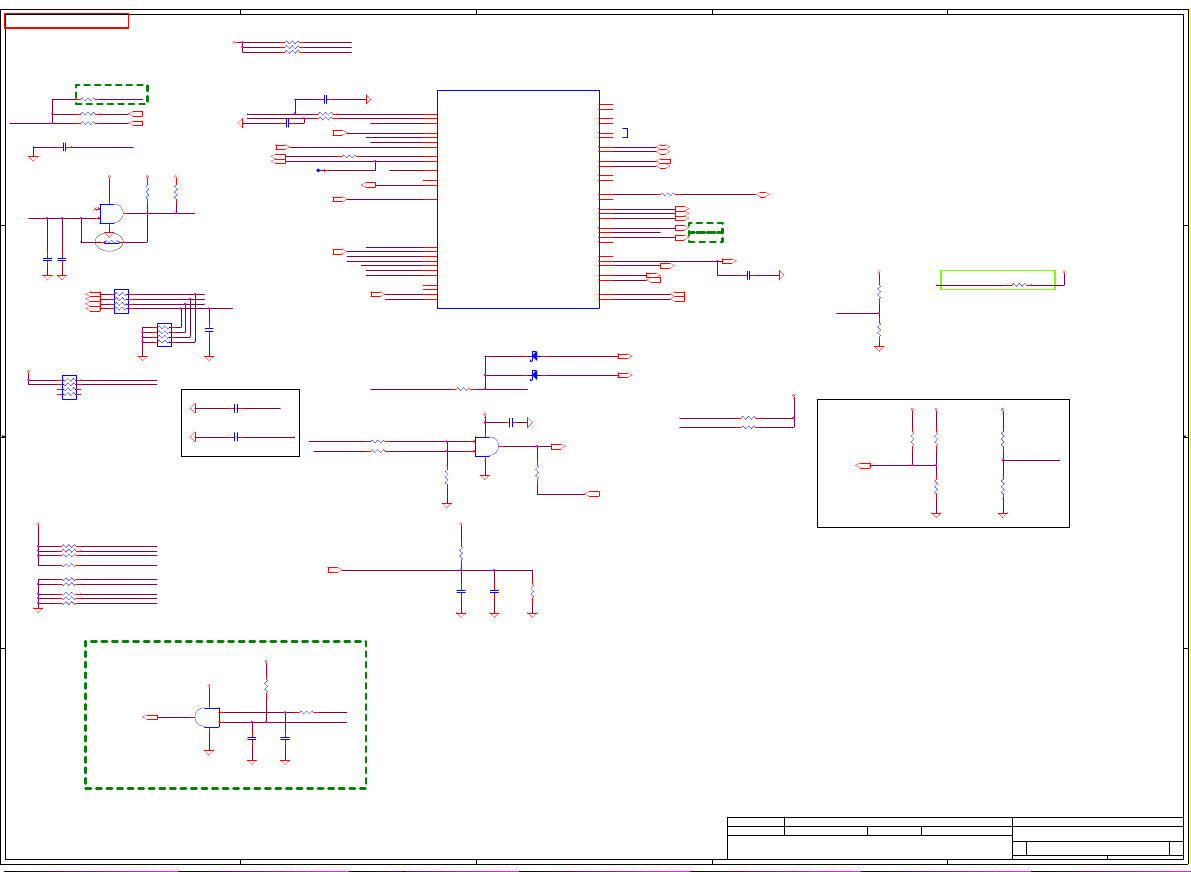

PROJECT NAME : CAL51/CLA61/CAL71

P

CB NO :

4

3

2

1

D D

Dell / Compal Confidential

Schematic Document

AMD Raven

AMD R17M-M2-50 (23 X 23mm)+GDDR5 x4

C C

B B

2017-11-09 Rev: 1.00 (A00)

@ : Un-pop Component

R5_PC@/R7_PC@/R3_PC/R5_PR@/R7_PR@/R5_PR_R3@/R7_PR_R3@:APU PN

45@: HDMI LOGO

PCB@/: MB part number

4G_S@/4G_M@/4G_H@/2G_H@/2G_M@/2G_S:

VRAM Strap Pin:

Vram 2G:S2G_R3@ / H2G_R3@ /M2G_R3@

Vram 4G:S4G_R3@ / H4G_R3@ /M4G_R3@

DIS@: GPU only

M50_R3@:GPU R3 PN

UMA@/:UMA only

TI@/PARADE@/NRDSA@ : SATA

3234@ :Audio

EMI@/ESD@/RF@ : EMI, ESD ,RF Component

@EMI@/@ESD@/@RF@ : EMI, ESD,RF unpop

KBBL@:for KB backlight use

PTP@/NPTP@/TP_WAKE@:Touch pad

TYPEC@/NOTYPEC@:TYPEC

@EMI@/Tyepc@ESD@: EMI/ESD typec component

A A

Typec

CRT@:D-sub TPM@:TPM FFS@:free fall sensor

HDT@ /Debug use

MODS@:moderd standby

curity Classification Compal Secret Data

curity Classification Compal Secret Data

curity Classification Compal Secret Data

Se

Se

Se

ed Date

ed Date

ed Date

Issu

Issu

Issu

IS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

IS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

IS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

TH

TH

TH

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECT RONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECT RONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECT RONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY T HIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY T HIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY T HIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

16/01/07 2017/01/07

16/01/07 2017/01/07

16/01/07 2017/01/07

20

20

20

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

Ti

Ti

Size Document Number Re v

Size Document Number Re v

Size Document Number Rev

Date : Sheet

Date : Sheet

Date: Sheet of

tle

tle

Cover Page

Cover Page

Cover Page

LA

LA

LA

mpal Electronics, Inc.

mpal Electronics, Inc.

mpal Electronics, Inc.

Co

Co

Co

-F121P

-F121P

-F121P

1

1 61Thursday, November 09, 2 017

1 61Thursday, November 09, 2 017

1 61Thursday, November 09, 2 017

of

of

3(X02)

3(X02)

3(X02)

0.

0.

0.

5

D D

AM 256M*16

VR

GDDR5 *4

Page 43,44

Page 43,44

Page 43,44Page 43,44

n IO/B

O

Realtek

RTD2166

C C

B B

UB-BOARDS

S

A A

I/O BOARD

4bit

6

MD R17M-M2-50

A

FCBGA631

25W 23x23mm

DP Conn.

e

H

arade

P

PS8330B

ort 0

P

SD

S

EN3 GEN1 GEN1

G

x

age 34

Page 34

P

Page 34Page 34

C

4

age 38~42

Page 38~42

P

Page 38~42Page 38~42

Page 16

Page 16

Page 16Page 16

DMI Conn.

Page 17

Page 17

Page 17Page 17

RT (Reserve)

age 36

Page 36

P

Page 36Page 36

NGFF 2230

iFi/BT4.0

W

ATA HDD Conn.

S

ATA ODD Conn.

S

x

Page 22

Page 22

Page 22Page 22

age 22

Page 22

P

Page 22Page 22

POWER BOARD

RT BOARD(Reserve)

nterposer board(M2_Sata)

i

5

C

4

EG 3.0 x4

P

DP0

P1

D

P2

D

1

Ethernet

R

(

Page 20

Page 20 Page 19

Page 20Page 20

ort 0

P

ort 1

P

PM 650

T

Reserve)

(

Page 10

Page 10

Page 10Page 10

DD BOARD

O

DP

e

DI

D

DI

D

CI-E

P

1

x

ort 4Port 5

P

TL8106E/RTL8111H(reserve)

10/100) default/1000

Page 19

Page 19Page 19

(Reserve)

FFS

age 22

Page 22

P

Page 22Page 22

ATA Rediver

S

Page 22

Page 22

Page 22Page 22

TPM 750

Reserve)

(

Page 10

P

Page 10Page 10

PI ROM

S

28Mb

1

Page 10

Page 10

Page 10Page 10

nt.KBD

I

ith KBBL

w

4

3

emory Bus

M

SB 3.1(GEN1)/DP(1.2)

U

P1.2

D

MD

HDMI1.4

A

Ravenl

Proces sor

BGA 1140

P1.2

D

MBUS

S

ATA3.0

S

ATA1.0

S

age 10

PI

S

2C to EC

I

E

Page 24 Page 24

Page 24Page 24

KB9022QD

LPC Bus

3MHz

3

NE KBC

Page 27

Page 27Page 24

Page 27Page 27

Page 6~12

Page 6~12

Page 6~12Page 6~12

PS/2

U

SB 3.0

U

SB2.0

U

2C

I

SB2.0

D Audio

H

ouch Pad

T

FAN CONN

ecurity Classification

ecurity Classification

ecurity Classification

S

S

S

ssued Date

ssued Date

ssued Date

I

I

I

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

T

T

T

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE T RANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED T O ANY T HIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED T O ANY T HIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED T O ANY T HIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECT RONICS, INC.

3

upport two CHs

400M HZ

s

2

USB544

T

age 33

Page 33

P

Page 33Page 33

sb 2.0 mux

u

age 32

Page 32

P

Page 32Page 32

CG4

C

Page 31

Page 31

Page 31Page 31

1_Port 0

USB 2.0 Conn.3

_Port 1

1

2C

I

Page 24

Page 24Page 24

hermal Sensor

T

2

2

2

SB 2.0 HUB IC

U

Audio Codec

LC3234(def ault)

A

age 24

Page 24

P

Page 24Page 24

age 28

Page 28

P

Page 28Page 28

ompal Secret Data

ompal Secret Data

ompal Secret Data

C

C

C

016/01/07 2017/01/07

016/01/07 2017/01/07

016/01/07 2017/01/07

eciphered Date

eciphered Date

eciphered Date

D

D

D

2

Digital Mic.

Page 18

Page 18

Page 18Page 18

2

DR4-DIMM X2

D

I2C to EC

0

On IO/B

age 25

Page 25

P

Page 25Page 25

Page 35

P

Page 35Page 35

.2V DDR4

1

_Port 0

0

_Port 0

0

_Port 1

0

0_Port 1

_Port 2

0

0_Port 2

_Port 3

age 35

Page 13~14

Page 13~14

Page 13~14Page 13~14

SB 3.0 TYPEC

U

USB 2.0

USB 3.0 Conn.1

USB 2.0 Conn.1

SB 3.0 Conn.2

U

USB 2.0 Conn.2

Page 32

Page 32

Page 32Page 32

Page 23

Page 23

Page 23Page 23

Page 23

Page 23

Page 23Page 23

Digital Camera

(With Digital MIC)

ard Reader

C

R

Touch Screen

NGFF 2230

W

Finger Printer

Headphone Jack /

Mic. Jack com bo

n IO/B

O

nt. Speaker R / L

I

itle

itle

itle

T

T

T

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date : Sheetof

Date : Sheetof

Date : Sheetof

TS517 0

iFi/BT4.0

Page 21

Page 21

Page 21Page 21

Page 18

Page 18

Page 18Page 18

ompal Electronics, Inc.

ompal Electronics, Inc.

ompal Electronics, Inc.

C

C

C

Block diagram

Block diagram

Block diagram

A-F121P

A-F121P

A-F121P

L

L

L

Page 16

Page 16

Page 16Page 16

n IO/B

O

Page 25

Page 25

Page 25Page 25

Page 16

Page 16

Page 16Page 16

Page 35

Page 35

Page 35Page 35

1

Page 20

Page 20

Page 20Page 20

1

2 61Thursday, November 09, 2 017

2 61Thursday, November 09, 2 017

2 61Thursday, November 09, 2 017

.3(X02)

.3(X02)

.3(X02)

0

0

0

5

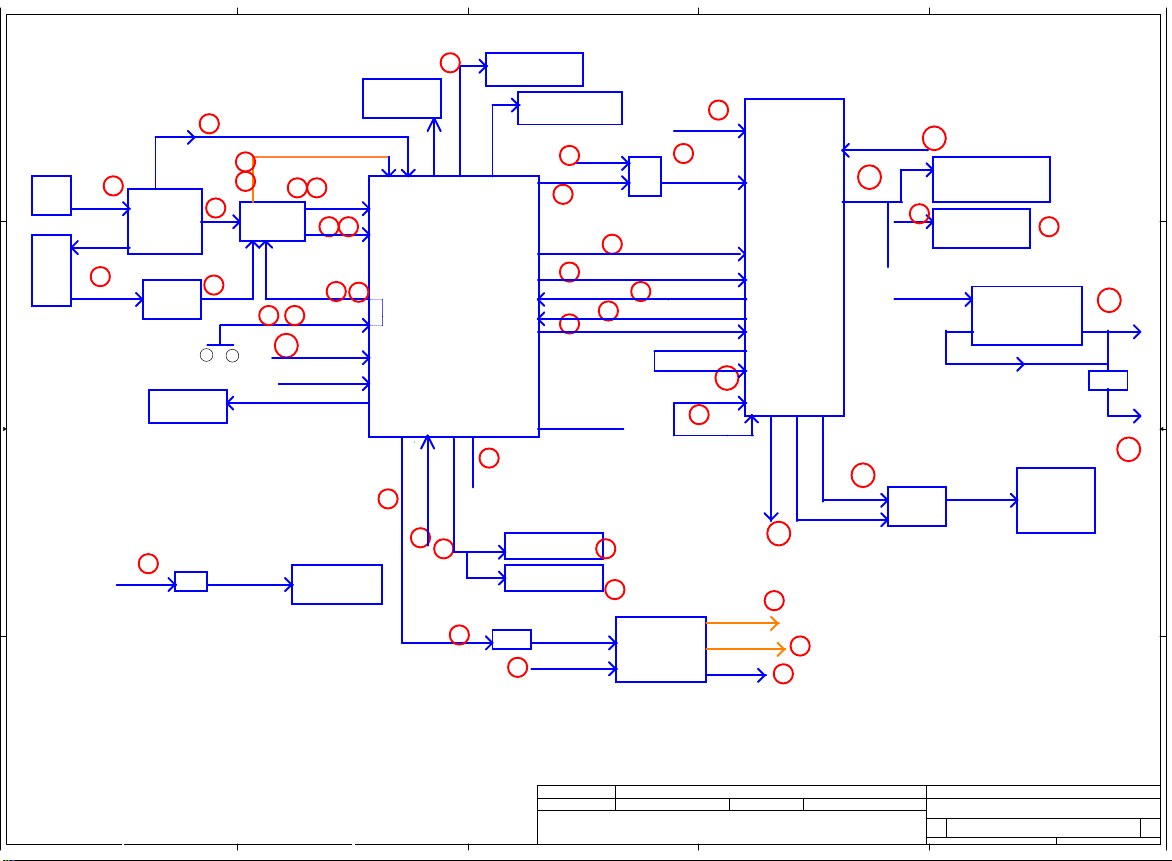

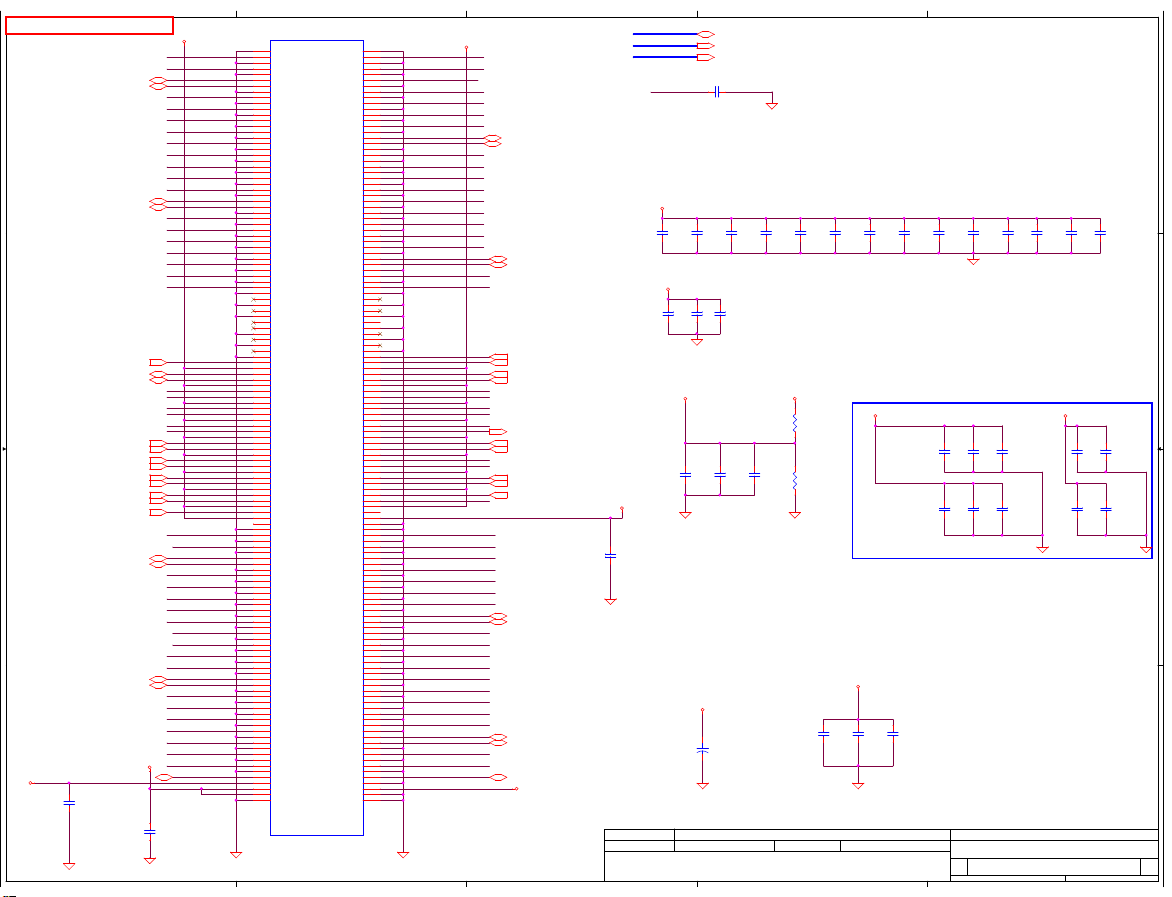

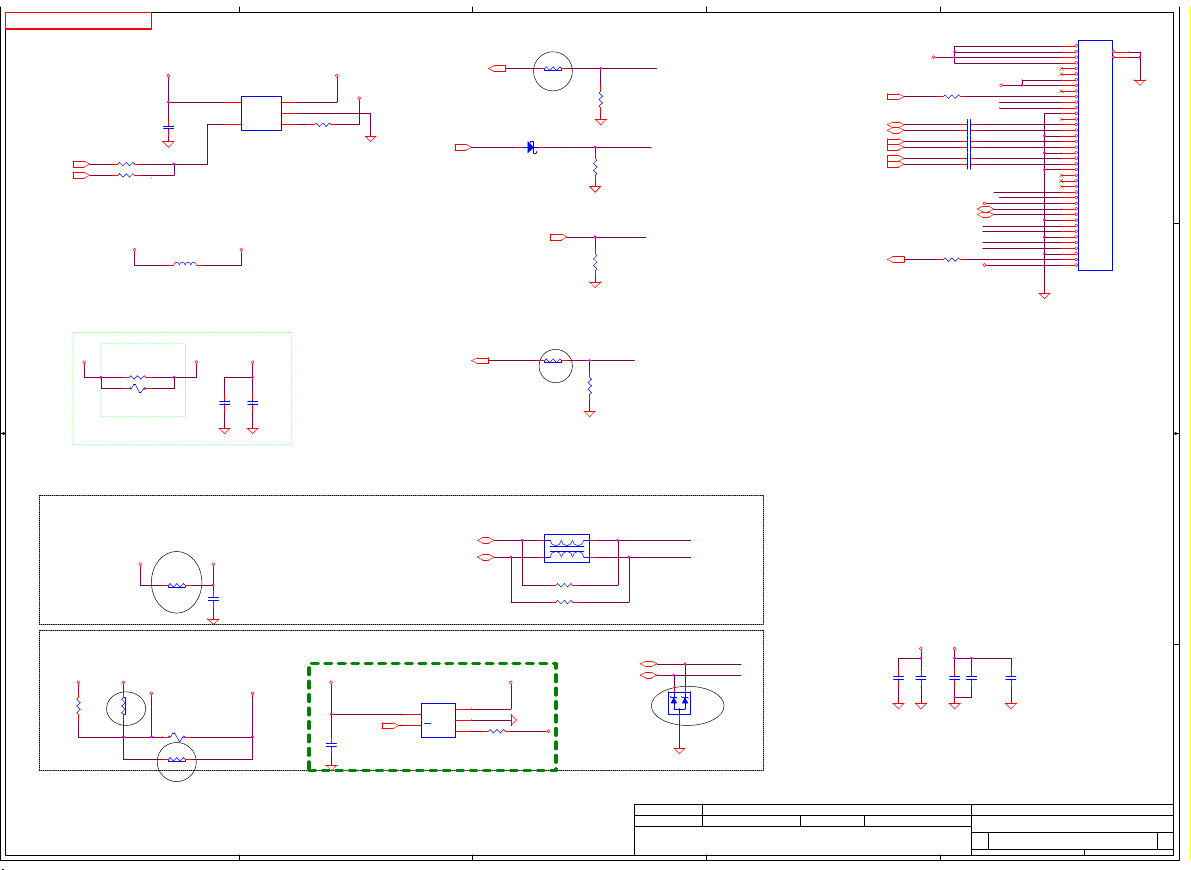

latform Power Sequence

P

LA-F121P

017/02/03

2

D D

C

A

MO DE

C

D

MODE

C C

B B

A1

19V_ADPIN

+

+

PUB01

SL9538HRTZ-T

I

17.4V_BATT+

+

B1

17.4V_BATT+A3PQB03

1

APU_PWRGD

CIN

A

9

1

AON7409

L1

U

RTL8106E-C G

-LAN CTRL

E

0c

A2

H1

D

B5

A3

9

A2

U300

P

PS51285BRUKR

T

19VB

+

2

B

19VB

+

PU_PWRGD_BUF

A

OK

P

3,13

6,20

A4

10d

LAN_PWR_SAVE#

4

+3VALW

B5

+5VALW

A2

4

B

+3VLP,VL

A5

B7

C_ON

E

B6

ON/OFF

LT_RST#

P

DGPU_PWROK

HDT1@

J

Debug connector

I1 SY6288D20AAC

U

5V_USB_PWR1

+

4

3

110

112

14

1

3

1

8

1

726

1

21

1

R_ON

V

9

8

USB_EN#

4

8

E1

U

KB9022QD

4

7

1

GATE

V

d

9

8

.95VS_PWR_ EN#

0

9

9

9

16

SUSP#

9

4 AO4354

U

+0.95Valw-> +0.95VS

U

+3ALW->+LAN_VDD33

OL_EN

W

32

8

9

100

22

1

6

4

1

2

127

5

7

4, EM5209VF

U

+5VS

U6, EM5209VF

+3VS

RZ19

P

c

9

3

L2 SY6288C20AAC

V

c

9

PU_FCH_POK

A

0

1

4

a

6

.95_1.8VALW_PWREN

0

NABLE_APU

E

PU_PWRGD

A

GATE

8a

5

2

b

8

KB_RST#

8

9

1

PU_FCH_PWRGD _R

A

ND

A

UC3

EC_RSMRST#

6

A

PUZ01

ISL62771HRTZ -T

WROK

P

PGOOD

3

TC_CLK

R

0a

BTN_OUT#

P

PM_SLP_S3#

PM_SLP_S5#

APU_RST#

PU_PWRGD

10b

+APU_CORE

+

VGATE

20

W14

A

V6

A

AT16

R15

A

AV13

T14

A

BB11

W4

A

15

D

0d

1

W2

A

H1

A

APU_CORE_NB

D11

B

P

LT_RST#

1

9

PU

A

U1 FP5

D5

B

0c

a

9d

2

W15

A

D15

B

W16

A

P

PU_PCIE_RST#

A

b

9

XS_PWREN

P

11

XS_RST#

WRGD_VGA

P

12

2a

1

8

5

U4&U6 EM 5209VF

USP#

S

DGPU_PWR_EN

ND Gate

A

U3(DIS@)

EM5209VF

CH1 +0.95V SDGPU

CH2 +1.8VGS

VS and 3VS

8

PUV01

ISL62771HRTZ-T

9

WROK

P

PWRGD_VGA

LT_RST_VGA#

P

U

D

1

8c

PGOOD

G1 AU29

GPUUV2

WRGD_VGA

P

0

2

PRV20

DGPU_PWROK

12a

2a

1

A A

ecurity Classification

ecurity Classification

ecurity Classification

S

S

S

ssued Date

ssued Date

ssued Date

I

I

I

HIS SHEET OF E NGINEERING DRAWING IS THE PROPRIETARY P ROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFID ENTIAL

HIS SHEET OF E NGINEERING DRAWING IS THE PROPRIETARY P ROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFID ENTIAL

HIS SHEET OF E NGINEERING DRAWING IS THE PROPRIETARY P ROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFID ENTIAL

T

T

T

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELEC TRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELEC TRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELEC TRONICS, INC.

3

016/01/07 2017/01/07

016/01/07 2017/01/07

016/01/07 2017/01/07

2

2

2

ompal Secret Data

ompal Secret Data

ompal Secret Data

C

C

C

Deciphered Date

Deciphered Date

Deciphered Date

ompal Electronics, Inc.

ompal Electronics, Inc.

ompal Electronics, Inc.

C

C

C

itle

itle

itle

T

T

T

Power Sequence diagram

Power Sequence diagram

Power Sequence diagram

ize

ocument Numb er Re v

ize

ocument Numb er Re v

ize

ocument Numb er Re v

S

D

S

D

S

D

A-F121P

A-F121P

A-F121P

L

L

L

Date: Sheetof

Date: Sheetof

2

Date: Sheetof

1

0

0

0

3 61Thursday, November 09, 2017

3 61Thursday, November 09, 2017

3 61Thursday, November 09, 2017

.3(X02)

.3(X02)

.3(X02)

5

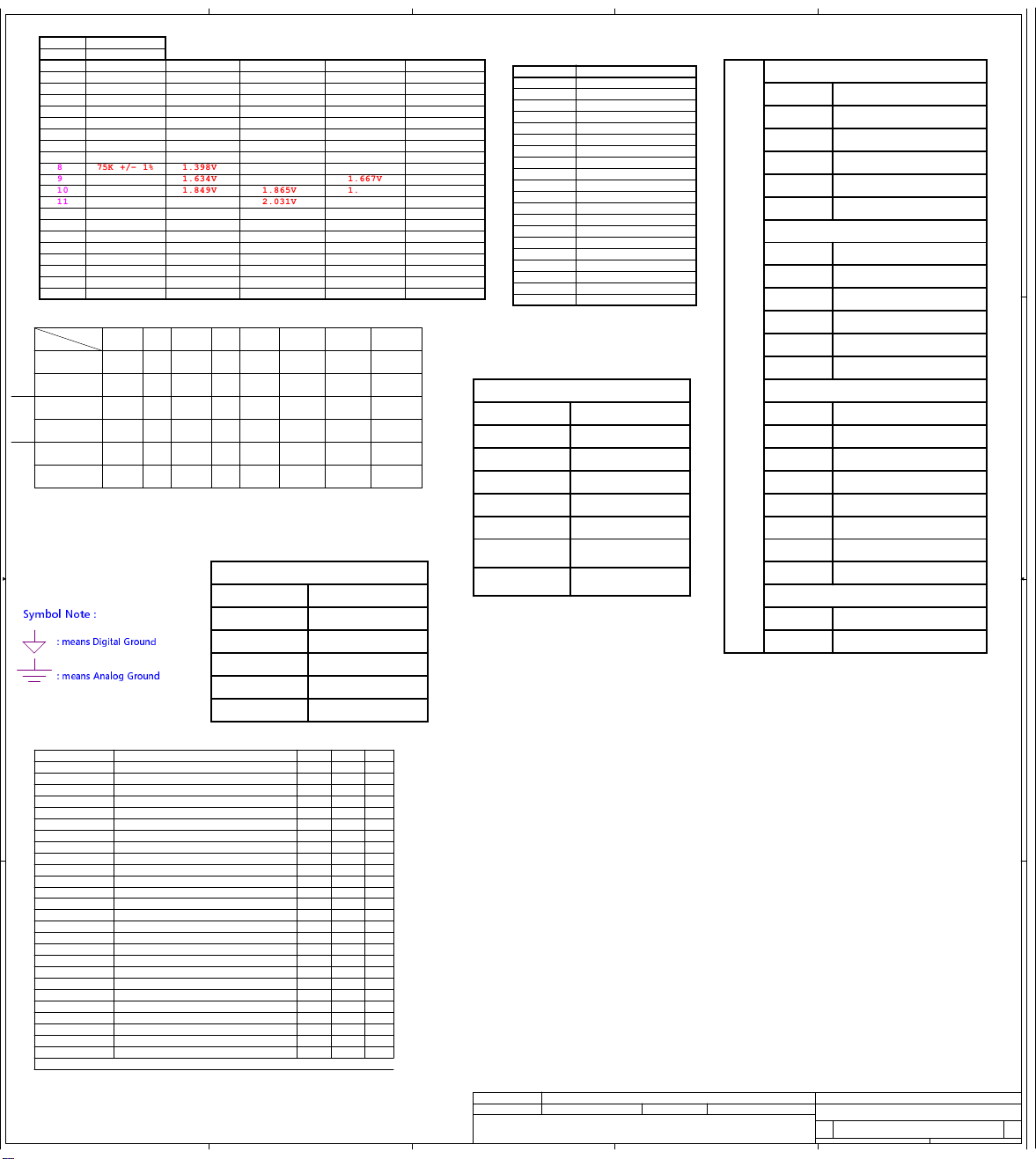

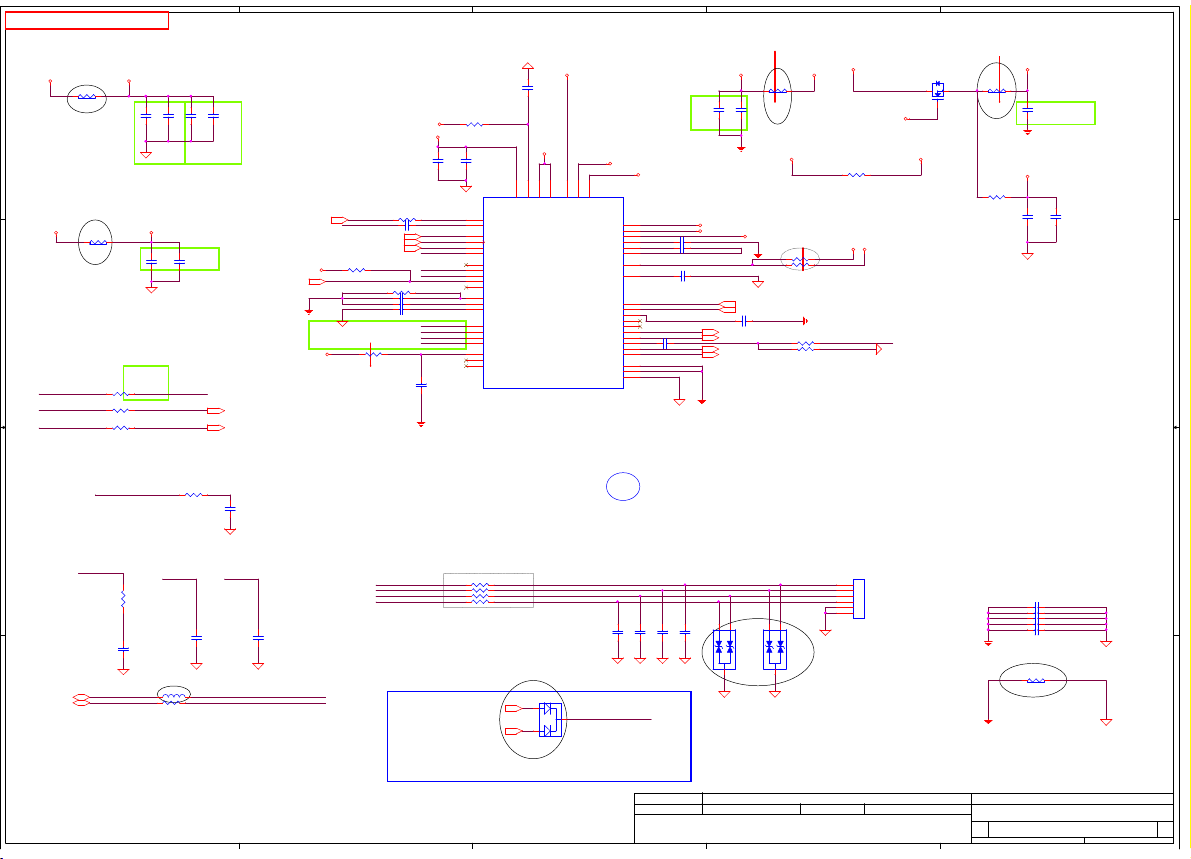

oard ID Table for AD channel

B

Vcc 3.3V +/- 1%

100K +/- 1%Ra

oard ID

B

0

1

2

3

4

5

6

D D

C C

7 56K +/- 1%

8

9

1

11

12

13

14

15 33 0K + /- 1%

16

17

18

19 N C

SMBUS Control Table

EC_SMB_CK 1

EC_SMB_DA 1

EC_SMB_CK 2

EC_SMB_DA 2

EC_I2C_TPC LK

EC_I2C_TPD AT

PU_SCLK0

A

APU_SDATA 0

APU_SCLK1

APU_SDATA 1

APU_SIC

APU_SID

Rb V m in

0 0.000 V

12K +/- 1%

15K +/- 1%

20K +/- 1%

27K +/- 1%

33K +/- 1%

43K +/- 1%

75K +/- 1% 1. 398V

100K +/- 1%

0

160K +/- 1%

200K +/- 1%

240K +/- 1%

270K +/- 1%

30K +/- 1%

4

560K +/- 1%

750K +/- 1%

SOURCE

KB9022Q

KB9022Q

KB9022Q

APU

PU

A

APU

D_BI D

A

0.347 V

0.423 V 0.430 V

0.541 V

0.691 V

0.807 V

0.978 V 0.992 V

1.169 V

1.634 V

1.849 V 1.865 V

2.015 V

2.185 V

2.316 V

2.395 V 2.408 V

2.521 V

2.667 V

2.791 V

2.905 V 2.912 V

3.000 V

ATT

harger

B

C

V

V

DIMM

V

hermal

T

Sensor

CLKOUT_PCIE0

Note :

Symbol

: means Digital Ground

: means Analog Ground

CLKOUT_PCIE1

CLKOUT_PCIE2

CLKOUT_PCIE3

4

typ

V

D_BI D

A

0.000 V 0.300 V

0.354 V

0.550 V

0.702 V

0.819 V

1.185 V

1.414 V 1.430 V

1.650 V

2.031 V

2.200 V

2.329 V

2.533 V

2.677 V

2.800 V

3.300 V

FS CRT

F

V

A

D_BI D

0.360 V

0.438 V

0.559 V

0.713 V

0.831 V

1.006 V

1.200 V

1.667 V

1.881 V130K +/- 1%

2.046 V

2.215 V

2.343 V

2.421 V

2.544 V

2.687 V

2.808 V

2.919 V

3.300 V

V

V

V

V

CLOCK SIGNAL

dGPU

0/100 LAN(GIGA RESERVE)

1

NGFF Card (WLAN)

NVME SSD

m

ax

EC AD3

x00 - 0x13

0

0x14 - 0x1E

0x1F - 0x25

0x26 - 0x30

0x31 - 0x3A

0x3B - 0x45

0x46 - 0x54

0x55 - 0x64

x65 - 0x76

0

0x77 - 0x87

0x88 - 0x96

0x97 - 0xA4

0xA5 - 0xAF

xB0 - 0xB7

0

0xB8 - 0xBF

0xC0 - 0xC9

0xCA - 0xD4

0xD5 - 0xDD

0xDE - 0xF0

0xF1 - 0xFF

3

BOARD ID Table

Board ID

0

1

2

3

4

5

6

7

8

9

10

11

2

1

13

14

15

16

17

18

19

PCI EXPRESS(GFX)

Lane 1

Lane 2

Lane 3

Lane 4

Lane 5

Lane 6

Lane 7

Lane 8

Raven EVT UMA

aven EVT DIS

R

aven DVT1 UMA

R

Raven DVT1 DIS

Raven DVT2 UMA

Raven DVT2 DIS

aven Pilot UMA

R

Raven Pilot DIS

(AMD)M2-50

PEG

(AMD)M2-50

PEG

PEG (AMD)M2-50

PEG (AMD)M2-50

RV2 NA

RV2 NA

RV2 NA

RV2 NA

2

V2 NA

R

RV2 NA

LT

U

RV2 NA

RV2 NA

RV2 Sata only

RV2 Sata only

_Port0

0

_Port1

0

0_Port2

0_Port3

1_Port0

1_Port1

_Port0

0

0_Port1

0_Port2

0_Port3

1_Port0

1_Port1

ane 1

L

Lane 2

Lane 3

Lane 4

Lane 5

Lane 6

Lane 7

Lane 8

ATA0

S

SATA1

1

USB3.0

YPE C

T

USB3 connector 1

SB3 connector 2

U

progaming DP signal

SB2.0

U

YPE C

T

SB connector 1

U

SB connector 2

U

amera

C

USB connector 1(D/B)

USB HUB

PCI EXPRESS(GPP)

NVME SSD

NVME SSD

VME SSD

N

NVME SSD

10/100 LAN(GIGA RESERVE)

GFF Card (WLAN)

N

use sata interface

use sata interface

SATA

DD

H

DD

O

B B

oltage Rails

V

dapter power supply

SDC_IN

+

+17.4V_BATT++

+19VB

APU_VDDCORE

+

+APU_VDDSOC VDDSOC voltage for APU

3VALW_APU 3V_always for APU

+

0.8VALW_APU ON*

+

+1.8V_ALW_APU

0.8VS

+

+VGA_CORE

1.35V_MEM_GFX +1.35VS power rail for G PU and VRAM

+

3VGS

+

+0.95VSDGPU 0.95V power rail for GPU

+3.3V_VDD_PIC

+3VALW System +3VALW always on power rail

3VLP

+

3VS

+

+0.6V_DDR_VTT

2.5V_MEM

+

A A

1.8VS System +1.8VS power rail

+

5VALW

+

5VS System +5VS power rail

+

RTCVCC RTC power

+

A

at t ery po wer s uppl y

B

AC or DC for power circuit

ore voltage for APU

C

0.8V_always for APU

.8V_always for APU

1

.8V_sustain for APU

0

GA core power rail for GPU

V

1.8VS power rail for G PU+1.8VGS

+

.3V power rail for PD chip

3

19VB to +3VLP power rail for suspend power

+

ystem +3VS power rail

S

DR +0.6VS power rail for DDR terminator

D

DR4/L-RS +1.2V power rail+1.2V_DDR

D

DR4/L-RS +2.5V power rail

D

ystem +5VALW power rail

S

S0 S3 S4/S5Power Plane De script i on

N

N/A

N/A

ON

ON

ON

O

ON

O

ON

ON

ON

O

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

N/A

/A

/A

N

N/A

N/A

N/A

N/A

OFF

OFF

OFF

OFF

N*

N

O

O

ON

N

N

N

ON

FF OFF

O

OFF

FF

O

OFF

OFF

OFF

N

O

ON

FF OFF

O

FF

O

N

O

ON

OFF

N

O

FF

O

N

O

ON*

OFF

O

OFF+3VS power rail for G PU

O

O

O

ON*

O

OFF

O

OFF

OFF

ON*

OFF

O

FF

FFOFF

FF

N*

N

FF

N

Note : ON* means that this power plane is ON on ly with AC power available, otherwise it is OFF

ecurity Classification

ecurity Classification

ecurity Classification

S

S

S

ssued Date

ssued Date

ssued Date

I

I

I

THIS SHEET OF ENGINEERING DRAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATIONIT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATIONIT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATIONIT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUTPRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

016/01/07 2017/01/07

016/01/07 2017/01/07

016/01/07 2017/01/07

2

2

2

ompal Secret Data

ompal Secret Data

ompal Secret Data

C

C

C

Deciphered Date

Deciphered Date

Deciphered Date

ompal Electronics, Inc.

ompal Electronics, Inc.

ompal Electronics, Inc.

C

C

C

itle

itle

itle

T

T

T

Notes List

Notes List

Notes List

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

LA-F121P

LA-F121P

LA-F121P

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

1

0.3(X02)

0.3(X02)

0.3(X02)

4 61Thursday, November 09, 2017

4 61Thursday, November 09, 2017

4 61Thursday, November 09, 2017

5

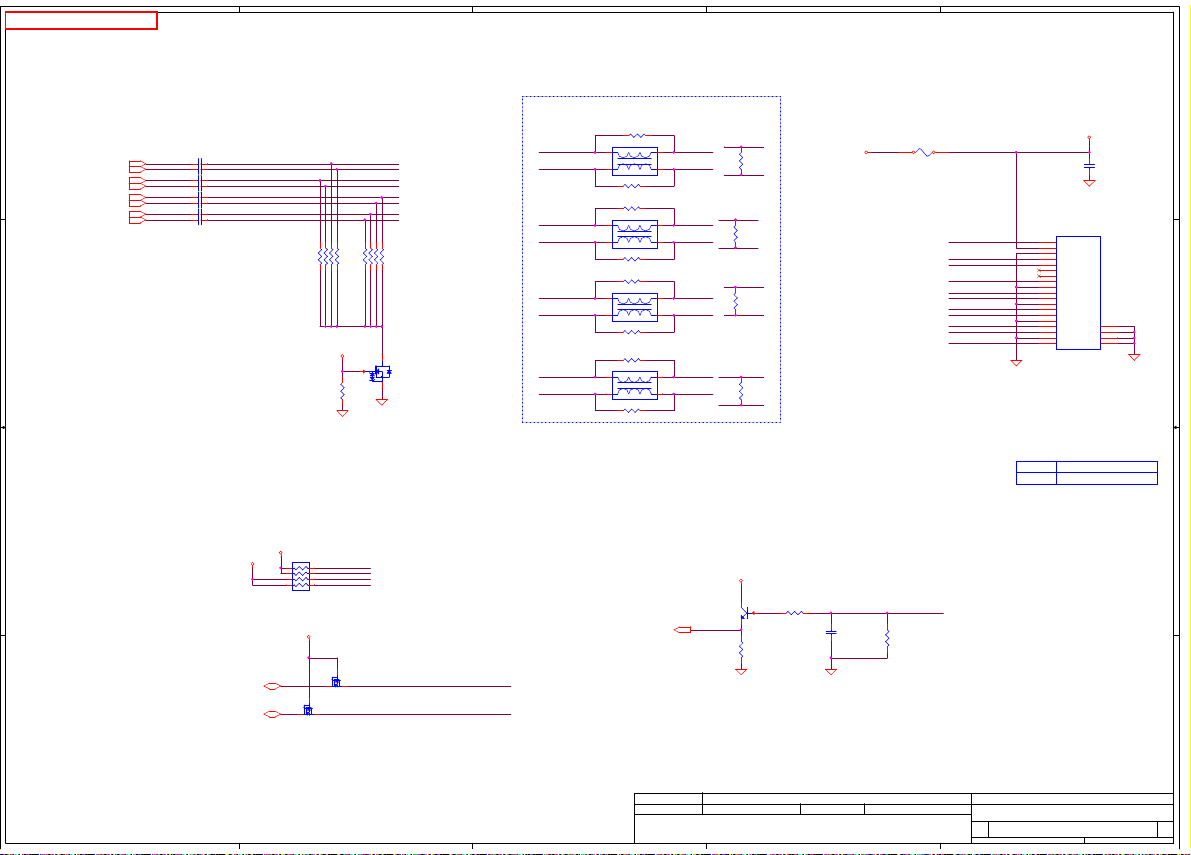

MBus Block Diagram

S

RPC64

RPC64

PU_SCLK0

A

BC20

PU_SDATA0

A

BA20

D D

RP4.2

aven

R

C C

A

AT13

H

J14

R13

14

+

PC3.1

R

PU_SIC

A

APU_SID

2C_3_SCL

I

I2C_3_SDA

3VS

K

1

RC24

EC_SMB_CK2

9

7

80

_SMB_DA2

EC

B B

RP4.1

RPC3.3

1K

N-MOS

N-MOS

QC2

3VS

+

RC25

2.2K

2.2K

.2K

2

2.2K

.2K

2

2.2K

EC_SMB_CK2

EC_SMB_DA2

4

3VS

+

3VS_T OUC H

+

EC_SMB_CK2

EC_SMB_DA2

J

Q11

N-MOS

N-MOS

3

TP

3VS

+

31

R

K

R32

1

1K

QV1

N-MOS

N-MOS

8

8 thermal sensor

U

7

RV5DIS@

RV6DIS@

45.3K

5.3K

4

GA_SMB_CK3

V

VGA_SMB_DA3

+

3VGS

2

253

DIMM1

54

2

253

DIMM2

254

1

FFS

4

2

1

CRT

J

11

U7

V1

U

PU

G

U8

1

BC

K

KB9022QD

.2K

RE509

2

3VAL W

+

2.2K

RE510

77

8

7

A A

5

EC_SMB_CK1

EC_SMB_DA1

4

PR770

0 ohm

0 ohm

PR769

PR20

100 ohm

100 ohm

PR18

LK_SMB

C

DAT_SMB

4

CL

S

U703

P

WER

PO

A

SD

harger

3

3

C

6

5

ATT

ATT1

B

PB

ONN

C

ecurity Classification

ecurity Classificati on

ecurity Classificati on

S

S

S

Issued Date

Issued Date

Issued Date

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

T

T

T

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM T HE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM T HE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM T HE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPALELECT RONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPALELECT RONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPALELECT RONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CONSENT OF COMPALELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CONSENT OF COMPALELECT RONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CONSENT OF COMPALELECT RONICS, INC.

2

2

2

ompal Secret Data

ompal Secret Data

ompal Secret Data

C

C

C

016/01/07 2017/01/07

016/01/07 2017/01/07

016/01/07 2017/01/07

Deciphered Date

Deciphered Date

Deciphered Date

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

2

DELL CONFIDENTIAL/PROPRIETARY

ompal Electronics, Inc.

ompal Electronics, Inc.

ompal Electronics, Inc.

C

C

C

itle

itle

itle

T

T

T

SMBus block diagram

SMBus block diagram

SMBus block diagram

ize

ocument Number Rev

ize

ocument Number Re v

ize

ocument Number Re v

S

D

S

D

S

D

A-F121P

A-F121P

A-F121P

L

L

L

Date: Sheetof

Date: Sheetof

Date: Sheetof

5 61Thursday, Nov ember 09, 2017

5 61Thursday, Nov ember 09, 2017

5 61Thursday, Nov ember 09, 2017

1

.3(X02)

.3(X02)

.3(X02)

0

0

0

ain Func = CPU

M

5

4

3

2

1

D D

EG_ARX_GTX_P[3..0][38]

P

EG_ARX_GTX_N[3..0][38]

P

CIE_ARX_DTX_P[3..0][34]

P

CIE_ARX_DTX_N[3..0][3 4]

C C

CHANGE LAN/WLAN NET NAME @2/23

B B

A A

P

C1

U

A0000BBJ0L

S

3_PC@

R

IC RAVEN3 ZM2300C4T2OFB 2G BGA 1140 APU

S

C1

U

A0000ASA2L

S

7_PC@

R

IC RAVEN7 ZM2000C4T4MF2 2G BGA 1140 APU

S

C1

U

A0000A8R0L

S

5_PC@

R

IC RAVEN5 ZM1800C4T4MF2 1.8G BGA 1140 APU

S

5

H

ODD

AN

L

WLAN

DD

HANGE PEG NET NAME @2/23

C

PEG

EG_ARX_GTX_P[3..0]

P

EG_ARX_GTX_N[3..0]

P

CHANGE SSD NET NAME @2/23

CIE_ARX_DTX_P[3..0]

P

CIE_ARX_DTX_N[3..0]

P

ATA_ARX_DTX_P0[22]

S

ATA_ARX_DTX_N0[22]

S

ATA_ARX_DTX_P1[22]

S

ATA_ARX_DTX_N1[22]

S

EG_ARX_GTX_P0

P

EG_ARX_GTX_N0

P

EG_ARX_GTX_P1

P

EG_ARX_GTX_N1

P

EG_ARX_GTX_P2

P

EG_ARX_GTX_N2

P

EG_ARX_GTX_P3

P

EG_ARX_GTX_N3

P

CIE_ARX_DTX_P0

P

CIE_ARX_DTX_N0

P

CIE_ARX_DTX_P1

P

CIE_ARX_DTX_N1

P

CIE_ARX_DTX_P2

SSD

CIE_ARX_DTX_P4[19]

P

CIE_ARX_DTX_N4[19]

P

CIE_ARX_DTX_P5[20]

P

CIE_ARX_DTX_N5[20]

P

P

CIE_ARX_DTX_N2

P

CIE_ARX_DTX_P3

P

CIE_ARX_DTX_N3

P

C1

U

A0000BBJ1L

S

3_PR@

R

IC RAVEN3 YM2200C4T2OFB 2.5G BGA 1140 APU

S

C1

U

A0000ASA3L

S

7_PR@

R

IC RAVEN7 YM2700C4T4MFB 2G BGA 1140 APU

S

C1

U

A0000A8R1L

S

5_PR@

R

IC RAVEN5 YM2500C4T4MFB 1.8G BGA 1140 APU

S

4

8

P

P

9

P

P

6

N

P

7

N

P

8

M

P

9

M

P

6

L

P

7

L

P

11

K

P

11

J

P

6

H

P

7

H

P

6

G

P

7

F

P

8

G

P

8

F

P

10

N

P

9

N

P

10

L

P

9

L

P

12

L

P

11

M

P

12

P

P

11

P

P

6

V

P

7

V

P

8

T

P

9

T

P

6

R

P

7

R

P

9

R

P

10

R

P

@

_GFX_RXP0

_GFX_RXN0

_GFX_RXP1

_GFX_RXN1

_GFX_RXP2

_GFX_RXN2

_GFX_RXP3

_GFX_RXN3

_GFX_RXP4

_GFX_RXN4

_GFX_RXP5

_GFX_RXN5

_GFX_RXP6

_GFX_RXN6

_GFX_RXP7

_GFX_RXN7

_GPP_RXP0

_GPP_RXN0

_GPP_RXP1

_GPP_RXN1

_GPP_RXP2

_GPP_RXN2

_GPP_RXP3

_GPP_RXN3

_GPP_RXP4

_GPP_RXN4

_GPP_RXP5

_GPP_RXN5

_GPP_RXP6/SATA_RXP0

_GPP_RXN6/SATA_RXN0

_GPP_RXP7/SATA_RXP1

_GPP_RXN7/SATA_RXN1

UC1B

PCIE

FP5 REV 0.90

ART 2 OF 13

P

P5_BGA1140~D

F

C1

U

A0000ASA4L

S

7_PR_R3@

R

IC RAVEN7 YM2700C4T4MFB 2.2G BGA 1140 APU A31 !

S

C1

U

A0000A8R2L

S

5_PR_R3@

R

IC RAVEN5 YM2500C4T4MFB 2G BGA 1140 APU A31 !

S

ecurity Classification

ecurity Classification

ecurity Classification

S

S

S

ssued Date

ssued Date

ssued Date

I

I

I

HIS SHEET OF E NGINEERING DRAWING IS THE PROPRIETARY P ROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFID ENTIAL

HIS SHEET OF E NGINEERING DRAWING IS THE PROPRIETARY P ROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFID ENTIAL

HIS SHEET OF E NGINEERING DRAWING IS THE PROPRIETARY P ROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFID ENTIAL

T

T

T

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELEC TRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELEC TRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELEC TRONICS, INC.

3

1

N

_GFX_TXP0

P

3

N

_GFX_TXN0

P

2

M

_GFX_TXP1

P

4

M

_GFX_TXN1

P

2

L

_GFX_TXP2

P

4

L

_GFX_TXN2

P

1

L

_GFX_TXP3

P

3

L

_GFX_TXN3

P

2

K

_GFX_TXP4

P

4

K

_GFX_TXN4

P

2

J

_GFX_TXP5

P

4

J

_GFX_TXN5

P

1

H

_GFX_TXP6

P

3

H

_GFX_TXN6

P

2

H

_GFX_TXP7

P

4

H

_GFX_TXN7

P

CIE_ATX_DRX_P0

P

2

N

_GPP_TXP0

P

_GPP_TXN0

P

_GPP_TXP1

P

_GPP_TXN1

P

_GPP_TXP2

P

_GPP_TXN2

P

_GPP_TXP3

P

_GPP_TXN3

P

_GPP_TXP4

P

_GPP_TXN4

P

_GPP_TXP5

P

_GPP_TXN5

P

_GPP_TXP6/SATA_TXP0

P

_GPP_TXN6/SATA_TXN0

P

_GPP_TXP7/SATA_TXP1

P

_GPP_TXN7/SATA_TXN1

P

016/01/07 2017/01/07

016/01/07 2017/01/07

016/01/07 2017/01/07

2

2

2

3

P

4

P

2

P

3

R

1

R

4

T

2

T

2

W

4

W

3

W

2

V

1

V

3

V

2

U

4

U

CIE_ATX_DRX_N0

P

CIE_ATX_DRX_P1

P

CIE_ATX_DRX_N1

P

CIE_ATX_DRX_P2

P

CIE_ATX_DRX_N2

P

CIE_ATX_DRX_P3

P

CIE_ATX_DRX_N3

P

CIE_ATX_DRX_P4

P

CIE_ATX_DRX_N4

P

CIE_ATX_DRX_P5

P

CIE_ATX_DRX_N5

P

ompal Secret Data

ompal Secret Data

ompal Secret Data

C

C

C

CIE_ATX_DRX_P[3..0]

P

CIE_ATX_DRX_N[3..0]

P

lace near UC1

p

C1 .1U_0402_16V7K

C

1 2

C2 .1U_0402_16V7K

C

1 2

C3 .1U_0402_16V7K

C

1 2

C4 .1U_0402_16V7K

C

1 2

Deciphered Date

Deciphered Date

Deciphered Date

2

EG_ATX_GRX_P0

P

EG_ATX_GRX_N0

P

EG_ATX_GRX_P1

P

EG_ATX_GRX_N1

P

EG_ATX_GRX_P2

P

EG_ATX_GRX_N2

P

EG_ATX_GRX_P3

P

EG_ATX_GRX_N3

P

PEG

EG_ATX_GRX_P[3..0]

P

EG_ATX_GRX_N[3..0]

P

CIE_ATX_DRX_P[3..0] [34]

P

CIE_ATX_DRX_N[3..0] [34]

P

SSD

CIE_ATX_C_DRX_P4 [19]

P

CIE_ATX_C_DRX_N4 [19]

P

CIE_ATX_C_DRX_P5 [20]

P

CIE_ATX_C_DRX_N5 [20]

ATA_ATX_DRX_P0 [22]

S

ATA_ATX_DRX_N0 [22]

S

ATA_ATX_DRX_P1 [22]

S

ATA_ATX_DRX_N1 [22]

S

P

HDD

ODD

itle

itle

itle

T

T

T

F

F

F

ize

ocument Numb er Re v

ize

ocument Numb er Re v

ize

ocument Numb er Re v

S

D

S

D

S

D

ustom

ustom

ustom

C

C

C

A-F121P

A-F121P

A-F121P

L

L

L

Date: Sheetof

Date: Sheetof

Date: Sheetof

EG_ATX_GRX_P[3..0] [38]

P

EG_ATX_GRX_N[3..0] [38]

P

AN

L

WLAN

ompal Electronics, Inc.

ompal Electronics, Inc.

ompal Electronics, Inc.

C

C

C

P4 PCIE/UMI

P4 PCIE/UMI

P4 PCIE/UMI

1

0

0

0

6 61Thursday, November 09, 2017

6 61Thursday, November 09, 2017

6 61Thursday, November 09, 2017

.3(X02)

.3(X02)

.3(X02)

ain Func = CPU

M

D D

C C

B B

5

DR_A_MA[13..0][13]

D

DR_A_MA0

D

DR_A_MA1

D

DR_A_MA2

D

DR_A_MA3

D

DR_A_MA4

D

DR_A_MA5

D

DR_A_MA6

D

DR_A_MA7

D

DR_A_MA8

D

DR_A_MA9

D

DR_A_MA10

D

DR_A_MA11

D

DR_A_MA12

D

DR_A_MA13

D

DR_A_MA14_WE#[13]

D

DR_A_MA15_CAS#[13]

D

DR_A_MA16_RAS#[13]

D

DR_A_BA0[13]

D

DR_A_BA1[13]

D

DR_A_BG0

D

DR_A_BG1

D

DR_A_BG0[1 3]

D

DR_A_BG1[1 3]

D

DR_A_ACT#

D

DR_A_ACT#[13]

D

DR_A_DM0

D

DR_A_DM[7..0][13]

D

DR_A_DM1

D

DR_A_DM2

D

DR_A_DM3

D

DR_A_DM4

D

DR_A_DM5

D

DR_A_DM6

D

DR_A_DM7

D

DR_A_DQS0[13]

D

DR_A_DQS0#[13]

D

DR_A_DQS1[13]

D

DR_A_DQS1#[13]

D

DR_A_DQS2[13]

D

DR_A_DQS2#[13]

D

DR_A_DQS3[13]

D

DR_A_DQS3#[13]

D

DR_A_DQS4[13]

D

DR_A_DQS4#[13]

D

DR_A_DQS5[13]

D

DR_A_DQS5#[13]

D

DR_A_DQS6[13]

D

DR_A_DQS6#[13]

D

DR_A_DQS7[13]

D

DR_A_DQS7#[13]

D

DR_A_CLK0[13]

D

DR_A_CLK0#[13]

D

DR_A_CLK1[13]

D

DR_A_CLK1#[13]

D

DR_A_CS0#[13]

D

DR_A_CS1#[13]

D

DR_A_CKE0[13]

D

DR_A_CKE1[13]

D

DR_A_ODT0[13]

D

DR_A_ODT1[13]

D

DR_A_ALERT#[13]

D

DR_A_EVENT#[13]

D

DR_A_RST#[13]

D

UC1A

MEMORY A

F25

A

A_ADD0

M

E23

A

A_ADD1

M

D27

A

A_ADD2

M

E21

A

A_ADD3

M

C24

A

A_ADD4

M

C26

A

A_ADD5

M

D21

A

A_ADD6

M

C27

A

A_ADD7

M

D22

A

A_ADD8

M

C21

A

A_ADD9

M

F22

A

A_ADD10

M

A24

A

A_ADD11

M

C23

A

A_ADD12

M

J25

A

A_ADD13_BANK2

M

G27

A

A_WE_L_ADD14

M

G23

A

A_CAS_L_ADD15

M

G26

A

A_RAS_L_ADD16

M

F21

A

A_BANK0

M

F27

A

A_BANK1

M

A21

A

A_BG0

M

A27

A

A_BG1

M

A22

A

A_ACT_L

M

21

F

A_DM0

M

27

G

A_DM1

M

24

N

A_DM2

M

23

N

A_DM3

M

L24

A

A_DM4

M

N27

A

A_DM5

M

W25

A

A_DM6

M

T21

A

A_DM7

M

27

T

SVD_36

R

22

F

A_DQS_H0

M

22

G

A_DQS_L0

M

27

H

A_DQS_H1

M

26

H

A_DQS_L1

M

27

N

A_DQS_H2

M

26

N

A_DQS_L2

M

21

R

A_DQS_H3

M

21

P

A_DQS_L3

M

M26

A

A_DQS_H4

M

M27

A

A_DQS_L4

M

N24

A

A_DQS_H5

M

N25

A

A_DQS_L5

M

U23

A

A_DQS_H6

M

T23

A

A_DQS_L6

M

V20

A

A_DQS_H7

M

W20

A

A_DQS_L7

M

24

V

SVD_41

R

23

V

SVD_40

R

D25

A

A_CLK_H0

M

D24

A

A_CLK_L0

M

E26

A

A_CLK_H1

M

E27

A

A_CLK_L1

M

G21

A

A_CS_L0

M

J27

A

A_CS_L1

M

23

Y

A_CKE0

M

26

Y

A_CKE1

M

G24

A

A_ODT0

M

J22

A

A_ODT1

M

A25

A

A_ALERT_L

M

E24

A

A_EVENT_L

M

24

Y

A_RESET_L

M

FP5 REV 0.90

ART 1 OF 13

P

P5_BGA1140~D

F

@

4

DR_A_DQ[63..0] [13]

D

DR_A_DQ0

D

21

J

A_DATA0

M

DR_A_DQ1

D

21

H

A_DATA1

M

DR_A_DQ2

D

23

F

A_DATA2

M

DR_A_DQ3

D

23

H

A_DATA3

M

DR_A_DQ4

D

20

G

A_DATA4

M

DR_A_DQ5

D

20

F

A_DATA5

M

DR_A_DQ6

D

22

J

A_DATA6

M

DR_A_DQ7

D

23

J

A_DATA7

M

DR_A_DQ8

D

25

G

A_DATA8

M

DR_A_DQ9

D

26

F

A_DATA9

M

DR_A_DQ10

D

24

L

A_DATA10

M

DR_A_DQ11

D

26

L

A_DATA11

M

DR_A_DQ12

D

23

L

A_DATA12

M

DR_A_DQ13

D

25

F

A_DATA13

M

DR_A_DQ14

D

25

K

A_DATA14

M

DR_A_DQ15

D

27

K

A_DATA15

M

DR_A_DQ16

D

25

M

A_DATA16

M

DR_A_DQ17

D

27

M

A_DATA17

M

DR_A_DQ18

D

27

P

A_DATA18

M

DR_A_DQ19

D

24

R

A_DATA19

M

DR_A_DQ20

D

27

L

A_DATA20

M

DR_A_DQ21

D

24

M

A_DATA21

M

DR_A_DQ22

D

24

P

A_DATA22

M

DR_A_DQ23

D

25

P

A_DATA23

M

DR_A_DQ24

D

22

M

A_DATA24

M

DR_A_DQ25

D

21

N

A_DATA25

M

DR_A_DQ26

D

22

T

A_DATA26

M

DR_A_DQ27

D

21

V

A_DATA27

M

DR_A_DQ28

D

21

L

A_DATA28

M

DR_A_DQ29

D

20

M

A_DATA29

M

DR_A_DQ30

D

23

R

A_DATA30

M

DR_A_DQ31

D

21

T

A_DATA31

M

DR_A_DQ32

D

L27

A

A_DATA32

M

DR_A_DQ33

D

L25

A

A_DATA33

M

DR_A_DQ34

D

P26

A

A_DATA34

M

DR_A_DQ35

D

R27

A

A_DATA35

M

DR_A_DQ36

D

K26

A

A_DATA36

M

DR_A_DQ37

D

K24

A

A_DATA37

M

DR_A_DQ38

D

M24

A

A_DATA38

M

DR_A_DQ39

D

P27

A

A_DATA39

M

DR_A_DQ40

D

M23

A

A_DATA40

M

DR_A_DQ41

D

M21

A

A_DATA41

M

DR_A_DQ42

D

R25

A

A_DATA42

M

DR_A_DQ43

D

U27

A

A_DATA43

M

DR_A_DQ44

D

L22

A

A_DATA44

M

DR_A_DQ45

D

L21

A

A_DATA45

M

DR_A_DQ46

D

P24

A

A_DATA46

M

DR_A_DQ47

D

P23

A

A_DATA47

M

DR_A_DQ48

D

W26

A

A_DATA48

M

DR_A_DQ49

D

V25

A

A_DATA49

M

DR_A_DQ50

D

V22

A

A_DATA50

M

DR_A_DQ51

D

W22

A

A_DATA51

M

DR_A_DQ52

D

U26

A

A_DATA52

M

DR_A_DQ53

D

V27

A

A_DATA53

M

DR_A_DQ54

D

W23

A

A_DATA54

M

DR_A_DQ55

D

T22

A

A_DATA55

M

DR_A_DQ56

D

W21

A

A_DATA56

M

DR_A_DQ57

D

U21

A

A_DATA57

M

DR_A_DQ58

D

P21

A

A_DATA58

M

DR_A_DQ59

D

N20

A

A_DATA59

M

DR_A_DQ60

D

R22

A

A_DATA60

M

DR_A_DQ61

D

N22

A

A_DATA61

M

DR_A_DQ62

D

T20

A

A_DATA62

M

DR_A_DQ63

D

R20

A

A_DATA63

M

24

T

SVD_34

R

25

T

SVD_35

R

25

W

SVD_51

R

27

W

SVD_52

R

26

R

SVD_27

R

27

R

SVD_28

R

27

V

SVD_43

R

26

V

SVD_42

R

DR_A_PAR

D

F24

A

A_PAROUT

M

DR_A_PAR [13]

D

3

DR_B_MA[13..0][14]

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

DR_B_MA14_WE#[14]

D

DR_B_MA15_CAS#[14]

D

DR_B_MA16_RAS#[14]

D

DR_B_BA0[14]

D

DR_B_BA1[14]

D

D

D

DR_B_BG0[1 4]

D

DR_B_BG1[1 4]

D

D

DR_B_ACT#[14]

D

D

DR_B_DM[7..0][14]

D

D

D

D

D

D

D

D

DR_B_DQS0[14]

D

DR_B_DQS0#[14]

D

DR_B_DQS1[14]

D

DR_B_DQS1#[14]

D

DR_B_DQS2[14]

D

DR_B_DQS2#[14]

D

DR_B_DQS3[14]

D

DR_B_DQS3#[14]

D

DR_B_DQS4[14]

D

DR_B_DQS4#[14]

D

DR_B_DQS5[14]

D

DR_B_DQS5#[14]

D

DR_B_DQS6[14]

D

DR_B_DQS6#[14]

D

DR_B_DQS7[14]

D

DR_B_DQS7#[14]

D

DR_B_CLK0[14]

D

DR_B_CLK0#[14]

D

DR_B_CLK1[14]

D

DR_B_CLK1#[14]

D

DR_B_CS0#[14]

D

DR_B_CS1#[14]

D

DR_B_CKE0[14]

D

DR_B_CKE1[14]

D

DR_B_ODT0[14]

D

DR_B_ODT1[14]

D

DR_B_ALERT#[14]

D

DR_B_EVENT#[14]

D

DR_B_RST#[14]

D

DR_B_MA0

DR_B_MA1

DR_B_MA2

DR_B_MA3

DR_B_MA4

DR_B_MA5

DR_B_MA6

DR_B_MA7

DR_B_MA8

DR_B_MA9

DR_B_MA10

DR_B_MA11

DR_B_MA12

DR_B_MA13

DR_B_BG0

DR_B_BG1

DR_B_ACT#

DR_B_DM0

DR_B_DM1

DR_B_DM2

DR_B_DM3

DR_B_DM4

DR_B_DM5

DR_B_DM6

DR_B_DM7

2

UC1I

MEMORY B

G30

A

B_ADD0

M

C32

A

B_ADD1

M

C30

A

B_ADD2

M

B29

A

B_ADD3

M

B31

A

B_ADD4

M

A30

A

B_ADD5

M

A29

A

B_ADD6

M

30

Y

B_ADD7

M

A31

A

B_ADD8

M

29

W

B_ADD9

M

H29

A

B_ADD10

M

32

Y

B_ADD11

M

31

W

B_ADD12

M

L30

A

B_ADD13_BANK2

M

K30

A

B_WE_L_ADD14

M

K32

A

B_CAS_L_ADD15

M

J30

A

B_RAS_L_ADD16

M

H31

A

B_BANK0

M

G32

A

B_BANK1

M

31

V

B_BG0

M

29

V

B_BG1

M

30

V

B_ACT_L

M

21

C

B_DM0

M

25

C

B_DM1

M

32

E

B_DM2

M

30

K

B_DM3

M

P30

A

B_DM4

M

W31

A

B_DM5

M

B26

B

B_DM6

M

D22

B

B_DM7

M

32

N

SVD_21

R

22

D

B_DQS_H0

M

22

B

B_DQS_L0

M

25

D

B_DQS_H1

M

25

B

B_DQS_L1

M

29

F

B_DQS_H2

M

30

F

B_DQS_L2

M

31

K

B_DQS_H3

M

29

K

B_DQS_L3

M

R29

A

B_DQS_H4

M

R31

A

B_DQS_L4

M

W30

A

B_DQS_H5

M

W29

A

B_DQS_L5

M

C25

B

B_DQS_H6

M

A25

B

B_DQS_L6

M

C22

B

B_DQS_H7

M

A22

B

B_DQS_L7

M

31

N

SVD_20

R

29

N

SVD_18

R

C31

A

B_CLK_H0

M

D30

A

B_CLK_L0

M

D29

A

B_CLK_H1

M

D31

A

B_CLK_L1

M

E30

A

B_CLK_H2

M

E32

A

B_CLK_L2

M

F29

A

B_CLK_H3

M

F31

A

B_CLK_L3

M

J31

A

B0_CS_L0

M

M31

A

B0_CS_L1

M

J29

A

B1_CS_L0

M

M29

A

B1_CS_L1

M

29

U

B0_CKE0

M

30

T

B0_CKE1

M

32

V

B1_CKE0

M

31

U

B1_CKE1

M

L31

A

B0_ODT0

M

M32

A

B0_ODT1

M

L29

A

B1_ODT0

M

M30

A

B1_ODT1

M

30

W

B_ALERT_L

M

G29

A

B_EVENT_L

M

31

T

B_RESET_L

M

@

FP5 REV 0.90

P

ART 9 OF 13

P5_BGA1140~D

F

21

B

B_DATA0

M

21

D

B_DATA1

M

23

B

B_DATA2

M

23

D

B_DATA3

M

20

A

B_DATA4

M

20

C

B_DATA5

M

22

A

B_DATA6

M

22

C

B_DATA7

M

24

D

B_DATA8

M

25

A

B_DATA9

M

27

D

B_DATA10

M

27

C

B_DATA11

M

23

C

B_DATA12

M

24

B

B_DATA13

M

26

C

B_DATA14

M

27

B

B_DATA15

M

30

C

B_DATA16

M

29

E

B_DATA17

M

29

H

B_DATA18

M

31

H

B_DATA19

M

28

A

B_DATA20

M

28

D

B_DATA21

M

31

F

B_DATA22

M

30

G

B_DATA23

M

29

J

B_DATA24

M

31

J

B_DATA25

M

29

L

B_DATA26

M

31

L

B_DATA27

M

30

H

B_DATA28

M

32

H

B_DATA29

M

30

L

B_DATA30

M

32

L

B_DATA31

M

P29

A

B_DATA32

M

P32

A

B_DATA33

M

T29

A

B_DATA34

M

U32

A

B_DATA35

M

N30

A

B_DATA36

M

P31

A

B_DATA37

M

R30

A

B_DATA38

M

T31

A

B_DATA39

M

U29

A

B_DATA40

M

V30

A

B_DATA41

M

B30

B

B_DATA42

M

A28

B

B_DATA43

M

U30

A

B_DATA44

M

U31

A

B_DATA45

M

Y32

A

B_DATA46

M

Y29

A

B_DATA47

M

A27

B

B_DATA48

M

C27

B

B_DATA49

M

A24

B

B_DATA50

M

C24

B

B_DATA51

M

D28

B

B_DATA52

M

B27

B

B_DATA53

M

B25

B

B_DATA54

M

D25

B

B_DATA55

M

C23

B

B_DATA56

M

B22

B

B_DATA57

M

C21

B

B_DATA58

M

D20

B

B_DATA59

M

B23

B

B_DATA60

M

A23

B

B_DATA61

M

B21

B

B_DATA62

M

A21

B

B_DATA63

M

31

M

SVD_17

R

30

N

SVD_19

R

31

P

SVD_26

R

32

R

SVD_29

R

30

M

SVD_16

R

29

M

SVD_15

R

30

P

SVD_25

R

29

P

SVD_24

R

G31

A

B_PAROUT

M

DR_B_DQ0

D

DR_B_DQ1

D

DR_B_DQ2

D

DR_B_DQ3

D

DR_B_DQ4

D

DR_B_DQ5

D

DR_B_DQ6

D

DR_B_DQ7

D

DR_B_DQ8

D

DR_B_DQ9

D

DR_B_DQ10

D

DR_B_DQ11

D

DR_B_DQ12

D

DR_B_DQ13

D

DR_B_DQ14

D

DR_B_DQ15

D

DR_B_DQ16

D

DR_B_DQ17

D

DR_B_DQ18

D

DR_B_DQ19

D

DR_B_DQ20

D

DR_B_DQ21

D

DR_B_DQ22

D

DR_B_DQ23

D

DR_B_DQ24

D

DR_B_DQ25

D

DR_B_DQ26

D

DR_B_DQ27

D

DR_B_DQ28

D

DR_B_DQ29

D

DR_B_DQ30

D

DR_B_DQ31

D

DR_B_DQ32

D

DR_B_DQ33

D

DR_B_DQ34

D

DR_B_DQ35

D

DR_B_DQ36

D

DR_B_DQ37

D

DR_B_DQ38

D

DR_B_DQ39

D

DR_B_DQ40

D

DR_B_DQ41

D

DR_B_DQ42

D

DR_B_DQ43

D

DR_B_DQ44

D

DR_B_DQ45

D

DR_B_DQ46

D

DR_B_DQ47

D

DR_B_DQ48

D

DR_B_DQ49

D

DR_B_DQ50

D

DR_B_DQ51

D

DR_B_DQ52

D

DR_B_DQ53

D

DR_B_DQ54

D

DR_B_DQ55

D

DR_B_DQ56

D

DR_B_DQ57

D

DR_B_DQ58

D

DR_B_DQ59

D

DR_B_DQ60

D

DR_B_DQ61

D

DR_B_DQ62

D

DR_B_DQ63

D

DR_B_PAR

D

DR_B_DQ[63..0] [14]

D

DR_B_PAR [14]

D

1

VENT# pull high

E

1.2V_DDR

+

1 2

C1 1K_0402_5%

R

1.2V_DDR

+

C2 1K_0402_5%

R

A A

1 2

DR_B_EVENT#

D

DR_A_EVENT#

D

5

ecurity Classification

ecurity Clas sification

ecurity Clas sification

S

S

S

ssued Date

ssued Date

ssued Date

I

I

I

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

HIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

T

T

T

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

ompal Secret Data

ompal Secret Data

ompal Secret Data

C

C

C

016/01/0 7 2017/01/07

016/01/0 7 2017/01/07

016/01/0 7 2017/01/07

2

2

2

2

eciphered Date

eciphered Date

eciphered Date

D

D

D

ompal Electronics, Inc.

ompal Electronics, Inc.

ompal Electronics, Inc.

C

C

C

itle

itle

itle

T

T

T

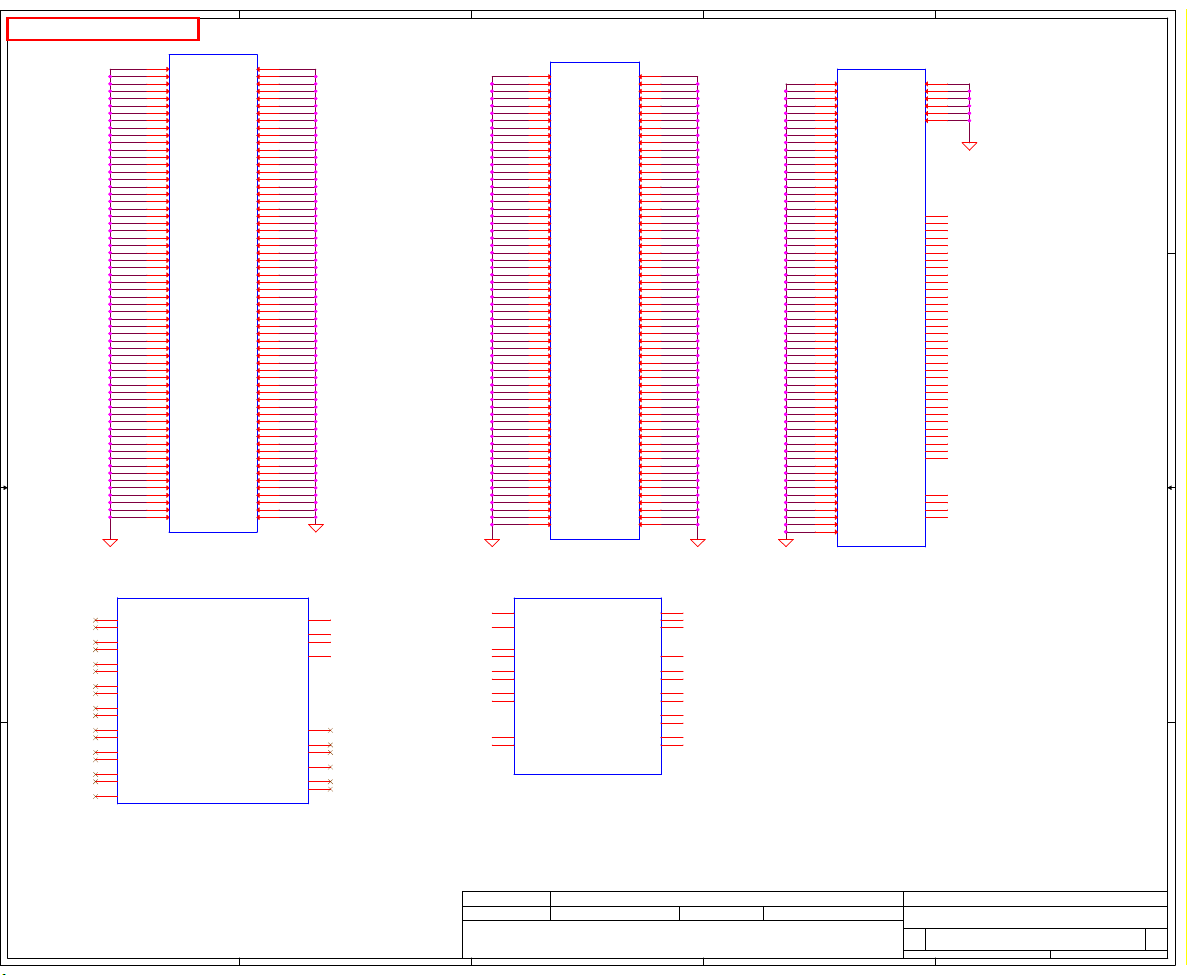

P4 DDR4 MEMORY I/F

P4 DDR4 MEMORY I/F

P4 DDR4 MEMORY I/F

F

F

F

ze

ze

ze

Si

Si

Si

ocument Number Rev

ocument Number Rev

ocument Number Rev

D

D

D

ustom

ustom

ustom

C

C

C

A-F121P

A-F121P

A-F121P

L

L

L

Date: Sheetof

Date: Sheetof

Date: Sheetof

1

7 61Thursday, November 09, 20 17

7 61Thursday, November 09, 20 17

7 61Thursday, November 09, 20 17

.3(X02)

.3(X02)

.3(X02)

0

0

0

1 2

1 2

1 2

E

E

A

18

A

27

A

36

45

H

HERMTRIP#

T

R

1K_0402_5%

R

1K_0402_5%

R

1K_0402_5%

C_SMB_CK2[27,28,39]

C_SMB_DA2[27,28,39]

PU_SID

PU_ALERT#

PU_SIC

_PROCHOT#

A

1.8VS

+

PC30

@

R

18

27

36

45

10K_0804_8P4R_5%

@

C6

@

C7

@

C8

C250

C

1 2

0.1U_0402_16V7K

@ESD@

1 2

@ESD@

1 2

1 2

PU_SVT

A

PU_SVC

A

PU_SVD

A

C_SMB_CK2

E

C_SMB_DA2

E

C_SMB_CK2

E

C_SMB_DA2

E

PU at EC side

@ESD@

PU_RST#

A

C527P_0402_50V8F

C

PU_PWRGD

A

C627P_0402_50V8F

C

C27220_0402_5%

R

@

DP_TXP0[16]

E

DP_TXN0[16]

E

DP

e

DP_TXP1[16]

E

DP_TXN1[16]

E

PU_DP1_P0[17]

A

PU_DP1_N0[17]

A

PU_DP1_P1[17]

A

PU_DP1_N1[17]

A

DMI

H

PU_DP1_P2[17]

A

PU_DP1_N2[17]

A

PU_DP1_P3[17]

A

PU_DP1_N3[17]

A

C616 0_0402_5%

R

1 2

C617 0_0402_5%

R

1 2

_PROCHOT#[10,27,46,48,53]

H

PU_SVC[53]

A

PU_SVD[53]

A

PU_SVT[53]

A

ain Func = CPU

M

1 1

PU_TEST14

A

PU_TEST15

A

PU_TEST16

A

PU_TEST17

A

1.8VS

+

2 2

3VS

+

PC3

R

1K_0804_8P4R_5%

3VS

+

C24 1K_0402_5%@

R

1 2

C25 1K_0402_5%@

R

1 2

3 3

3VS

+

1 2

C26

R

1K_0402_5%

1 2

C664

R

1K_0402_5%

4 4

DP_TXP0

E

DP_TXN0

E

DP_TXP1

E

DP_TXN1

E

PU_SIC

A

PU_SID

A

C12 300_0402_5%

R

1.8VS

+

C15 300_0402_5%

R

1.8VS

+

PU_PWRGD[53]

A

C18 0_0402_5%

R

C20 0_0402_5%

R

C22 0_0402_5%

R

B

1 2

1 2

1 2

1 2

1 2

C

P3: Typec

D

DP2: CRT

DP1: HDMI

DP0: eDP

UC1C

DISPLAY/SVI2/JTA G/TES T

8

C

P0_TXP0

D

8

A

P0_TXN0

D

8

D

P0_TXP1

D

8

B

P0_TXN1

D

6

B

P0_TXP2

D

7

C

P0_TXN2

D

6

C

P0_TXP3

D

6

D

P0_TXN3

PU_DP1_P0

A

PU_DP1_N0

A

PU_DP1_P1

A

PU_DP1_N1

A

PU_DP1_P2

A

PU_DP1_N2

A

PU_DP1_P3

A

PU_DP1_N3

A

PU_TDI

A

PU_TDO

A

PU_TCK

A

PU_TMS

A

PU_TRST#

A

PU_DBREQ#

A

PU_RST#

A

PU_PWRGD

A

PU_SIC

A

PU_SID

A

PU_ALERT#

A

HERMTRIP#

T

HERMTRIP#[27]

T

PU_SVC_R

A

PU_SVD_R

A

PU_SVT_R

A

D

6

E

P1_TXP0

D

5

D

P1_TXN0

D

1

E

P1_TXP1

D

1

C

P1_TXN1

D

3

F

P1_TXP2

D

4

E

P1_TXN2

D

4

F

P1_TXP3

D

2

F

P1_TXN3

D

U2

A

DI

T

U4

A

DO

T

U1

A

CK

T

U3

A

MS

T

V3

A

RST_L

T

W3

A

BREQ_L

D

W4

A

ESET_L

R

W2

A

WROK

P

14

H

IC

S

14

J

ID

S

15

J

LERT_L

A

P16

A

HERMTRIP_L

T

19

L

ROCHOT_L

P

16

F

VC0

S

16

H

VD0

S

16

J

VT0

S

@

PU_TRST#

A

H21 33_0402_5%@

R

1 2

H22 10K_0402_5%@

R

1 2

H23 10K_0402_5%@

R

1 2

H24 10K_0402_5%@

R

1 2

FP5 REV 0.90

ART 3 OF 13

P

P5_BGA1140~D

F

D

P_STEREOSYNC

D

C

DDP_SENSE

V

DDCR_SOC_SENSE

V

DDCR_SENSE

V

SS_SENSE_A

V

SS_SENSE_B

V

PU_TRST#_R

A

P_BLON

D

P_DIGON

D

P_VARY_BL

P0_AUXP

D

P0_AUXN

D

P0_HPD

D

P1_AUXP

D

P1_AUXN

D

P1_HPD

D

P2_AUXP

D

P2_AUXN

D

P2_HPD

D

P3_AUXP

D

P3_AUXN

D

P3_HPD

D

SVD_4

R

SVD_3

R

SVD_2

R

T

T

T

EST14

T

EST15

T

EST16

T

EST17

T

EST31

T

EST41

T

EST470

T

EST471

T

MU_ZVDD

S

ORETYPE

ANEL_BKLEN_EC

P

15

G

NVDD_R

E

15

F

NVTPWM_R

I

14

L

9

D

9

B

10

C

11

G

11

F

13

G

12

J

12

H

13

K

10

J

10

H

8

K

P_STEREOSYNC

D

15

K

14

F

12

F

10

F

P14

A

EST4

N14

A

EST5

13

F

EST6

18

G

19

H

18

F

19

F

24

W

R11

A

J21

A

K21

A

MU_ZVDDP

S

4

V

W11

A

N11

A

19

J

18

K

SS_SENSEA

V

18

J

M11

A

P

2

T

3

T

4

T

PU_TEST4

A

PU_TEST5

A

PU_TEST6

A

PU_TEST14

A

PU_TEST15

A

PU_TEST16

A

PU_TEST17

A

PU_TEST31

A

PU_TEST41

A

PU_TEST470

A

PU_TEST471

A

C13 196_0402_1%

R

1 2

C17 10K_0402_5%@

R

1 2

16

T

18

T

100

T

120

T

121

T

122

T

ANEL_BKLEN_EC[9]

DP_AUXP [16]

E

DP_AUXN [16]

E

DP_HPD [16]

E

PU_DP1_CTRL_CLK [17]

A

PU_DP1_CTRL_DATA [17]

A

PU_DP1_HPD [17]

A

PU_DP2_AUXP [36]

A

PU_DP2_AUXN [36 ]

A

PU_DP2_HPD [36]

A

PU_DP3_AUXP [33]

A

PU_DP3_AUXN [33 ]

A

PU_DP3_HPD [31,33]

A

5

T

6

T

7

T

8

T

9

T

10

T

11

T

12

T

13

T

14

T

15

T

DDP_SENSE_H [51]

V

PU_VDDSOC_SEN [53 ]

A

PU_VDDCR_SEN [53]

A

DDP_SENSE_L [51]

V

123

T

124

T

125

T

NVDD_R[9]

E

0.9VS

+

3VALW

+

C19 0_0402_5%

R

R

PU_TCK

A

H27 0_0402_5%

@

1 2

PU_TMS

A

A

D

ANEL_BKLEN_EC

P

1.8VS

+

NVDD_R

E

NVTPWM_R

I

12

PU_PWRGD_BUF

PU_RST#_BUF

A

PU_DBREQ#_R

A

D

S

123

C1 MESS138W-G_SOT323-3

Q

G

1.8VS

+

5

C5

U

1

P

C

N

4

Y

2

A

G

NL17SZ07DFT2G_SC70-5

3

SA00004BV00

1.8VS

+

5

C2

U

1

P

C

N

4

Y

2

A

G

NL17SZ07DFT2G_SC70-5

3

SA00004BV00

17

T

PU_VDD_RUN_FB_L

A

DT+

H

DT debug + HDT@

H

R

PU_TDI

A

H28 0_0402_5%

@

1 2

PU_TDO

A

@

H1 DB2J31400 L_SOD323-2

D

21

H2 DB2J31400 L_SOD323-2

D

21

@

1 2

H25 33_0402_5%

R

A

@

E

PU_DBREQ#

NVDD [16]

NVTPWM [16]

I

A

A

3VS

+

C3

R

2.2K_0402_5%

1 2

NVDD

E

NVTPWM

I

ANEL_BKLEN_EC

P

NVDD_R

E

P_STEREOSYNC

D

PU_VDD_RUN_FB_L [53]

A

PU_TRST#

A

PU_PWRGD

PU_RST#

E

P

1 2

C4

R

4.7K_0402_5%

1 2

C5

R

4.7K_0402_5%

R

100K_0804_8P4R_5%

1 2

R

1K_0402_5%

1 2

R

1K_0402_5%

@

H26 1K_0402_5%@

R

1 2

PU_TCK

A

PU_TMS

A

PU_TDI

A

PU_DBREQ#

A

PU_TDI

A

PU_DBREQ#

A

PU_TRST#

A

ANEL_BKLEN [27]

3VS

+

PC1

18

27

36

45

1.8VS

+

C10

C16

PH1

R

1 8

2 7

3 6

4 5

1K_0804_8P4R_5%

@

1 2

1 2

1 2

C251

C

@ESD@

1 2

0.1U_0402_16V7K

1.8V_ALW

+

1.8V_ALW

+

H40.01U_0402_16V7K @

C

H30.01U_0402_16V7K @

C

H20.01U_0402_16V7K HDT@

C

ecurity Classification

ecurity Classification

ecurity Classification

S

S

S

ssued Date

ssued Date

ssued Date

I

I

I

HIS SHEET OF E NGINEERING DRAWING IS THE PROPRIETARY P ROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFID ENTIAL

HIS SHEET OF E NGINEERING DRAWING IS THE PROPRIETARY P ROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFID ENTIAL

HIS SHEET OF E NGINEERING DRAWING IS THE PROPRIETARY P ROPERTY OF COMPAL EL ECTRONICS, INC. AND CONTAINS CONFID ENTIAL

T

T

T

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELEC TRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELEC TRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELEC TRONICS, INC.

C

016/01/07 2017/01/07

016/01/07 2017/01/07

016/01/07 2017/01/07

2

2

2

ompal Secret Data

ompal Secret Data

ompal Secret Data

C

C

C

Deciphered Date

Deciphered Date

Deciphered Date

T

S

S

S

Date: Sheetof

Date: Sheetof

D

Date: Sheetof

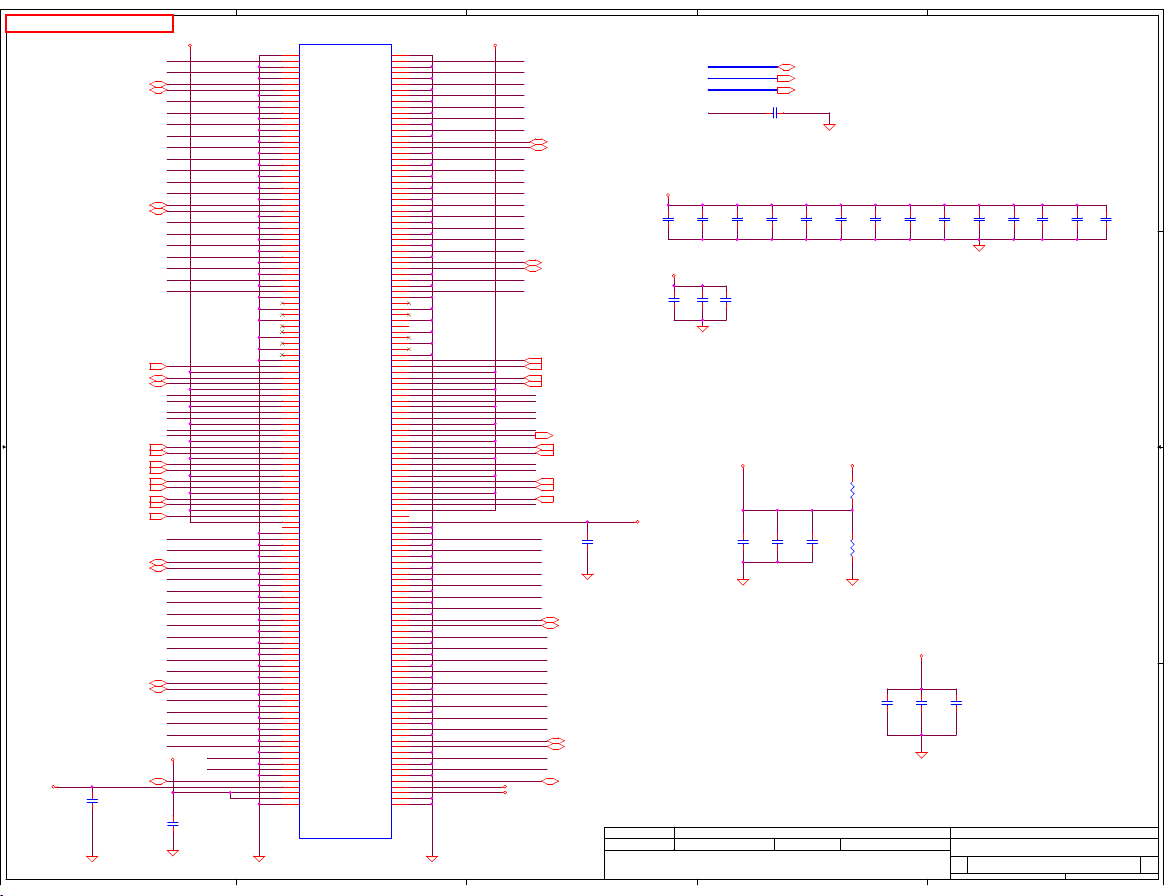

P4 DISP/MISC/HDT

P4 DISP/MISC/HDT

P4 DISP/MISC/HDT

F

F

F

ize

ocument Numb er Re v

ize

ocument Numb er Re v

ize

ocument Numb er Re v

D

D

D

ustom

ustom

ustom

C

C

C

A-F121P

A-F121P

A-F121P

L

L

L

8 61Thursday, November 09, 2017

8 61Thursday, November 09, 2017

8 61Thursday, November 09, 2017

E

.3(X02)

.3(X02)

.3(X02)

0

0

0

ompal Electronics, Inc.

ompal Electronics, Inc.

ompal Electronics, Inc.

C

C

C

itle

itle

itle

T

T

ain Func = CPU

M

A

1 2

3VS

+

1 2

1 2

B

EVSLP0_HDD

D

C62010K_0402_5% @

R

SD_DEVSLP

S

C66310K_0402_5% @

R

ATA_ACT#

S

C62110K_0402_5%

R

C

D

E

C630 0_040 2_5%MODS@

R

0A3_GPIO

S

1 2

C28 0_0402_5%@

R

12

GATE [27,51,53]

PU_FCH_PWRGD

A

C30 0_0402_5%

.1U_0402_16V7K

+

C8 100P_0 402_50V8J

C

PU_FCH_PWRGD

A

2

C9

C

1

DA_BIT_CLK_R[18]

H

DA_SDOUT_R[18]

H

DA_SYNC_R[18]

H

DA_RST#_R[18]

H

3VS

2.2K_0804_8P4R_5%

3VALW

+

C6130 10K_0402_5%

R

C6122 10K_0402_5%

R

C53 10K_0402_5%

R

C56 10K_0402_5%PTP @

R

C57 10K_0402_5%NPTP@

R

C58 10K_0402_5%

R

C59 10K_0402_5%

R

C60 10K_0402_5%@

R

C62 10K_0402_5%@

R

R

@ESD@

12

H23 close to UC1

C

2

C10

C

.1U_0402_16V7K

1

PC64

R

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

C39 0_0402_5%@

R

18

27

36

45

1 1

2 2

3 3

4 4

V

12

PU_FCH_POK [27]

A

INPU T

PU_FCH_PWRGD

A

3VALW_EC+3VALW+3VS

+

12

C33

R

@

5

C3

U

1

.7K_0402_5%

P

4

PU_FCH_PWRGD_R

A

C

N

4

Y

2

A

G

NL17SZ07DFT2G_SC70-5

3

SA00004BV00

12

EMI@

PC4

R

DA_BIT_CLK

H

1 8

DA_SDOUT

H

2 7

DA_SYNC

H

3 6

DA_RST#

H

4 5

33_0804_8P4R_5%

1 8

2 7

3 6

4 5

PU_SCLK0

A

PU_SDATA0

A

swap @04/14

TC_DET#

R

ATA_ODD_PRSNT#

S

BTN_OUT#

P

GPIO8

A

GPIO8

A

DA_SDIN1

H

DA_SDIN2

H

DA_SDIN0

H