Dell 5570 Schematics

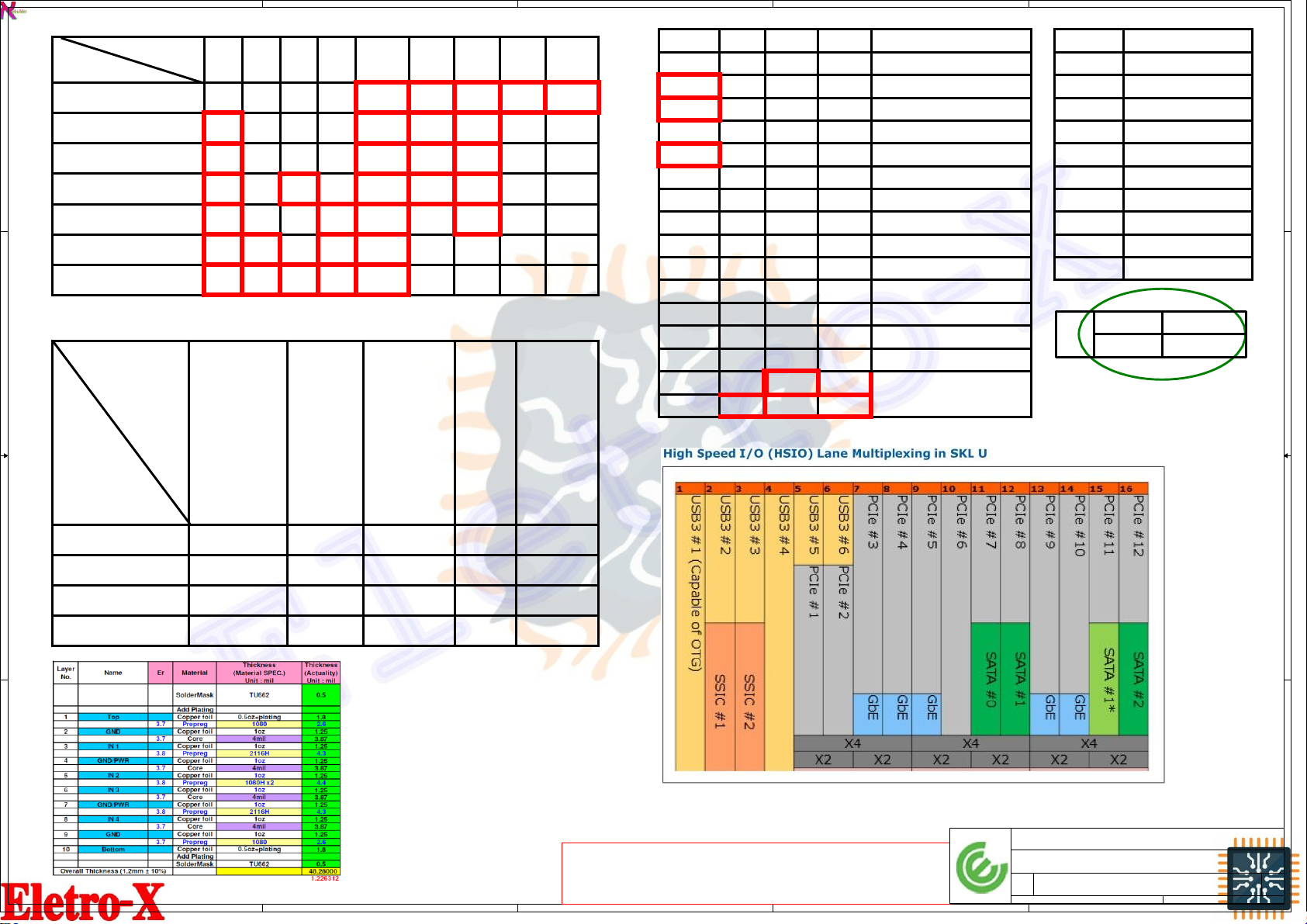

A B C D E

COMPAL CONFIDENTIAL

1 1

MODEL NAME : ADM80

PCB NO : DAA000AD000

BOM P/N : 4319XY31L01/L02

Park City 12" UMA

Skylake U

2 2

@ : Nopop Component

EMC@ : EMI, ESD and RF Component

@EMC@ : EMI, ESD and RF Nopop Component

CXDP@ : XDP Component

3 3

CONN@ : Connector Component

2015-09-25

REV : 1.0 (A00)

X76@ : SATA REDRIVER OPTION

MBPCB

Part Number

DAA000AD000

4 4

COPYRIGHT 2015

ALL RIGHT RESERVViEnD

REV: A00

PWB: 6N3K7

Description

PCB 1DK LA-C642P REV0 MB

Layout Dell logo

A B C D E

afix.com

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AN D SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT BE

TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION, NEITHER

THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY

WITHOUT DELL'S EXPRESS WRITTENCONSENT.

DELL CONFIDENTIAL/PROPRIETARY

Tiiitllle

Siiize DocumentNumber

Date: Sheet of

Compal Electronics, Inc.

CoverSheet

LA-C642P

1 60Thursday, September 24,2015

Rev

1.0

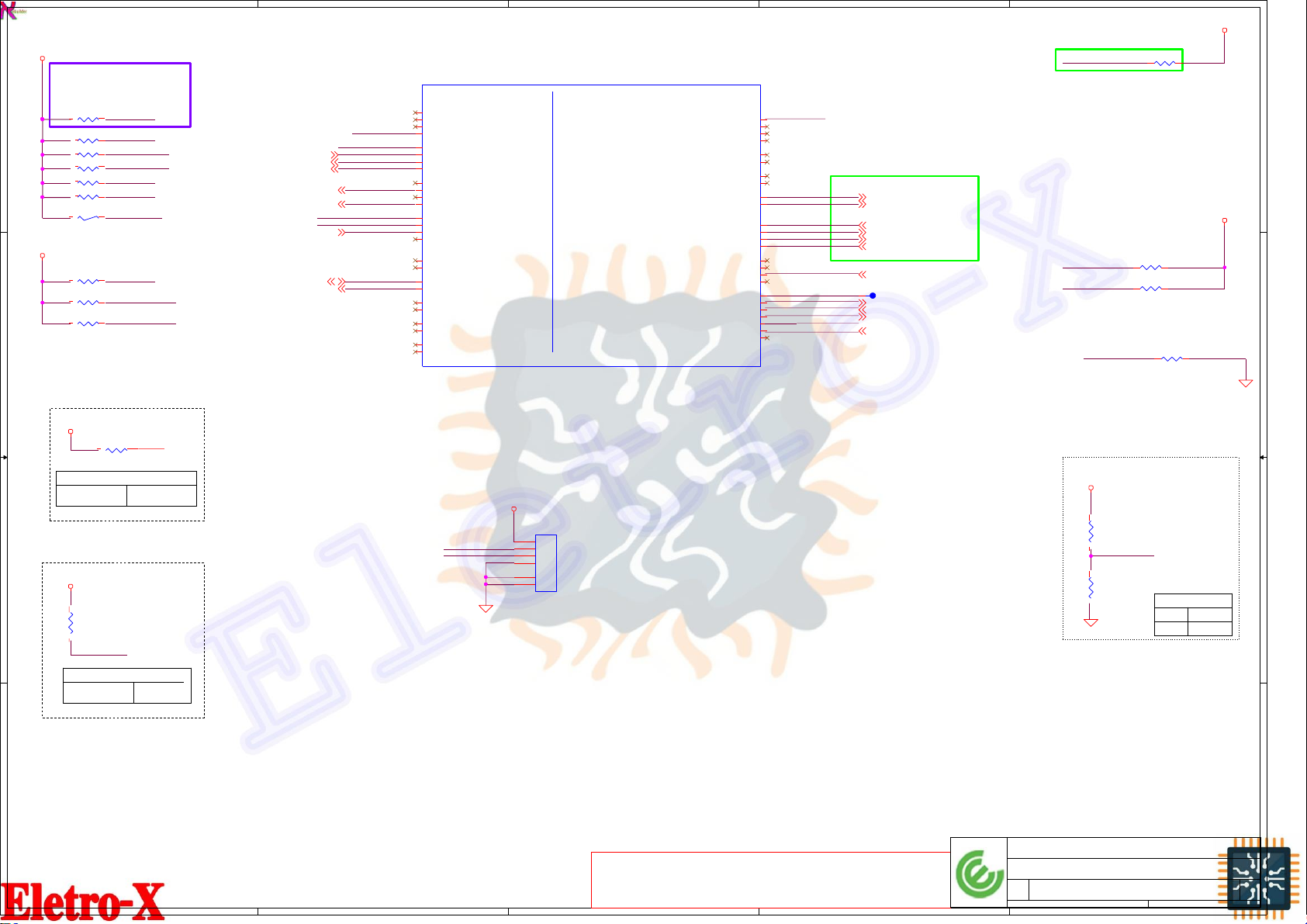

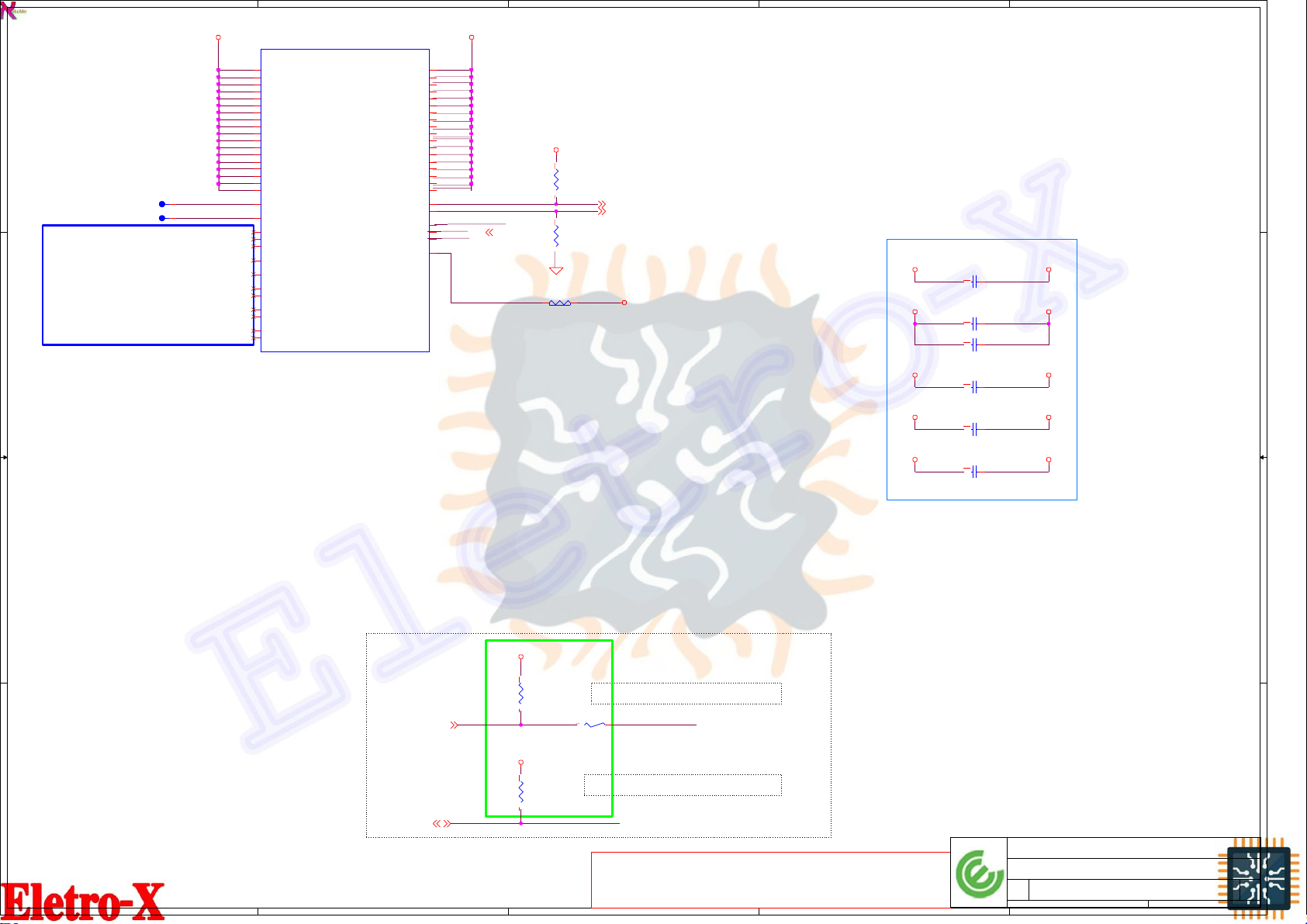

A B C D E

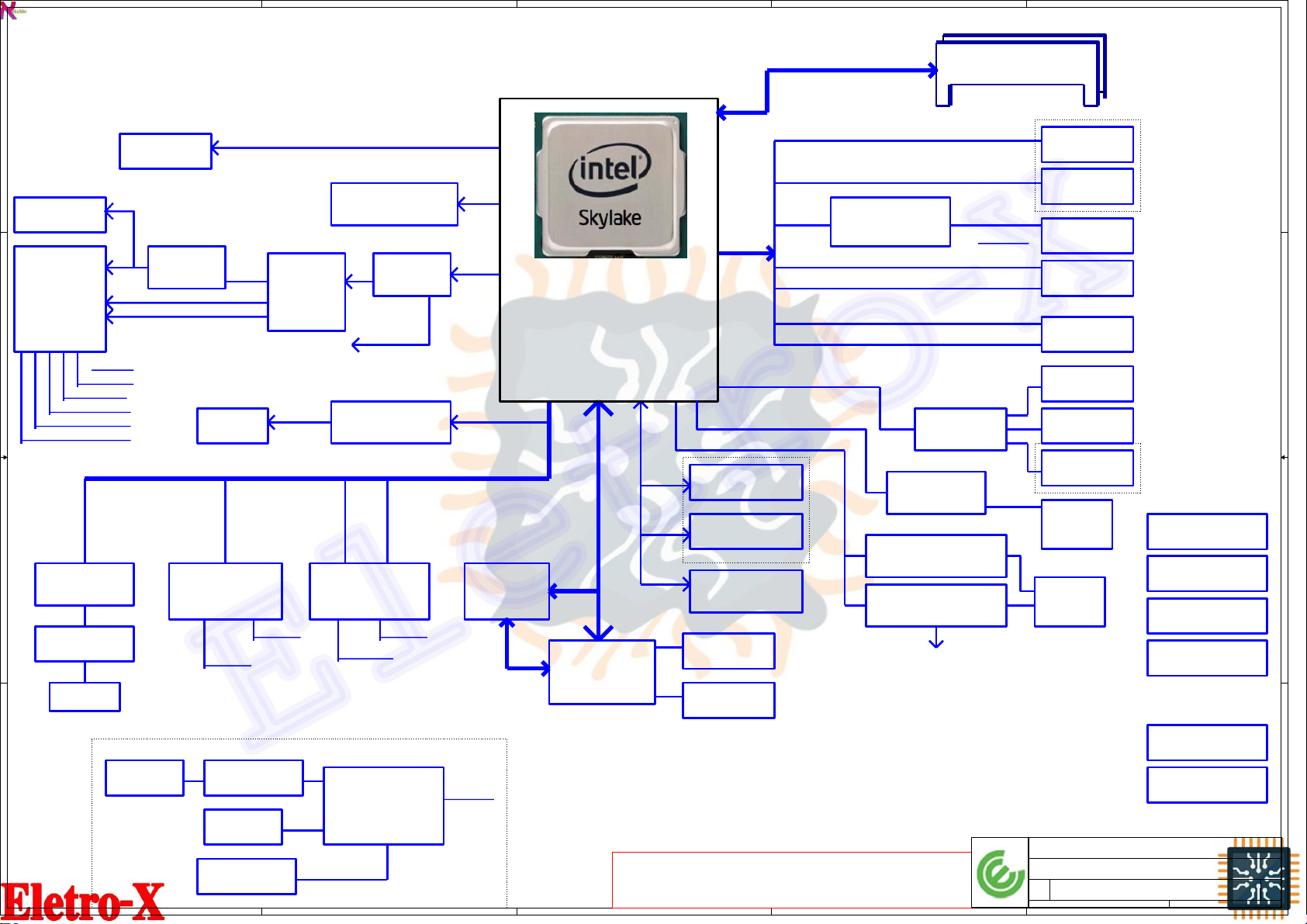

Reverse Type

Block Diagram

Memory BUS (DDR4)

2133MHz

1 1

eDP Lane x2

P24

To M2 Wi Gig card

Card reader

RTS5250

HDMI 1.4b

CONN

DPDeMUX

PS8338

WIGIGDP

DDI[1]

P22

USB

DDI[2]

P23

PCIE[10]

P28P28

SKYLAKE_U MCP

SPI

PAG E6~19

HD Audio I/F

SATA[0]/PCIE[7]

SATA[2]/PCIE[11],[12]

USB2.0[1]

PI5USB2544

USB POWERSHARE

VGA CONN

EDP CONN

P25

P26

VGA Switch

VGA

DP

DP

SYNATICS

VMM3320

P25

DOCKING

CONN

2 2

P38

DAI

LAN

SATA1

DOCK_USB2.0[5]

DOCK_USB2.0[6]

DOCK_USB3.0[5]

SD4.0

DDR4-SO-DIMM X2

BANK 0, 1, 2, 3

P20~21

USB2.0[1]_PS

P36

HDA Codec

ALC3235

USB2.0[9]

USB2.0[2]

USB3.0[1]

USB2.0[4]

USB3.0[4]

USB2.0[3]

USB3.0[3]

P30

LCD Touch

P26

Camera

P26

USB3.0 Conn

PS(RIGHT)

USB3.0 Conn

(REAR LEFT)

USB3.0 Conn

(LEFT)

INT.Speaker

Universal Jack

Trough eDP Cable

P36

P37

P37

P30

P30

Dig. MIC

W25Q128FVSIQ

PCIE[9]

PCIE[3]

PCIE[5] PCIE[6]

LPC

W25Q64CVSSIQ

3 3

Intel Jacksonville

I219LM

Transformer

P27

P27

M.2,3042 Key B

WWAN/LTE/HCA

P29

USB2.0[10]

USB3.0[5]

M.2,3030 Key A

WLAN+BT/WIGIG

USB2.0[8]

WIGIG_DP

P29

SMSCSIO

ECE5048

BCBUS

P31

TPM2.0

NPCT650JAAYX

KB/TP CONN

SMSCKBC

P39

P33

P8

P8

SATA REPEATER

P42

SATA/PCIE REPEATER X1

PS8555

P34

SATA/PCIE REPEATER X1

PS8555

P34

Spindle

HDDConn

Key M

HDD Conn

P42

P35

reserve PCIE signal for SATA express HDD

MEC5085

RJ45

P27

P32

FAN CONN

P32

Trough eDP Cable

LID SWITCH

USH CONN

CPU&PCH XDP Port

AUTOMATIC POWER

SWITCH(APS)

LED/ B

P33

P14

P11

DC/DC Interface

Smart Card

4 4

A B C D E

TDA8034HN

RFID/NFC

Fingerprint

CONN

SPI

SPI

USH TPM1.2

BCM58102

USB2.0[7]

USHboard

P30

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT BE

TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION, NEITHER

THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY

WITHOUT DELL'S EXP RESS WRITTENCONSENT.

DELL CONFIDENTIAL/PROPRIETARY

Tiiitllle

Siiize DocumentNumber

Date: of

Compal Electronics,Inc.

POWER ON/OFF

SW & LED

Blockdiagram

LA-C642P

Sheet

2

P40

P41

Rev

1.0

60Thursday, September 24, 2015

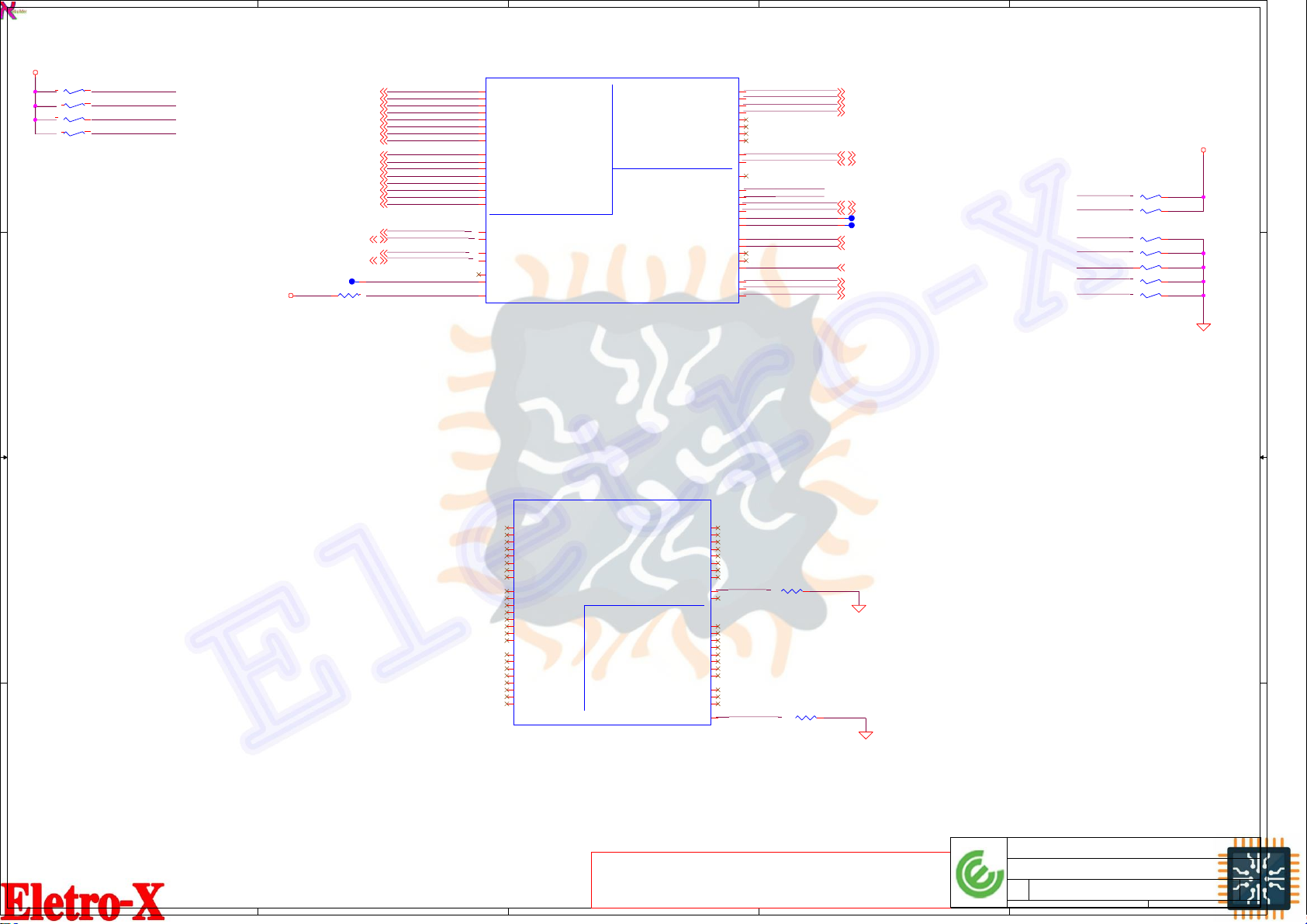

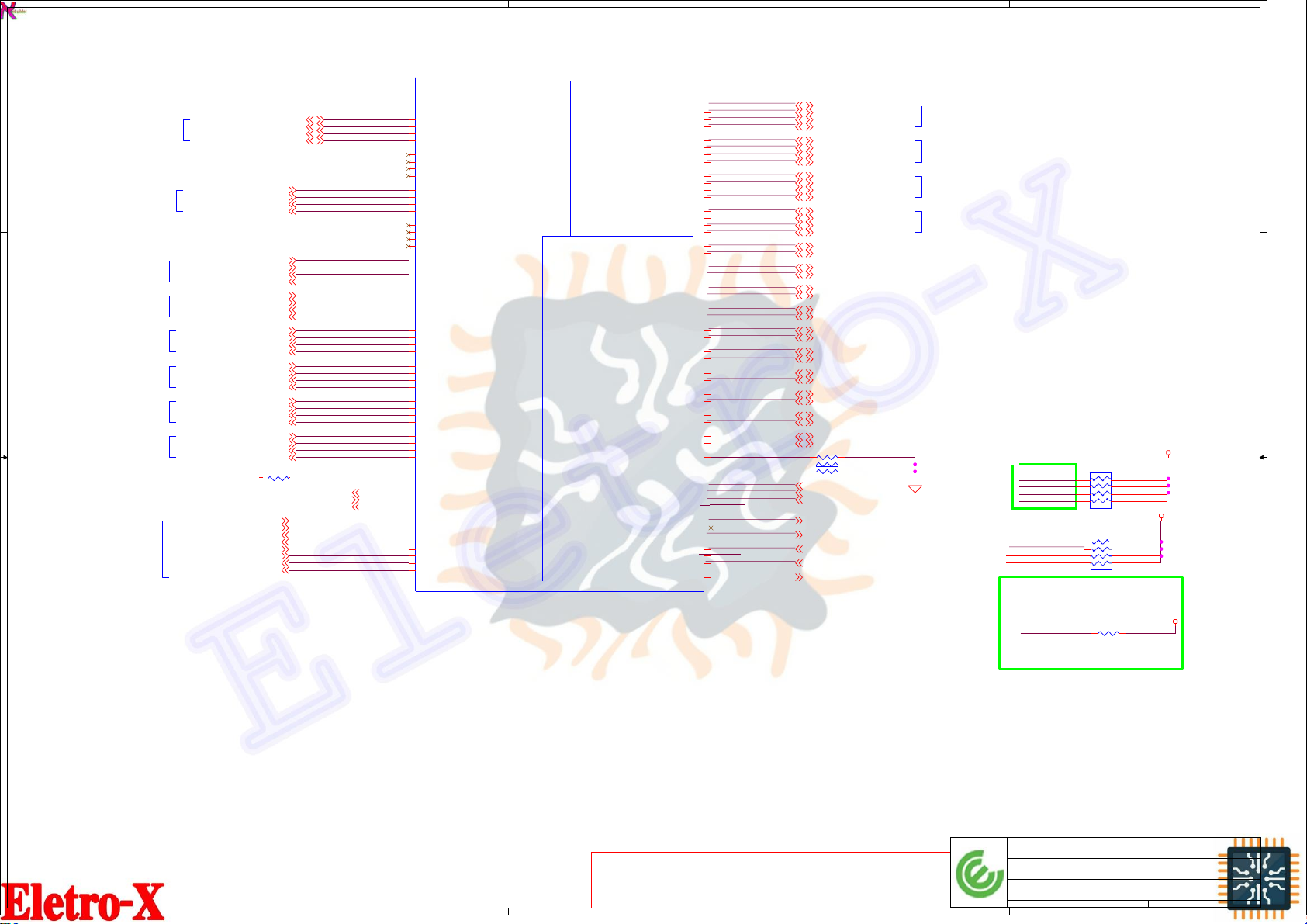

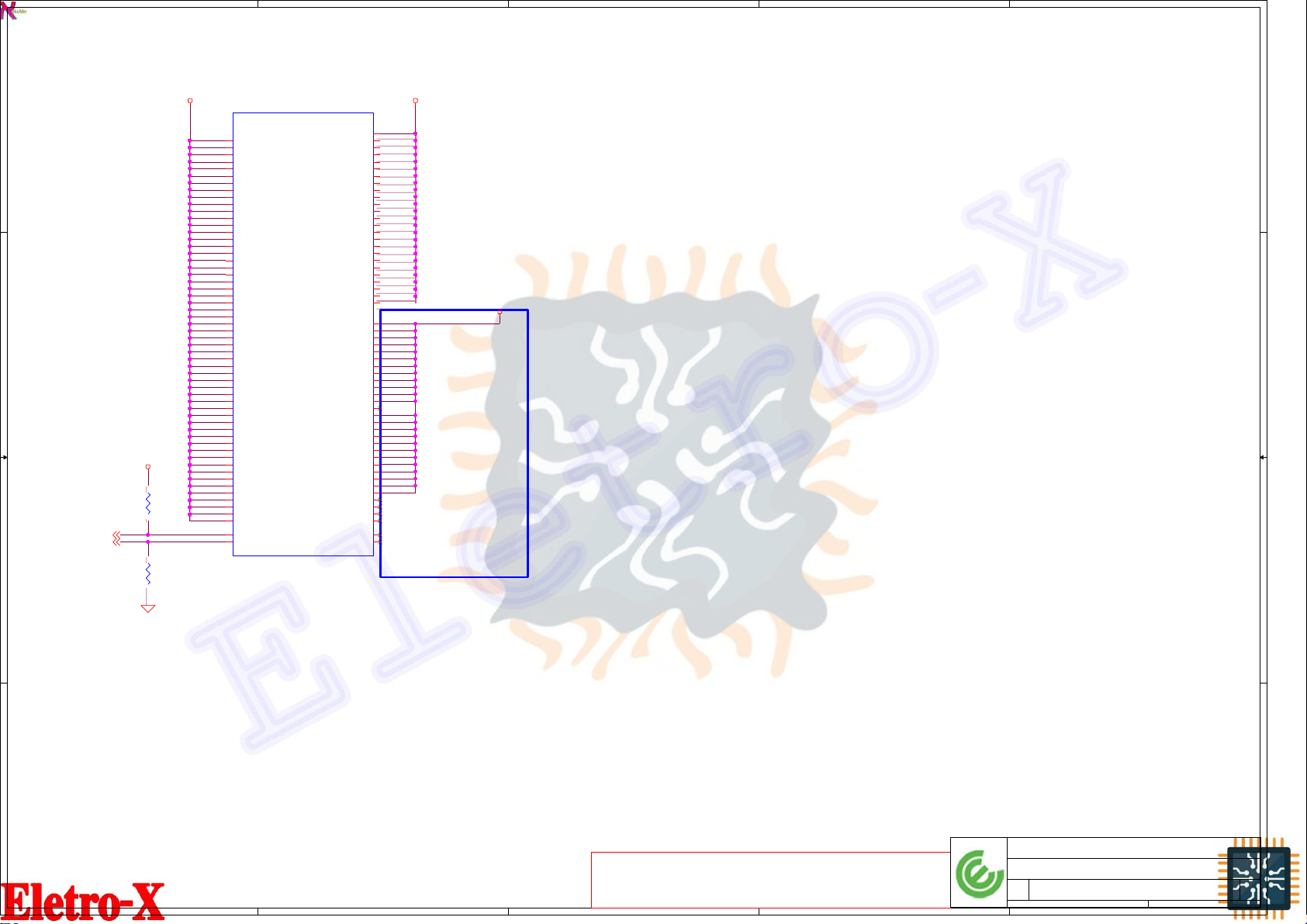

5 4 3 2 1

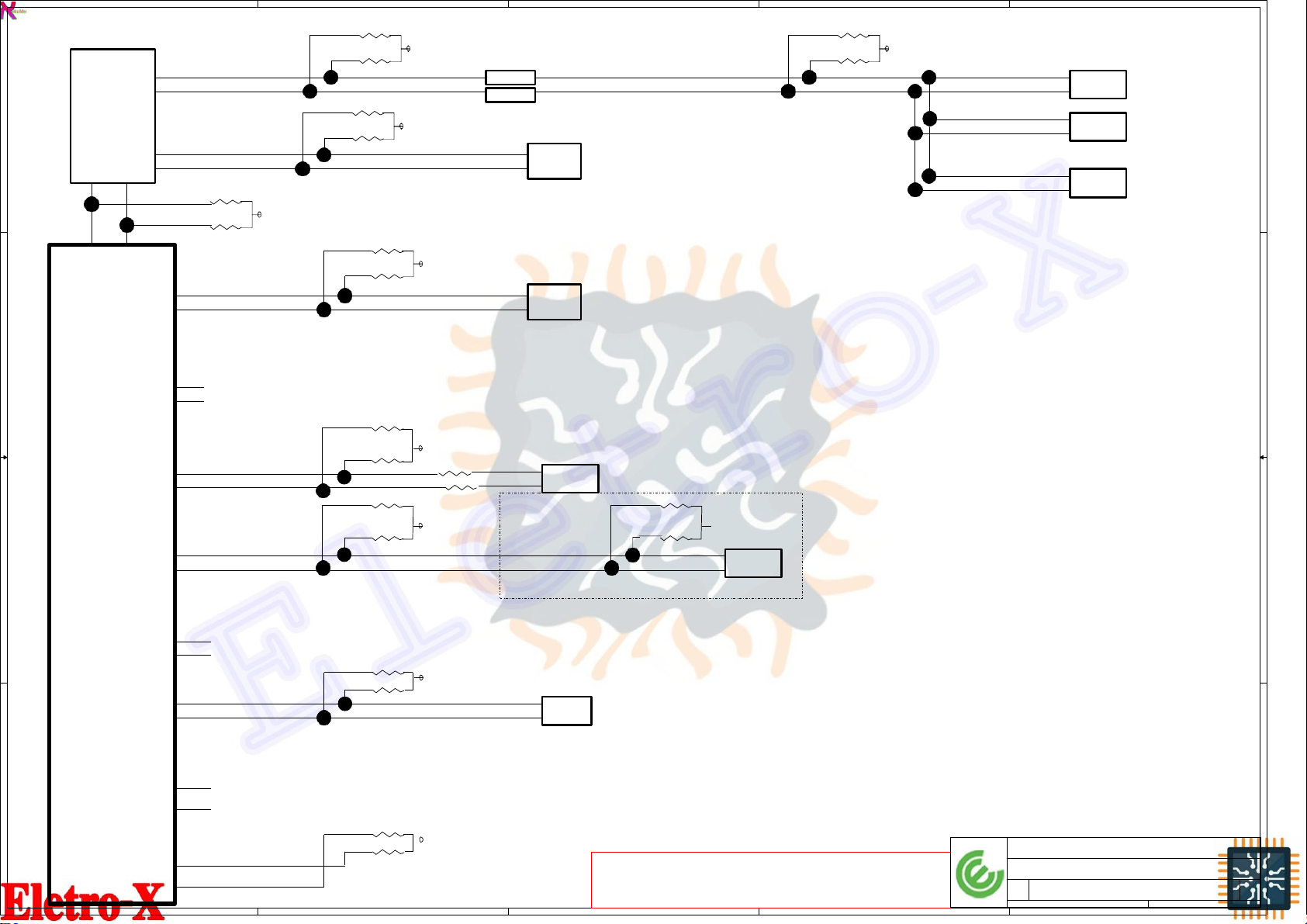

RT8207M

(PU201)

SIO_SLP_S4#

+1.2V_MEM

ADAPTER

(PU401)

SIO_SLP_SUS#

RUN_ON

SIO_SLP_SUS#

ALWON

ALWON

+1.0V_PRIM

+1.0VS_VCCIO

TPS22961

(UV28)

+1.0V_PRIM_CORE

+5V_ALW

+5V_ALW2

+3.3V_RTC_LDO

+3.3V_ALW2

+1.0V_RUN_VMM

D D

SYX198D

(PU301)

TPS62134A

CHARGER

BQ24777

(PU801)

+PWR_SRC

HUB_LP_EN

TPS62134B

(PU402)

SYX198C

BATTERY

C C

(PU100)

SYX198B

(PU100)

+3.3V_ALW

ISL95857

(PU602)

AO6405

(QV1)

LDOIN

RT8207

(PU201)

+0.6V_DDR_VTT

TPS22961

(UZ20)

TPS22961

(UZ19)

TPS22961

(UZ21)

TPS22967

(UZ23)

EM5209

(UZ4)

EM5209

(UZ5)

PI5USB2544

(UI3)

SY6288

(UI1)

SY6288

(UI2)

SY8032A

(PU501)

EM5209

(UZ2)

@SIO_SLP_WLAN#

MPHYP_PWR_EN

SIO_SLP_S3#

SIO_SLP_S4#

3.3V_HDD_EN

RUN_ON

AUD_PWR_EN

USB_PWR_SHR_VBUS_EN

USB_PWR_EN1#

USB_PWR_EN2#

SIO_SLP_SUS#

SIO_SLP_LAN#

3.3V_WWAN_EN

+1.0V_MPHYGT

+1.0V_VCCSTG

+1.0V_VCCST

+5V_HDD

+5V_RUN

+5V_RUN_AUDIO

+USB_LEFT_PWR

+USB_REAR_PWR

+1.8V_PRIM

+3.3V_LAN

+3.3V_WWAN

+5V_USB_CHG_PWR

AP7175SP

(PU1500)

SIO_SLP_S4#

0.675_DDR_VTT_ON

CPU PWR

PCH PWR

GPU PWR

Peripheral Device PWR

+2.5V_MEM

(QV8)

3.3V_TS_EN

+3.3V_RUN

3.3V_CAM_EN#

+3V_TSP

+1.5V_RUN

+3.3V_CAM

+3.3V_HDD

DELL CONFIDENTIAL/PROPRIETARY

Tiiitllle

Siiize DocumentNumber

Date:

Compal Electronics,Inc.

Powerrails

Thursday, September 24, 2015

LA-C642P

Rev

4

Sheet

1

1.0

60

of

LP2301

AP7175SP

(PU502)

LP2301A

(QZ1)

(UZ4)

AUX_EN_WOWL

@SIO_SLP_WLAN#

RUN_ON

AUD_PWR_EN

A_ON

SIO_SLP_SUS#

@PCH_ALW_ON

CV2_ON

ENVCC_PCH

+3.3V_WLAN

+3.3V_RUN

+3.3V_RUN_AUDIO

+3.3V_M

+3.3V_ALW_PCH

+3.3V_CV2

+LCDVDD

USH/B

IMVP_VR_ON

B B

IMVP_VR_ON

IMVP_VR_ON

+BL_PWR_SRC

+VCC_GT+VCC_SA

+VCC_CORE

EN_INVPWR

EM5209

(UZ3)

EM5209

(UZ5)

TPS22967

(UZ8)

EM5209

TPS22967

A A

(UZ18)

AP2821

(UV24)

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT BE

TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION, NEITHER

THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DE LL'S EXPRESS WRITTENCONSENT.

5 4 3 2

5 4 3 2 1

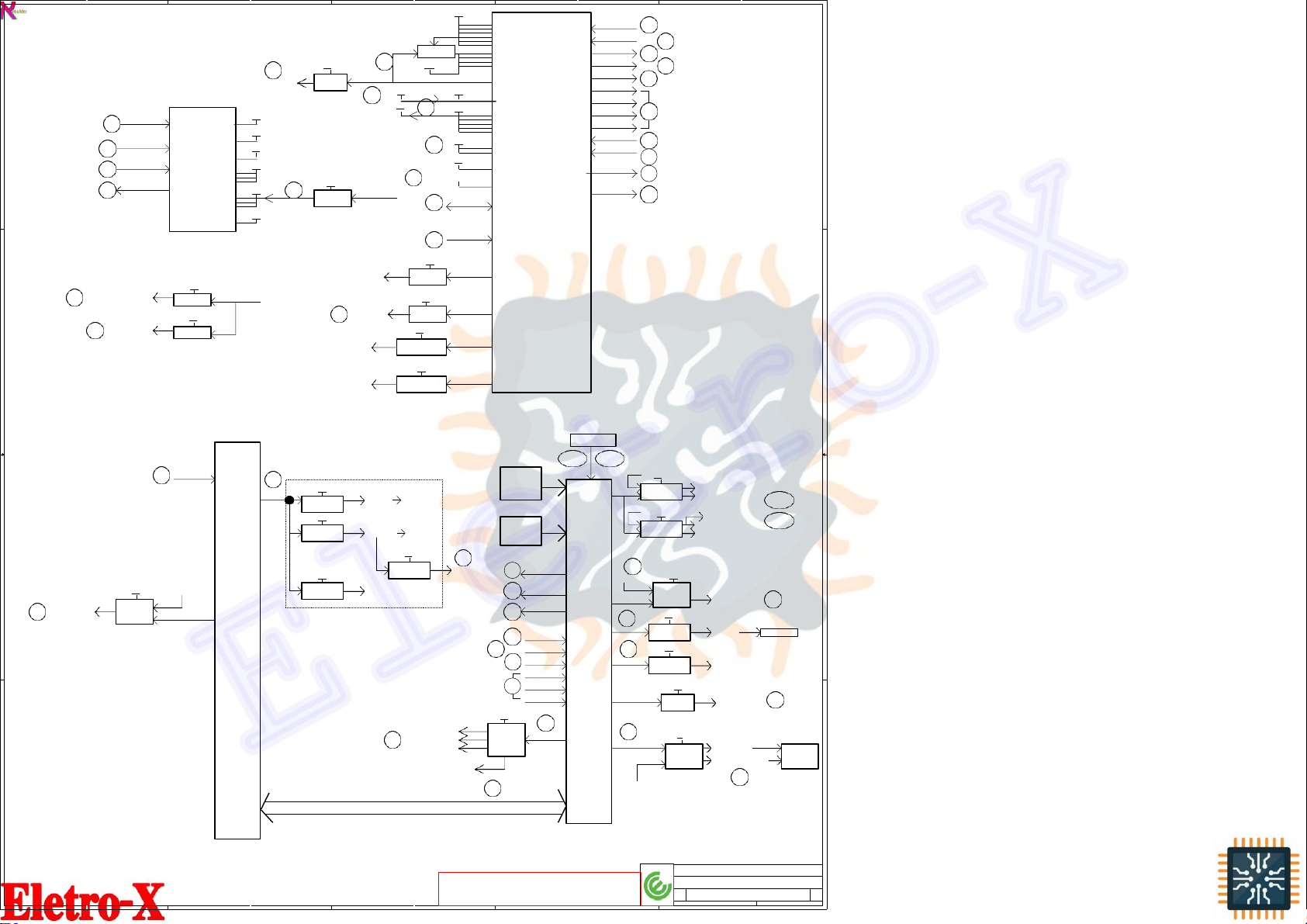

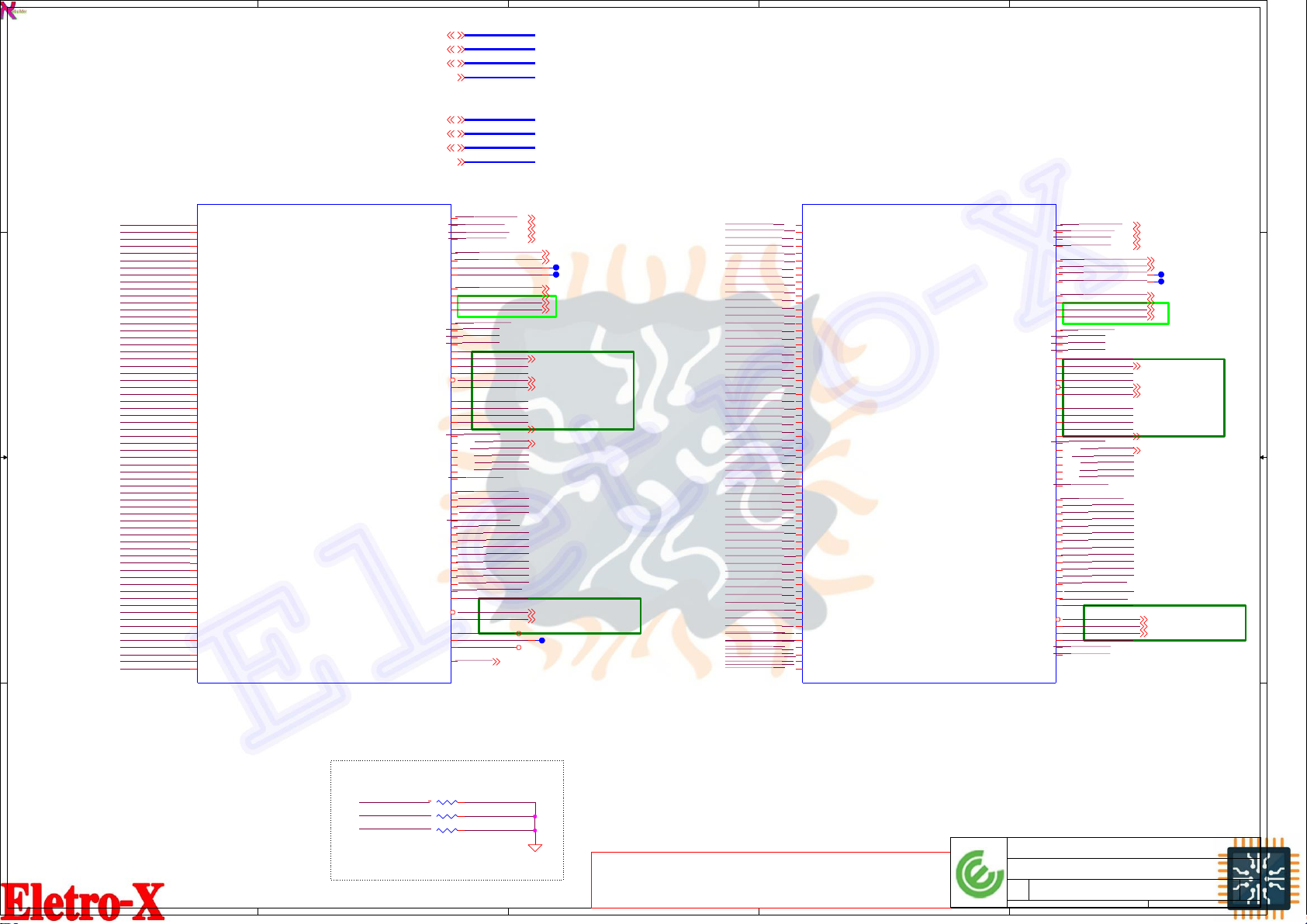

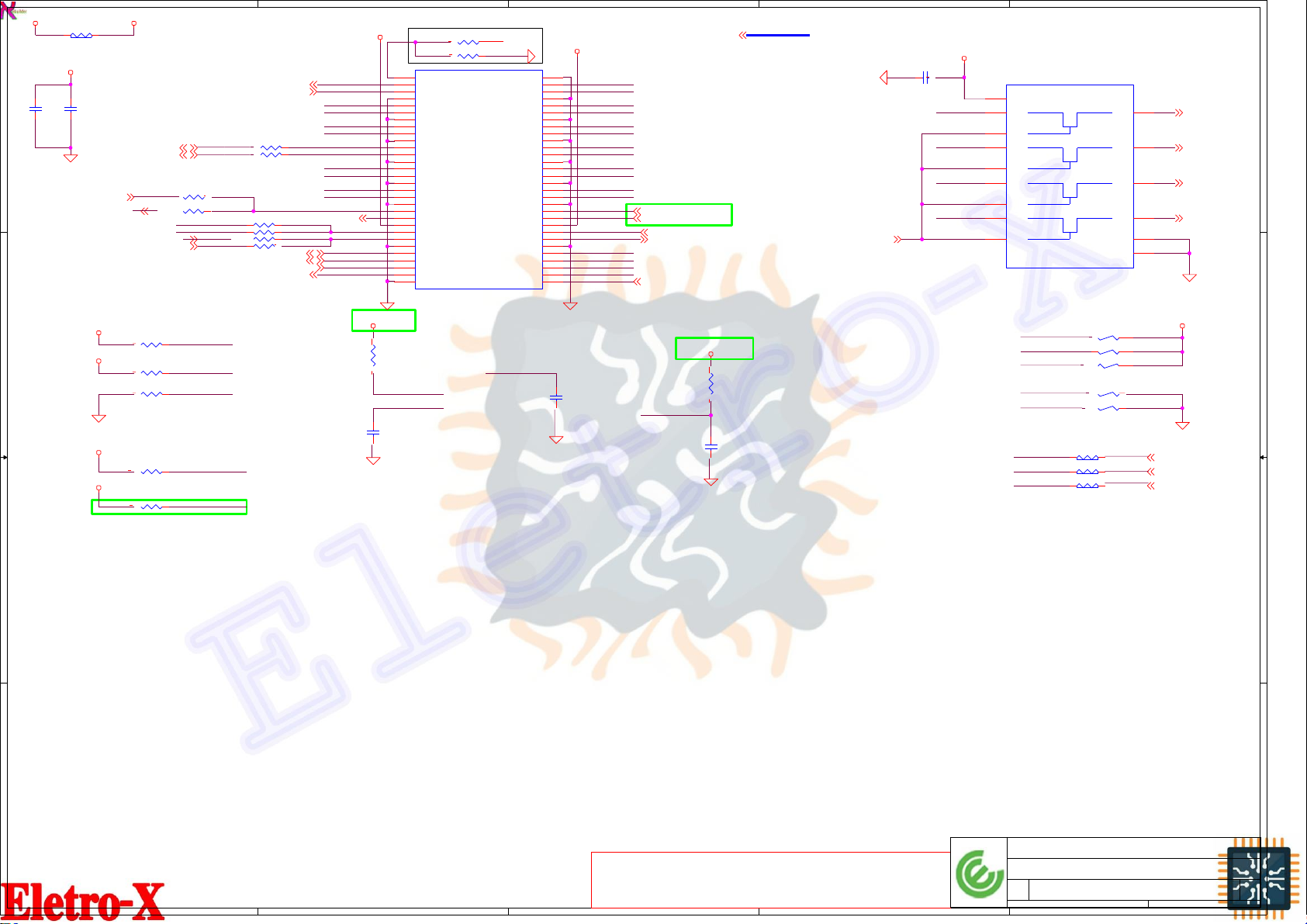

1K

+3.3V_ALW_PCH

2.2K

2.2K

+3.3V_ALW_PCH

+3.3V_ALW

2N7002

2N7002

127

129

28

31

LOM

Dock

R7

R8

MEM_SMBCLK

MEM_SMBDATA

499

1K

D D

SKL-U

R9

W2

SML0_SMBCLK

499

SML0_SMBDATA

V3W3

B4

A3

B5

A4

1K

1K

DOCK_SMB_CLK

DOCK_SMB_DAT

+3.3V_ALW_PCH

SML1_SMBDATA

SML1_SMBCLK

B6A5

3A

3A

1A

1A

C C

1B

1B

2.2K

2.2K

+3.3V_RUN

202

200

202

200

DIMMA

DIMMB

53

51

XDP

2.2K

KBC

A56

1C1CB59

PBAT_SMBCLK

PBAT_SMBDAT

2.2K

@2.2K

A50

B53

USH_SMBCLK

USH_SMBDAT

B B

MEC 5085

1E

1E

@2.2K

+3.3V_ALW

100 ohm

100 ohm

+3.3V_ALW

7

6

BATTERY

CONN

2.2K

2.2K

+3.3V_CV2

M9

L9

USH

USH/B

A49

2B

B52

2B

B50

A47

B7

A7

B48

B49

CHARGER_SMBCLK

CHARGER_SMBDAT

GPU_SMBDAT

GPU_SMBCLK

1G

1G

A A

2D

2D

2A

2A

5 4 3 2

10K

10K

2.2K

2.2K

+3.3V_ALW

+3.3V_RUN

9

8

Charger

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT BE

TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION, NEITHER

THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DE LL'S EXPRESS WRITTENCONSENT.

Tiiitllle

Siiize DocumentNumber

Date:

Compal Electronics,Inc.

SMbus Blockdiagram

Thursday, September 24, 2015

LA-C642P

Rev

5

Sheet

1

1.0

60

of

5

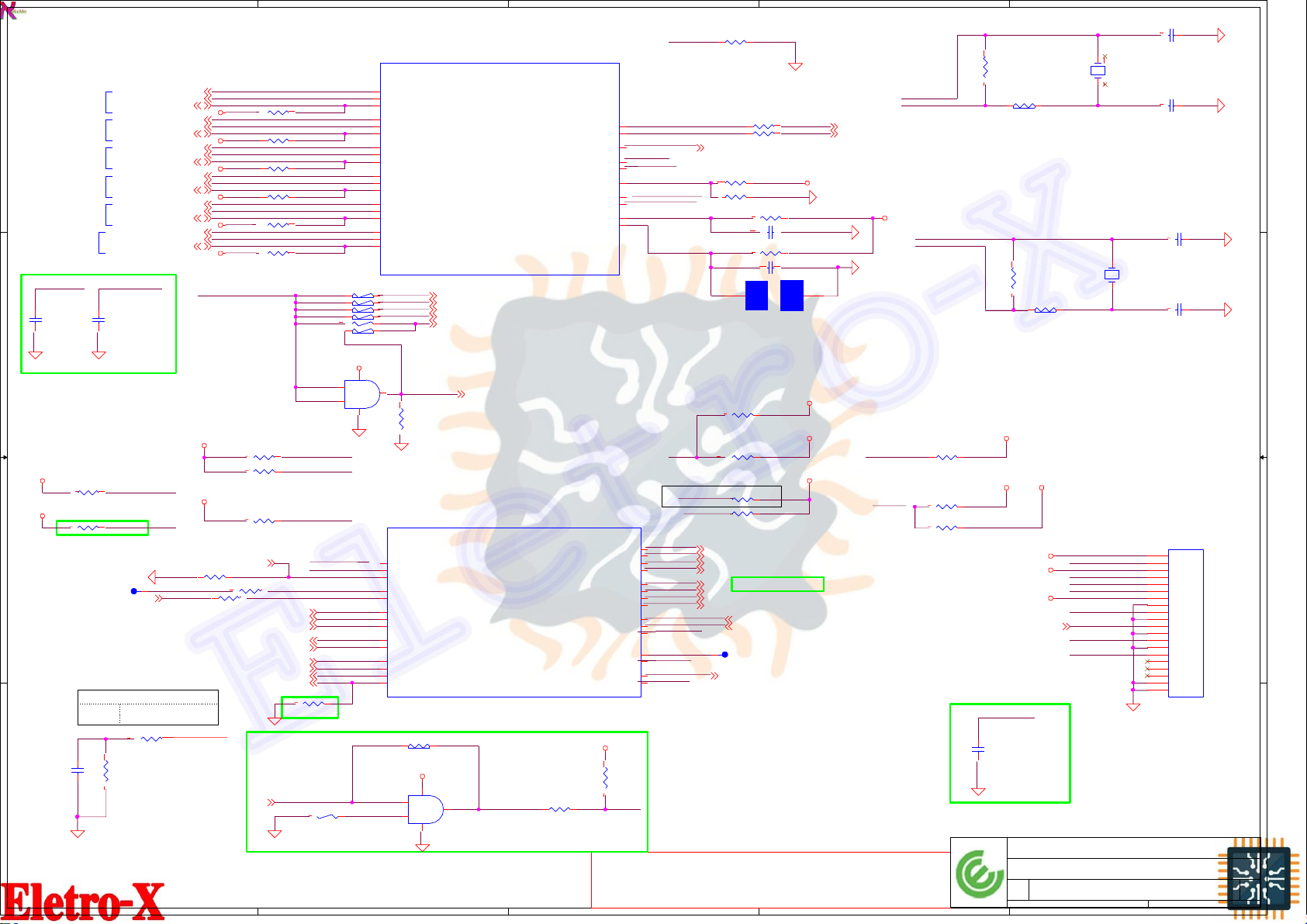

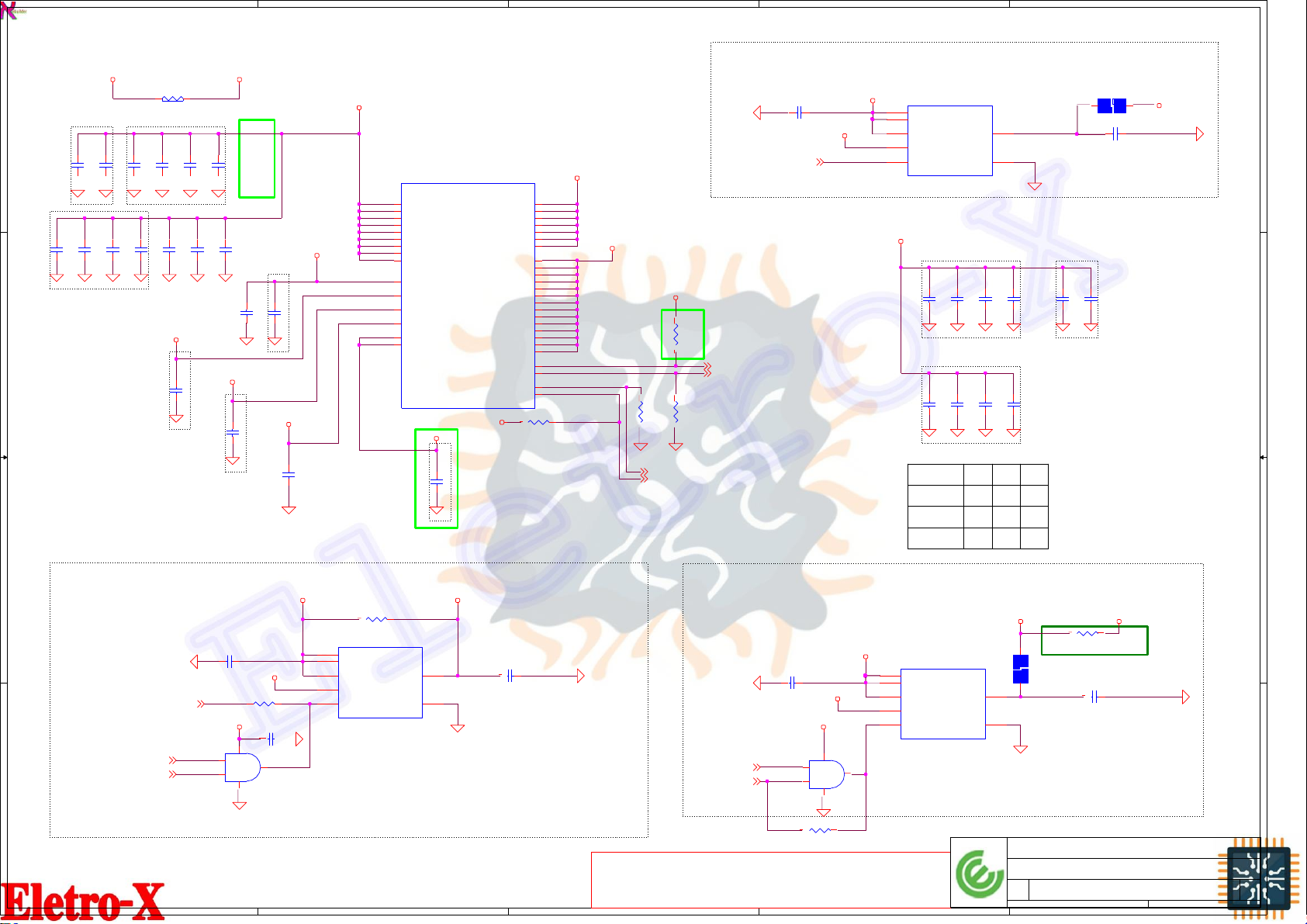

Timing Diagram for S5 to S0 mode

D D

5

C C

B B

+3.3V_WLAN

11

A A

VCCST_PWRGD

12

H_CPUPWRGD

15

PCH_PLTRST#

17

0.675V_DDR_VTT_ON

12

+1.0V_PRIM_CORE

+1.8V_PRIM

5

+3.3V_ALW

EM5209VF

VCCST_PWRGD VCC

PROCPWRGD

PLTRST#

DDR_VTT_CNTL

+PWR_SRC

TLV62130

+3.3V_ALW

TLV62130

SIO_SLP_WLAN#

11

@SIO_SLP_WLAN#

AUX_EN_WOWL

CPU

VCCIO

VCCGT

VDDQ

VDDQC

VCCPLL_OC

VCCST

VCCSTG

VCCPLL

VCCSA

SIO_SLP_SUS#

SIO 5048

4

6

+1.0V_PRIM

+VCC_CORE

+1.0VS_VCCIO

+VCC_GT

+1.35V_MEM

+1.0V_VCCST

+VCC_SA

11

RUN_ON

10

+PWR_SRC

SYX198

+1.0V_PRIM

TPS22961

+5V_ALW

EM5209VF

+3.3V_ALW

EM5209VF

+PWR_SRC

TLV62130

3

+1.0V_PRIM

TPS22961

6

+1.0V_MPHYGT

+3.3V_ALW +3.3V_ALW_DSW

3 VCCDSW_3P3

+3.3V_SPI 5+3.3V_ALW_PCH

+1.8V_PRIM

5

+RTC_CELL

5

SIO_SLP_S4#

+1.0V_PRIM_CORE

17

4

+3.3V_ALW

11

+LCDVDD

+3.3V_LAN

+5V_TSP

+5V_RUN +5V_HDD

+3.3V_RUN +3.3V_HDD

+1.0VS_VCCIO

+3.3V_RUN

APL5930

13

AP2821K

+3.3V_ALW

EM5209VF

+5V_RUN

LP2301ALT1G

+3.3V_RUN

LP2301ALT1G+3.3V_CAM

+VCC_SA

+VCC_CORE

+VCC_GT

BC BUS

EXT_PWR_GATE#

PCH_PLTRST#

PCH_DPWROK

ENVDD_PCH

SIO_SLP_LAN#

3.3V_TS_EN

3.3V_CAM_EN#

11

+1.5V_RUN

PCH_PWROK

VCCPRIM_1P0

VCCPRIM_CORE

DCPDSW_1P0

VCCMPHYAON_1P0

VCCAPLL_1P0

VCCCLK1~6

VCCMPHYGT_1P0

VCCSRAM_1P0

VCCAMPHYPLL_1P0

VCCAPLLEBB

EXT_PWR_GATE#

VCCHDA

VCCSPI

VCCPRIM_3P3

VCCPGPPA~E

VCCRTCPRIM

VCCPGPPG

VCCATS

VCCRTC

VCCPRIM_CORE

PLTRST#

DSW_PWROK

EDP_VDDEN

SLP_LAN#

GPP_B21

GPD7

ADAPTER

BATTERY

7

4

16

5

10

9

11

+PWR_SRC

ISL95857

14

PCH

SLP_WLAN#/GPD9

PCH_RSMRST#

PCH_DPWROK

RESET_OUT#

SIO_SLP_SUS#

SIO_SLP_S4#

SIO_SLP_S5#

SIO_SLP_LAN#

SIO_SLP_S3#

SIO_SLP_A#

12

IMVP_VR_ON

2

PWRBTN#

RSMRST#

SLP_SUS#

SLP_S5#

SLP_S4#

SLP_S3#

SLP_A#

SLP_LAN#

SYS_PWROK

PCH_PWROK

VCCST_PWRGD

PROCPWRGD

Power Button

1BAT 2AC

EC 5085

SIO_PWRBTN#

PCH_RSMRST#

SIO_SLP_SUS#

SIO_SLP_S5#

SIO_SLP_S4#

SIO_SLP_S3#

SIO_SLP_A#

SIO_SLP_LAN#

SIO_SLP_WLAN#

RESET_OUT#

PCH_PWROK

VCCST_PWRGD

H_CPUPWRGD

ALWON

SIO_SLP_SUS#

@PCH_ALW_ON

11

A_ON

SUS_ON

EN_INVPWR

SUS_ON

0.675V_DDR_VTT_ON

10

10

12

5

8

7

5

9

10

11

16

14

15

+PWR_SRC

SYX198

+PWR_SRC

SYX198

+3.3V_ALW

EM5209VF

+3.3V_ALW

+3.3V_ALW

EM5209VF

+PWR_SRC

AO6405

+PWR_SRC

RT8207MZ

+5V_ALW2

+5V_ALW

+3.3V_RTC_LDO

+3.3V_ALW2

+3.3V_ALW

+3.3V_ALW_PCH

+3.3V_MEM5209VF

+3.3V_SUS

+BL_PWR_SRC

+1.35V_MEM

+0.675V_DDR_VTT

12

1

1BAT

2AC

5

Popoption

+3.3V_SPI

18

VDDQ

DDR

VTT

DELL CONFIDENTIAL/PROPRIETARY

PROPRI ETARY NOTE: THIS SHE ET OF ENGI NEERING DR AWING AND SPECIFICAT IONS CONTA INS

CONFID ENTIAL TRA DE SECRET AND OTHER PROPRIETA RY INFORMA TION OF DE LL INC. (" DELL") THI S

DOCUME NT MAY NOT BE TRANS FERRED OR COPIED WIT HOUT THE E XPRESS WRI TTEN AUTHO RIZATION O F

DELL. IN ADDITION , NEITHE R THIS SHE ET NOR THE INFORMATI ON IT CONT AINS WAY B E USED BY OR

DISCLO SED TO ANY THIRD PA RTY WITHOU T DELL'S E XPRESS WRI TTEN CONSEN T.

5

4

3

2

Compal Electronics, Inc.

Tiiitttllle

Siiize DocumentttNumberrr

Dattte::: Thurrrsday,,, Septttemberrr 24,,,2015 Sheettt 55 offf

PowerSequence

LA-C631P,C641P

1

Rev

1...0

60

5 4 3 2 1

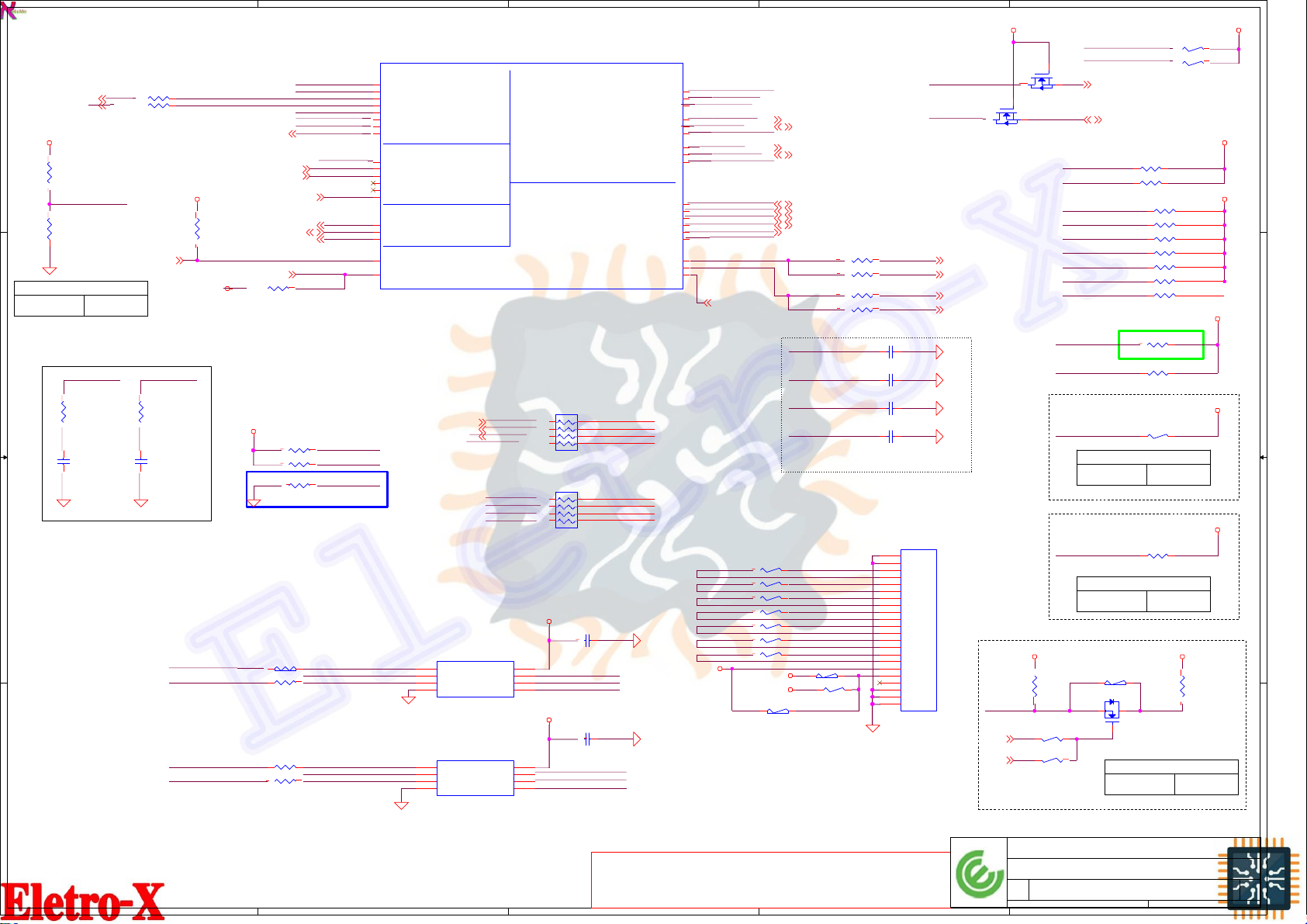

POWER STATES

Signal

State

S0 (Full ON) / M0 HIGH HIGH HIGH HIGH ON ON ON ON ON

D D

S3 (Suspend to RAM) / M3 LOW HIGH HIGH HIGH ON ON ON OFF OFF

S4 (Suspend to DISK) / M3 LOW LOW HIGH HIGH ON ON OFF OFF OFF

S5 (SOFT OFF) / M3 LOW LOW LOW HIGH ON ON OFF OFF OFF

S3 (Suspend to RAM) / M-OFF LOW HIGH HIGH LOW ON OFF ON OFF OFF

S4 (Suspend to DISK) /M-OFF LOW LOW HIGH LOW ON OFF OFF OFF OFF

S5 (SOFT OFF) / M-OFF LOW LOW LOW LOW ON OFF OFF OFF OFF

SLP

S3#

SLP

S4#

SLP

S5#

SLP A#ALWAYS

PLANE

M

PLANE

SUS

PLANE

RUN

PLANE

CLOCKS

USB3.0 SSIC PCIE SATA DESTINATION

USB3.0-1 JUSB3-->Right

USB3.0-2 SSIC-1 EDOCK PORT1

USB3.0-3 SSIC-2 JUSB1-->LEFT

USB3.0-4 JUSB2-->Rear LEFT

USB3.0-5 PCIE-1 M2 3042(WWAN)

USB3.0-6 PCIE-2 NA

PCIE-3

PCIE-4

M.2 3042(HCA or QCA LTE)

NA

PCIE-5 M.2 3030(WLAN)

PCIE-6 M.2 3030(WIGIG)

PCIE-7 SATA-0 HDD SATA

PM TABLE

C C

power

plane

State

S0 ON ON ON ON ON

+5V_ALW

+3.3V_ALW

+3.3V_ALW_DSW

+3.3V_ALW_PCH

+RTC_CELL

+1.8V_PRIM +2.5V_MEM +1.5V_RUN

+1.0V_PRIM

+1.0V_PRIM_CORE

+5V_ALW2

+3.3V_ALW2

+3.3V_RTC_LDO

+1.0V_MPHYGT

+3.3V_SUS

+1.2V_MEM

+1.0V_VCCST

+5V_RUN

+3.3V_RUN

+0.6V_DDR_VTT

+3.3V_M

(M-OFF)

+3.3V_M

+VCC_CORE

+VCC_GT

+1.0VS_VCCIO

+VCC_SA

PCIE-8 SATA-1 EDOCK E-SATA

PCIE-9 LOM

PCIE-10 Card Reader

PCIE-11

PCIE-12

SATA-1*

SATA-2

M.2 Socket 3 (Key M)

(PCIex2 or SATA)

USB PORT# DESTINATION

1 JUSB1-->Right

2 Camera

3 JUSB2-->LEFT

4 JUSB3-->Rear LEFT

5 EDOCK PORT1

6 EDOCK PORT2

7 USH

8

M.2 304230(BT)

9 Touch Screen

10 M2 3042(WWAN)

USH

0

1

BIO

NA

Check

B B

A A

S3 ON ON OFF ON OFF

S5 S4/AC ON OFF OFF ON OFF

S5 S4/AC doesn't exist OFF OFF OFF OFF OFF

DELL CONFIDENTIAL/PROPRIETARY

PROPR IETARY NOT E: THIS SHE ET OF ENG INEERING DRAW ING AND SPECI FICATIONS CO NTAINS CO NFIDENTIAL

TRADE SECRET AND OTH ER PROPR IETARY I NFORM ATION OF DE LL INC. (" DELL") THIS DOCUMEN T MAY NOT B E

TRANSFE RRED OR COP IED WITHOU T THE EX PRESS WRITTEN A UTHOR IZATION OF DELL. I N ADDI TION, NEITHER

THIS SHE ET NOR THE INF ORMATI ON IT CONTAI NS WAY BE U SED BY OR DISCLOSED TO A NY THI RD PA RTY

WITHOUT DELL'S E XPRE SS WRITTEN CONS ENT.

5 4 3 2 1

Tiiitllle

Siiize Document Number

Date: Sheet of

Compal Electronics, Inc.

Port assignment

Thursday, Septem ber 24,2015 3 60

LA-C642P

Rev

1.0

5 4 3 2 1

+3.3V_RUN

CPU_DP1_CTRL_CLK

1

2

2

2

2

2.2K_0402_5%

CPU_DP1_CTRL_DATA

1

2.2K_0402_5%

CPU_DP2_CTRL_CLK

1

2.2K_0402_5%

CPU_DP2_CTRL_DATA

1

2.2K_0402_5%

+1.0VS_VCCIO

RC175

RC178

D D

RC176

RC177

<22> CPU_DP1_N0

<22> CPU_DP1_P0

<22> CPU_DP1_N1

<22> CPU_DP1_P1

<22> CPU_DP1_N2

<22> CPU_DP1_P2

<22> CPU_DP1_N3

<22> CPU_DP1_P3

<23> CPU_DP2_N0

<23> CPU_DP2_P0

<23> CPU_DP2_N1

<23> CPU_DP2_P1

<23> CPU_DP2_N2

<23> CPU_DP2_P2

<23> CPU_DP2_N3

<23> CPU_DP2_P3

<22> CPU_DP1_CTRL_CLK

<22> CPU_DP1_CTRL_DATA

<23> CPU_DP2_CTRL_CLK

<23> CPU_DP2_CTRL_DATA

@

T120

PAD~D

1 2

RC2

24.9_0402_1%

CPU_DP1_CTRL_CLK

CPU_DP1_CTRL_DATA

CPU_DP2_CTRL_CLK

CPU_DP2_CTRL_DATA

GPP_E23

EDP_COMP

COMPENSATION PU FOR eDP

CAD Note: Trace wi dth=20 mi ls ,Spa cing= 25mil,

C C

B B

Max len gth=10 0mil s.

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

L13

GPP_E18/DDPB_CTRLCLK

L12

N7

GPP_E20/DDPC_CTRLCLK

N8

N11

GPP_E22/DDPD_CTRLCLK

N12

E52

SKL-U_BGA1356

UC1A

DDI1_TXP[3]

DDI2_TXP[3]

GPP_E19/DDPB_CTRLDATA

GPP_E21/DDPC_CTRLDATA

GPP_E23/DDPD_CTRLDATA

EDP_RCOMP

SKL-U Ballout Rev0.71 & INTEL symbol Rev1.0

UC1I

CSI-2

A36

CSI2_DN0

B36

CSI2_DP0

C38

CSI2_DN1

D38

CSI2_DP1

C36

CSI2_DN2

D36

CSI2_DP2

A38

CSI2_DN3

B38

CSI2_DP3

C31

CSI2_DN4

D31

CSI2_DP4

C33

CSI2_DN5

D33

CSI2_DP5

A31

CSI2_DN6

B31

CSI2_DP6

A33

CSI2_DN7

B33

CSI2_DP7

A29

CSI2_DN8

B29

CSI2_DP8

C28

CSI2_DN9

D28

CSI2_DP9

A27

CSI2_DN10

B27

CSI2_DP10

C27

CSI2_DN11

D27

CSI2_DP11

SKL-U_BGA1356

SKL-U

DDI

DISPLAYSIDEBANDS

SKL_ULT

1OF 20

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

EDP

EDP_DISP_UTIL

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTCTL

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMMC

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

9OF 20

C47

EDP_TXN[0]

C46

EDP_TXP[0]

D46

EDP_TXN[1]

C45

EDP_TXP[1]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

C37

D37

C32

D32

C29

D29

B26

A26

E13

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

CSI2_COMP 1 B7

RC3

EMMC_RCOMP

CPU_DP1_AUXN

CPU_DP1_AUXP

CPU_DP3_AUXN

CPU_DP3_AUXP

1

RC4

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_BKLTEN

EDP_VDDEN ENVDD_PCH <26,32>

2

100_0402_1%

2

200_0402_1%

EDP_TXN0 <26>

EDP_TXP0 <26>

EDP_TXN1 <26>

EDP_TXP1 <26>

EDP_AUXN <26>

EDP_AUXP <26>

CPU_DP2_AUXN <23>

CPU_DP2_AUXP <23>

@

PAD~D

@

T2

PAD~D

CPU_DP1_HPD <22>

CPU_DP2_HPD <23>

EDP_HPD <26>

PANEL_BKLEN <26>

EDP_BIA_PWM <26>

T1

SupportQHD

CPU_DP1_AUXN

100K_0402_5%

CPU_DP2_AUXN

100K_0402_5%

CPU_DP2_AUXP

100K_0402_5%

CPU_DP1_AUXP

100K_0402_5%

EDP_HPD

100K_0402_5%

CPU_DP1_HPD

100K_0402_5%

CPU_DP2_HPD

100K_0402_5%

+3.3V_RUN

2

1

RC179

2

1

RC181

2

1

RC182

2

1

RC180

2

1

RC1

2

1

@

RC312

1

2

RC242

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT BE

TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION, NEITHER

THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY

WITHOUT DELL'S EXP RESS WRITTENCONSENT.

5 4 3 2 1

Tiiitllle

Siiize DocumentNumber

Date:

Compal Electronics,Inc.

CPU(1/14)

Thursday, September 24, 2015

LA-C642P

Sheet

Rev

6

1.0

60

of

5 4 3 2 1

<20> DDR_A_DQS#[0..7]

<20> DDR_A_D[0..63]

<20> DDR_A_DQS[0..7]

<20> DDR_A_MA[0..16]

D D

DDR4, Ballout for side by side(Non-Interleave)

UC1B

DDR_A_D0

AL71

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D32

DDR_A_D33

C C

B B

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

SKL-U_BGA1356

SKL-U

DDRCH - A

<21> DDR_B_DQS#[0..7]

<21> DDR_B_D[0..63]

<21> DDR_B_DQS[0..7]

<21> DDR_B_MA[0..16]

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL DDR_VTT_CTRL <20>

2OF 20

DDR_A_CLK#0

AU53

DDR_A_CLK0

AT53

DDR_A_CLK#1

AU55

DDR_A_CLK1

AT55

BA56

BB56

DDR_A_CKE2

AW56

DDR_A_CKE3

AY56

AU45

DDR_A_CS#1

AU43

DDR_A_ODT0

AT45

DDR_A_ODT1

AT43

DDR_A_MA5

BA51

DDR_A_MA9

BB54

DDR_A_MA6

BA52

DDR_A_MA8

AY52

DDR_A_MA7

AW52

DDR_A_BG0

AY55

DDR_A_MA12

AW54

DDR_A_MA11

BA54

DDR_A_ACT#

BA55

DDR_A_BG1

AY54

DDR_A_MA13

AU46

DDR_A_MA15

AU48

DDR_A_MA14

AT46

DDR_A_MA16

AU50

DDR_A_BA0

AU52

DDR_A_MA2

AY51

AT48

AT50

BB50

BA50

DDR_A_MA4

BB52

DDR_A_DQS#0

AM70

AM69

AT69

AT70

DDR_A_DQS#4

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

DDR_B_DQS5

BA26

AW50

DDR_A_PARITY

AT52

AY67

+DDR_VREF_A_+DDQ

AY68

BA67

AW67

DDR_A_CKE0

DDR_A_CKE1

DDR_A_CS#0

DDR_A_BA1

DDR_A_MA10

DDR_A_MA1

DDR_A_MA0

AY50

DDR_A_MA3

DDR_A_DQS0

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_DQS4

DDR_A_DQS#5

DDR_A_DQS5

DDR_B_DQS#0

DDR_B_DQS0

DDR_B_DQS#1

DDR_B_DQS1

DDR_B_DQS#4

DDR_B_DQS4

DDR_B_DQS#5

DDR_A_ALERT#

DDR_A_CLK#0 <20>

DDR_A_CLK0 <20>

DDR_A_CLK#1 <20>

DDR_A_CLK1 <20>

DDR_A_CKE0 <20>

DDR_A_CKE1 <20>

@

T3

PAD~D

@

T4

PAD~D

DDR_A_CS#0 <20>

DDR_A_CS#1 <20>

DDR_A_ODT0 <20>

DDR_A_ODT1 <20>

Check ODT schematic 0918

DDR_A_BG0 <20>

DDR_A_ACT# <20>

DDR_A_BG1 <20>

DDR_A_BA0 <20>

DDR_A_BA1 <20>

DDR0 _PAR,D DR0_ALE RT# for DDR4

DDR_A_ALERT# <20>

DDR_A_PARITY <20>

DR_VREF_CA

@T132

PAD~D

+DDR_VREF_B_DQ

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D58

DDR_B_D53

DDR_B_D59

DDR_B_D54

DDR_B_D60

DDR_B_D55

DDR_B_D61

DDR_B_D56

DDR_B_D62

DDR_B_D57

DDR_B_D63

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[57]

DDR1_DQ[52]

AU21

AN27

DDR1_DQ[58]

AT21

DDR1_DQ[53]

AN25

DDR1_DQ[59]

AN22

DDR1_DQ[54]

AP25

DDR1_DQ[60]

AP22

DDR1_DQ[55]

AT22

DDR1_DQ[61]

AP21

DDR1_DQ[56]

AU22

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKL-U_BGA1356

UC1C

SKL-U

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDRCH - B

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

3OF 20

AN45

DDR_B_CLK#1

AN46

DDR_B_CLK0

AP45

DDR_B_CLK1

AP46

AN56

AP55

AN55

AP53

BB42

DDR_B_CS#1

AY42

DDR_B_ODT0

BA42

AW42

AY48

DDR_B_MA9

AP50

DDR_B_MA6

BA48

DDR_B_MA8

BB48

DDR_B_MA7

AP48

DDR_B_BG0

AP52

DDR_B_MA12

AN50

DDR_B_MA11

AN48

DDR_B_ACT#

AN53

DDR_B_BG1

AN52

BA43

DDR_B_MA15

AY43

DDR_B_MA14

AY44

AW44

DDR_B_BA0

BB44

DDR_B_MA2

AY47

DDR_B_MA4

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

DDR_B_PARITY

AP43

DDR_DRAMRST#

AT13

SM_RCOMP0

AR18

SM_RCOMP1

AT18

SM_RCOMP2

AU18

DDR_B_CLK#0

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CKE2

DDR_B_CKE3

DDR_B_CS#0

DDR_B_ODT1

DDR_B_MA5

DDR_B_MA13

DDR_B_MA16

DDR_B_BA1

BA44

DDR_B_MA10

AW46

DDR_B_MA1

AY46

DDR_B_MA0

BA46

DDR_B_MA3

BB46

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_DQS#3

DDR_A_DQS3

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_DQS#7

DDR_A_DQS7

DDR_B_DQS#2

DDR_B_DQS2

DDR_B_DQS#3

DDR_B_DQS3

DDR_B_DQS#6

DDR_B_DQS6

DDR_B_DQS#7

DDR_B_DQS7

DDR_B_ALERT#

DDR_B_CLK#0 <21>

DDR_B_CLK#1 <21>

DDR_B_CLK0 <21>

DDR_B_CLK1 <21>

DDR_B_CKE0 <21>

DDR_B_CKE1 <21>

@

T5

PAD~D

@

T6

PAD~D

DDR_B_CS#0 <21>

DDR_B_CS#1 <21>

DDR_B_ODT0 <21>

DDR_B_ODT1 <21>

Check ODT schematic0918

DDR_B_BG0 <21>

DDR_B_ACT# <21>

DDR_B_BG1 <21>

DDR_B_BA0 <21>

DDR_B_BA1 <21>

DDR1 _PAR,D DR1_ALE RT# for DDR4

DDR_B_ALERT# <21>

DDR_B_PARITY <21>

DDR_DRAMRST# <20>

DDR4 COMPENSATION SIGNALS

A A

5 4 3 2

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

CAD N ote:

Trace width=12~15 mil, S pacing =20 mils

Max trac e leng th= 500 mil

RC5

RC6

RC7

1 2

1 2

1 2

121_0402_1%

80.6_0402_1%

100_0402_1%

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT BE

TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. INADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DE LL'S EXPRESS WRITTENCONSENT.

DELL CONFIDENTIAL/PROPRIETARY

Tiiitllle

Siiize DocumentNumber Rev

Date:

Compal Electronics,Inc.

CPU(2/14)

Thursday, September 24, 2015

LA-C642P

7

Sheet

1

of

1.0

60

5 4 3 2 1

L

AT

L

AT

L

AT

SPI _MOSI= SP I_IO0

SPI _MISO= SP I_IO1

PCH EDSR0 .7 p.2 35~236

PCH_SPI_CLK

PCH_SPI_D1

RC30

RC316

1

1

1

1

PCH_SPI_D0

PCH_SPI_D2

PCH_SPI_D3

PCH_SPI_CS#0

PCH_SPI_CS#1

PCH_SPI_CS#2

2

10K_0402_1%

1 2

1

1

2

2

2

2

ONE_DIMM#

PCH_SPI_D2_R1

1K_0402_5%

PCH_SPI_D3_R1

2

1K_0402_5%@RC31

PCH_SPI_D3_R1

2

1K_0402_5%

0_0402_5%

33_0402_5%

0_0402_5%

33_0402_5%

1 2

<14> PCH_SPI_DO_XDP

<14> PCH_SPI_DO2_XDP

D D

+3.3V_RUN

10K_0402_5% 10K_0402_5%

12

@RC267 RC268

12

RC11

ONE_DIMM#

RC10

1

<32> SIO_RCIN#

DIM M Detect

HIGH

LOW

C C

B B

A A

1 DIMM

2 DIMM

PCH_SPI_CLK_1_R PCH_SPI_CLK_0_R

33_0402_5%

2

@EMC@ CC7

RC28

33P_0402_50V8J

@EMC@

1 2 1

1K_0402_1%

2

1K_0402_1%

<33> PCH_SPI_CS#2

<33> TPM_PIRQ#

<42> FFS_INT2

+3.3V_RUN

33_0402_5%

2

@EMC@ CC8

RC29

33P_0402_50V8J

@EMC@

1 2 1

9/5 M OW

Option 1: Implemen t a 1 kO hm pull- down resistor on the signal an d de-populate the

requir ed 1 kOh m pull-up resistor . In this case, customers must en sure that the SPI

flash dev ice on the platform has HOLD functi onality disabl ed bydefa ult.

Note t hat the pull down r esistor on SP I0_IO3 is only ne eded for SK L U/Y platfor ms

with E S and SKL S /H platform s with pre-ES1 /ES1samp les.

PCH_SPI_CS#0_R1 @

PCH_SPI_D2_R1

PCH_SPI_CS#1_R1

PCH_SPI_D2_R1 PCH_SPI_D2_1_R

12

RC13

<31,32> IRQ_SERIRQ

+3.3V_RUN

<28> MEDIACARD_IRQ#

<29> PCH_CL_CLK1

<29> PCH_CL_DATA1

<29> PCH_CL_RST1#

10K_0402_5%

RC21 1

+3.3V_SPI

@

@

RC37

RC39

RC42

@

RC43

@

UC1E

AV2

SPI0_CLK

AW3

SPI0_MISO

AV3

SPI0_MOSI

AW2

SPI0_IO2

AU4

SPI0_IO3

AU3

SPI0_CS0#

AU2

SPI0_CS1#

AU1

SPI0_CS2#

SPI - TOUCH

M2

GPP_D1/SPI1_CLK

M3

GPP_D2/SPI1_MISO

J4

GPP_D3/SPI1_MOSI

V1

GPP_D21/SPI1_IO2

V2

GPP_D22/SPI1_IO3

M1

GPP_D0/SPI1_CS#

G3

CL_CLK

G2

CL_DATA

G1

CL_RST#

AW13

GPP_A0/RCIN#

AY11

GPP_A6/SERIRQ

SKL-U_BGA1356

<33> PCH_SPI_D1_R1

<33> PCH_SPI_CLK_R1

PCH_SPI_CS#0_R2

PCH_SPI_D1_0_R

PCH_SPI_D2_0_R

PCH_SPI_CS#1_R2

PCH_SPI_D1_1_R

SPI - FLASH

C LINK

<33> PCH_SPI_D0_R1

128Mb Flash ROM

UC5

1

/CS

2

DO(IO1)

3

/WP(IO2) CLK

4

GND DI(IO0)

W25Q128FVSIQ_SO8

64Mb Flash ROM

UC6 @

1

/CS VCC

2

DO(IO1) /HOLD(IO3)

3

/WP(IO2) CLK

4

GND DI(IO0)

W25Q64FVSSIQ_SO8

SKL-U

PCH_SPI_D1_R1

PCH_SPI_D0_R1

PCH_SPI_CLK_R1

PCH_SPI_D3_R1

PCH_SPI_D3_R1

PCH_SPI_CLK_R1

PCH_SPI_D0_R1

PCH_SPI_D1_R1

VCC

/HOLD(IO3)

LPC

GPP_A14/SUS_STAT#/ESPI_RESET#

SOFTWARE TAA

RPC1

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

RPC2

@

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

+3.3V_SPI

0.1U_0201_10V6K

8

7

PCH_SPI_D3_0_R

6

PCH_SPI_CLK_0_R

PCH_SPI_D0_0_R

5

+3.3V_SPI

0.1U_0201_10V6K

8

PCH_SPI_D3_1_R

7

PCH_SPI_CLK_1_R

6

PCH_SPI_D0_1_R

5

SMBUS, SMLINK

GPP_C0/SMBC

GPP_C1/SMBD

GPP_C2/SMBALERT

GPP_C3/SML0C

GPP_C4/SML0D

GPP_C5/SML0ALERT

GPP_C6/SML1C

GPP_C7/SML1D

GPP_B23/SML1ALERT#/PCHHOT

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

PCH_SPI_D1_0_R

PCH_SPI_D0_0_R

PCH_SPI_CLK_0_R

PCH_SPI_D3_0_R

PCH_SPI_D3_1_R

PCH_SPI_CLK_1_R

PCH_SPI_D0_1_R

PCH_SPI_D1_1_R

CC9

2

1

@

CC10

1 2

5OF 20

R7

K

R8

A

PCH_SMB_ALERT#

R10

#

R9

K

SML0_SMBDATA

W2

A

W1

#

SML1_SMBCLK

W3

K

V3

A

AM7

#

AY13

BA13

BB13

AY12

BA12

BA11

AW9

PCI_CLK_LPC1

AY9

AW11

+3.3V_SPI

MEM_SMBCLK

MEM_SMBDATA

SML0_SMBCLK

GPP_C5

SML1_SMBDATA

GPP_B23

SUS_STAT#

PCI_CLK_LPC0

CLKRUN# <31,32>

RC32

@

RC33 0_0402_5%

RC34 0_0402_5%

RC35 0_0402_5%

RC36 0_0402_5%

RC38 0_0402_5%

RC40 0_0402_5%

+3.3V_ALW_PCH

@

RC41

SML0_SMBCLK <27>

SML1_SMBCLK <32>

LPC_LFRAME# <31,32>

Reserve

12

0_0402_5%

12

12

12

12

12

12

@

+3.3V_M

@RC276

2

SML0_SMBDATA <27>

SML1_SMBDATA <32>

LPC_LAD0 <31,32>

LPC_LAD1 <31,32>

LPC_LAD2 <31,32>

LPC_LAD3 <31,32>

1 2

EMC@ RC16

1 2

EMC@ RC18

1 2

EMC@ RC22

1 2

EMC@ RC24

CLK_PCI_5048

27P_0402_50V8J

CLK_PCI_MEC

27P_0402_50V8J

CLK_PCI_LPDEBUG

27P_0402_50V8J

CLK_PCI_DOCK

27P_0402_50V8J

Reserve for RF

PCH_SPI_CS#1_R

PCH_SPI_CS#1

PCH_SPI_D0_R1

PCH_SPI_D0

PCH_SPI_D1_R1

PCH_SPI_D1

PCH_SPI_CLK_R1

PCH_SPI_CLK

PCH_SPI_CS#0_R1

PCH_SPI_CS#0

PCH_SPI_D2_R1

PCH_SPI_D2

PCH_SPI_D3_R1

PCH_SPI_D3

2 1

RC289

+3.3V_SPI_R

1

0_0402_5%

MEM_SMBCLK

MEM_SMBDATA

22_0402_5%

22_0402_5%

22_0402_5%

22_0402_5%

2

1

EMC@

CC3

2

1

EMC@

CC4

2

1

EMC@

CC5

2

1

EMC@

CC6

E-T_6705K-Y20N-00L

22

GND2

21

GND1

1

20

20

19

19

18

18

17

17

16

15

16

14

15

13

14

12

13

11

12

10

11

9

10

8

9

7

8

6

7

5

4

0_0402_5%

12

0_0402_5%

6

3

5

3

2

4

2

1

1

JSPI1

CONN@

<11,32> SIO_SLP_A#

<11,17,18,32,41,46,47,48> SIO_SLP_SUS#

CLK_PCI_5048 <31>

CLK_PCI_MEC <32>

CLK_PCI_LPDEBUG <32>

CLK_PCI_DOCK <38>

+3.3V_RUN

DDR_XDP_WAN_SMBDAT

2.2K_0402_5%

DDR_XDP_WAN_SMBCLK

6 1

5

DMN65D8LDW -7_SOT363-6

3 4

QC2B

DMN65D8LDW -7_SOT363-6

2

QC2A

SML0_SMBCLK

SML0_SMBDATA

MEM_SMBCLK

MEM_SMBDATA

SML1_SMBCLK

SML1_SMBDATA

SUS_STAT#

Reserve

SML0_SMBCLK

SML0_SMBDATA

CLKRUN#

FFS_INT2

PCH_SMB_ALERT#

2.2K_0402_5%

DDR_XDP_WAN_SMBCLK <14,20,21,42>

DDR_XDP_WAN_SMBDAT <14,20,21,42>

1 2

@

RC19

1

@

RC20

@RC26

RC347

RC348 499_0402_1%

RC27 8.2K_0402_5%

RC322 10K_0402_5%

RC23 2.2K_0402_5%

TLS CONFIDENT IALITY

HIG H

LOW(DEFAULT)

GPP_C5

EC interf ace

HIG H

LOW(DEFAULT)

+3.3V_RUN +3.3V_ALW_PCH

150K_0402_5%

@

RC326

@

RC327

1

@

RC339

@RC340

2

12

0_0402_5%

2

1

0_0402_5

GPP_B23 GPP_B23_Q

12

0_0402_5%

D

S

13

@

QC3

L2N7002WT1G_SC-70-3

G

2

%

EXI BO OT STALL BYPASS

HIG H

LOW(DEFAULT)

WEAK INTERNALPD

1

RC12

1

RC14

1

RC15

1

RC17

1

1

1

8/5 CKLT0.9

1 2

1 2

ENABLE

DISABLE

1 2

ESPI

LPC

2

2

499_0402_1%

2

499_0402_1%

2

1K_0402_5%

2

1K_0402_5%

2

1K_0402_5%

2

1K_0402_5%

2

10K_0402_5%

2

499_0402_1%

2

+3.3V_ALW_PCH

12

+3.3V_ALW_PCH

10K_0402_5%@RC25

150K_0402_5%

1 2

ENABLED

DIABLED

+3.3V_RUN

1

RC318

1

RC319

+3.3V_LAN

+3.3V_ALW_PCH

+3.3V_RUN

RC317

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DE LL'S EXPRESS WRITTENCONSENT.

5 4 3 2

DELL CONFIDENTIAL/PROPRIETARY

Tiiitllle

Siiize DocumentNumber

Date:

Compal Electronics,Inc.

CPU(3/14)

Thursday, September 24, 2015

LA-C642P

8

Sheet

1

of

Rev

1.0

60

5 4 3 2 1

+3.3V_ALW_PCH

+3.3V_RUN

UC1F

LPSS ISH

AN8

D D

C C

RC270

RC282

@RC335

@RC336

RC279

RC292

RC237

+3.3V_ALW_PCH

RC283

RC330

RC331

+3.3V_ALW_PCH

1

2

1

1

1

1

1

1

1

1

@RC186

10K_0402_5%

100K_0402_5%

10K_0402_5%

10K_0402_5%

10K_0402_5%

10K_0402_5%

1

TS_EN

2

LPSS_UART2_TXD

2

49.9K_0402_1%

LPSS_UART2_RXD

2

49.9K_0402_1%

AUD_PWR_EN

2

HOST_SD_WP#

2

SIO_EXT_SCI#

1

SIO_EXT_WAKE#

2

LPSS_UART2_RXD

2

49.9K_0402_1%

LPSS_UART2_TXD

2

49.9K_0402_1%

NRB_BIT

2

4.7K_0402_5%

Reserve

Reserve

<32> SIO_EXT_SCI#

<26> TS_EN

<42> HDD_EN

<32> UART0_TXD

<28> HOST_SD_WP#

<32> SIO_EXT_WAKE#

<39> I2C_1_SDA

<39> I2C_1_SCL

NRB_BIT

3.3V_TP_EN

LPSS_UART2_RXD

LPSS_UART2_TXD

Reserve

3.3V_TP_EN

2

GPP_B15/GSPI0_CS#

AP7

GPP_B16/GSPI0_CLK

AP8

GPP_B17/GSPI0_MISO

AR7

GPP_B18/GSPI0_MOSI

AM5

GPP_B19/GSPI1_CS#

AN7

GPP_B20/GSPI1_CLK GPP_D5/ISH_I2C0_SDA

AP5

GPP_B21/GSPI1_MISO GPP_D6/ISH_I2C0_SCL

AN5

GPP_B22/GSPI1_MOSI

AB1

GPP_C8/UART0_RXD

AB2

GPP_C9/UART0_TXD

W4

GPP_C10/UART0_RTS#

AB3

GPP_C11/UART0_CTS#

AD1

GPP_C20/UART2_RXD

AD2

GPP_C21/UART2_TXD

AD3

GPP_C22/UART2_RTS#

AD4

GPP_C23/UART2_CTS#

U7

GPP_C16/I2C0_SDA

U6

GPP_C17/I2C0_SCL

U8

GPP_C18/I2C1_SDA

U9

GPP_C19/I2C1_SCL

AH9

GPP_F4/I2C2_SDA GPP_A19/ISH_GP1

AH10

GPP_F5/I2C2_SCL GPP_A20/ISH_GP2

AH11

GPP_F6/I2C3_SDA GPP_A22/ISH_GP4

AH12

GPP_F7/I2C3_SCL GPP_A23/ISH_GP5

AF11

AF12

GPP_F8/I2C4_SDA

GPP_F9/I2C4_SCL

SKL-U_BGA1356

SKL-U

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

GPP_D15/ISH_UART0_RTS#

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UAR T1_RTS#

GPP_C15/UART1_CTS#/ISH_UAR T1_CTS#

GPP_A18/ISH_GP0

GPP_A21/ISH_GP3

GPP_A12/BM_BUSY#/ISH_GP6

6OF 20

DIMM_TYPE

P2

P3

P4

P1

M4

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

AC1

AC2

AC3

AB4

AY8 CLKDET#

BA8

BB7

BA7

AY7

AW7

AP13

NON_DOCK

9/24: Reserve f or embed ded loc ation ,refer Intel PDG 0.9

ISH_I2C2_SDA <29>

ISH_I2C2_SCL <29>

ISH_UART0_RXD <29>

ISH_UART0_TXD <29>

ISH_UART0_RTS# <29>

ISH_UART0_CTS# <29>

LCD_CBL_DET# <26>

@

T121

PAD~D

VMM3320_LPM_DIS <24>

KB_DET# <39>

AUD_PWR_EN <30>

IR_CAM_DET# <26>

WWAN

WLAN

NO R EBOOT STRA P

HIG H

LOW(DEFAULT)

Wea kIPD

B B

+3.3V_ALW_PCH

12

@ RC184

8.2K_0402_5%

HDD_EN

No R EBOOT

REBO OTENA BLE

+5V_ALW

LPSS_UART2_TXD

LPSS_UART2_RXD

JUART1

1

1

2

2

3

3

4

4

5

6

GND

GND

ACES_50207-00471-P01

8/21

KB_DET#

LCD_CBL_DET#

IR_CAM_DET#

+3.3V_ALW_PCH

RC287 100K_0402_5%

RC346 100K_0402_5%

NON_DOCK

11 2

@

RC341

10K_0402_5%

DIMM_TYPE

RC342

10K_0402_5%

2

1 2

RC288 10K_0402_5%

1 2

1 2

1 2

100_0402_1%@RH359

DIMM_TYPE

HIGH

DDR3L

LOW DDR4

+3.3V_RUN

BOOT BIOS Dest ination(Bit 10)

HIG H

LOW(DEFAULT)

LPC

SPI

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT BE

TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION, NEITHER

THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY

WITHOUT DELL'S EXP RESS WRITTENCONSENT.

5 4 3 2

Tiiitllle

Siiize DocumentNumber

Date: of

Compal Electronics,Inc.

CPU (4/14)

Thursday, September 24, 2015

LA-C642P

1

Sheet

9 60

Rev

1.0

5 4 3 2 1

UC1H

PCIE/USB3/SATA

D D

WWAN

WWAN--->

WLAN --->

WIGIG--->

C C

SATA HDD--->

E DOCK ESATA--->

10/100/1G LAN --->

Card Reader --->

SATA EXPRESS HDD --->

B B

<29> USB3_PRX_DTX_N5

<29> USB3_PRX_DTX_P5

<29> USB3_PTX_DRX_N5

<29> USB3_PTX_DRX_P5

<29> PCIE_PRX_DTX_N3

<29> PCIE_PRX_DTX_P3

<29> PCIE_PTX_DRX_N3

<29> PCIE_PTX_DRX_P3

<29> PCIE_PRX_DTX_N5

<29> PCIE_PRX_DTX_P5

<29> PCIE_PTX_DRX_N5

<29> PCIE_PTX_DRX_P5

<29> PCIE_PRX_DTX_N6

<29> PCIE_PRX_DTX_P6

<29> PCIE_PTX_DRX_N6

<29> PCIE_PTX_DRX_P6

<42> SATA_PRX_DTX_N0

<42> SATA_PRX_DTX_P0

<42> SATA_PTX_DRX_N0

<42> SATA_PTX_DRX_P0

<38> SATA_PRX_DTX_N1

<38> SATA_PRX_DTX_P1

<38> SATA_PTX_DRX_N1

<38> SATA_PTX_DRX_P1

<27> PCIE_PRX_DTX_N9

<27> PCIE_PRX_DTX_P9

<27> PCIE_PTX_DRX_N9

<27> PCIE_PTX_DRX_P9

<28> PCIE_PRX_DTX_N10

<28> PCIE_PRX_DTX_P10

<28> PCIE_PTX_DRX_N10

<28> PCIE_PTX_DRX_P10

RC45

<34> PCIE_PRX_DTX_N11

<34> PCIE_PRX_DTX_P11

<34> PCIE_PTX_DRX_N11

<34> PCIE_PTX_DRX_P11

<34> PCIE_PRX_DTX_N12

<34> PCIE_PRX_DTX_P12

<34> PCIE_PTX_DRX_N12

<34> PCIE_PTX_DRX_P12

1 2

100_0402_1%

<14> CPU_XDP_PRDY#

<14> CPU_XDP_PREQ#

<42> HDD_FALL_INT

PCIE_RCOMPN

PCIE_RCOMPP

H13

PCIE1_RXN/USB3_5_RXN

G13

PCIE1_RXP/USB3_5_RXP

B17

PCIE1_TXN/USB3_5_TXN

A17

PCIE1_TXP/USB3_5_TXP

G11

PCIE2_RXN/USB3_6_RXN

F11

PCIE2_RXP/USB3_6_RXP

D16

PCIE2_TXN/USB3_6_TXN

C16

PCIE2_TXP/USB3_6_TXP

H16

PCIE3_RXN

G16

PCIE3_RXP

D17

PCIE3_TXN

C17

PCIE3_TXP

G15

PCIE4_RXN

F15

PCIE4_RXP

B19

PCIE4_TXN

A19

PCIE4_TXP

F16

PCIE5_RXN

E16

PCIE5_RXP

C19

PCIE5_TXN

D19

PCIE5_TXP

G18

PCIE6_RXN

F18

PCIE6_RXP

D20

PCIE6_TXN

C20

PCIE6_TXP

F20

PCIE7_RXN/SATA0_RXN

E20

PCIE7_RXP/SATA0_RXP

B21

PCIE7_TXN/SATA0_TXN

A21

PCIE7_TXP/SATA0_TXP

G21

PCIE8_RXN/SATA1A_RXN

F21

PCIE8_RXP/SATA1A_RXP

D21

PCIE8_TXN/SATA1A_TXN

C21

PCIE8_TXP/SATA1A_TXP

E22

PCIE9_RXN

E23

PCIE9_RXP

B23

PCIE9_TXN

A23

PCIE9_TXP

F25

PCIE10_RXN

E25

PCIE10_RXP

D23

PCIE10_TXN

C23

PCIE10_TXP

F5

PCIE_RCOMPN

E5

PCIE_RCOMPP

D56

PROC_PRDY#

D61

PROC_PREQ#

BB11

GPP_A7/PIRQA#

E28

PCIE11_RXN/SATA1B_RXN

E27

PCIE11_RXP/SATA1B_RXP

D24

PCIE11_TXN/SATA1B_TXN

C24

PCIE11_TXP/SATA1B_TXP

E30

PCIE12_RXN/SATA2_RXN

F30

PCIE12_RXP/SATA2_RXP

A25

PCIE12_TXN/SATA2_TXN

B25

PCIE12_TXP/SATA2_TXP

SKL-U_BGA1356

SKL-U

SSIC /USB3

USB2

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_3_RXN/SSIC_2_RXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_TXP/SSIC_2_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2_COMP

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E8/SATALED#

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_ID

8OF 20

H8

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

AB10

AD6

AD7

AH3

AJ3

AD9

AD10

AJ1

AJ2

AF6

AF7

AH1

AH2

AF8

AF9

AG1

AG2

AH7

AH8

AB6

AG3

AG4

A9

C9

D9

USB_OC3#

B9

J1

J2

J3

H2

H3 SATAGP1

G4

H1

USBCOMP RC44

Reserve

Reserve

USB3_PRX_DTX_N1 <36>

USB3_PRX_DTX_P1 <36>

USB3_PTX_DRX_N1 <36>

USB3_PTX_DRX_P1 <36>

USB3_PRX_DTX_N2 <38>

USB3_PRX_DTX_P2 <38>

USB3_PTX_DRX_N2 <38>

USB3_PTX_DRX_P2 <38>

USB3_PRX_DTX_N3 <37>

USB3_PRX_DTX_P3 <37>

USB3_PTX_DRX_N3 <37>

USB3_PTX_DRX_P3 <37>

USB3_PRX_DTX_N4 <37>

USB3_PRX_DTX_P4 <37>

USB3_PTX_DRX_N4 <37>

USB3_PTX_DRX_P4 <37>

USB20_N1 <36>

USB20_P1 <36>

USB20_N2 <26>

USB20_P2 <26>

USB20_N3 <37>

USB20_P3 <37>

USB20_N4 <37>

USB20_P4 <37>

USB20_N5 <38>

USB20_P5 <38>

USB20_N6 <38>

USB20_P6 <38>

USB20_N7 <33>

USB20_P7 <33>

USB20_N8 <29>

USB20_P8 <29>

USB20_N9 <26>

USB20_P9 <26>

USB20_N10 <29>

USB20_P10 <29>

1 2

@

1 2

RC337

1 2

RC338

USB_OC0# <36>

USB_OC1# <37>

USB_OC2# <37>

HDD_DEVSLP <42>

M2_DEVSLP <35>

HDD_DET# <42>

IFDET_SATA#_PCIE <34,35>

PCH_SATA_LED# <35,40>

-----> Ext USB3 Port 3 Charge(RIGHT)

-----> EDOCK

-----> Ext USB3 Port 1(LEFT)

-----> Ext USB3 Port 2(REAR LEFT)

-----> Ext US B Port 3 Charge(RIGHT)

----->Camera

-----> Ext US B Port 1(LEFT)

-----> Ext US B Port 2(REAR LEFT)

-----> EDOCK PORT1

-----> EDOCK PORT2

----->USH

----->BT

-----> LCD Touch

-----> M23042(WWAN)

113_0402_1% 8/19 for layout routingchange

0_0402_5%

1K_0402_5%

USB_OC0#

USB_OC3# 3 6

USB_OC1# 2 7

USB_OC2# 1 8

HDD_FALL_INT

IFDET_SATA#_PCIE

PCH_SATA_LED#

HDD_DET#

SATAGP1 1

RPC3

4 5

10K_8P4R_5%

RPC4

4 5

3

6

7

2

1 8

10K_8P4R_5%

RC246 10K_0402_5%

CKLT0.9

2

+3.3V_ALW_PCH

+3.3V_RUN

+3.3V_ALW_PCH

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT BE

TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION, NEITHER

THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY

WITHOUT DELL'S EXP RESS WRITTENCONSENT.

5 4 3 2

Tiiitllle

Siiize DocumentNumber

Date: of

Compal Electronics,Inc.

CPU (5/14)

Thursday, September 24, 2015

LA-C642P

1

Sheet

10 60

Rev

1.0

5 4 3 2 1

CC21

SUSCLK 1

UC1J

<29> CLK_PCIE_N0

WW AN

D D

WLAN--->

WIGIG --->

SA TA EXP RESS HDD--->

LAN --->

MMI --->

H_CPUPWRGD VCCST_PWRGD

EMC@ CC300

100P_0402_50V8J

12

C C

ESD Request:place near CPU side

+1.0V_VCCST

1

RC71

+3.3V_ALW_PCH

1 2

@RC74 10K_0402_5%

10/6 depop, prevent singal step.

B B

T9

<14,32> VCCST_PWRGD

RC2 15

POP

DE-POP

PCH_DPWROK

0.01UF_0402_25V7K

1

A A

2

<29> CLK_PCIE_P0

<29> CLKREQ_PCIE#0

<29> CLK_PCIE_N1

<29> CLK_PCIE_P1

<29> CLKREQ_PCIE#1

<29> CLK_PCIE_N2

<29> CLK_PCIE_P2

<29> CLKREQ_PCIE#2

<35> CLK_PCIE_N3

<35> CLK_PCIE_P3

<35> CLKREQ_PCIE#3

<27> CLK_PCIE_N4

<27> CLK_PCIE_P4

<27> CLKREQ_PCIE#4

<28> CLK_PCIE_N5

<28> CLK_PCIE_P5

<28> CLKREQ_PCIE#5

@EMC@ CC301

100P_0402_50V8J

12

VCCST_PWRGD

2

1K_0402_5%

ME_SUS_PWR_ACK

@

PAD~D

NO S upport Deep sleep

Support D eep sleep

1

@RC215

100K_0402_1%

12

RC220

CC266

+3.3V_RUN

+3.3V_RUN

+3.3V_RUN

+3.3V_RUN

+3.3V_RUN

+3.3V_RUN

+3.3V_ALW_DSW

+3.3V_RUN

<14,39> PCH_RSMRST#_Q

RC75

H_CPUPWRGD_R

RC78

PCH_RSMRST#_Q

2

0_0402_5%

RC189

RC47

RC50

RC59

RC51

RC190

PCH_PLTRST#

1 2

RC67 1K_0402_5%

1 2

RC323 10K_0402_5%

1 2

@RC225 8.2K_0402_5%

1 2

10K_0402_5%

1 2

@RC77

1 2

<14,32> RESET_OUT#

<32> PCH_DPWROK

<32> ME_SUS_PWR_ACK

<31,32> PCH_PCIE_WAKE#

<27,32> LAN_WAKE#

<27> PM_LANPHY_ENABLE

<26> 3.3V_CAM_EN#

<14> XDP_DBRESET#

1 2

10K_0402_5%

1 2

1 2

1 2

60.4_0402_1%

<49> PCH_PWROK

10K_0402_5%

10K_0402_5%

10K_0402_5%

1 2

10K_0402_5%

1 2

10K_0402_5%

TC7SH08FU_SSOP5~D

PCH_PCIE_WAKE#

LAN_WAKE#

ME_RESET#

1K_0402_5%

VCCST_PWRGD_CPU

<32> SUSACK#

1 2

RC311 10K_0402_5%

8/28 schematicreview

XDP_DBRESET#

@RC227 8.2K_0402_5%

UC7

PCH_PLTRST#

SYS_RESET#

PCH_RSMRST#_Q

H_CPUPWRGD

2 1

D42

C42

AR10

B42

A42

AT7

D41

C41

AT8

D40

C40

AT10

B40

A40

AU8

E40

E38

AU7

2

2

2

2

2

2

+3.3V_ALW_PCH

1

P

B

2

A

G

3 5

AN10

AY17

A68

B65

BA20

BB20

AR13

AP11

BB15

AM15

AW17

AT15

ME_RESET#

CLKOUT_PCIE_N0

CLKOUT_PCIE_P0

GPP_B5/SRCCLKREQ0#

CLKOUT_PCIE_N1

CLKOUT_PCIE_P1

GPP_B6/SRCCLKREQ1#

CLKOUT_PCIE_N2

CLKOUT_PCIE_P2

GPP_B7/SRCCLKREQ2#

CLKOUT_PCIE_N3

CLKOUT_PCIE_P3

GPP_B8/SRCCLKREQ3#

CLKOUT_PCIE_N4

CLKOUT_PCIE_P4

GPP_B9/SRCCLKREQ4#

CLKOUT_PCIE_N5

CLKOUT_PCIE_P5

GPP_B10/SRCCLKREQ5#

SKL-U_BGA1356

1

RC61 @0_0402_5%

1

RC62 @0_0402_5%

1

RC64 @0_0402_5%

1

RC244 @0_0402_5%

1

RC60@0_0402_5%

1

RC325@0_0402_5%

PCH_PLTRST#_AND

4

O

12

@ RC65

100K_0402_5%

UC1K

SYSTEM POWERMANAGEMENT

GPP_B13/PLTRST#

B5

SYS_RESET#

RSMRST#

PROCPWRGD

VCCST_PWRGD

B6

SYS_PWROK

PCH_PWROK

DSW_PWROK

GPP_A13/SUSWARN#/SUSPW RDNACK

GPP_A15/SUSACK#

WAKE#

GPD2/LAN_WAKE#

GPD11/LANPHYPC

GPD7/RSVD

SKL-U_BGA1356

1 2

@

RC290

2

+3.3V_RUN

5

1

P

B

A

G

74AHC1G09GW_TSSOP5

3

0_0402_5%

O

if pop U C12, RC2 91 also ne ed pop( 74AHC 1G09GW is OD out put)

5 4 3 2

SKL_ULT

CLOCKSIGNALS

PLTRST_VMM2320# <24>

PLTRST_LAN# <27>

PLTRST_5048# <31>

PCH_PLTRST#_EC <32>

PLTRST_TPM# <33>

PCH_PLTRST#_AND <28,29,33,35>

SYS_RESET#_R

4

@ UC12

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

SKL-U

GPP_B11/EXT_PWR_GATE#

1 2

RC224 1K_0402_5%

F43

GPD8/SUSCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

RTCX1

RTCX2

SRTCRST#

RTCRST#

10OF 20

CLK_ITPXDP_N

E43

CLK_ITPXDP_P

BA17

XTAL24_IN

E37

XTAL24_OUT

E35

E42

XCLK_BIASREF

AM18

PCH_RTCX2

AM20

AN18 SRTCRST#

AM16

PCH_RTCRST#

@ RC297

@ RC298

For Sk ylake p op RC5 2a nd dep op RC32 4

For C annonl ake depop R C52 and po p RC32 4

5467 65_5467 65_2014W W48_Skyl ake_MO W_Rev_1 _0

PCH_RTCX1

@

RC324

CMOS1 must take care sh ort & touch risk on layou tplace ment

@RC344

SIO_SLP_LAN#

8/21 can change to 10K for merge to RP

GPP_B12/SLP_S0#

GPD4/SLP_S3# SIO_SLP_S3# <17,32,48>

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD9/SLP_WLAN#

GPD6/SLP_A#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

GPP_A11/PME#

INTRUDER#

GPP_B2/VRALERT#

11OF 20

+3.3V_RUN

12

@ RC291

10K_0402_5%

SYS_RESET#

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DE LL'S EXPRESS WRITTENCONSENT.

AT11

AP15

BA16

AY16

AN15

AW15

BB17

AN16

BA15

AY15

PCH_BATLOW#

AU13

AU11 PME#

AP16 INTRUDER#

AM10

AM11 VRALERT#

PCH_BATLOW#

AC_PRESENT

SIO_SLP_S0# <17,33,47>

SIO_SLP_S4# <17,32,45,54>

SIO_SLP_S5# <32>

SIO_SLP_SUS# <8,17,18,32,41,46,47,48>

SIO_SLP_LAN# <32,41>

AC_PRESENT <32>

2

1K_0402_5%@RC48

2.7K_0402_1%

2

59_0402_1%

1 2

1 2

1U_0402_6.3V6K

1 2

1 2

1

1

SHORTPADS~D

@

CMOS1

2

10K_0402_5%

10K_0402_5%@RC68

2

8.2K_0402_5%

2

@

T115

2

0_0402_5%

2

0_0402_5%

20K_0402_5%

20K_0402_5%

1U_0402_6.3V6K

2

+3.3V_ALW_PCH

+3.3V_ALW

+3.3V_ALW_DSW

SLP_S0# for support connect stand bymode

1

1

SUSCLK <29,35>

1 2

RC52

1

RC56

CC24

RC57

CC25

1

1 2

1

RC72

1

RC243 10K_0402_5%

SIO_SLP_WLAN# <31,41>

SIO_SLP_A# <8,32>

SIO_PWRBTN# <14,32>

PAD~D

MPHYP_PWR_EN <18>

connect to VCCMPHYGTAON_1P0 enable pin

CLK_ITPXDP_N_R <14>

CLK_ITPXDP_P_R <14>

+1.0V_CLK5

2

8/21 CRB1.0 change to 0603 1/10W

+RTC_CELL

INTRUDER#

VRALERT#

XTAL24_IN

XTAL24_OUT

@

1M_0402_1%

1 2

@

RC295 0_0402_5%

For S kylak e YC1 24MHz (50 Ohm ESR)

For C annon lake YC1 38.4M Hz(30 Oh m ESR )

5467 65_5467 65_2014W W48_Skyl ake_MO W_Rev_1 _0

PCH_RTCX1

PCH_RTCX2

+RTC_CELL

1 2

RC69 1M_0402_5%

+3.3V_ALW +3.3V_ALW_PCH

1 2

RC73

RC343 10K_0402_5%

10K_0402_5%

1 2

ESD Request:place near CPUside

<32,40> POWER_SW#_MB

SYS_RESET#

0.1U_0402_25V6

12

DELL CONFIDENTIAL/PROPRIETARY

RC46

1 2

RC54

10M_0402_5%

1 2

1

@

RC296

+3.3V_ALW_PCH

+3.3V_ALW_DSW

+3.3V_ALW_DSW

@EMC@

CC302

Tiiitllle

Siiize DocumentNumber

Thursday, September 24, 2015

Date:

4

3

YC1

24MHZ_12PF_X3G024000DC1H

1

2

XTAL24_OUT_R

12

PCH_RTCX2_R

2

0_0402_5%

SIO_SLP_S3#

SIO_SLP_S5#

SIO_SLP_S4#

SIO_SLP_A#

PCH_RTCRST#

SYS_RESET#

SIO_SLP_S0#

Compal Electronics,Inc.

CPU(6/14)

LA-C642P

1 2

15P_0402_50V8J

CC22

1 2

15P_0402_50V8J

CC23

1

2

5P_0402_50V8C

YC2

32.768KHZ 9PF10PPM 9H03200055

ESR MAX=50k ohm

2

5P_0402_50V8C

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

GND

20

GND

ACES_50506-01841-P01

Sheet

1

CC26

1

JAPS1

CONN@

11

of

Rev

1.0

60

5 4 3 2 1

+1.0V_VCCST

8/21DG0.9

@

RC79149.9_0402_1%

RC80 1K_0402_5%

+1.0V_VCCSTG

8/19 DG0.9

RC83 1K_0402_5%

+3.3V_RUN

D D

RC272 10K_0402_5%

10K_8P4R_5%

+3.3V_ALW_PCH

RC236 10K_0402_5%

C C

B B

1

1

1 2

RPC5

435

2 7

1 8

1 2

H_CATERR#

2

H_THERMTRIP#

2

H_PROCHOT#

2

TOUCHPAD_INTR#

TOUCH_SCREEN_PD#

6

CAM_MIC_CBL_DET#

CONTACTLESS_DET#

SIO_EXT_SMI#

<30> HDA_SYNC_R

<30> HDA_BIT_CLK_R

<30> HDA_SDOUT_R

<30> HDA_RST#_R

22P_0402_50V8J

Close toRC93

<20,21,32> H_THERMTRIP#

HDA_BIT_CLK_R

1

CC27

2

<32,49,51> H_PROCHOT#

1 2

RC92

1 2

EMC@RC93

ME_FWP

RC94

RC223

1

RC95

1

<32> PECI_EC

8/19DG0.9

1 2

RC84 499_0402_1%

<14> XDP_OBS0_R

<14> XDP_OBS1_R

T10

T11

<32> SIO_EXT_SMI#

<26> TOUCH_SCREEN_PD#

<39> TOUCHPAD_INTR#

<26> TOUCH_SCREEN_DET#

RC88

2

1

2

1

49.9_0402_1%

33_0402_5%

33_0402_5%

2

33_0402_5%

2

1K_0402_5%

<30> SPKR

<30> HDA_SDIN0

33_0402_5%

1 2

@

PAD~D

@

PAD~D

EDRAM_OPIO_RCOMP

RC89

2

1

49.9_0402_1%

HDA_SYNC

HDA_BIT_CLK

HDA_SDOUT

HDA_RST#

H_CATERR#

H_PROCHOT#_R

H_THERMTRIP#

XDP_OBS2_R

XDP_OBS3_R

CPU_POPIRCOMP

PCH_POPIRCOMP

EOPIO_RCOMP

RC90

RC91

2

1

49.9_0402_1%

49.9_0402_1%

D63

A54

C65

C63

A65

C55

D55

BPM#[1]

B54

C56

A6

A7

BA5

AY5

AT16

AU16

H66

H65

UC1G

BA22

HDA_SYNC/I2S0_SFRM

AY22

HDA_BLK/I2S0_SCLK

BB22

HDA_SDO/I2S0_TXD

BA21

HDA_SDI0/I2S0_RXD

AY21

HDA_SDI1/I2S1_RXD

AW22

HDA_RST#/I2S1_SCLK

J5

GPP_D23/I2S_MCLK

AY20

I2S1_SFRM

AW20

I2S1_TXD

AK7

GPP_F1/I2S2_SFRM

AK6

GPP_F0/I2S2_SCLK

AK9

GPP_F2/I2S2_TXD

AK10

GPP_F3/I2S2_RXD

H5

GPP_D19/DMIC_CLK0

D7

GPP_D20/DMIC_DATA0

D8

GPP_D17/DMIC_CLK1

C8

GPP_D18/DMIC_DATA1

AW5

GPP_B14/SPKR

SKL-U_BGA1356

UC1D

CATERR#

PECI

PROCHOT#

THERMTRIP#

SKTOCC#

BPM#[0]

BPM#[2]

BPM#[3]

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

SKL-U_BGA1356

AUDIO

CPUMISC

SKL-U

SKL-U

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

JTAGX

4OF 20

CPU_XDP_TCLK

B61

D60

CPU_XDP_TDI

CPU_XDP_TDO

A61

CPU_XDP_TMS

C60

CPU_XDP_TRST#

B59

PCH_JTAG_TCK

B56

PCH_JTAG_TDI

D59

PCH_JTAG_TDO

A56

PCH_JTAG_TMS

C59

CPU_XDP_TRST#

C61

A59

SDIO/SDXC

GPP_A17/SD_PWR_EN#/ISH_GP7

GPP_A16/SD_1P8_SEL

PCH_JTAG_TDI <14>

PCH_JTAG_TDO <14>

PCH_JTAG_TMS <14>

XDP_JTAGX

1 2

@RC87

2

@

RC328

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

SD_RCOMP

GPP_F23

7OF 20

CPU_XDP_TCLK <14>

CPU_XDP_TDI <14>

CPU_XDP_TDO <14>

CPU_XDP_TMS <14>

CPU_XDP_TRST# <14>

PCH_JTAG_TCK <14>

1K_0402_5%

CPU_XDP_TCLK

1

0_0402_5%

AB11

AB13

AB12

W12

CONTACTLESS_DET#

W11

W8

W7

BA9

BB9

SD_RCOMP

AB7

AF13

2

+1.0V_VCCSTG

CAM_MIC_CBL_DET# <26>

W10

1

RC96

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

1

51_0402_5%@RC86

Servic e Mode Switc h:

Add a switch to M E_FWP signal to un lock the ME region and

allow the entire region of the SPI flash to be updated usin gFPT.

+3.3V_ALW_PCH

12

ME_F WP PCH has internal 20KPD.

(suspe nd power rail)

FLASH DE SCRIPTOR SECURITY OVERRIDE

LOW = ENABLE (DEF AULT) -->P in1 & Pin3 short

HIGH = DISABLE (ME can update ) -->Pin2 & Pin3 short

CONTACTLESS_DET# <33>

2

200_0402_1%

2

51_0402_5%

2

100_0402_1%

2

51_0402_5%

ME_FWP_EC

@

RC221 0_0402_5%

PT,ST pop RC222 and SW 1; MP pop RC221

@

RC222

1K_0402_5%

<31> ME_FWP_EC

1

RC81

1

RC82

1

RC130

2 1

ME_FWP

+1.0V_VCCSTG

ME_FWP

@

SW1

1

A

2

B

3

4 C

5 G1

G2

SS3-CMFTQR9_3P

+3.3V_ALW_PCH +3.3V_ALW_PCH

1

2

@RC183

TOP SW AP STRAP

A A

HIG H

LOW(DEFAULT)

8.2K_0402_5%

ENABLE

DISABLE

SPKR

@RC187

Flash Des criptor Securi ty override

HIG H

LOW(DEFAULT)

HDA_SDOUT

1

2

4.7K_0402_5%

DISABLE

ENABLE

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT BE

TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION, NEITHER

THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY

WITHOUT DELL'S EXP RESS WRITTENCONSENT.

5 4 3 2

Tiiitllle

Siiize DocumentNumber

Date: of

Compal Electronics,Inc.

CPU (7/14)

Thursday, September 24, 2015

LA-C642P

1