Davicom DM9301F Datasheet

General Description

DM9301

100Mbps Ethern et Fi ber/Twi sted Pai r Si ngle Chi p Media C onvert er

The DM9301 is a physical-layer, single-chip, lowpower media converter for 100BASE-TX/FX full

duplex repeater applications. On the TX media side,

it provides a direct interface to Unshielded Twisted

Pair Cable 5 (UTP5) for 100BASE-TX Fast Ethernet.

On the FX media side, it provides a direct interface to

a Pseudo Emitter Coupled Logic level interface

(PECL).

The DM9301 uses a low power and high

performance CMOS process. It contains the entire

physical layer functions of 100BASE-TX as def ined

by IEEE802.3u, including the Physical Coding

Sublayer (PCS), Physical Medium Attachment

(PMA), Twisted Pair Physical Medium Dependent

Sublayer (TP-PMD) and a PECL compliant interface

for a fiber opti c modul e, com pliant with ANSI X3.166.

The DM9301 provides two independent clock

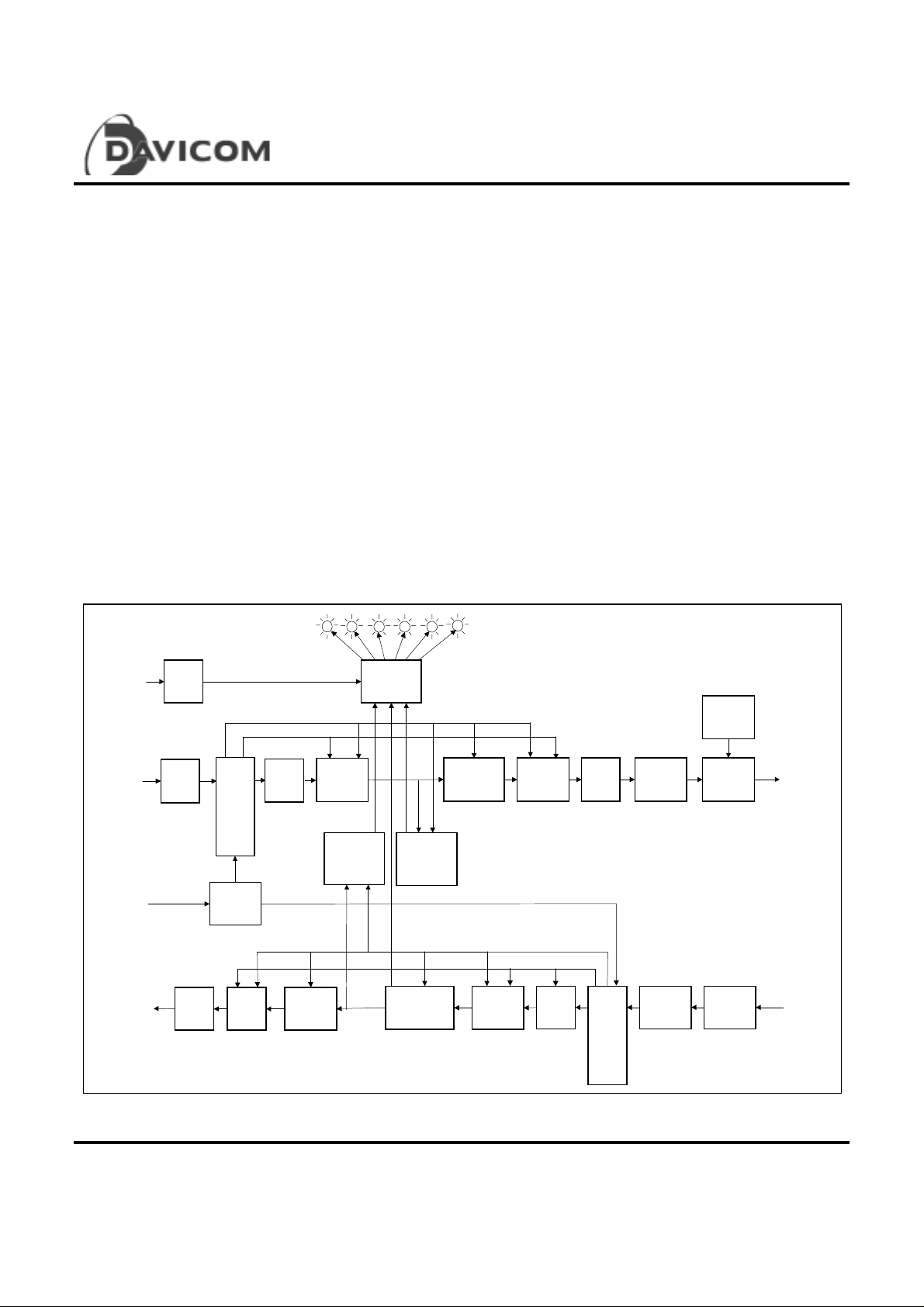

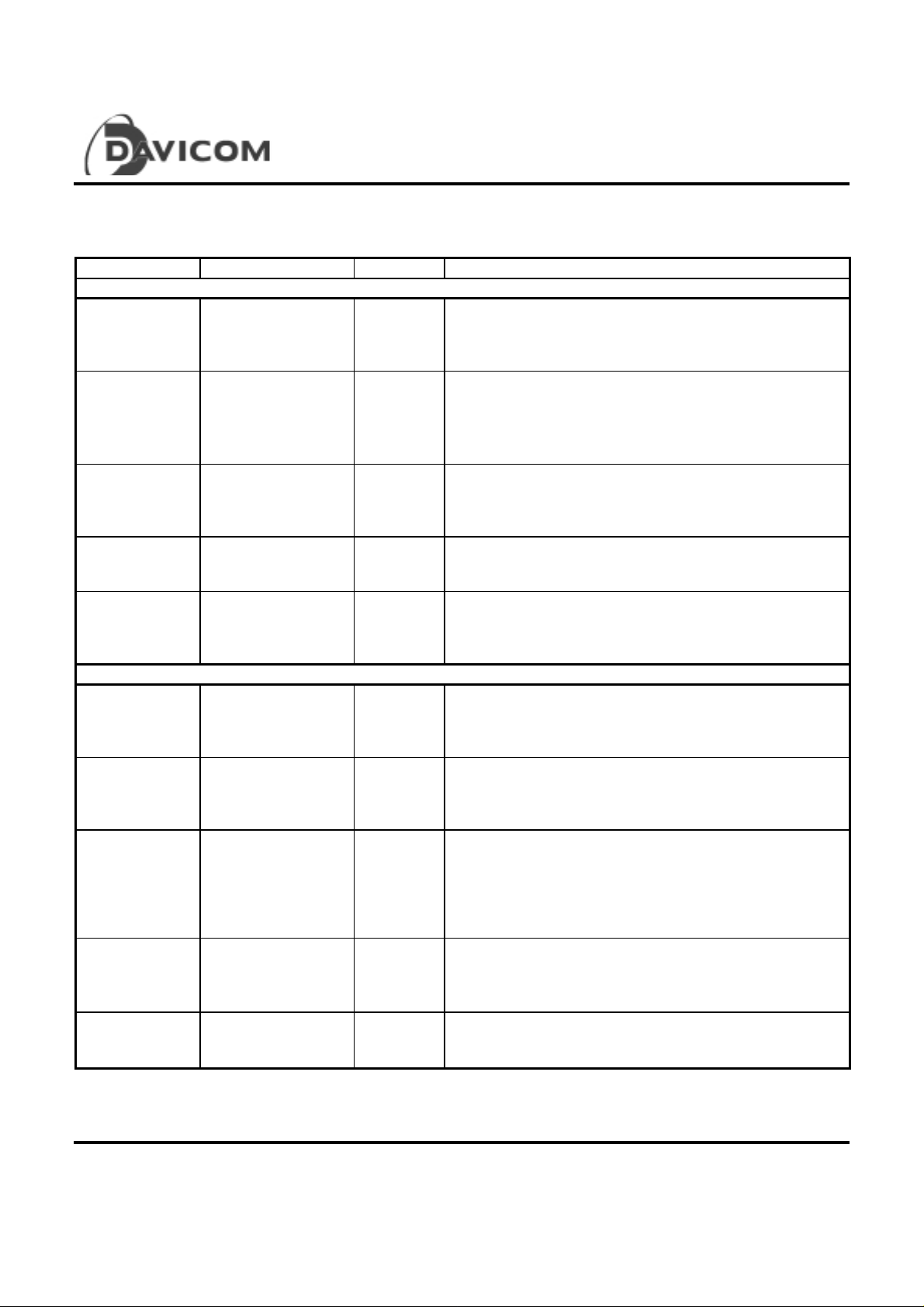

Block Diagram

PECLSD

FXSD

RCVR

25M FXRXCLK

125M FXRXCLK

Link Status

Monitor &

LED Driver

recovery circ uits to minimize bit delay through the

converter (no FIFO are used to buffer data between

the FX and TX interfaces). Furthermore, due to the

excellent rise/fall time control by a built-in waveshaping filter, the DM9301 needs no external filter to

transport signals to the media on the 100Base-TX

interface.

Patent-Pending Circ u its

• Smart adaptive receiv er equalizer

• Digital algorithm for high frequency clock/data

recovery circuit

• High speed wave-shaping circuit

Rise/Fall

Time

CTL

NRZI

to

NRZ

NRZ

to

NRZI

RX

CRM

NRZI to

MLT-3

MLT-3 to

NRZI

MLT-3

Driver

Adaptive

EQ

TPTXO+/-

TPRXI+/-

PECLRXI +/-

25M

OSC/XTAL

PECLTXO +/-

PECL

RCVR

PECL

TXMT

RX

CRM

CGM

NRZ

to

NRZI

NRZI

to

NRZ

Parallel

to Serial

Serial to

Parallel

TX Code-

group

Alignment

Monitor

FX Code-

group

Alignment

Monitor

25M TPRXCLK

Descrambler

Scrambler

Serial to

Parallel

Parallel

to Serial

125M TPRXCLK

Final 1

Version: DM9301 - DS -F02

May 8, 2000

Table of Contents

DM9301

100Mbps Ethern et Fi ber/Twi sted Pai r Si ngle Chi p Media C onvert er

General Descri pti on................................................1

Block Diagram........................................................1

Table of contents....................................................2

Features.................................................................3

Pin Configuration: DM9301 QFP.............................4

Pin Description.......................................................5

Functional Descr i pti on ..........................................10

100Base-FX to TX Oper ation................................10

T

FX PECL Receiver............................................10

T

FX Receiver Clock Recovery Module ................10

T

FX NRZI to NRZ Converter ...............................10

T

FX Serial to Parallel Converter..........................11

T

FX Code Group Alignment Monitor....................11

T

TX Scrambler....................................................11

T

TX Parallel to Serial Converter ..........................11

T

TX NRZ to NRZI Converter ...............................11

T

TX NRZI to MLT-3 Converter.............................11

T

TX MLT-3 Driver ...............................................11

100Base-TX to FX Operati on................................12

T

TX Signal Detect...............................................12

T

TX Digital Adaptive Equalization........................12

T

TX MLT-3 to NRZI Decoder...............................13

T

TX Clock Recovery Modul e ............................... 13

T

TX NRZI to NRZ Decoder..................................13

T

TX Serial to Parallel Converter..........................13

T

TX Code Group Monitor ....................................13

T

TX Descrambler................................................13

T

FX Parallel to Serial Converter..........................13

T

FX NRZ to NRZI Encoder .................................13

T

Link Monitor and LED Driver .............................13

Abso lu te Maximum Ratings..................................14

DC Electrical Characteristics ................................15

AC Electrical Characteristics.................................16

Timing Wave for ms ...............................................17

T

100BASE-TX to FX Transmit Timing Diagram...17

T

100BASE-FX to TX Transmit Timing Diagram...17

T

5-Bit Symbol 100Base-TX/FX Transm it Timing

Diagram ............................................................17

T

5-Bit Symbol 100Base-TX/FX Receive Timing

Diagram ............................................................18

Applica tion Circ uit (For Reference Only)...............19

Package Information.............................................21

Ordering Informatio n.............................................22

Disclaimer............................................................22

Company Overview..............................................22

Products...............................................................22

Contact Windows..................................................22

Warning...............................................................22

2 Final

Version: DM9301-DS-F02

May 8, 2000

Features

DM9301

100Mbps Ethern et Fi ber/Twi sted Pai r Si ngle Chi p Media C onvert er

• 100BASE-TX/FX s ingle-chip media converter

• Total bit delay from FX to TX interface is 20 bit

times (10 bit times each direction).

• Optional propagate HALT on no Link condition

• Compliant with IEEE802.3u 100BASE-TX standard

• Compliant with ANSI X3T12 TP-PMD 1995

standard

• Compliant with ANSI X3.166 FDDI-PMD

• Supports Half and Full Duplex operation 100Mbps,

the DM9301 operates in Full Duplex mode at all

times

• High performance 100Mbps clock generator and

data recovery circuit

• Controlled output edge rates in the 100Base-TX

transmitter without the need for an external filte r

• LED support for FX Link, TX link , FX receive data,

TX receive data, FX code group error and TX code

group error.

• Built in LED test, all LED will light during a reset

condition on the DM9301

• Digital clock recovery and regeneration circuit

usin g a n a d va n ce d dig it al al gorithm to minimi z e

jitter

• Supports diagnostic T X t o TX anal og l oopbac k and

FX to FX analog loopback (Loopback at the NRZI

interface)

• Supports diagnostic T X t o TX di gital loopback and

FX to FX digital loopback (Loopback at the 5B

symbol interface)

• Low-power, high-performance CMOS process

• Available in a 100 QFP package

Final 3

Version: DM9301 - DS -F02

May 8, 2000

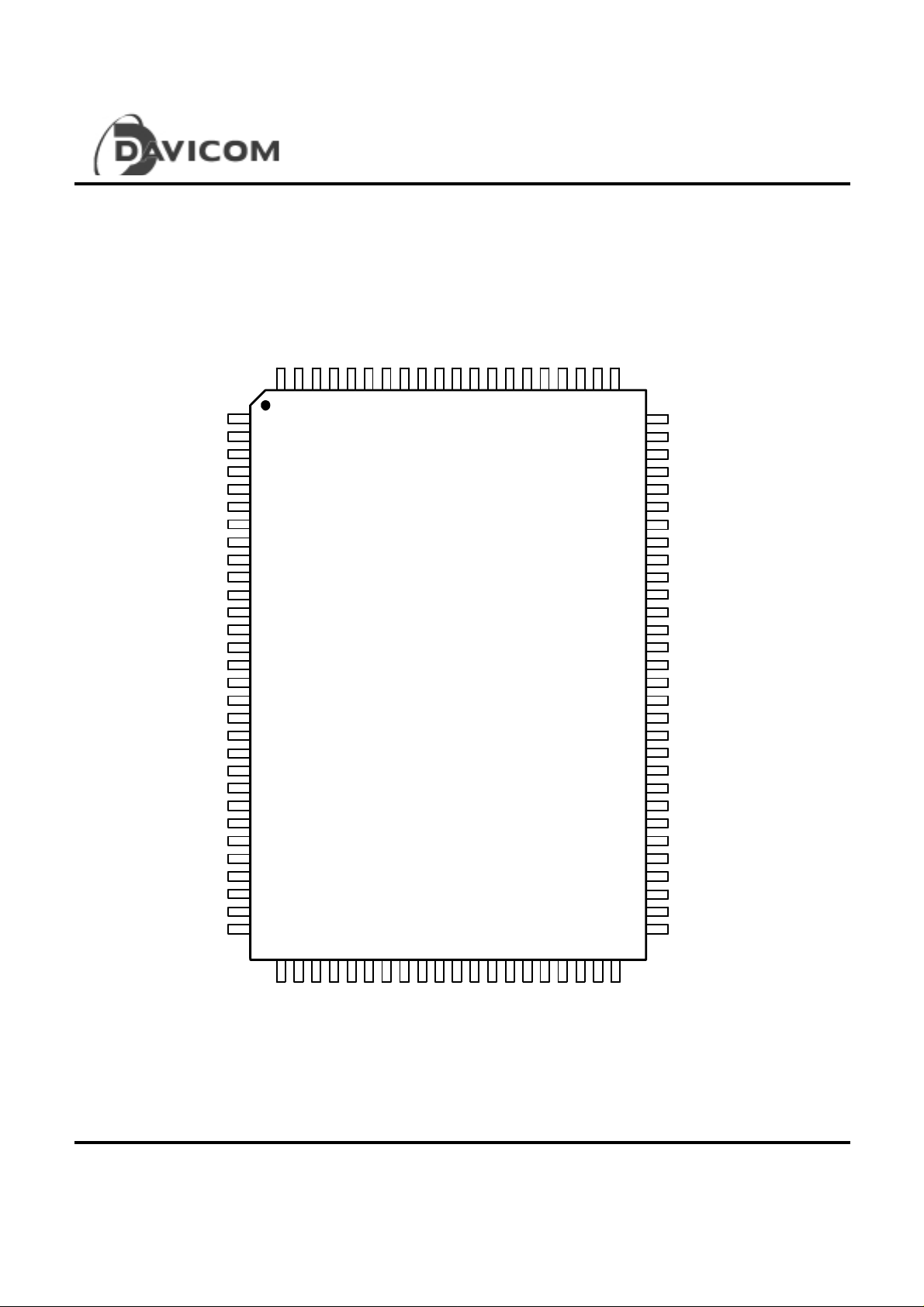

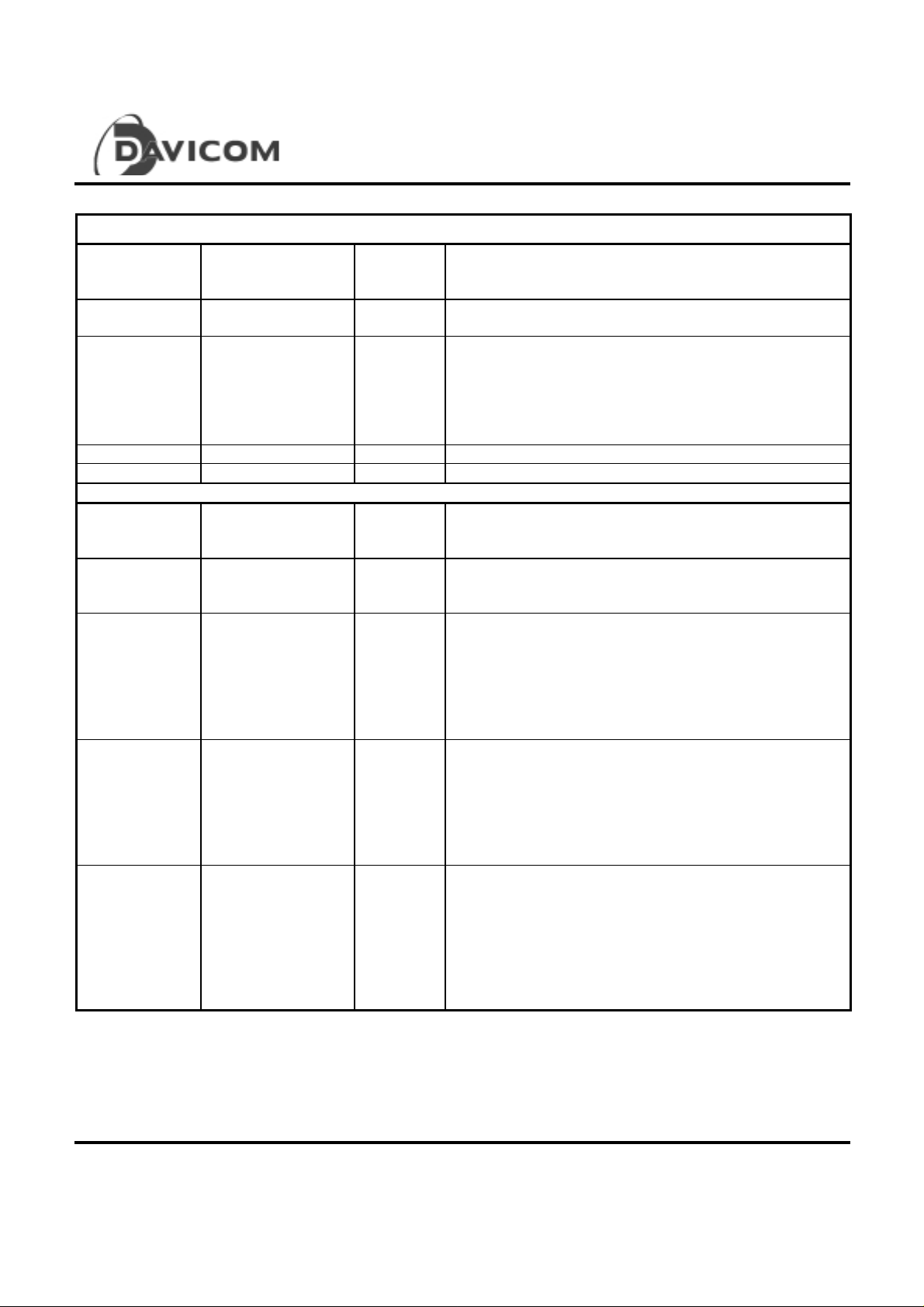

Pin Configu ration: DM9301 F QFP

DM9301

100Mbps Ethern et Fi ber/Twi sted Pai r Si ngle Chi p Media C onvert er

TPRXI+

TPRXI-

AVCC

AVCC

AGND

AGND

AVCC

BGREF

BGRET

AVCC

AGND

AGND

TPTXO-

TPTXO+

AVCC

AGND

AGND

PECLTXO-

PECLTXO+

AGND

AVCC

PECLSD-

PECLSD+

PECLRXI-

PECLRXI+

AVCC

OSC/X1

X2

AGND

OSC/XTL#

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

AGND

AGND

99

100

32

31

DGND

TXDLPBK

97

98

34

33

TPI2

TPI3

DVCC

FXDLPBK

96

CONFIGA

CONFIGB

93

94

95

92

91

DM9301F

39

38

37

36

35

TPI1

DGND

89

90

424041

TPI0

88

43

TPMUX

DVCC

86

87

45

44

RESET#

TRIDRV

84

85

47

46

DGND

DVCC

TESTMODE

81

82

83

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

FXERRLED#

RXD0

DGND

RXD1

RXD2

DVCC

RXD3

RXD4

DGND

TXCLK

RXCLK

FXRCVLED#

DGND

FXLNKLED#

DVCC

TPO6

TXLNKLED#

DGND

TXRCVLED#

TPO0

TPO1

DGND

TPO2

TPO3

DVCC

TPO4

TPO5

DGND

TXERRLED#

DVCC

TXD1

AVCC

AGND

DGND

HLTNOLNK

DVCC

TXALPBK

FXALPBK

TPEN

MUXCTL1

DGND

MUXCTL0

BPSCRAM

TXD4

TXD3

TXD2

DVCC

TXD0

FRCFXSD

DGND

4 Final

Version: DM9301-DS-F02

May 8, 2000

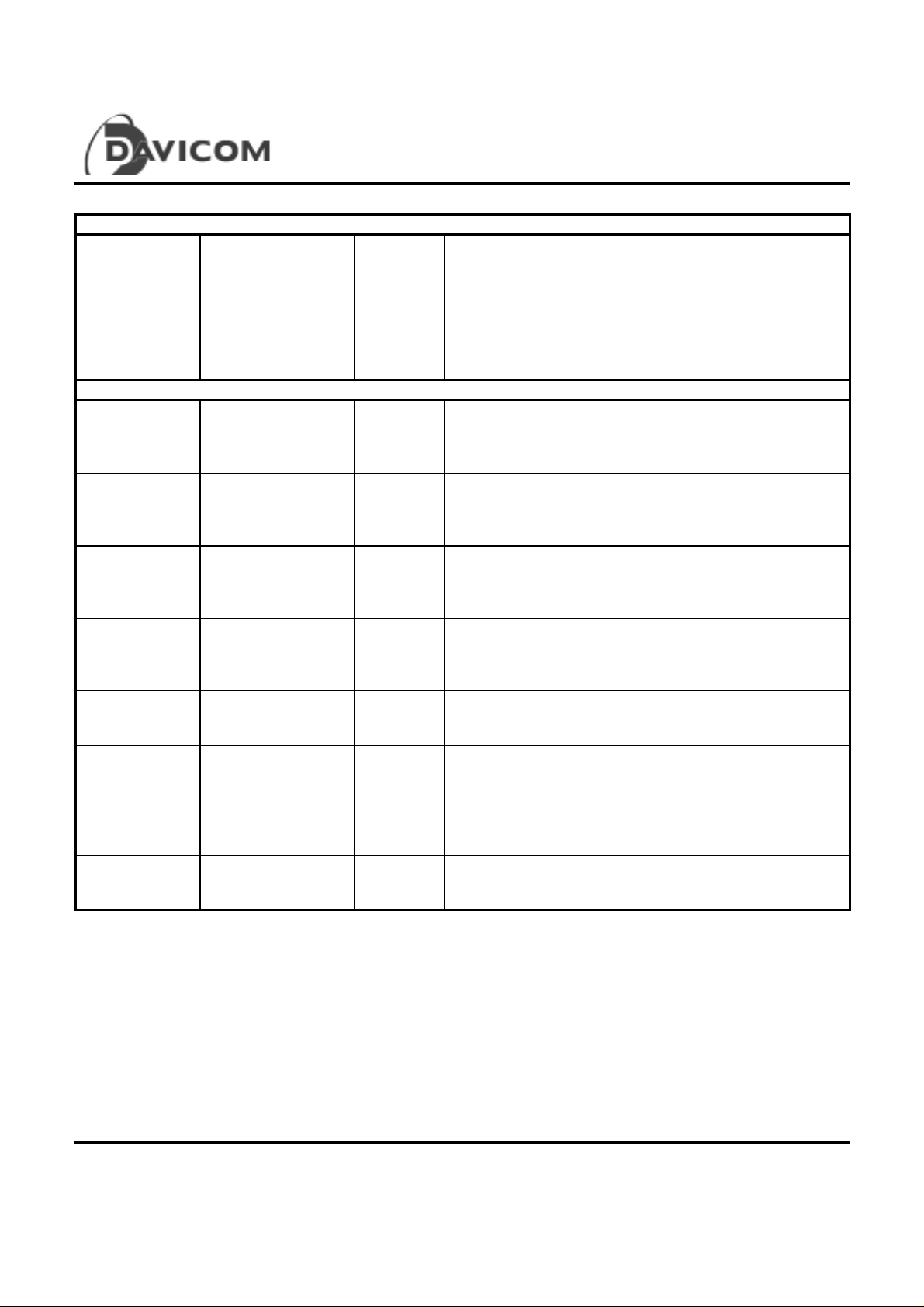

100Mbps Ethern et Fi ber/Twi sted Pai r Si ngle Chi p Media C onvert er

Pin Description

Pin No. Pin Name I/O Description

Media Interface

1, 2 TPRXI+,

TPRXI-

13, 14 TPTXO-,

TPTXO+

24, 25 PECLRXI-,

PECLRXI+

18, 19 PECLTXO- ,

PECLTXO+

22, 23 PECLSD-,

PECLSD+

Clock and Misc. Interface

27 OSCI/X1 I

28 X2 O

30 OSC/XTL# I

8BGREFI

9BGRETI

I

O

I

O

I

100Mbps-TX Differential Input Pair:

These pins are differential receive input for 100BASETX. They are capable of receiving 100BASE-TX MLT-3

data.

100BASE-TX Differential Output Pa i r:

These outputs drive MLT-3 encoded data over 100Mbps

twisted pair cable and provide controlled rise and fall

times designed to filter the transmitter output,

reducing any associated EMI.

100BASE-FX PECL Receive Data Differential Pair:

These pins are differential receive input for 100BASEFX PECL. They are capable of receiving PECL

100BASE-FX NRZI data.

100BASE-FX Transmit Differential Out pu t Pair:

These outputs drive NRZI encoded data for PECL FX

interface.

100BASE-FX PECL Signal detect:

These pins are differential signals t hat indicate to the

DM9301 that the Optical Module interface is detecting

valid optical energy.

Cryst al or Oscillat or Input:

This pin should connect t o one side of a 25MHz, 50ppm

crystal if OSC/XTL#=0. This pi n is the 25MHz, 50ppm

external TTL oscillator input, if OSC/XTLB=1.

Crystal Oscillat or Output:

The othe r side of a 25MH z, 50ppm c rystal should

connect to thi s pin if OSC/XTL#=0. Leave this pin open

if OSC/XTL#=1.

Cryst al or Oscillat or Selec t or Pin:

OSC/XTL#=0: An external 25MHz, 50ppm crystal

should connect to X1 and X2 pins.

OSC/XTL#=1: An external 25MHz, 50ppm oscillator

should connect to X1 and left X2 pin

open.

Bandga p Voltage R eference Resistor:

It connects to a 6.49KΩ, 1% error tolerance resistor

between this pin and BGRET pin 9 to provide an

accurate current reference for the chip.

Bandgap Return

Return pin for 6.49KΩ resistor connection, DO NOT

CONNECT TO GROUND.

DM9301

Final 5

Version: DM9301 - DS -F02

May 8, 2000

100Mbps Ethern et Fi ber/Twi sted Pai r Si ngle Chi p Media C onvert er

Clock and Misc. Interface (Continued)

84 TRIDRV I

85 RESET# I

34 HLTNOLNK I

93 CONFIGA I

95 CONFIGB I

LED Interface

67 FXLNKLED# OD

64 TXLNKLED# OD

69 FXRCVLED# OD

62 TXRCVLED# OD

80 FXERRLED# OD

DM9301

Tristate Digital Output Pin s:

When set high, all digital output pins are set to high

impedance.

Reset: Active Low input that initializes the DM9301,

must be asserted low for 30msecs after VCC is stable.

Send Ha lt on no Link Condition:

Causes the DM9301 to Send out a Halt symbol to the

TX interface if no FX link active or send out a Halt

symbol to the FX interface if no TX link active.

Propagates a no-link condition to the Link P artner if 1,

Idle symbol if 0. Active high

Config A: Must be connected to GND

Config B: Must be connected to GND

FX Link LED:

Indicates Good Link stat us for 100Mbps FX operat ion.

Active low (Open Drain Output)

TX Link LED:

Indicates Good Link stat us for 100Mbps TX operat ion.

Active low (Open Drain Output)

FX Receive LED:

Indicates the presence of receive activity for 100Mbps

FX operation. A ctive low (Open Drain Output)

The DM9301 incorporates a "monostable" function on

the FXRCVLED output. This ensures that ev en

minimum size packets generate adequate LED ON to

insure visibility.

TX Receive LED:

Indicates the presence of receive activity for 100Mbps

TX operation. A ctive low (Open Drain Output)

The DM9301 incorporates a "monostable" function on

the TXRCVLED output. This ensures that ev en

minimum size packets generate adequate LED ON to

insure visibility.

FX Error LED:

Indicates an error was detected by the FX Code Group

Alignment Monitor function on the FX receiver. Active

low (Open Drain Output)

The DM9301 incorporates a "monostable" function on

the FXERRLED output. This ensures that ev en

minimum size errors generate adequate LED ON to

insure visibility.

6 Final

Version: DM9301-DS-F02

May 8, 2000

LED Interface(Continued)

52 TXERRLED# OD

Diagnostic Port Interface

36 FXALPBK I

35 TXALPBK I

96 FXDLPBK I

97 TXDLPBK I

79, 77,

76, 74,

73

70 RXCLK O

48, 47,

45, 44,

43

71 TXCLK O

RXD0, RXD1,

RXD2, RXD3,

RXD4

TXD0, TXD1,

TXD2, TXD3,

TXD4

DM9301

100Mbps Ethern et Fi ber/Twi sted Pai r Si ngle Chi p Media C onvert er

TX Error LED:

Indicates an error was detected by the TX Code Group

Alignment Monitor function on the TX receiver. Active

low (Open Drain Output)

The DM9301 incorporates a "monostable" function on

the TXERRLED output. This ensures that ev en

minimum size errors generate adequate LED ON to

insure visibility.

FX Interface Analog Loop Back:

Loops the FX NRZI analog transmit data path to the FX

NRZI analog receive path.

Initiated at a H/W reset. Active high.

TX Interface Analog Loop Back:

Loops the TX NRZI analog transmit data path to the TX

NRZI analog receive path.

Initiated at a H/W reset. Active high.

FX Interface Digital Loop Back:

Loops the FX 5-bit symbol digital transmit data path to

the FX 5-bit symbol digital receive path.

Initiat ed at a H/W reset. Active high.

TX Interface Digital Loop Back:

Loops the TX 5-bit symbol digital transmit data path to

the TX 5-bit symbol digital receive path.

Initiated at a H/W reset. Active high.

0

I

Receive Data 4 through 0:

The receive data 5-bit symbol interface. Data is clocked

out on the falling edge of RXCLK.

Receive Clock:

25 Mhz recovered clock, clock source is selected by the

MUXCTL1 and MUXCTL0.

Transmit Data 4 through 0:

The transmit data 5-bit symbol interface. Data is clocked

in on the rising edge of TXCLK.

Transmit Clock:

25 Mhz recovered clock, clock source is selected by the

MUXCTL1 and MUXCTL0.

Final 7

Version: DM9301 - DS -F02

May 8, 2000

Loading...

Loading...