Davicom DM8108 Datasheet

General Description

L

C

U

DM8108

8 port 10/100M Fast Ethernet Swit ching Control ler

The DM8108 is an 8 port 10/100Mbit/s nonblocking

Ethernet switch with on-chip address-lookup engine. The

DM8108 provides a low-cost, high-performance switch

solution with PHYs and single SGRAM.

The DM8108 provides eight 10/100Mbit/s Fast Ethernet

interface. In half-duplex mode, all ports support backpressure capability to reduce the risk of data loss for a long

burst of activity. In the full-duplex mode of operation, the

device uses IEEE std. 802.3 frame-based pause protocol

for flow control. With full-duplex capability, port 0 – 7 s upport

1.6Gbit/s aggregate bandwidth connections. The DM8108

also supports port trunking/load balancing on the

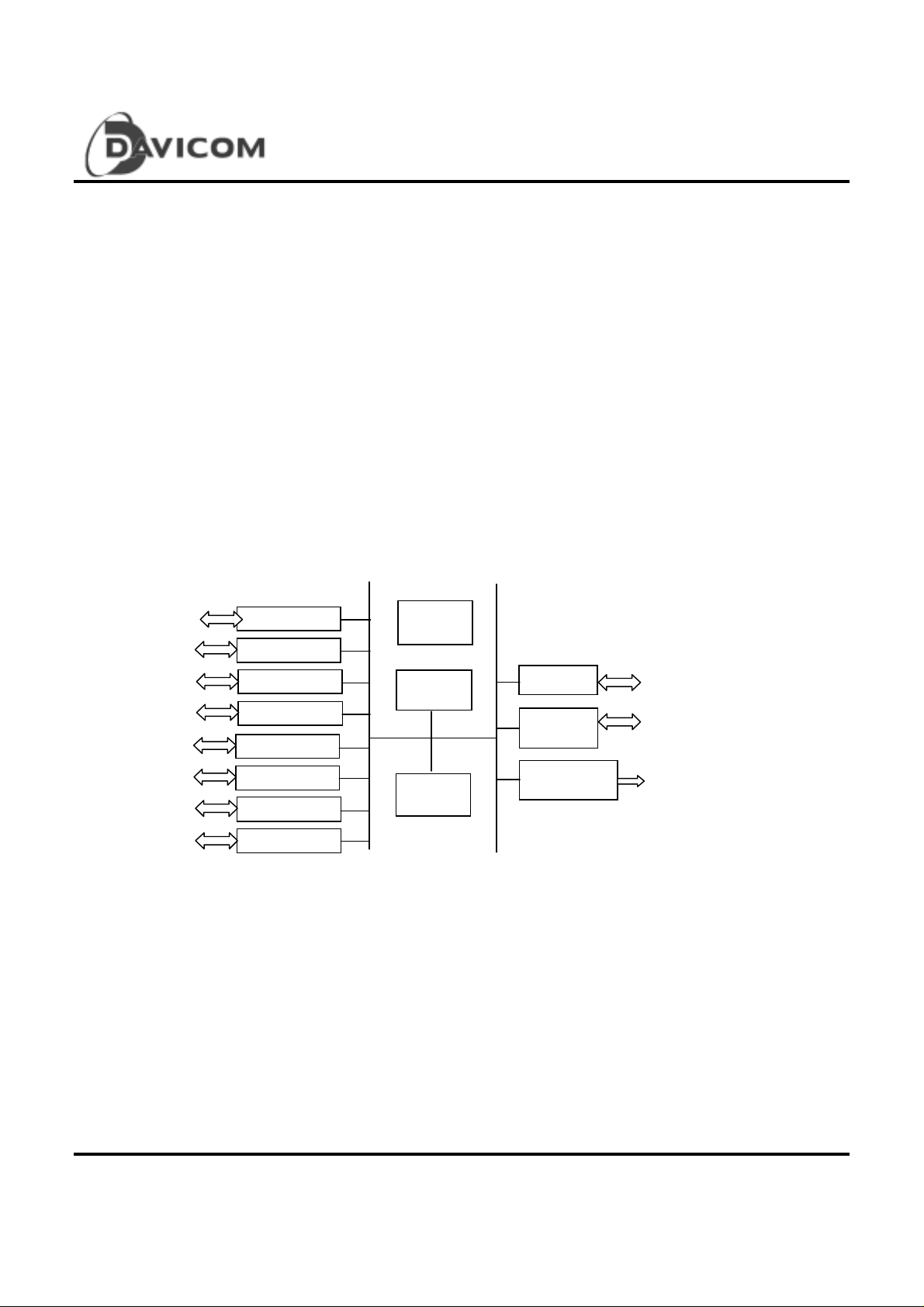

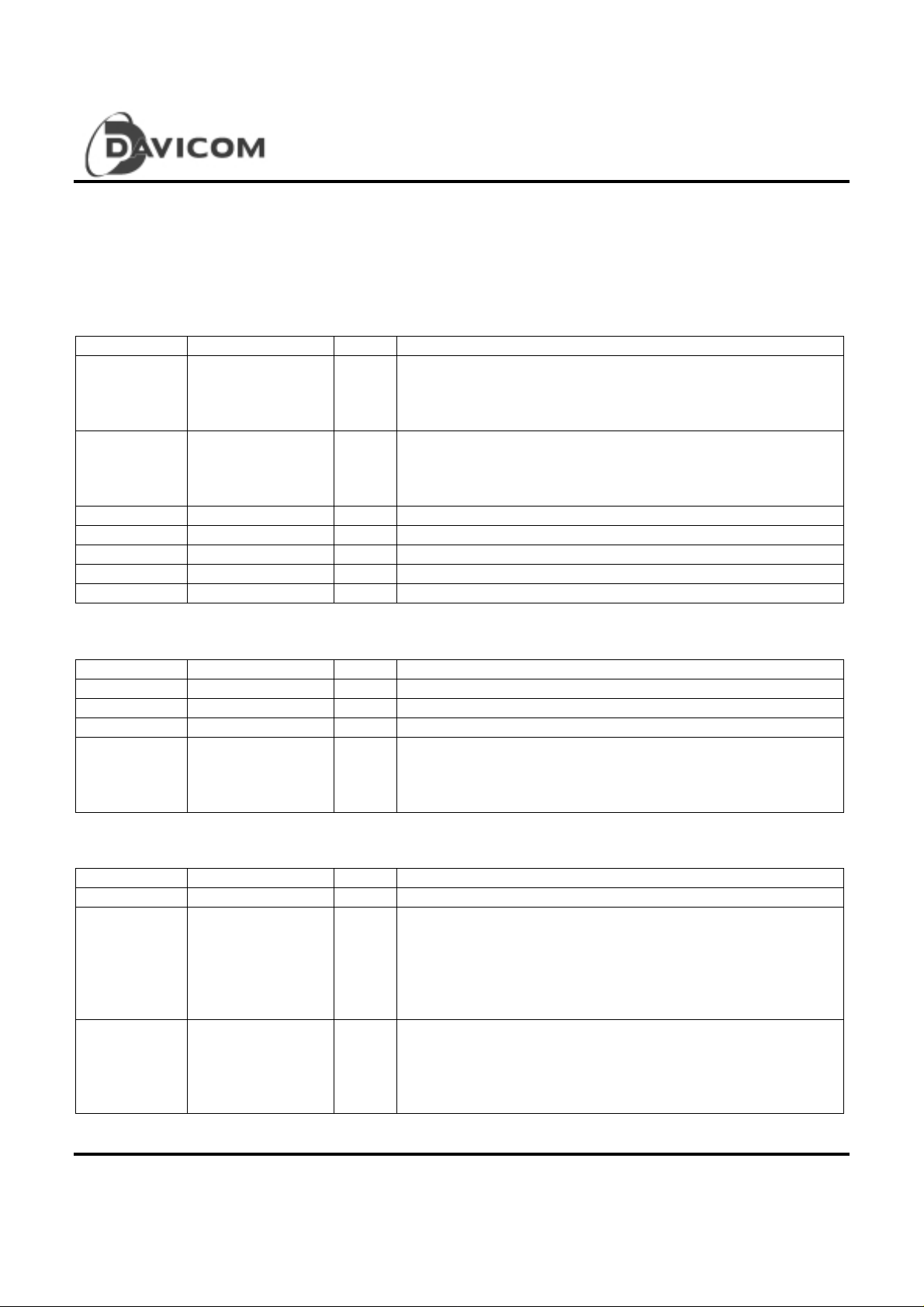

Block Diagram

Contro l &

Status

Address

earning

10/100Mbit ports. This can be used to group ports on interswitch links to increase the effective bandwidth between the

systems.

The internal address-lookup engine supports up to 16.25K

unicast and unlimited multica st and broadc ast addresses.

This engine performs destination and source addresses

book-keeping and comparison which also forwards

unknown destination address packets to all ports.

The DM8108 is fabricated with a .35um technology.

Working at 3.3V, the inputs are 5V to le ran t and the outputs

are capable of directly driving at TTL leve ls.

Expansion

MEM

ontroller

Switching

Engine

LED Control

nit

Preliminary 1

Version: DM8108-DS-P02

November 25, 1999

Features

T

Low cost Fast Ethernet Switching Controller.

O Provide packet switching functions between

eight

10/100Mbps, auto-negotiated on-chip Fast

Ethernet ports and a proprietary Full-duplex

Expansion port.

O Cascade max. 8 DM8108s without extra glue

logic for 64-port configuration.

T

Incorporates three 802.3 compliant 10/100Mbps

Media Access Controllers

O Direct interface to MII (Media Independent

Interface)

O Half/Full Duplex Support for individual port (upto

200Mbps/port)

O IEEE 802.3 100Base-TX, T4.FX compatible

T

Auto-negotiation supported through Serial MII

interface

T

High-performance Distributed Switching Engine

O Performs packet forwarding and filtering at full

wire-speed

O 148,800 packets/sec. on each Ethernet port

T

Direct support for packet buffering

O Glue-less interface with 1 or 2 Mbytes of SDRAM

(SGRAM)

O 32 bit memory bus configuration

O 66 Mhz – 90Mhz memory bus speed

O Up-to 1.1K buffers, 1536-byte each, allocated to

receive ports

T

Support Store and Forward switching approach

DM8108

8 port 10/100M Fast Ethernet Swit ching Control ler

O Low last-bit to first-bit out del ay

O Allow mixed speed Ethernet packet switching

O Allow conversion between different protocols

T

Flow control

O Support partitioning function

O Support back-pressure while lack of internal

resources

O Support 802.3x PAUSE function in full duplex

mode

O Support up to 4-port trunking for 800Mbps

bandwidth

T

Advanced Address Learning and Searching

O Self learning mechanism

O Cache 128 address entries internally

O Record up-to 16K Uni-cast MAC addresses and

unlimited Multicast and Broadcast addresses

O Automatic aging scheme

O Broadcast filtering rate control

T

Expansion Bus

O Up-to 8 SW devices can be cascaded via

expansion bus without extra logic

O Full duplex mode transfer

O Less Bus overhead

O Automatic flow control

T

Complete status report to a simple LED interface

T

Suitabl e for low cost Switc h market to replace

Hub

T

0.35m process, 3. 3V wit h 5V tolerant I/O

T

208-pin PQFP package

2 Preliminary

Version: DM8108-DS-P02

November 25, 1999

8 port 10/100M Fast Ethernet Swit ching Control ler

r

r

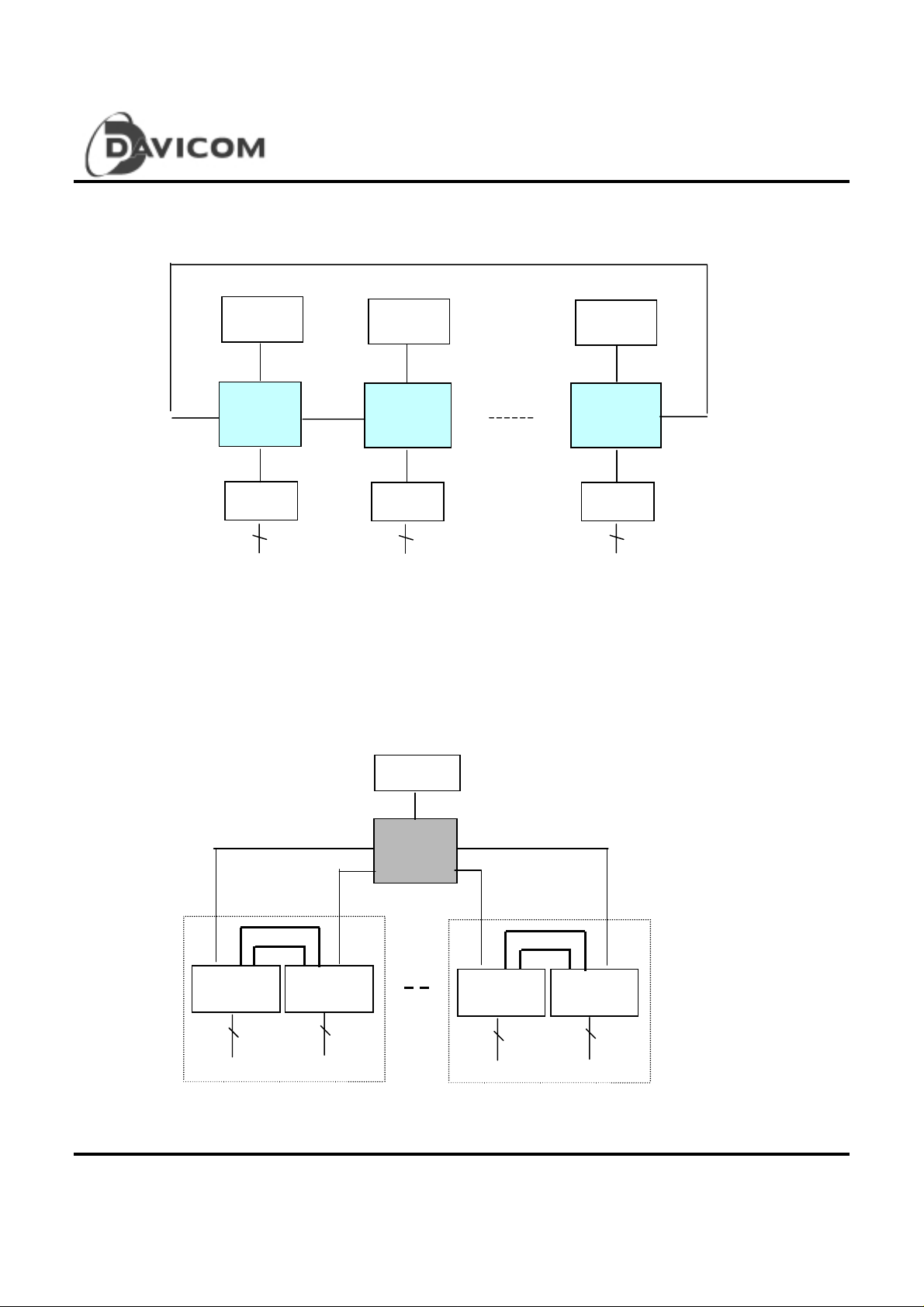

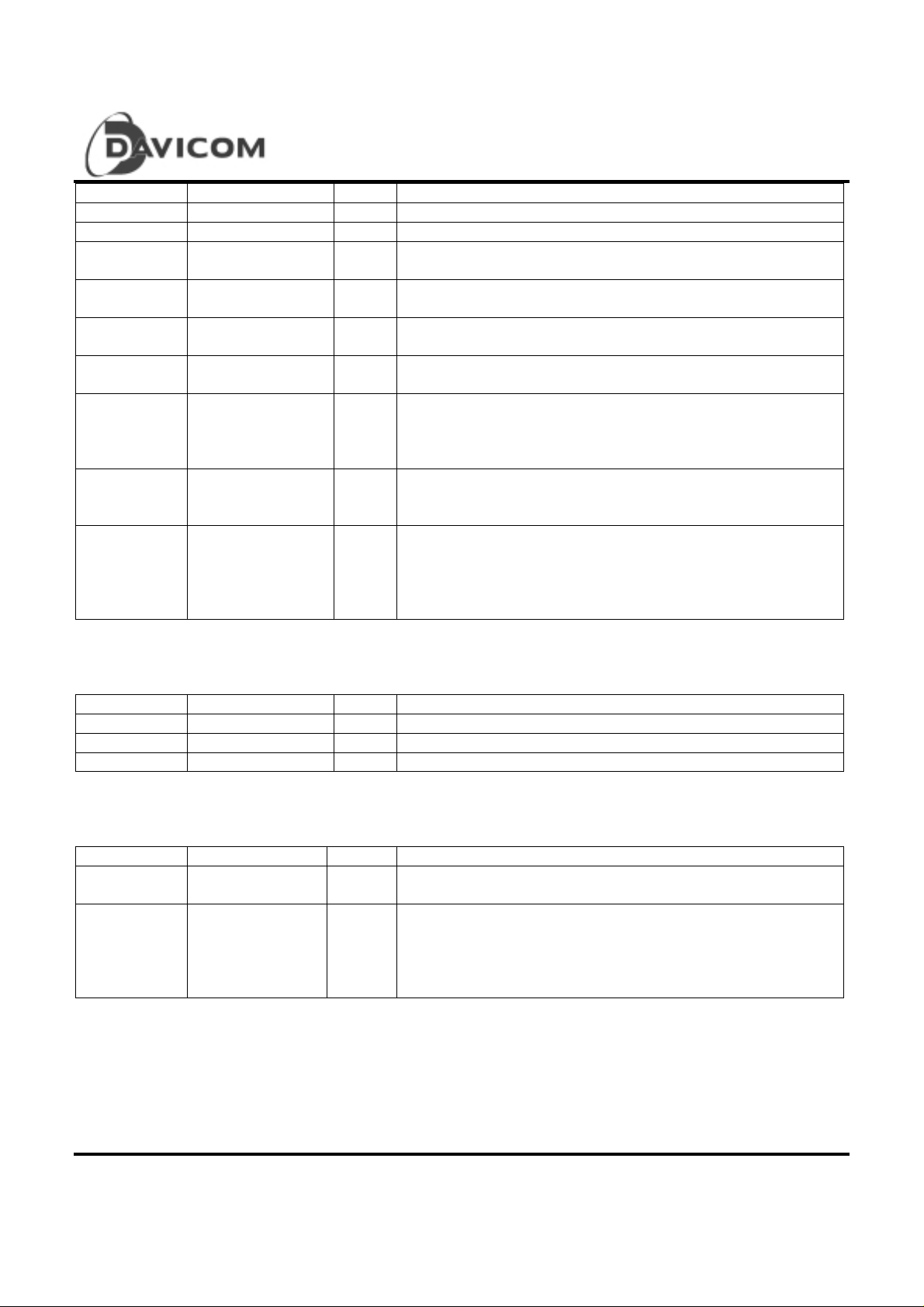

Applica tion Example: Low cost 8 to 64 ports 10/100 Mbps auto-sensing switch

DM8108

MEM

DM8108

PHY

8 8

8

MEM

DM8108

PHY

MEM

DM8108

PHY

Applica tion Exa mple : Low cost auto-sens ing switc hing hub implementation

Cascaded up-to 64 10/100Mbps Fast Ethernet ports

10/100 BaseTx

MEM

MII MII

#1 Hub Module #4 Hub Module

10/100 BaseTx

Preliminary 3

Version: DM8108-DS-P02

November 25, 1999

PHY with

PHY with

DM8108

PHY with

epeater

PHY with

epeater

8 port 10/100M Fast Ethernet Swit ching Control ler

High density mixed switching and hub ports with 8 collision domains

DM8108

4 Preliminary

Version: DM8108-DS-P02

November 25, 1999

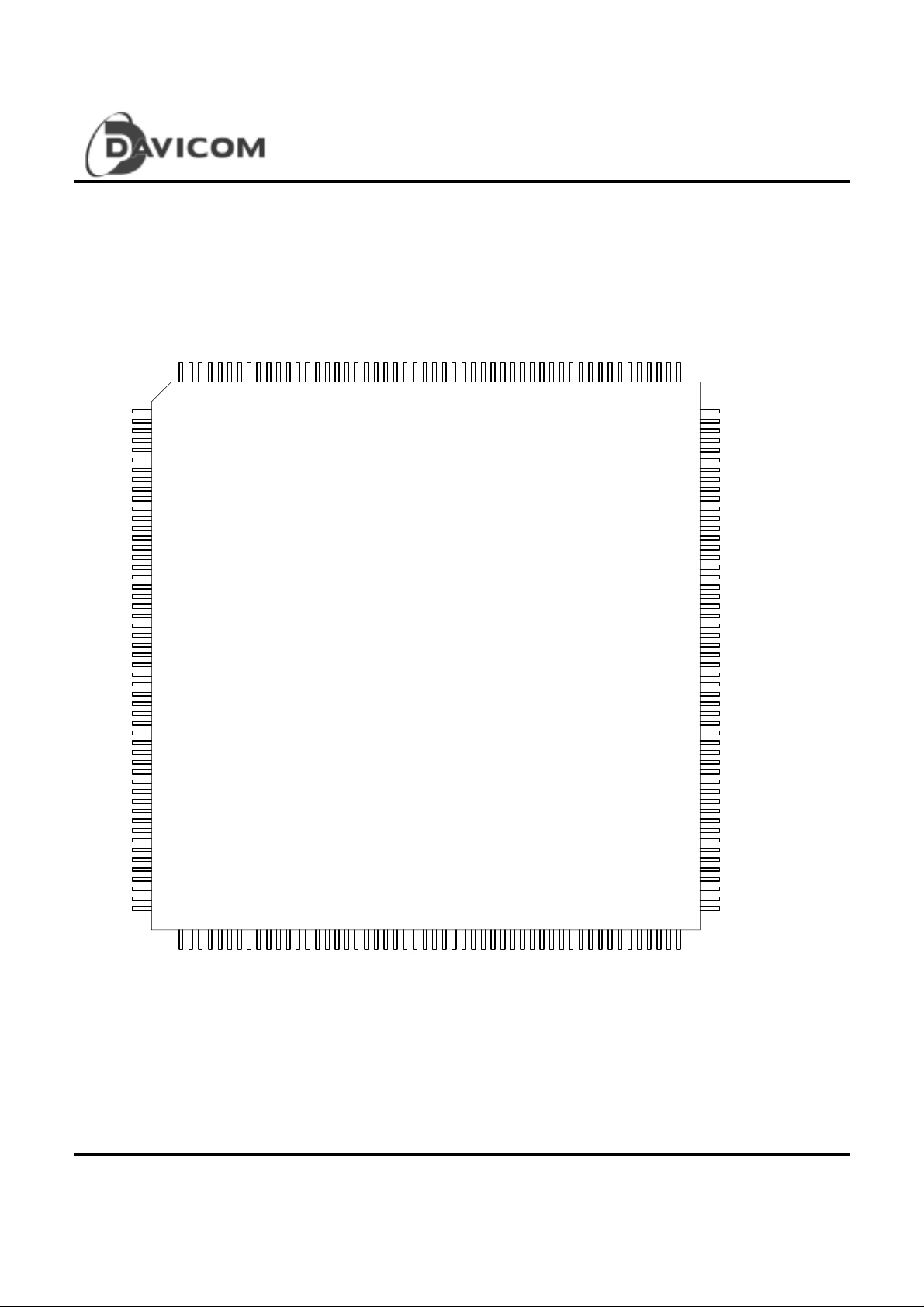

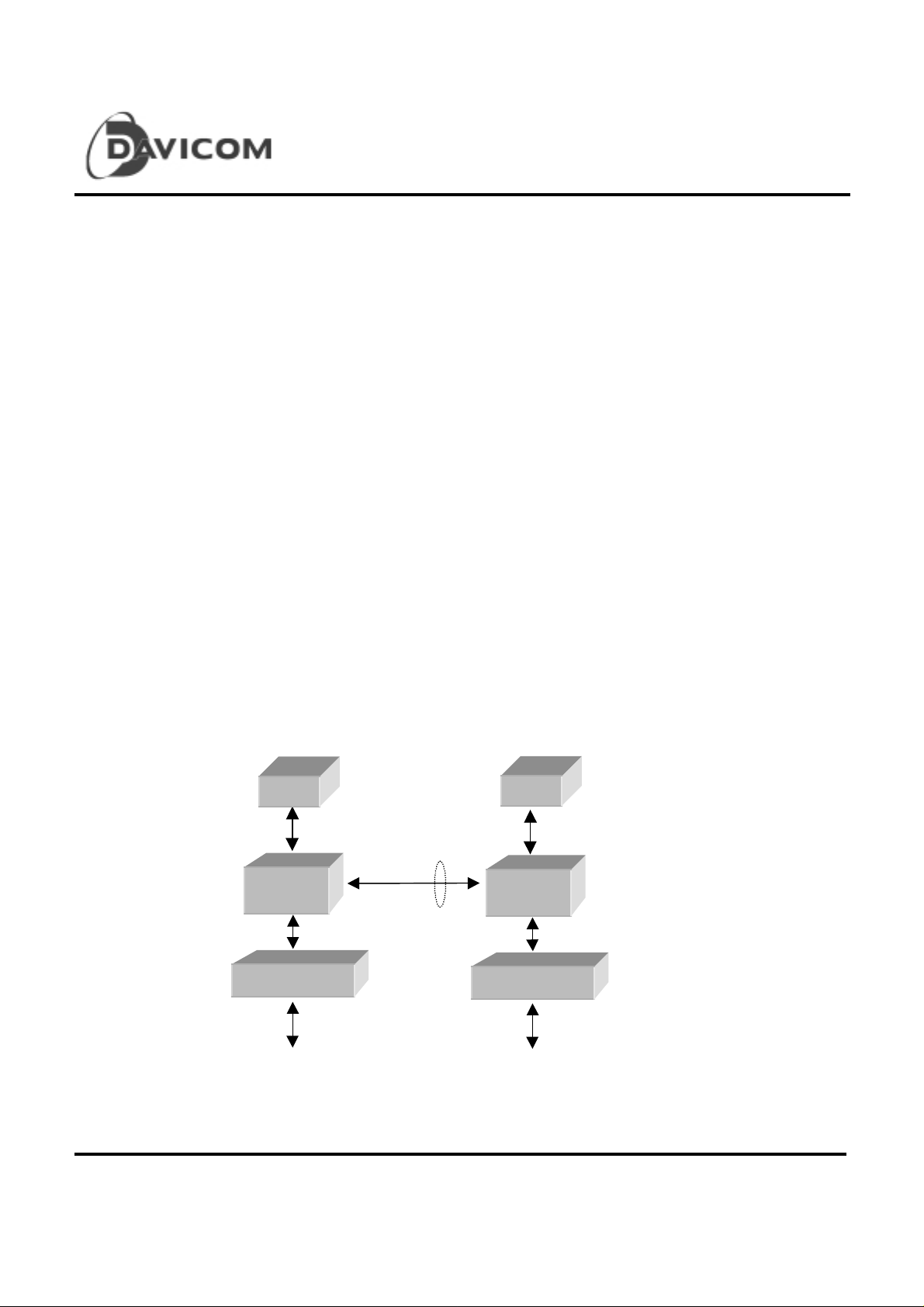

Pin Configuration

DM8108

8 port 10/100M Fast Ethernet Swit ching Control ler

VSS

LEDCLK

LEDSTB

LEDD

RST#

TESTEN

VSS

RXER0

RXDV0

COL0

CRS0

RXCLK0

RXD0[0]

RXD0[1]

RXD0[2]

RXD0[3]

TXCLK0

TXEN0

TXD0[0]

TXD0[1]

TXD0[2]

TXD0[3]

VDD

RXER1

RXDV1

COL1

CRS1

RXCLK1

RXD1[0]

RXD1[1]

RXD1[2]

RXD1[3]

TXCLK1

TXEN1

TXD1[0]

TXD1[1]

TXD1[2]

TXD1[3]

VSS

RXER2

RXDV2

COL2

CRS2

RXCLK2

RXD2[0]

RXD2[1]

RXD2[2]

RXD2[3]

TXCLK2

TXEN2

TXD2[0]

TXD2[1]

RXCLK8

VSS

TXD8[3]

TXD8[2]

TXD8[1]

TXD8[0]

202

201

200

199

VDD

198

RXD8[0]

RXD8[2]

RXD8[1]

RXD8[3]

203

204

205

206

207

208

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

5355545657585960616263646566676869707172737475767778798081828384858687888990919293949596979899

TXCLK8

VSS

DMA0

195

196

197

DMA2

DMA1

DMA3

DMA4

VSS

DMA5

189

190

191

192

193

194

DM8108

DMA6

DMA7

187

188

DMA8

VDD

185

186

DMA9

SBA

183

184

DWE#

VSS

SDDQM#

180

181

182

SDCS#

CAS#

178

179

VSS

RAS#

176

177

SCLK

VSS

174

175

DMD0

DMD1

172

173

DMD3

DMD2

170

171

DMD4

DMD5

168

169

DMD6

DMD7

166

167

VSS

165

DMD9

DMD8

163

164

DMD11

DMD10

DMD12

160

161

162

100

101

DMD15

DMD14

DMD13

158

159

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

102

103

104

157

VDD

DMD16

DMD17

DMD18

DMD19

DMD20

DMD21

DMD22

DMD23

VSS

DMD24

DMD25

DMD26

DMD27

DMD28

DMD29

DMD30

DMD31

VSS

TXD7[3]

TXD7[2]

TXD7[1]

TXD7[0]

TXEN7

TXCLK7

RXD7[3]

RXD7[2]

RXD7[1]

RXD7[0]

RXCLK7

CRS7

COL7

RXDV7

RXER7

VDD

TXD6[3]

TXD6[2]

TXD6[1]

TXD6[0]

TXEN6

TXCLK6

RXD6[3]

RXD6[2]

RXD6[1]

RXD6[0]

RXCLK6

CRS6

COL6

RXDV6

RXER6

VSS

TXD5[3]

VDD

TXD2[2]

TXD2[3]

COL3

RXER3

RXDV3

CRS3

RXCLK3

RXD3[2]

RXD3[0]

RXD3[1]

TXEN3

RXD3[3]

TXCLK3

TXD3[1]

TXD3[0]

TXD3[2]

TXD3[3]

MIID

MIICLK

RXER4

RXDV4

COL4

CRS4

RXD4[1]

RXD4[0]

RXCLK4

RXD4[2]

TXCLK4

RXD4[3]

TXEN4

TXD4[0]

TXD4[1]

TXD4[3]

TXD4[2]

VDD

RXER5

COL5

RXDV5

CRS5

RXCLK5

RXD5[0]

RXD5[2]

RXD5[1]

TXEN5

RXD5[3]

TXCLK5

TXD5[0]

TXD5[1]

TXD5[2]

VSS

VSS

Preliminary 5

Version: DM8108-DS-P02

November 25, 1999

DM8108

8 port 10/100M Fast Ethernet Swit ching Control ler

Pin Description

Pin Ass ignme nt

# NAME # NAME # NAME # NAME # NAME

1 VSS 43 CRS2 85 TXEN4 127 RXCLK7 169 MD(4)

2 LEDCLK 44 RXCLK2 86 TXD4(0) 128 RXD7(0) 170 MD(3)

3 LEDSTB 45 RXD2(0) 87 TXD4(1) 129 RXD7(1) 171 MD(2)

4 LEDD 46 RXD2(1) 88 TXD4(2) 130 RXD7(2) 172 MD(1)

5 RST* 47 RXD2(2) 89 TXD4(3) 131 RXD7(3) 173 MD(0)

6 TESTEN* 48 RXD2(3) 90 VDD 132 TXCLK7 174 VSS

7 VSS 49 TXCLK2 91 RXER5 133 TXEN7 175 SCLK

8 RXER0 50 TXEN2 92 RXDV5 134 TXD7(0) 176 VSS

9 RXDV0 51 TXD2(0) 93 COL5 135 TXD7(1) 177 SRAS*

10 COL0 52 TXD2(1) 94 CRS5 136 TXD7(2) 178 SDCAS*

11 CRS0 53 TXD2(2) 95 RXCLK5 137 TXD7(3) 179 SDCS*

12 RXCLK0 54 TXD2(3) 96 RXD5(0) 138 VSS 180 SDWE*

13 RXD0(0) 55 VDD 97 RXD5(1) 139 MD(31) 181 VSS

14 RXD0(1) 56 RXER3 98 RXD5(2) 140 MD(30) 182 SDQM*

15 RXD0(2) 57 RXDV3 99 RXD5(3) 141 MD(29) 183 MA(10) – SBA

16 RXD0(3) 58 COL3 100 TXCLK5 142 MD(28) 184 MA(9)

17 TXCLK0 59 CRS3 101 TXEN5 143 MD(27) 185 VDD

18 TXEN0 60 RXCLK3 102 TXD5(0) 144 MD(26) 186 MA(8)

19 TXD0(0) 61 RXD3(0) 103 TXD5(1) 145 MD(25) 187 MA(7)

20 TXD0(1) 62 RXD3(1) 104 TXD5(2) 146 MD(24) 188 MA(6)

21 TXD0(2) 63 RXD3(2) 105 TXD5(3) 147 VSS 189 MA(5)

22 TXD0(3) 64 RXD3(3) 106 VSS 148 MD(23) 190 VSS

23 VDD 65 TXCLK3 107 RXER6 149 MD(22) 191 MA(4)

24 RXER1 66 TXEN3 108 RXDV6 150 MD(21) 192 MA(3)

25 RXDV1 67 TXD3(0) 109 COL6 151 MD(20) 193 MA(2)

26 COL1 68 TXD3(1) 110 CRS6 152 MD(19) 194 MA(1)

27 CRS1 69 TXD3(2) 111 RXCLK6 153 MD(18) 195 MA(0)

28 RXCLK1 70 TXD3(3) 112 RXD6(0) 154 MD(17) 196 VSS

29 RXD1(0) 71 VSS 113 RXD6(1) 155 MD(16) 197 TXENCLK

30 RXD1(1) 72 MDCLK 114 RXD6(2) 156 VDD 198 VDD

31 RXD1(2) 73 MDIO 115 RXD6(3) 157 MD(15) 199 TXD8(0)

32 RXD1(3) 74 VSS 116 TXCLK6 158 MD(14) 200 TXD8(1)

33 TXCLK1 75 RXER4 117 TXEN6 159 MD(13) 201 TXD8(2)

34 TXEN1 76 RXDV4 118 TXD6(0) 160 MD(12) 202 TXD8(3)

35 TXD1(0) 77 COL4 119 TXD6(1) 161 MD(11) 203 VSS

36 TXD1(1) 78 CRS4 120 TXD6(2) 162 MD(10) 204 RXDVCLK

37 TXD1(2) 79 RXCLK4 121 TXD6(3) 163 MD(9) 205 RXD8(0)

38 TXD1(3) 80 RXD4(0) 122 VDD 164 MD(8) 206 RXD8(1)

39 VSS 81 RXD4(1) 123 RXER7 165 VSS 207 RXD8(2)

40 RXER2 82 RXD4(2) 124 RXDV7 166 MD(7) 208 RXD8(3)

41 RXDV2 83 RXD4(3) 125 COL7 167 MD(6)

42 COL2 84 TXCLK1 126 CRS7 168 MD(5)

6 Preliminary

Version: DM8108-DS-P02

November 25, 1999

DM8108

8 port 10/100M Fast Ethernet Swit ching Control ler

Pin Description

Please refer to the “Strap pin default value after reset section” for the detail description of the

Strap pins.

DRAM Interfac e

Pin No. Pin Name I/O Description

139 – 146,

148 – 155,

157 – 164,

166 – 173

183 – 184,

186 – 189,

191 – 195

177 SRAS* O Row address strobe for SDRAM

178 SDCAS* O Column address strobe for SDRAM

180 SDWE* O Write cycle indication, internally pulled up

182 SDQM O Data Mask f or SDRAM

179 SDCS* O Chip select for SDRAM

Expansion B us

(continued)

MD(31:0) I/O DRAM data lines 31 – 0

MA(10:0) I/O DRAM address lines 10-0; strap pins during reset

MA9: 0= enable limit4, 1=disbale limit 4

MA8: DRAM size selection; 0= 1M, 1=2M

MA7-0: Auto-negotiation enable for port 7-0; 0= enabled

Pin No. Pin Name I/O Description

204 RXDVCLK I/O Expansion port’s receiving data valid

208 – 205 RXD8[3:0] I/O Expansion port’s receive data input

197 TXENCLK I/O Expansion port’s transmit enable output

202 – 199 TXD8[3:0] I/O Expansion port’s transmit data output

Strap pins during reset:

TXD8[2:0] = device # setting

TXD8[3] = dram timi ng

LED Interface

Pin No. Pin Name I/O Description

2 LEDCLK O LED data clock

4 LEDD O LED data: active low. Data stream that contains LED indicators per

port. The data is shifted out and should be qualified by LDSTB* to

clock into ext er nal regi st er s to driv e L EDs.

Strap pin during re set:

0: expansion port with fast speed

1: expansion port with lower apees

3 LDSTB I/O LED data strobe: active high. Used to strobe the LD into an external

register

Strap pin during re set:

0: force link

1: link detection through serial MII

Preliminary 7

Version: DM8108-DS-P02

November 25, 1999

8 port 10/100M Fast Ethernet Swit ching Control ler

MII Interfa ce

Pi n No. Pin Name I/O Description

133,117,101,

85,66,50,34,18

132,116,100,84,

65,49,33,17

22 – 19 TXD0(3:0) B Transmit data for port 0; synchronous to TXCLK0.

38 – 36 TXD1(3:0) B Transmit data for port 1; synchronous to TXCLK1.

54 – 51 TXD2(3:0) B Transmit data for port 2; synchronous to TXCLK2.

70 – 67 TXD3(3:0) B Transmit data for port 3; synchronous to TXCLK3.

89 – 86 TXD4(3:0) O Transmit data for port 4; synchronous to TXCLK4.

105 –102 TXD5(3:0) O Transmit data for port 5; synchronous to TXCLK5.

121 –118 TXD6(3:0) O Transmit data for port 6; synchronous to TXCLK6.

137 –134 TXD7(3:0) O Transmit data for port 7; synchronous to TXCLK7.

16 – 13 RXD0(3:0) I Receive data for port 0; synchronous to RXCLK0.

32 – 29 RXD1(3:0) I Receive data for port 1; synchronous to RXCLK1.

48 – 45 RXD2(3:0) I Receive data for port 2; synchronous to RXCLK2.

64 – 61 RXD3(3:0) I Receive data for port 3; synchronous to RXCLK3.

83 – 80 RXD4(3:0) I Receive data for port 4; synchronous to RXCLK4.

TXEN(7:0) B Transmi t Enabl e: Activ e high , synchronous to TXCLK; indicate that

the transmission data is valid.

Strap function during reset-TXEN(7:0): 0 = port 7-0 full duplex

TXCLK(7:0) I Transmit Clock: Provides the timing reference for the transfer of

TXEN, TXD signals. It is 25MHz for 100Mbps and 2.5MHz for

10Mbps.

Strap function during reset-TDX0[0]: 0=80Mhz, 1=66Mhz CLOCK operation

TXD0[1]: 0=enable partition mode, 1=disable partition mode

TXD0[2]: 0=enable expansion por t, 1=disa ble e xpansion port

TXD0[3]: 0=init only, 1= enable BIST

Strap function during reset -TXD1[2 :0]: te st mod e

TXD1[3]: 0=enable CRC, 1=disbale CRC

Strap function during reset -TXD2[2:0]: device # setting

TXD2 [3]: DRAM timing 0=fa st, 1= slo w

Strap function during reset -TXD3[0]: 0=max. packet size 1536, 1=max. packet size 1518(default)

TXD3[1]: 0=enable back_pressure, 1= disable (default)

TXD3[3:2]: age strap pins

00= 64 sec. 01= 128 sec.

10= 256 sec. 11= disbale

Strap function during reset –

TXD4[0]: 0= port 0 trunking enable 1= port 0 no trunking (default)

TXD4[1]: 0= port 1 trunking enable 1= port 1 no trunking (default)

TXD4[2]: 0= port 2 trunking enable 1= port 2 no trunking (default)

TXD4[3]: 0= port 3 trunking enable 1= port 3 no trunking (default)

Strap function during reset –

TXD5[1:0]: br oadcast f iltering rate selection

00 = 8k/sec 01 = 16k/sec

10 = 64k/sec 11= disable

DM8108

8 Preliminary

Version: DM8108-DS-P02

November 25, 1999

DM8108

8 port 10/100M Fast Ethernet Swit ching Control ler

99 – 96 RXD5(3:0) I Receive data for port 5; synchronous to RXCLK5.

115 - 112 RXD6(3:0) I Receive data for port 6; synchronous to RXCLK6.

137 - 128 RXD7(3:0) I Receive data for port 7; synchronous to RXCLK7.

127,111,95,79,

60,44,28,12

124,108,92,76,

57,41,25,9

123,107,91,75,

56,40,24,8

126,110,94,78,

59,43,27,11

125,109,93,77,

58,42,26,10

72 MDCLK I/O Serial MII management interface clock signal: 1MHz clock for MDIO

73 MDIO I/O Serial MII management interface data; this bi-direction line is used to

RXCLK(7:0) I Receive clock for port 7 – 0; synchronous to RXD, RXDV,RXER; has

same clock rate as TXCLK.

RXDV(7:0) I Receive data valid indication for port 7 – 0.

RXER(7:0) I Receive data error indication for port 7 – 0.

CRS(7:0) I Carri er sense; acti ve high. Ind icates that either the tra n smit or

receive medium is not Idle. CRS is not synchronous to any clock.

COL( 7:0 ) I C ollis ion De tect ; active high. Indicates a collision has been detected

on the wire.

This input is ignored during full duplex operation and in the half duplex

mode while TXEN of the same port is low.

data reference. Connected to all PHY ports; It is an input pin if t he

device # is not 0 in SDRAM mode; else, it is an output pin.

transfer control Information and status between the PHY and the

DM8108. It conforms to the IEEE-802.3 specifications.

This signal may be connected to the PHY devices of all ports.

Pulled down if not used.

Miscellaneous Interface pins

Pin No. Pin Name I/O Descriptio n

175

5

6

Power pins

Pin No. Pin Name I/O Description

23,55,90,122,

156,185,198

1,7,39,71,74,

106,138,147,

165,174,176,

181,190,196,

203

SCLK

RST*

TESTEN*

VCC

GND

I

Memory clock: used by the DRAM state machine.

I

Reset signal for the chip.

I

Test pin to enable test functions

Power

Ground Connected to Ground plane

Connected to 3.3V Power plane

Preliminary 9

Version: DM8108-DS-P02

November 25, 1999

o

Functional Description

M

DM8108

8 port 10/100M Fast Ethernet Swit ching Control ler

Fast Ethe rnet P orts Functiona l Overv iew

The DM8108 is a high-performance, low-cost Fast

Ethernet Switching Controller which provides packet

switching between eight on-chip, 10/100 Mbps ports

and one optional expansion port. It is suitable for the

auto-sensing 10/100Mbps switch application.

Switching Architecture

The switching architecture is based on the shared memory

and handshaking signals to swi tch pack ets between on-chip

ports hard-wired.

For an incoming packet, the receiving port’s MA C s to r es i t in

the receiv ing buff ers if it i s a good packet. At the same

time, the switching engine determines which port the packet

will forward to and update the address table which will be

used for future packet forwarding reference.

Fast Ethernet Ports

The DM8108 integrates eight Fast Ethernet ports, working

at 10/100Mbps (half-duplex) or 20/200Mbps (full-duplex)

with of f-the-shelf PHY chips. The inte rface is glu e-less

through Media Independent Interfaces (MII). The autonegotiation function determines the port’s operating mode.

With auto-negotiation disabled, the po r ts can be forced to

operate at a certain mode, if so desi red. Each port i n c ludes

the Media Access Control function (MAC), LED signals for

Link, Co llis io n, R e ce ive/Tra ns mit, Ha lf/Full duplex and

Rece ive Bu ffer Full indica tio ns .

Address Recognition

The DM8108 in a system can recognize up t o 1 6K Uni -c ast

MAC addresses and unlimited Multica s t/ Broadca st MAC

addresses. An intelligent address recognition mechanism

enables filtering and forwarding packets at full Ethernet wire

speed. The DM8108 provides an address self-learning

mechanism. As each DM8108 learns new address, it

updates the address table in the storage.

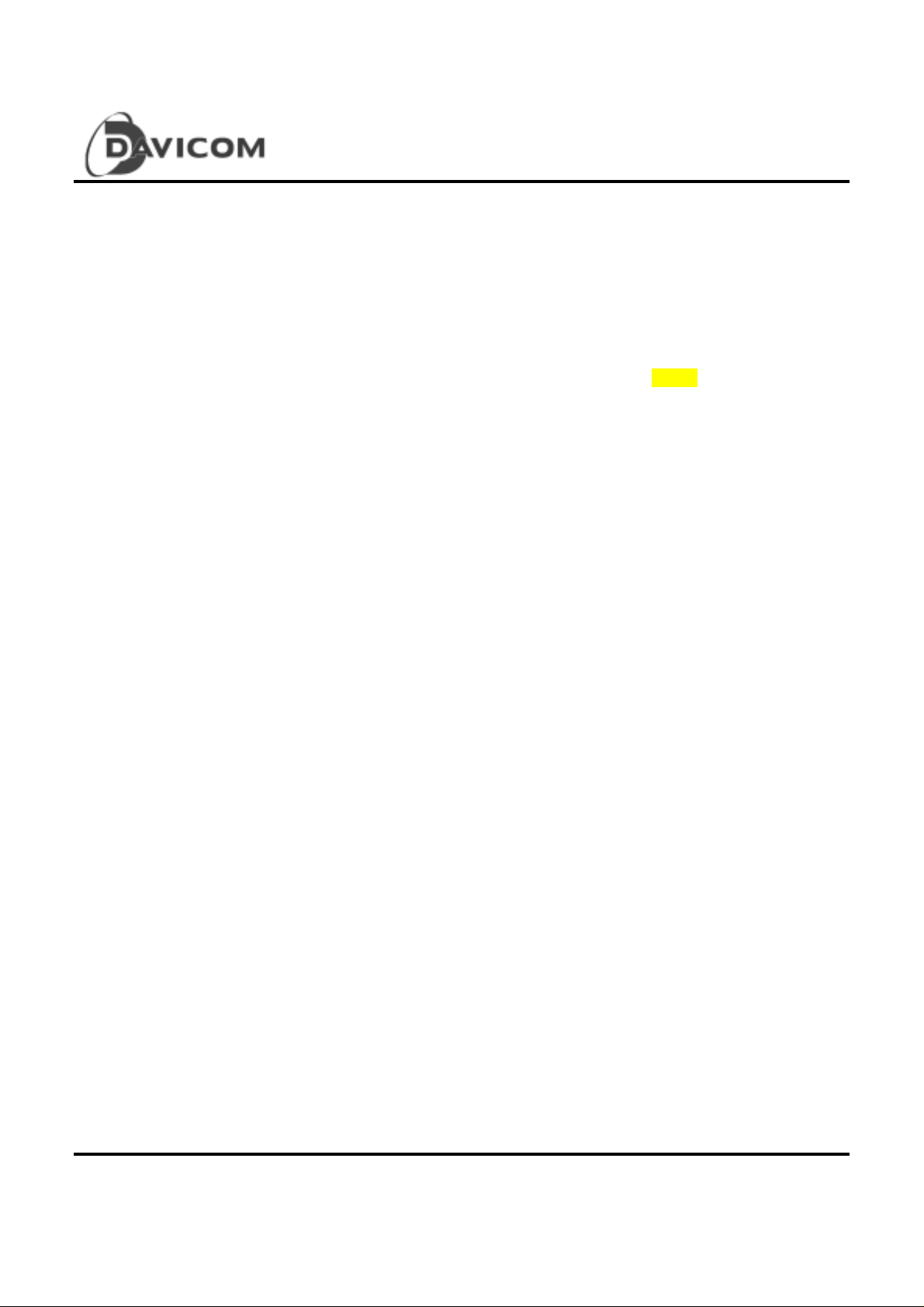

Fig.1: Typical 10/100 Mbps auto-sensing switching hub application

EM

ptional

DM8108

10/100 Mbps PHY

MEM

DM8108

10/100 Mbps PHY

Switch Ports Switch Ports

10 Preliminary

Version: DM8108-DS-P02

November 25, 1999

DM8108

8 port 10/100M Fast Ethernet Swit ching Control ler

Packet Routing

As any port in the DM8108 receives a packet, the DM8108

will p ut th e re ce ived data in the receiving buffer and start the

address recognition at same time.

1. If the destination address is pointed to a local port

other than receiving port, the DM8108 will update the

Transmit Descriptor of the target port with the buffer

location and byte count information and wait for

transmission.

2. If the destination address is pointed to a port located in

other devices, the DM8108 will update the

Transmit Descriptor of the expansion port with the

receiving buffer location and byte count information

and wait for transmission.

3. I

f the destination address is not found in the Address

Table, the DM8108 will update all the Transmit

De s cr ip to r s , exc e pt th e one of t he r ec eivi ng port, for

transmission.

4. For the Multicast/Broadcast addresses, the DM8108

simply updates all the Transmit Descriptors, except

the one of th e re ceiv i ng p o rt or t h e ports that are

disabled, for Transmission.

5. For bad packet, the DM8108 simply discards it.

6. If the receiving buffer or the Transmit Descriptor for a

particular port is full, the packet will be lost.

The DM8108 is targeted for the non-managed Ethernet

Switching application. No management functions provided.

DRAM Interfac e

The DM8108 interfaces to 1M or 2M bytes of SGRAM or

SDRAM. The DRAM is used to store incoming packets as

well as he address table and Transmit Descriptors. The

DRAM can operate at up to

512kx16 SGRAM are required respectively for 1M or 2M

shared memory size.

Expansion B us

The expansion bus contains Receive Port and Transmit

Port. Each po rt is 4- bit wide.

The Receive Port takes the incoming packet into a FIFO

that has to be distributed to the Receiving Buffer

immediately. At the same time, the DM8108 will check th e

destination and source addresses to determine the target

port and update the Address Table if necessary.

The Transmit Port is dedicated for transferring packets out

to other switching members if the Transmit Descriptor for

this port saying the transmission is pending.

90MHz. One 256k x32 o r

Total of 8-DM8108 can be cascaded for a 64-port switching

Network Manage ment Fea tures

Preliminary 11

Version: DM8108-DS-P02

November 25, 1999

system.

Loading...

Loading...