DATEL ADS-325A, ADS-238Q Datasheet

INNOVATION and EX C ELL E N C E

® ®

TEST MODE

FEATURES

• 10-bit, 20MHz sampling

• ±1LSB max. differential nonlinearity

• Internal calibration circuit

• Internal S/H amplifier

• 70MHz input bandwidth

• TTL/CMOS compatible in-out logic

• Latched three-state output data

• Single +5V supply

• Low 150mW power dissipation

• Small 48 pin LQFP package

• Low cost

GENERAL DESCRIPTION

DATEL's ADS-325A is a low power, 10-bit, 20MHz, CMOS

sampling A/D converter. Its small 48 pin plastic LQFP package

contains a S/H amplifier, a 3-state output register, linearity

calibration circuitry, and all necessary control logic. Only two

external reference voltages, an A/D clock and a few digital

inputs are required. The A/D clock may be applied with 50%

duty cycle.

The excellent dynamic performance includes a spurious free

dynamic range of 65dB and a signal-to-noise ratio with

distortion of 54dB with a 3MHz input. ADS-325A is capable of

operating from a single +5V power supply and typically

consumes only 150mW. It can also operate from a +5V analog

S with +3.3V digital VS enabling an interface with 3.3V logic

V

circuitry. The ADS-325A is ideally suited for high quality video/

CCD imaging applications.

Sampling A/D Converter

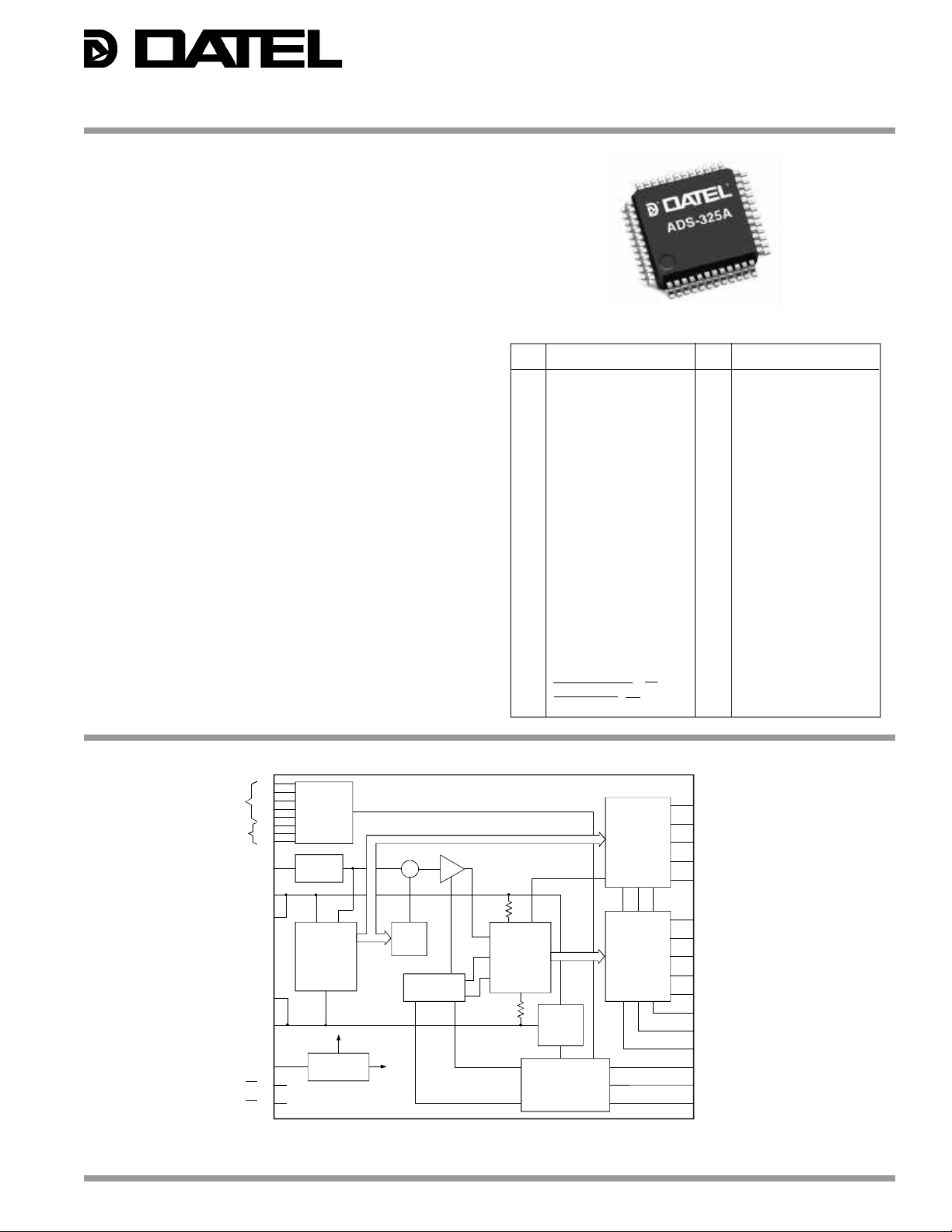

INPUT/OUTPUT CONNECTIONS

PIN FUNCTION

1 BIT 10 (LSB)

2 BIT 9

3 BIT 8

4 BIT 7

5 BIT 6

6 DIGITAL GROUND (DGND)

7 +DV

8 BIT 5

9 BIT 4

10 BIT 3

11 BIT 2

12 BIT 1 (MSB)

13 TEST PIN

14 TEST SIGNAL IN

15 RESET

16 DIGITAL GROUND (DGND)

17 SELECT (SEL)

18 +AVS (Analog)

19 TEST MODE

20 LINV

21 MINV

22 A/D CLOCK

23 OUTPUT ENABLE (OE)

24 CHIP ENABLE (CE)

(Digital)

S

ADS-325A

10-Bit, 20MHz

PIN FUNCTION

48 DIGITAL GROUND (DGND)

47 NO CONNECTION

46 NO CONNECTION

45 +DV

44 ANALOG GROUND (AGND)

43 ANALOG GROUND (AGND)

42 TEST SIGNAL IN

41 CALIBRATION (CAL)

40 NO CONNECTION

39 ANALOG INPUT (V

38 TEST SIGNAL OUT

37 TEST SIGNAL IN

36 ANALOG GROUND (AGND)

35 REFERENCE BOTTOM (

34 REFERENCE BOTTOM (V

33 NO CONNECTION

32 NO CONNECTION

31 NO CONNECTION

30 REFERENCE TOP (V

29 REFERENCE TOP (V

28 ANALOG GROUND (AGND)

27 ANALOG GROUND (AGND)

26 +AVS (Analog)

25 +AVS (Analog)

(Digital)

S

IN)

RT)

RT)

VRB)

RB)

44

43

27

AGND

S

+AV

VIN

V

VRT

VRB

V

A/D CLOCK

28

36

18

25

26

39

RT

29

30

34

RB

35

22

CE

24

OE

23

SENSE

AMP

#1

S/H AMP

COARSE

COMPARISON

AND

ENCODE

TIMING GEN.

CORRECTION

+

x8

DAC

CALIBRATION

UNIT

Figure 1. ADS-325A Functional Block Diagram

FINE

COMPARISON

AND

ENCODE

AUTOCALIBRATION

SENSE

AMP

#2

PULSE

GENERATOR

COARSE

AND

LATCH

FINE

LATCH

12 BIT 1 (MSB)

11 BIT 2

10 BIT 3

9 BIT 4

8 BIT 5

5 BIT 6

4 BIT 7

3 BIT 8

2 BIT 9

1 BIT 10 (LSB)

21 MINV

20 LINV

19

41 CAL

17 SEL

15 RESET

DATEL, Inc., Mansfield, MA 02048 (USA) • Tel: (508) 339-3000, (800) 233-2765 Fax: (508) 339-6356 • Email: sales@datel.com • Internet: www.datel.com

ADS-325A

® ®

ABSOLUTE MAXIMUM RATINGS (TA = +25°C)

PARAMETERS LIMITS UNITS

Supply Voltages (+AV

Reference Voltage (V

Input Voltage, Analog (V

Input Voltage, Digital (V

Output Voltage, Digital (V

and +DVS ) 0 to +7 Volts

S

RT

and VRB) –0.5 to +AVS +0.5 Volts

) –0.5 to +AVS +0.5 Volts

IN

and VIL) –0.5 to +AVS +0.5 Volts

IH

and VOL) –0.5 to +DVS +0.5 Volts

OH

FUNCTIONAL SPECIFICATIONS

(Typical at fS = 20MHz, +AVS = +5V, +DVS = +3.3V, VRB = +2.0V, VRT = +4.0V,

= +25°C unless otherwise specified.)

and T

A

ANALOG INPUTS MIN. TYP. MAX. UNITS

Input Voltage Range, V

Input Current

IN = +4V — 40 50 µA

V

IN = +2V –50 –40 — µA

V

Capacitance, C

Bandwidth (–1dB) — 70 — MHz

REFERENCE

Reference Input Voltage

RT — +4 +4.6 Volts

V

RB +1.8 +2 — Volts

V

Input Current

RT 5 7 11 mA

I

RB –11 –7 –5 mA

I

Offset Voltage

RT +40 +90 +140 mV

V

RB –120 –70 –20 mV

V

Resistance (V

DIGITAL INPUTS

Input Voltage

IH, Logic "1" +2.3 — — Volts

V

IL, Logic "0" — — +0.8 Volts

V

Input Current

IH, Logic Loading "1" ➀ — — 5 µA

I

IL, Logic Loading "0" ➁ — — 5 µA

I

A/D Clock Pulse Width

PW1 25 — — ns

T

PW0 25 — — ns

T

DIGITAL OUTPUTS

Output Logic Current

OH, Logic "1" ➂ –3.5 — — mA

I

OL, Logic "0" ➃ 3.5 — — mA

I

Leak Current at OE = "1" ➄ — — 1 µA

3-State Enable Time, T

3-State Disable Time, T

Data Delay, T

PERFORMANCE

Resolution 10 — — Bits

Max. Throughput Rate ➇ 20 — — MHz

Min. Throughput Rate ➇ — — 0.5 MHz

Integral Linearity Error — ±1.3 ±2 LSB

Differential Linearity Error — ±0.5 ±1 LSB

Differential Gain Error ➈ — 1.0 — %

Differential Phase Error ➈ — 0.3 — Degrees

Aperture Delay, Tsd 2 4 6 ns

SNR & Distortion

IN = 100kHz — 53 — dB

f

IN = 500kHz — 52 — dB

f

IN = 1MHz — 53 — dB

f

IN = 3MHz — 54 — dB

f

IN = 7MHz — 47 — dB

f

IN = 10MHz — 45 — dB

f

IN +2 to +4 Volts

IN — 9 — pF

RT – VRB) 180 280 380 Ω

PZE ➅ 10 15 20 ns

PEZ ➆ 20 25 30 ns

DL (CL = 20pF) 8 13 18 ns

PERFORMANCE (CONT.) MIN. TYP. MAX. UNITS

Spurious Free Dynamic Range

IN = 100kHz — 60 — dB

f

IN = 500kHz — 59 — dB

f

IN = 1MHz — 60 — dB

f

IN = 3MHz — 65 — dB

f

IN = 7MHz — 50 — dB

f

IN = 10MHz — 49 — dB

f

POWER REQUIREMENTS

Power Supply Voltage

S +4.75 +5.0 +5.25 Volts

+AV

S +3.0 — +5.25 Volts

+DV

|DGND – AGND| — — 100 mV

Supply Current

Analog, +AI

Digital, +DI

S 20 27 34 mA

S — 3 5 mA

Standby Current (CE = "1")

Analog, +AI

Digital, +DI

S — — 1 mA

S — — 1 µA

Power Dissipation — 150 — mW

PHYSICAL/ENVIRONMENTAL

Operating Temperature Range –20 — +75 °C

Storage Temperature Range –55 — +150 °C

Weight 0.2 grams

Package 48-pin plastic LQFP

Footnotes:

= Max., V

+DV

➀

S

+DVS = Max.,

➁

➂

OE = AGND, +DVS = Min.,

OH

= +DVS-0.5V

V

➃

OE = AGND, +DVS = Min.,

OL

= 0.4V

V

IH

V

IL

= +DV

=

0V

➄

S

OE = +AVS, +DVS = Max.,

OH

= +DVS, and VOL = 0V

V

➅

Hi-Z to Active, asynchronous with clock.

➆

Active to Hi-Z, asynchronous with clock.

➇

Fin = 1kHz

➈

NTSC 401RE mod. ramp, fc = 14.3MHz

TECHNICAL NOTES

1. Caution to ESD: Since the ADS-325A is a CMOS device,

precautions against static electricity should be taken.

S and +DVS: While the unit has separate pins for both

2. +AV

the analog supply (+AV

time skew between supplying (or removing) both +AV

S may cause a latch-up problem. DATEL recommends

+DV

using a common power supply for both +AV

avoid latch-up conditions. It is possible to use +3.3V for

S along with +5V for +AVS. Compared to the singe +5V

+DV

supply application, there will be no significant difference in

performance. However, special care should be taken to

minimize the time skew between +AV

turning on/off.

3. PC board layout: To obtain fully specified performance

careful attention to PC board layout is required. Place large

ground planes on the board and connect both analog and

digital grounds at one point right beneath the converter. In

the case where the grounds are tied at a location distant

from the converter, the voltage difference between the

grounds must be within 100mV. Tie all ground pins directly

to the appropriate ground plane beneath the converter.

Bypass +AV

S and +DVS pins to ground using 10µF

tantalum capacitors in parallel with 0.1µF ceramic

capacitors at locations as close to the unit as possible.

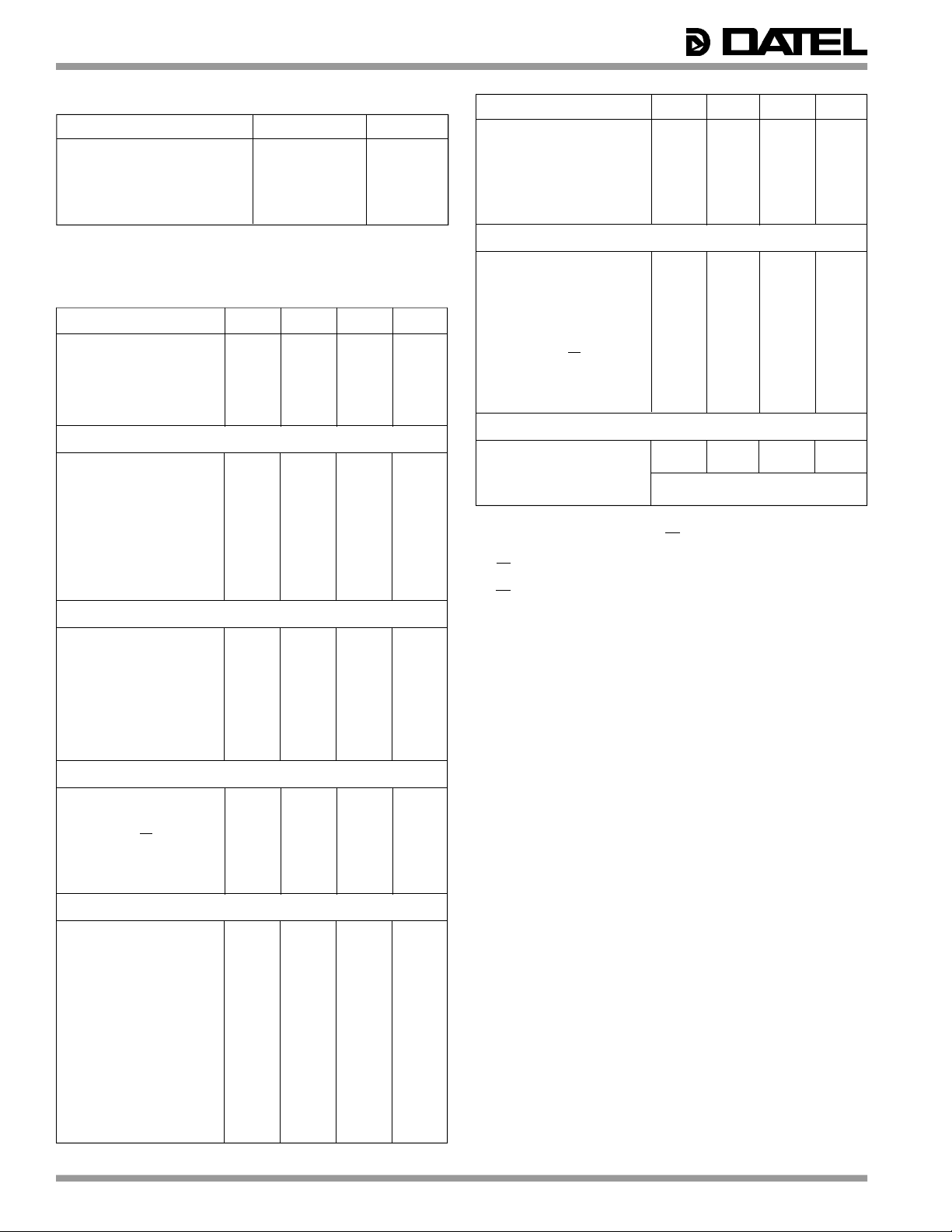

4.Reference Input: Two external voltage references are

required for the two reference inputs VRT (pin 29, 30) and

VRB (pin 34, 35). Typically, these are +4V for VRT and +2V

S) and the digital supply (+DVS), a

S and

S and +DVS to

S and +DVS when

2

® ®

AGND

AGND

OUTPUT ENABLE (OE) 23

DGND

OUTPUT

AGND

ADS-325A

for VRB, which give an analog input range of +2V to +4V.

The reference voltages must be within the following

limitations:

+AVS – 0.4V > = VRT > VRB >= +1.8V, and

VRT – VRB > =1.8V

Stability of the reference will directly affect the accuracy of

the A/D conversion. In this sense, the reference sources

must be capable of driving more than 10mA. Also, the VRT

and VRB pins should be bypassed to analog ground with

0.1µF ceramic capacitors placed as close to the pins as

possible.

5. Analog Input: ADS-325A has a broad input bandwidth of

70MHz (@–1dB) with only 9pF of input capacitance at its

analog input. The analog input should be driven by a high

speed buffer amplifier with sufficient current drive.

6. Digital Inputs: All digital input pins including A/D clock input

are CMOS compatible. Each of these pins has an internal

overvoltage protection circuit with diodes as shown in Figure

2 (Equivalent circuit diagrams).

7. Control Logic Inputs: ADS-325A has several control logic

input pins. Functions of these pins are described in the

following:

TEST MODE (pin 19), MINV (pin 21), LINV (pin 20)

These three pins select the output data format. With a

combination of these input states the output data takes any

form of binary, complementary binary, 2's compliment, or

certain test pattern. Refer to Table 1 (Output coding) and

Table 2 (Truth table).

CE (Chip Enable, pin 24)

For normal operation the input to this pin should be logic

low. Input high applied to the pin puts the unit into standby

mode. In standby mode the unit dissipates only a few milliwatts or less.

OE (Output Enable, pin 23)

Input logic low applied to this pin enables the three-state

output bits (Bit 1 to Bit 10). Input high disables the outputs.

RESET (pin 15)

This pin can be used to re-initiate start-up calibration.

Normally connect this pin to logic high. See Calibration

Function for more details.

CAL (Calibration Input, pin 41)

This pin is the input for an external calibration pulse. See

Calibration Function for more details.

SEL (Select, pin 17)

Applying logic high to this pin allows use of the internal auto

calibration function and blocks out the external pulse from

the CAL input. Inputting logic low to the pin disables the

internal cal function and allows usage of the external cal

pulses.

8. Test IN/OUT pins: Test signal input/output pins are used in

the production process. The test signal output pins (pin 13,

38) should normally be left open. Tie the test signal input pin

42 to +AV

S and the pins 14 and 37 to +AVS or AGND.

9. Three-state output buffer: A/D output buffer (BIT 1 to

BIT 10) is a three-state register controlled by the OE pin.

The output logic high level is dependent on +DV

S.

+AVS

39

VIN

TEST MODE 19

CHIP ENABLE (CE) 24

CAL. PULSE IN (CAL) 41

Analog Signal Input

RESET 15

SELECT 17

LINV 20

MINV 21

CLOCK 22

+AVS

Digital Data Outputs

S

+AV

29

30

RT

V

AGND

S

+AV

34

35

RB

V

+DVS

BIT

SEL, CLK, CAL, RESET, OE, CE, Test Mode,

LINV and MINV Inputs

Reference Input

Figure 2. Equivelant Circuits

3

Loading...

Loading...