Page 1

W183

Full Feature Peak Reducing EMI Solution

Features

Cypress PREMIS™ family offering

•

• Generates an EMI optimized c loc king signa l at the output

• Selectable output frequency range

• Single 1.25%, 3.75% down or center spread output

• Integrated loop filter components

• Operates with a 3.3 or 5V supply

• Low power CMOS design

• Available in 14 -p i n S OIC (S mall Outl in e Int e g ra te d

Circuit)

Key Specifications

Suppl y Voltages: .............. .......... .......... .. .......VDD = 3.3V±5%

or V

= 5V±10%

DD

≤

Fr equency Range: ........ ............ ........28 MHz ≤ F

Crystal Reference Range:................. 28 MHz ≤ F

in

≤

in

75 MHz

40 MHz

Cycle to Cy c le Ji tte r: .......... ......... .......... ... ....... 300 ps (ma x .)

Selectabl e Spread Percentage: .......... ..........1.25% or 3.75%

Output Duty Cycle: ............................... 40/60% (worst case)

Output R is e a n d Fall Tim e : . .. .. .......... .......... ......... 5 ns (max.)

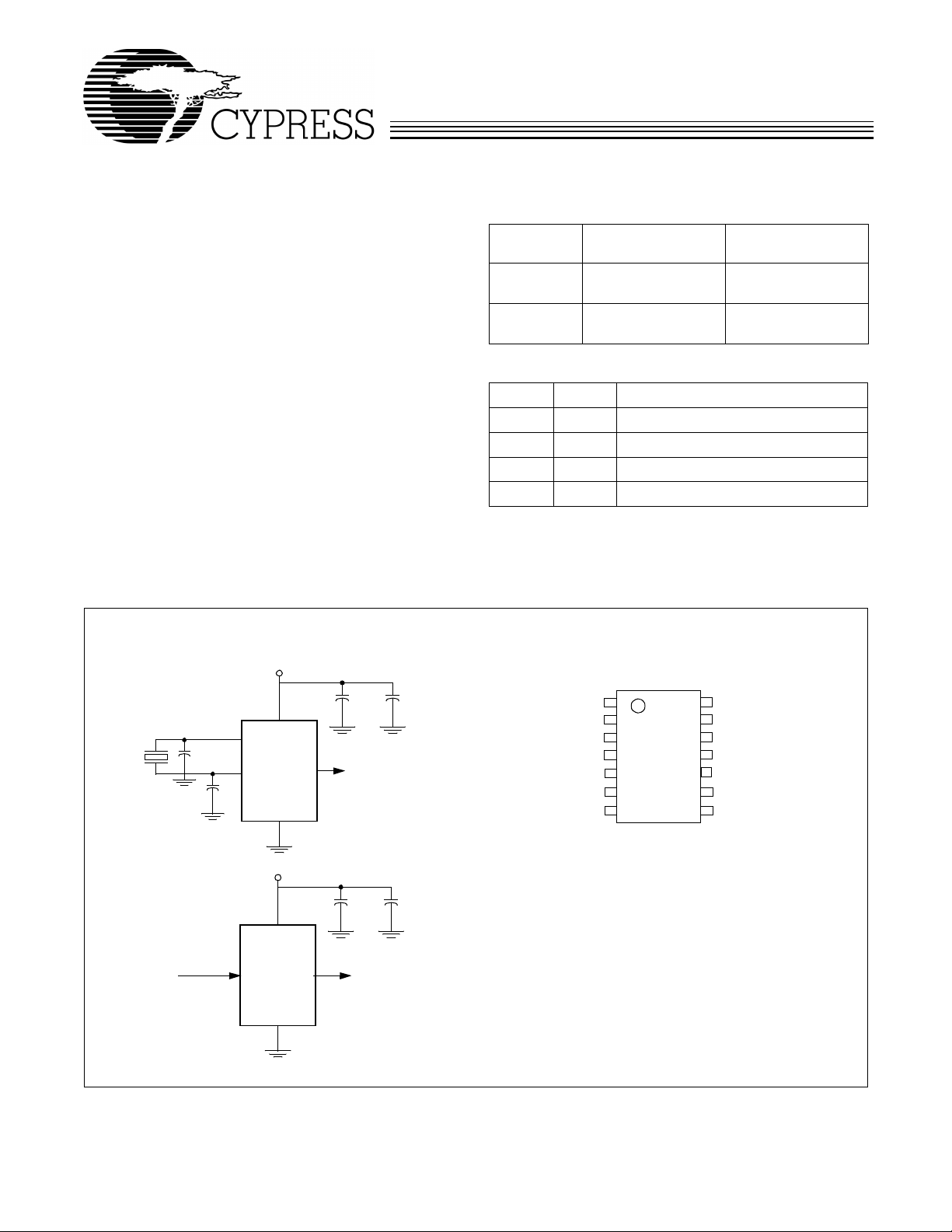

Simplified Block Diagram

3.3V or 5.0 V

Table 1. Modulation Width Selection

W183

SS%

0F

1F

≥

in

1.25%

≥

in

3.75%

Output

F

out

F

out

≥

–

F

in

F

in

– 0.625%

≥

–

F

in

F

in

–1.875%

T able 2. Frequency Range Selection

FS2 FS1 Frequency Range

0 0 28 MHz ≤ F

0 1 38 MHz ≤ F

10 46 MHz ≤ F

11 58 MHz ≤ F

IN

IN

IN

IN

Pin Configuration

SOIC

W183-5

Output

+ 0.625% ≥ F

+ 1.875% ≥ F

≤

38 MHz

≤

48 MHz

≤

60 MHz

≤

75 MHz

in

in≥

≥

X1

XT AL

Input

40 MHz

Max

Oscillator or

Reference Input

PREMIS is a trademark of Cypress Semiconductor Corporation.

X2

W183

3.3V or 5.0V

W183

Spread Spe ctrum

Output

(EMI supp ressed )

Spread Spectrum

Output

(EMI suppre ss ed)

FS2

CLKIN or X1

NC or X2

GND

GND

SS%

FS1

1

W183/W183-5

2

3

4

5

6

7

14

13

12

11

10

9

8

REFOUT

OE#

SSON#

Reset

VDD

VDD

CLKOUT

Cypress Semiconductor Corporation

• 3901 North First Street • San Jose • CA 95134 • 408-943-2600

July 25, 2000, rev.*B

Page 2

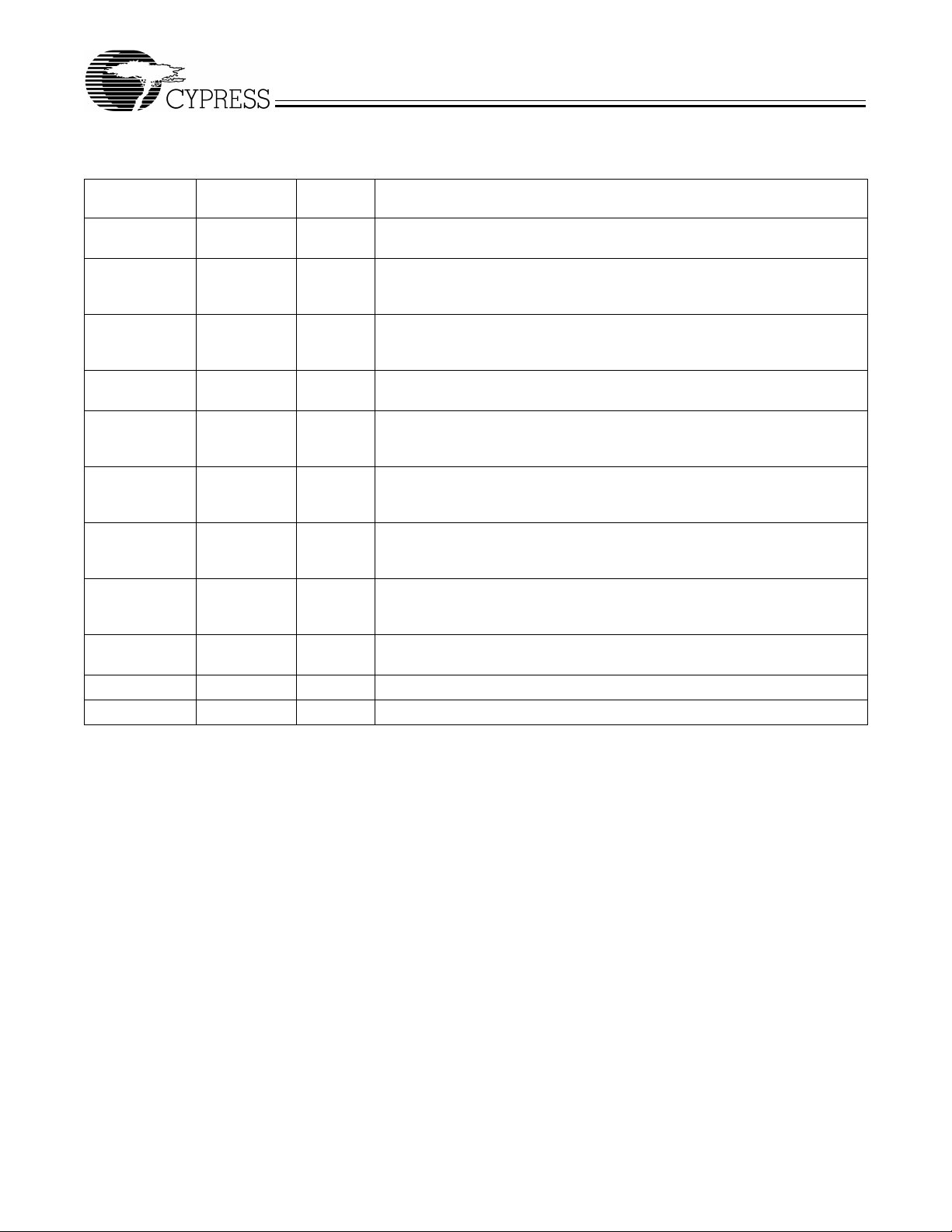

Pin Definitions

W183

Pin Name Pin No.

CLKOUT 8 O

REFOUT 14 O

CLKIN or X1 2 I

NC or X2 3 I

SSON# 12 I

SS% 6 I

OE# 13 I

Reset 11 I

FS1:2 7, 1 I

VDD 9, 10 P

GND 4, 5 G

Pin

Ty pe Pin Description

Output Modulated Frequency

(SSON# asserted).

Non-Modulated Output:

This output will not have the Spread Spectrum f eatur e regardl ess of the st ate

of logic input SSON#.

Crystal Connection or External Reference Frequency Input:

dual functions. It may either be connected to an ex ternal crystal , or to an

external reference clock.

Crystal Connection:

ternal reference, this pin mus t be left unconnected.

Spread Spectrum Contro l (Active LOW):

turns the internal modul ation wav e f orm on. Thi s pin has an internal pul l-do wn

resistor.

Modulation Width Selection:

this pin is used to select the am ount of variation and peak EMI reduction that

is desired on the output signal. This pin has an internal pull -up resistor.

Output Enable (Active LOW):

are placed in a high-impedance mode. This pin has an internal pull-down resistor.

Modulation Profile Restart:

pattern at the begi nning of its de fined path . This pin has an internal pul l-do wn

resistor.

Frequency Selection Bits:

tion. Refer to Table 2. These pins hav e internal pull-up resistors.

Po wer Connec tion:

Ground Connection:

Input connectio n for an external crystal. If using an ex-

Connected to 3.3V or 5V po wer supply.

Connect all g round pins to the common ground plane.

: Freq uency modulat ed copy of the input clock

This pin provides a copy of the ref erence frequ ency.

This pin has

Asserting this signal (acti ve LOW )

When Spread Spectrum feature is turned on,

When this pi n is he ld HIGH, th e output b uff er s

A rising edge on this input restarts the modulati on

These pins select the frequency range of opera-

2

Page 3

W183

Overview

The W183 product is one of a seri es of de v ices i n the Cypr ess

PREMIS family. The PREMIS family incorporates the latest

advanc es in PLL spread spectrum frequency synthesizer t echniques. By frequency modulating the output with a low frequency carrier, peak EMI is greatl y reduced. Use of this technology allows s ystems to pass increasingl y diff icult EMI testin g

without resorting to costly shielding or redesign.

In a system, not only i s EMI reduce d in the v arious cl oc k li nes,

but also in all signals which are synchronized to the clock.

Therefore, the benefits of using this technology increase with

the number of address and dat a lines in the syst em. The Simplified Block Diagram shows a simple implementation.

Functional Description

The W183 uses a phase-locked loop (PLL) to f requency modulate an input clock. The result is an output clock whose frequency is slowly swept over a narrow band near t he input signal. The basic circuit topology is shown in Figure 1. The i nput

refer ence signa l is div ided b y Q and fe d to the phase detector.

A signal from the VCO is divided by P and fed back to the

phase detector also. The PLL will force the frequency of the

VCO output signal to change until the divided output signal

and the divided reference signal match at the phase detector

input. The output frequency is then equal to the ratio of P/Q

times the ref er ence fre quenc y. (Note: F or t he W183 t he outpu t

frequency is equal to the input f requency.) The unique feature

of the Spread Spect rum Fr equ ency Timi ng Gener ator is that a

modulating wa vef orm is supe rimposed a t the input to the VCO .

This causes the VCO output to be slowly swept across a predetermined frequency ban d.

Because the modulating frequency is typically 1000 times

slower than the fundamental clock, the spread spectrum process has little impact on system performance.

Frequency Selection With SSFTG

In Spread Spectrum Frequency Timing Generation, EMI reduction depends on the shape, modulation percentage, and

frequency of the modulating waveform. While the shape and

frequency of the modulating waveform are fixed for a given

frequency, the modulation percentage may be va ried .

Using frequency select bits (FS2: 1 pins), the frequency range

can be set (see Table 2). Spreading percentage is set with pin

SS% as shown in Table 1.

A larger spreading per centage improves EMI reduction. However, large spread percentages may either exceed system

maximum frequ ency ra tings o r lo wer the a v er age fr eque ncy to

a point where performance is affected. For these reasons,

spreading percentages between 0.5% and 2.5% are most

common.

V

DD

Clock Input

Reference Input (EMI suppressed)

Freq. Phase

Q

Detector

Feedback

Divider

P

Charge

Pump

GND

Σ

Modulating

Waveform

VCO

PLL

Post

DividersDivider

CLKOUT

Figure 1. Functional Block Diagram

3

Page 4

W183

Spread Spectrum Frequency Timing

Generation

The device generates a clock that is frequency modulated in

order to increase the bandwidth that it occu pies. By increas ing

the bandwidth of the fundamental and its harmonics, the amplitudes of the radiated electromagnetic emissions are reduced. This effect is depicted in

As shown in

)LJXUH

, a harmonic of a modulated clock has a

much low er amplit ude than that of an un modulated si gnal. The

reduction in amplitude is dependent on the harmonic number

and the frequency deviation or spread. The equation for the

reduction is:

dB = 6.5 + 9*log

Amplitude (dB)

(P) + 9*log10(F)

10

SSFTG Typical Clock

)LJXUH

.

Where P is the pe rcentag e of de vi ation an d F is the frequency

in MHz where the reduction is measured.

The output clock is modulated with a waveform depicted in

)LJXUH

. This waveform, as discussed in “Spread Spectrum

Clock Gener ation f or the Redu ct ion of Radiat ed Emission s” by

Bush, Fessler, and Hardin produces the maximum reduction

in the amplitude of radiated electromagnetic emissions.

details the Cypress spreading pattern. Cypress does offer

)LJXUH

options with more spread and greater EMI reduction. Contact

your local Sales representativ e for details on these devices.

EMI Reduction

Spread

Spectrum

Enabled

Amplitude (dB)

Non-

Spread

Spectrum

Frequency Span (MHz)

Center Spread

Frequency Span (MHz)

Down Spread

Figure 2. Clock Harmonic with and with out SSCG Modulati on Frequency Dom ain Representat ion

MAX.

10%

20%

30%

40%

50%

60%

70%

80%

FREQUENCY

MIN.

90%

100%

10%

20%

30%

40%

50%

60%

70%

80%

Figure 3. Typical Modulation Pr ofile

90%

100%

4

Page 5

Absolute Maximum Ratings

W183

Stresses greater than those listed in this table may cause permanent damage to the de vice . These represent a stress ratin g

only. Operation of the device at these or any other conditions

.

above those specified i n the operating sec ti ons of this specif ication is not implied. Maximum conditions for extended periods may affect reliability.

Parameter Description Rating Unit

V

, V

DD

IN

T

STG

T

A

T

B

P

D

DC Electr i cal C h ar acteristics

Voltage on any pin with respect to GND –0.5 to +7 .0 V

Storage Temperature –65 to +150 °C

Operating Tempera ture 0 to +70 °C

Ambient Temperature under Bias –55 to +125 °C

Power Dissi pation 0.5 W

:

0°C < T

< 70°C, VDD = 3.3V ±5%

A

Parameter Description T est Condition Min. T yp. Max. Unit

I

DD

t

ON

V

IL

V

IH

V

OL

V

OH

I

IL

I

IH

I

OL

I

OH

C

I

R

P

Z

OUT

Note:

1. Inputs FS1:2 have a pull-up resistor, Input SSON# has a pull-down resistor.

Supply Current 18 32 mA

Power Up Time First locked clock cycle after Power

5ms

Good

Input Low Voltage 0.8 V

Input High Vol tage 2.4 V

Output Low Voltage 0.4 V

Output High Voltage 2.4 V

Input Low Current Not e 1 –50 µA

Input High Current Note 1 50 µA

Output Low Current @ 0.4V, VDD = 3.3V 15 mA

Output High Current @ 2.4V, VDD = 3.3V 15 mA

Input Capacitance 7pF

Input Pull-Up Resistor 500 kΩ

Clock Output I mp edance 25 Ω

5

Page 6

W183

DC Electr i cal C h ar acteristics:

0°C < T

< 70°C, VDD = 5V ±10%

A

Parameter Description Test Condition Min. Typ. Max. Unit

I

t

V

V

V

V

I

I

I

I

C

R

Z

DD

ON

IL

IH

OL

OH

IL

IH

OL

OH

I

P

OUT

Supply Current 30 50 mA

Power Up Time First locked clock cycle after

5ms

Power Good

Input Low Voltage 0.15V

Input High Voltage 0.7V

DD

DD

Output Low Voltage 0.4 V

Output High Voltage 2.4 V

Input Low Current Note 2 –50 µA

Input High Current Note 2 50 µA

Output Low Current @ 0.4V, VDD = 5V 24 mA

Output High Current @ 2.4V, VDD = 5V 24 mA

Input Capacitance 7pF

Input Pull-Up Resistor 500 kΩ

Clock Output I mp edance 25 Ω

TA = 0°C to +70°C, VDD = 3.3V ±5% or 5V±10%

AC Electrical Characteristics:

Symbol Parameter T est Condition Min. Typ. Max. Unit

f

IN

f

OUT

f

XOSC

t

R

t

F

t

OD

t

ID

t

JCYC

Input Frequency Input Clock 28 75 MHz

Output Frequency Spread Off 28 75 MHz

Crystal Oscillator Frequency 28 40 MHz

Output Rise Time 15-pF load, 0.8V–2.4V 2 5 ns

Output Fall Time 15-pF load, 2.4V–0.8V 2 5 ns

Output Duty Cycle 15-pF load 40 60 %

Input Duty Cycle 40 60 %

Jitter, Cycle-to-Cyc le 250 300 ps

Harmonic Reduction f

= 40 MHz, thir d harmonic

out

measured, reference board,

8dB

15-pF load

Note:

2. Inputs FS2:1 have a pull-up resistor, Input SSON# has a pull-down resistor.

V

V

6

Page 7

W183

Application Information

Recommended Circuit Configuration

For optimum performance in system applications the power

supply decoupli ng scheme sho wn in Figure 4 should be used .

VDD decoupling is important to both reduce phase jitter and

EMI radiation. The 0.1-µF decoupling capacitor should be

placed as close to the V

Xtal Connec tio n or Re f e ren ce Input

Xtal Connec tion or Reference Input

pin as possible, otherwise the in-

DD

Xtal Connection or NC

GND

3.3V or 5V System Supply

Figure 4. Recommended Circuit Configuration

Xtal Connection or

NC

G

G

W183

14

13

12

11

10

9

8

1

2

3

4

5

6

7

creased trace inductance will negate its decoupling capability.

The 10-µF decoupling capacitor shown should be a tantalum

type. For further EMI protection, the V

made via a ferrite bead, as shown.

connection can be

DD

Recommended Board Layout

Figure 5 shows a recommended a 2-layer board la yout

C3

µF

0.1

µF recommended).

µF tantalum

R1

Clock

Output

C1

µF

0.1

FB

C1, C3 =

C3

G

C1

G

C2

µF Tantalum

10

High frequency supply decoupling

capacitor (0.1-

C2 =

Common supply low frequency

decoupling capacitor (10recommended).

R1 =

Match value to line impedance

FB

=

Ferrite Bead

G

=

Via To GND Plane

Power Supply Input

(3.3V or 5V)

Ordering Information

Ordering Code

W183

W183-5

Document #: 38-00798-B

R1

G

FB

C2

Figure 5. Recommended Board Layout (2-Layer Board)

Package

Name Packag e Type

G 14-Pin Plastic SOIC (150-mil)

7

Clock Output

Page 8

Package Diagram

W183

14-Pin Small Outline Integrated Circuit (SOIC, 150-m il)

© Cypress Semiconductor Corporation, 2000. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use

of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it conv ey or imply any lice nse under patent or other rights. Cypress Semicondu ctor does not authorize

its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress

Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.

Loading...

Loading...