Page 1

Spread Aware™, Zero Del ay Buffer

W162

Cypress Semiconductor Corporation

• 3901 North First Street • San Jose • CA 95134 • 408-943-2600

July 31, 2000, rev. *B

Features

• Spread Aware™—designed to work with SSFTG

reference signals

• Two banks of four outputs, plus the fed back output

• Outputs may be three-stated

• Available in 16-pin SOIC or SSOP package

• Extra strength output drive available (-19 version)

• Internal feedback

Key Specifications

Operating Voltage: ............................................... 3.3V±10%

Operating Range: .................................15 < f

OUT

< 133 MHz

Cycle-to-Cycle Jitter: .................................... .............. 250 ps

Output to Output Skew: .......................... .................... 150 ps

Propagation Delay :..................................................... 150 ps

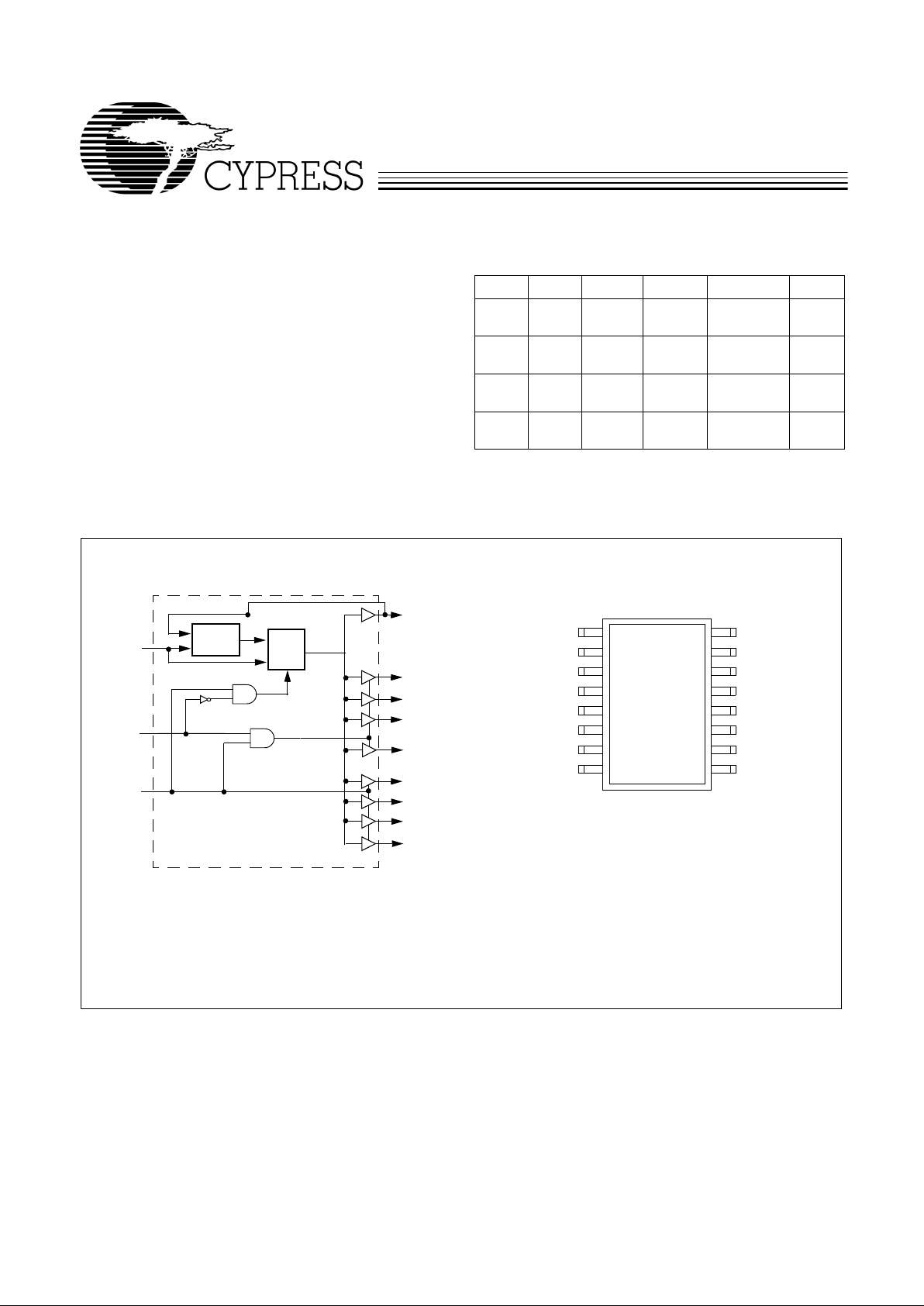

Table 1. Input Logic

SEL1 SEL0 QA0:3 QB0:3 PLL QFB

00Three-

State

Three-

State

Shutdown Active

01ActiveThree-

State

Active,

Utilized

Active

1 0 Active Active Shutdown,

Bypassed

Active

1 1 Active Active Active,

Utilized

Active

Spread Aware is a trademark of Cypress Semiconductor Corporation.

Block Diagram

Pin Configuration

PLL

REF

MUX

QA1

QA2

QA3

QB0

QB1

SEL0

QB2

QB3

SEL1

QFB

QA3

QA2

VDD

GND

QB3

QB2

SEL0

16

15

14

13

12

11

10

9

REF

QA0

QA1

VDD

GND

QB0

QB1

SEL1

1

2

3

4

5

6

7

8

QFB

QA0

Page 2

W162

2

Overview

The W162 products are nine-output zero delay buffers. A

Phase-Lock ed Loop (PLL) is used to tak e a time-v arying signal

and provide eight copies of that same signal out.

Interna l feedback is used to m aximize the number of output

signals provid ed in the 16-p in package.

Spread Aware

Many systems b eing designed now util ize a technolog y ca lle d

Spread Spectrum F requency T iming Gener ation. Cypre ss has

been one of the pioneers of SSFTG development, and w e designed this product so as not to fil ter of f the S prea d Spe ctrum

feature of the Ref erence input, ass uming it exists . When a zero

delay buffer is not designed to pass the SS feature through,

the result is a significant amount of tracking skew which may

cause problems in systems requiring synchronization.

For more details on Spread Spectrum timing technology,

please see the Cyp ress App licat ion not e titled , “EMI Sup pression Techniques with Spread Spectrum Frequency Timing

Generator (SSFTG) ICs.”

Functional Description

Logic inputs pro v ide the us er th e ab ili ty to turn off one or both

banks of cloc k s wh en n o t in us e , a s d es crib ed i n Table 1. Disabling a bank of unused outputs will reduce jitter and power

consumption, and will als o reduce the amoun t of EMI generated by the W162.

These same inputs allo w the user to b ypass the PLL e ntirely if

so desired. When this is done, the device no longer acts as a

zero delay buffer, it simply reverts to a standard nine-output

clock driver.

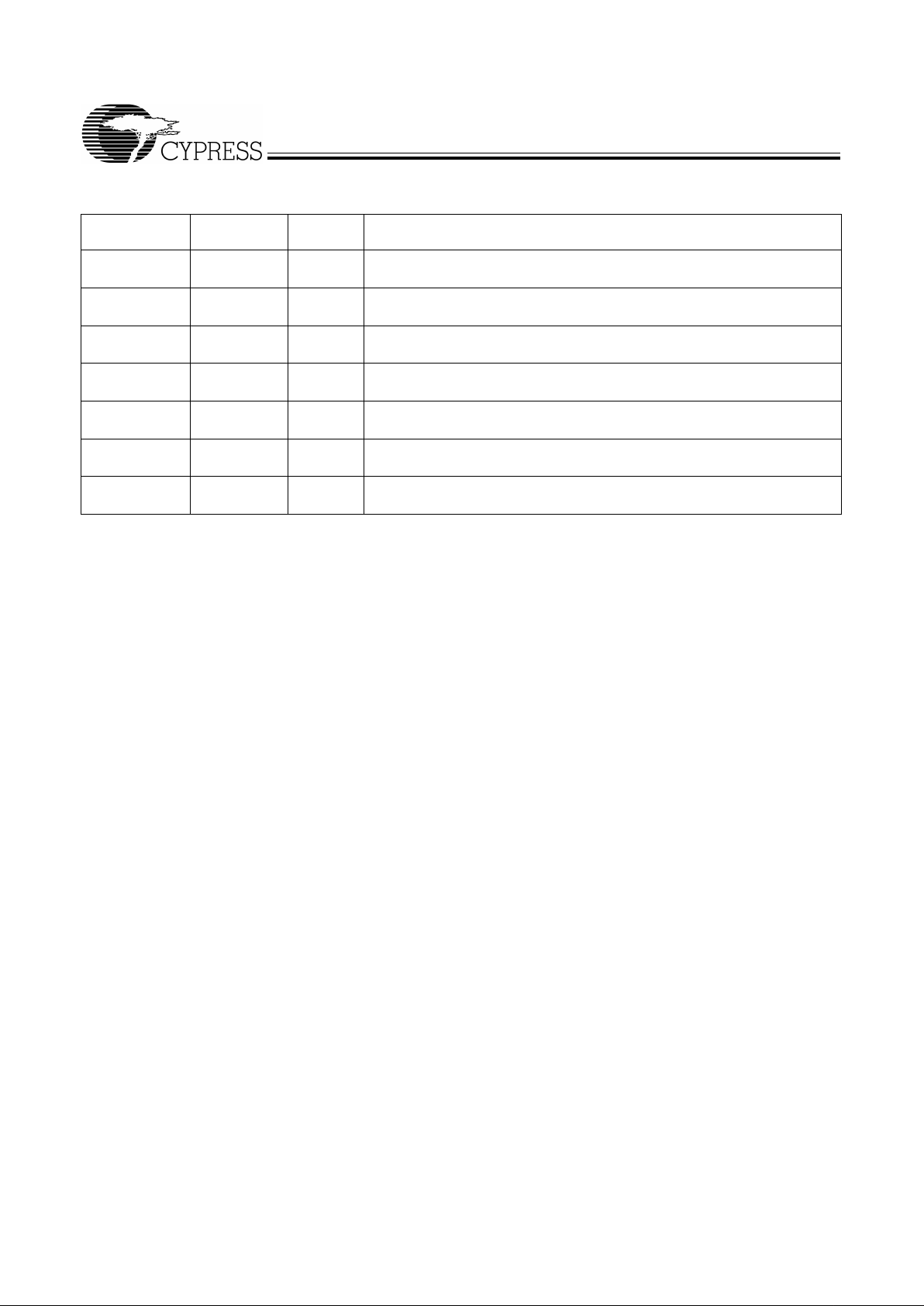

Pin Definitions

Pin Name Pin No.

Pin

Type Pin Description

REF 1 I

Reference Input:

The output signals QA0:3 through QB0:3 will be synchro-

nized to this signal unless the device is programmed to bypass the PLL.

QFB 16 O

Feedback Output:

This signal is used as the feedback internally to esta b lish

the propagation delay of nearly 0.

QA0:3 2, 3, 14, 15 O

Outputs from Bank A:

The frequency of the signals provided by these pins

is equal to the signal connected to REF.

QB0:3 6, 7, 10, 11 O

Outputs from Bank B:

The frequency of the signals provided by these pins

is equal to the signal connected to REF.

VDD 4, 13 P

Power Conn ections:

Connect to 3.3V. Use ferrite beads to help reduc e noise

for optimal jitter performance.

GND 5, 12 P

Ground Connections:

Connect all grounds to the common system ground

plane.

SEL0:1 9, 8 I

Function Select Inputs:

Tie to V

DD

(HIGH, 1) or GND (LOW, 0) as desired

per Table 1.

Page 3

W162

3

Absolute Maximum Ratings

Stresses greater than tho se listed in thi s tabl e ma y cause permanent damage to the devi ce. Thes e represent a s tress ratin g

only. Operation of the device at these or any other conditions

above thos e s pecified in the operating sectio ns of thi s s pe cif ication is not implied. Maximum conditions for extended periods may affect reliability

.

Parameter Description Rating Unit

V

DD

, V

IN

Voltage on any pin with respect to GND –0.5 to +7.0 V

T

STG

Storage Temperature –65 to +150 °C

T

A

Operating Temperature 0 to +70 °C

T

B

Ambient Temperature under Bias –55 to +125 °C

P

D

Power Dissipation 0.5 W

DC Electrical Characteristics

:

T

A

=0°C to 70°C, VDD = 3.3V ±10%

Parameter Description Test Condition Min Typ Max Unit

I

DD

Supply Current Unloaded, 100 MHz 40 mA

V

IL

Input Low Voltage 0.8 V

V

IH

Input High Voltage 2.0 V

V

OL

Output Low Voltage IOL = 12 mA (-19)

I

OL

= 8 mA (-9)

0.4 V

V

OH

Output High Voltage IOL = 12 mA (-19)

IOL = 8 mA (-9)

2.4 V

I

IL

Input Low Current VIN = 0V –500 µA

I

IH

Input High Current VIN = V

DD

10 µA

AC Electrical Characteristics:

TA = 0°C to +70°C, VDD = 3.3V ±10%

Parameter Description Test Condition Min Typ Max Unit

f

IN

Input Frequency 15 133 MHz

f

OUT

Output Fr equ en cy 15-pF load

[5]

15 133 MHz

t

R

Output Rise Time (-09)

[1]

2.0 to 0.8V, 15-pF load 2 2.5 ns

Output Rise Time (-19)

[1]

2.0 to 0.8V, 20-pF load 1.5 ns

t

F

Output Fall Time (-09)

[1]

2.0 to 0.8V, 15-pF load 2 2.5 ns

Output Rise Time (-19)

[1]

2.0 to 0.8V, 20-pF load 1.5 ns

t

PD

FBIN to REF Skew

[2, 3]

Measured at VDD/2 150 ps

t

SK

Output to Output Skew All outputs loaded equally 150 ps

t

D

Duty Cycle 15-pF load

[4]

45 50 55 %

t

LOCK

PLL Lock Time Power supply stable 1.0 ms

t

JC

Jitter , Cyc le-t o-C ycle 250 ps

Notes:

1. Long input rise and fall time will degrade skew and jitter performance.

2. All AC specifications are measured with a 50Ω transmission line, load terminated with 50Ω to 1.4V.

3. Skew is measured at V

DD

/2 on rising edges.

4. Duty cycle is measured at V

DD

/2

5. For the higher drive -19, the load is 20 pF.

Page 4

W162

4

Schematic

Document #: 38-00788-B

Ordering Information

Ordering Code Option

Package

Name Package Type

W162 -09, -19 G

H

16-pin Plastic SOIC (150-mil)

16-pin Plastic SSOP (150-mil)

9

2

3

1

4

7

6

8

5

16

13

14

15

10

11

12

V

DD

V

DD

10

µ

F

0.1

µ

F

Ferrite

Bead

Ferrite

Bead

VDD or GND (for desired operation mode)VDD or GND (for desired operation mode)

Output

OutputOutput

Output

Ground

PowerPower

OutputRef In

Output

Output

Output

Output

Logic In Logic In

Ground

10

µ

F

0.1

µ

F

Page 5

W162

5

Package Diagrams

16-pin SSOP Small Shrunk Outline Package (SSOP, 150-mil)

Page 6

W162

© Cypress Semiconductor Corporation, 2000. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use

of any circuitry other than circui try embodied in a Cypress S emiconductor p roduct. Nor does i t conv ey or imply an y license under pa tent or other rights. Cypress S emiconductor doe s not authorize

its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress

Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.

Package Diagrams

(continued)

16-Pin Small Outlined Integrated Circuit (SOIC, 150-mil)

Loading...

Loading...