Page 1

®

Voltage-to-Frequency

and Frequency-to-Voltage

CONVERTER

VFC32

FEA TURES

● OPERATION UP TO 500kHz

● EXCELLENT LINEARITY

±0.01% max at 10kHz FS

±0.05% max at 100kHz FS

● V/F OR F/V CONVERSION

● MONOTONIC

● VOLTAGE OR CURRENT INPUT

APPLICATIONS

● INTEGRATING A/D CONVERTER

● SERIAL FREQUENCY OUTPUT

● ISOLATED DATA TRANSMISSION

● FM ANALOG SIGNAL MOD/DEMOD

● MOTOR SPEED CONTROL

● TACHOMETER

V

OUT

Comparator

Input

DESCRIPTION

The VFC32 voltage-to-frequency converter provides

an output frequency accurately proportional to its

input voltage. The digital open-collector frequency

output is compatible with all common logic families.

Its integrating input characteristics give the VFC32

excellent noise immunity and low nonlinearity.

Full-scale output frequency is determined by an external capacitor and resistor and can be scaled over a

wide range. The VFC32 can also be configured as a

frequency-to-voltage converter.

The VFC32 is available in 14-pin plastic DIP, SO-14

surface-mount, and metal TO-100 packages. Commercial, industrial, and military temperature range models

are available.

+V

CC

f

–In

+In

–V

CC

International Airport Industrial Park • Mailing Address: PO Box 11400 • Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd. • Tucson, AZ 85706

Tel: (602) 746-1111 • Twx: 910-952-1111 • Cable: BBRCORP • Telex: 066-6491 • FAX: (602) 889-1510 • Immediate Product Info: (800) 548-6132

©

1977 Burr-Brown Corporation PDS-372G Printed in U.S.A. October, 1998

One-Shot

VFC32

One-Shot

Capacitor

OUT

Common

Page 2

SPECIFICATIONS

At T

= +25°C and V

A

PARAMETER CONDITIONS MIN TYP MAX MIN TYP MAX MIN TYP MAX UNITS

INPUT (V/F CONVERTER) F

Voltage Range

Positive Input >0 +0.25mA ✽✽✽✽V

Negative Input >0 –10 ✽✽✽✽V

Current Range

Bias Current

Inverting Input 20 100 ✽✽ ✽✽ nA

Noninverting Input 100 250 ✽✽ ✽✽ nA

Offset Voltage

Differential Impedance 300 || 10 650 || 10 ✽✽ ✽ ✽ kΩ || pF

Common-mode

Impedance 300 || 3 500 || 3 ✽✽ ✽✽ MΩ || pF

INPUT (F/V CONVERTER) V

Impedance 50 || 10 150 || 10 ✽✽ ✽✽ kΩ || pF

Logic “1” +1.0 ✽✽✽✽V

Logic “0” –0.05 ✽✽✽ ✽V

Pulse-width Range 0.1 150k/F

ACCURACY

Linearity Error

Offset Error Input

Offset Votlage

Offset Drift

Gain Error

Gain Drift

(6)

(2)

(6)

Full Scale Drift f = 10kHz ±75 ±50 ±100 ±70 ±150 ppm of FSR/°C

(offset drift and

(6, 7)

gain drift)

Power Supply f = DC, ±VCC = 12VDC

Sensitivity to 18VDC ±0.015 ✽✽% of FSR/%

OUTPUT (V/F CONVERTER) (open collector output)

Voltage, Logic “0” I

Leakage Current,

Logic “1” V

Voltage, Logic “1” External Pull-up Resistor

Pulse Width For Best Linearity 0.25/F

Fall Time I

OUTPUT (F/V CONVERTER) V

Voltage IO ≤ 7mA 0 to +10 ✽✽ V

Current V

Impedance Closed Loop 1 ✽✽Ω

Capacitive Load Without Oscillation 100 ✽✽pF

DYNAMIC RESPONSE

Full Scale Frequency 500

Dynamic Range 6 ✽✽ decades

Settling Time (V/F) to Specified Linearity

Overload Recovery < 50% Overload

POWER SUPPLY

Rated Voltage ±15 V

Voltage Range ±11 ±20 ✽ V

Quiescent Current ±5.5 ±6.0 ✽✽ ✽ mA

TEMPERATURE RANGE

Specification 0 +70 –25 +85 –55 +125 °C

Operating –25 +85 –55 +125 –55 +125 °C

Storage –25 +85 –65 +150 –65 +150 °C

= ±15V, unless otherwise noted.

CC

= VIN/7.5 R1 C

(1)

(1)

(2)

(3)

OUT

= 7.5 R1 C1 F

OUT

0.01Hz ≤ Oper

Freq ≤ 10kHz ±0.005 ±0.010

0.1Hz ≤ Oper

Freq ≤ 100kHz ±0.025 ±0.05 ✽✽ ✽✽% of FSR

0.5Hz ≤ Oper

Freq ≤ 500kHz ±0.05 ✽✽% of FSR

(2)

Required (see Figure 4) V

= 5mA, C

OUT

OUT

for a Full Scale Input Step

VFC32KP, KU VFC32BM VFC32SM

1

x R

1

>0 +0.25 ✽✽✽✽mA

14 ✽✽ ✽✽ mV

IN

✽✽✽✽µs

MAX

(4)

✽✽ ✽✽% of FSR

14 ✽✽ ✽✽ mV

±3 ✽✽ppm of FSR/°C

5 ✽✽% of FSR

f = 10kHz ±75 ±50 ±100 ±70 ±150 ppm/°C

= 8mA 0 0.2 0.4 ✽✽✽✽✽✽ V

SINK

= 15V 0.01 1.0 ✽✽ ✽✽ µA

O

PU

= 500pF 400 ✽✽ns

LOAD

≤ 7VDC +10 ✽✽ mA

O

MAX

(8)

✽✽ kHz

(9)

(9)

✽✽V

✽✽s

✽✽

✽✽

(5)

✽ Specification the same as VFC32KP.

NOTES: (1) A 25% duty cycle (0.25mA input current) is recommended for best linearity. (2) Adjustable to zero. See Offset and Gain Adjustment section. (3) Linearity error is specified

at any operating frequency from the straight line intersecting 90% of full scale frequency and 0.1% of full scale frequency. See Discussion of Specifications section. Above 200kHz,

it is recommended all grades be operated below +85°C. (4) ±0.015% of FSR for negative inputs shown in Figure 5. Positive inputs are shown in Figure 1. (5) FSR = Full Scale Range

(corresponds to full scale frequency and full scale input voltage). (6) Exclusive of external components’ drift. (7) Positive drift is defined to be increasing frequency with increasing

temperature. (8) For operations above 200kHz up to 500kHz, see Discussion of Specifications and Installation and Operation sections. (9) One pulse of new frequency plus 1µs.

2VFC32

Page 3

ABSOLUTE MAXIMUM RATINGS

Supply Voltage................................................................................... ±22V

Output Sink Current (F

Output Current (V

Input Voltage, –Input..................................................................... ±Supply

Input Voltage, +Input..................................................................... ±Supply

Comparator Input .......................................................................... ±Supply

Storage Temperature Range:

VFC32BM, SM ............................................................. –65°C to +150°C

VFC32KP, KU ................................................................ –25°C to +85°C

) ................................................................ 50mA

OUT

) ...................................................................... +20mA

OUT

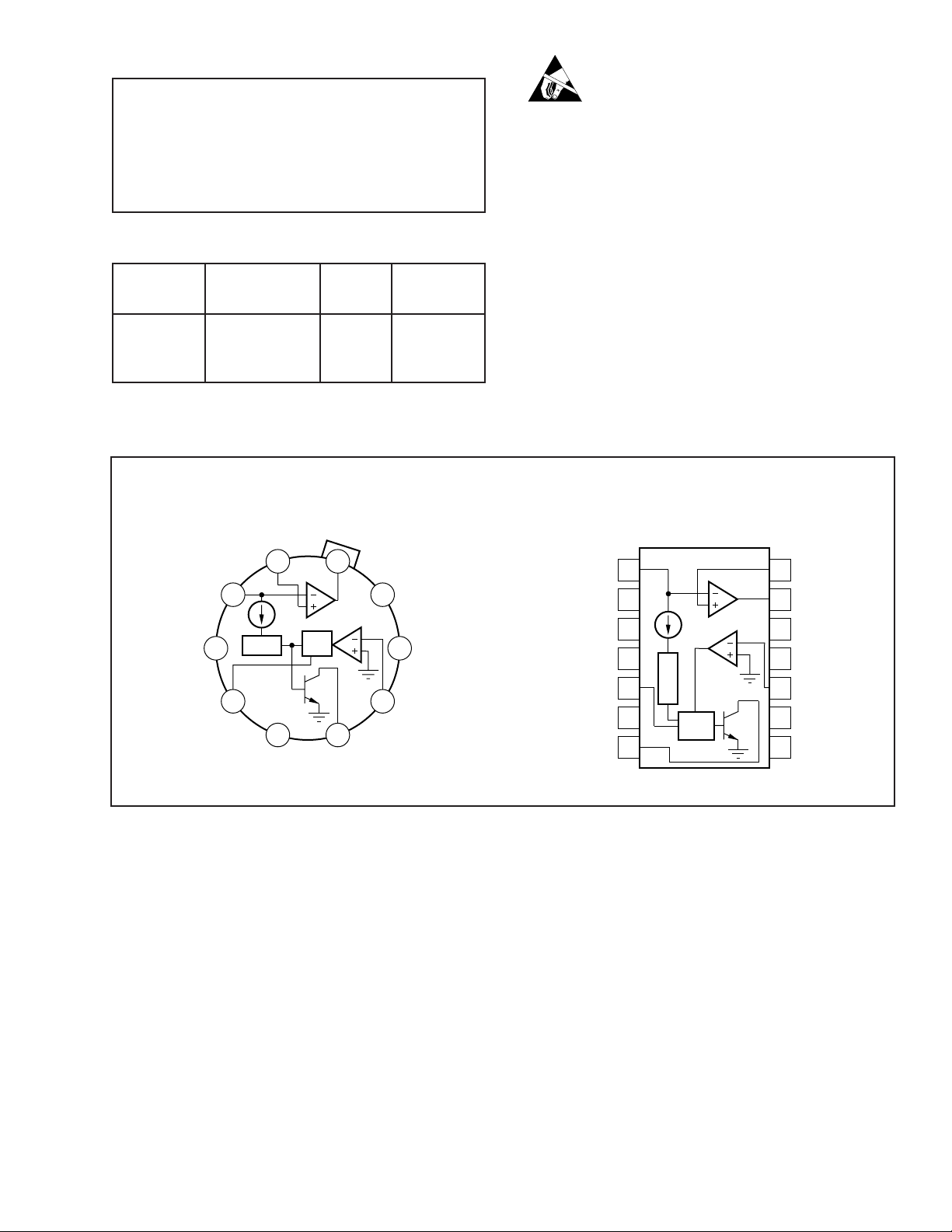

PACKAGE/ORDERING INFORMATION

PACKAGE

DRAWING TEMPERATURE

(1)

PRODUCT PACKAGE NUMBER

VFC32KP 14-Pin Plastic DIP 010 0°C to 70°C

VFC32BM TO-100 Metal 007 –25°C to +85°C

VFC32SM TO-100 Metal 007 –55°C to +125°C

VFC32KU SO-14 SOIC 235 0°C to +70°C

NOTE: (1) For detailed drawing and dimension table, please see end of data

sheet, or Appendix C of Burr-Brown IC Data Book.

RANGE

PIN CONFIGURATIONS

Top View

ELECTROSTATIC

DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown

recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling and

installation procedures can cause damage.

ESD damage can range from subtle performance degradation to

complete device failure. Precision integrated circuits may be

more susceptible to damage because very small parametric

changes could cause the device not to meet its published specifications.

–V

(Case)

CC

One-Shot

Capacitor

M Package

(TO-100)

+In

1

Input Amp

2

–In

Switch

3

4

56

NC

NC = no internal connection

External connection permitted.

One-

shot

P Package

U Package

V

OUT

10

+V

CC

9

Common

8

Comparator

7

Input

f

OUT

–In

NC

NC

–V

One-Shot

Capacitor

NC

f

OUT

CC

(Epoxy Dual-in-line)

1

2

3

4

5

6

7

Switch

One-

shot

Input

Amp

14

13

12

11

10

9

8

+In

V

OUT

+V

CC

Common

Comparator

Input

NC

NC

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes

no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject to change

without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant

any BURR-BROWN product for use in life support devices and/or systems.

3 VFC32

Page 4

TYPICAL PERFORMANCE CURVES

q

)

g

)

q

)

At T

= +25°C and V

A

= ±15V, unless otherwise noted.

CC

0.10

LINEARITY ERROR vs FULL SCALE FREQUENCY

Duty Cycle = 25%

at Full Scale

0.01

Typical Linearity Error (% of FSR)

0.001

1k 1M

10k 100k

Full Scale Fre

uency (Hz

1000

100

LINEARITY ERROR vs OPERATING FREQUENCY

1

0.5

0

Linearity Error (Hz)

TA = +25°C

–0.5

–1.0

0 10k

FULL SCALE DRIFT vs FULL SCALE FREQUENCY

(SM, KP, KU)

(BM)

f

FULL SCALE

1k 7k

2k 3k 4k 5k 6k 8k 9k

= 10kHz, 25% Duty Cycle

= +25°C

T

A

Operatin

Frequency (Hz

Full Scale Temp Drift (ppm of FSR/°C)

10

1k 1M

10k 100k

Full Scale Fre

uency (Hz

4VFC32

Page 5

APPLICATION INFORMATION

Figure 1 shows the basic connection diagram for frequencyto-voltage conversion. R1 sets the input voltage range. For a

10V full-scale input, a 40kΩ input resistor is recommended.

Other input voltage ranges can be achieved by changing the

value of R1.

V

R1=

R1 should be a metal film type for good stability. Manufacturing tolerances can produce approximately ±10% variation

in output frequency. Full-scale output frequency can be

trimmed by adjusting the value of R1—see Figure 3.

The full-scale output frequency is determined by C1. Values

shown in Figure 1 are for a full-scale output frequency of

10kHz. Values for other full-scale frequencies can be read

from Figure 2. Any variation in C1—tolerance, temperature

drift, aging—directly affect the output frequency. Ceramic

NPO or silver-mica types are a good choice.

For full-scale frequencies above 200kHz, use larger capacitor values as indicated in Figure 2, with R1 = 20kΩ.

The value of the integrating capacitor, C2, does not directly

influence the output frequency, but its value must be chosen

within certain bounds. Values chosen from Figure 2 produce

FS

0.25mA

(1)

approximately 2.5Vp-p integrator voltage waveform. If C2’s

value is made too low, the integrator output voltage can

exceed its linear output swing, resulting in a nonlinear

response. Using C2 values larger than shown in Figure 2 is

acceptable.

Accuracy or temperature stability of C2 is not critical because its value does not directly affect the output frequency.

For best linearity, however, C2 should have low leakage and

low dielectric absorption. Polycarbonate and other film

capacitors are generally excellent. Many ceramic types are

adequate, but some low-voltage ceramic capacitor types

may degrade nonlinearity. Electrolytic types are not recommended.

FREQUENCY OUTPUT PIN

The frequency output terminal is an open-collector logic

output. A pull-up resistor is usually connected to a 5V logic

supply to create standard logic-level pulses. It can, however,

be connected to any power supply up to +VCC. Output pulses

have a constant duration and positive-going during the oneshot period. Current flowing in the open-collector output

transistor returns through the Common terminal. This terminal should be connected to logic ground.

V

IN

0 to 10V

Pinout shown is

for DIP or SOIC

packages.

R

40kΩ

f

O

V

INT

+15V

C

2

10nF film

1

V

INT

0.1µF

–15V

0.1µF

One-Shot

C

1

3.3nF

NPO Ceramic

VFC32

Pull-Up Voltage

0V ≤ V

PU ≤ +VCC

+5V

R

PU

4.7kΩ

0 to 10kHz

f

OUT

V

PU

≤ 8mA

R

PU

FIGURE 1. Voltage-to-Frequency Converter Circuit.

5 VFC32

Page 6

FREQUENCY-TO-VOLTAGE CONVERSION

q

)

Figure 4 shows the VFC32 connected as a frequency-tovoltage converter. The capacitive-coupled input network C3,

R6 and R7 allow standard 5V logic levels to trigger the

comparator input. The comparator triggers the one-shot on

the falling edge of the frequency input pulses. Threshold

voltage of the comparator is approximately –0.7V. For

frequency input waveforms less than 5V logic levels, the

R6/R7 voltage divider can be adjusted to a lower voltage to

assure that the comparator is triggered.

The value of C1 is chosen from Figure 2 according to the

full-scale input frequency. C2 smooths the output voltage

waveform. Larger values of C2 reduce the ripple in the

output voltage. Smaller values of C2 allow the output voltage

to settle faster in response to a change in input frequency.

Resistor R1 can be trimmed to achieve the desired output

voltage at the full-scale input frequency.

0.1µF

C

2

10nF

1nF

Capacitor Value

100pF

10pF

33,000pF

C1 = – 30pF

f

FS (kHz)

R1 = 40kΩ

Above 200kHz Full-Scale

66,000pF

C

= – 30pF

1

f

FS (kHz)

R1 = 20kΩ

1k 1M

10k 100k

Full Scale Fre

uency (Hz

PRINCIPLES OF OPERATION

The VFC32 operates on a principle of charge balance. The

signal input current is equal to VIN/R1. This current is

integrated by input op amp and C2, producing a downward

ramping integrator output voltage. When the integrator output ramps to the threshold of the comparator, the one-shot is

triggered. The 1mA reference current is switched to the

integrator input during the one-shot period, causing the

integrator output ramp upward. After the one-shot period,

the integrator again ramps downward.

The oscillation process forces a long-term balance of charge

(or average current) between the input signal current and the

reference current. The equation for charge balance is:

IIN= I

R(AVERAGE)

V

IN

= fOtOS(1mA)

R

1

(2)

(3)

Where:

fO is the output frequency

tOS is the one-shot period, equal to

tOS = 7500 C1 (Farads) (4)

The values suggested for R1 and C1 are chosen to produce a

25% duty cycle at full-scale frequency output. For full-scale

frequencies above 200kHz, the recommended values produce a 50% duty cycle.

FIGURE 2. Capacitor Value Selection.

C

2

0.1µF

Gain Trim

V

IN

10kΩ

Offset

Trim

35kΩ

+15V

10MΩ

100kΩ

–15V

Pinout shown is for

DIP and SOIC packages.

1

14

FIGURE 3. Gain and Offset Voltage Trim Circuit.

1mA

V

INT

13

10

4

–15V

+15V

12

One-Shot

5

C

33nF

VFC32

1

+5V

4.7kΩ

7

11

f

O

6VFC32

Page 7

0 to 10kHz

f

5V Logic

Input

+15V

500pF

IN

12kΩ

2.2kΩ

2.5V

0V

–2.5V

C

2

0.1µF

R

1

40kΩ

0V

+15V

V

O

0 to 10V

+15V

10MΩ

1

14

100kΩ

–15V

FIGURE 4. Frequency-to-Voltage Converter Circuit.

C

2

2nF

1

V

IN

0V to –10V

14

13

10

12

7

NC

One-Shot

11

VFC32

4

5

C

3.3nF

1

–15V

+15V

+5V

0.1µF

13

10

12

One-Shot

7

f

OUT

0 to 50kHz

R

1

40kΩ

Nonlinearity may be higher than

0.1µF

specified due to common-mode

voltage on op amp input.

FIGURE 5. V/F Converter—Negative Input Voltage.

VFC32

4

5

650pF

C

1

–15V

7 VFC32

11

Pinout shown is

for DIP or SOIC

package.

Loading...

Loading...