Page 1

V-Data VDS8616A8A

A

A

A

A

A

A

Synchronous DRAM 4M x 16 Bit x 4 Banks

General Description

The VDS8616A8A are four-bank Synchronous

DRAMs organized as 4,194,304 words x 16 bits x 4

banks,

Synchronous design allows precise cycle control

with the use of system clock I/O transactions are

possible on every clock cycle.

Range of operating frequencies, programmable

burst length and programmable latencies allow the

same device to be useful for a variety of high

bandwidth high performance memory system

applications

Ordering Information.

Part No. Frequency Interface Package

VDS8616A8A-75 133Mhz-333 LVTTL 400mil 54pin TSOPII

Features

•JEDEC standard LVTTL 3.3V power supply

•MRS Cycle with address key programs

-CAS Latency (2 & 3)

-Burst Length (1,2,4,8,& full page)

-Burst Type (sequential & Interleave)

•4 banks operation

ll inputs are sampled at the positive edge of

•

the system clock

•Burst Read single write operation

•Auto & Self refresh

•DQM for masking

•8192 Refresh Cycles

•Package:54-pins 400 mil TSOP-Type II

VDS8616A8A-75A 133Mhz-222 LVTTL 400mil 54pin TSOPII

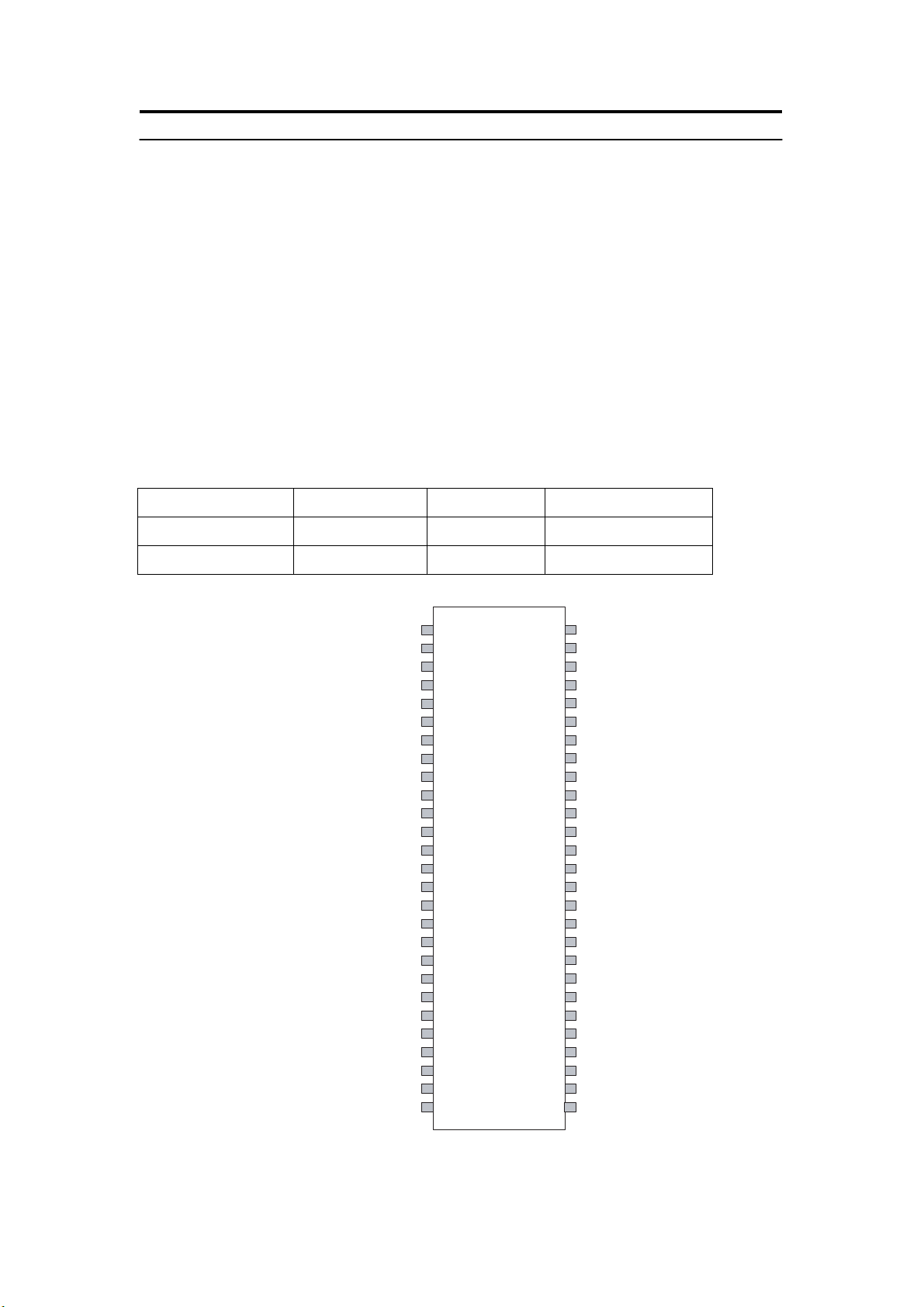

Pin Assignment

V

DD

DQ0

V

DDQ

NC

DQ1

V

SSQ

NC

DQ2

DDQ

V

NC

DQ3

SSQ

V

NC

V

DD

NC

/WE

/CAS

/RAS

/CS

BA0

BA1

10/AP

0

1

2

3

DD

V

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27 28

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

Vss

DQ7

Q

Vss

NC

DQ6

V

DDQ

NC

DQ5

V

SSQ

NC

DQ4

DDQ

V

NC

V

SS

NC/RFU

DQM

CK

CKE

NC

A11

A9

A8

A7

A6

A5

A4

SS

V

54-pin plastic TSOP II 400 mil

Rev 1.0 December, 2001

1

Page 2

V-Data VDS8616A8A

Pin Description

PIN NAME FUNCTION

CK System Clock Active on the positive edge to sample all inputs.

CKE Clock Enable Masks system clock to freeze operation from the next clock cycle. CKE

should be enabled at least on cycle prior new command. Disable input

buffers for power down in standby

/CS Chip Select Disables or Enables device operation by masking or enabling all input

except CK, CKE and L(U)DQM

A0~A12 Address Row / Column address are multiplexed on the same pins.

Row address : A0~A12

Column address : A0~A8

BS0~BS1 Banks Select Selects bank to be activated during row address latch time.

Selects bank for read / write during column address latch time.

DQ0~DQ16 Data Data inputs / outputs are multiplexed on the same pins.

/RAS Row Address Strobe Latches row addresses on the positive edge of the CLK with /RAS low

/CAS Column Address Strobe Latches Column addresses on the positive edge of the CLK with /CAS low

/WE Write Enable Enables write operation and row recharge.

VDD/VSS Power Supply/Ground Power and Ground for the input buffers and the core logic.

VDDQ/VSSQ Data Output Power/Ground Power supply for output buffers.

NC No Connection This pin is recommended to be left No Connection on the device.

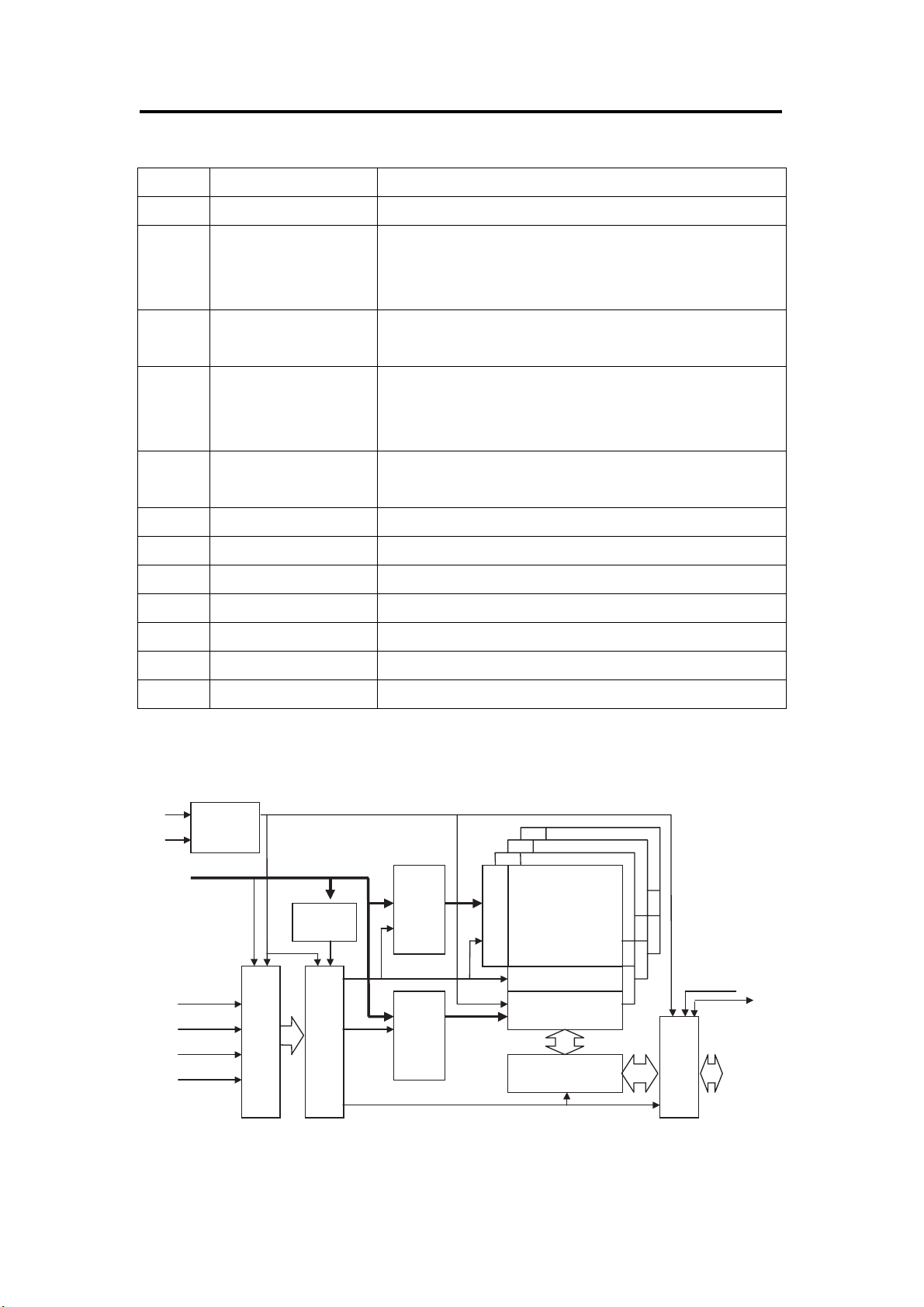

Block Diagram

CK

CKE

Address

/CS

/RAS

/CAS

/WE

Clock

Generator

Mode

Register

Command Decoder

Control Logic

Address

Buffer

&

Refresh

Counter

Column

Address

Buffer

&

Refresh

Counter

Row Decoder

Amplifier

Column Decoder

Data Control Circuit

Bank3

Bank2

Bank1

Bank0

Data Latch

DQ0~DQn

DQM

DQS

Rev 1.0 December, 2001

2

Page 3

V-Data VDS8616A8A

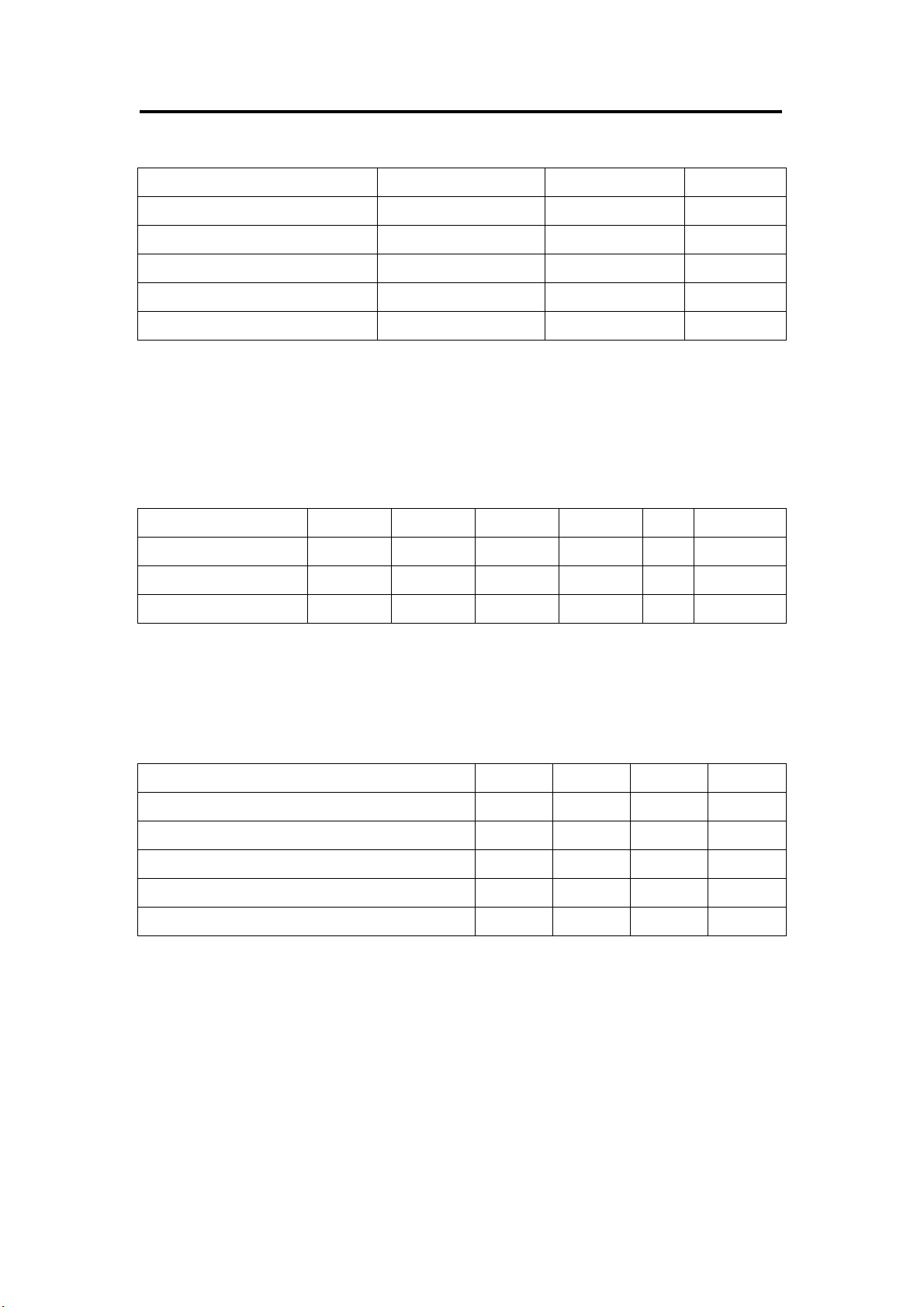

Absolute Maximum Ratings

Parameter Symbol Value Unit

Voltage on any pin relative to Vss VIN, Vout -0.3 ~VDD+0.3 V

Voltage on VDD supply relative to Vss VDD, VDDQ -0.3 ~ 4.6 V

Storage temperature TSTG -55 ~ +150

Power dissipation PD 1 W

Short circuit current IOUT 50 mA

Note : Permanent device damage may occur if ABSOLUTE MAXIMUM RATING are exceeded.

Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

℃

DC Operating Condition

Voltage referenced to Vss = 0V, TA = 0 to 70 ℃

Parameter Symbol Min Typ Max Unit Note

Supply voltage VDD, VDDQ 3.0 3.3 3.6 V

Input logic high voltage VIH 2.0 3.0 VDD+0.3 V 2

Input logic low voltage VIL -0.3 - 0.8 V 2

Note : 1. VIH (max)=Vcc/ VccQ+1.2V for pulse width ≦ 5ns acceptable.

2.V

IL(min)=-Vss/ VssQ-1.2V for pulse width ≦ 5ns acceptable.

AC Operating Condition

Voltage referenced to Vss = 0V, TA = 0 to 70 ℃

Parameter Symbol Value Unit Note

AC input high / low level voltage VIH / VIL 2.4 / 0.4 V

Input timing measurement reference level voltage Vtrip 1.4 V

Input rise / fall time TR / tF 2 Ns

Output timing measurement reference level Voutfef 1.4 V

Output load capacitance for access time measurement CL 50 pF 2

Note: 1. 3.15V ≦ VDD ≦ 3.6V is applied for VDS8616A8A55.

2. Output load to measure access times is equivalent to two TTL gates and one capacitor (30pF). For details,

refer to AC/DC output load circuit.

Rev 1.0 December, 2001

3

Page 4

V-Data VDS8616A8A

Capacitance

TA= 25℃, f-=1Mhz, VCC=3.3V

Parameter Pin Symbol Min Max Unit

CK Cclk - 3.5 pF Input capacitance

A0~A12,BS0 ,BS1,CKE,/CS,/RAS,

/CAS,/WE,LDQM

Data input / output capacitance CI/O - 6.5 pF

Cl1 - 3.8 pF

Output load circuit

3.3 V

50 ohms

Output

Z= 50 ohms

50 pF

DC Characteristics I

Parameter Symbol Min Max Unit Note

Input leakage current ILI -5 5 uA

Output leakage current ILO -5 5 uA

Output high voltage VOH 2.4 - V IOH = -4mA

Output low voltage VOL - 0.4 V IOL = 4mA

Note : 1.VIN = 0 TO 3.6V, All other pins are not tested under VIN = 0V.

2.D

OUT is disabled, VOUT = 0 to 3.6.

Rev 1.0 December, 2001

4

Page 5

V-Data VDS8616A8A

DC Characteristics II

Parameter Symbol Test condition

Speed

Unit Note

75 75A

Operating Current ICC1

Precharge standby

current in power down

mode

Precharge standby

current in Non power

down mode

No Operating Current

in power down mode

Burst mode operating

current

ICC2P

ICC2PS

ICC2

ICC2S

ICC3

ICC3P

ICC4

Burst length=1, One bank active

tRC≧tRC(min),I

CKE≦V

CKE≦V

CKE≧V

tCK=min input signals are

changed one time during 2clks. All

other pins ≧VDD-0.2V or ≦

0.2V

CKE≧V

Input signals are stable.

CKE≦V

CKE≦V

t

CK≧tCK(min),IOL=0 mA

All banks active

OL=0mA

IL(max), tCK=min

IL(max), tCK=∞

IH(min), /CS≧VIH(min),

IH(min), tCK=∞

IL(max), tCK=min

IL(max), tCK=∞

80 75 1

1 1

1 1

40 35

10 10

60 55

10 10

100 95 1

mA

t

Auto refresh current ICC5

ICC6 Standard 3 3

Self refresh current

ICC6L Lower Power - 1

Note: 1. ICC1 and ICC4 depend on output loading and cycle rates. Specified values are measured with the output

open.

2. Min. of tCK is shown at AC characteristics.

CK≧tCK(min),IOL=0 mA

170 160 2

All banks active

Rev 1.0 December, 2001

5

Page 6

V-Data VDS8616A8A

AC Characteristics

Speed

Parameter Symbol

System clock

Cycle time

Clock high pulse width tCHW

Clock low pulse width tCLW

Access time form

clock

Time

/RAS cycle time tRC

/RAS to /CAS delay tRCD

/RAS active time tRAS

/RAS precharge time tRP

/RAS to /RAS bank active delay tRRD

/CAS to /CAS delay tCCD

Data – input setup time tDS

Data – input hold time tDH

Address setup time tAS

Address hold time tAH

CKE setup time tCKS

CKE hold time tCKH

Command setup time tCMS

Command hold time tCMH

Output Data Hold Time tOH

Output Data High Impedance Time tHZ

Output Data Low Impedance Time tLZ

Mode register Set Cycle Time tRSC

Refresh time tREF

Note : 1. Assume tR / tF (input rise and fall time) is 1 ns.

2. Access times to be measured with input signals of 1v / ns edge rate.

3.A new command can be given tRRC after self refresh exit.

/CAS Latency = 2 tCK2

/CAS Latency = 3 tCK3

/CAS Latency = 2 tAC2

/CAS Latency = 3 tAC3

/CAS Latency = 2 tWR2 7.5 10 7.5 Write Recovery

/CAS Latency = 3 tWR3 7 7.5 7

75 75A

Min Max Min Max

7.5

7 1000 7.5 7

2.5 2.5

2.5 2.5

5.4

5.4

56 65

15 20

40 100K 45

15 20

15 15

1 1

1.5 1.5

0.8 0.8

1.5 1.5

0.8 0.8

1.5 1.5

0.8 0.8

1.5 1.5

0.8 0.8

3 3

3 7 3

0 0

14 15

64

Unit Note

1000 10 7.5

ns

ns 1

ns 1

6

ns 2

5.4

ns

ns

100K ns

ns

ns

CLK

ns 1

ns 1

ns 1

ns 1

ns 1

ns 1

ns 1

ns 1

ns

7.5 ns

ns

ns

64 ms

Rev 1.0 December, 2001

6

Page 7

V-Data VDS8616A8A

Command Truth-Table

Command CKEn-1 CKEn /CS /RAS /CAS /WE DQM ADDR A10/AP BA

Mode Register Set H X L L L L X OP code

No Operation H X

Bank Active H X L L H H X RA V

Read L

H X L H L H X CA

Read with Auto Precharge

Write L

H X L H L L X CA

Write with Auto Precharge

Precharge All Bank H X

H X L L H L X X

Precharge select Bank

Burst Stop H X L H H L X X

DQM H X V X

Auto Refresh H H L L L H X X

Entry H L L L L H X

Self Refresh

Exit L H

Entry H L

Precharge

Power down

Exit L H

H X X X

L H H H

H X X X

L H H H

H X X X

L H H H

H X X X

L H H H

X X

V

H

V

H

L V

X

X

X

X

X

Clock Suspend

Entry H L

Exit L H X X

Rev 1.0 December, 2001

H X X X

L V V V

7

X

X

Page 8

V-Data VDS8616A8A

Package Information

SYMBOL

A 1.20 0.047

A1 0.05 0.10 0.15 0.002 0.004 0.006

A2 ----- 1.00 ----- ----- 0.039 -----

B 0.24 0.32 0.40 0.009 0.012 0.016

c -----

D

HE 11.56 11.76 11.96 0.455 0.463 0.471

E 10.06 10.16 10.26 0.396 0.400 0.404

e

L 0.40 0.50 0.60 0.016 0.020 0.024

L1 0.80 REF 0.032 REF

MIN. NOM. MAX. MIN. NOM. MAX.

-----

S

θ

0 ° - 8 ° 0 ° - 8 °

MILLIMETER INCH

0.15

22.22 22.6222.12

-----

0.80 BSC

0.71 REF 0.028 REF

------

-----

-----

0.871

-----

0.006

0.875

0.0315

0.905

-----

400mil 54pin TSOP II Package

Rev 1.0 December, 2001

8

Loading...

Loading...