Page 1

DATA SHEET

MOS INTEGRATED CIRCUIT

µ

PD9903

µ

PD9903 ANALOG SUBSCRIBER LINE LSI (DIGITAL CODEC)

The µPD9903 is a digital CODEC that can be used in analog subscriber circuits such as private branch exchangers

(PBXs) and switching equipment for central offices. It features three of the functions required for analog subscriber

circuits: 2W/4W conversion, CODEC supervision, and subscriber line supervision.

µ

Use of the

in analog subscriber circuits.

FEATURES

• Single-chip monolithic LSI (CMOS)

• PCM CODEC → oversampling-type A/D and D/A converters

• Programmable functions

• Termination impedance

• Hybrid balance network

• Feed resistance

• Feed current

• PAD control

• A-law and

• Digital gain set function

• Ring-Trip function

• Single power supply (+5 V)

• Low power consumption during standby mode: 20 mW (TYP.)

PD9903 in combination with a BS-SLIC (µPC7073) can reduce the number of components required

µ

-law

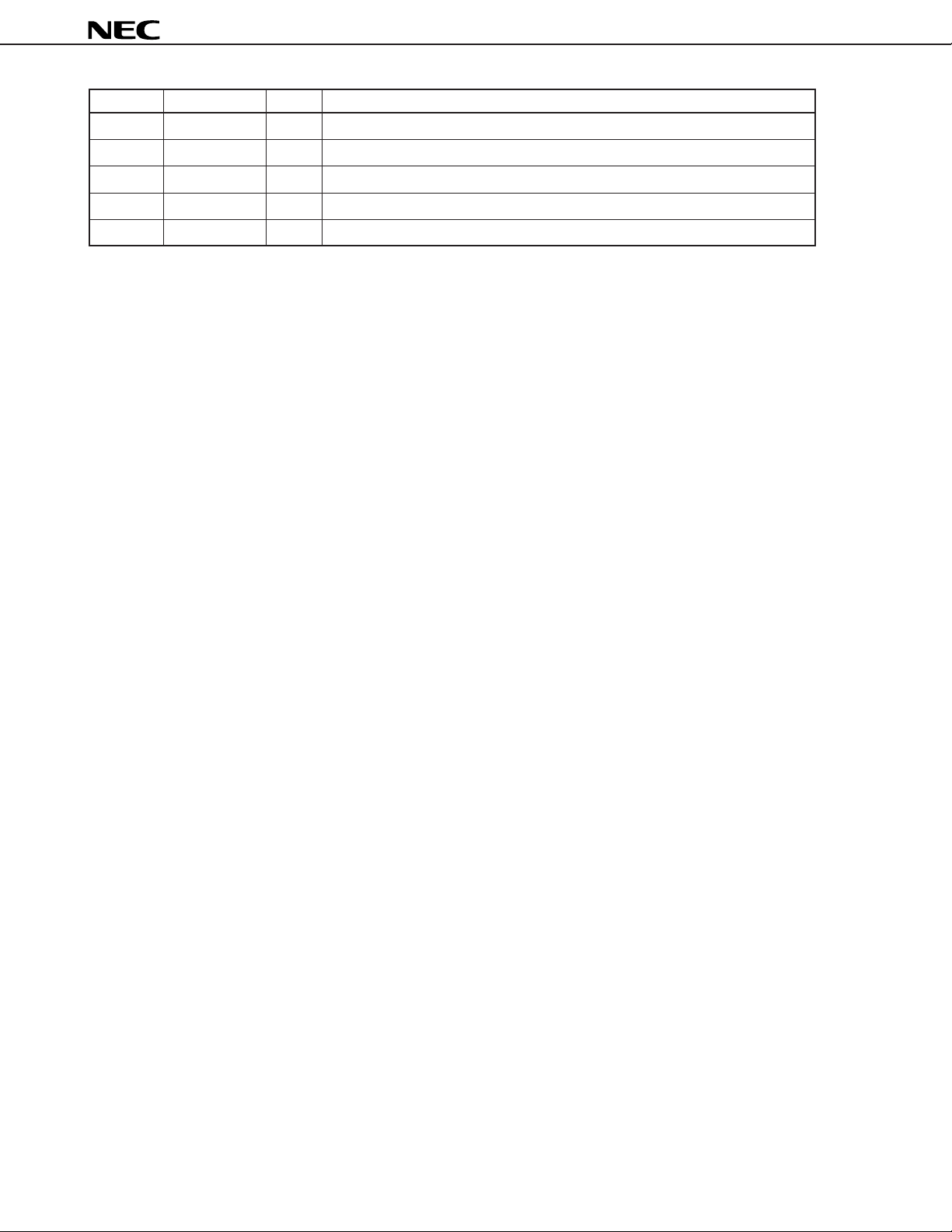

ORDERING INFORMATION

Part Number Package

µ

PD9903GT 48-pin plastic shrink SOP (375 mil)

The information in this document is subject to change without notice.

Document No. S10897EJ3V0DS00 (3rd edition)

Date Published June 1997 N

Printed in Japan

The mark shows major revised points.

©

1996

Page 2

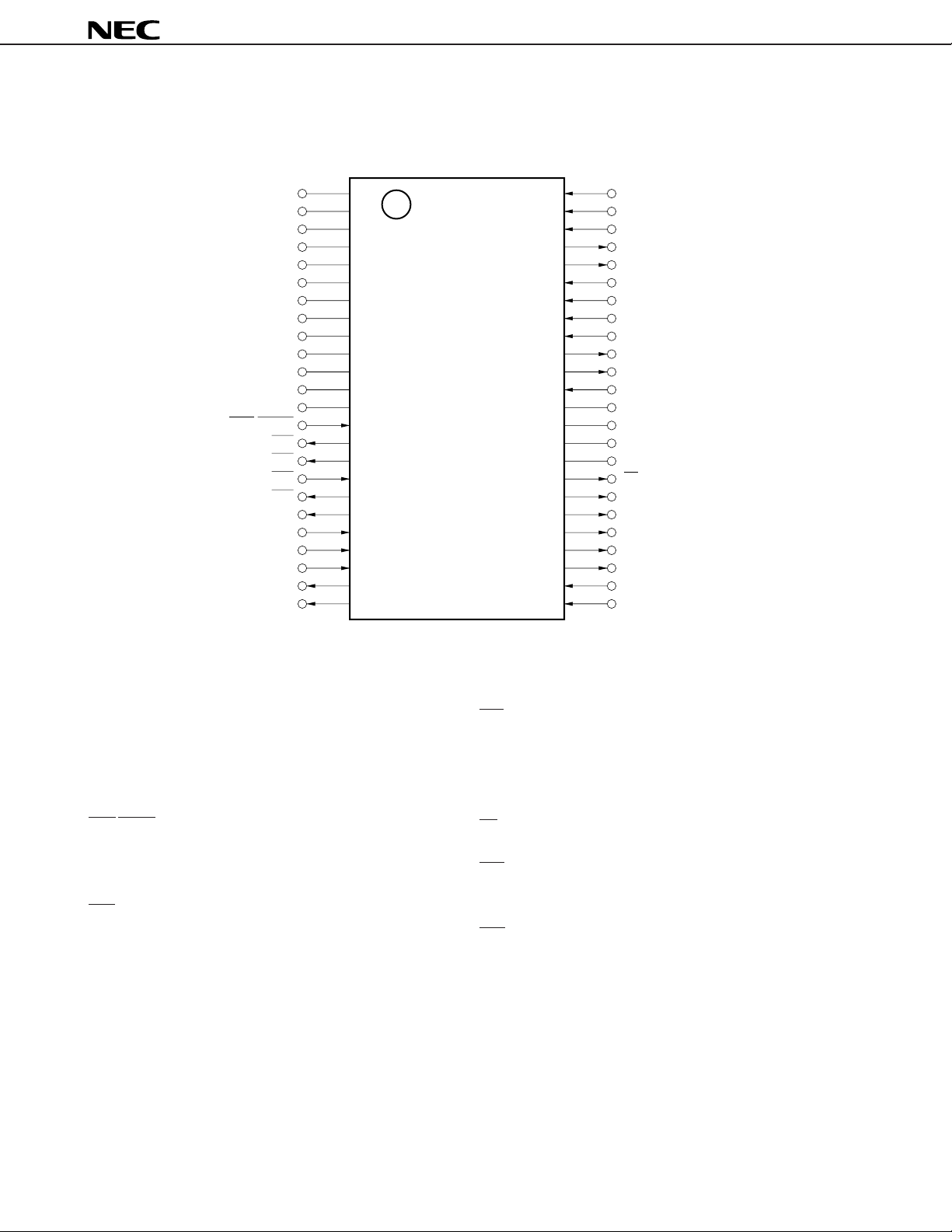

PIN CONFIGURATION (Top View)

48-pin plastic shrink SOP (375 mil)

µ

PD9903

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

AV

DV

DD1

DV

DD2

AUX/MODE

BSY

SUS

RST

EXS

EXD

HW

DCLK

FS

HW

TYPE

1

2

3

4

5

6

7

8

9

10

DD

11

µ

PD9903GT

12

13

14

15

16

17

18

19

R

20

21

22

X

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

DC

IN3

DC

IN2

DC

IN1

DC

OUT1

DC

OUT2

BB

IN

ASCN

AGDT

A

IN

A

OUT

ACOM

ACOM

AGND

SUB

DGND1

DGND2

PD

ALM

BCUT

1

RC

RC

2

RC

3

RT

IN0

RT

IN1

OUT

IN

ACOMIN : ANALOG COMMON VOLTAGE IN DGND1, DGND2: DIGITAL GROUND

ACOMOUT : ANALOG COMMON VOLTAGE OUT DVDD1, DVDD2 : DIGITAL POSITIVE POWER SUPPLY

AGDT : ANALOG GROUND DETECTION SIGNAL IN EXD : EXPANSION PORT DATA

AGND : ANALOG GROUND EXS :

EXPANSION PORT SYNCHRONIZATION

AIN : ANALOG SIGNAL IN FS : FRAME SYNCHRONOUS CLOCK IN

ALM : ALARM OUT HW

R : RECEIVE HIGHWAY DATA IN

AOUT : ANALOG SIGNAL OUT HWX : TRANSMIT HIGHWAY DATA OUT

ASCN : ANALOG LOOP DETECTION SIGNAL IN NC : NO CONNECTION

AUX/MODE : EXTERNAL SIGNAL IN/MODE CONTROL SET PD : POWER DOWN CONTROL OUT

DD : ANALOG POSITIVE POWER SUPPLY RC1 - RC3 : RELAY CONTROL OUT

AV

BBIN :VBB VOLTAGE INFORMATION IN RST : RESET IN

BCUT : BATTERY FEED CUT SIGNAL OUT RT

IN0, RTIN1 : RING TRIP SIGNAL IN

BSY : BUSY SIGNAL OUT SUB : SUB GROUND

DCIN1 - DCIN3 : DC FEEDBACK CONTROL IN SUS : SUSPEND SIGNAL OUT

DCLK : DATA CLOCK IN TYPE : TYPE SIGNAL OUT

OUT1, DCOUT2 : DC FEEDBACK CONTROL OUT

DC

2

Page 3

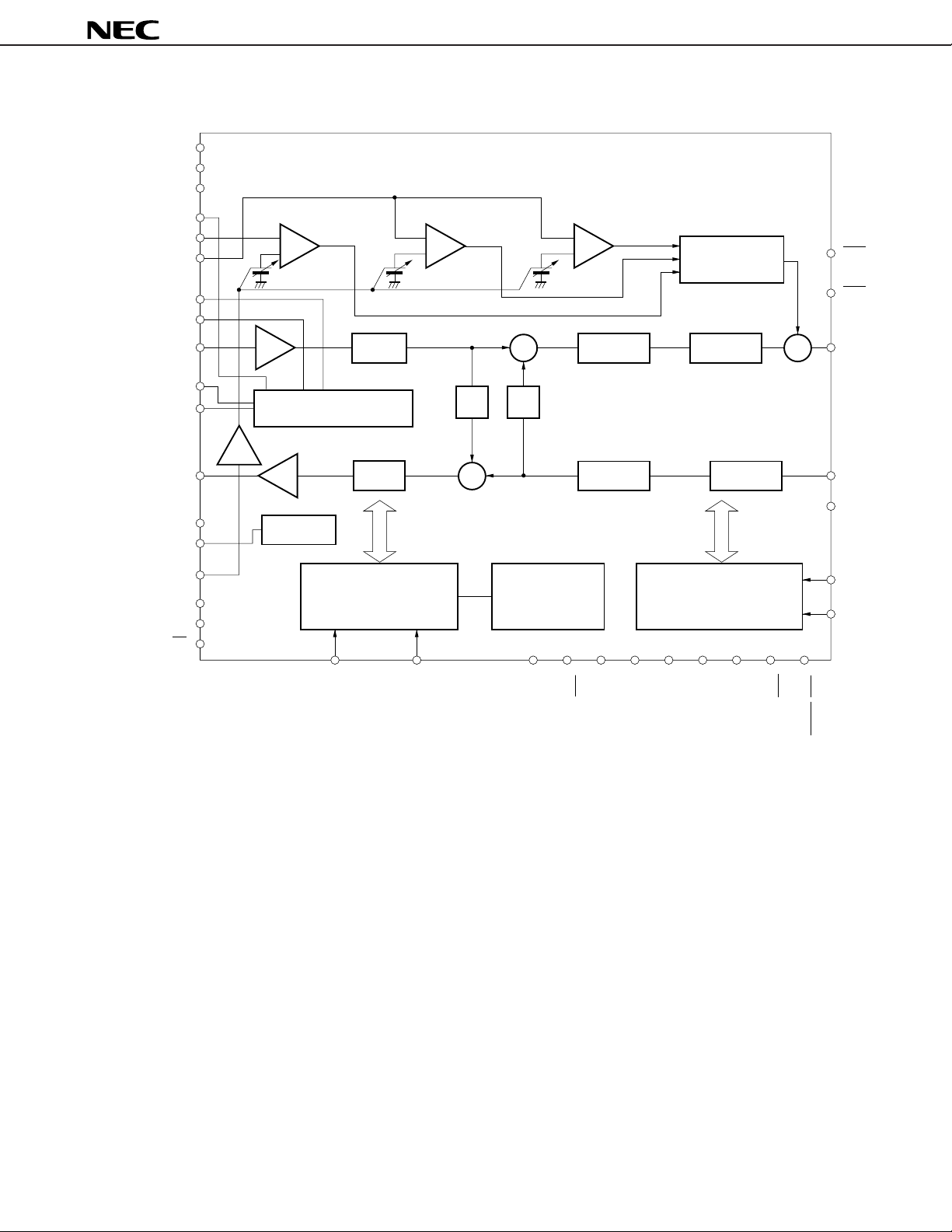

BLOCK DIAGRAM

RC

1

RC

2

RC

3

DC

IN1

ASCN

AGDT

IN2

DC

DC

IN3

A

IN

DC

OUT1

DC

OUT2

A

OUT

ACOM

IN

ACOM

OUT

COMP. COMP. COMP.

+

H

Z

B

Feed control

Reference

voltage

A/D

D/A

H

+

Channel

filter

Channel

filter

SUS

GDT

Waveform shaping

guard processing

SCN

Linear to

m

A or

A or to

linear

µ

PD9903

µ

BSY

SUS

+

HW

HW

X

R

TYPE

BB

BCUT

ALM

PD

IN

FS

Controller Ring-Trip Timing

DCLK

RT

IN0

RT

IN1

EXD

EXS

SUB

AGND

DGND

AVDDDVDDRST

AUX/MODE

3

Page 4

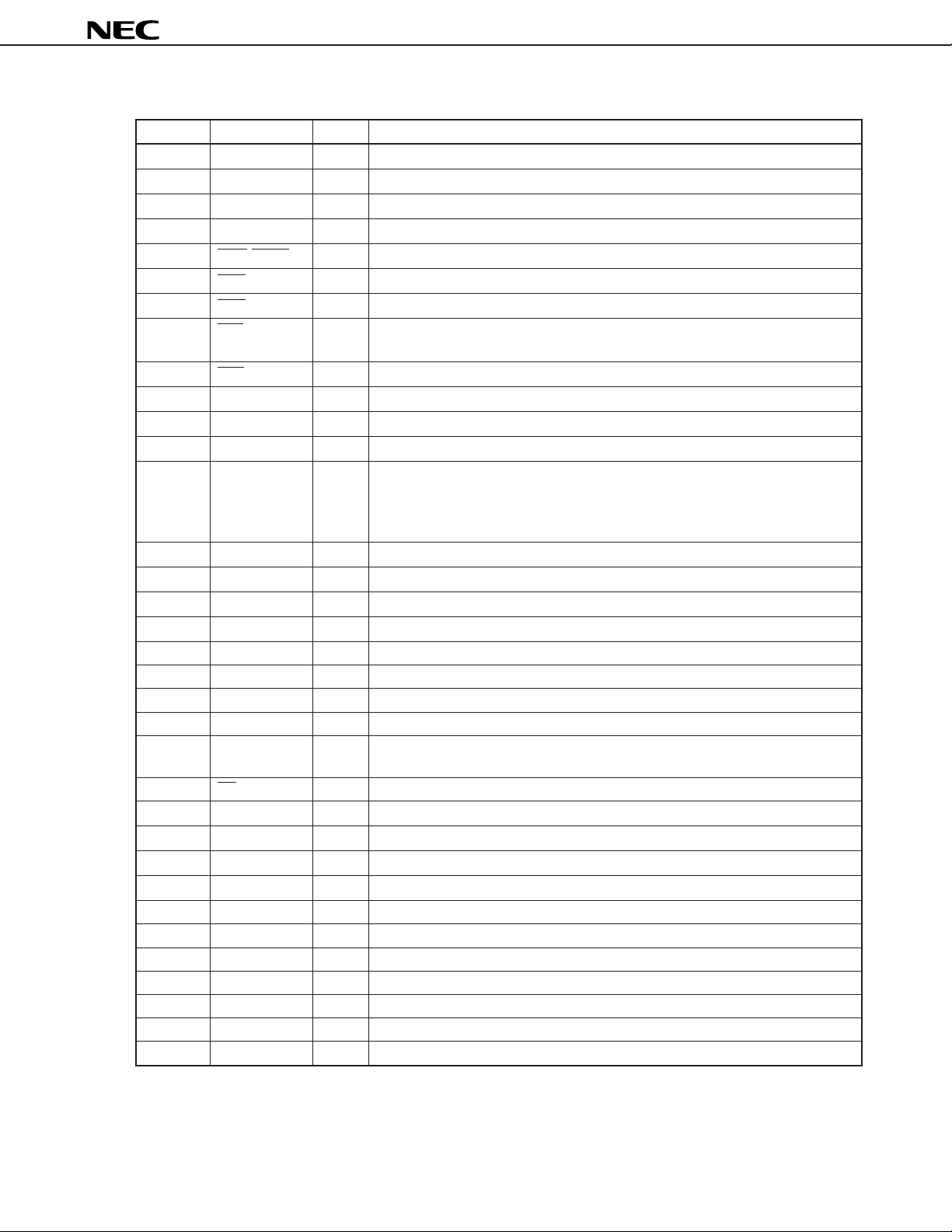

µ

PD9903

CONTENTS

1. PIN FUNCTIONS ...................................................................................................................... 5

2. USE CAUTIONS ....................................................................................................................... 7

3. ELECTRICAL SPECIFICATIONS ........................................................................................... 8

3.1 Discrete unit Ratings...................................................................................................................... 8

3.2 Combined Specifications with the µPC7073 ............................................................................. 17

4. SYSTEM APPLICATION EXAMPLE USING THE µPC7073 AND µPD9903............. 21

5. PACKAGE DRAWING ............................................................................................................. 22

6. RECOMMENDED SOLDERING CONDITIONS ................................................................... 23

4

Page 5

µ

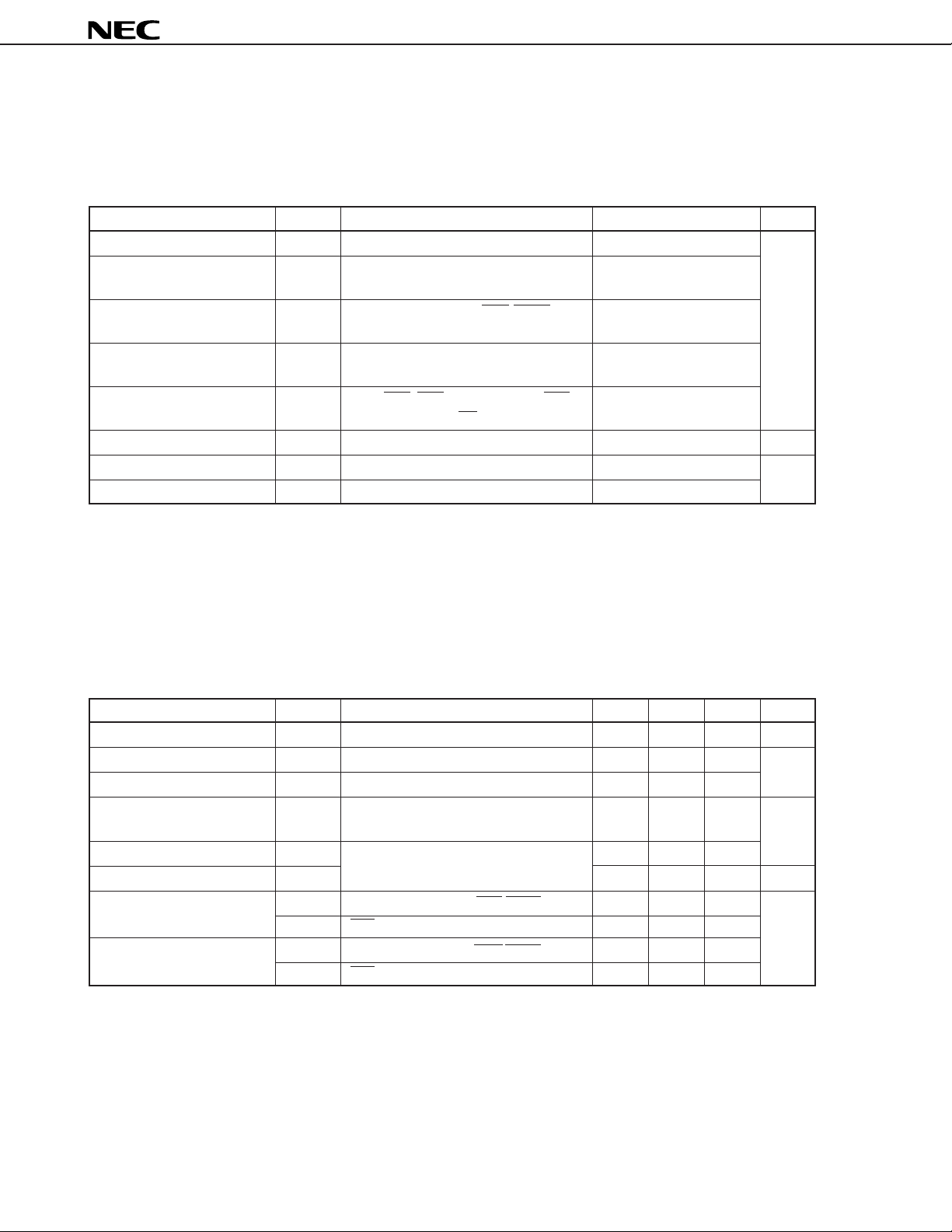

1. PIN FUNCTIONS

Number Pin Name I/O Function

1-10 NC – Leave this pin open.

11 AV DD – +5 V power supply (analog)

12 DVDD1 – +5 V power supply (digital)

13 DVDD2 – +5 V power supply (digital)

14 AUX/MODE I External signaling input

15 BSY O BUSY LED driver output

16 SUS O SUS LED driver output

17 RST I Pin for reset input and power-on reset

H: HWX valid, L: HWX output’s internal F/F clear status

18 EXS O SIPO sync signal output for expansion port

19 EXD O SIPO serial data output for expansion port

20 HWR I Reception highway input [PCM data (8-bit) + CTL data (8-bit)]

21 DCLK I Clock input (2.048 MHz)

22 FS I 8-kHz sync input Rising: HWR PCM data input start

Rising: HWX PCM data output start

Falling: HWR CTL data input start

Falling: HWX SCN data output start

23 HWX O Transmission highway output [PCM data (8-bit) + SCN data (8-bit)]

24 TYPE O HWX data enable

25 RT IN1 I Ring-Trip signal input 2

26 RT IN0 I Ring-Trip signal input 1

27 RC3 O Relay control for network testing [to the µPC7073’s pin 22]

28 RC2 O Relay control for line testing [to the µPC7073’s pin 21]

29 RC1 O Relay control for ringer transmit [to the µPC7073’s pin 20]

30 BCUT O High and wet control output [to the µPC7073’s pin 19]

31 ALM O Control output for ground-fault/power line contact protection mode

32 PD O Power-down control output [to the µPC7073’s pin 17]

33 DGND2 – Digital ground 2

34 DGND1 – Digital ground 1

35 SUB – Substrate ground

36 AGND – Analog ground

37 ACOM IN I Signal ground input

38 ACOM OUT O Signal ground output

39 AOUT O Analog signal output for receive side [to the µPC7073’s pin 10]

40 AIN I Analog signal input for transmit side [to the µPC7073’s pin 9]

41 AGDT I Tip-Ring sum current detection input [to the µPC7073’s pin 8]

42 ASCN I Tip-Ring difference current detection input [to the µPC7073’s pin 7]

43 BB IN IVBB voltage information input [to the µPC7073’s pin 6]

Note 2

Note 2

Note 2

Note 2

Note 3

Note 3

Note 1

Note 1

[to the µPC7073’s pin 18]

[to the µPC7073’s pin 11]

[to the µPC7073’s pin 11]

PD9903

Notes 1. SIPO: Serial In Parallel Out

2. Short AGND, DGND1, DGND2, and SUB directly under the IC and connect them to an analog ground.

3. Short ACOM

IN and ACOMOUT directly under the IC.

5

Page 6

Number Pin Name I/O Function

44 DCOUT2 O DC feedback bias voltage output [to the µPC7073’s pin 5]

45 DCOUT1 O DC feedback control output [to the µPC7073’s pin 4]

46 DCIN1 I DC feedback control input 1 [to the µPC7073’s pin 3]

47 DCIN2 I DC feedback control input 2 [to the µPC7073’s pin 2]

48 DCIN3 I DC feedback control input 3 [to the µPC7073’s pin 1]

µ

PD9903

6

Page 7

µ

PD9903

2. USE CAUTIONS

(1) Combined characteristics of the µPC9903 and µPD7073

• The µPD9903 is designed to be used in combination with the µPC7073. Therefore, the first half of the electrical

µ

specifications described below are ratings for the

combined ratings with the µPC7073.

• Subscriber circuit constants that are determined by factors such as termination impedance are configured to

enable setting by external order parameters. Consequently, input of an order that is not suitable for the target

impedance may result in failure to obtain the required characteristics.

(2) Absolute maximum ratings

Application of voltage or current in excess of the absolute maximum ratings may result in damage. Be

especially cautious about surges, etc.

(3) Load of by-pass capacitor

µ

Because the

supply impedance can cause instability in these internal operational amplifiers (such as oscillation). To

suppress such instability and eliminate power supply noise, connect by-pass capacitors (CACOM = approximate

µ

F) having superior high frequency characteristics as close as possible to the µPC7073’s power supply

0.1

pins (VBB and VCC) and the µPD9903’s power supply pins (AVDD and DVDD).

PC7073 and µPD9903 use several internal high-frequency operational amplifiers, high power

PD9903 as a discrete unit while the second half are

(4) Addition of ACOM pin connection capacitor

µ

The voltage of the ACOM pin between the

source between the µPC9903 and µPC7073. Superposing of noise on this pin may have adverse effects

on transmission characteristics. Therefore, make the wires between the ACOM pins of the two LSIs as short

as possible, and connect capacitors (C

characteristics as close as possible to the pins.

PC7073 and µPD9903 is the reference voltage of the signal

ACOM = approximate 0.1

µ

F) having superior high frequency

7

Page 8

3. ELECTRICAL SPECIFICATIONS

3.1 Discrete unit Ratings

Absolute maximum ratings (TA = +25 °C)

Parameter Symbol Conditions Rating Units

Power supply voltage VDD AVDD, DVDD1, DVDD2 –0.3 to +7.0 V

Analog input voltage VAIN AIN, ASCN, AGDT, ACOMIN, BBIN, –0.3 to VDD + 0.3

DCIN1, DCIN2, and DCIN3 pins

Digital input voltage VDIN HWR, DCLK, FS, RST, AUX/MODE, –0.3 to VDD + 0.3

RTIN0, and RTIN1 pins

Applied voltage to analog VAOUT AOUT, DCOUT1, DCOUT2, and ACOMOUT –0.3 to VDD + 0.3

output pin pins

Applied voltage to digital VDOUT HWX, BSY, SUS, RC1, RC2, RC3, EXS, –0.3 to VDD + 0.3

output pin EXD, BCUT, ALM, PD, and TYPE pins

Power dissipation PT 500 mW

Ambient operating temperature

Storage temperature T stg –65 to +150

TA 0 to +70 ˚C

µ

PD9903

Caution If the absolute maximum rating for any of the above parameters is exceeded even momentarily,

it may adversely affect the quality of this product. In other words, these absolute maximum

ratings have been set to prevent physical damage to the product. Do not use the product in such

a way as to exceed any of these ratings.

Recommended operating conditions (T

A = 0 to 70 °C, VDD = 5 V ± 5 %, GND = 0 V)

(1) DC conditions

Parameter Symbol Conditions MIN. TYP. MAX. Units

Ambient operating temperature

Power supply voltage VDD 4.75 5.0 5.25 V

Analog input voltage VAI ASCN, and AGDT pins 0 VDD

Analog input driving

resistance

Analog output load resistance

Analog output load capacitance

Low level input voltage VIL1 FS, DCLK, HWR, and AUX/MODE pins 0 0.8 V

High level input voltage VIH1 FS, DCLK, HWR, and AUX/MODE pins 2.0 VDD

TA 0 2570˚C

RLA1 ASCN, and AGDT pins 20 kΩ

RLOAD AOUT pin 100

CLOAD 100 pF

VIL2 RST, RTIN0, and RTIN1 pins 0 0.2 × VDD

VIH2 RST, RTIN0, and RTIN1 pins 0.8 × VDD VDD

8

Page 9

µ

PD9903

(2) AC conditions

Parameter Symbol Conditions MIN. TYP. MAX. Units

Data clock frequency fDCLK (= 1/tCY) ± 50 ppm 2048 kHz

Data clock pulse width tDCLK 200 ns

Frame sync clock frequency fS ± 50 ppm 8.0 kHz

High level frame sync pulse tWHS tCY × 8ns

width

Low level frame sync pulse tWLS tCY × 8ns

width

Clock rise time tR 30 ns

Clock fall time tF 30 ns

Float in sync timing tCSD1 100 ns

tCSD2 40 ns

High level width of frame tWHSC 100 ns

sync clock and data clock

HWR set-up time tDSR Note 1 65 ns

HWR hold time tDHR Note 1 120 ns

Minimum width of reset pulse

PWRST RST pin

Note 2

10

µ

s

Notes 1. During timing measurement, use 5 ns as the rise time and fall time for the digital input wave form and

clock signal.

µ

2. The

PD9903 is initialized when high level input is applied to the RST pin after applying low level input

for several clock widths. (However, use of the RST pin is not guaranteed during low level input. Also,

µ

low level input alone does not initialize the

PD9903.)

9

Page 10

µ

PD9903

DC Characteristics (TA = 0 to 70 °C, VDD = 5 V ± 0.25 V, VDG = VAG = 0 V, fDCLK = 2048 kHz, all output pins are

unloaded)

(1) Current consumption

Parameter Symbol Conditions MIN. TYP. MAX. Units

Circuit current IDD During normal mode 15 21 mA

Power-down circuit current IDDPD During power-down mode 46 6

(2) Digital interface

Parameter Symbol Conditions MIN. TYP. MAX. Units

Digital input current IID 0 ≤ VDIN ≤ VDD for FS, DCLK, HWR, –10 +10

RTIN0, RTIN1, and RST pins

Digital input pull-up current IIL VDIN = 0 V for AUX/MODE pin –50 –7 –0.5

3-state leakage current IL 0 ≤ VDIN ≤ VDD for HWX pin –10 +10

Low level output voltage VOL1 IOL = 3.4 mA for HWX pin 0.4 V

VOL2 IOL = 0.2 mA for RC1, RC2, RC3, BCUT, 0.4

ALM, PD, EXS, and EXD pins

VOL3 IOL = 5 mA for BSY and SUS pins 1.1

High level output voltage VOH1 IOH = –0.6 mA for HWX and TYPE pins 2.4

VOH2 IOH = –2.0 mA for RC1, RC2, RC3, BCUT, 2.4

ALM, PD, EXS, and EXD pins

VOH3 IOH = 0 mA for BSY and SUS pins VDD – 0.5

Output capacitance of digital COD f = 1 MHz, 15 pF

output pin unmeasured pins returned to 0 V

Input capacitance of digital CID f = 1 MHz, 10

input pin unmeasured pins returned to 0 V

µ

A

(3) AIN pin

Parameter Symbol Conditions MIN. TYP. MAX. Units

Input bias current IB Input voltage: –10 +10

Input resistance RIN 1MΩ

Input capacitance CIN 10 pF

µ

A

(4) AOUT pin

Parameter Symbol Conditions MIN. TYP. MAX. Units

Output offset voltage VOA HWR PCM data: zero PCM code, –100 +100 mV

referenced to VACOM

Output resistance ROUT I/O current: –100 to +100 µA50Ω

10

Page 11

µ

PD9903

(5) ASCN and AGDT output pins

Parameter Symbol Conditions MIN. TYP. MAX. Units

Input bias current IB Input voltage: 0 to VDD –10 +10

Input resistance RIN 1MΩ

(6) ACOMOUT pin

Parameter Symbol Conditions MIN. TYP. MAX. Units

Output voltage VACOM I/O current: –0.1 to +0.1 mA 2380 2420 mV

µ

A

11

Page 12

AC characteristics (TA = 0 to 70 °C, VDD = 5 V ± 0.25 V, VDG = VAG = 0, fDCLK = 2048 kHz)

Parameter Symbol Conditions MIN. TYP. MAX. Units

Data enable delay time tDZX1 HWX and TYPE pins, when FS is delayed 170 ns

longer than DCLK

tDZX2 HWX and TYPE pins, when DCLK is 170 ns

delayed longer than FS

Data delay time tDDX HWX pin 180 ns

Data hold time tHZX HWX and TYPE pins 30 200 ns

Delay time to EXS falling edge

Delay time to EXS rising edge

EXD data delay time tDEXD EXD pin 120 ns

Signaling bit set-up delay tDSIG 2

time

Status bit set-up delay time tDST 2

LED driver set-up delay time tDLED BSY and SUS pins 2

Delay time to rising edge tTHL 100 ns

Delay time to falling edge t TLH 100 ns

Transmit delay time to tDAUX AUX pin 125

external bit

tDEXSf EXS pin 120 ns

tDEXSr EXS pin 120 ns

µ

PD9903

µ

s

µ

s

µ

s

µ

s

12

Page 13

Timing charts

µ

PD9903

(1) PCM data transmission timing (HW

(a) DCLK is later than FS

t

R

FS

t

CY

t

CSD2

DCLK

12 8

t

DCLK

t

DZX2

Hi-Z

HW

X

MSB 2nd 7th LSB

(PCM data)

t

DZX2

TYPE

Hi-Z

(b) FS is later than DCLK

X pin)

t

R

t

t

DDX

DCLK

t

WHS

t

F

t

HZX

t

HZX

t

F

Hi-ZHi-Level

FS

DCLK

HW

(PCM data)

TYPE

CSD1

t

WHSC

t

12 8

t

DZX1

Hi-Z

X

t

DZX1

Hi-Z

MSB 2nd 7th LSB

Hi-Level Hi-Z

13

Page 14

(2) SCN data transmission timing (HWX pin)

(a) DCLK is later than FS

µ

PD9903

F

t

FS

t

CSD2

DCLK

t

DZX2

Hi-Z

HW

X

(SCN data)

t

DZX2

TYPE

Hi-Z

(b) FS is later than DCLK

FS

t

WLS

t

CY

t

R

t

DCLK

t

F

12 8

HZX

t

DCLK

t

DDX

t

MSB 2nd 7th LSB

t

HZX

Hi-ZHi-Level

t

R

DCLK

HW

(SCN data)

TYPE

t

CSD1

WHSC

t

12 8

t

DZX1

Hi-Z

X

t

DZX1

Hi-Z

MSB 2nd 7th LSB

Hi-Level Hi-Z

14

Page 15

(3) PCM data reception timing (HWR pin)

(a) DCLK is later than FS

t

R

FS

t

CY

t

t

CSD2

RtDCLK

µ

PD9903

t

WHS

t

F

t

F

DCLK

R

HW

(PCM data)

Note

Note Don’t care

(b) FS is later than DCLK

FS

t

CSD1

t

WHSC

DCLK

189

1

t

DSR

MSB

t

DCLK

t

DHR

Note

2

2 8

tR, t

F

2nd 7th

Note

8th

9

Note

15

Page 16

(4) CTL data reception timing (HWR pin)

(a) DCLK is later than FS

t

F

FS

t

CY

t

t

CSD2

RtDCLK

µ

PD9903

t

WLS

t

F

t

R

DCLK

HW

(CTL data)

R

Note

Note Don’t care

(b) FS is later than DCLK

FS

t

CSD1

t

DCLK

1

t

DSR

DCLK

t

DHR

t

MSB

WHSC

18

28

tR, t

F

Note

2nd 7th

Note

8th

9

Note

2

16

Page 17

µ

PD9903

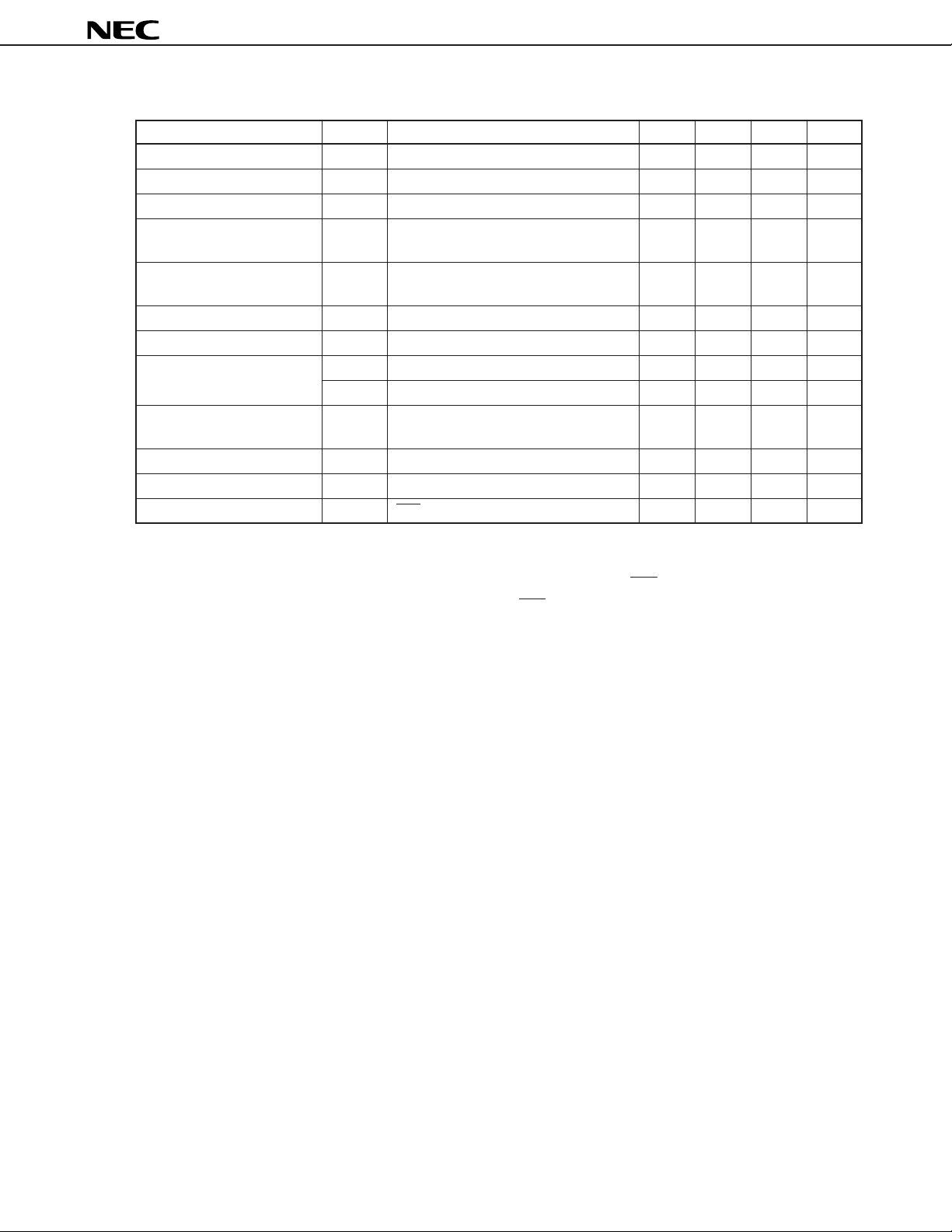

3.2 Combined Specifications with the µPC7073

DC characteristics

µ

PC7073 (VBB = –42 to –58 V, VCC = 5 V ± 0.25 V, TA = 0 to 70 ˚C, 18 ≤ IL ≤ ILMAX (mA))

µ

PD9903 (TA = 0 to 70 ˚C, VDD = 5 V ± 0.25 V, VDG = VAG = 0 V, fDCLK = 2048 kHz)

Parameter Symbol Conditions MIN. TYP. MAX. Units

DC feed resistance RBF 200 Ω feed 180 200 220 Ω

400 Ω feed 360 400 440

Minimum loop current ILMIN VBB = –51 V 200 Ω feed 21.7 22.2 22.6 mA

RL = 1900 Ω 400 Ω feed 18.2 18.8 19.3

Maximum current setting ILMAX ILMAX = 76 mA setting 200 Ω feed 70 76 82 mA

value 400 Ω feed 50 55 60

ILMAX = 45 mA setting 40 45 50

ILMAX = 35 mA setting 31 35 39

Pin voltage during on-hook VTS Normal on-hook, 2.25 2.55 2.85 V

between Tip and GND, VBB = –48 V

VRS Normal on-hook, 3.05 3.35 3.65

between Ring and VBB, VBB = –48 V

VTS On-hook transmission, 2.25 2.55 2.85

between Tip and GND, VBB = –48 V

VRS On-hook transmission, 3.05 3.35 3.65

between Ring and VBB, VBB = –48 V

Voltage between lines VTS VBB = –48 V VBB – 7.0 VBB – 5.9 VBB – 5.0 V

during on-hook

Supervisory control VBBF 32 35 38 V

– VBB abnormal voltage

17

Page 18

µ

PD9903

Parameter

Loop detection operating RON1 Includes termination 200 Ω feed 2500 Ω

resistance (during normal resistance 400 Ω feed 2100

transmission)

Loop detection non-operating 200 Ω feed 3900

resistance (during normal 400 Ω feed 3500

transmission)

Loop detection operating RON2 Includes termination 200 Ω feed 1900 Ω

resistance (during on hook resistance 400 Ω feed 1500

transmission)

Loop detection non-operating

resistance (during on hook 400 Ω feed 2440

transmission)

Loop release non-operating RON3 Includes termination 200 Ω feed 2960 Ω

resistance resistance 400 Ω feed 2560

Loop release operating 200 Ω feed 4540

resistance 400 Ω feed 4140

Ground detection 1 (C/O) RON4 Includes termination resistance 5.2 kΩ

operating resistance

Ground detection 1 (C/O) 20

non-operating resistance

Note

Symbol Conditions MIN. TYP. MAX. Units

200 Ω feed 2840

Ground-fault/power line RON6 Includes termination ILMAX = 45/76 mA 340 Ω

contact detection resistance

operating resistance Off-hook state

Ground-fault/power line Includes termination ILMAX = 45/76 mA 870 Ω

contact detection non- resistance

operating resistance

Ground-fault/power line RON7 Includes termination resistance 1.4 kΩ

contact release nonoperating resistance

Ground-fault/power line 10

contact release operating

resistance

ILMAX = 35 mA 480

ILMAX = 35 mA 1130

Note The above values are resistance-converted values.

18

Page 19

µ

PD9903

Transmission characteristics

µ

PC7073 (VBB = –42 to –58 V, VCC = 5 V ± 0.25 V, TA = 0 to 70 ˚C, 18 ≤ IL ≤ ILMAX (mA))

µ

PD9903 (TA = 0 to 70 ˚C, VDD = 5 V ± 0.25 V, VDG= VAG = 0 V, fDCLK = 2048 kHz)

Parameter Symbol Conditions MIN. TYP. MAX. Units

Insertion loss IL A-D input signal –0.45 0.0 +0.45 dB

0 dBm0 1 kHz

D-A input signal –0.45 0.0 +0.45

0 dBm0 1 kHz

Transfer loss frequency FRX A-D 60 Hz 24.0 – dB

characteristics Reference input signal 200 Hz 0.6 2.0

1015 Hz 0 dBm0 300 Hz –0.15 +0.21

400 to 3000 Hz –0.15 +0.15

3200 Hz –0.15 +0.65

3400 Hz 0.2 0.8

FRR D-A 60 Hz 0.2 4.0

Reference input signal 200 Hz 0.1 1.0

1015 Hz 0 dBm0 300 Hz –0.15 +0.25

400 to 3000 Hz –0.15 +0.15

3200 Hz –0.15 +0.65

3400 Hz 0.2 0.8

Gain tracking GTX A-D +3 to –40 dBm0 –0.2 +0.2 dB

(tone method) Reference input signal –50 dBm0 –0.5 +0.5

–10 dBm0 –55 dBm0 –1.0 +1.0

f = 700 to 1100 Hz

GTR D-A +3 to –40 dBm0 –0.2 +0.2

Reference input signal –50 dBm0 –0.4 +0.4

–10 dBm0 –55 dBm0 –0.8 +0.8

f = 700 to 1100 Hz

Return loss RL Input signal 300 Hz 16 dB

0 dBm0 500 to 2000 Hz 20

ZT = 600 Ω + 2.16 µF 2000 to 3400 Hz 16

Echo attenuation TBRL Input signal 300 Hz 18 dB

0 dBm0 500 to 2500 Hz 22

ZT = 600 Ω + 2.16 µF 3400 Hz 18

Transmit channel total SDX A-D +3 to –30 dBm0 36 dB

power distortion factor Input signal –40 dBm0 30

(tone method) f = 700 to 1100 Hz –45 dBm0 25

SDR D-A +3 to –30 dBm0 36

Input signal –40 dBm0 30

f = 700 to 1100 Hz –45 dBm0 25

19

Page 20

µ

PD9903

Parameter Symbol Conditions MIN. TYP. MAX. Units

Absolute delay DA A-A Input signal 0 dBm0 540

characteristics

Absolute delay distortion DO A-A 500 Hz 1400

frequency characteristics 600 HZ 700

1000 to 2600 Hz 200

2800 Hz 1400

Intermodulation (2 Tone) IMD A-D Input signal 44.0 dB

f1, f2: 300 to 3400 Hz

–4 to –21 dBm0

Measurement signal: 2 × f1 – f2

level (2 × f1 – f2) vs level (f1, f2)

D-A Input signal 44.0

f1, f2: 300 to 3400 Hz

–4 to –21 dBm0

Measurement signal: 2 × f1 – f2

level (2 × f1 – f2) vs level (f1, f2)

Single frequency noise NSF D-A –54 dBm0

PAD level set at 0 dB

Measurement signal up to f = 256 kHz

Deviation in gain setting ∆DGSX

for transmission channel Setting value: +7.5 to +3.0 dB –0.2 +0.2

Deviation in gain setting ∆DGSR

for reception chanel Setting value: 0.0 to –5.0 dB –0.1 +0.1

Idle circuit noise IDN24

IDN42

Line to ground balance LCL RF = 50 Ω f = 300 to 600 Hz 42 dB

attenuation

AC induction noise LFI IL = 0 mA VIN = 6 Vrms 43 dBrnc

resistance

A-D

Difference from reference set value

+3.0 to –3.5 dB –0.1 +0.1

D-A

Difference from reference set value

–5.0 to –8.5 dB –0.2 +0.2

2W-4W A-law Psophometric weighted

µ

-law C message weighted

4W-2W A-law Psophometric weighted

µ

-law C message weighted

Relative accuracy = 0.5 %

IL = 20 mA VIN = 15 Vrms 20

f = 600 to 3400 Hz

48

–67 dBm0p

23 dBrnc0

–76 dBm0p

14 dBrnc0

µ

dB

s

20

Page 21

T

R

TEST0

TEST1

TEST2

TEST3

S

S

T1 R

T2

50 Ω

(0.5 %, 1 W)

Z1

Z2

FT

R

D2

D3

R

FR

50 Ω

(0.5 %, 1 W)

D4

BB

V

Q1

D1

3.6 kΩ (1 %, 1 W)

Q4

(–48 V)

1 F

(6 V)

R

TE

R

RE

3.6 kΩ (1 %, 1 W)

C

VCC

+

µ

37

38

24

40

42

32

44

45

0.1 F

(100 V)

R T1 T2

–

48 25 27 29

CC

V

RY1RY2RY

B

T

T

E

T

EF

T

S

R

S

R

EF

R

E

R

B

IN

BB

V

TTX

23

47

C

VBB

–

+

µ

PC7073

µ

(BS-LSI)

GND231GND115CPSR46C

PSR

C

0.68 F

µ

(50 V)

36

–++

DC

33

C

–

0.68 F

(10 V)

3

ACOM

DC

DC

DC

IN+

OP

34

DC

µ

T

BIAS

R

OUT3

OUT2

OUT1

DC

IN1

DC

IN2

BCUT

ALM

PD

RC

RC

RC

BB

OUT

IN–

ASCN

OP

AGDT

11

35

X

9

10

X

1

2

3

4

5

19

18

17

20

1

21

2

22

3

6

7

8

C

C

COM

0.1 F

µ

(5 V)

C

AC

0.68 F (50 V)

µ

+

–

GDT

–

37

38

40

39

48

47

46

45

44

30

31

32

29

28

27

43

42

41

+

0.68 F

(10 V)

C

VDD

+

–

0.1 F

µ

(6 V)

ACOM

ACOM

A

IN

A

OUT

CD

CD

CD

DC

DC

BCUT

11 12 13 16 15

IN

DD

OUT

AV

IN3

IN2

IN1

OUT1

PC9903

µ

OUT2

(HCS-LSI)

ALM

PD

1

RC

RC

2

RC

3

BB

IN

ASCN

AGDT

µ

AGND

SUB

36 35 34 33 26 25

DD2DVDD1

DV

DGND1

R

SUS

1 kΩ

SUS

AUX/MODE

DGND2

BSY

R

1 kΩ 2 kΩ

R

PULL

BSY

23

HW

X

24

TYPE

22

FS

21

DCLK

20

HW

R

19

EXD

18

EXS

17

RST

14

IN1RTIN0

RT

V

CC

(+5 V)

V

DD

(+5 V)

HW

X

TYPE

FS

DCLK

HW

R

EXD

EXS

RST

AUX/MODE

4. SYSTEM APPLICATION EXAMPLE USING THE

µ

PC7073 AND

µ

PD9903

21

CR

G

Ring-Trip detector

µ

PD9903

Page 22

5. PACKAGE DRAWING

48 PIN PLASTIC SHRINK SOP (375 mil)

48 25

detail of lead end

–3°

+7°

3°

µ

PD9903

124

A

G

F

E

C

M

M

D

N

NOTE

Each lead centerline is located within 0.10

mm (0.004 inch) of its true position (T.P.) at

maximum material condition.

H

I

K

B

L

P48GT-65-375B-1

ITEM MILLIMETERS INCHES

A

B

C

D

E

F

G

H

K

L

M

N

16.21 MAX.

0.63 MAX.

0.65 (T.P.)

0.30±0.10

0.125±0.075

2.0 MAX.

1.7±0.1

10.0±0.3

I

J

8.0±0.2

1.0±0.2

+0.10

0.15

–0.05

0.5±0.2

0.10

0.10

0.639 MAX.

0.025 MAX.

0.026 (T.P.)

+0.004

0.012

–0.005

0.005±0.003

0.079 MAX.

0.067±0.004

+0.012

0.394

–0.013

0.315±0.008

+0.009

0.039

–0.008

+0.004

0.006

–0.002

+0.008

0.020

–0.009

0.004

0.004

J

22

Page 23

µ

PD9903

6. RECOMMENDED SOLDERING CONDITIONS

This product should be soldered and mounted under the conditions recommended below.

For details of recommended soldering conditions, refer to the information document Semiconductor Device

Mounting Technology Manual (C10535E).

For soldering methods and conditions other than those recommended, please contact your NEC sales

representative.

SURFACE MOUNT TYPE

µ

PC9903GT: 48-pin plastic shrink SOP (375 mil)

Soldering Method Soldering Conditions

Infrared ray reflow Package peak temperature: 235 ˚C IR35-00-1

Reflow time: 30 sec. max. (210 ˚C or above)

Number of times: 1 time

Partial heating Pin temperature: 300 ˚C max. –

method Heat time: 3 sec. max. (per each side of the device)

Recommended

Condition Symbol

23

Page 24

[MEMO]

µ

PD9903

24

Page 25

[MEMO]

µ

PD9903

25

Page 26

[MEMO]

µ

PD9903

26

Page 27

NOTES FOR CMOS DEVICES

1 PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note: Strong electric field, when exposed to a MOS device, can cause destruction

of the gate oxide and ultimately degrade the device operation. Steps must

be taken to stop generation of static electricity as much as possible, and

quickly dissipate it once, when it has occurred. Environmental control must

be adequate. When it is dry, humidifier should be used. It is recommended

to avoid using insulators that easily build static electricity. Semiconductor

devices must be stored and transported in an anti-static container, static

shielding bag or conductive material. All test and measurement tools

including work bench and floor should be grounded. The operator should

be grounded using wrist strap. Semiconductor devices must not be touched

with bare hands. Similar precautions need to be taken for PW boards with

semiconductor devices on it.

µ

PD9903

2 HANDLING OF UNUSED INPUT PINS FOR CMOS

Note: No connection for CMOS device inputs can be cause of malfunction. If no

connection is provided to the input pins, it is possible that an internal input

level may be generated due to noise, etc., hence causing malfunction. CMOS

devices behave differently than Bipolar or NMOS devices. Input levels of

CMOS devices must be fixed high or low by using a pull-up or pull-down

circuitry. Each unused pin should be connected to VDD or GND with a

resistor, if it is considered to have a possibility of being an output pin. All

handling related to the unused pins must be judged device by device and

related specifications governing the devices.

3 STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note: Power-on does not necessarily define initial status of MOS device. Production

process of MOS does not define the initial operation status of the device.

Immediately after the power source is turned ON, the devices with reset

function have not yet been initialized. Hence, power-on does not guarantee

out-pin levels, I/O settings or contents of registers. Device is not initialized

until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

27

Page 28

µ

PD9903

[MEMO]

The application circuits and their parameters are for reference only and are not intended for use in actual design-ins.

No part of this document may be copied or reproduced in any form or by any means without the prior written

consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in

this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property

rights of third parties by or arising from use of a device described herein or any other liability arising from use

of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other

intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices,

the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or

property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety

measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a

customer designated "quality assurance program" for a specific application. The recommended applications of

a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device

before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment,

audio and visual equipment, home electronic appliances, machine tools, personal electronic

equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster

systems, anti-crime systems, safety equipment and medical equipment (not specifically designed

for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life

support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books.

If customers intend to use NEC devices for applications other than those specified for Standard quality grade,

they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

M4 96.5

Loading...

Loading...