Page 1

INTEGRATED CIRCUITS

DATA SH EET

TDA5155

Pre-amplifier for Hard Disk Drive

(HDD) with MR-read/inductive write

heads

Preliminary specification

File under Integrated Circuits, IC11

1997 Apr 08

Page 2

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

with MR-read/inductive write heads

CONTENTS

1 FEATURES

2 APPLICATIONS

3 GENERAL DESCRIPTION

4 ORDERING INFORMATION

5 QUICK REFERENCE DATA

6 BLOCK DIAGRAM

7 PINNING

8 FUNCTIONAL DESCRIPTION

8.1 Read mode

8.2 Write mode

8.3 Sleep mode

8.4 Standby mode

8.5 Active mode

8.6 Bi-directional serial interface

8.6.1 Addressing

8.6.2 Programming data

8.6.3 Reading data

8.7 Operation of the serial interface

8.7.1 Configuration

8.7.2 Power control

8.7.3 Head select

8.7.4 Servo write

8.7.5 Test

8.7.6 Write amplifier programmable capacitors

8.7.7 High frequency gain attenuator register

8.7.8 High frequency gain boost register

8.7.9 Settle pulse

8.7.10 Address registers summary

8.8 Head unsafe

8.9 HUS survey

9 LIMITING VALUES

10 HANDLING

11 THERMAL RESISTANCE

12 RECOMMENDED OPERATION

CONDITIONS

13 CHARACTERISTICS

14 DEFINITIONS

15 LIFE SUPPORT APPLICATIONS

TDA5155

1997 Apr 08 2

Page 3

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

with MR-read/inductive write heads

1 FEATURES

• Designed for 10 dual-stripe MR-read/inductive write

heads

• Current bias-current sense architecture

• Single supply voltage (5.0 V ±10%); a separate write

drivers supply pin can be biased from VCC to 8 V +10%

• MR elements connected to ground (GND)

• Equal bias currents in the two MR stripes of each head

• On-chip AC couplings eliminate MR head DC offset

• 3-wire serial interface for programming

• Programmable voltage/current mode write data input

• Programmable high frequency zero-pole gain boost

• Programmable write driver compensation capacitance

• Programmable MR bias currents and write currents

• 1-bit programmable read gain

• Sleep, standby, active and test modes available

• Measurement of head resistances in test mode

• In test mode, one MR bias current may be forced to a

minimum current

• Short write current rise and fall times with near

rail-to-rail voltage swing

• Head unsafe pin for signalling of abnormal conditions

and behaviour

• Low supply voltage write current inhibit (active or

inactive)

• Support servo writing

• Provide temperature monitor

• Thermal asperity detection with programmable

threshold level

• Requires only one external resistor.

2 APPLICATIONS

• Hard Disk Drive (HDD).

TDA5155

3 GENERAL DESCRIPTION

The 5.0 V pre-amplifier for HDD applications has been

designed for five terminal, dual-stripe

Magneto-Resistive (MR)-read/inductive write heads.

The disks of the disk drive are connected to ground.

To avoid voltage breakthrough between the heads and the

disk, the MR elements of the heads are also connected to

ground. The symmetry of the dual-stripe head-amplifier

combination automatically distinguishes between the

differential signals such as signals and the common-mode

effects like interference. The latter are rejected by the

amplifier.

The device incorporates read amplifiers, write amplifiers, a

serial interface, digital-to-analog converters, reference and

control circuits which all operate on a single supply voltage

of 5 V ±10%. The output drivers have a separate supply

voltage pin which can be connected to a higher supply

voltage of up to 8 V +10%. The complementary output

stages of the write amplifier allow writing with near

rail-to-rail peak voltages across the inductive write head.

The read amplifier has low input impedance. The DC offset

between the two stripes of the MR head is eliminated using

on-chip AC coupling. Fast settling features are used to

keep the transients short. As an option, the read amplifier

may be left biased during writing so as to reduce the

duration of these transients even further. Series

inductance in the leads between the amplifier and

MR heads influences the bandwidth which can be

compensated by using a programmable high frequency

gain boost (HF zero). HF noise and bandwidth can be

attenuated using a programmable high frequency gain

attenuator (HF pole).

On-chip digital-to-analog converters for MR bias currents

and write currents are programmed via a 3-wire serial

interface. Head selection, mode control, testing and servo

writing can also be programmed using the serial interface.

In sleep mode the CMOS serial interface is operational.

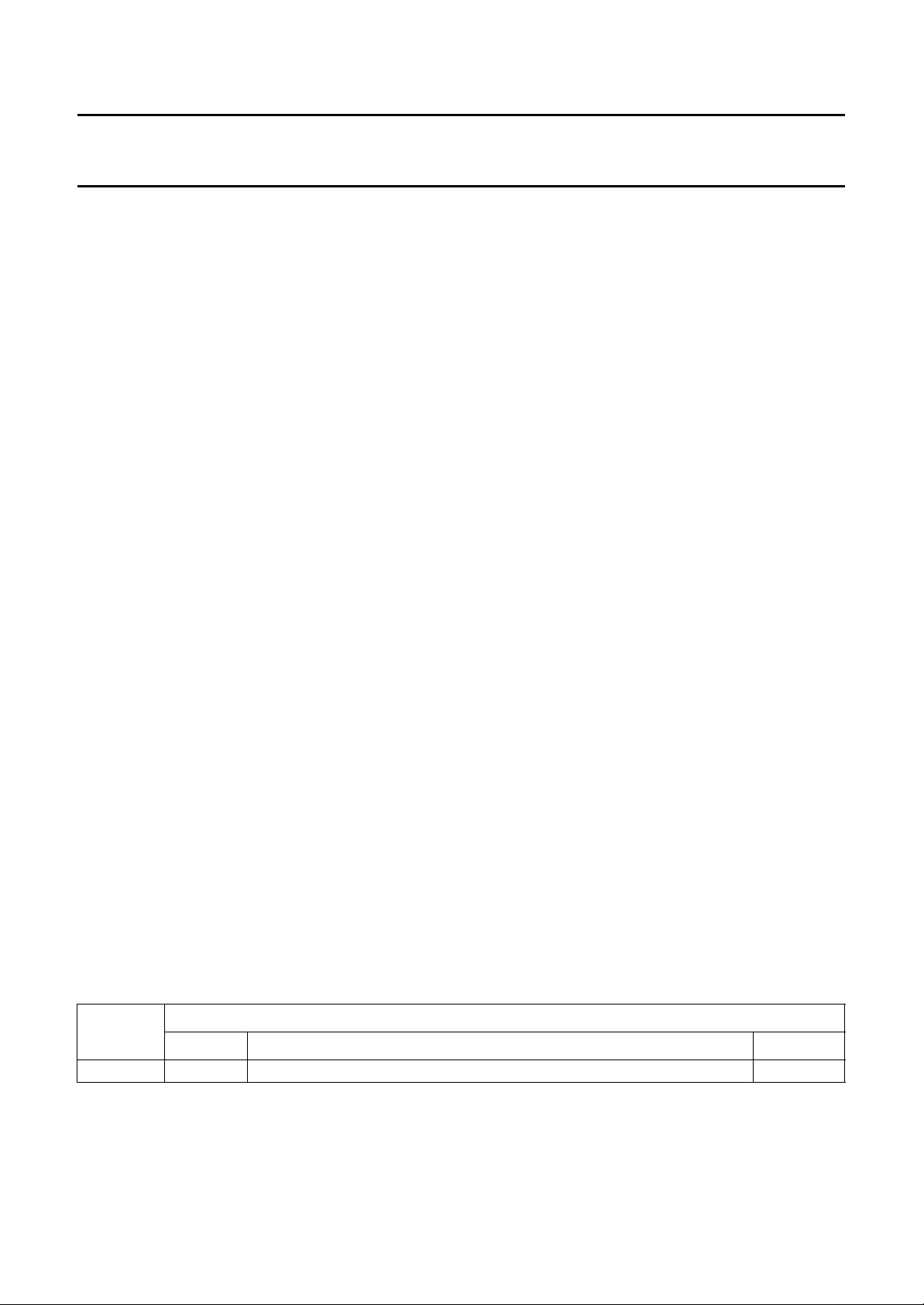

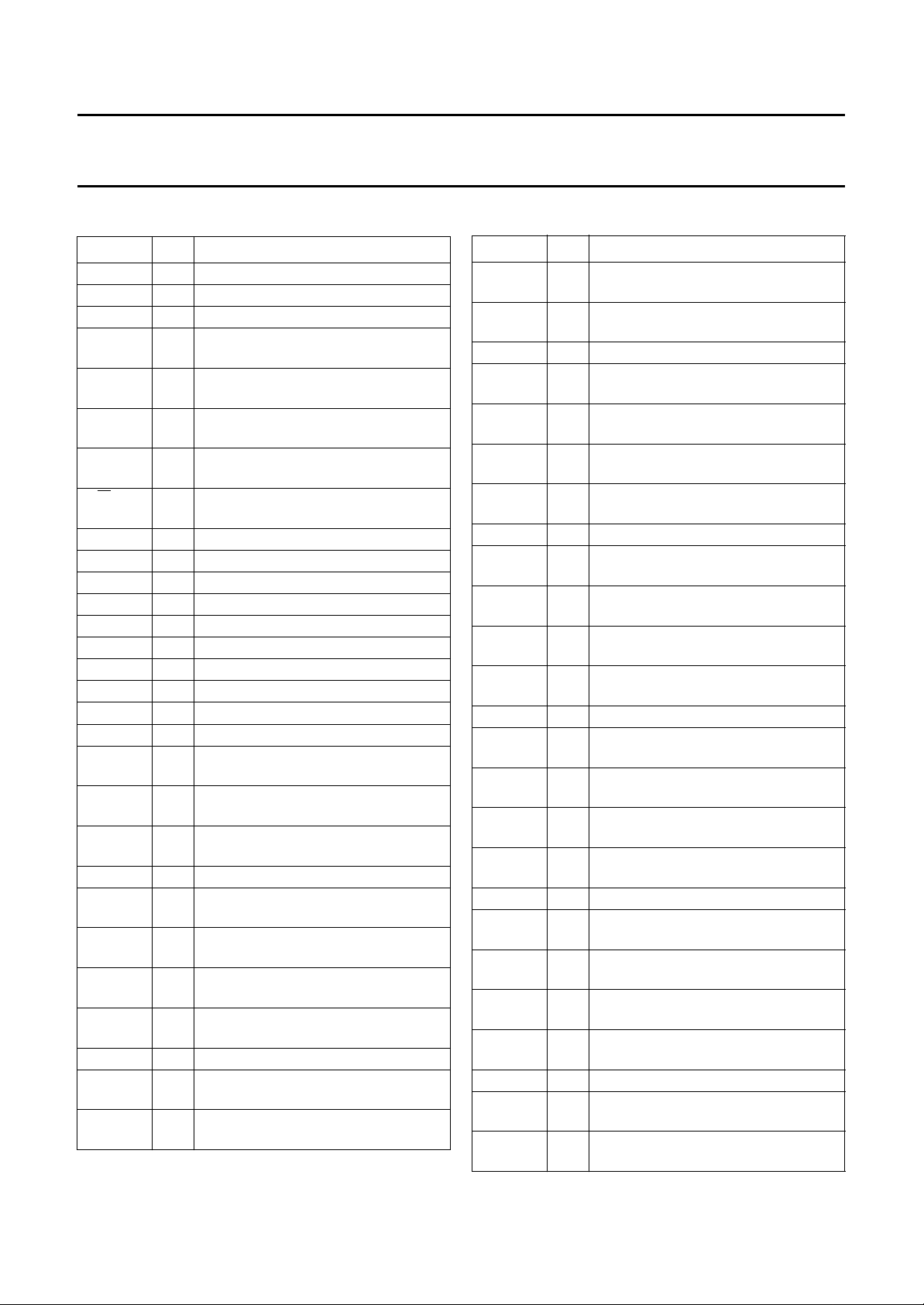

Fig.1 shows the block diagram of the device.

4 ORDERING INFORMATION

TYPE

NUMBER

TDA5155X − naked die −

1997 Apr 08 3

NAME DESCRIPTION VERSION

PACKAGE

Page 4

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

TDA5155

with MR-read/inductive write heads

5 QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

CC

V

CC(WD)

G

v(dif)

B

−3dB

F noise figure R

V

irn

CMRR common mode rejection ratio

PSRR power supply rejection ratio

, t

t

r

f

I

MR(PR)

I

WR(b-p)

f

SCLK

supply voltage 4.5 5.0 5.5 V

supply voltage for write drivers V

CC

8.0 8.8 V

differential voltage gain from head inputs to RDx, RDy;

RMR=28Ω; IMR=10mA

data bit d4 = 0 − 160 −

data bit d4 = 1 − 226 −

−3 dB frequency bandwidth upper bandwidth without gain

− 220 − MHz

boost (4 nH lead inductance)

=28Ω; IMR=10mA;

MR

T

=25°C; f = 20 MHz

amb

input referred noise voltage RMR=28Ω; IMR=10mA;

T

=25°C; f = 20 MHz

amb

− 3.0 3.2 dB

− 0.9 1.0 nV/√Hz

IMR=10mA

mismatch <5%

R

MR

f < 1 MHz − 45 − dB

f < 100 MHz − 25 − dB

IMR=10mA

(input referred) R

mismatch <5%

MR

f < 1 MHz − 80 − dB

f < 100 MHz − 50 − dB

write current rise/fall time

(10% to 90%)

programming MR bias current

Lh= 150 nH; Rh=10Ω;

IWR= 35 mA; f = 20 MHz

V

V

R

ext

= 8.0 V −−1.8 ns

CC(WD)

= 6.5 V −−2.1 ns

CC(WD)

=10kΩ 5 − 20.5 mA

range

programming write current range

R

=10kΩ 20 − 51 mA

ext

(base-to-peak)

serial interface clock rate −−25 MHz

1997 Apr 08 4

Page 5

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

with MR-read/inductive write heads

6 BLOCK DIAGRAM

handbook, full pagewidth

WDlx(i)

WDly(i)

WDlx(v)

WDly(v)

HUS

R

ext

6

7

4

5

3

17

WRITE DRIVER

INPUT

HEAD UNSAFE

INDICATOR

LOW SUPPLY

VOLTAGE

INDICATOR

V

CC

16

TDA5155

FF

WRITE

CURRENT

SOURCE

VOLTAGE

REFERENCE

TDA5155

V

CC(WD)

(5 to 8 V)

1

20, 25, 30, 35,

40, 45, 50, 55,

10

10

10

WRITE DRIVER

AND

READ PREAMP

(10×)

60, 65

19, 24,

29, 34, 39, 44,

49, 54, 59, 64

nWy

nWx

R/W

SCLK

SEN

SDATA

RDx

RDy

+V

CC

8

11

9

10

13

14

SERIAL

INTERFACE

20 kΩ

5

4

4

GNDn

TAS

DETECTOR

4

head select

CURRENT

SOURCE

2, 12, 15, 18

5

3

10

R

MR

23, 28, 33, 38,

43, 48, 53, 58,

10

10

10

63, 68

22, 27, 32, 37,

42, 47, 52, 57,

62, 67

21, 26, 31, 36,

41, 46, 51, 56,

61, 66

MGG982

nRy

nGND

nRx

Fig.1 Block diagram.

1997 Apr 08 5

Page 6

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

with MR-read/inductive write heads

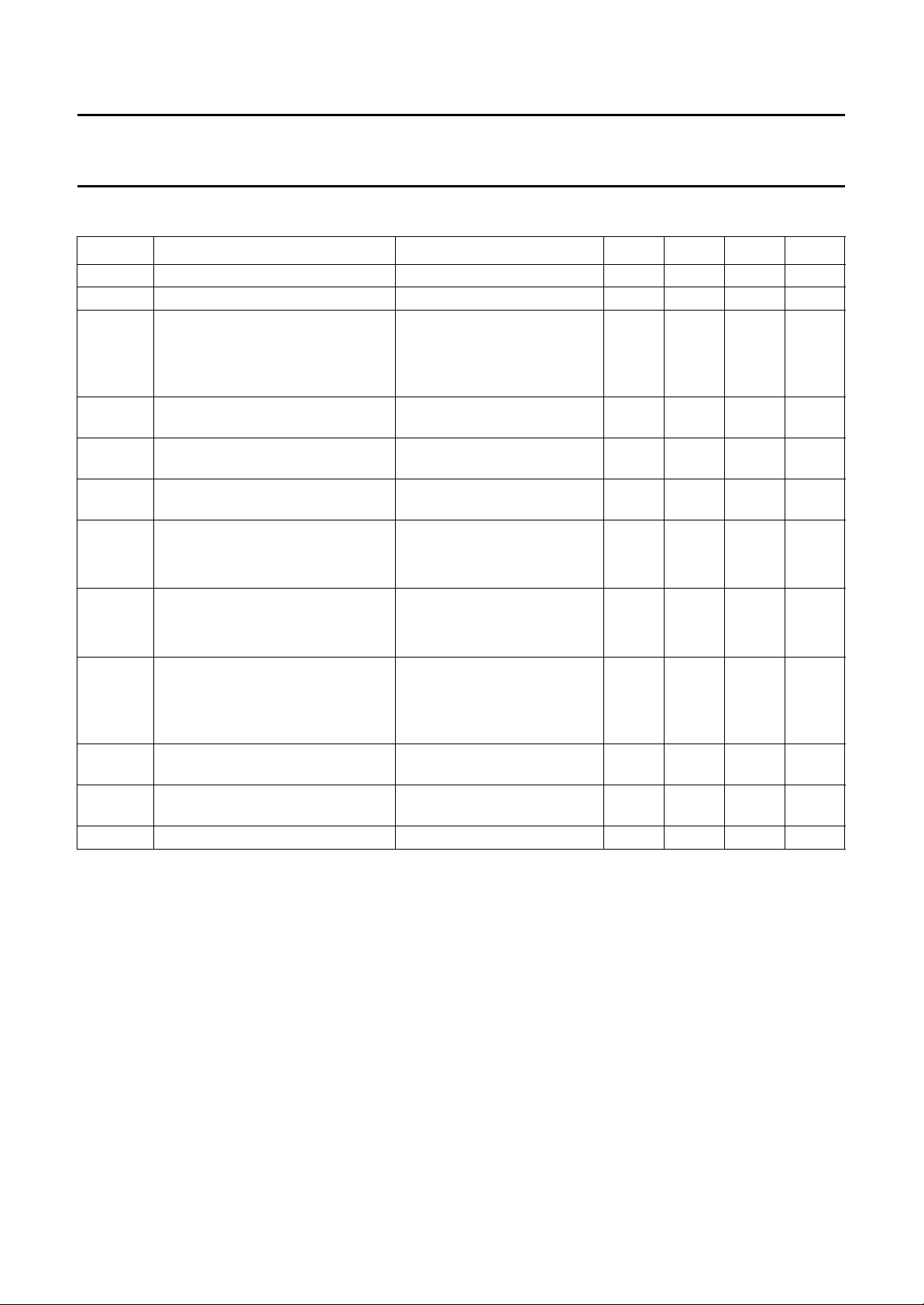

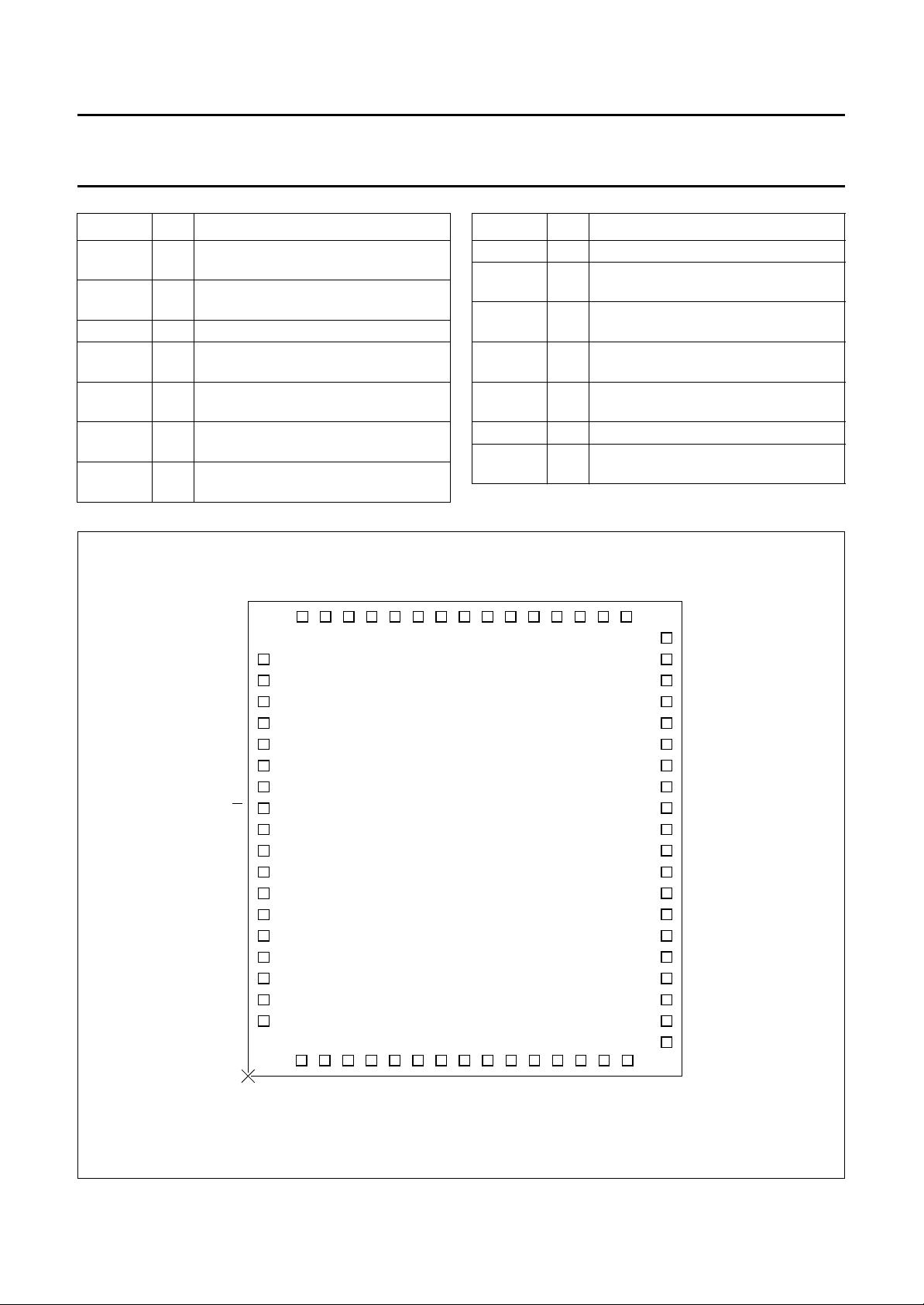

7 PINNING

SYMBOL PAD DESCRIPTION

V

CC(WD)

GND1 2 ground connection 1

HUS 3 head unsafe output

WDIx(v) 4 write data input (differential, voltage

WDIy(v) 5 write data input (differential, voltage

WDIx(i) 6 write data input (differential, current

WDIy(i) 7 write data input (differential, current

R/

W 8 read/write (read = active HIGH,

SEN 9 serial bus enable

SDATA 10 serial bus data

SCLK 11 serial bus clock

GND2 12 ground connection 2

RDx 13 read data output (differential x − y)

RDy 14 read data output (differential x − y)

GND3 15 ground connection 3

V

CC

R

ext

GND4 18 ground connection 4

0Wx 19 inductive write head connection for

0Wy 20 inductive write head connection for

0Rx 21 MR-read head connection for head

0GND 22 ground connection for head H0

0Ry 23 MR-read head connection for head

1Wx 24 inductive write head connection for

1Wy 25 inductive write head connection for

1Rx 26 MR-read head connection for head

1GND 27 ground connection for head H1

1Ry 28 MR-read head connection for head

2Wx 29 inductive write head connection for

1 supply voltage for the write drivers

input)

input)

input)

input)

write = active LOW)

16 supply voltage

17 10 kΩ external resistor

head H0 (differential x − y)

head H0 (differential x − y)

H0 (differential x − y)

H0 (differential x − y)

head H1 (differential x − y)

head H1 (differential x − y)

H1 (differential x − y)

H1 (differential x − y)

head H2 (differential x − y)

TDA5155

SYMBOL PAD DESCRIPTION

2Wy 30 inductive write head connection for

head H2 (differential x − y)

2Rx 31 MR-read head connection for head

H2 (differential x − y)

2GND 32 ground connection for head H2

2Ry 33 MR-read head connection for head

H2 (differential x − y)

3Wx 34 inductive write head connection for

head H3 (differential x − y)

3Wy 35 inductive write head connection for

head H3 (differential x − y)

3Rx 36 MR-read head connection for head

H3 (differential x − y)

3GND 37 ground connection for head H3

3Ry 38 MR-read head connection for head

H3 (differential x − y)

4Wx 39 inductive write head connection for

head H4 (differential x − y)

4Wy 40 inductive write head connection for

head H4 (differential x − y)

4Rx 41 MR-read head connection for head

H4 (differential x − y)

4GND 42 ground connection for head H4

4Ry 43 MR-read head connection for head

H4 (differential x − y)

5Wx 44 inductive write head connection for

head H5 (differential x − y)

5Wy 45 inductive write head connection for

head H5 (differential x − y)

5Rx 46 MR-read head connection for head

H5 (differential x − y)

5GND 47 ground connection for head H5

5Ry 48 MR-read head connection for head

H5 (differential x − y)

6Wx 49 inductive write head connection for

head H6 (differential x − y)

6Wy 50 inductive write head connection for

head H6 (differential x − y)

6Rx 51 MR-read head connection for head

H6 (differential x − y)

6GND 52 ground connection for head H6

6Ry 53 MR-read head connection for head

H6 (differential x − y)

7Wx 54 inductive write head connection for

head H7 (differential x − y)

1997 Apr 08 6

Page 7

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

with MR-read/inductive write heads

SYMBOL PAD DESCRIPTION

7Wy 55 inductive write head connection for

head H7 (differential x − y)

7Rx 56 MR-read head connection for head

H7 (differential x − y)

7GND 57 ground connection for head H7

7Ry 58 MR-read head connection for head

H7 (differential x − y)

8Wx 59 inductive write head connection for

head H8 (differential x − y)

8Wy 60 inductive write head connection for

head H8 (differential x − y)

8Rx 61 MR-read head connection for head

H8 (differential x − y)

handbook, full pagewidth

9Wx

9GND

9Rx

9Wy

8Ry

9Ry

TDA5155

SYMBOL PAD DESCRIPTION

8GND 62 ground connection for head H8

8Ry 63 MR-read head connection for head

H8 (differential x − y)

9Wx 64 inductive write head connection for

head H9 (differential x − y)

9Wy 65 inductive write head connection for

head H9 (differential x − y)

9Rx 66 MR-read head connection for head

H9 (differential x − y)

9GND 67 ground connection for head H9

9Ry 68 MR-read head connection for head

H9 (differential x − y)

7Wx

7Wy

7Rx

7GND

7Ry

8Wx

8Wy

8Rx

8GND

V

CC(WD)

GND1

WDIx(v)

WDIy(v)

WDIx(i)

WDIy(i)

SDATA

SCLK

GND2

GND3

GND4

HUS

R/W

SEN

RDx

RDy

V

CC

R

ext

6465666768 54555657585960616263

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19 20 21 22 23 24 25 26 27 28 29 30 31 32 33

TDA5155

6Ry

53

52

6GND

51

6Rx

50

6Wy

49

6Wx

48

5Ry

47

5GND

46

5Rx

45

5Wy

44

5Wx

43

4Ry

42

4GND

41

4Rx

40

4Wy

39

4Wx

38

3Ry

37

3GND

36

3Rx

35

3Wy

34

3Wx

0

0Wx

0Wy

0Rx

0GND

0Ry

1Wx

1Wy

Fig.2 Pad arrangement.

1997 Apr 08 7

1Rx

1GND

1Ry

2Wx

2Wy

2Rx

2GND

2Ry

MGG981

Page 8

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

with MR-read/inductive write heads

8 FUNCTIONAL DESCRIPTION

8.1 Read mode

The read mode disables the write circuitry to save power

while reading. The read circuitry is disactivated for write,

sleep and standby modes. The read circuitry may also be

biased during write mode to shorten transients.

The selected head is connected to a multiplexed low-noise

read amplifier. The read amplifier has low-impedance

inputs nRx and nRy (n is the number of the head) and

low-impedance outputs RDx and RDy. The signal polarity

is non-inverting from x and y inputs to x and y outputs.

Ambient magnetic fields at the MR elements result in a

relative change in MR resistance:

dR

MR

-------------R

MR

This change produces a current variation:

dR

dI

MRIMR

where I

MR

The current variation is amplified to form the read data

output signal voltage, which is available at RDx and RDy.

AC coupling between MR elements and amplifier stages

prevents the amplifier input stages from overloading by DC

voltages across the MR elements. A fast settling

procedure shortens DC settling transients.

MR

×=

-------------R

MR

,

is the bias current in the MR element.

TDA5155

8.2 Write mode

To minimize power dissipation, the read circuitry may be

disabled in write mode. The write circuitry is disabled in

read, sleep and standby modes. In write mode, a

programmable current is forced through the selected

two-terminal inductive write head. The push-pull output

drivers yield near rail-to-rail voltage swings for fast current

polarity switching.

The write data input can be either voltage or current input

(see Chapter 12). In voltage mode, the differential write

data inputs WDIx(v) and WDIy(v) are PECL (Positive

Emitter Coupled Logic) compatible. The write data flip-flop

can either be used or passed-by. In the case that the write

data flip-flop is used, current polarity is toggled at the

falling edges of

V

V

data

WDIx v()VWDIy v()

=

------------------------------------------------------

Switching to write mode initializes the data flip-flop so that

the write current flows in the write head from x to y. In the

case that the write data flip-flop is not used, the signal

polarity is non-inverting from x and y inputs to

x and y outputs.

The write current magnitude is controlled through on-chip

DACs. The write current is defined as follows:

10kΩ

I

-------------- -

WR

R

ext

–

2

20 16d4 8d3 4d2 2d1 d0+++++()=

An on-chip generated stable temperature reference

voltage (1.32 V), available at the R

pin, is dropped

ext

across an external resistor (10 kΩ) to form a global

reference current for the write and the MR bias currents.

The MR bias current DACs are programmed through the

serial interface according to the following formula:

10kΩ

I

MR

0.5

10 16d4 8d3 4d2 2d1 d0+++++()×=

-------------- R

ext

(in mA), where d4-d0 are bits (either logic 0 or logic 1).

At power-up all bits are set to logic 0, which results in a

default MR current of 5 mA. The adjustable range of the

MR currents is 5 mA to 20.5 mA. The MR bias currents are

equal for the two stripes of each head. The gain amplifier

is 1-bit programmable. The amplifier gain can be set to its

nominal value or to the nominal value +3 dB.

(in mA), where d4-d0 are bits (either logic 0 or logic 1).

The adjustable range of the write current is 20 mA to

51 mA. At power-up, the default values

d4 = d3 = d2 = d1 = d0 = logic 0 are initialized,

corresponding to I

= 20 mA. IWR is the current provided

WR

by the write drivers: the current in the write coil and in the

damping resistor together. The static current in the write

coil is

I

WR

,

---------------- R

h

1

+

------ R

d

where R

R

d

is the resistance of the coil including leads and

h

is the damping resistor.

1997 Apr 08 8

Page 9

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

with MR-read/inductive write heads

8.3 Sleep mode

In sleep mode, the device is accessible via the serial

interface. All circuits are inactive, except the circuits of the

CMOS serial interface and the circuitry which forces the

data registers to their default values at power-up and

which fixes the DC level of outputs RDx and RDy (required

when operating with more than one amplifier). Typical

static current consumption is −30 µA. Dynamic current

consumption during operation of the serial interface in

sleep mode due to external activity at the inputs to the

serial interface is not included. In all modes, including the

sleep mode, data registers can be programmed. Sleep is

the default mode at power-up. Switching to other modes

takes less than 0.1 ms.

8.4 Standby mode

The circuit can be put in standby mode using the serial

interface. In standby mode, the typical DC current

consumption is 330 µA. Transients from standby mode to

active mode are two orders of magnitude shorter than from

sleep mode to active mode. This is important in the case

of cylinder mode operation with multiple amplifiers.

All amplifiers can operate from standby mode and all head

switch times can be kept just as short as in the case of

operation with a single amplifier. Head switch times are

summarized in the switching characteristics.

8.5 Active mode

Active mode is either read mode or write mode depending

on the status of the R/

W pin.

TDA5155

Three phases in the communication are distinguishable:

addressing, programming and reading. Each

communication sequence starts with an addressing

phase, followed by either a programming phase or a

reading phase.

8.6.1 A

When SEN goes HIGH, bits are latched in at rising edges

of SCLK. The first eight bits a7 to a0 (starting with a0) are

shifted serially into an address register. If SEN goes LOW

before 16 bits have been received, the operation is

ignored. When more than 16 bits (address and data) are

latched in before SEN goes LOW, the first 8 bits are

interpreted as an address and the last 8 bits as data. SEN

should go HIGH at least 5 ns before the first rising edge of

SCLK. Data should be valid at least 5 ns before and after

a rising edge of SCLK. The first six bits a5 to a0 constitute

the register address. Bit a6 is unused. If bit a7 = logic 0,

a PROGRAMMING sequence starts. If bit a7 = logic 1,

READING data from the pre-amplifier can start.

8.6.2 P

If a7 = 0, the last eight bits d7 to d0 before SEN goes LOW

are shifted into an input register. When SEN goes LOW,

the communication sequence is ended and the data in the

input register is copied in parallel to the data register that

corresponds to the decoded address a0 to a5. SEN

should go LOW at least 5 ns after the last rising edge of

SCLK. See Fig.3 for the timing diagram of the

programming.

DDRESSING

ROGRAMMING DATA

8.6 Bi-directional serial interface

The serial interface is used for programming the device

and for reading of status information. 16 bits (8 bits for

data and 8 for address) are used to program the device.

The serial interface requires 3 pins: SDATA, SCLK and

SEN. These pins (and R/

The logic input R/W has an internal 20 kΩ pull-up resistor

and the SEN logic input has an internal 20 kΩ pull-down

resistor. Thus, in case the SEN line is opened, no data will

be registered and in case the R/W line is opened, the

device will never be in write mode.

SDATA: serial data; bi-directional data interface. In all

circumstances, the LSB is transmitted first.

SCLK: serial clock; 25 MHz clock frequency.

SEN: serial enable; data transfer takes place when SEN is

HIGH. When SEN is LOW, data and clock signals are

prohibited from entering the circuit.

1997 Apr 08 9

W as well) are CMOS inputs.

8.6.3 R

Immediately after the IC detects that a7 = logic 1, data

from the data register (address a5 to a0) is copied in

parallel to the input register. Two wait clock cycles must

follow before the controller can start inputting data. At the

first falling edge of SCLK after the 2 wait rising edges of

SCLK, the LSB d0 is placed on SDATA line followed by d1

at the next falling edge of SCLK etc. If SEN goes LOW

before 8 address bits (a7 to a0) have been detected, the

communication is ignored. If SEN goes LOW before the

8 data bits have been sent out of the IC, the reading

sequence is immediately interrupted. See Fig.4 for the

timing diagram of the reading via the serial interface.

EADING DATA

Page 10

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

with MR-read/inductive write heads

handbook, full pagewidth

SEN

SCLK

SDATA

a0 d0a1 d1a2 d2a3 d3a4 d4a5 d5a6 d60d7

address data

TDA5155

MGG983

Fig.3 Timing diagram of the write sequence of the serial interface operation (a7 = logic 0).

handbook, full pagewidth

SEN

SCLK

SDATA

a0 d0a1 d1a2 d2a3 d3a4 d4a5 d5a6 d61d7

address data

wait

cycles

MGG984

Fig.4 Timing diagram of the read sequence of the serial interface operation a7 = logic 1).

1997 Apr 08 10

Page 11

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

with MR-read/inductive write heads

8.7 Operation of the serial interface

The serial interface programming is summarized in

Section 8.7.10.

8.7.1 C

d0:

By default (d0 = logic 0), write data passes from the

write data input via the data flip-flop to the write driver.

The write driver toggles the current in the head at the

falling edges of:

V

I

data

When d0 = logic 1, the write data flip-flop is not used.

The signal polarity is non-inverting from the inputs WDIx

and WDIy to the outputs nWx and nWy.

d1:

By default (d1 = logic 0), the pre-amplifier senses PECL

write signals at WDIx(v) and WDIy(v). When

d1 = logic 1, the pre-amplifier senses input write

currents at WDIx(i) and WDIy(i).

d2:

By default (d2 = logic 0), the write current is inhibited

under low supply voltage conditions. The write current

inhibit is made inactive by programming d2 to logic 1.

d3:

By default (d3 = logic 0), in write mode low supply

voltage, open head, and other conditions are monitored

and flagged at HUS. If d3 = logic 1, HUS is LOW in write

mode and HIGH in read mode.

d4:

The amplifier read gain may be programmed in the

configuration register. By default (d4 = logic 0), the read

gain is typically 160 with R

read amplifier gain is 3 dB higher (226 in this case).

d5:

In order to minimize the write-to-read recovery times,

the first stage of the read amplifier may be kept biased

during write mode. By default, (d5 = logic 0) the read

amplifier is powered down during write mode, and the

fast settling procedure is activated after write-to-read

switching. If d5 = logic 1 the read amplifier is kept biased

during write mode, and the fast settling procedure still

occurs if the head is changed or the MR current is

re-programmed.

ONFIGURATION

V

WDIx v()VWDIy v()

=

data

------------------------------------------------------

I

WDIx i()IWDIy i()

=

---------------------------------------------2

–

–

2

or

=28Ω. If d4 = logic 1, the

MR

TDA5155

8.7.2 P

By default, d1 = d0 = logic 0, the pre-amplifier powers up

in sleep mode. If d1 = logic 0, d0 = logic 1 or d1 = logic 1,

d0 = logic 0 the circuit goes in standby mode.

If d1 = d0 = logic 1, the circuit goes in active mode (read or

write mode depending on the R/W input).

8.7.3 H

Selection of a wrong head (H10-H15) causes an head

unsafe condition. HUS goes HIGH when in write mode a

wrong head is selected and when d3 in the configuration

register is LOW. When in read mode and a wrong head is

selected, head H0 is therefore selected and if d3 in the

configuration register is LOW, HUS goes LOW.

8.7.4 S

The circuit is prepared for servo writing. However, the

device will not be guaranteed.

8.7.5 T

d2 = d1 = d0 = logic 0. The circuit is not in test mode. This

is the default situation.

8.7.5.1 MR head test

d2 = logic 0, d1 = logic 0, d0 = logic 1. In read mode, the

voltages at Rx and Ry (at the top of the MR elements) of

the selected head are fed to outputs RDx and RDy.

By measuring the output voltages single ended at two

different IMR currents, the MR resistance can be accurately

measured according to the following formula:

R

MRx

Open head and head short-circuited-to-ground conditions

can therefore be detected.

d2 = logic 0, d1 = logic 1, d0 = logic 0. Same as before,

with the difference that I

value of 5 mA. Measuring in the same way as above with

I

MR1

shorted together.

8.7.5.2 Temperature monitor

d2 = logic 0, d1 = logic 1, d0 = logic 1. The temperature

monitor voltages are connected to RDx and RDy.

The output differential voltage depends on the

temperature according to: dV = −0.00364 × T + 1.7;

0 < T < 140 °C. The temperature may be measured with a

typical precision of 5 °C.

OWER CONTROL

EAD SELECT

ERVO WRITE

EST

V

–

RDx1VRDx2

=

-------------------------------------- -

–

I

MRx1IMRx2

for the x-side.

is fixed to a minimum constant

MR2

> 5 mA, enables the detection of MR elements

1997 Apr 08 11

Page 12

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

with MR-read/inductive write heads

8.7.5.3 Thermal asperity detector

d2 = logic 1, d1 = x, d0 = (0,1). Unlike the above tests, the

thermal asperity detection does not use the RDx and RDy

outputs. Thus, the reader is fully operational. In case a

thermal asperity is detected, it is flagged at the HUS pin.

The threshold voltage for the thermal asperity detection is

2-bit programmable. These 2 bits consist of d0 (LSB) of

the test mode register (address = 0xxx0110), and d2 of the

compensation capacitor register (address = 0xxx0111).

V

d0 of test mode register;

d2 of the compensation capacitor register.

8.7.6 W

By default (d2 = d1 = d0 = logic 0) the programmable

capacitors are zero. These capacitors are used to improve

the performance of the write amplifier according to the

write amplifier output load.

8.7.7 H

210 560.d0 280.d2++()µV=

th

RITE AMPLIFIER PROGRAMMABLE CAPACITORS

IGH FREQUENCY GAIN ATTENUATOR REGISTER

TDA5155

frequency noise. The HF pole can be used in combination

with the HF zero in order to boost the HF gain locally and

yet limit the very high frequency noise enhancement.

8.7.8 HIGH FREQUENCY GAIN BOOST REGISTER

By default (d3 = d2 = d1 = d0 = logic 0) the high frequency

gain boost is not active.

The gain boost provides a zero which allows to optimize

the bandwidth of the read amplifier and to correct for

attenuation caused by series inductances in the leads

between the MR heads and the read amplifier inputs.

8.7.9 S

By default (d2 = d1 = d0 = logic 0) the settle pulse has a

nominal duration of 3 µs. Its value can be programmed

from 2.125 µs to 3 µs according to the following formula:

t

st

The settle pulse is used to shorten the transients during

switching.

ETTLE PULSE

2µs

------------------------------------------------------------------ -

4.d2 2.d1 1.d0 1+++()

1

µ s+=

By default (d3 = d2 = d1 = d0 = logic 0) the high frequency

gain attenuator is not active. The gain attenuator provides

a pole which limits the bandwidth and reduces the high

8.7.10 A

DDRESS REGISTERS SUMMARY

ADDRESS REGISTERS

(1)

A7 A6 A5 A4 A3 A2 A1 A0

0XXX0000configuration register:

d0 = 0: use data flip-flop; d0 = 1: by-pass data flip-flop

d1 = 0: WDI PECL; d1 = 1: current input

d2 = 0: write current inhibit active; d2 = 1: write current inhibit inactive

read mode: d3 = 0: HUS active; d3 = 1: HUS HIGH

write mode: d3 = 0: HUS active; d3 = 1: HUS LOW

d4 = 0: read gain nominal; d3 = 1: read gain +3 dB

d5 = 0: read amplifier OFF during write mode; d5 = 1: read amplifier ON

during write mode

0XXX0001power control register:

(d1,d0) = (0,0): sleep mode

(d1,d0) = (1,0) or (0,1): standby mode

(d1,d0) = (1,1): active mode (write or read)

0XXX0010head select register:

(d3,d2,d1,d0) = (0,0,0,0) to (1,0,0,1): H0 to H9

addressing H10 to H15 causes HUS to go HIGH if in write mode and H0 to be

selected if in read mode

FUNCTION

1997 Apr 08 12

Page 13

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

TDA5155

with MR-read/inductive write heads

ADDRESS REGISTERS

A7 A6 A5 A4 A3 A2 A1 A0

0XXX0011

0XXX0100

0XXX0101servo write register:

0XXX0110test mode register:

0XXX0111compensation capacitor register:

0XXX1000

0XXX1001

0XXX1010

1XXX1111device ID register

1XXXa3a2a1a0when a7 = 1, data from the register with address a3 to a0 is read out on

(1)

FUNCTION

MR current DAC register:

I

MR

0.5

10kΩ

10 16.d4 8.d3 4.d2 2.d1 d0+ ++++()×=

-------------- R

ext

mA

write current DAC register:

WR

10kΩ

-------------- -

I

20 16.d4 8.d3 4.d2 2.d1 d0+ ++++()=

R

ext

mA

(d0,d1) = (0,0): one head

(d0,d1) = (1,1): all heads

(d0,d1) = (1,0): odd numbered heads (H1, H3, H5, H7 and H9)

(d0,d1) = (0,1): even numbered heads (H0, H2, H4, H6 and H8)

(d2,d1,d0) = (0,0,0) = not in test mode

(d2,d1,d0) = (0,0,1) = read head test (I

(d2,d1,d0) = (0,1,0) = read head test (I

MR1=IMR2

MR2

)

= 5 mA fixed)

(d2,d1,d0) = (0,1,1) = temperature monitor

(d2,d1,d0) = (1,X,d0) = thermal asperity detection, see note 2

= (210 + 560.d0 + 280.d2) µV

V

th

equivalent differential capacitance = (4.d2 + 2.d1 + 1.d0) × 2pF

high frequency gain attenuator register

nominal pole frequency =

---------------------------------------------------------------------

8.d3 4.d2 2.d1 1.d0+++

800 MHz

high frequency gain boost register

nominal zero frequency =

---------------------------------------------------------------------

8.d3 4.d2 2.d1 1.d0+++

800 MHz

settle time register

settle time:

2µs

t

st

------------------------------------------------------------------ -

4.d2 2.d1 1.d0 1+++()

1

µ s+=

ID = 8.d3 + 4.d2 + 2.d1 + 1.d0; d3 to d0 are preset to (0,0,1,1)

SDATA

Notes

1. Unused bits in the registers (indicated byX) are don’t care. Default data, initialized at Power-up, is zero in all

registers. For VCC<2.5 V, the register contents are not guaranteed.

2. Vth programming uses both the test mode register and the compensation capacitor register. d0 in the formula above

is the LSB of the test mode register and d2 is the d2 data bit of the compensation capacitor register.

1997 Apr 08 13

Page 14

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

with MR-read/inductive write heads

8.8 Head unsafe

The HUS pin is an open collector output. Therefore when

the pin is not connected to an external pull-up resistor,

HUS is LOW. HUS pins can be connected together in case

of operation with more than one amplifier. It is used to

detect abnormal or unexpected operation.

Sleep mode: HUS is HIGH, to permit working with more

than one amplifier.

Standby mode: HUS is HIGH, to permit working with

more than one amplifier.

Read mode:

• If in the configuration register d3 = 1, HUS is HIGH

• If in the configuration register d3 = 0, HUS goes LOW

for:

– Selection of a wrong head (H10 to H15)

–R

pin open, short-circuited to ground or to V

ext

(read current too low or too high)

– Low VCC and V

conditions. A low supply

CC(WD)

voltage detector is placed close to the VCC and

V

CC(WD)

pins.

Detection of low VCC (main supply): a VCC supply voltage

below 4.0 V ±5% is flagged at the HUS pin. The voltage

detection range is then 4.2 to 3.8 V with an hysteresis of

110 mV ±10%. Detection of low V

CC(WD)

supply): a fault will be flagged at the HUS pin if V

drops 0.8 V ±10% below VCC. One must be aware that

such a detection is only aimed to warn for a catastrophic

situation. Indeed, V

should never be below VCC.

CC(WD)

(1)

CC

(write drivers

CC(WD)

TDA5155

Test mode: HUS is HIGH except when the TAS detector

is ON. If a thermal asperity is detected, HUS goes LOW.

Servo write mode: HUS is LOW.

Write mode:

• If in the configuration register d3 = 1, HUS is LOW

• If in the configuration register d3 = 0, HUS goes HIGH

for:

– Selection of a wrong head (H10 to H15)

–R

pin open, short-circuited to ground or to V

ext

(write current too low or too high)

– Write Data Input frequency too low (WDIx-WDIy)

– Write head Wx, Wy open, Wx or Wy short-circuited to

(2)

ground

– Write driver still left biased while not selected

– Low VCC and V

conditions (write current inhibit

CC(WD)

can be active or inactive).

The same detector is used for read and write mode.

The write current may be inhibited if d2 = 0 in the

configuration register.

The HUS line indicates an unsafe condition as long as the

fault is present, in read mode as well as in write mode.

It indicates again a safe condition only 0.5 µs to 1 µs after

the last fault has disappeared.

(1) Head numbers 0 to9 are correct, 10 to 15 are signalled as

unsafe.

(2) Switching to write mode makes HUS LOW. After the transient

the HUS detection circuitry is activated. The target for the

head open detection time is 15 ns.

(1)

CC

8.9 HUS survey HUS DATA BIT D3

MODE STATE 0 1

Sleep mode −−HIGH HIGH

Standby mode −−HIGH HIGH

Active mode Read Read mode ACTIVE HIGH

A-test mode

Write Write mode ACTIVE LOW

A-test mode

Servo mode

Notes

1. A-test mode = analog test mode.

2. In servo mode, the performance of the IC is not guaranteed.

1997 Apr 08 14

(1)

HIGH HIGH

TAS mode ACTIVE ACTIVE

(1)

(2)

HIGH HIGH

LOW LOW

Page 15

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

TDA5155

with MR-read/inductive write heads

9 LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

SYMBOL PARAMETER MIN. MAX. UNIT

V

CC

V

CC(WD)

V

n1

V

n2

V

n3

I

nGND

T

stg

T

j

10 HANDLING

supply voltage −0.5 +6.0 V

write driver supply voltage −0.5 +9.5 V

voltage on all pins except V

, read inputs nRx, nRy

CC(WD)

−0.5 +5.5 V

and write driver outputs nWx, nWy (n = 0 to 9)

absolute maximum value − V

+ 0.5 V

CC

voltage on write driver outputs nWx, nWy −0.5 +8.8 V

absolute maximum value − V

CC(WD)

+ 0.5 V

voltage on read inputs nRx, nRy −0.5 +1 V

ground current (pins nGND) − 0.1 A

storage temperature −65 +150 °C

junction temperature − 150 °C

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is

desirable to take normal precautions appropriate to handling integrated circuits.

11 THERMAL CHARACTERISTICS

The thermal resistance depends on the flex used. The TDA5155X is shipped in naked dies form.

1997 Apr 08 15

Page 16

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

TDA5155

with MR-read/inductive write heads

12 RECOMMENDED OPERATION CONDITIONS

SYMBOL PARAMETER CONDITIONS MIN. TYP MAX. UNIT

V

CC

V

CC(WD)

V

IH

V

IL

V

i(dif)(p-p)

supply voltage note 1 4.5

write driver supply voltage note 2 V

HIGH level input voltage (CMOS) 3.5

LOW level input voltage (CMOS) 0

differential input voltage

(peak-to-peak value)

V

IH(PECL)

V

IL(PECL)

I

i(dif)(p-p)

HIGH level PECL input voltage note 3

LOW level PECL input voltage note 3 1.5 2.15

differential input current

(peak-to-peak value)

I

IH(dif)

I

IL(dif)

T

amb

T

j

R

MR

)RMR mismatch note 5

∆(R

MR

L

l(tot)

R

l(tot)

V

MR

V

sig(dif)(p-p)

HIGH level differential input current note 4 −1.4 −1.2

LOW level differential input current note 4

ambient temperature 0

junction temperature reading

MR element resistance 15 28 34 Ω

total lead inductance to the head in each lead; note 6 − 25

total lead resistance to the head in each lead; note 6 − 1.5

voltage on top of MR elements note 7

differential MR head input voltage

(peak-to-peak value)

L

wh

R

wh

C

wh

R

ext

write head inductance including lead; note 6

write head resistance including lead; note 6 − 10

write head capacitance including lead; note 6 − tbf

external reference resistor − 10 − kΩ

−

CC

−

−

−

note 3 0.4 0.7 1.5 V

−

2.85 V

note 4 0.4 0.8 1.0 mA

−

−0.4 −0.1 mA

−

−−

writing (V

CC(WD)

=8V)

−−

−−

−−

0.4 1 2 mV

−

V

I

ref

ref

=

---------- R

ext

0.15

5.5 V

8.8 V

V

CC

V

0.8 V

CC

−

−

V

V

mA

70 °C

110 °C

130 °C

4Ω

−

−

nH

Ω

0.5 V

−

−

−

µH

Ω

pF

1997 Apr 08 16

Page 17

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

with MR-read/inductive write heads

Notes to the recommended operating conditions

1. A supply by-pass capacitor from VCC to ground or a

low pass filter may be used to optimize the PSRR.

2. The supply voltage V

in normal mode, and two diode 1.4 V above VCC in

servo mode.

3. The given values should be interpreted in the way that

the single ended voltage could swing from

0.2 to 0.75 V, and that the common mode voltage

should be such that for any of the two states, the

V

IH(PECL)

is less than VCC and V

1.5 V.

PECL voltage swing: a wider peak-to-peak voltage

swing can be used. In that case a current will flow

through the WDI inputs. This current is approximately

equal to

WDIx v() WDIy v()– 1.4–

-------------------------------------------------------------------------

must never be below V

CC(WD)

IL(PECL)

200

CC

is more than

TDA5155

4. Same comments for the given values as for the

voltage input mode. The HIGH (respectively LOW)

level input current is defined such that it produces the

same effect at the output of the writer (Wx, Wy) as the

HIGH (resp. LOW) level input voltage.

5. The mismatch refers to the resistance of the two

stripes of the same head. This is defined as follows:

∆(R

) = abs(R

MR

6. These parameters depend on the head model.

The data given in the table are those used for testing.

7. The combination of maximum head resistance, lead

resistance and bias current is not permitted. To avoid

voltage breakthrough between heads and disk, the

voltage over the MR elements is limited by two diode

voltages.

MR1

− R

MR2

).

1997 Apr 08 17

Page 18

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

TDA5155

with MR-read/inductive write heads

13 CHARACTERISTICS

V

= 5.0 V; V

CC

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Read characteristics

I

MR

∆I

MR

G

v(dif)

R

i(dif)

C

i(dif)

THD total harmonic distortion − 1 − %

B

L

B

H

F noise figure R

V

irn

B

F(L)

B

F(H)

α

cs

PSRR power supply rejection ratio;

CMRR common mode rejection

=8V; V

CC(WD)

MR current adjust range R

tolerance (excluding R

differential voltage gain;

note 1

GND

=0V; T

ext

=25°C; unless otherwise specified.

amb

=10kΩ; 0.5 mA steps 5 − 20.5 mA

ext

)IMR programmed at 10 mA −±4−%

from head inputs to RDx, RDy;

RMR=28Ω; IMR=10mA;

f = 20 MHz

d4 = 0 − 160 −

d4 = 1 − 226 −

differential input resistance IMR=10mA − 13 −Ω

differential input

− 16 − pF

capacitance

lower signal gain pass-band

−3dB −− 100 kHz

edge

higher signal gain

pass-band edge

−3 dB; note 2

without gain boost

− 220 − MHz

(4 nH lead inductance)

with gain boost

− 170 − MHz

(50 nH lead inductance)

input referred noise voltage;

note 3

lower noise band edge

(+3 dB)

=28Ω; IMR= 10 mA;

MR

T

=25°C; f = 20 MHz

amb

RMR=28Ω; IMR= 10 mA;

T

=25°C; f = 20 MHz

amb

RMR=28Ω; IMR= 10 mA;

T

=25°C;

amb

− 3.0 3.2 dB

− 0.9 1.0 nV/√Hz

−−400 kHz

no lead inductance

upper noise band edge

(+3 dB)

RMR=28Ω; IMR= 10 mA;

=25°C;

T

amb

− 220 − MHz

no lead inductance

channel separation; note 4 unselected head − 50 − dB

=10mA − 80 − dB

MR

=10mA − 50 − dB

MR

MR

note 5

ratio; note 5

f < 1 MHz; I

f < 100 MHz; I

from nRx-nRy to RDx-RDy R

mismatch < 5%

IMR=10mA

f < 1 MHz − 45 − dB

f < 100 MHz − 25 − dB

1997 Apr 08 18

Page 19

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

TDA5155

with MR-read/inductive write heads

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

DR rejection ratio of SCLK and

SDATA; note 6

V

O(R)(dif)

output DC offset voltage in

read mode (differential

after DC settling)

Z

o(R)

output impedance in read

mode

I

o(max)(dif)

maximum differential

output current

V

o(cm)

common mode output

voltage in read mode

V∆

ocm()

--------------------- V

∆

CC

Z

o(n)(dif)

common mode DC supply

rejection ratio in read mode

differential output

impedance in other modes

(write, standby, sleep)

from SCLK, SDA T A inputs to the

− 50 − dB

RDx-RDy outputs; a 200 mV

(peak-to-peak) signal is applied

to SCLK or SDATA inputs at

25 MHz, and measurement is

performed at RDx-RDy

DC voltage between RDx and

−−±0.2 V

RDy

single ended − 16 −Ω

− 4 − mA

RDx, RDy 1.0 1.5 2.0 V

− 20 − dB

− 50 − kΩ

Write characteristics

I

WR

write current adjust range

(in the write drivers)

∆I

WR

V

s(max)(p-p)

tolerance (excluding R

maximum voltage swing

(peak-to-peak value)

R

o(dif)

differential output

resistance

C

o(dif)

differential output

capacitance

t

r,tf

write current rise/fall time

without flip-flop

(10% to 90%); note 7

t

as

write current rise/fall time

asymmetry; note 8

t

pd

propagation delay 50% of

(WDIx/WDIy) to 50% of

(Wx, Wy)

α

cs

channel separation not-selected head − 45 − dB

R

=10kΩ; 1 mA steps 20 35 51 mA

ext

)IWR programmed at 35 mA −±7−%

ext

V

V

=5V −−8V

CC(WD)

= 8 V (differential) −−13 V

CC(WD)

− 200 −Ω

not including the head

− 5 − pF

capacitance

Lh= 150 nH; Rh=10Ω;

IWR= 35 mA; f = 20 MHz

V

CC(WD)

V

CC(WD)

percentage of tr or tf (tr or tf and

= 8.0 V −−1.8 ns

= 6.5 V −−2.1 ns

−−5%

logic asymmetry)

write head short-circuited, data

−−5ns

flip-flop by-passed

1997 Apr 08 19

Page 20

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

TDA5155

with MR-read/inductive write heads

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Switching characteristics

f

SCLK

∆V

o(cm)

t

rec(W-R)

t

sw(R)

t

off(R)

t

st(W)

t

off(W)

t

sw(W)

t

sw(S)

serial interface clock rate −−25 MHz

common mode DC output

IMR= 10 mA; IWR=35mA − 200 − mV

voltage change from read to

write mode

write-to-read recovery time

(AC and DC settling);

note 9

from 50% of the rising edge of

R/W to steady state read-back

signal: AC and DC settling at

90% (without load at RDx, RDy)

read amplifier OFF: d5 = 0 − 3 4.5 µs

read amplifier ON: d5 = 1 − 100 150 ns

head switching (in read

mode), standby to read

active and MR current

from falling edge of SEN to

steady state read-back signal

(without load at RDx, RDy)

− 3 4.5 µs

change recovery time.

(AC and DC settling);

note 10

read amplifier off time from falling edge of R/W to read

−−50 ns

head inactive

write settling times; note 11 from 50% of the falling edge of

−−70 ns

R/W to 90% of the steady state

write current (in write mode)

write amplifier off time from rising edge of R/W to

1

⁄10× IWR (programmed)

−−50 ns

(IWR=35mA)

head switching (in write

mode), and standby to write

from falling edge of SEN to write

head active

− 50 70 ns

head active

switch time to and from

−−100 µs

sleep mode

DC characteristics

I

CC(R)

I

CC(W)

I

DD(STB)

read mode supply current IMR= 10 mA; note 12 − 72 80 mA

write mode supply current IWR= 35 mA; note 13

from V

from V

(5 V) − 33 41 mA

CC

CC(WD)

standby mode supply

current

I

DD(S)

V

ref

sleep mode supply current static −−0.02 − mA

reference voltage for R

ext

1997 Apr 08 20

(5 to 8 V) − 54 61 mA

− 0.25 1 mA

− 1.32 − V

Page 21

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

with MR-read/inductive write heads

Notes to the characteristics

1. The differential voltage gain depends on the MR

resistance. It can be improved by programming the

d4 bit in the configuration register.

2. The gain boost implements a pole-zero combination:

The +3 dB gain boost corner frequency is

---------------------------------------------------------------------

8.d3 4.d2 2.d1 1.d0+++

attenuation corner frequency is

---------------------------------------------------------------------

8.d3 4.d2 2.d1 1.d0+++

are to be programmed via the serial interface. In

practical use, the bandwidth is limited by the

inductance of the connection between the MR heads

and the pre-amplifier.

3. Noise calculation

a) Definitions: The amplifier has a low input

b) Noise figure versus I

c) Input referred noise voltage: The input referred

4. The channel separation is defined by the ratio of the

gain response of the amplifier using the selected head

H(n) to the gain response of the amplifier using the

adjacent head H(n ±1), head H(n) being selected.

800 MHz

. The −3 dB gain

800 MHz

, where d3, d2, d1 and d0

resistance. No lead resistance is taken into

account. The input referred noise voltage,

excluding the noise of the MR resistors, is defined

2

V

()

as: ,

irn

where G

is the voltage gain, Vno is the noise

v

--------G

no

v

4kT R

+()×–=

MR1RMR2

2

V

voltage at the output of the amplifier, k is the

Boltzmann constant and T is the temperature in K.

The noise figure is defined as follows:

2

V

no

--------G

v

+()×

MR1RMR2

in 1 Hz

F10

log×=

------------------------------------------------------------

4kT R

bandwidth. Note that R

includes all resistances

MR

between Rx or Ry to ground.

and RMR: Table 1 shows

MR

the variation of the noise figure with IMR and RMR.

noise voltage calculation can be significantly

different (from 1.0 to 0.44 nV/√Hz for instance) by

taking an equivalent signal-to-noise ratio into

account when using two MR stripes (28 Ω for each

stripe) or one MR stripe (42 Ω). It assumes that the

signal coming from the head is larger for a

dual-stripe head than for a single-stripe head (50%

extra signal for a dual-stripe head).

TDA5155

5. The PSRR (in dB) is defined as input referred ratio:

G

v

PSRR 20 log

×=

, where G

------ G

p

to differential output gain, and Gp is the power supply

to differential output gain.The CMRR (in dB) is defined

as input referred ratio: , where

is the differential input to differential output gain and

G

v

G

is the common mode input to differential output

cm

CMRR 20 log

gain. Flex and board lay-out may affect these

parameters significantly.

6. This refers to the crosstalk from SCLK and SDATA

inputs via the read inputs to RDx and RDy. Two cases

can be distinguished:

a) When SEN is LOW, SCLK and SDATA are

prohibited reaching the device and crosstalk is low.

b) Programming via the serial interface is done with

SEN HIGH. Then crosstalk can occur. A careful

design of the board or flex-foil is required to avoid

crosstalk via this path.

7. The rise and fall times depend on the

write amplifier/write head combination. L

represent the components on the evaluation board.

Parasitic capacitances also limit the performance.

8. The write current rise/fall time asymmetry is defined by

–

t

rtf

-----------------------

+()

2t

rtf

9. Write-to-read recovery time includes the write mode to

read mode switching using the R/

head (see Fig.5). The AC signal reaches its full

amplitude few tens of ns after appearing at the reader

RDx and RDy outputs.

10. In read mode, the head switching, standby to read

active switching and changing MR current include fast

current settling (see Fig.5). The AC signal reaches its

full amplitude few tenth of ns after appearing at the

reader RDx and RDy outputs.

11. Write settling time includes the read mode to write

mode switching using the R/W pin.

12. The typical supply current in read mode depends on

the bias current for the MR element.

13. The typical supply current in write mode also depends

on the write current.

is the differential input

v

G

×=

v

---------- G

cm

and R

h

h

W pin on the same

1997 Apr 08 21

Page 22

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

with MR-read/inductive write heads

Table 1 Noise figure

RMR(Ω)

IMR= 7 mA IMR=10mA IMR=15mA

20 2.7 2.9 3.1

25 2.8 3.0 3.3

30 2.9 3.1 3.5

handbook, full pagewidth

R/W

RDx-RDy

TDA5155

F (dB)

handbook, full pagewidth

t

rec(W-R)

t

off(R)

MGG985

Fig.5 Timing diagram of the reader: write-to-read switching on the same logic head.

SEN

RDx-RDy

t

sw(R)

MGG986

Fig.6 Timing diagram of the reader: typical head, current and standby-to-read characteristics.

1997 Apr 08 22

Page 23

Philips Semiconductors Preliminary specification

Pre-amplifier for Hard Disk Drive (HDD)

TDA5155

with MR-read/inductive write heads

14 DEFINITIONS

Data sheet status

Objective specification This data sheet contains target or goal specifications for product development.

Preliminary specification This data sheet contains preliminary data; supplementary data may be published later.

Product specification This data sheet contains final product specifications.

Limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or

more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation

of the device at these or at any other conditions above those given in the Characteristics sections of the specification

is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information

Where application information is given, it is advisory and does not form part of the specification.

15 LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these

products can reasonably be expected to result in personal injury. Philips customers using or selling these products for

use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such

improper use or sale.

1997 Apr 08 23

Page 24

Philips Semiconductors – a worldwide company

Argentina: see South America

Australia: 34 Waterloo Road, NORTH RYDE, NSW 2113,

Tel. +61 2 9805 4455, Fax. +61 2 9805 4466

Austria: Computerstr. 6, A-1101 WIEN, P.O. Box 213,

Tel. +43 1 60 101, Fax. +43 1 60 101 1210

Belarus: Hotel Minsk Business Center, Bld. 3, r. 1211, Volodarski Str. 6,

220050 MINSK, Tel. +375 172 200 733, Fax. +375 172 200 773

Belgium: see The Netherlands

Brazil: see South America

Bulgaria: Philips Bulgaria Ltd., Energoproject, 15th floor,

51 James Bourchier Blvd., 1407 SOFIA,

Tel. +359 2 689 211, Fax. +359 2 689 102

Canada: PHILIPS SEMICONDUCTORS/COMPONENTS,

Tel. +1 800 234 7381

China/Hong Kong: 501 Hong Kong Industrial Technology Centre,

72 Tat Chee Avenue, Kowloon Tong, HONG KONG,

Tel. +852 2319 7888, Fax. +852 2319 7700

Colombia: see South America

Czech Republic: see Austria

Denmark: Prags Boulevard 80, PB 1919, DK-2300 COPENHAGEN S,

Tel. +45 32 88 2636, Fax. +45 31 57 0044

Finland: Sinikalliontie 3, FIN-02630 ESPOO,

Tel. +358 9 615800, Fax. +358 9 61580920

France: 4 Rue du Port-aux-Vins, BP317, 92156 SURESNES Cedex,

Tel. +33 1 40 99 6161, Fax. +33 1 40 99 6427

Germany: Hammerbrookstraße 69, D-20097 HAMBURG,

Tel. +49 40 23 53 60, Fax. +49 40 23 536 300

Greece: No. 15, 25th March Street, GR 17778 TAVROS/ATHENS,

Tel. +30 1 4894 339/239, Fax. +30 1 4814 240

Hungary: see Austria

India: Philips INDIA Ltd, Shivsagar Estate, A Block, Dr. Annie Besant Rd.

Worli, MUMBAI 400 018, Tel. +91 22 4938 541, Fax. +91 22 4938 722

Indonesia: see Singapore

Ireland: Newstead, Clonskeagh, DUBLIN 14,

Tel. +353 1 7640 000, Fax. +353 1 7640 200

Israel: RAPAC Electronics, 7 Kehilat Saloniki St, PO Box 18053,

TEL AVIV 61180, Tel. +972 3 645 0444, Fax. +972 3 649 1007

Italy: PHILIPS SEMICONDUCTORS, Piazza IV Novembre 3,

20124 MILANO, Tel. +39 2 6752 2531, Fax. +39 2 6752 2557

Japan: Philips Bldg 13-37, Kohnan 2-chome, Minato-ku, TOKYO 108,

Tel. +81 3 3740 5130, Fax. +81 3 3740 5077

Korea: Philips House, 260-199 Itaewon-dong, Yongsan-ku, SEOUL,

Tel. +82 2 709 1412, Fax. +82 2 709 1415

Malaysia: No. 76 Jalan Universiti, 46200 PETALING JAYA, SELANGOR,

Tel. +60 3 750 5214, Fax. +60 3 757 4880

Mexico: 5900 Gateway East, Suite 200, EL PASO, TEXAS 79905,

Tel. +9-5 800 234 7381

Middle East: see Italy

Netherlands: Postbus 90050, 5600 PB EINDHOVEN, Bldg. VB,

Tel. +31 40 27 82785, Fax. +31 40 27 88399

New Zealand: 2 Wagener Place, C.P.O. Box 1041, AUCKLAND,

Tel. +64 9 849 4160, Fax. +64 9 849 7811

Norway: Box 1, Manglerud 0612, OSLO,

Tel. +47 22 74 8000, Fax. +47 22 74 8341

Philippines: Philips Semiconductors Philippines Inc.,

106 Valero St. Salcedo Village, P.O. Box 2108 MCC, MAKATI,

Metro MANILA, Tel. +63 2 816 6380, Fax. +63 2 817 3474

Poland: Ul. Lukiska 10, PL 04-123 WARSZAWA,

Tel. +48 22 612 2831, Fax. +48 22 612 2327

Portugal: see Spain

Romania: see Italy

Russia: Philips Russia, Ul. Usatcheva 35A, 119048 MOSCOW,

Tel. +7 095 755 6918, Fax. +7 095 755 6919

Singapore: Lorong 1, Toa Payoh, SINGAPORE 1231,

Tel. +65 350 2538, Fax. +65 251 6500

Slovakia: see Austria

Slovenia: see Italy

South Africa: S.A. PHILIPS Pty Ltd., 195-215 Main Road Martindale,

2092 JOHANNESBURG, P.O. Box 7430 Johannesburg 2000,

Tel. +27 11 470 5911, Fax. +27 11 470 5494

South America: Rua do Rocio 220, 5th floor, Suite 51,

04552-903 São Paulo, SÃO PAULO - SP, Brazil,

Tel. +55 11 821 2333, Fax. +55 11 829 1849

Spain: Balmes 22, 08007 BARCELONA,

Tel. +34 3 301 6312, Fax. +34 3 301 4107

Sweden: Kottbygatan 7, Akalla, S-16485 STOCKHOLM,

Tel. +46 8 632 2000, Fax. +46 8 632 2745

Switzerland: Allmendstrasse 140, CH-8027 ZÜRICH,

Tel. +41 1 488 2686, Fax. +41 1 481 7730

Taiwan: Philips Semiconductors, 6F, No. 96, Chien Kuo N. Rd., Sec. 1,

TAIPEI, Taiwan Tel. +886 2 2134 2865, Fax. +886 2 2134 2874

Thailand: PHILIPS ELECTRONICS (THAILAND) Ltd.,

209/2 Sanpavuth-Bangna Road Prakanong, BANGKOK 10260,

Tel. +66 2 745 4090, Fax. +66 2 398 0793

Turkey: Talatpasa Cad. No. 5, 80640 GÜLTEPE/ISTANBUL,

Tel. +90 212 279 2770, Fax. +90 212 282 6707

Ukraine: PHILIPS UKRAINE, 4 Patrice Lumumba str., Building B, Floor 7,

252042 KIEV, Tel. +380 44 264 2776, Fax. +380 44 268 0461

United Kingdom: Philips Semiconductors Ltd., 276 Bath Road, Hayes,

MIDDLESEX UB3 5BX, Tel. +44 181 730 5000, Fax. +44 181 754 8421

United States: 811 East Arques Avenue, SUNNYVALE, CA 94088-3409,

Tel. +1 800 234 7381

Uruguay: see South America

Vietnam: see Singapore

Yugoslavia: PHILIPS, Trg N. Pasica 5/v, 11000 BEOGRAD,

Tel. +381 11 625 344, Fax.+381 11 635 777

For all other countries apply to: Philips Semiconductors, Marketing & Sales Communications,

Building BE-p, P.O. Box 218, 5600 MD EINDHOVEN, The Netherlands, Fax. +31 40 27 24825

© Philips Electronics N.V. 1997 SCA54

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed

without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license

under patent- or other industrial or intellectual property rights.

Internet: http://www.semiconductors.philips.com

Printed in The Netherlands 297027/20/01/pp24 Date of release: 1997 Apr 08 Document order number: 9397 750 01427

Loading...

Loading...