Page 1

STW20NA50

N - CHANNEL ENHANCEMENT MODE

FAST POWER MOS TRANSISTOR

TYPE V

DSS

R

DS(on)

I

D

STW20NA50 500 V < 0.27 Ω 20 A

■ TYPICAL R

■ ± 30V GATE TO SOURCE VOLTAGE RATING

■ 100% AVALANCHE TESTED

■ REPETITIVE AVALANCHE DATA AT 100

■ LOW INTRINSIC CAPACITANCES

■ GATE GHARGE MINIMIZED

■ REDUCED THRESHOLD VOLTAGE SPREAD

DS(on)

= 0.22 Ω

o

C

DESCRIPTION

This series of POWER MOSFETS represents the

most advanced high voltage technology. The optimized cell layout coupled with a new proprietary

edge termination concur to give the device low

R

and gate charge, unequalled ruggedness

DS(on)

and superior switching performance.

APPLICATIONS

■ HIGH CURRENT, HIGH SPEED SWITCHING

■ SWITCH MODE POWERSUPPLIES (SMPS)

■ DC-AC CONVERTERS FOR WELDING

EQUIPMENT AND UNINTERRUPTIBLE

POWER SUPPLIES AND MOTOR DRIVE

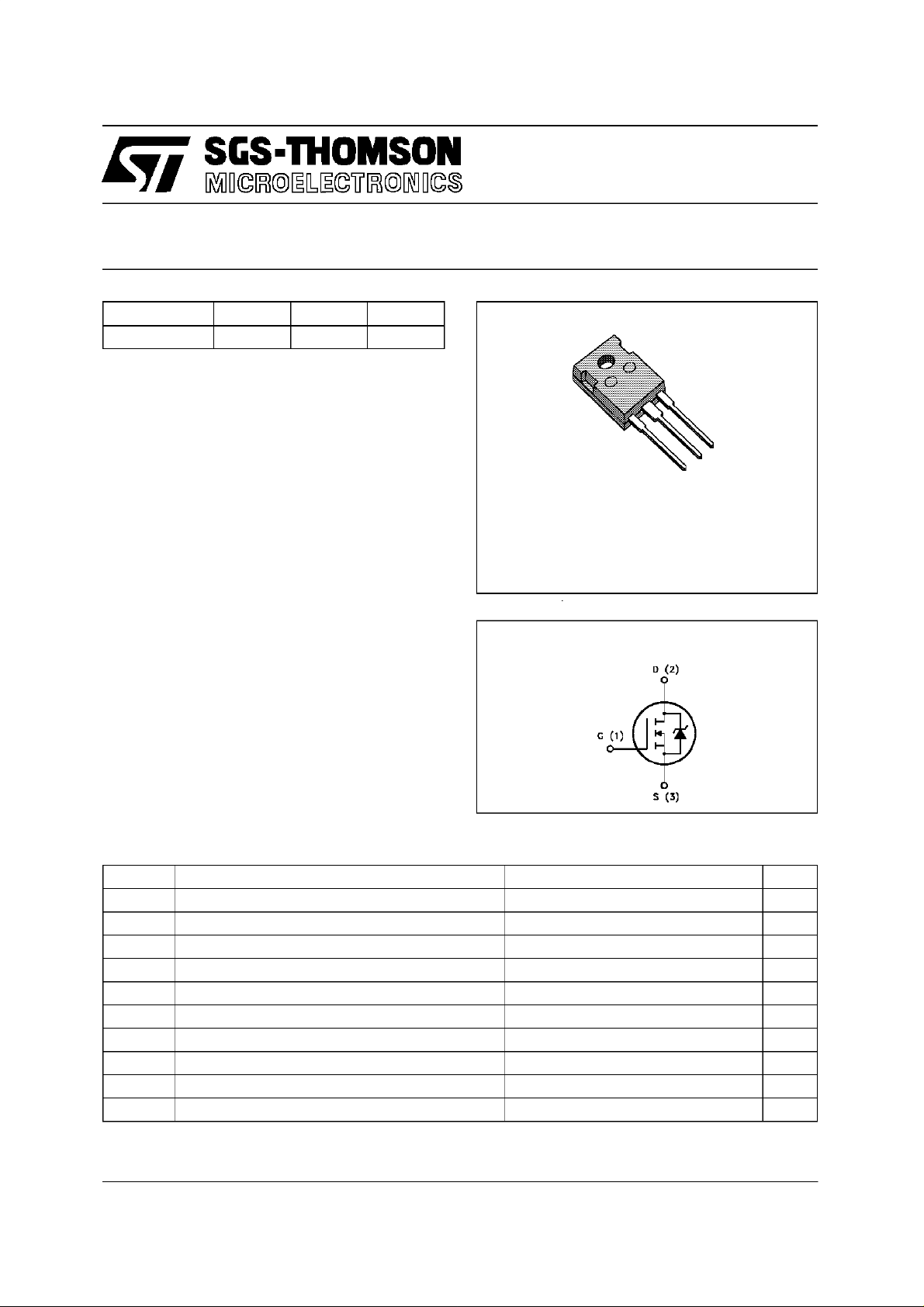

3

2

1

TO-247

INTERNAL SCHEMATIC DIAGRAM

ABSOLUTE MAXIMUM RATINGS

Symb o l Paramet er Val u e Unit

V

V

V

I

DM

P

T

(•) Pulsewidth limited bysafe operating area

December 1996

Drain - s ource Voltage (VGS= 0) 500 V

DS

Drain- gate Voltage (RGS=20kΩ) 500 V

DGR

Gate-source Voltage ± 30 V

GS

Drain Current (continuous) at Tc=25oC20A

I

D

Drain Current (continuous) at Tc=100oC12.7A

I

D

(•) Drain Current (pulsed) 80 A

Total Di ssipation at Tc=25oC 250 W

tot

Derating F actor 2 W/

St or a ge Tem perature -65 to 150

stg

Max. Operating Junction Temperature 150

T

j

o

C

o

C

o

C

1/9

Page 2

STW20NA50

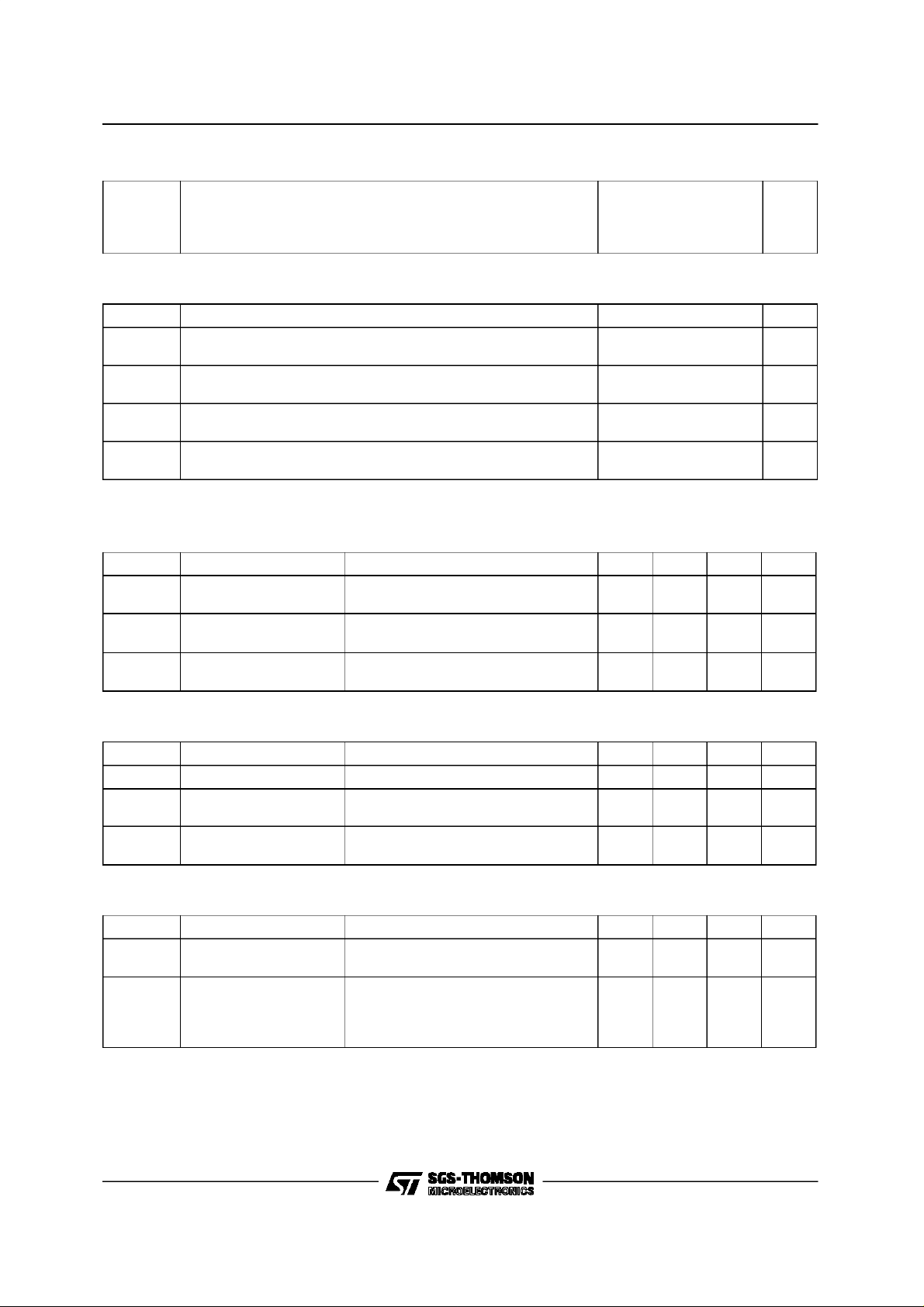

THERMAL DATA

R

thj-case

R

thj-amb

R

thj-amb

T

AVALANCHE CHARACTERISTICS

Symbol Parameter Max Valu e Uni t

I

AR

E

E

I

AR

Thermal Resistance Junction - cas e Max

Thermal Resistance Junction- ambient Max

Thermal Resistance Case-sink Typ

Maximum L ead Temperat ur e For Soldering Purpos e

l

Avalanc h e Cu rr ent , Repet itive or Not-R ep et itive

(pulse width limited by Tjmax, δ <1%)

Single Pul se Avalanche Ener gy

AS

(starti ng Tj=25oC, ID=IAR,VDD=50V)

Repetitive Avalanc he Energ y

AR

(pulse width limited by Tjmax, δ <1%)

Avalanc h e Cu rr ent , Repet itive or Not-R ep et itive

(Tc= 100oC, pulse width limited by Tjmax, δ <1%)

0.5

30

0.1

300

20 A

1000 mJ

8mJ

12.7 A

o

C/W

o

C/W

o

C/W

o

C

ELECTRICAL CHARACTERISTICS (T

=25oC unless otherwise specified)

case

OFF

Symbol Parameter Test Condition s Min. Typ. Max. Unit

V

(BR)DSS

Drain - s ource

ID=250µAVGS= 0 500 V

Break d own Volta ge

I

DSS

I

GSS

Zer o Gate Volt age

Drain Current (V

GS

Gat e- body Leak age

=0)

=MaxRating

V

DS

V

= Max Rating x 0 .8 Tc=125oC

DS

25

250

VGS= ± 30 V ± 100 nA

Current (VDS=0)

ON (∗)

Symbol Parameter Test Condition s Min. Typ. Max. Unit

V

GS(th)

R

DS(on)

Gate Threshold Voltage VDS=VGSID=250µA 2.25 3 3.75 V

St at ic Drain-s our ce O n

VGS=10V ID= 10 A 0.22 0.27 Ω

Resistance

I

D(on)

On State Drain Current VDS>I

D(on)xRDS(on)max

20 A

VGS=10V

DYNAMIC

Symbol Parameter Test Condition s Min. Typ. Max. Unit

(∗)Forward

g

fs

Tr ansconductance

C

C

C

Input Capacitance

iss

Out put Capacitance

oss

Reverse Transfer

rss

Capacitance

VDS>I

D(on)xRDS(on)maxID

= 10 A 10 17.5 S

VDS=25V f=1MHz VGS= 0 3600

490

140

4700

650

180

µA

µA

pF

pF

pF

2/9

Page 3

STW20NA50

ELECTRICAL CHARACTERISTICS (continued)

SWITCHING ON

Symbol Parameter Test Condition s Min. Typ. Max. Unit

t

d(on)

(di/dt)

Q

Q

Q

Turn-on T im e

t

Rise Time

r

Turn-on C urrent S lope VDD=400V ID=20A

on

Total Gate Charge

g

Gat e- Source Charge

gs

Gate-Drain Charge

gd

SWITCHING OFF

Symbol Parameter Test Condition s Min. Typ. Max. Unit

t

r(Voff)

t

Off -voltage R ise Time

t

Fall Time

f

Cross-over Time

c

SOURCE DRAIN DIODE

VDD=250V ID=10A

RG=4.7 Ω VGS=10V

30

55

(see test circuit, figure 3)

160 A/µs

RG=47 Ω VGS=10V

(see test circuit, figure 5)

VDD= 400 V ID=20A VGS=10V 150

18

72

VDD=400V ID=20A

RG=4.7 Ω VGS=10V

(see test circuit, figure 5)

40

25

75

40

75

195 nC

55

35

100

ns

ns

nC

nC

ns

ns

ns

Symbol Parameter Test Condition s Min. Typ. Max. Unit

I

I

SDM

SD

Source-drain Current

(•)

Source-drain Current

20

80

(pulsed)

V

(∗) Forward On Volt age ISD=20A VGS=0 1.6 V

SD

t

Reverse Recovery

rr

Time

Q

Reverse Recovery

rr

ISD= 20 A di/dt = 100 A/µs

VDD= 100 V Tj=150oC

(see test circuit, figure 5)

610

10.1

Charge

I

RRM

Reverse Recovery

33

Current

(∗) Pulsed:Pulse duration = 300 µs, dutycycle 1.5 %

(•) Pulse widthlimited by safeoperating area

Safe Operating Areas Thermal Impedance

A

A

ns

µC

A

3/9

Page 4

STW20NA50

Derating Curve

Transfer Characteristics

Output Characteristics

Transconductance

Static Drain-source On Resistance

4/9

Gate Charge vs Gate-source Voltage

Page 5

STW20NA50

Capacitance Variations Normalized Gate Threshold Voltage vs

Temperature

Normalized On Resistance vs Temperature Turn-on Current Slope

Cross-over TimeTurn-off Drain-source Voltage Slope

5/9

Page 6

STW20NA50

Switching SafeOperating Area Accidental Overload Area

Source-drain Diode Forward Characteristics

Fig. 1: Unclamped Inductive Load Test Circuits Fig. 2: Unclamped Inductive Waveforms

6/9

Page 7

STW20NA50

Fig. 3: Switching Times Test Circuits For

Resistive Load

Fig. 5: Test Circuit For Inductive Load Switching

And Diode Recovery Times

Fig. 4: Gate Charge Test Circuit

7/9

Page 8

STW20NA50

TO-247 MECHANICAL DATA

DIM.

MIN. TYP. MAX. MIN. TYP. MAX.

A 4.7 5.3 0.185 0.208

A1 2.87 0.113

A2 1.5 2.5 0.059 0.098

b 1 1.4 0.039 0.055

b1 2.25 0.088

b2 3.05 3.43 0.120 0.135

C 0.4 0.8 0.015 0.031

D 20.4 21.18 0.803 0.833

e 5.43 5.47 0.213 0.215

E 15.3 15.95 0.602 0.628

L 15.57 0.613

L1 3.7 4.3 0.145 0.169

Q 5.3 5.84 0.208 0.230

ØP 3.5 3.71 0.137 0.146

mm inch

8/9

C

A

b1

A1

b

e

b2

A2

Q

D

L1

L

ø

E

Page 9

STW20NA50

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsability for the

consequences of useof such informationnor for any infringement of patents or other rightsof third parties which mayresults fromits use. No

licenseis granted by implication orotherwise under any patentor patent rights of SGS-THOMSONMicroelectronics. Specificationsmentioned

in thispublication are subject to change withoutnotice. Thispublication supersedes andreplacesall informationpreviously supplied.

SGS-THOMSONMicroelectronics products are not authorizedfor use ascriticalcomponents in lifesupportdevicesor systems withoutexpress

writtenapproval ofSGS-THOMSONMicroelectonics.

1996 SGS-THOMSON Microelectronics -Printed in Italy- AllRightsReserved

Australia- Brazil -Canada -China - France- Germany - HongKong- Italy - Japan- Korea- Malaysia - Malta- Morocco - The Netherlands -

Singapore - Spain - Sweden - Switzerland-Taiwan - Thailand- UnitedKingdom - U.S.A

SGS-THOMSONMicroelectronics GROUPOF COMPANIES

.

9/9

Loading...

Loading...