Page 1

.

HOOK SWITCH DRIVER

.

RING INDICATOR

.

LINE INTERFAC E

- DC TERMINATION (4V AT 20mA )

- 2W/4W HYBRID CONVERTER

- FLAT FREQUENCY RESPONSE DOWN TO

10Hz FOR 56Kps MODEM

.

INTERFACE WITH CAPACITIVE ISOLATION

BARRIER

.

CALLER ID INTERFA CE

.

DIGITAL PHONE LINE OR OVER LOOP

CURRENT LIMIT DETECT

.

PHONE LINE IN USE CHECK

APPLICA TIONS

.

MODEMS UP TO V.34, 33.6KBPS A ND 56K bps

.

PCMCIA CARDS

.

FAX MA CHINES

.

PERSONAL DIGITAL ASSISTANTS

.

ANSWERING MACHINES

.

HIGH FEATURE PHONES

.

WEBPHONES AND SET TOP BOXES

DESCRIPTION

ST952 is a line interface designed to implement

Modem application up to 56Kbps and Voice applications.

ST952 interfaces between telephone line and capacitive isolation barrier.

A complete D. A.A. is made with ST75951 which

interfaces between capacitive isolation barrier and

the DSP or HSP signals.

Tip

Digital

ST75951 ST952

Signals

It incorporates Krypton Isolation Inc. patented silicon DAA technology.

The ring burst signal is detected by ST952 and is sent

to ST75951 through the capacitive isolation barrier.

Using t he control signals given by ST7 5951, through

the cap ac itiv e isolation barrier, ST952 ac ti va tes t he

off-hook or the CLID external transistor sw it c h.

Ring

ST952

D.A.A. LINE INTERFACE

PRELIMINARY DATA

TQFP32

(Thin Plastic Quad Flat Pack)

ORDER CODE :

If CLID external transistor switch is enabled, a

limited amount of current, less than 1mA, is drawn

from the line.

In off-hook state, ST952 DC voltage, 4V at a 20mA

line current, allows to interface with most of public

networks in the world.

The return loss is externally adjustable t o real or

complex impedance.

In case of a wrong connection in a digital phone

line, ST952 detects the over current value and

sends to ST75951 an alert signal through the ca pacitive isolation barrier.

Before starting a line connection, ST952 is abled

to check if the line is used by an other terminal

connected on the same telephone line.

PIN CONNECTIONS

16

17TER1

SET

VDR

LINE

IDG

952-02.EPS

IDI

LINI

GAIN

18

19

20

21

22

23

24

25 26 27 28 29

(7 x 7 x 1.4mm)

TER2

VDREF

IREF

AIN

AOUT

LCOM

ST952TQF7

OHC

NC

NCNC

30 31 32

D1

NC

101112131415

COM

D2

IDC

9

8

7

6

5

4

3

2

1

LCOM

LIM1

LIM2

TOFF

D6

D5

RIN

D4

D3

952-01.EPS

December 1998

This is advance information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

1/12

Page 2

ST952

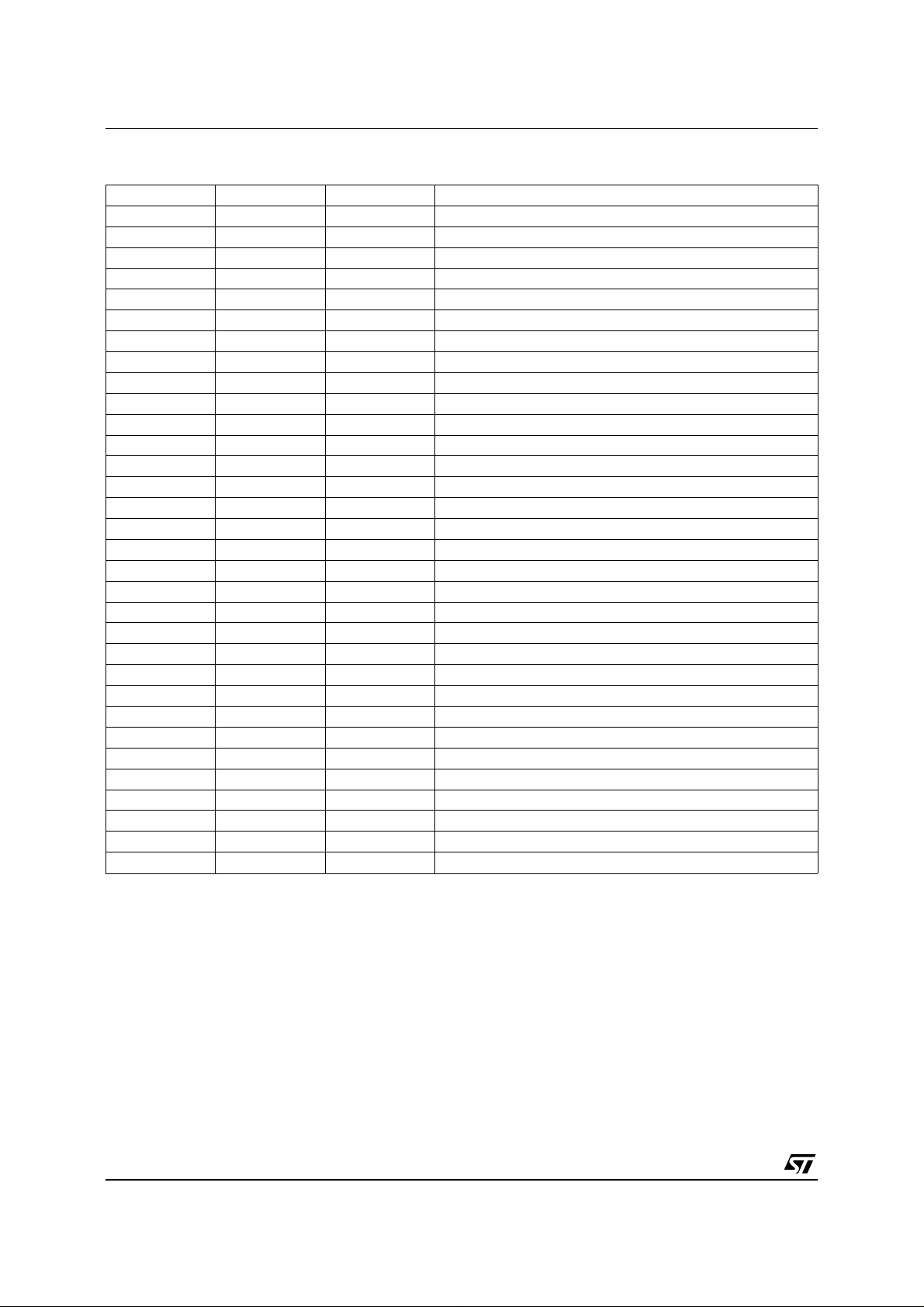

PIN LIST

Pin Number Name Type Description

1 D3 Output Isolation Signal Output

2 D4 Output Isolation Signal Output

3 RIN Input Ring Signal Input

4 D5 Input Isolation Control Signal Input

5 D6 Input Isolation Control Signal Input

6 TOFF Supply Internal Reference Supply

7 LIM2 Input Loop Current Limiter Control

8 LIM1 Output Loop Current Limiter Control

9 IDC Output Caller ID Control Output

10 COM Output Off-hook & ID Commun Output

11 OHC Output Off-hook Control Output

12 N.C. - Not Connected

13 N.C. - Not Connected

14 IREF Input Current Reference Setting

15 VDREF Supply Internal Reference Pin

16 TER2 Output Current Regulator Control Feedback

17 TER1 Output Current Regulator Control Output

18 SET Input Current Regulator Filter

19 VDR Supply Line DC Voltage Regulator

20 LINE Output Line AC Signal Output

21 IDG Input Caller ID Voltage Reference Input

22 IDI Input Caller ID Signal Input

23 LINI Input Line AC Signal Input

24 GAIN Input Transmit Gain / Trans-Hybrid Loss Set

25 LCOM Ground Line Side Common Ground

26 AIN Input Analog Transmit Signal Input

27 AOUT Output Analog Transmit Signal Output

28 N.C. - Not Connected

29 N.C. - Not Connected

30 D1 Input Isolation Signal Input

31 D2 Input Isolation Signal Input

32 LCOM Ground Line Side Common Ground

Note :

Pins 12, 13, 28 and 29 must be left opened.

952-01.TBL

2/12

Page 3

PIN DESCRIPTION

D1 - D2

These pins input the A C signal modulated at Fmod

coming from ST75951 through the capacitive isolation barrier.

ST952

RIN

During the ring burst, a 1MHz oscillator is pow ered

on this pin and a 6V

and D4 to indicate the ring presence.

/1MHz signal is sent on D3

PP

D3 - D4

These pins output the AC signal modulated at Fmod

in off-hook mode and at Fmod /2 in CLID mode to

ST7 59 51 through t he capacitiv e isolatio n barrier .

In ring mode, these pins out put the ring information,

a differential 6V

/1MHz signal.

PP

D5 - D6

These control pins input a 5V

/Fmod signal com-

PP

ing from ST75951 through the capacitive isolation

barrier.

These signals control the off-hook and CLID external transistor switches and are sent to the internal

transmit demodulator and receive modulator.

Off-hook mode is enabled with a 5V

/Fmod signal

PP

sent on D5 and D6 inputs with an opposite phase

(see Figure 1). With a dedicated application it is

possible to reduce the input level to 3V

CLID mode is enabled with a 5V

.

PP

/Fmod signal

PP

sent on D5 input only ( s ee Figure 2). With a dedicated application it is possible to reduce the input

level to 3V

PP

.

Figure 1

D5

D6

5V

Fmod

5V

Fmod

LINE

DC positive line connection and line AC signal output.

LCOM

Negative line connection.

LINI

Line AC signal input in off-hook mode.

AIN - AOUT

The transmit signal coming from AIN pin is injected

in AOUT pin to the 2W/4W internal converter stage.

The line echo is minimized if R3, connected between LINE and VDR pins is equal to 620Ω.

IREF

Internal reference current source setting, R4 must

be equal to 82kΩ.

VDR

Power supply for the transmit and receive paths in

Off-Hook mode.

VDREF

Internal resistor reference.

SET

Line gyrator AC/DC filter.

OHC

When D5 and D6 inputs a 5V

/Fmod signal in

PP

opposite phase, this pin puts ON the hook swit ch

external Q1/Q2 transistor stage.

IDC

When D5 input a 5V

/Fmod sign al, this pin puts

PP

ON the CLID external Q3/Q4 transistor stage.

R2 limits t he line current in CL ID mode at 1mA

max.

COM

Commun output for off-hook and CLID external

transistor stages

TER1 - TER2

These pins control the external Q5 transistor, in

which the main part of the line current goes

through to meet the line DC, V = f(I

952-03.EPS

), termination

L

requirements.

IDI

Line AC signal input in CLID mode.

IDG

Power supply for the r ec eive path in CLID mode.

LIM1 - LIM2

200mA over current detection for device protection.

TOFF

Internal Reference Supply.

Figure 2

GAIN

R1 connected on this pin fi xes the transm it gain.

The R1 recommanded value, on a 600Ω AC line

termination, is 82Ω.

D5

D6

5V

Fmod

3/12

952-04.EPS

Page 4

ST952

BLOCK DIAGRAM

C8

Tip

2627

R8

Ring

C6

R7

R6

R2

IDG

21

CLID

Q4 Q5

Q2

R3

C3

VDR

191415

VOLTAGE

REFERENCE

C4

R4

DREF

REF

V

I

VOLTAGE

OFF-HOOK

REFERENCE

C5

TER1

TER2

R5

Q3

Q1

C1

R1

LINE

GAIN

20

24

Output

Amplifier

23

C2

LINI

IDI

22

C7

SET

R9

16 17 18

4/12

AOUT AIN

ST952

FILTER

LOW PASS

FILTER

HIGH PASS

30

31

D1

D2

Fmod

2W/4W

& HYBRID

CONVERTER

1

2

D3

D4

ST75951

RING

DETECT

3

RIN

Fmod

LIMITER

CURRENT

CLID & OFF-HOOK

SWITCH CONTROL

4

5

D5

D6

8

LIM1

7

LIM2

IDC

9

OHC

11

COM

10

TOFF

6

LCOM

25

LCOM

32

C9

952-05.EPS

Page 5

ST952

ABSOL UT E MAXIMUM RATING

(AGND = DGND = 0V , all voltages with respect to 0V)

Symbol Parameter Value Unit

V

T

MLINE

oper

Positive Line Voltage Continuous 14 V

Operating Temperature 0, +70 °C

Tstg Storage Temperature -55, +150 °C

THERMAL DATA

Symbol Parameter Value Unit

R

th (j-a)

ELECTRICAL CHARACTERI STICS

Junction-ambient Thermal Resistance Max. 80

= 25oC, unless otherwise specified)

(T

amb

Symbol Parameter Test Conditions Min. Typ. Max. Unit

DC AND AC TERMINATION (see Figure 3)

V

LINE

ZLOSS Return Loss I

RECEIVE PATH (I

Grx Receive Gain V

Grf Receive Frequency Response V

Rxhd Receive 2nd/3th/4th Harmonic Distortion V

Thl Trans-Hybrid Loss V

Rn Receive Noise Floor V

TRANSMIT PATH (IL = 20mA, f = 1kHz, V

Gtx Transmit Gain V

Gtf Transmit Frequency Response V

Txhd Transmit 2nd/3th/4th Harmonic Disto rtion V

Line Voltage IL = 20mA

IL = 120mA

= 20mA, V

L

f = 200 to 4000Hz 24

= 20mA, f = 1kHz, see Figure 4)

L

= 0dBV, V

LAC

= 0dBV, V

LAC

f = 200 to 3400Hz

f = 50 to 200Hz

= 0dBV, V

LAC

f = 150Hz

f = 1000Hz

= 0, V

LAC

Fmod = 1.5MHz

= V

LAC

f = 200-3400Hz, 100Hz BW

= 0, see Figure 4)

LAC

= -6dBV -0.5 0 0.5 dB

TAC

= -6dBV, f = 200 to 4000Hz -0.2 +0.2 dB

TAC

= -6dBV, Fmod = 1.5MHz -82 dBV

TAC

TAC

10.5

= -6dBV

LAC

= 0 -0.5 0 0.5 dB

TAC

= 0

TAC

-0.1

-0.5

= 0

TAC

= -6dBV,

TAC

30 35 dB

= 0,

4.1

-79

-82

-93 dBV

Txmax Max Line Drive Voltage 3 V

Tn Transmit Noise Floor V

= 0,

TAC

f = 200-3400Hz, 100Hz BW

-93 dBv

POWER AND DC LOGIC INPUT (see Figure 5)

V

I

LINE

OFH

Line Current ST952 Line Pin + Ic(Q5) 10 120 mA

Hook Switch Input D5 and D6 Input

Active (Off-hook)

2.7 5.25

Inactive (On-hook)

V

CLID

CLID Input D5 Input

Active (CLID On)

2.7 5.25

Inactive (On-hook)

CALLER ID RECEIVE PATH (see Figure 6)

G

I

LID

CLID Receive Gain V

RID

= -15dBV -1 0 +1 dB

TAC

CLID Line Current 1mA

RING INDICATOR (see Figure 7)

V

V

Note :

RIOF

RION

D3 & D4 Ring indicator D3 = D4 = 0

D3 = D4 = 3VPP 18

D3 and D4 are complementary outputs.

o

C/W

+0.1

+0.5dBdB

0.8VV

0.8VV

8V

V

V

dB

dB

dBV

dBV

PP

V

952-02.TBL

952-03T.BL

952-04.TBL

5/12

Page 6

ST952

Figure 3 :

Test 1

ZTER - 600

W

600

F

m

100

LAC

V

= 20 & 120mA

L

ACLINE

V

ZTER + 600

AC

I

at I

LINE

557

20

L

I

W

47k

82

W

GAIN

24

LINE

S1 opened :

- V

47k

BC

557

F

m

1

LINI

23

ZTER =

S1 closed :

- ZLOSS measured

W

W

47k

1nF

IDI

IDG

22

ZLOSS = 20.log

BC

547

BC

547

BC

547

W

620

21

39

W

F

m

47

VDR

191415

100nF

DREF

V

F

W

m

82k

4.7

REF

I

AC

S1

I

AC

+ I

L

I

ACLINE

V

BC

SET

Output

Amplifier

2627

F

m

1

CLID

VOLTAGE

REFERENCE

OFF-HOOK

REFERENCE

AOUT AIN

FILTER

LOW PASS

2W/4W

& HYBRID

CONVERTER

CURRENT

Fmod

Fmod

FILTER

ST952

HIGH PASS

30

31

D1

D2

D3

RING

DETECT

1

2

D4

3

RIN

CLID & OFF-HOOK

4

D5

TER1

VOLTAGE

TER2

16 17 18

8

LIM1

7

LIM2

LIMITER

IDC

9

OHC

11

COM

10

TOFF

6

SWITCH CONTROL

LCOM

25

LCOM

32

5

D6

100nF

6/12

VD5/1.5MHz

VD6/1.5MHz

952-06.EPS

Page 7

ST952

Figure 4 :

Test 2

= 0

= 0

= 0

LAC

TAC

and V

RAC

ACLINE

V

BC

23

LINI

557

47k

V

Gr = 20.log

W

1nF

IDI

22

LAC

600

F

m

V

W

100

20mA

BC

LINE

557

20

W

47k

F

m

1

82

W

GAIN

24

ACLINE

V

and V

ACLINE

V

Gt = 20.log

TAC

V

W

47k

IDG

LAC

@ V

RAC

ACLINE

V

V

thl = 20.log

BC

547

BC

547

BC

547

W

620

21

39

W

F

m

47

VDR

191415

100nF

DREF

V

F

W

m

82k

4.7

REF

I

SET

Output

Amplifier

2627

F

m

1

CLID

VOLTAGE

REFERENCE

OFF-HOOK

REFERENCE

AOUT AIN

FILTER

LOW PASS

2W/4W

& HYBRID

CONVERTER

CURRENT

Fmod

Fmod

FILTER

ST952

HIGH PASS

30

D1

1.5MHz

DEMODULATOR

RING

DETECT

1

D3

2

D4

31

D2

3

RIN

1.5MHz

DEMODULATOR

CLID & OFF-HOOK

4

D5

5V/1.5MHz

RAC

TAC

V

V

TER1

VOLTAGE

TER2

16 17 18

8

LIM1

7

LIM2

LIMITER

IDC

9

OHC

11

COM

10

TOFF

6

SWITCH CONTROL

LCOM

25

LCOM

32

5

D6

5V/1.5MHz

100nF

952-07.EPS

7/12

Page 8

ST952

Figure 5 :

Test 3

F

m

1

2627

600

W

F

m

100

I

LINE

W

47k

BC

557

82

W

LINE

GAIN

20

24

Output

Amplifier

47k

W

BC

557

F

m

1

23

1nF

LINI

IDI

22

BC

BC

BC

W

47k

IDG

21

CLID

W

620

REFERENCE

547

547

547

191415

VOLTAGE

39

F

m

47

VDR

W

W

82k

100nF

DREF

REF

V

I

VOLTAGE

OFF-HOOK

REFERENCE

F

m

4.7

TER1

TER2

SET

16 17 18

AOUT AIN

ST952

FILTER

LOW PASS

FILTER

HIGH PASS

30

31

D1

D2

Fmod

2W/4W

& HYBRID

CONVERTER

1

2

D3

D4

RING

DETECT

3

RIN

Fmod

LIMITER

CURRENT

CLID & OFF-HOOK

SWITCH CONTROL

4

5

D5

D6

VD5/1.5MHz

VD6/1.5MHz

8

LIM1

7

LIM2

IDC

9

OHC

11

COM

10

TOFF

6

LCOM

25

LCOM

32

100nF

952-08.EPS

8/12

Page 9

ST952

Figure 6 :

Test 4

RAC

ACLINE

V

BC

23

LINI

557

47k

22

Grid = 20.log

IDI

V

W

1nF

BC

BC

BC

W

47k

IDG

21

CLID

39

547

547

547

W

620

F

m

47

VDR

191415

VOLTAGE

REFERENCE

W

100nF

DREF

V

OFF-HOOK

REFERENCE

F

W

m

82k

4.7

REF

I

TER1

VOLTAGE

TER2

16 17 18

SET

LAC

600

F

m

100

1mA

BC

Amplifier

LINE

557

20

W

47k

GAIN

24

ACLINE

V

Output

2627

F

m

1

V

W

F

m

1

82

W

AOUT AIN

ST952

FILTER

LOW PASS

FILTER

HIGH PASS

30

31

D1

D2

8

LIM1

7

2W/4W

& HYBRID

CONVERTER

Fmod

Fmod

RING

DETECT

1

D3

2

0.75MHz

DEMODULATOR

RAC

V

D4

3

RIN

CURRENT

CLID & OFF-HOOK

4

D5

VD5/1.5MHz

LIM2

LIMITER

IDC

9

OHC

11

COM

10

TOFF

6

SWITCH CONTROL

LCOM

25

LCOM

32

5

D6

100nF

952-09.EPS

9/12

Page 10

ST952

Figure 7 :

D1

30

D2

31

D3

D4

RIN

10k

W

Ur

D5

D6

Test 5

ST952

1

2

3

4

5

DETECT

32

LCOM

RING

25

LCOM

HIGH PASS

FILTER

Fmod

Fmod

CLID & OFF-HOOK

SWITCH CONTROL

COM

11

9

OHC

10

6

TOFF

IDC

AOUT AIN

LOW PASS

FILTER

2W/4W

CONVERTER

& HYBRID

CURRENT

LIMITER

8

7

LIM2

LIM1

1mF

2627

Output

Amplifier

CLID

REFERENCE

VOLTAGE

OFF-HOOK

REFERENCE

VOLTAGE

16 17 18

TER2

TER1

SET

20

24

23

22

21

19

15

14

LINE

GAIN

LINI

IDI

IDG

VDR

V

DREF

I

REF

82

W

1mF

1nF

47k

620

47mF

100nF

82k

4.7mF

BC

557

47k

W

BC

557

W

W

W

BC

547

47k

W

BC

547BC547

39

W

100nF

For Ur = V1, no signal on D3/D4

For Ur = V2, 6V

/1MHz on D3/D4

PP

952-10.EPS

10/12

Page 11

ST952

TYPICAL APPLICATION

Tip

W

10

W

22k

47nF

D4

D6

Q4

D5

D7

47k

SMTPA

270

Ring

22k

47nF

W

(5V Supply on ST75951)

W

82k

1mF

82

1nF

47k

W

W

100nF

Q5

W

47k

Q1

W

13V

Q2

Q3

W

620

F

m

47

100nF

W

39

ST952

LINI

23

ST75951

GAIN

24

D1

OHC

11

10

COM

TER1

17

TER2

16

RIN

3

LINE

20

IDI

22

IDG

21

IDC

9

VDR

19

VDREF

15

IREF

14

SET

18

F

m

LCOM

25

4.7

LCOM

32

6

TOFF

D2

D3

D4

D5

D6

LIM2

LIM1

AOUT

AIN

30

31

1

2

4

5

7

8

27

26

1mF

35

34

31

30

27

26

D1

D2

D3

D4

D5

D6

MCLK

SCLK

FS

DIN

DOUT

RESET

PWRDWN

HC1

46

47

43

11

8

2

3

P

R

O

C

E

S

S

O

R

9

952-11.EPS

11/12

Page 12

ST952

PACKAGE MECHANICAL DATA

32 PINS - PLASTIC THIN QUAD FLAT PACK (TQFP)

32 25

1

e

24

E3

E1

E

A

A2

A1

0,10 mm

.004 inch

SEATING PLANE

B

17

L1

c

L

K

0,25 mm

.010 inch

GAGE PLANE

Dimensions

8

916

D3

D1

D

Millimeters Inches

Min. Typ. Max. Min. Typ. Max.

A 1.60 0.063

A1 0.05 0.15 0.002 0.006

A2 1.35 1.40 1.45 0.053 0.055 0.057

B 0.30 0.37 0.45 0.012 0.015 0.018

C 0.09 0.20 0.004 0.008

D 9.00 0.354

D1 7.00 0.276

D3 5.60 0.220

e 0.80 0.031

E 9.00 0.354

E1 7.00 0.276

E3 5.60 0.220

L 0.45 0.60 0.75 0.018 0.024 0.030

L1 1.00 0.039

K0

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the

consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from

its use. No licence is granted by implicat ion or otherwise under any patent or patent rights of STMicroelectronics. Specifications

mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information

previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or sys te ms

without express written approv al of STMi cr oelec troni cs.

Purchase of I

Rights to use these components in a I

Australia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands

Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

The ST logo is a registered trademark of STMicroelectronics

© 1998 STMicroelectronics - All Rights Reserved

2

C Components of STMicroelectronics, conveys a license under the Philips I2C Pate n t .

2

the I

C Standard Specifications as defined by Phili ps.

STMicroelectronics GROUP OF COMPANIES

2

C system, is granted provided that the system conforms to

http://www.st.com

o

(Min.), 7o (Max.)

12/12

PM-5V.EPS

5V.TBL

Loading...

Loading...