Page 1

ISDN HDLC AND GCI CONTROLLER

MONOLITHIC ISDN ORIENTED HDLC AND

GCI CONTROLLER.

GCI ANDµW/DSI COMPATIBLE.

FULLY CONTROLLING GCI AND GCI-SCIT

M & C/I CHANNELS MANAGEMENT.

FULLY SUPPORTINGLAPBANDLAPDPRO-

TOCOL ON B OR D CHANNEL.

EASILY INTERFACEABLE WITH ANY KIND

OF STANDARD NON MULTIPLEXED OR

MULTIPLEXEDBUS MICROPROCESSOR.

DMAACCESS WITH MULTIPLEXEDBUSµP

CAN HANDLE AND STORE AT THE SAME

TIME TWO FRAMES IN TRANSMISSION

(64bytes FIFO Tx) AND EIGHT FRAMES IN

RECEPTION (64bytesFIFO Rx)

COMPATIBLE WITH ALL THE STMicroelectronics ISDN PRODUCTFAMILY.

ST5451

SO28

ORDERING NUMBER: ST5451D

GENERAL DESCRIPTION

ST5451 HDLC and GCI controller is a CMOS circuit fully developed by STMicroelectronics and

diffused in advanced 1.2 µm HCMOS3 technology.

The device is intendedto be used mainly in ISDN

applications, in Terminal (TE) and in Line Terminations (LT).

ST5451 can handle HDLC packets either on

16Kbit/s D channel or 64 Kbit/s B channel; it can

work witha wide range of PCM signals going from GCI (General Circuit Interface) to DSI

(Digital System Interface) to any PCM-like

stream.

ST5451 is a complete GCI controller designed to

comply with the GCI and GCI-SCIT (Special Circuit Interface for Terminal) completely handling

Monitor (M) and Command/Indicate (C/I) channels.

ST5451 can be easily controlled by many different kind of microprocessors or microcontrollers

having either non-multiplexed or multiplexed bus

structure.

ST5451 can be used in connection with ST5420/1

S Interface Devices (SID-µW and SID-GCI) and

ST5080 Programmable ISDN Combo (PIC) in

Terminals and with ST5410 U Interface Device

(UID) in Line Terminations.

March 2000

PIN CONNECTION(Top view)

1/34

T is advancedinformation on a new product now in development or undergoing evaluation. Details are subject to change without

Page 2

ST5451

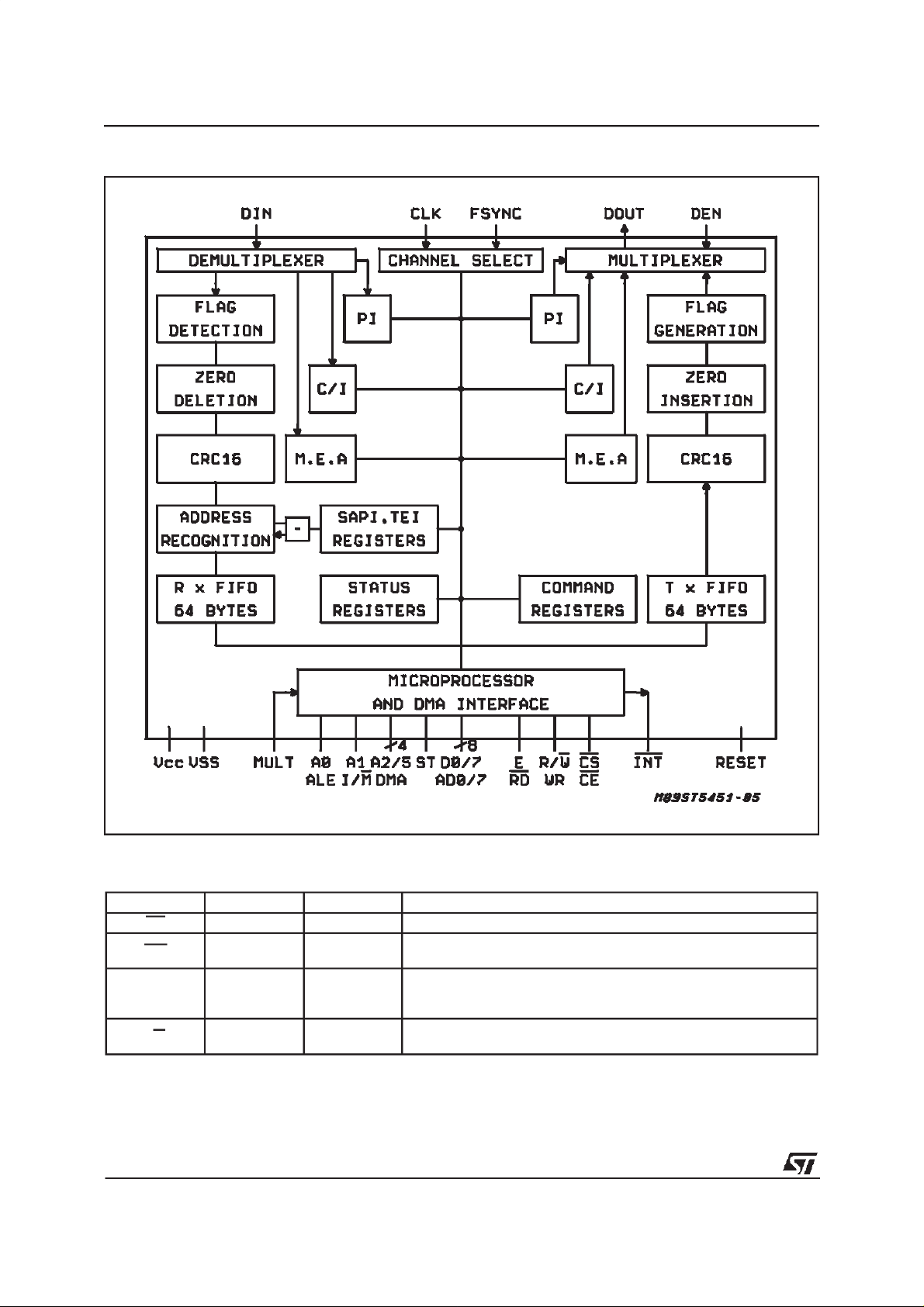

BLOCK DIAGRAM

PIN DESCRIPTION

NAME PIN TYPE FUNCTION

CS 1 I Chip Select. A lowlevel enables ST5451 forread/write operations.

INT 25 O

MULT 2 I

I/M 4 I

2/34

Interrupt request is asserted by ST5451 when it request aservice.

Open drain output.

Multiplexed Bus. Indicates the

MULT = 1: multiplexed bus andDMA available.

MULT = 0: address and data bus separated.

Intel/Motorola. When MULT = 1 this pin selects either Intel or

Motorola 6805 bus.

P bus interface selected.

µ

Page 3

DEMULTIPLEXED MICROPROCESSOR BUS INTERFACE (MULT = 0)

NAME PIN TYPE FUNCTION

A0/A5 3-8 I Address Bus. To transfer addresses from

D0/D7 17-24 I/O Data Bus. To transfer data between

R/W 27 I Read/Write. ”1” indicates a read operation; ”0” a write operation.

E26I

Enable. Read/write operations are synchronized with thissignal; its

falling edge marks the end of an operation.

µP to ST5451.

P and ST5451.

µ

MULTIPLEXEDMICROPROCESSORBUS INTERFACE (MULT = 1 I/M=1)

NAME PIN TYPE FUNCTION

AD0/AD7 17-24 I/O

WR 27 I Write. This signal indicates a write operation.

RD 26 I Read. This signal indicates a read operation.

ALE 3 I Falling edge latches the address from the external A/D Bus.

Address Data Bus. To transfer addresses and data between

and ST5451.

MULTIPLEXEDMICROPROCESSORBUS INTERFACE (MULT = 1;I/M=0)

NAME PIN TYPE FUNCTION

AD0/AD7 17-24 I/O

R/W 27 I Read/Write. ”1” Indicates a write operation; ”0” a write operation.

DS 26 I

AS 3 I

Address Data Bus. To transfer addresses and data between

and ST5451.

Data Strobe. Read/Write operations are synchronized with this

signal: its falling edge marks the end ofan operation.

Address Strobe. Fallingedge latches the address from the external

A/D Bus.

ST5451

µP

P

µ

DMA (directmemory access): only when MULT = 1

NAME PIN TYPE FUNCTION

DMA REQ X

DMA REQ R

DMA ACK X

DMA ACK R

7

5

8

6

O

O

I

I

Direct Memory Access Requests: these outputs are asserted by

the device to request an exchange of byte from the memory.

Direct Memory Access Acknowledge: these inputs are asserted by

the DMA controller to signal to the HDLC controller that a byte is

being transferred in response to a previous transferrequest.

GCI INTERFACE

NAME PIN TYPE FUNCTION

D

OUT

D

IN

C

LK

FS 13 I

DEN 10 I

15 I/O

12 I/O

11 I

Data output for Band D channels. In GCI mode it outputs B1,

B2, M and C/I channels. InTE mode (GCI-SCIT) it can invert to

input data for M’ and C/I’ channels (See Table 2).

Data input for B and D channels. In GCI mode it inputs B1, B2, M

and C/I channels. In TE mode (GCI-SCIT) itcan invert tooutput

data for M’ and C/I’ channels (See Table 2).

Data Clock. It determines the data shift rate for GCI channels on

the module interface.

Frame synchronization. This signal is a 8 kHz signal for frame

synchronization. The front edge gives the time reference of the first

bit in theframe.

Data Enable. In TE mode, this pin is a normally low input pulsing

high to indicate the active bit times for D channel transmit at DOUT

pin. It is intended to be gated with CLK to control the shifting of

data from HDLC controller to S interface device.

3/34

Page 4

ST5451

NON GCI INTERFACE

NAME PIN TYPE FUNCTION

Data output. Digital output for serial data. Three modes:

D

OUT

D

IN

C

LK

FS 13 I

DEN 10 I Data Enable. When high, enable the data transfer. on D

15 O

12 I Data input. Digital input for serial data. Three modes (See D

11 I

OTHERS

NAME PIN TYPE FUNCTION

V

DD

V

SS

R

ST

ST 9 I Special Test. (Reserved) must be tied to V

28 I Positive power supply = 5V +5%

14 I Signal ground

16 I Reset

- HDLC Protocol multiplexed link

- HDLC Protocol non multiplexed link

- Non HDLC protocol (transparent Mode).

Data Clock. It determines the data shift rate. Two modes: Single or

double bit rate.

Frame synchronization. Used in mode HDCL protocol multiplexed

link. Don’t care in other modes. The rising edge gives the time

reference of the first bit of the frame.

SS

OUT

OUT

).

2 - FUNCTIONS

2 - 1 - Basic HDLC Functions

2 - 1 - 1 - In Receive Direction:

- Channel selection

In GCI channel B1 or B2 or D may be selected.

B1 or B2 may be selected without M and C/I

channels

- Flag detection

A zero followedby six consecutiveones and another zero is recognizedas a flag

- Zerodelete

A zero, after five consecutive ones within an

HDLC frame, is deleted

- CRC checking

The CRC field is checked according to the generator polynomial

16+X12+X5

X

+1

- Check for abort

Seven or more consecutiveones are interpreted

as an abort flag

- Check for idle

Fifteen or more consecutive ones are interpretedas ”idle”

- Minimumlenght checking

HDLC frames with less than n bytes between

start and end flag are ignored: allowed values are3 ≤

n ≤ 6.

This value is set by aprogrammable register

- Address Field recognition

4 SAPI and/or 3 TEI may be recognized. Several programmableregisters indicate the recognized address types.

2 - 1 - 2 - In TransmitDirection:

- Shift control in TE mode

D channeldata are signalled by DEN pin.

- Flag generation

A flag is generated at the beginning and at the

end of every frame.

- Zero insert

A zero is inserted after five consecutive ones

within an HDLC frame

- CRC generation

The CRC field of the transmittedframe is generated according to the generatorpolynomial

16+X12+X5

X

+1

- Abort sequencegeneration

An HDLC frame may be terminated with an

abort sequence under microprocessorcontrol

- Interframetime fill

Flags or idle (consecutive ones) may be transmitted during the interframe time. A programmable bitselects the mode.

4/34

Page 5

ST5451

2 - 2 - FIFO Structure

2 - 2 - 1 - Receive FIFO Structure

In receive direction, a 64 byte FIFO memory is

used. It is divided in 8 blocks of 8 bytes automatically chained.

In case of a frame length of 64 bytes or less,the

whole frame can be stored in the FIFO. After the

first 32 bytes have been received µP is interrupted and may read the availabledata.

In case of frames longer than 64 bytes, the µPis

interruptedto read out the FIFO by 32 byte block.

In caseof several shortframes, up to eight may be

storedinside the FIFO.Afteran interrupt, one frame

is available for the µP. The eventual other seven

framesare queuedand transferredoneby one.

2 - 2 - 2 - TransmitFIFO Structure

In transmit direction, a 64 byte FIFO memory is

TABLE 1

- ST5451 Internal Registers

Address Hexa Read Write

00 Receive FIFO Transmit FIFO

1F - 20 ISTA0 ISTA0

21 ISTA1 ISTA1

22 ISTA2 ISTA2

23 STAR CMDR

24 MODE MODE

25 RFBC TSR

26 CA CA

27 CB CB

28 CC CC

29 CD CD

2A CE CE

2B CF CF

2C CIR1 CIX1

2D CIR2 CIX2

2E MONR1 MONX1/0

2F - MONX1/1

30 MONR2 MONX2/0

31 - MONX2/1

32 - MASK0

33 - MASK1

34 - MASK2

3E CCR CCR

used, structured in 2 blocksof 32 bytes. ST5451

is requested to transmit after 32 bytes have been

written into the FIFO.

If a transmission request does not include a message end, the HDLC controller will request the

next data blockby an interrupt.

2 - 3 - MicroprocessorInterface

Three types of microprocessor interfaces are

available (MULT and I/M control pins set the desired interface).

- Motorola non multiplexedfamilies.

- Motorola multiplexed family (6805 type)

- Intel family.

You can connect ST5451 to a Direct Memory Ac-

cessController as MC68440 or MC6450 (dual or

quad channels).

A programmable register indicates DMA Interface

enabling.

5/34

Page 6

ST5451

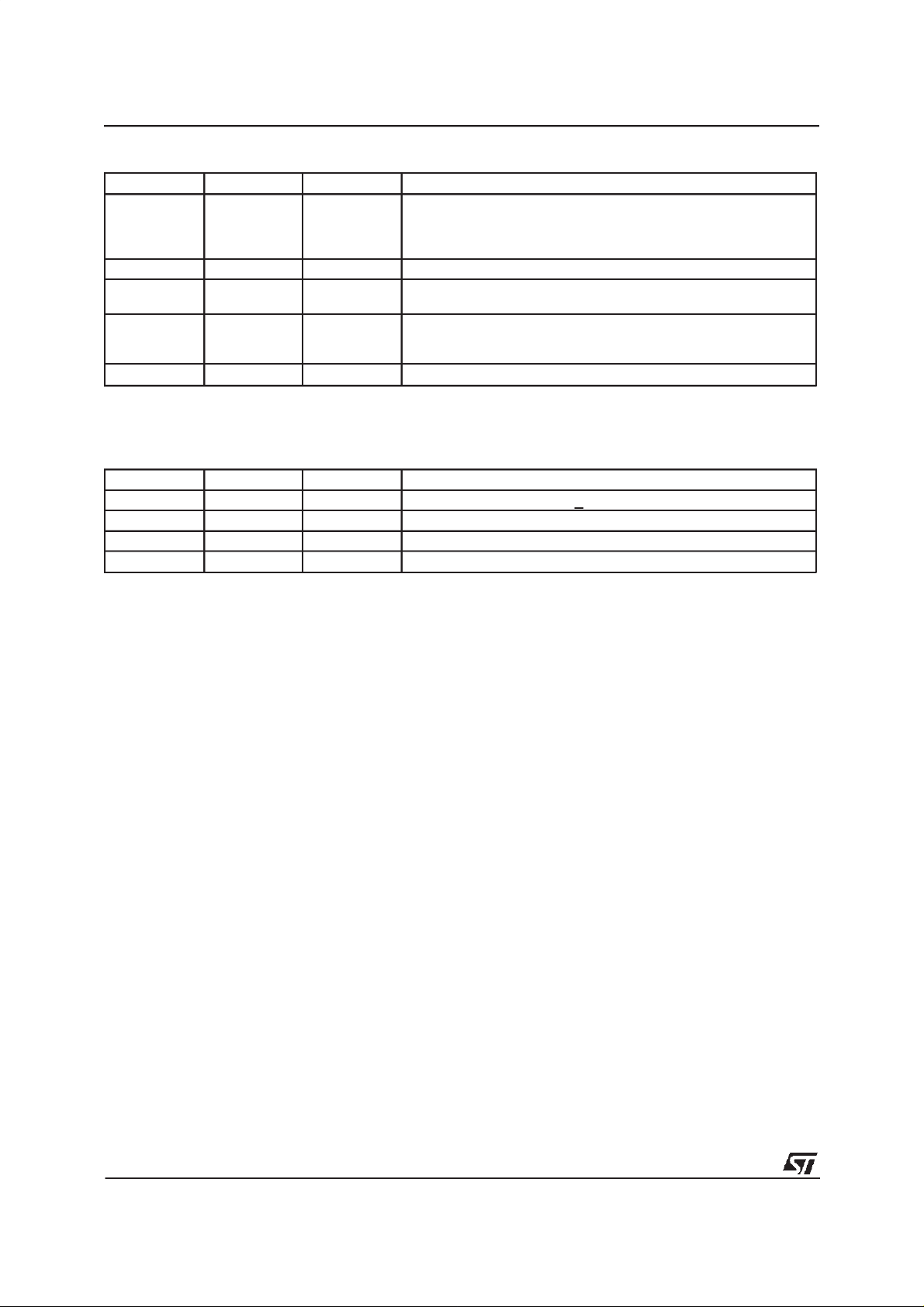

TABLE 2 - CHANNEL ASSIGNMENTSELECT

6/34

Page 7

ST5451

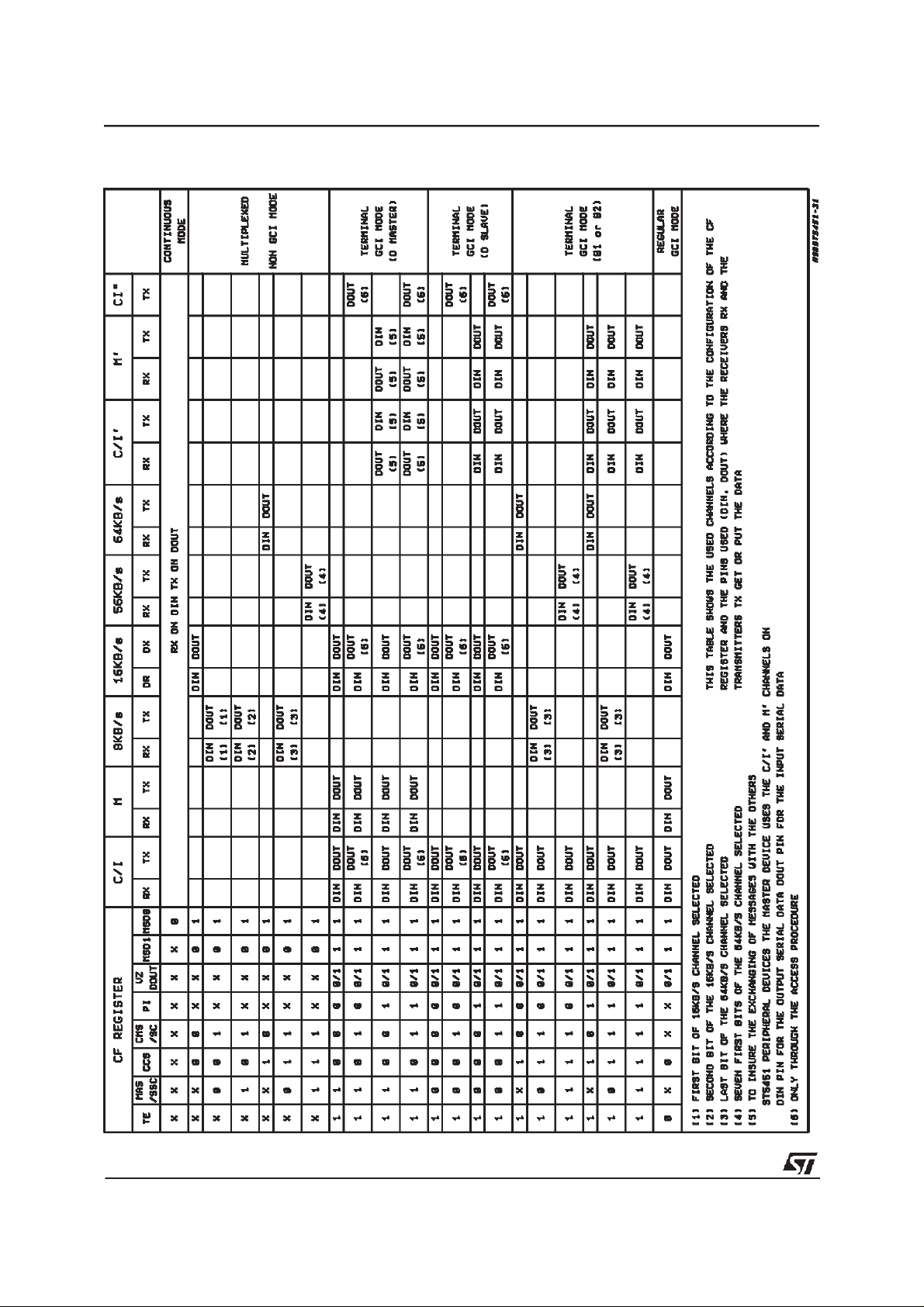

3 - REGISTERDESCRIPTION

For all the register pictures MSB is on the left and

LSB on the right

Ifnototherwisestatedbitareconsideredactiveat1.

FIFOS

RFIFO (read), XFIFO (write).

The address range of the two FIFOs are identical.

All the 32 addresses give access to the ”current”

FIFO location.

When the closing Flag of a receive frame is detected, a status byte is available in the RFIFO.

This byte has the following format:

RBC RDO CRC RAB 0 0 0 0

RBC ReceiveByte Count.

The length of the received frame is n

time 8 bits (n=3,4,5,...)

RDO Receive Data Overflow

A part of the frame has not been lost

becausethe receiveFIFO was full

CRC CRC Check

ThereceivedCRCbyteswerenotcorrect

RAB Receive Abort

The received framewas not aborted

A status byte equal to D0H indicates a correctly

received frame

enteredinto the XFIFO.

XDU TransmitData Underrun

A transmitted frame was terminated

with an abort sequence because no

data were available for transmission in

XFIFO and no XME command was issued. It is not possible to transmit

frame when that interrupt remains unacknowledgedand XRES has not been

set.

EXI2 Extended Interrupt2

The interruptreason is indicated in register ISTA2

EXI1 ExtentedInterrupt1

The interruptreason is indicated in register ISTA1.

ISTA1 InterruptStatus Register 1

After RESET 01H

(GCI mode only)

0 0 CIC1 EOM1 XAB1 RMR1 RAB1 XMR1

CIC1 Comman/IndicateChange

A change in the value of CIR1 is detected

EOM1 End of Message1 (monitorchannel)

MON1 has received an end of message.

XAB1 MonitorTransmit ABORT

The received byte has not been detectedin two successiveframes.

MON1 has sent an ABORT (A bit) to

the remote transmitter.

ISTA0

InterruptStatus Register 0

AfterRESET 10H

RME RPF RFO XPR XDU EXI2 EXI1 0

RME

ReceiveMessage End

One complete frame of length less than

or equal to 32 bytes, or the last part of

a frame of length greater than 32 bytes

is stored in the RFIFO.

RPF ReceivePool Full

32 bytes of a frame are in RFIFO. The

frame is not yet completelyreceived.

RFO ReceiveFrame Overflow

A complete frame was lost because no

storage space was available in the

RFIFO.

XPR Transmit Pool Ready

One data block (32 bytes max) may be

RMR1 ReceiveMonitor Register1 ready

A byte has been received in register

MONR1.

RAB1 ReceiveAbort

MON1 received an ABORT from the remote receiver.

XMR1 Transmit Monitor Register 1 ready

A byte can be stored in register

MONX1

ISTA2

InterruptStatus Register 2

After RESET 01H

(GCI and TE modeonly)

0 0 CIC2 EOM2 XAB2 RMR2 RAB2 XMR2

CIC2 Command/IndicateChange

A change in the value of CIR2 is detected.

7/34

Page 8

ST5451

EOM2 End of Message2 (monitor channel)

MON2 has received an end of message.

XAB2 Monitor Transmit ABORT

The received byte has not been detectedin two successive frames.

MON2 has sent an ABORT (A bit) to

the remote transmitter.

RMR2 Receive Monitor Register2 ready

A byte has been received in register

MONR2.

RAB2 ReceiveABORT

MON2 received an ABORT from the remotereceiver.

XMR2 TransmitMonitor Register 2 ready

A byte can be stored in register

MONX2.

MASK0, MASK1, MASK2

After Reset FF; the three mask registers MASK0,

MASK1, MASK2 are associated respectively to

the three interrupt registers ISTA0, ISTA1,and

ISTA2.

Each interrupt source in ISTA registerscan be selectively masked by setting to ”1” the corresponding bit in MASK1. Interrupt sources (masked or

not) are indicated when ISTA is read by the microprocessor. When an interrupt source is not

masked, INT goes low.

STAR Status Register

AfterReset 48H

XDOV XFW IDLE RLA DCIO 0 0 0

XDOV TransmitData Overflow

More than 32 bytes have been written

into the XFIFO.

XFW XFIFOWrite enable

Data can be entered into the XFIFO.

IDLE IDLE State

15 or more consecutive ones have

been detectedon the input data line.

RLA Receive Line Active

Frames or interframe flags are being

received

DCIO D and C/I Channels are occupied

CMDR CommandRegister

After Reset 00

XHF XME RMC RMD RHR XRES M2RES M1RES

XHF HDLCframe transmission can start.

XME Transmit MessageEnd

The last part of the frame was entered

in XFIFOand can be sent.

RMC Receive Message Complete

Reaction to RPF or RME interrupt. The

received frame (or one pool of data)

has been read and the corresponding

RFIFOis free.

RMD Receive Message Delete

Reaction to RPF or RME interrupt. The

entire frame will be ignored. The part of

frame already stored is deleted.

RHR Reset HDLC receiver

XRES Reset HDLC transmitter

XFIFO is cleared and the transmitted

frame (if any) is aborted.

M2RES Monitor2 Reset

Reset MONITOR and C/I channels (TX

and RX).

M1RES Monitor1 Reset

Reset MONITOR and C/I channels (TX

and RX).

* For the four first bits (XHF, XME, RMC,

RMD), the reset is done by the device;

the other bits level sensitive

MODE HDLC Mode Register

After Reset 00

DMA FL1 FL0 ITF RAC CAC NHF FLA

DMA DMA Interfaceactivation

FL1/0 Frame Length

Minimum framelength accepted

FL1 FL0

3 bytes

4 bytes

5 bytes

6 bytes

0

0

1

1

0

1

0

1

ITF InterframeTimeFill

ITF= 1 : Flags are transmitted

ITF= 0 : IDLE is transmitted

8/34

RAC RAC=1 : ActivateRX

RAC= 0 : deactivateRX

Page 9

ST5451

CAC ChannelActivation

CAC= 1 : Activate RX and TX

CAC= 0 : deactivate RX and TX

NHF HDLC Function Select

NHF = 1 :disable HDLC function

FLA Flag

FLA = 1 : transmitshared flags

FLA = 0 : transmittwo flags between

consecutiveframes.

RFBC ReceiveFrame Byte Counter

Afterreset 00

RDC7 RDC6 RDC5 RDC4 RDC3 RDC2 RDC1 RDC0

RDC 0/7 ReceiveData Count

Total number of bytes of received

frame without CRC.

RDC 0/4 Indicate the number of bytesin the cur-

rent block available in RFIFO.

RDC 5/7 Indicate the number of 32 bytes blocks

received. If the frame exceeds 223

bytes, RDC 5/7 hold the value ”111”,

only RDC 4/0 continueto count modulo

32.

See Table3.

The contents of the register are valid after an

RME interrupt. The µP must read N+1 bytes to

transfer the number of bytes received and the

status byte into the memory.

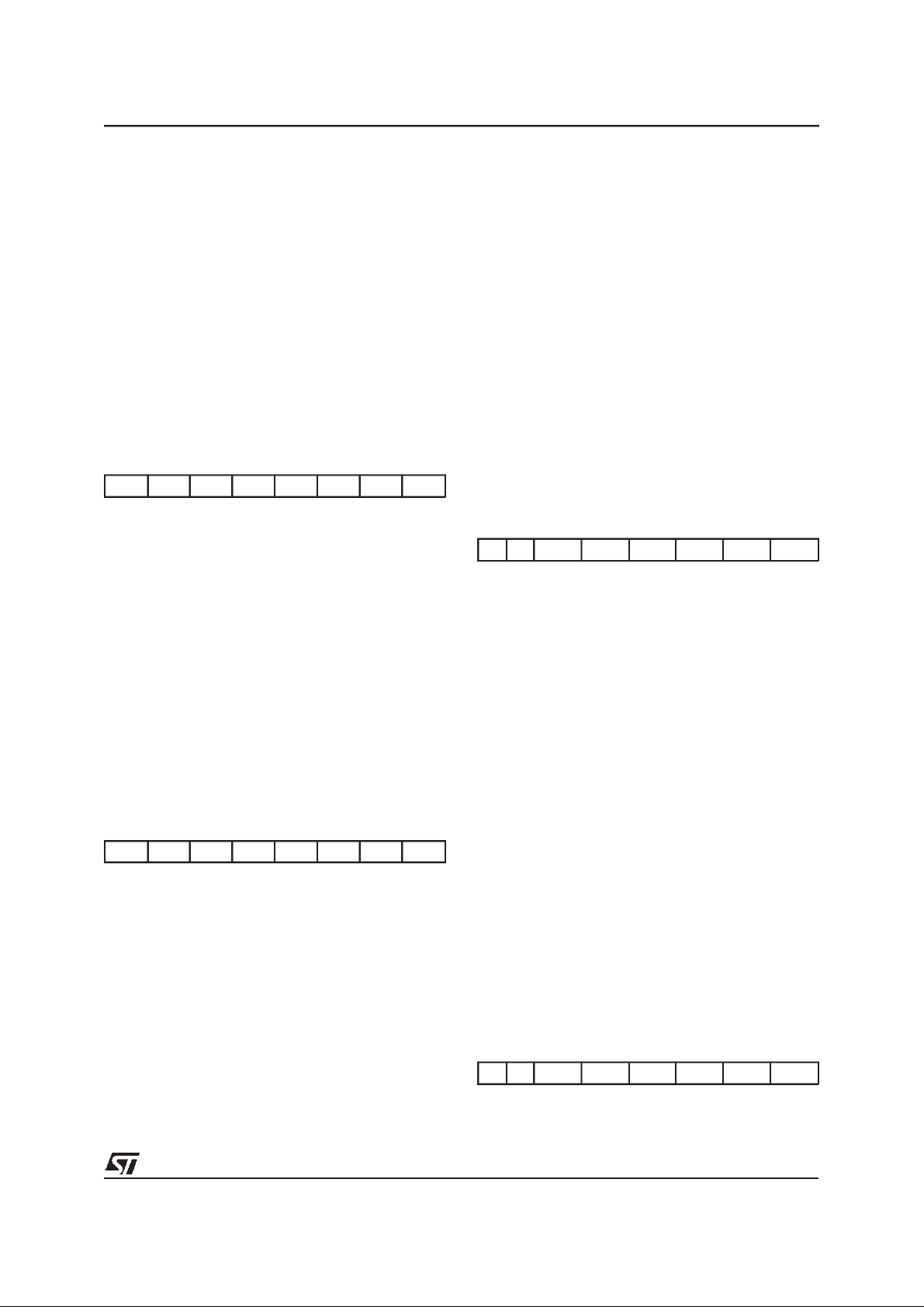

MONX1 Monitor Transmit Register 1

After reset FFH

(GCI only)

M1 M2 M3 M4 M5 M6 M7 M8

The value written in MONX1 is transmitted in the outgoing Monitor channel

according to GCI transfer protocol.

XMR1 interrupt indicates when MONX1

is again available.

MONR1

MonitorReceive Register 1

After reset FFH

(GCI only)

M1 M2 M3 M4 M5 M6 M7 M8

The value read from MONR1 gives the

value of the byte received in the monitor channel according to GCI transfer

protocol. RMR1 interrupt indicates

when a new byte is available in

MONR1register.

CIX2 Command/IndicateTransmitRegister 2

After Reset FFH

(GCI and TE modeonly)

1 1 P1 P2 P3 P4 P5 P6

P1/P6 Code transmitted permanently in the

2nd GCI C/I channel.

CIX1 Command/IndicateTransmitRegister1

Afterreset FFH

(GCIonly)

1 1 1 1 C1C2C3C4

C1, C2, C3, C4:

Code to be transmitted permanently

in the outgoing GCI C/I channel.

CIR1

Command/IndicateReceiveRegister 1

Afterreset FFH

(GCIonly)

1 1 1 1 C1C2C3C4

C1, C2, C3, C4:

Incoming GCI C/I channel.

CIR2 Command/IndicateReceive Register 2

After reset FFH

(GCI and TE modeselected only)

1 1 P1 P2 P3 P4 P5 P6

P1/P6 The contents of the 2nd C/I channel;

they are the different requests received

from TE peripheral devicesto µP.

Six peripherals can make a simultaneous request.

MONX2

MonitorTransmit Register 2

After reset FFH

(GCI and TE modeonly)

The value written in MONX2 is transmitted in the 2nd GCI M channel to a

peripheral(if PI= 1; registerCF).

9/34

Page 10

ST5451

TABLE 3

N (number of bytes in the

frame received without CRC)

Nnmn

1 Min 000 00001 0

2 000 00010 0

3 000 00011 0

30 000 11110 0

31 000 11111 0

32 001 00000 1

33 001 00001 1

62 001 11110 1

63 001 11111 1

64 010 00000 2

222 110 11110 6

223 110 11111 6

224 111 11111 7

256 111 00000 7

257 111 00001 7

- 111 - 7

Counter n (number of 32 bytes blocks

765 43210

received )

MONR2

Monitor ReceiveRegister 2

Afterreset FFH

(GCIand TE mode only)

The value read from MONR2 gives the

value of the byte received from M

channel in 2nd GCI channel.

TSR Time Slot Register

Afterreset 00

TSR7 TSR6 TSR5 TSR4 TSR3 TSR2 TSR1 TSR0

In GCI mode (MDS1= 1 in CF Register)

a) CCS=1in CFReg. (64 Kbit/s)

Then: TSR2 indicatesB1 or B2

TSR4/7indicate positionof

GCI channel

b) CCS=0in CF Reg. (16 Kbit/s)

Then: TSR4/7indicate positionof

GCI and its D channel

In Multiplexed Mode

(MDS1=0in CF Register)

a) CCS=1 in CF Reg. (64 Kbit/s)

Then: TSR2/7 indicatechannel

positionin the 64 timeslots

multiplex

b) CCS=0 in CF Reg. (16 Kbit/s)

Then: TSR0/7 indicatechannel

positionin the 256 timeslots

multiplex.

CA ConfigurationnRegister A

After reset 00

CA7 CA6 CA5 CA4 CA3 CA2 CA1 CA0

CA0 SAPI 0 is recognized CA0 = 1

CA1 SAPI 63 CA1 = 1

CA2 SAPI x CA2 = 1

CA3 SAPI y CA3 = 1

CA4 TEI 127 CA4 = 1

CA5 TEI z CA5 = 1

CA6 TEI t CA6 = 1

CA7 Address filter active CA7 = 1

CB ConfigurationregisterB

After reset 00

Contentof CBindicate SAPI x value

HighOrder 6 Bits

SAPI 0 0

CC ConfigurationRegister C

After reset 00

Contentof CCindicate SAPI y value

HighOrder 6 Bits

SAPI 0 0

10/34

Page 11

ST5451

CD ConfigurationRegister D

Afterreset 00

Contentof CD indicateTEI z value.

7 High Order Bits

TEI 0

CE ConfigurationRegisterE

Afterreset 00

Contentof CE indicateTEI t value.

7 High Order Bits

TEI 0

CF Configuration RegisterF

After00

TE MAS/SSC CCS CMS/SC PI VZDOUT MDS1 MDS0

TE TE mode

TE = 1 : the frame is constitued by

three GCI channels (GCI-SCIT)

MAS/SSCIf CCS= 0, TE = 1, MDS0and MDS1= 1

(i.e. GCI mode, TE mode, 16 Kbit/s)

MAS/SScis MAS and:

MAS = 0 means ”Slave device”

MAS = 1 means ”Master device”

If SC = 1 (i.e. a sub-channel is selected)MAS/SSC is SSC; if 16Kb is selected SSC chooses between first on

second bit of the stream while, if 64Kb

is selected SSC chooses between first

or last seven bits of the stream (see

TABLE 2 and CMS/SC)

CCS ChannelCapacity Selection

CCS= 1: 64 Kb/s

CCS= 0: 16 Kb/s.

CMS/SC If CCS= 0, TE= 1,MDS0andMDS1= 1

(i.e. GCI mode, TE mode, 16Kbit/s)

CMS/SC is CMS (Contention mode selection)and:

CMS = 1 means ”D and C/I channel

accessprocedure active”

CMS = 0 means ”D and C/Z channel

accessprocedure active”

If CCS = 1 and TE = 1 CMS/SC is SC

(Subchannel)and:

SC = 0 means ”16Kbit/sor 64Kbit/sis

used”

SC = 1 means ”an 8Kbit/s or 56Kbit/s

subchannelinside a 16Kbit/sor

64kbit/sisused”(seeMAS/SSC)

PI PeripheralInterface (only if TE=1)

PI = 1: CIX2, CIR2, MONX2, MONR2,

active

VZDOUT When level 1 device is inactive (i.e.

CIR1 = DI = 1111) and GCI has to be

wakenup (i.e. TIM = 0000 in CIX1),

DOUT is set to zero requiring FS

and CLK if VZ DOUT=1.

MDS1 Mode Bit 1

MDS1 = 1:GCImode

MDS1 = 0: Multiplexed mode

MDS0 Mode Bit 0

MDS0 = 1: Multiplexer and Demultiplexer are active.

MDS=0No multiplexer.

CCR ConfigurationRegister 00

After reset 00

TLP ADDR AD3 AD2 AD1 AD0 CRS TRI

TLP Test Loop

TLP = 1: The transmitter is internally

connected to the receiver; the transmit

output is not activated.The digital interface must be activated to provide the

bit clock and frame Synchro.

ADDR Address Recognized

If TE= 1 and PI = 1

ADDR = 1: The first byte received in

MONR2 is compared with AD0/3. If

equal the message is accepted, otherwise is ignored.

ADDR = 0: The message is always accepted.

AD0/3 When PI = 1, is the component ad-

dress.

AD0/2 Address bit used to access D and C/I

channels (TE = CMS =1, CCS = 0).

CRS ClockRate Selection

CRS = 1: Clock frequency is twice the

data rate (GCI).

CRS = 0: Clock frequency and data

rate are identical.

TRI Tristate

TRI = 1: DOUT in tristate

TRI = 0: DOUT in open drain.

11/34

Page 12

ST5451

4 - WORKING PROCEDURES

4 - 1 - RECEIVE FRAME

Recognized frame (by means of SAPI and/or TEI

identification), having a minimum length is stored

in the RFIFO with all bytes between the opening

flag and CRC field.

When the frame is less than or equal to 32 bytes,

is transferred in one block, and just after the receiving completion interrupt (RME), a status byte

is appended at the end. The frame and its status

byte remain stored until

µP acknowledgement

(RMC).

When the frame is longerthan 32 bytes,blocks of

32 bytes plus one remainder block of lenght 1 to

32 are transferred to the microprocessor. The receiving 32 byte block generates a RPF interrupt

and the data in RFIFO remains valid until µPacknowledgement(RMC).

µP can ignore a received frame by meaning

The

RMD (Receive Memory Delete), reaction to RPF

or RME. The part of frame already stored is de-

Figure 1:

Receivingof an HDCL frame

leted and the remainder frame is ignored by the

HDLCController.

The last block of the frame generates the RME interrupt.

RFBC register bits 0 to 4 indicate the number of

bytes currently stored in the RFIFO. Bits 5 to 7 indicate the total number of 32 byte blocks already

received. Bits 5 to 7 do not overflow. When the

counter status 7 has been reached, it indicates a

frame length greater than 223 bytes (see Table

3).

RFBC register is valid only after the RME inter-

rupt and remains valid until RMC acknowledgement by µP.

At each read access by the µP, RFBC 5/7 bits remain unchanged,RFBC 0/4 bits are decreasedto

reachvalue 0 when the whole block is read.

Interrupts are queued inside the device. They are

sent one by one to the microprocessor after each

acknowledgement RMC. If a frame is lost because the RFIFO was full, a RFO interrupt is generated.

12/34

Page 13

ST5451

4- 2 - TRANSMITFRAME

After polling bit XFW or after a XPR interrupt, up

to 32 bytes may be stored in XFIFO. Transmission begins after that XHF command is issued by

µP. ST5451 will request another data block by an

XPR interrupt if the XFIFO contains less than 32

bytes.

When XME is set, all remaining XFIFO bytes are

Figure 2:

Transmissionof an HDCL frame

transmitted,the CRC field and the closing flag are

added. The HDLC controller then generates a

new XPR interrupt.

If the XFIFO becomes empty while XME command has not been set, an abort sequence is

generated, followed by interframe time fill and

XDUinterrupt is generated.

A frame may be aborted by XRES command as

well.

13/34

Page 14

ST5451

4 - 3 - COMMAND/INDICATEPROCEDURE

The exchange of information in the C/I channel

runs as follows:

The two circuits (i.e. ST5421 and ST5451) connected on the GCI interface send one each other

a permanentfourbit commandcode in C/I field.

RECEIVEC/I

The ST5451stores on every frame the fourbits of

C/I channel coming from level 1 circuit in a first

register CIR. This value is compared with the previous one. If a one new appears during two consecutive frames, this new value is loadedin register CIR1 and a CIC1 interruptis generated.

TRANSMITC/I

The transmit register CIX1 can be written at any

time by the µP. Its content is continuouslysent in

the C/I channel.

Note: The TIM command (0000) forces a low

level on DOUT, if CIR1 = DI (1111) when VZ

DOUT = 1 torequire FS and CLK.

4 - 4 - MONITOR CHANNEL

The GCI Monitor channel procedure allows full

duplex data transmission with acknowledgement

using A bit.

MESSAGERECEIVING

An interrupt (bit RMR1 in ISTA1 register) is gen-

erated when a new byte is available in register

MONR1.

ST5451 generates an interrupt bit (XAB1 in

ISTA1) if it does not read twice the same bytes

meanwhile sending an ABORT to the remote

transmitter.

It performs an interrupt (EOM in ISTA1) also

when it has received an End Of Message. Acknowledgementto remotetransmitter is sent if:

- the byte was receivedtwice with the same value

- the microprocessor reads the previous byte

stored in registerMONR1.

This procedure performs flow control between S

interfacedevice and µP.

MESSAGETRANSMISSION

ST5451generates an interrupt (XMR1 in ISTA1)

when register MONX1 is available.

Writing register MONX1/0 generates a message

transmission. When the last byte is stored in the

register MONX1/1, ST5451 sends the End of

Message to remote receiver. If an Abort is received, one interrupt (RAB1) is generated.

4 - 5 - M’ and C/I’ CHANNELS

The procedure allows a full duplex data transmis-

sion between microprocessor and the peripheral

devices connected on C/I’ local and M’ channel

throughGCI-SCIT channel 1.

ReceiveInterrupt on C/I’ (DOUT is aninput).

A new value on C/I’ indicates to ST5451 master

that one device in the terminal wants to send a

message. Up to six peripherals may generate

suchan interruptto themicroprocessor.

ST5451 writes at every frame the six bits of C/I’

channel coming from peripherals in registerCIR’.

This value is comparedwith the previous one and

if a new one appears during two consecutive

frames,is loaded in register CIR2 and CIC2 interrupt (ISTA2 register)is generated.

µP may send a messageon M’ channel (DIN becomes an output)to allow the peripheral deviceto

transmit.

MESSAGETRANSMISSIONON M’ CHANNEL

ST5451 sets interrupt XMR2 (ISTA2 register) if

register MONX2/0 is available. Writing MONX2/0

generates a message transmission. When the

last byte is stored in register MONX2/1,

ST5451sends End of Message to remote peripheral.

If an ABORT is received, interrupt RAB2 (ISTA2

register) is issued. Then microprocessor may

send its message again.

MESSAGERECEPTIONON M’ CHANNEL

Interrupt bit RMR2 (ISTA2 register) is generated

when a newbyte is available in MONR2register.

ST5451 sets interrupt bit XAB2 (ISTA2 register) if

it does not read twice the same byte; in thiscase,

it sends an ABORT to remote peripheral.

The controller generates interrupt bit EOM2

(ISTA2 register) when End Of Message is received.

4 - 6 - ACCESS PROCEDURE TO D AND C/I

CHANNELS(GCI and TE mode selected only)

Up to eight HDLC controllers may be connected

to D channel and C/I channel. A contention resolution mechanism is used if bit CMS (Contention

ModeSelection) is set.

The mechanism allows to give an access without

losing data.

An access request may be generated, if CIX1

(Command/Indicate Register 1) contains a different code fromDI (1111).During the procedure,M

channel (with A and E bits) may be used. On input DIN, the GCI controller checks the CMS4 bit

(CMSchannel- ThirdGCI channel)(see Fig. 4).

CMS4 indicates the status of C/I and D channels

CMS4= 1 ”channels free”; CMS4= 0 channelsoccupied.

If the channels are free, the HDLC controller

starts transmitting its individual address AD2 on

CMS1, AD1 on CMS2, AD0 on CMS3. If an erroneous address is detected, the procedure is terminatedimmediately. If the complete address can

be read without error, the D and C/I channels are

occupied: the ST5451 transmits CMS4 = 0: The

HDLC controller which has the lowest address

has priorityover the others.

The access request is withdrawn if the HDLC

controllertransmits code DI = 1111. the CMS4 bit

(CMSfield) is set.

14/34

Page 15

Figure 3: GCI-SCITFrame Timing

ST5451

Figure 4:

GCI-SCITChannels Timing

15/34

Page 16

ST5451

4 - 7 - DMA ACCESS

The HDLC controller has a DMA interface which

is activated by DMA bit in MODE register.The

DMA interface is available only when multiplexed

bus is selected.

ST 5451 asserts DMA REQR or DMA REQX to

request an exchangeof bytes between the FIFOS

and the externalmemory.

The external DMA controller asserts DMA ACKR

or DMA ACKX to access the FIFOS.

These signals are equivalent to E/DS/RD functions.

During DMA access, CS/CE pin must be inactive;

AS andE/DS/RD signals can be present.

Outside DMA Access, all registers are accessible

Figure 5: D and C/I channelsAccess Procedure

by the µP except the FIFOS.

FRAMERECEPTION:

When one block has been stored in RFIFO,DMA

REQ R pin goeslow and RPF (or RME) interrupts

the µP. The DMA controller reads the RFIFO. After the RME interrupt, the frame length will be

available in RFBC register. The block is acknowledgedby RMC command.

FRAMETRANSMISSION:

When a 32 byte block is free in XFIFO, DMA request goes low and XPR interrupts the µP. The

DMA controller can write data in the XFIFO. At

the end of the frame, the µP send XME to HDLC

controller; CRC and closing flag will be sent by

the HDLC controller.

16/34

Page 17

ST5451

4 - 8 - INTERRUPT PROCEDURE

4 - 8 - 1 - HDLC CHANNELS

4 - 8 - 1 - 1 - RECEIVEDIRECTION

RRE and RPF interrupts

RPF bit (register ISTA0) set high to indicate the

HDLC controller has received a block of 32 bytes

which is not a completemessage.

This bit remains high until it is erased by the microprocessor.

As for each bit of ISTA0 register, except the extension bits of ISTA1 and ISTA2 (EXI1, EXI2), the

way to erase RPF is to write a ”0” at its location

and to write a ”1” at the location of the others (for

example 7FH into ISTA0 to erase RME). The

processingorder is:

- put Mask0 on ISTA0 (if Mask Off)

- (Read FIFOR) X 32

- Write ISTA0 to erase RPF (BFH)

- Write RMC to ”1” forasking for another block

of the frame

(NB: RMC, RMD are automatically erased

by the controller)

- Remove Mask0

RME bit (register ISTA0) set high to indicate the

HDLC controller has received a shortframe or the

last block of a large frame. The message is now

complete, the bit remains high until it is erased by

the microprocessor.The processingorder is:

- put Mask0 on ISTA0 (if upper level Mask Off)

- Read RFBC with a mask on the 3 most significant bits, to know the number ”N” of

transfersto do

- (Read FIFOR) x N for data

- Read FIFOR for status on the frame

- Write ISTA0 to erase RME (7FH)

- Write RMC or RMD to ”1” for asking for another frame.

RF0 interrupts

RF0 is a bit of the interrupt register ISTA0 set

high to indicate an overflow of the receive FIFO

has been detected, either because more than 8

frames cannot be stored or because more than

64 bytes can’t be stored. This information is also

stored into the status of the concerned frame

(RDO).

The processing order of the microprocessoris:

- Looking for RPF and RME bits and pop - up

the frames. Then look for the status and

throw down the frame concerned.In general

case, only one frame is lost.

4 - 8 - 1 - 2 - TRANSMIT DIRECTION

XPR Interrupt

XPR is a bit of the interrupt register ISTA0 coming

high to indicate HDLC controller has a free block

of 32 bytes. This bit remains high until the micro-

processor write a byte into the block and erase

this bit into ISTA0; if another block is free, XPR

get high again immediately.

The processing order of the microprocessor is in

non DMA Mode:

- Put Mask0on ISTA0 (if upper level Mask Off)

- Write at least one byte into FIFOX

- Write ISTA0 to erase XPR

- Write XHF to ”1” for launching the transmit

operation of block (a block is not necessarily

32 bytes)

or write XME to ”1” for launching the transmit of a short frame or of the last part of a

frame

- Remove masks

In DMA Mode two general cases are possible:

1) The external DMA controller works by ”pages”

less or equal to 32 bytes. The ”process” of the

DMAC is a short frame transmission and the

processor must give an XME at the end of the

DMAC process(refer to figure 2).

2) The DMA controller works by ”pages” of more

than 32 bytes. It’s process is the transfer of the

wholeframe.

The circuit doesn’t need an XHF at the end of an

intermediate 32 byte block; since it has reached

32 bytes written into the current fifo, it begins the

transferand toggles on thesecond fifo as soon as

the first is full. (At this moment an XME is possible if the 32

case 1) and then, a 33

nd

byte was the end of the frame -

rd

write operation into the

fifo generates an internal XHF and the frame followingblocks are expected.

- In the two cases the flow control is done between DMAC and ST5451 by the way of

REQX and ACKX signals

The processingorder is:

- Put Mask0

- Give order to DMAC to begin transfer

- Wait for DMAC end of process

- Write ISTA to erase on XPR

- Write XME to signal the end of the frame to

the ST5451 (otherwise the ST5451 will put

”underrun” interrupt, as soon as its two

blocks are free).

XDU Interrupt

XDU is a bit of the interrupt register ISTA0 coming high to indicate HDLC controller has detected

an underrun (a frame is being transmitted and no

more bytesare available into the FIFO).

The HDLC controller finish the frame by transmitting an ”Abort” and no more data can be transmitted even in NHF mode. To be sure XDU is seen

by the MIcroprocessor, XDU interrupt bit must be

erased in ISTA0 in addition of XRES security procedure

The transmit control is frozen and the only way to

reinitializea transmitsession is to writean XRES,

after erasingXDU.

17/34

Page 18

ST5451

4 - 8 - 2 - M CHANNELS INTERRUPTS EOM,

RMR, XMR, RAB

Receive Direction

RMR 1/2 is a bit of interrupt register ISTA 1/2

coming high to indicate the M (or M’) channel

controller has received a valid byte on receiving

channel (two identical consecutivebytes).

The microprocessorprocessing orderis;

1. ErasingRMR 1/2 interrupt into ISTA 1/2

2. Read MONR 1/2 register.

This order can’t be inverted because, as long as

MONR isn’t read, the receive state machine is

locked in wait state, a new byte can’t be acknowledged and so, a new interrupt can’t be done.

More, if MONR is read first, the receive state machine is ready for receiving a new byte and create

another interrupt. So, if the interrupt bit corresponding to the previous frame isn’t erased before a new byte arrives, this byte won’t be seen

(the microprocessor won’t be informed) and the

controllerwill be locked waitingfor MONR read.

XAB 1/2 is a bit of the interrupt register coming

high to indicate the receive controller has detected an abort (two conscutive bytes not identical) as long as this interrupt isn’t erased, the receiver is locked in wait state.

EOM 1/2 is a bit of the interrupt register coming

high to indicate the receive controller has detected an end of message. As long as the interrupt isn’t erased, the receiver is locked in wait

state.

TransmitDirection

XMR 1/2 is a bit of the interrupt register coming

high to indicate a byte can be writteninto MONX.

The processing order is:

1. ErasingXMR bit

2. Writinga new byte into MONX.

If this order is inverted, the new byte will be trans-

mitted and a new XMR may be erasedbefore being seenby themicroprocessor.

RAB 1/2 is a bit of the interrupt register coming

high to indicate the remote receiver has reported

an abortdetection.The processing order is:

1. ErasingRAB bit

2. ErasingXMR bit

3. Writinga new byte into MONX.

If a write operation of the new byte is done before

the RAB erasing, the byte will be lost and the

transmitterwill staywaiting for it.

4 - 8 - 3 - CI CHANNEL INTERRUPTS

CIC 1/2 is a bit of ISTA 1/2 interrupt register com-

ing high to indicate a valid byte has been detected by the command indicate receive controller, and readable into CIR 1/2 register. The

processingorder is:

1. Erasing CIC bit

2. Reading CIR register.

If this order is inverted, a next byte may be un-

seen by the microprocessor. It is recommended

to work with ”Ping Pong” protocol on CI channels,

as non flow control is done.

4 - 9 - SOFTWARERESET PROCEDURES

4 - 9 - 1 - XRES (Transmit Direction)

XRES is a level sensitive command of CMDR

whichinitialize the transmit process.

- XPR interrupt bit is erased

- XDU interrupt bit is not erased (security procedure)

- All data in FIFOs are lost

- After an XRES, the microprocessormust wait

for an XPR before writing new data.

The processingorder is:

- Writing a ”1” into XRES (CMDR)

- Writing a ”0” into XRES (CMDR)

- Read ISTA0 waiting XPR or enable XPR interrupt

4 - 9 - 2 - RHR(Receive Direction)

RHR is a level sensitive command of CMDR,

whichreinitialize the receiveprocess.

- RME, RPF bits are erased

- RFO bit is erased

- All frames in FIFO R are lost

- If RHR is released (got down) at the time a

frame is on line, the HDLC controller waits

for a flag.

4 - 9 - 3 - M1RES,M2RES M/CI channels

MRES is a level sensitive command of CMDR

which initialize the M/CI channelprotocole in both

directions.

XMR, RAB, RMR, CIC, XAB, EOM bits are

erasedby MRES.

After a clock programming (bit CRS), it’s necessary to put MRES bit to initialize properly the M

protocol.

18/34

Page 19

ST5451

TYPICALAPPLICATIONS

ST5451 HDLC controller may be used in TE,

NT2, NT12or LT.

Figures 6 to 8 illustrate three typical applications

in multifunctionalTE.

The D channel containing only signalling is processed by the LAPD controller and routed via a

parallel µP interface to the terminal processor.

The support of the LAPD protocol which is implemented by the HDLC controller device allows in

cost senstive applications the use of a low cost

microprocessor.See fig. 6.

Fig. 7 illustrates a configuration in which the D

channel containing signalling data (SAPI s) as

well as packet switched data (SAPI p) is processed by two controllers and two independentmicroprocessors.

Fig. 8 illustrates a configuration in which one microprocessoris connected to two controllers via a

DMA controller.

D channelwith LAPD signalling data and B chan-

Figure 6: Low cost GCI terminal application

nel LAPBpacket data are processed by the same

µP. A DMA controller performs device to memory

transfers.It is a typical work station application.

Fig. 9 and 10 illustrate 2 typical applications in

NT2 or exchange.

An NT2 or LT in fig.9 with eight D channelcontrollers connected to the GCI interface handle subscriber 0 to 7. Any GCI compatible transceiver (S

or U) may be used to do the subscriberline interface; a GCI compatible exchange circuit may implement the system interface. This is one decentralizedapplication.

Fig. 10 illustrates a centralized application. Using

a switching net work, it is possibleto connect:

up to thirty two 64 Kbit/s channels on a 2 Mb/s

PCM highway to 32 B channelcontrollers

up to sixty four 64 Kbit/s channels on a 4 Mb/s

PCM highway to 64 B channelcontrollers

up to two hundred fifty six D channelson a 4 Mb/s

highway to 256 D channelcontrollers.

S - INT

19/34

Page 20

ST5451

Figure 7: LAPBand LAPD protocol on the same D channel handlended with 2 differentµPs

S - INT

Figure 8: LAPBand LAPD protocol handlingan B and D channel

S - INT

20/34

Page 21

FIgure 9: DecentralizedD channel handling in NT2 or LT

ST5451

Figure 10:

CentralizedD channel handling in NT2 or LT

21/34

Page 22

ST5451

Figure 11: HDCLFrame Transmission Procedure

22/34

Page 23

Figure 12: HDCLFrame Transmission Procedurein D Channel

ST5451

23/34

Page 24

ST5451

Figure 13: SActivation and Deactivationprocedure

24/34

Page 25

ST5451

ELECTRICALCHARACTERISTICS

(T from 0 to 70°C, V

=5±0.25V).

DD

Symbol Parameter Test Condition Min. Typ. Max. Unit

Supply Current CLK Freq. = 4MHz

I

S

CLK Freq. = 2MHz

NO CLK Freq.

–

–

–

20

4

2

–

4

300

STATIC CHARACTERISTICS - GCI INTERFACE(T from 0 to 70°C, VDD=5± 0.25V).

Symbol Parameter Condition Min. Max. Unit

VIH High Level Input Voltage Maximum leakage current : ± 10

VIL Low LevelInput Voltage Maximum leakage current : ± 10

VOH High Level Output Voltage IOH = -0,4

µA 2,4 V

VOL Low Level Output Voltage IOL = 2mA 0,45 V

VOL Low Level Output Voltage

D

OUT.Din

. INT

IOL = 7mA 0,45 V

C Input/Output Capacity 10 pF

C

Load Capacity DIN/DOUT 150 pF

OUT

Load Capacity INT 150 pF

Load Capacity AD0/7 100 pF

µA 2.4 VDD+0,4 V

µA VSS-0,4 0,8 V

mA

mA

µA

DYNAMICELECTRICAL CHARACTERISTICS- GCIInterface

Symbol Parameter Min. Typ. Max. Unit

FSync 8 KHz 8 KHz

F

CLK

t

WCH

t

WCL

t

RC

t

t

HCF

t

SFC

t

DCD

t

DCZ

t

DFD

t

SDC

t

HDC

64 x nx FSync 1

Period of CLK High 80 ns

Period of CLK Low 80 ns

Rise Time of CLK 10 ns

Full Time of CLK 10 ns

FC

Hold Time: CLK - FS 0 ns

Set-up Time: FS - CLK 30 ns

Delay Time: CLK High to datavalid. out: 150 pF 80 ns

Delay Time: to Data Disabled 0 80 ns

Delay Time: FSync. High to data valid. count: 150 pF. Applies

only if Sync rises later than CLK raising edge.

Set-up Time: Data valid to CLK receive edge. 30 ns

Hold Time: CLK low to data invalid. 30 ns

8 512 4096 KHz

≤ n ≤

80 ns

25/34

Page 26

ST5451

DYNAMICELECTRICAL CHARACTERISTICS- Double Clock Interface

Symbol Parameter Min. Typ. Max. Unit

FSync 8 KHz 8 KHz

F

t

WCH

t

WCL

t

t

t

HCF

t

SFC

t

DCD

t

DCZ

t

DFD

t

SDC

t

HDC

16 x nx FSync 1

CLK

Period of CLK High 50 ns

Period of CLK Low 50 ns

Rise Time of CLK 10 ns

RC

Full Time of CLK 10 ns

FC

Hold Time: CLK - FS 0 ns

Set-up Time: FS - CLK 30 ns

Delay Time: CLK High to datavalid. out: 150 pF 80 ns

Delay Time: to Data Disabled 0 80 ns

Delay Time: FSync. High to data valid. count: 150 pF. Applies

only if Sync rises later than CLK raising edge.

Set-up Time: Data valid to CLK receive edge. 30 ns

Hold Time: CLK low to data invalid. 30 ns

ELECTRICALCHARACTERISTICS - SingleClock Interface

Symbol Parameter Min. Typ. Max. Unit

FSync 8 KHz 8 KHz

F

t

WCH

t

WCL

t

t

t

HCF

t

SFC

t

DCD

t

DCZ

t

DFD

t

SDC

t

HDC

8 x n x FSync 1

CLK

Period of CLK High 80 ns

Period of CLK Low 80 ns

Rise Time of CLK 10 ns

RC

Full Time of CLK 10 ns

FC

Hold Time: CLK - FS 0 ns

Set-up Time: FS - CLK 100 ns

Delay Time: CLK High to datavalid. out: 150 pF 80 ns

Delay Time: to Data Disabled 0 80 ns

Delay Time: FSync. High to data valid. count: 150 pF. Applies

only if Sync rises later than CLK raising edge.

Set-up Time: Data valid to CLK receive edge. 30 ns

Hold Time: CLK low to data invalid. 30 ns

64 128 8192 KHz

≤ n ≤

80 ns

64 64 4096 KHz

≤ n ≤

80 ns

26/34

Page 27

ST5451

Figure 14:

GCITiming

Figure 15:

SingleClock Diagram

27/34

Page 28

ST5451

Figure 16:

Non-multiplexedµPbus timing

READ CYCLE (Non-multiplexed mode)

Symbol Parameter Min. Max. Unit

t

EAH

t

EAH

t

AES

t

AES

t

ACC

t

t

Address Hold After E 10 ns

R/W Hold After E 10 ns

Address to E Setup 20 ns

R/W to E. Setup 20 ns

Data Delay from E 110 ns

Output Float Delay 25 ns

DF

Minimum Widthof E 110 ns

WE

WRITE CYCLE(Non-multiplexed mode)

Symbol Parameter Min. Max. Unit

t

EAH

t

EAH

t

AES

t

AES

t

DES

t

EDH

t

t

Address Hold After 10 ns

R/W Hold After E 10 ns

Address to E Setup 20 ns

R/W to E.CS Setup 20 ns

Data to End of E Setup 35 ns

End of E.CS to Data hold 10 ns

Minimum Widthof E 60 ns

WE

Minimum Widthof RESET 100 ns

RW

28/34

Page 29

ST5451

Figure 17:

MultiplexedIntel-likeµP bus timing

READ CYCLE (MultiplexedIntel Mode)

Symbol Parameter Min. Max. Unit

t

t

t

t

t

t

t

t

CSS

t

CSH

Address Hold After ALE 10 ns

LA

Address to ALE Setup 20 ns

AL

Data Delay from RD 110 ns

RD

RD Pulse Width 110 ns

RR

Output Float Delay 25 ns

DF

RD Control Interval 70 ns

RI

ALE Pulse Width 30 ns

WA

CE to RD or WR set-up t

CE hold after RD to WR t

CSS

CSH

20 ns

10 ns

WRITE CYCLE(Multiplexed Intel Mode)

Symbol Parameter Min. Max. Unit

WR Pulse Width 60 ns

ww

Data Setup to WR 35 ns

Data Hold after WR 10 ns

WR Control Interval 70 ns

WI

t

t

t

DW

WD

t

29/34

Page 30

ST5451

Figure 18:

MultiplexedMotorola-likeµP bus timing

Symbol Parameter Min. Max. Unit

t

WAS

t

WDS

t

ASDS

t

RWS

t

RWH

t

CSS

t

CSH

t

AAS

t

AAH

AS Pulse Width 30 ns

DS Pulse Width 110 ns

AS low to DS high 10 ns

RW to DS setup 20 ns

RW hold after DS 10 ns

CS to DS setup 20 ns

CS hold after DS 10 ns

Address to AS setup 20 ns

Address hold after AS 10 ns

READ CYCLE

Symbol Parameter Min. Max. Unit

t

t

Data Valid after DS 110 ns

DV

Output Flat Delay 25 ns

DF

WRITE CYCLE

Symbol Parameter Min. Max. Unit

t

DWS

t

DWH

Data to DS setup 35 ns

Data Hold after DS 10 ns

30/34

Page 31

DMA BUS TIMING (Reception Mode)

Symbol Parameter Min. Max. Unit

t

ACC

t

t

W

t

WAR

t

DRAR

Data Delay from ACKR 110 ns

Output Float Delay 25 ns

DF

AR Minimum width ACKR 110 ns

Minimum width ACKR 70 ns

REQR Delay from ACKR 80 ns

Figure 19: DMAframe receptiontiming

ST5451

Figure 20:

DMA BUS TIMING

DMAframe transmission timing

(TransmissionMode)

Symbol Parameter Min. Max. Unit

t

DAS

t

DAH

t

W

t

WAX

t

DRAX

Data Setup to ACKX 35 ns

Data Hold from ACKX 10 ns

AX Minimum width ACKX 60 ns

Minimum width ACKX 70 ns

REQX Delay from ACKX 80 ns

31/34

Page 32

ST5451

DEN TIMING

Symbol Parameter Min. Max. Unit

t

DRCS

t

DRCH

t

DFCS

t

DRCH

Figure 21: DENTiming

DEN setup toCLK 30 ns

DEN Hold from CLK 30 ns

DEN Setup to CLK 30 ns

DEN Hold from CLK 30 ns

32/34

Page 33

ST5451

DIM.

MIN. TYP. MAX. MIN. TYP. MAX.

A 2.65 0.104

a1 0.1 0.3 0.004 0.012

b 0.35 0.49 0.014 0.019

b1 0.23 0.32 0.009 0.013

C 0.5 0.020

c1 45° (typ.)

D 17.7 18.1 0.697 0.713

E 10 10.65 0.394 0.419

e 1.27 0.050

e3 16.51 0.65

F 7.4 7.6 0.291 0.299

L 0.4 1.27 0.016 0.050

S8°(max.)

mm inch

OUTLINE AND

MECHANICAL DATA

SO28

33/34

Page 34

ST5451

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is

granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are

subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products

are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

2000 STMicroelectronics – Printed in Italy– All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - HongKong - India - Italy - Japan - Malaysia - Malta - Morocco -

Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com

34/34

Loading...

Loading...