Page 1

®

ST52T430/E430

8-BIT INTELLIGENT CONTROLLER UNIT (ICU)

Memories

Up to 8 Kbytes EPROM/OTP

256 bytes of RAM

Readout Protection

Core

Register File Based Architecture

55 instru ctio ns

Hardware multiplication and division

Decision Processor for the implementation of

Fuzzy Logic algorithms

Clock and Power Supply

Up to 20 MHz clock frequency.

Power Saving features

Interrupts

6 interrupt vectors

Top Level External Interrupt (INT)

ST52T430/E43 0

Three Timer/PWMs, ADC, SCI

PRELIMINARY DATA SHE ET

Peripherals

3 Programmable 8-bit Timer/PWMs with internal

16-bit Prescaler featuring:

– PWM output

– Input capture

– Output Compare

– Pulse Generator mode

Watchdog timer

On-chip 8-bit Sample and Hold A/D Converter

with 8-channel analog multiplexer

Serial Communication Interface with

asynchronous protocol (UART)

I/O Ports

23 I/O PINs configurable in Input and Output

mode

High current sink/source in all pins.

Development tools

High level Software tools

Emulator

Low cost Programmer

Gang Programmer

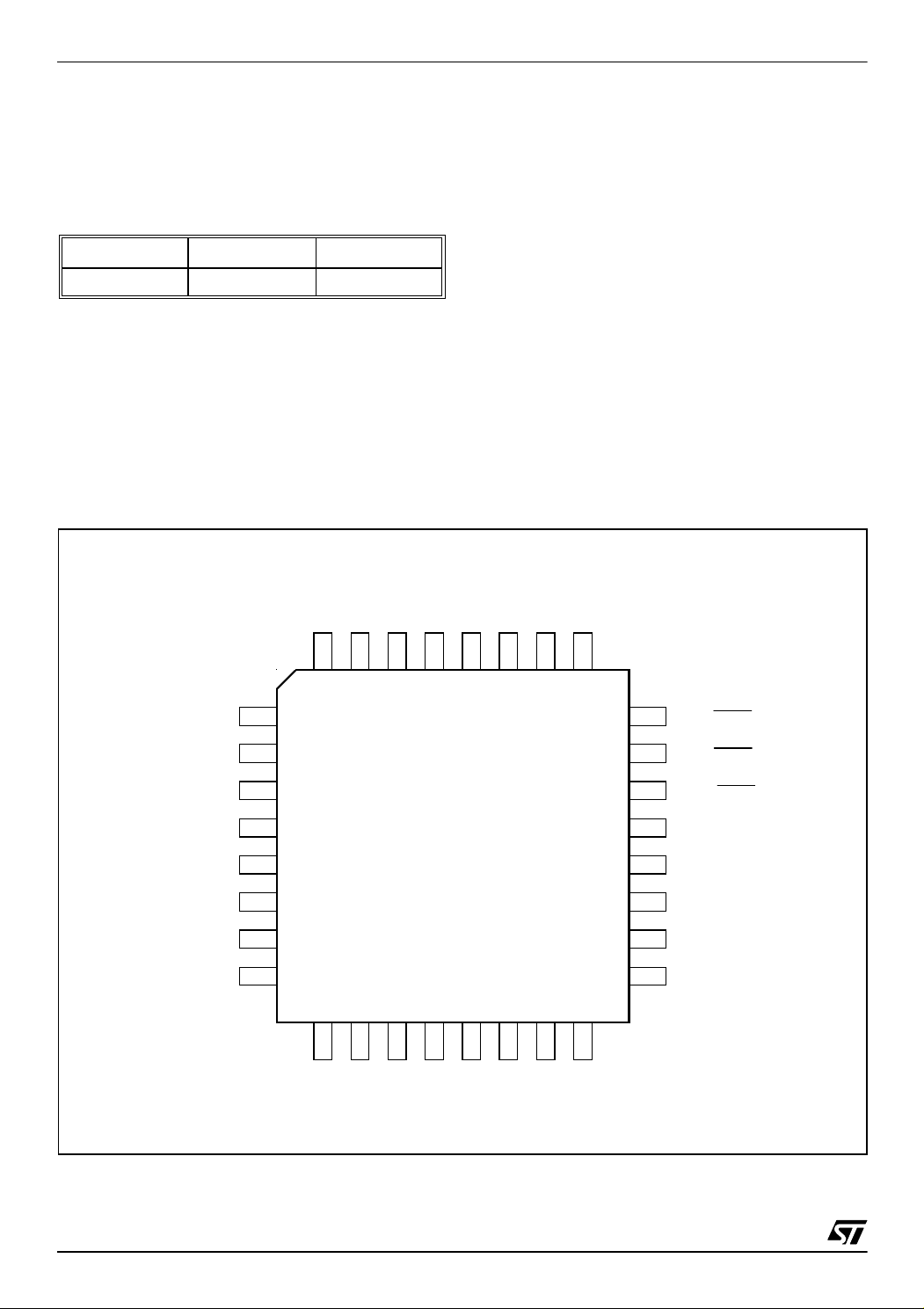

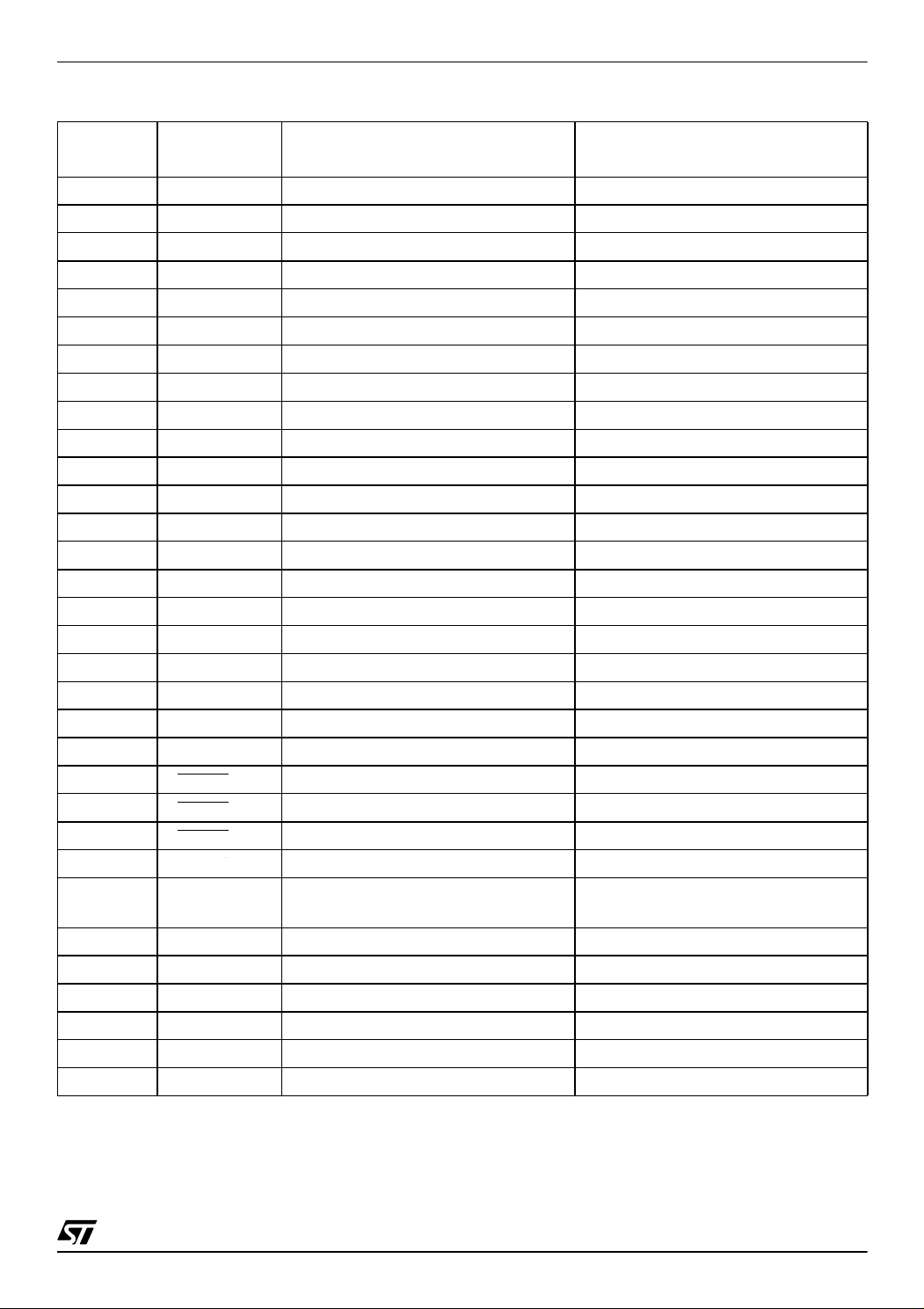

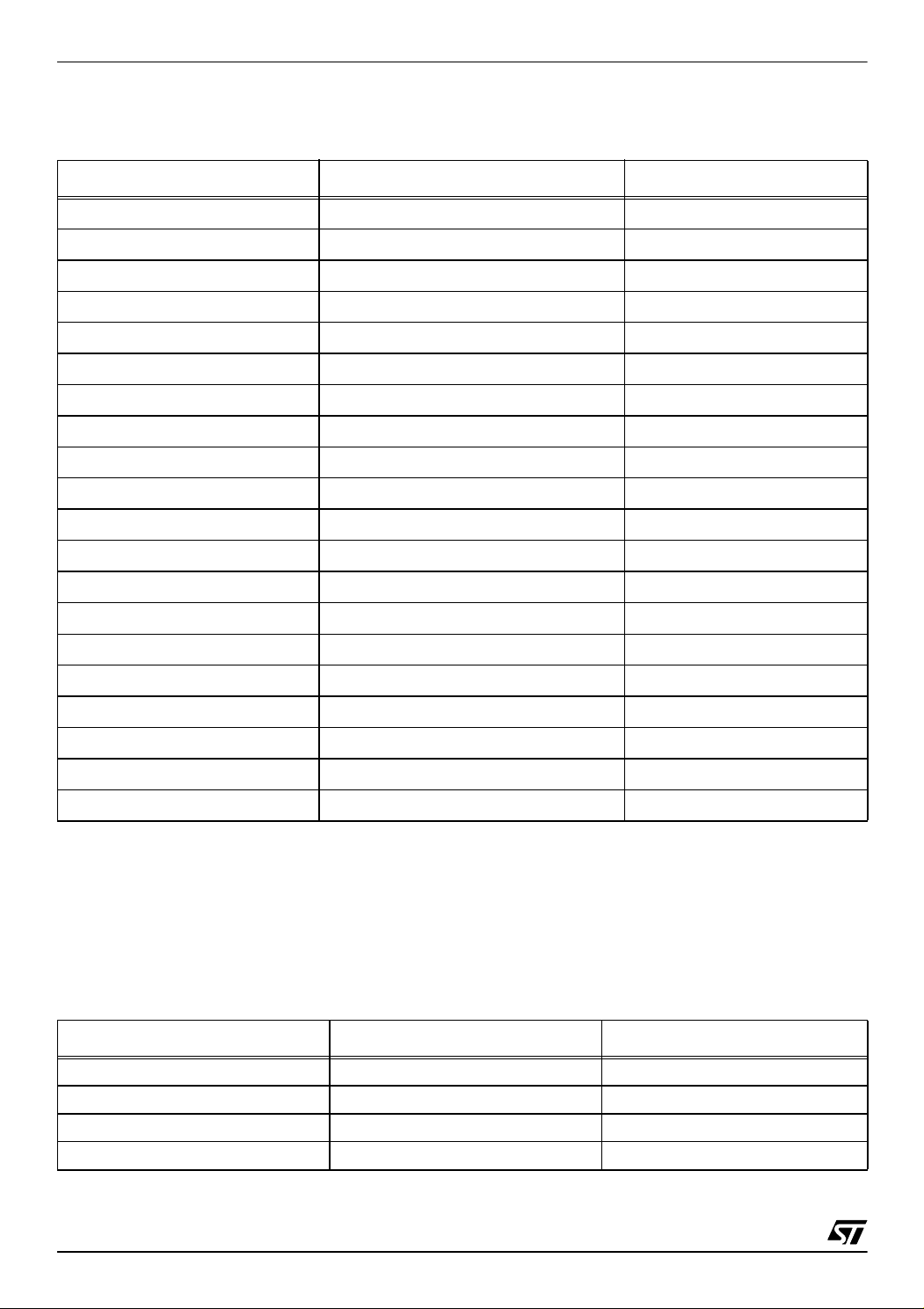

ST52x430 Devices Summary

Device NVM RAM

ST52T430K1 2K OTP 256 3x8-bit 8-Ch Yes Yes 3.0-5.5 V 23 Sdip32 Sso34 Tqfp32

ST52T430K2 4K OTP 256 3x8-bit 8-Ch Yes Yes 3.0-5.5 V 23 Sdip32 Sso34 Tqfp32

ST52T430K3 8K OTP 256 3x8-bit 8-Ch Yes Yes 3.0-5.5 V 23 Sdip32 Sso34 Tqfp32

ST52E430K3 8K EPROM 256 3x8-bit 8-Ch Yes Yes 3.0-5.5 V 23 Csdip32w

Timer

PWM

ADC SCI Watchdog

Operating

Supply

I/O Package

Rev. 1.9 - May 2003 1/88

This is preliminary information on a new product foreseen to be developed. Details are subject to change without notice.

Page 2

ST52T430/E430

2/88

Page 3

ST52T430/E430

TABLE OF CONTENTS

TABLE OF CONTENTS

1 GENERAL DESCRIP TION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

1.2 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

1.2.1 Memory Programming Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.2.2 Working mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.3 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

2 INTER NAL ARCHI T ECTURE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.1 ST52x430 Operating Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

2.2 Control Unit and Data Processing Unit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

2.2.1 Program Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.2.2 Flags. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.3 Address Spaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

2.3.1 RAM and STACK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.3.2 Input Registers Bench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.3.3 Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.3.4 Output Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.4 Arithmetic Logic Unit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

3 EPROM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.1 EPROM Programming Phase Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

3.1.1 EPROM Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.1.2 EPROM Locking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.1.3 EPROM Writing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 5

3.1.4 EPROM Read/Verify Margin Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.1.5 Stand by Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 6

3.1.6 ID code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.2 Eprom Erasure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

4 INTER RUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4.1 Interrupt Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

4.2 Global Interrupt Request Enabling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

4.3 Interrupt Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

4.4 Interru p t M as kability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

4.5 Interrupt Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

4.6 Interrupts and Low power mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 1

4.7 Interrupt RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

5 CLOCK, RESET & POWER SAVING MODE. . . . . . . . . . . . . . . . . . . . . . . . . . 32

5.1 System Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

5.2 RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3 2

5.3 Power Saving Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

5.3.1 Wait Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

5.3.2 Halt Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3/88

Page 4

ST52T430/E430

6 I/O PORTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

6.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3 5

6.2 Input Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 5

6.3 Output Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 6

6.4 Alternate Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

6.5 I/O Port Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

7 FUZZY COMPUTA T ION (DP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

7.1 Fuzzy Inference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

7.2 Fuzzyfication Phase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

7.3 Inference Phase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

7.4 Defuzzyfication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

7.5 Input Membership Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

7.6 Output Singleton. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

7.7 Fuzzy Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

8 A/D CONVERTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

8.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 5

8.2 Operational Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

8.2.1 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

8.2.2 Power Down Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

8.3 A/D Registers Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

9 WATCHDOG TIMER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

9.1 Operational Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

9.2 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

10 PWM/TIMER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

10.1 Timer Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

10.2 PWM Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

10.3 Timer Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 3

11 SERI AL COMMUNIC AT ION INTE RF ACE. . . . . . . . . . . . . . . . . . . . . . . . . . . 64

11.1 SCI Receiver block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 4

11.2 SCI Transmitter Block. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

11.3 Baud Rate Generator Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

12 ELECTRICAL CH ARACTERIS TICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

12.1 Parameter Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

12.1.1 Minimum and Maximum values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

12.1.2 Typical values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

12.1.3 Typical curves. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 8

12.1.4 Loading capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

12.1.5 Pin input voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

12.2 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

12.3 Recommended Operating Condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

12.4 Supply Current Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

4/88

Page 5

ST52T430/E430

12.5 Clock and Timing Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

12.6 Memory Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

12.7 ESD Pin Protection Strategy. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

12.7.1 Standard Pin Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

12.7.2 Multi-supply Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

12.8 Port Pin Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

12.8.1 General Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

12.9 Control Pin Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 0

12.9.1 RESET pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

12.9.2 VPP pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

12.10 8-bit A/D Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

5/88

Page 6

ST52T430/E430

6/88

Page 7

ST52T430/E430

1 GENERAL DESCRIPTION

1.1 Introduction

ST52x430 is an 8-bit Intelligent Control Units (ICU)

of the ST Five Family , which can perform both

boolean and fuzzy algorithms in an efficient

manner, in order t o reach the best perform ances

that the two methodologies allow.

ST52x430 is produced by STMicroelectronics

using the reliable high performance CMOS

process, including in tegrated-o n-chip peri pherals

that allow maximization of system reliability,

decreasing system costs and minimizing the

number of external components.

The flexible I /O configurat ion of ST52x4 00/440

allows for an interface with a wide range of external

devices, like D/A converters or power control

devices.

ST52x430 pins are configurable, allowing the user

to set the input or output signals on each single pin.

A hardware m ultiplier (8 bit by 8 bit with 16 bit

result) and a divider (16 bit over 8 bit with 8 bit

result and 8 bit remainder) are available to

implement complex func tions by using a single

instruction. The program memory utilization and

computational speed is optimized.

Fuzzy Logic dedicated structures in ST52x430

ICU’s can be exploited to model compl ex system s

with high accuracy in a useful and easy way.

Fuzzy Expert Systems for overall system

management and fuzzy Real time Controls can be

designed to increa se performances at highly

competitive costs.

The linguistic approach characterizing Fuzzy Logic

is based on a set of IF-THEN rules, which describe

the control behavior, as well as on Membership

Functions, which are associated to input and

output variables.

Up to 334 Member ship Functio ns, with triangu lar

and trapezoidal shapes, or singleton values are

available to describe fuzzy variables.

The Timer/PWM peripheral allows the

management of power devices and timing signals,

implementing different o perating m odes and high

frequency PWM (Pulse W ith M odul ation) c ontrols.

Input Capture and O utput Comp are functions are

available on the TIMER.

The prog rammable Timer has a 16 bit Internal

Prescaler and an 8 bit Count er. It can use internal

or external Start/Stop signals and clock.

An internal programmabl e Watchdog is available

to avoid loop errors and to reset the ICU.

ST52x430 includes an 8-bit Analog to Digital

Converter with an 8-analog channel Multiplexer.

Single/M ultiple chan nels and Si ngle/Seque nce

conversion modes are supported.

A Serial Communication peripheral (SCI), which

uses the UART protocol allows data transfer from

the ST52x430 to other external devices.

In order to optimize energy consumption, two

different pow er saving modes are ava ilable: Wait

mode and Halt mode.

Progra m Memory (EPRO M/OTP) address ing

capability addresses up to 8 Kbytes of memory

locations to store both program instructions and

permanent data.

EPROM can be locked by the user to prevent

external undesired operations.

Operations may be performed on data stored in

RAM, allowing the direct combination of new input

and feedback data. All bytes of RAM are used like

Register File.

OTP (One Time Programmable) version devices

are fully compatible with the EPROM windowed

version, which may be used for prototyping and

pre-production phases of development.

A powerful development environment consisting of

a board and software tools allows an easy

configuration and use of ST52x430.

TM

The VISUAL FIVE

software tool allows

development of projects through a user-friendly

graphical interface and opt imization of gener ated

code.

1.2 Functional Description

ST52x430 ICU can work in two modes:

■ Memory Programming Mode

■ Working Mode

according to RE SET and Vpp signals levels (s ee

pins description).

Note: When RESET=0 it is advisa ble not to use

the sequence “101010“ to port PA (7 : 2).

1.2.1 Memory Program m ing M od e.

The ST52 x430 mem ory is loaded in the Mem ory

Programming Phase. All fuzzy and standard

instructions are written inside the memory.

This phase starts by s etting the cont rol signals as

illustrated below:

RESET

V

ss

TEST V

V

ss

12V/V

PP

DD

When this phase starts, the ST52x430 core is set

to RESET status; then 12V are applied to th e Vpp

7/88

Page 8

ST52T430/E430

pin in order to start EPROM programming. A signal

applied t o PB1 is used to in crement the memory

address; the data is supplied to PORT A (see

EPROM programming for further details).

1.2.2 Working mode.

Below are the control signals of this mode:

RESET TEST V

V

DD

V

SS

PP

V

SS

The processor starts the working phase following

the instructions, whi ch have been previously

loaded in the memory.

ST52x430’s internal structure includes a

computational block, CONTROL UNIT (CU) /

DATA PROCESSING UNIT (DPU) , which allows

processing of boolean functions and fuzzy

algorithms.

Figure 1.1 TQFP32 Pin Configuration

The CU/DPU can manage up to 334 different

Membership Functions for the fuzzy rules

antecedent part. The rule consequents are “crisp”

values (real numbers). The maximum number of

rules that can be defined is limited by the

dimensions of the implemented standard

algorithm.

EPROM is then shared between fuzzy and

standard algorithms. The Membership Function

data is stored inside the first 1024 memory

locations. The Fuzzy rules are parts of the program

instr uct ion s.

The Cont rol Unit (CU) reads the info rmation an d

the status deriving from the peripherals.

Arithmetic calculus can be performed on these

values by usi ng the internal CU an d the 128/256

bytes of RAM, which supports all computations.

The peripheral input can be fuzzy and/or arithmetic

output, or the val ues contained in Data RAM and

EPROM locations.

INT / PC0

T0OUT / PC1

T1OUT / PC2

T2OUT / PC3

TX / PC4

RX / PC5

PC6

PC7

OSCIN

TEST

32

1

2

3

4

5

6

7

8

9 10 11 12 13

AIN0 / PB0

31

AIN1 / PB1

30 29 28

OSCOUT

AIN2 / PB2

PA0 / T0RES

Vpp

Vss

Vdd

RESET

27 26 25

24

23

22

21

20

19

18

17

14 15 16

Vdda

GNDA

AIN3 / PB3

AIN4 / PB4

AIN5 / PB5

PA1 / T0OUT

PA2 / T1OUT

PA3 / T2OUT

PA4 / STRT

PA5 / T0CLK

PA6

PA7 / PB7 / AIN7

PB6 / AIN6

8/88

Page 9

Figure 1.2 SSO34 Pin Configuration

ST52T430/E430

RESET

OSCOUT

OSCIN

TEST

INT/PC0

T0OUT/PC1

T1OUT/PC2

T2OUT/PC3

TX/PC4

RX/PC5

PC6

PC7

nc

PB0/Ai n0

PB1/Ain1

PB2/A in2

PB3/A in3

Figure 1.3 PSDIP32 Pin Configuration

DD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

V

Vss

V

PP

PA0/T0RES

PA1/T0OUT

PA2/T1OUT

PA3/T2OUT

PA4/T0STRT

PA5/T0CLK

PA6

PB7/PA 7/Ai n7

PB6/A in6

nc

PB5/Ain5

PB4/Ain4

GNDA

DDA

V

RESET

OSCOUT

OSCIN

TEST

INT/PC0

T0OUT/PC1

T1OUT/PC2

T2OUT/PC3

TX/PC4

RX/PC5

PC6

PC7

PB0/Ain0

PB1/Ain1

PB2/Ain2

PB3/Ain3

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

VDD

Vss

PP

V

PA0/T0RES

PA1/T0OUT

PA2/T1OUT

PA3/T2OUT

PA4/T0STRT

PA5/T0CLK

PA6

PB7/PA7/Ain7

PB6/Ain6

PB5/Ain5

PB4/Ain4

GNDA

V

DDA

9/88

Page 10

ST52T430/E430

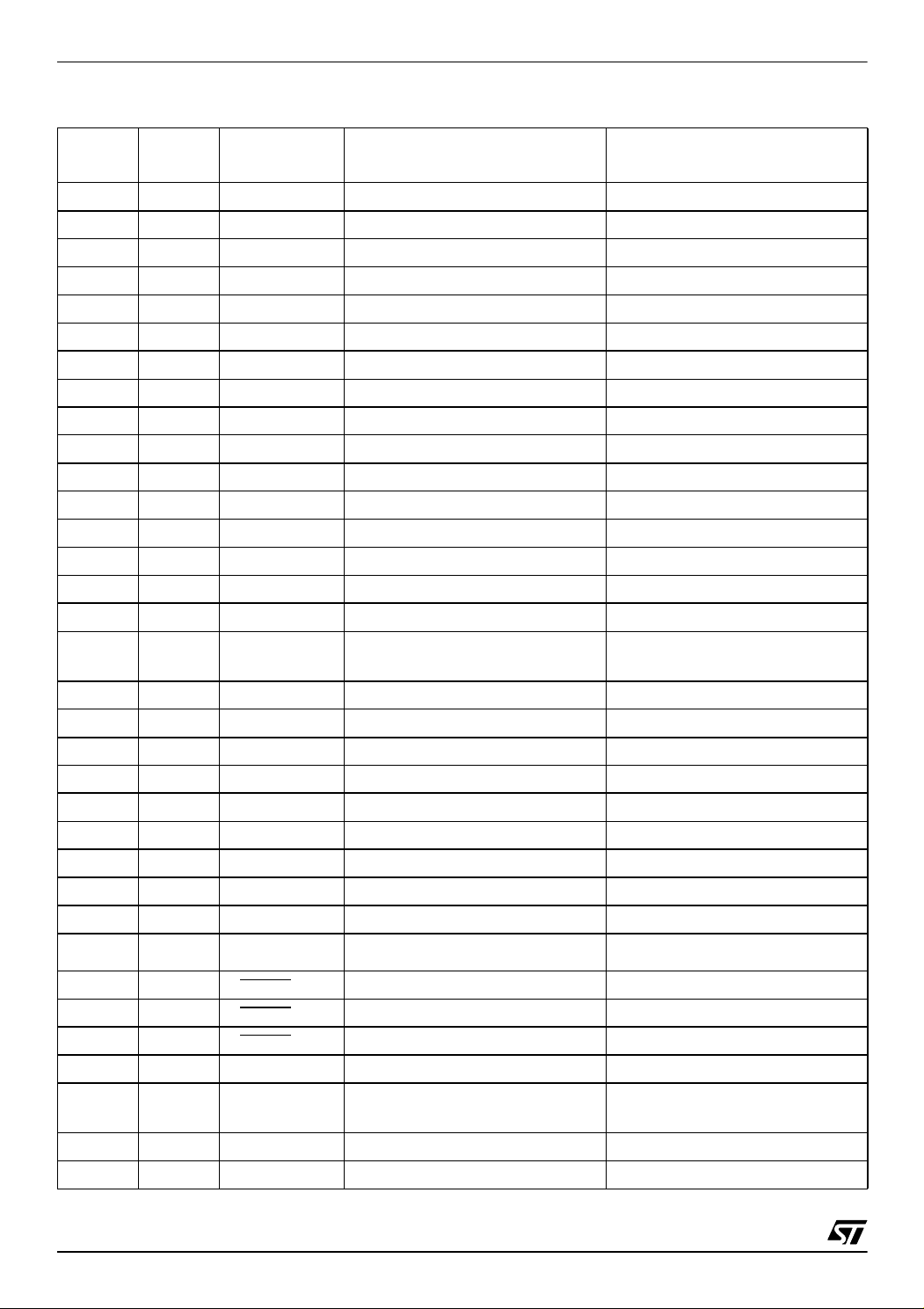

Table 1.1 ST52x430 SSO34 & PSDIP32 Pin list

SSO34

Pins

SDIP32

Pins

NAME Programming Phase Working Phase

1 1 RESET General Reset General Reset

2 2 OSCOUT Oscillator Output

3 3 OSCIN Oscillator Input

4 4 TEST Must be tied to V

ss Must be tied to Vss

5 5 INT/PC0 PHASE signal (PHASE) External interrupt, Digital I/O

6 6 T0OUT/PC1 Timer/PWM 0 output, Digital I/O

7 7 T1OUT/PC2 Timer/PWM 1 output, Digital I/O

8 8 T2OUT/PC3 Timer/PWM 2 output, Digital I/O

9 9 TX/PC4 SCI Output, Digital I/O

10 10 RX/PC5 SCI Input, Digital I/O

11 11 PC6 Digital I/O

12 12 PC7 Digital I/O

13 nc

14 13 Ain0/PB0 Address Reset (RST_ADD) Analog Input, Digital I/O

15 14 Ain1/PB1 Address Increment (INC_ADD) Analog Input, Digital I/O

16 15 Ain2/PB2 Configuration Reset (RST_CONF) Analog Input, Digital I/O

17 16 Ain3/PB3

Configuration Increment

(INC_CONF)

Analog Input, Digital I/O

18 17 V

DDA Analog Power Supply Analog Power Supply

19 18 GNDA Analog Ground Analog Ground

20 19 Ain4/PB4 Analog Input, Digital I/O

21 20 Ain5/PB5 Analog Input, Digital I/O

22 nc

23 21 Ain6/PB6 Analog Input, Digital I/O

24 22 Ain7/PB7/PA7 I/O EPROM Data Analog Input, Digital I/O

25 23 PA6 I/O EPROM Data Digital I/O

26 24 T0CLK/PA5 I/O EPROM Data Timer/PWM 0 clock, Digital I/O

27 25 T0STRT/PA4 I/O EPROM Data Timer/PWM 0 start/stop, Digital I/O

28 26 T2OUT

/PA3 I/O EPROM Data

29 27 T1OUT/PA2 I/O EPROM Data

30 28 T0OUT/PA1 I/O EPROM Data

Timer/PWM 2 compl. output, Digital I/O

Timer/PWM 1 compl. output, Digital I/O

Timer/PWM 0 compl. output, Digital I/O

31 29 T0RES/PA0 I/O EPROM Data Timer/PWM 0 Reset, Digital I/O

32 30 VPP

33 31 V

34 32 V

DD Digital Power Supply Digital Power Supply

ss Digital Ground Dig ital Ground

EPROM Programming Power

supply (12V ± 5%)

EPROM V

DD or Vss

10/88

Page 11

ST52T430/E430

Table 1.2 ST52x430 TQFP32 Pin list

TQFP32

Pins

1 INT/PC0 PHASE signal (PHASE) External interrupt, Digital I/O

2 T0OUT/PC1 Timer/PWM 0 output, Digital I/O

3 T1OUT/PC2 Timer/PWM 1 output, Digital I/O

4 T2OUT/PC3 Timer/PWM 2 output, Digital I/O

5 TX/PC4 SCI Output, Digital I/O

6 RX/PC5 SCI Input, Digital I/O

7 PC6 Digital I/O

8 PC7 Digital I/O

9 Ain0/PB0 Address Reset (RST_ADD) Analog Input, Digital I/O

10 Ain1/PB1 Address Increment (INC_ADD) Analog Input, Digital I/O

11 Ain2/PB2 Configuration Reset (RST_CONF) Analog Input, Digital I/O

12 Ain3/PB3 Configuration Increment (INC_CONF) Analog Input, Digital I/O

13 V

14 GNDA Analog Ground Analog Ground

15 Ain4/PB4 Analog Input, Digital I/O

16 Ain5/PB5 Analog Input, Digital I/O

21 Ain6/PB6 Analog Input, Digital I/O

22 Ain7/PB7/PA7 I/O EPROM Data Analog Input, Digital I/O

19 PA6 I/O EPROM Data Digital I/O

20 T0CLK/PA5 I/O EPROM Data Timer/PWM 0 clock, Digital I/O

21 T0STRT/PA4 I/O EPROM Data Timer/PWM 0 start/stop, Digital I/O

22 T2OUT

23 T1OUT

24 T0OUT

25 T0RES/PA0 I/O EPROM Data Timer/PWM 0 Reset, Digital I/O

26 V

NAME Programming Phase Working Phase

DDA Analog Powe r Supply Analog Power Supply

/PA3 I/O EPROM Data Timer/PWM 2 compl. output, Digital I/O

/PA2 I/O EPROM Data Timer/PWM 1 compl. output, Digital I/O

/PA1 I/O EPROM Data Timer/PWM 0 compl. output, Digital I/O

PP

EPROM Programming Power supply

(12V ± 5%)

EPROM V

DD or Vss

27 V

28 V

ss Digital Ground Digital Ground

DD Digital Power Supply Digital Power Supply

29 RESET General Reset General Reset

30 OSCOUT Oscillator Output

31 OSC IN Oscillator Input

32 TEST Must be tied to V

ss Must be tied to Vss

11/88

Page 12

ST52T430/E430

1.3 Pin Description V

DD, VSS

, V

, GNDA, VPP. In order to avoid

DDA

noise disturbances, the power supply of the digital

part is kept separate fr om the power supply of the

analog part.

Main Power Supply Voltage (5V± 10%).

V

DD.

. Digital circuit ground.

V

SS

. Analog VDD of the Analog to Digital

V

DDA

Converter.

GNDA. Analog V

Converter. Must be tied to V

of the Analog to Digital

SS

SS

.

VPP. Main P ower Supp ly for interna l EPROM

(12.5V±5%, in programming phase) and MODE

selector. During the Programming phase

(programming), V

Working phase V

must be set at 12V. In the

PP

must be equal to VSS.

PP

OSCin and OSCout. These pins are internally

connected with the on-chip oscillator circuit. A

quartz crystal or a ceramic resonator can be

connected between these two pins in order to allow

the correct operations of ST52x430 with various

stability/cost trade-off. An external clock signal can

be applied to OSCin, in this case OSCout must be

floating.

RESET. This signal is used to restart ST52x430 at

the beginning of its program. It also allows one to

select the program mode for EPROM.

Ain0-Ain8. These 8 lines are conne cted to the

input of the analog multiplexer. They allow t he

acquisition of 8 analog input. During the

Programming phase, Ain0, Ain1, Ain2 and Ain3 are

used to manage EPROM operation.

PA0-PA7, PB0-PB7, PC0-PC7. These lines are

organized as I/O port. Each pin can be configured

as input or output. PA 7/PB7 are t ied to the same

output. During Programming phase PA port is used

for EPROM read/write data.

T0RES, T0CLK, T0STRT. These pins are related

with the in ternal Programm able Timer/P WM 0.

This Timer can be reset externally by using

T0RES. In Working Mode, T0RES resets the

address counter of the Timer. T 0RES is activ e at

low leve l.

The Timer 0 Clock can be the internal clock or can

be supplied externally by using pin T0CLK.

An external Start/Stop signal can be used to

control the Timer through T0STRT pin.

T0OUT, T1OUT, T2OUT. The TIMER/PWM

outputs are available on these pins.

T0OUT

, T1OUT, T2OUT. The TIMER/PWM

complem entary out puts are availa ble on these

pins.

Tx. Serial data output of SCI transm itter block

Rx. Serial data input of the SCI receiver block.

TEST. Duri ng the Programming and Working

phase it must be set to Vss.

12/88

Page 13

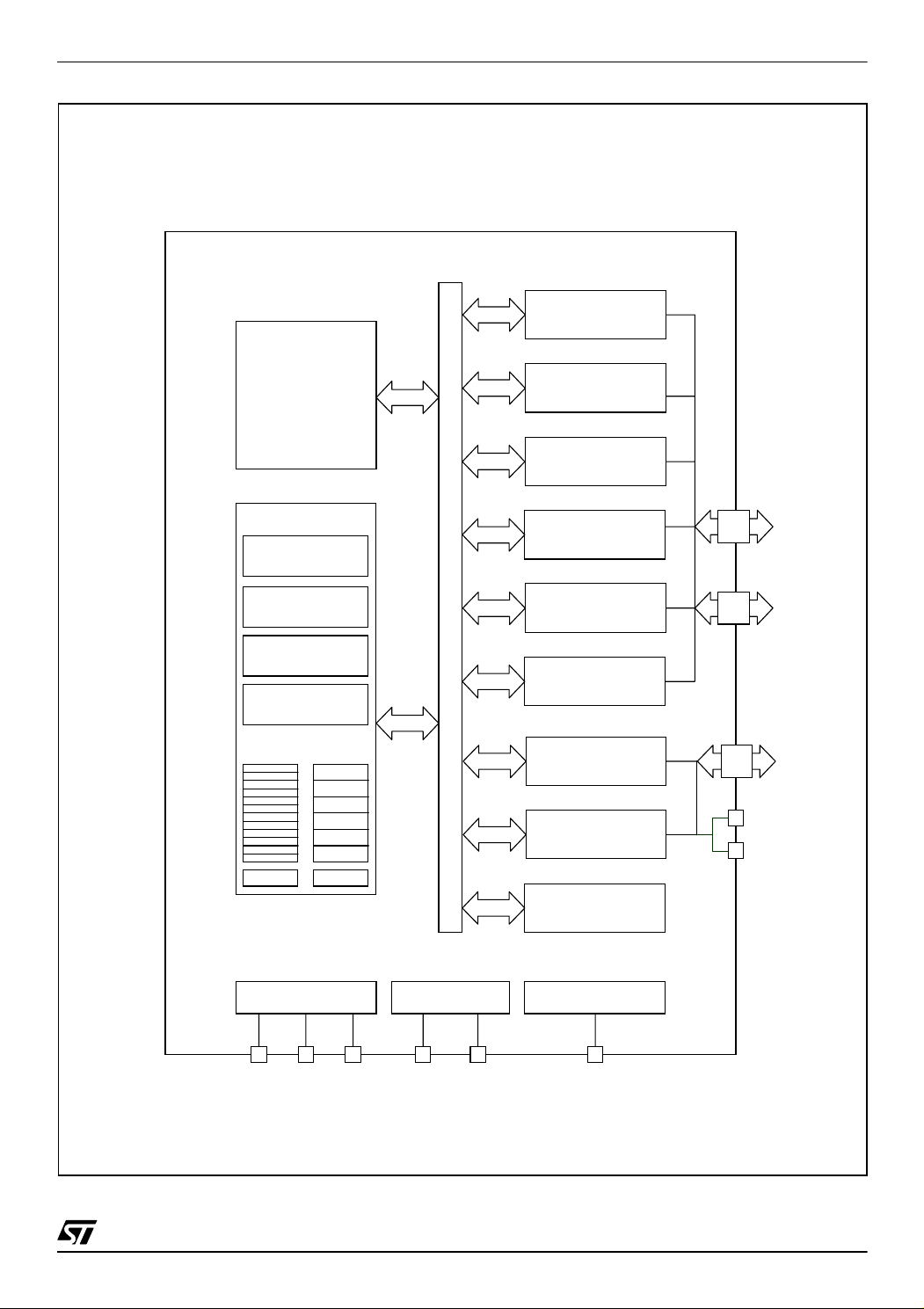

Figure 1.4 ST52X430 Block Diagram

PROGRAM

MEMORY

EPROM

ST52T430/E430

TIMER/P WM 0

TIMER/P WM 1

TIMER/P WM 2

CORE

INTERRUPTS

CONTROLLER

ALU &

DPU

DECISION

PROCESSOR

CONTROL

UNIT

Register File

256 bytes

PC FLAGS

POWER SUPPLY OSCILLATOR

Input

registers

PORT A

PORT C

SCI

PORT B

ADC

WATCHDOG

RESET CIRCUIT

PA7:0

PC7:0

PB7:0

VDDA

GNDA

VDD VPP VSS OSCIN OSCOUT RESET

13/88

Page 14

ST52T430/E430

2 INTERNAL ARCHITECTURE

ST52x430 is made up of the following blocks and

peripherals:

■ Control Unit (CU) and Data Processing Unit

(DPU)

■ ALU / Fuzzy Core

■ EPROM

■ 256 Byte RAM

■ Clock Osc illator

■ Analog Multiplexer and A/D Converter

■ 3 PWM / Timers

■ SCI

■ Digital I/O port

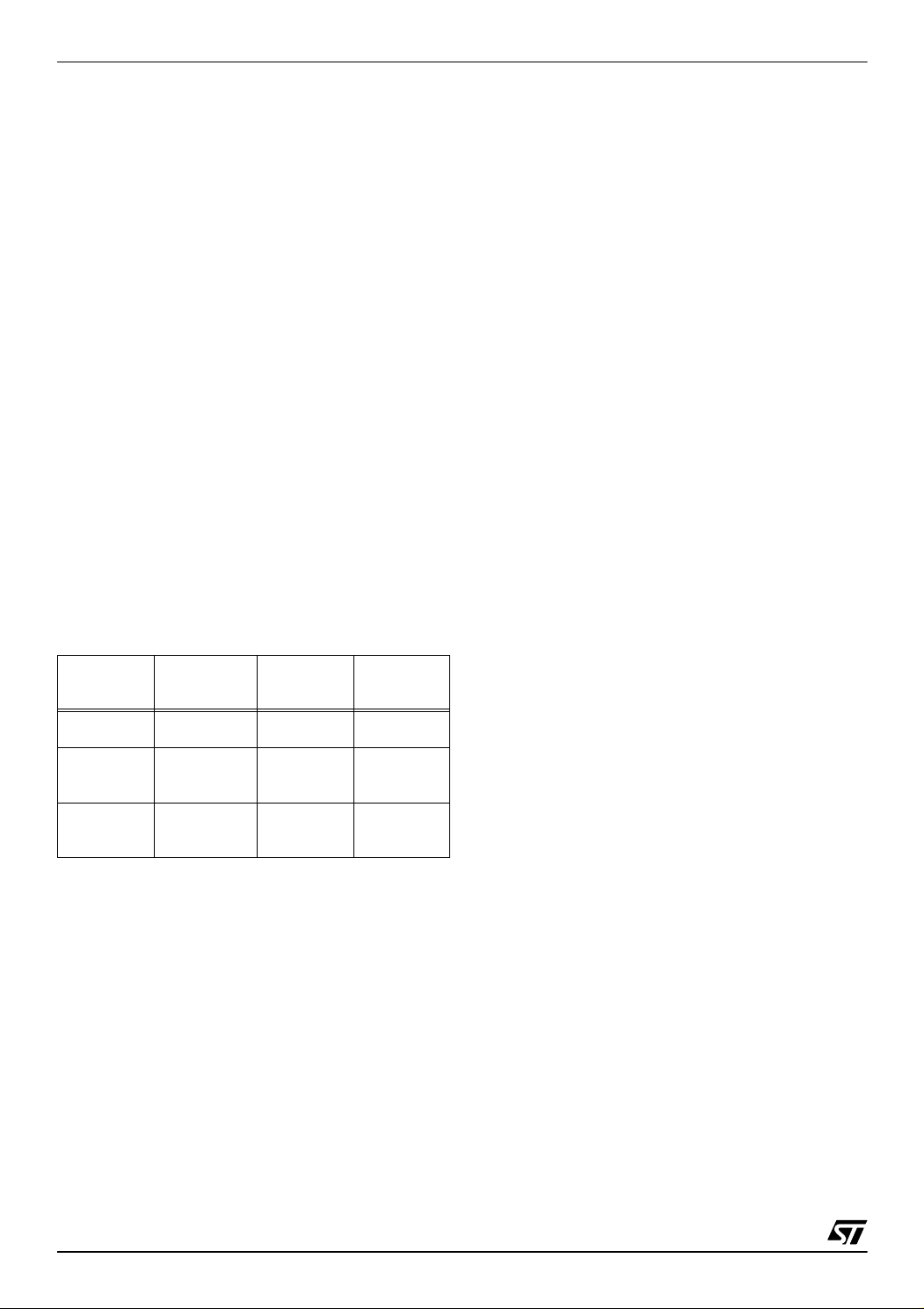

2.1 ST52x430 Operating Modes

ST52x430 works in two modes, Programm ing and

Working Modes, depending on the control signals

level RESET, TEST and V

PP

The Operating modes are selected by setting the

control signal level as specified in the Control

Signals Setting table.

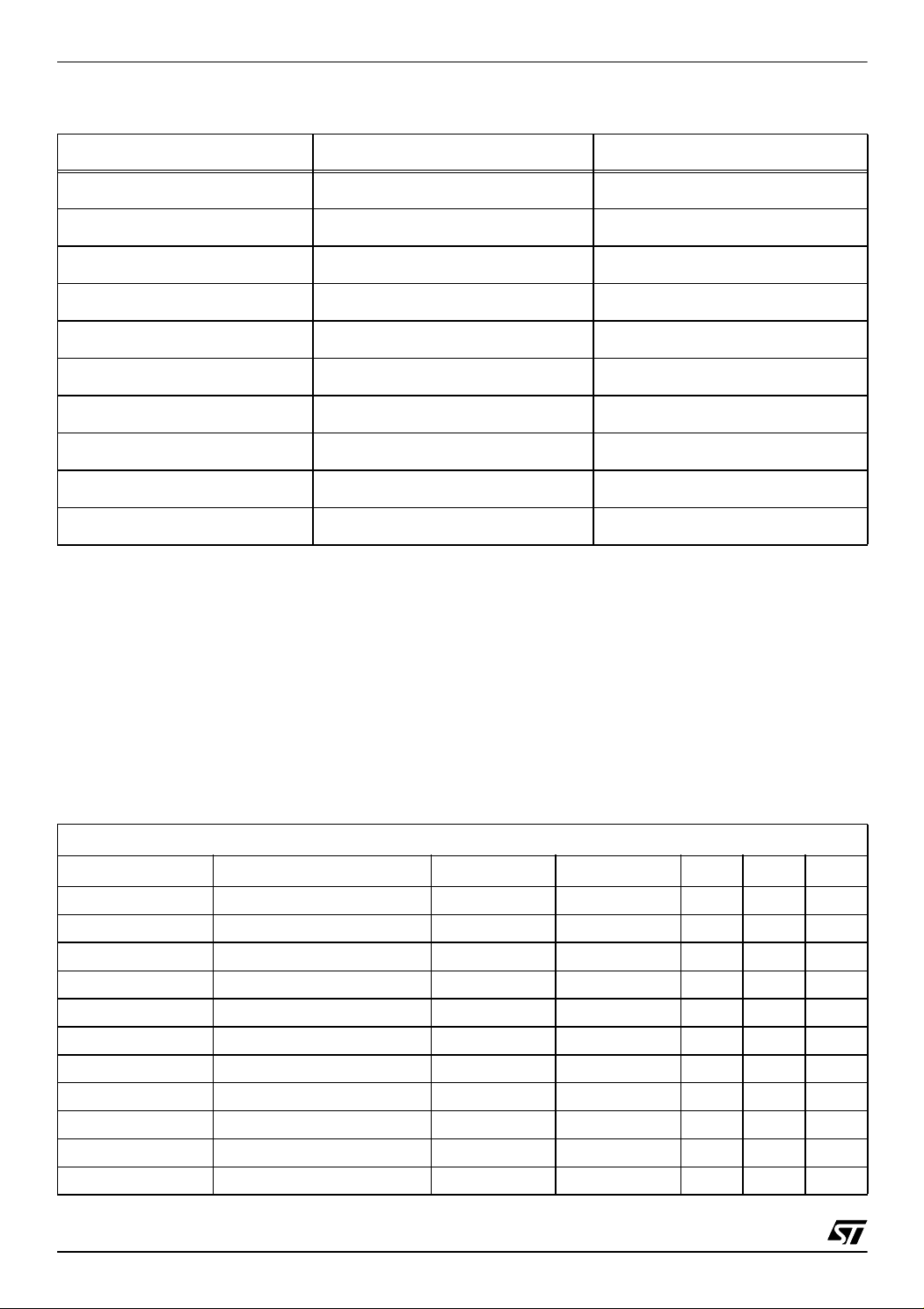

Table 2.1 Control Signals Setting

Control

Signal

RESET V

TEST VSS

VPP 12 V

Pro-

gramming

SS VSS VDD

Reset Workin g

VSS VSS

SS VSS

V

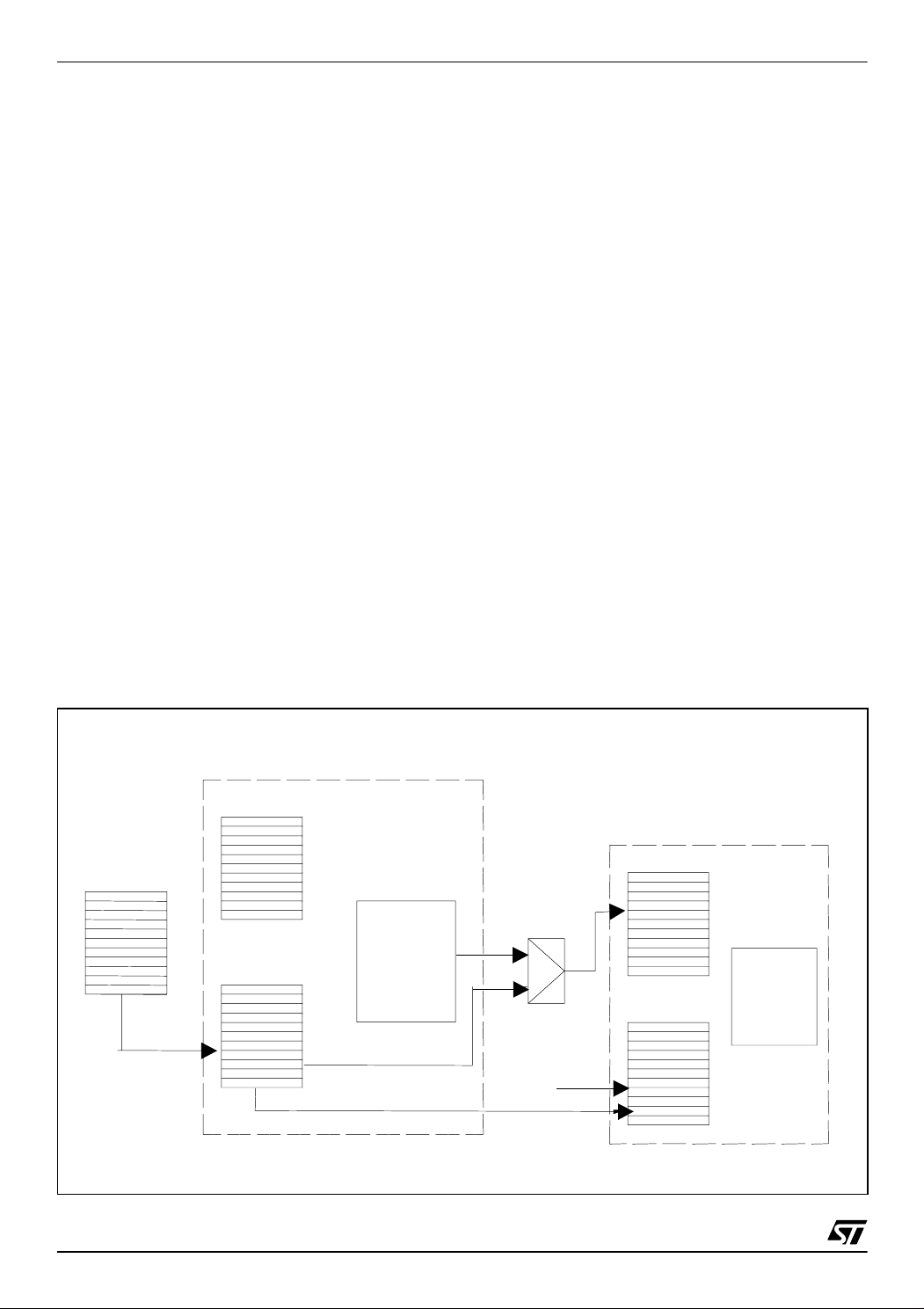

2.2 Control Unit and Data Processing Unit

The Cont rol U nit (CU ) form ally inc ludes five m ain

blocks. Each block decodes a set of instructions,

generating the appropriate control signals. The

main parts of the CU are illustrated in Figure 2.1.

The five different parts of the CU manage Loading,

Logic/Arithmetic, Jump, Control and the Fuzzy

instruction set.

The block called “Co llector” manages the s ignals

deriving from the different parts of the CU, defining

the signals for the Data Processing Unit (DPU) and

the different peripherals of the microcontroller.

The block called “Arbiter” manages the different-

parts of the CU so that only one part of the system

is activated during working mode.

The CU structure is very flexible. It was desig ned

with the purpose of easily adapting the core o f the

microcontroller to market needs. New instruction

sets or new peripherals can be easily included

without changing the structure of the

microcontroller, maintaining code compatibili ty.

The CU reads the instructions stored on EPROM

(Fetch) and decodes them. According to the

instruction types, the arbiter activates one o f the

main blocks of the CU. Afterwards, all the control

signals for the DPU are generated.

A set of 46 different arithmetic, fuzzy and logic

instructions is available. Each instruction requires

6 (fuzzy instructions) to 26 (DIVISION) clock

pulses to be performed.

The DPU receives, stores and sends instructions

deriving from EPROM, RAM or peripherals in order

to execute them.

2.2.1 Program Counter.

The Program Counter (PC) is a 13-bit register that

contains the address of the next memory location

to be processed by the core. This memory location

may be an opcode, operand, or an address of an

operand.

The 13-bit length allows direct addressing of a

maximum of 8,192 bytes in the program space.

After having read the current instruction address,

the PC value is incremented. The result of this

operation is shifted back into the PC.

The PC can be changed in the following ways:

■ JP (Jump)PC = Jump Address

■ InterruptPC = Interrupt Vector

■ RETIPC = Pop (stack)

■ RETPC = Pop (stack)

■ CALLPC = Subroutines address

■ ResetPC = Reset Vector

■ Normal InstructionPC = PC + 1

2.2.2 Flags.

The ST52x430 core includes a different set of

flags that correspond to 2 different m odes : norm al

mode and interrupt mode. Each set of flags consists of a CARRY flag (C), ZERO flag (Z) and

SIGN flag (S).

One set (CN, ZN, SN) is used during normal

operation and one is used during interrupt mode

(CI, ZI, SI). Formally, t he user has to manage

only one set of flags: C, Z and S.

14/88

Page 15

Figure 2.1 Data Processing Unit (DPU)

ST52T430/E430

CU

EPROM

INPUTS

PERIPHERALS

ADDRESS RAM

STACK POINT

M

U

X

Figure 2.2 CU/DPU Block Diagram

PROGRAM CO U NTER

RAM

256 Bytes

ACCUMU LATOR

FLAGS REG.

PERIPHERALS

FUZZY

REGISTERS

MULTIPLEXER

ALU

add_EPR

E

P

R

O

M

M icrocode

RAM

C

U

Control S ignals

EP RO M A ddress

RAM Data 8 Bit

RAM A ddr.

8 Bit

RAM

D a ta O u t

8 Bit

D

P

U

To Peripherals

From

Pe riph erals

15/88

Page 16

ST52T430/E430

The ST52x430 core us es flags that correspond to

the actual mode. As soon as an interrupt is

generated the ST52x430 core uses the interrupt

flags instead of the normal flags.

Each interrupt level has its own set of flags, which

is saved in the STAC K toge ther with the Program

Counter. These flags are restored from the STACK

automatically when a RETI instruction is executed.

If the MCU was in normal mode before an interrupt,

the normal flags are restored when the RETI

instruction is executed.

Note:

A CALL subroutine is a normal mode

execution. For this reason, a RET instruction,

consequent to a CALL ins truction does not affect

the normal mode set of flags.

Flags are not cleared during context switching and

remain in the state they were at the end of the last

interrupt routine switching.

The Carry flag is set when an overflow occurs

during arithmetic operations, otherwise it is

cleared.

The Sign flag is set when an underflow occurs

during arithmetic operations, otherwise it is

cleared.

2.3 Address Spaces

ST52x430 has four separate address spaces:

■ RAM: 256 Bytes

■ Input Registers: 20 8-bit registers

■ Output Registers 10 8-bit registers

■ Configuration Registers: 21 8-bit registers

■ Program memory up to 8K Bytes

Program memory will be described in further

details in the MEMORY sec t io n

2.3.1 RAM and STACK.

RAM memory consists of 256 general purpose 8bit RAM registers.

All the registers in RAM can be specified by using

a decimal address. For e xample, 0 identifies the

first register of RAM.

To read or write RAM registers LOAD instructions

must be used. See Table 2.5

Each interrupt level has its own set of flags, which

is saved in the STAC K together w ith the P rogram

Counter. These flags are restored from the STACK

automatically when a RETI instruction is executed.

When the instructions like Interrupt request or

CALL are executed, a STACK level is used to push

the PC.

The STACK is located in RAM. For each l evel of

stack, 2 bytes of RAM are used. The values of this

stack are stored from the last RAM register

(address 255). The maximum level of stack

must be less than 128.

Figure 2.3 Address Spaces Description

ST52X430 CORE

PROGRAM MEMORY

INPUT REGISTERS

CONTROL UNI T

RAM

LDRI

DPU

ALU

LDRC

LDCR

LDPR

LDCE

ON CHIP PERIPHERALS

PERIPHERAL REGISTERS

CONFIGURATION

REGISTERS

PERIPHERAL

BLOCK

16/88

Page 17

ST52T430/E430

The STACK POINTER indicates the first level

available to store data. When a subrou tine call or

interrupt request occurs, the content of t he PC and

the current set of flags are stored into the level

located by the STACK POINTER.

When a interrupt return occurs (RETI instruction),

the data stored in the highest stack level is

restored back into the PC and current flags.

Instead, when a subroutine return occurs (RET

instruction) the data stored in the highest stack

level are restored in the PC not affecting the flags.

These operating modes are illustrated in Figure

2.4.

The user must pay close attention to avoid

Note:

overwriting RAM locations where the STACK could

be stored

.

2.3.2 Input Registers Bench.

The Input Registers (IR) bench consists of 20 8-bit

registers containing data or the status of the

peripherals.

Figure 2.4 Stack Operation

All the registers can be specified by using a

decimal address (for exam ple, 0 identifies the first

register of the IR).

The assembler instruction:

LDRI RAM_Reg. IR_i

loads the value of the i-th IR in the RAM location

identified by the RAM_Reg address.

The first input register is dedicated to store the

value of the stack pointer. The next 8 registers

(ADC_OUT_0:7) of the IR are dedicated to t he 8

converted values deriving from the ADC. The last

9 Input Registers contain data from the I/O ports

and PWM/Timers. The following table summarizes

the IR address and the relative peripherals. In

order to simplify the concept, a mnemonic name is

assigned to the registers. The same name is used

in VISUALSTUDI O

®

development tools

REG 0

REG 1

REG 2

REG 3

REG 4

REG 5

WHEN RETI OR RET

OCCURS

REG 252

REG 253

REG 254

REG 255

PRO G RAM CO U NTER

RAM

WHEN CALL OR

INTERRUPT REQ.

OCCURS

Stack

Pointer

STACK LEVEL n

..........................

STACK LEVEL 2

STACK LEVEL 1

17/88

Page 18

ST52T430/E430

Table 2.2 Input Registers

IR MNEMONIC NAME PERIPHERAL REGISTER ADDRESS

STACK_POINTER STACK POINTER 0

CHAN 0 A/D CHANNEL 0 1

CHAN 1 A/D CHANNEL 1 2

CHAN 2 A/D CHANNEL 2 3

CHAN 3 A/D CHANNEL 3 4

CHAN 4 A/D CHANNEL 4 5

CHAN 5 A/D CHANNEL 5 6

CHAN 6 A/D CHANNEL 6 7

CHAN 7 A/D CHANNEL 7 8

PORT_A PORT A INPUT REGISTER 9

PORT_B PORT B INPUT REGISTER 10

PORT_C PORT C INPUT REGISTER 11

PWM_ 0_COUNT PWM/TIMER 0 COUNTER 12

PWM_ 0_ STATUS PWM/TIMER 0 STATUS REGISTER 13

PWM_ 1_ COUNT PWM/TIMER 1 COUNTER 14

PWM_ 1_ STATUS PWM/TIMER 1 STATUS REGISTER 15

PWM_ 2_ COUNT PWM/TIMER 2 COUNTER 16

PWM_ 2_ STATUS PWM/TIMER 2 STATUS REGISTER 17

SCI_RX SCI DATA REGISTER 18

SCI_STATUS SCI STATUS REGISTER 19

2.3.3 Configuration Registers.

The ST52x430 configuration Registers allow the

configuration of all the blocks of the fuzzy

microcontroller. Table 2.3 describes the functions

and the related peripherals of each of the

instructions, the Configuration Registers can be

set by using values stored in the Program Memory

(EPROM) or in RAM.

Use and meaning of each register will be described

in further details in the corresponding section.

Configuration Registers. By using the load

Table 2.3 Configuration Registers

CONFIGURATION REGISTER PERIPHERAL DESCRIPTION

REG_CONF 0 INTERRUPT MASK Interrupts mask setting

REG_CONF 1 N.U. N.U.

REG_CONF 2 WATCHDOG TIMER Watchdog Timer Configuration

REG_CONF 3 A/D CONVERTER A/D configuration

18/88

Page 19

Table 2.3 Configuration Registers (continued)

CONFIGURATION REGISTER PERIPHERAL DESCRIPTION

ST52T430/E430

REG_CONF 4 PORT A

REG_CONF 5 PWM/TIMER 0

REG_CONF 6 PWM/TIMER 0

REG_CONF 7 PWM/TIMER 0

REG_CONF 8 PWM/TIMER 1

REG_CONF 9 PWM/TIMER 1

REG_CONF 10 PWM/TIMER 2

REG_CONF 11 PWM/TIMER 2

REG_CONF 12 PORT A

REG_CONF 13 PORT B

Set the relative bit like digital input

or digital output

PWM/Timer 0 Working mode

Configuration

PWM/TIMER 0 Prescaler

configuration and output waveform

selection.

PWM/TIMER 0 Working Mode

Configuration

PWM/TIMER 1 Working Mode

Configuration

PWM/TIMER 1 Prescaler

configuration and output waveform

selection.

PWM/TIMER 2 Working Mode

Configuration

PWM/Timer 2 Prescaler

configuration and output waveform

selection.

Set the bit 0,1 and 2 like Digital I/O

or complementary Timers Output.

Set the relative bit like digital input

or digital output.

REG_CONF 14 PORT B

REG_CONF 15 PORT C

REG_CONF 16 PORT C

REG_CONF 17 Interrupt Priority Set the Interrupts priority

REG_CONF 18 Interrupt Priority Set the Interrupts priority

REG_CONF 19 SCI Set the SCI working mode

REG_CONF 20 SCI Set the SCI working mode

2.3.4 Output Registers.

The Output Registers (OR) consist of 10 registers

containing data for the microcont roller peripherals

including the I/O Ports.

All registers can be specified by us ing a decimal

address (for example, 1 identifies the second OR).

By using LOAD instructions t he Output Registers

(OR) may be set by using values stored in the

Program Memory (LDPE) or in RAM (LDPR)

The assembler instruction:

LDPR OR_i RAM_Reg.

Set the relative I/O like Digital or

Analog.

Set the relative I/O like digital input

or digital output

Set the relative I/O like Digital I/O

or Timers Output

loads the value of the RAM location identified by

the address RAM_Reg in the OR i-th Table 2.4

describes OR.

In order to simplify the concept, a mnemonic name

is assigned to OR. T he same names are used in

FUZZYSTUDIO

TM

4.0 development tools.

Use and meaning of each register will be described

in further details in the corresponding section.

19/88

Page 20

ST52T430/E430

Table 2.4 Output Registers

OR MNEMONIC NAME PERIPHERAL REGISTER ADDRESS

PORT_ A PORT A OR 0

PORT_ B PORT B OR 1

PORT_C PORT C OR 2

PWM_0_COUNT TIMER/PWM 0 COUNTER 3

PWM_0_RELOAD TIMER/PWM 0 RELOAD REGISTER 4

PWM_1_COUNT TIMER/PWM 1 COUNTER 5

PWM_1_RELOAD TIMER/PWM 1 RELOAD REGISTER 6

PWM_ 2_ COUNT TIMER/PWM 2 COUNTER 7

PWM_2_RELOAD TIMER/PWM 2 RELOAD REGISTER 8

SCI_TX_DATA SCI DATA REGISTER 9

2.4 Arithmetic Logic Unit

The 8-bit Arithmetic Logic Unit (ALU) allows the

performance of arithmetic calculations and logic

instructions, which can be divided into 5 groups:

Load, Arithmetic, Jump, Interrupts and Program

Control instructions (refer to the ST52x430

Assembler Set for further details).

The computational time required for each

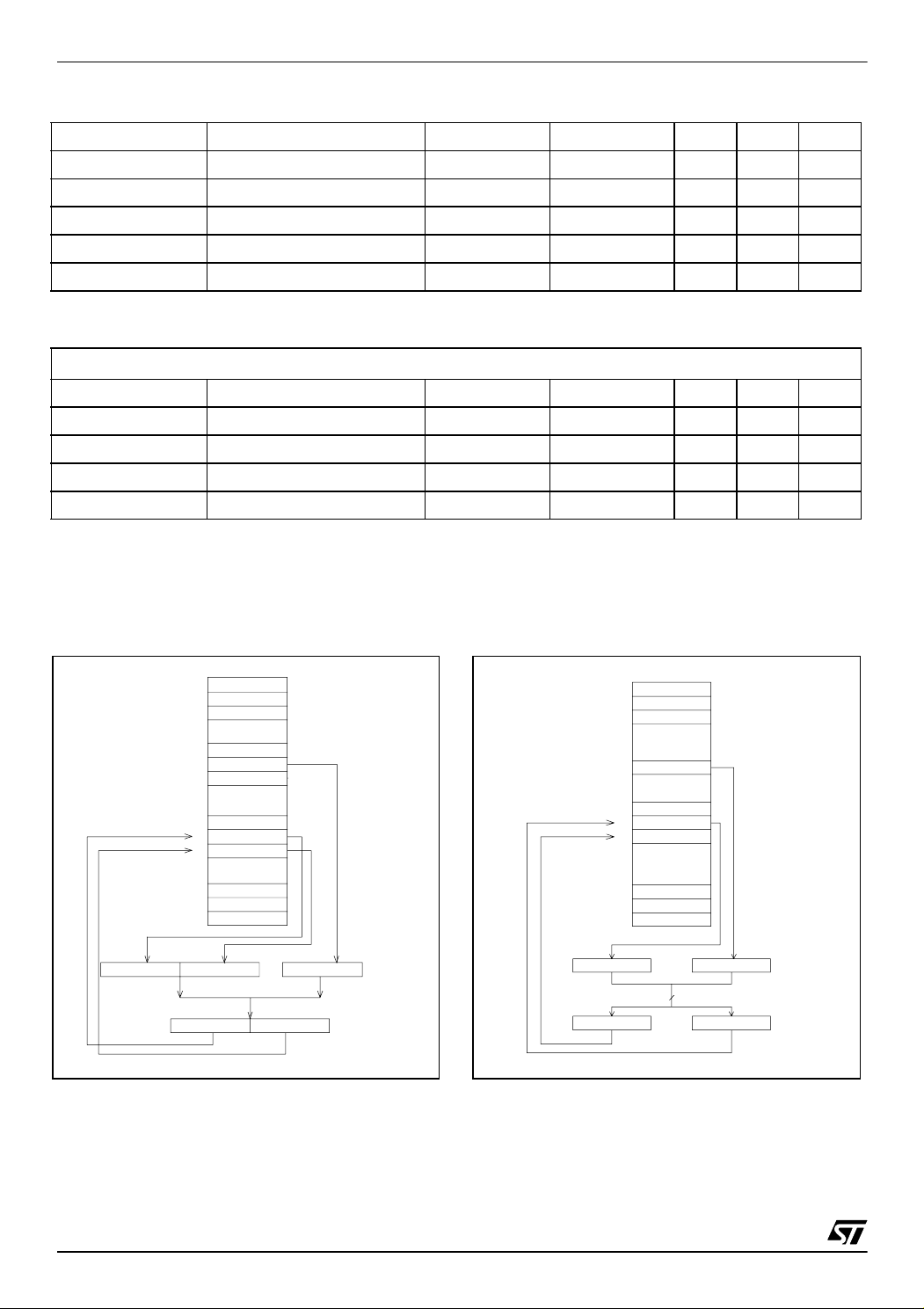

The ALU of the ST52x430 can perform

multiplication (MULT) and division (DIV).

Multiplication is performed by using 8 bit operands

storing the result in 2 registers (16 bit values), see

Figure 2.5 and Figure 2.6.

WARNING: If the LSB of the multiplication

result is 0, the Zero flag is set although the

result is not 0.

instruction consists of one clock pulse for each

Cycle plus 3 clock pulses for the decoding phase.

Table 2.5 Load instructions

Load Instructions

Mnemonic Instruction Bytes Cycles Z S C

LDCE LDCE conf, EPROM 3 17 - - -

LDCR LDCR conf, RAM 3 14 - - -

LDFR LDFR FUZZY_i_RAM RAM 3 14 - - LDPE L DPE per, EPROM 3 17 - - LDPE LDPE per, (RAM) 3 17 - - LDPR LDPR reg, RAM 3 14 - - -

LDRC LDRC RAM, const 3 14 - - -

LDRE LDRE RAMi, EPROMi 3 16 - - LDRE LDRE (RAMi), (RAMj) 3 18 - - -

LDRI LDRI RAM, inp_reg 3 15 - - -

LDRR LDRR RAMi, RAMj 3 16 - - -

20/88

Page 21

ST52T430/E430

Table 2.5 Load instructions

PGSET PGSET const 2 9 - - -

Table 2.6 Arithmetic & Logic instructions set

Arithmetic Instructions

Mnemonic Instruction Bytes Cycles Z S C

ADD ADD regi, regj 3 17 I - I

ADDO ADDO regi, regj 3 20 I I I

AND AND regi, regj 3 17 I - -

ASL ASL regi 2 15 I - I

ASR ASR regi 2 15 I I DEC DEC regi 2 15 I I -

DIV DIV regi, regj 3 26 I I I

INC INC regi 2 15 I - I

MULT MULT regi, regj 3 19 I - -

NOT NOT regi 2 15 I - -

OR OR regi, regj 3 17 I - -

SUB SUB regi, regj 3 17 I I -

SUBO SUBO regi, regj 3 20 I I I

MIRROR MIRROR regi 2 15 I - -

Table 2.7 Jump Instruction Set

Jump instructions

mnemonic instruction bytes cycles z s c

call call addr 3 18 - - -

jp jp addr 3 12 - - -

jpc jpc addr 3 10/12 - - jpnc jpnc addr 3 10/12 - - jpns jpns addr 3 10/12 - - jpnz jpnz addr 3 10/12 - - -

jps jps addr 3 10/12 - - -

jpz jpz addr 3 10/12 - - -

ret ret 1 13 - - -

Table 2.8 Interrupt Instructions Set

Interrupt Instructions

Mnemonic Instruction Bytes Cycles Z S C

HALT HALT 1 7/15 - - -

MEGI MEGI 1 7/15 - - -

21/88

Page 22

ST52T430/E430

Table 2.8 Interrupt Instructions Set (continued)

MDGI MDGI 1 6 - - -

RETI RET I 1 12 - - -

RINT RINT INT 2 8 - - -

UDGI UDGI 1 6 - - -

UEGI UEGI 1 7 /15 - - -

WAITI WAITI 1 7 /14 - - -

Table 2.9 Control Instructions Set

Control Instructions

Mnemonic Instruction Bytes Cycles Z S C

FUZZY FUZZY 1 5 - - -

NOP NOP 1 6 - - -

WDTRFR WDTRFR 1 7 - - -

WDTSLP WDTSLP 1 6 - - -

Notes:

I affec ted

- not affected

Figure 2.5 Multiplication Figure 2.6 Division

RAM

0

1

2

i-1

i

i+1

j-1

j

j+1

253

254

255

REG. j REG. j+1

REMAINDER QUOTIENT

:

REG. i

REG. j REG. i

LSB

RAM

0

1

2

i

j-1

j

j+1

253

254

255

X

16 Bit

MSB

22/88

Page 23

ST52T430/E430

3 EPROM

EPROM memory provides an on-chip userprogrammable non-volatile m emory, which allows

fast and reliable storage of user data.

EPROM memory can be locked by the user. In

fact, a memory location called Lock Cell is devoted

to lock EPROM and avoid external ope rations. A

software identification code, called ID CODE,

distinguishes which softw are version is stored in

the memo r y .

64 kbits of memory space with an 8-bit internal

parallelism (up to 8 kbytes) addressed by an 13-bit

bus are available. The data bus is 8 bits.

Memory has a double supply: V

12V±5% in Programming Phase or to V

Working Phase. V

is equal to 5V±10%.

DD

is equal to

PP

during

SS

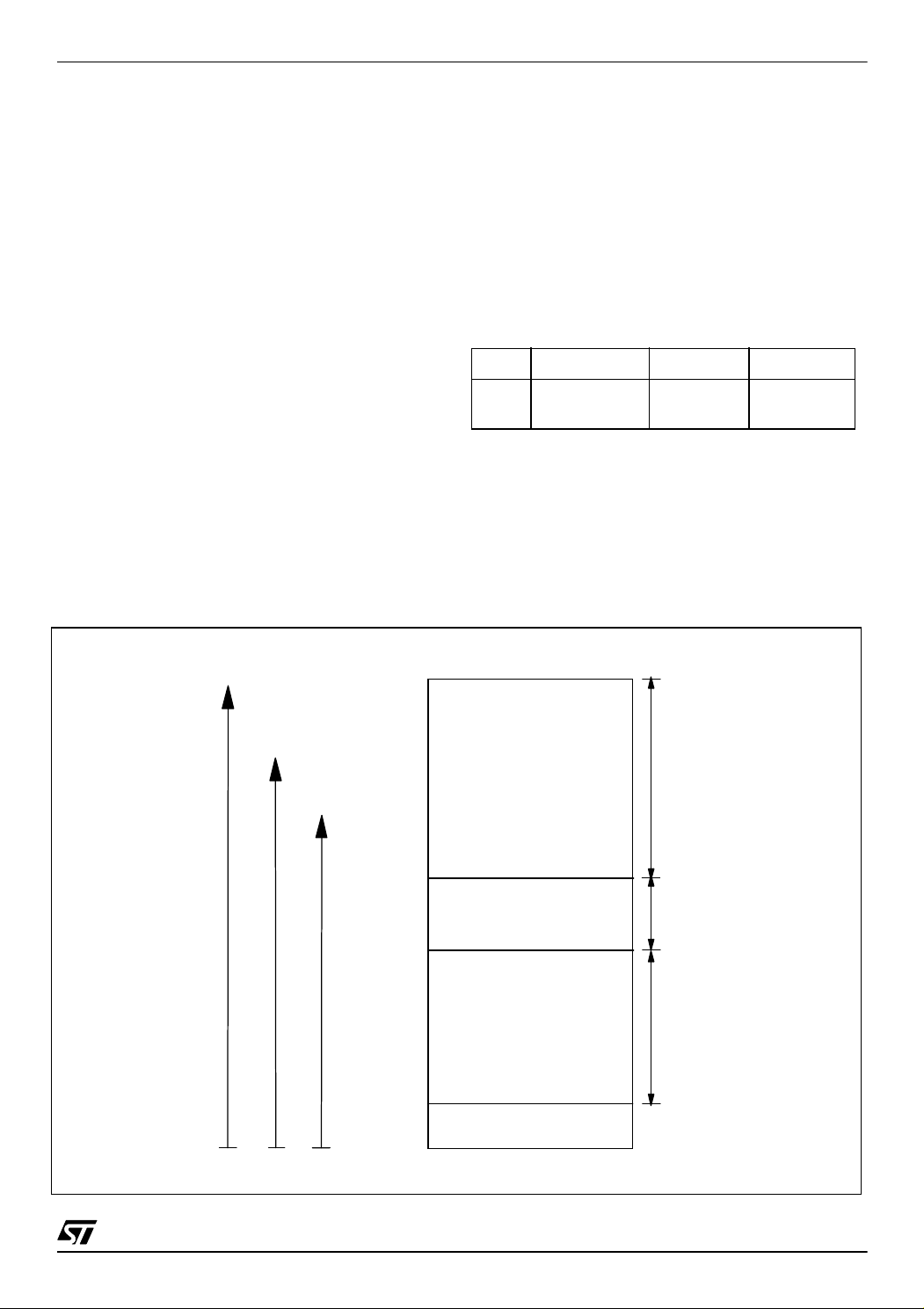

ST52x430 EPROM memory is divided into three

main blocks (see Figure ):

■

Interrupt Vectors memory block

(3 through 20)

contains the addresses for the interrupt routines.

Each address is composed of three bytes.

■

Mbfs Setting memory block

MemAdd

) contains the coordinates of the

(21 through

vertexes of every Mbf defined in the program.

■ The maximum value of MemAdd is 1023. This

area is dynamically assigned according to the

size of the fuzzy routines. The unused memory

area, if any, is assigned to the Program

Instruction Set memory block.

■ The Program Instructions Set memory block

(MemAdd through MemAddx) contains the

instruction set of the user program. The

following table summarizes the values of Mem

Addx for the different devices

Table 3.1 Mem Addx

ST52T430K1 ST52T430 ST52T430

Me

m

2047 4095 8191

Locations 0, 1 and 2 contain the address of the first

microcode instruction.Th e operations that can be

performed on EPROM during the Programming

Phase are: Stand By, Memory Writing, Reading

and Verify/Margin Mode, Memory Lock, IDCode

Writing and Verify.

Figure 3.1 Pro gra m M em ory Organizati on

ST52430K3

ST52430K2

ST52430K1

MemAdd+1

MemAdd

8191

4095

2047

21

20

Fuzzy and Boolean

Algorithms

Mbfs Parameters

INT_EXT

INT_SCI

INT_TIMER/PWM2

INT_TIMER/PWM1

INT_TIMER/PWM0

3

2

0

INT_ADC

Program Instruction

First Address

Program

Instruction

Set

Mbfs Setting

and Program

Instruction Set

Interrupt

Vectors

23/88

Page 24

ST52T430/E430

MEMORYVER

MARGINMOD

D

OUTV

D

VALIDDATA

DATAOUT

Table 3.2 EPROM Control Register

OPERATION REGISTER VALUE

Stand By 0

Memory Reading/Verify 1

The operations ab ove are managed by us ing the

internal 4-bit EPROM Control Register. The

reading phase is executed with V

the verify/Margin Mode phase needs V

5V±5%, while

PP=

PP

12V±5%. The Blank Check must be a reading

operation with V

PP=

5V±5%.

Table 3.2 illustrates EPROM Control Register

codes used to identify the operation running.

=

Memory Unlock and

Lock Status Reading

2

Memory Writing 3

Memory Lock 4

ID CODE Writing 5

Memory Lock Status

Reading/Verify

ID CODE Reading/

Verify

9

10

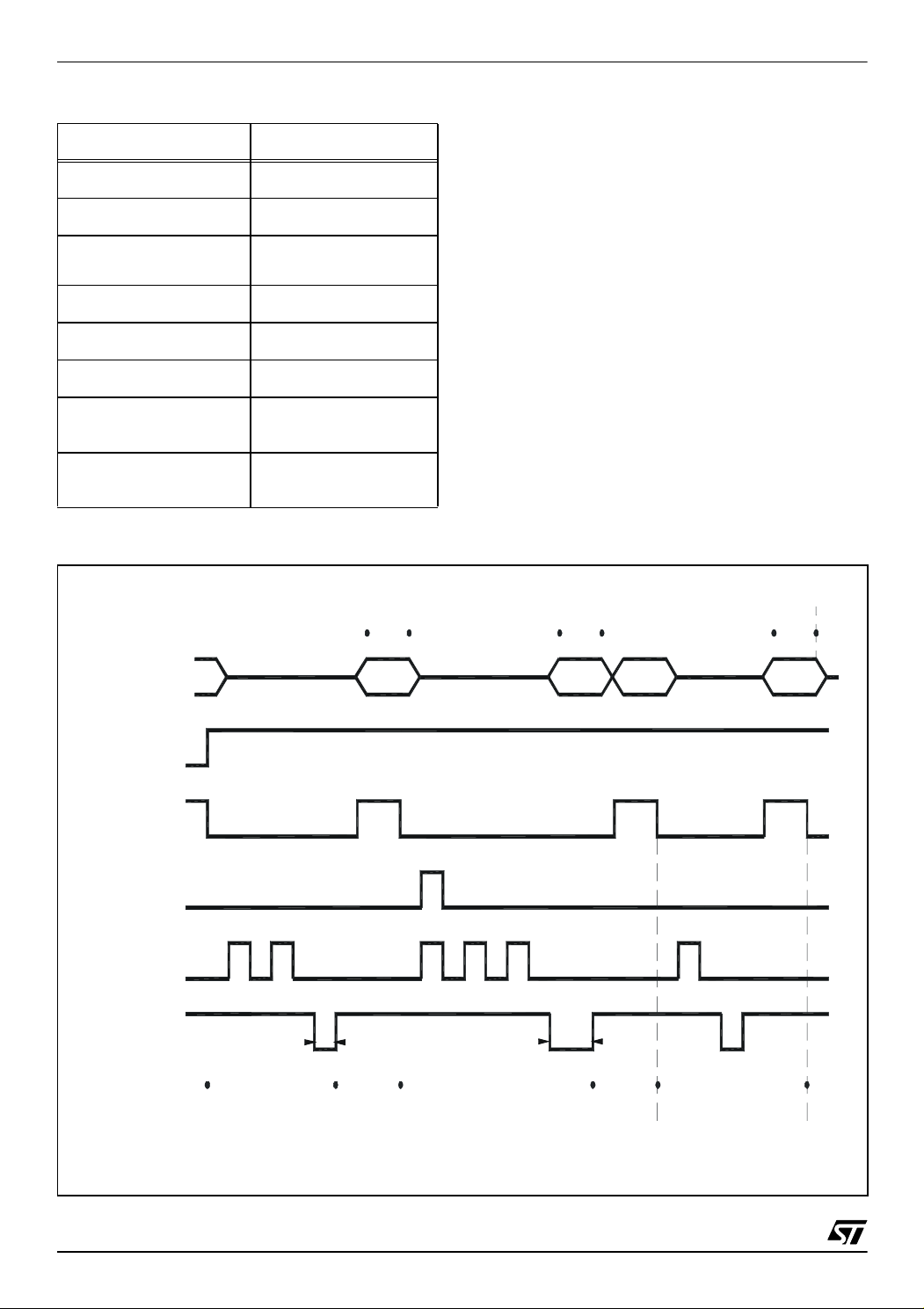

Figure 3.2 Eprom Programmi ng Timing

PA(0:7)

RST_ADD

ALID

ATA

ATA

3.1 EPROM Programming Phase Procedure

The Programming mode is selected by applying

12V±5% voltage or 5V ±5% voltage to the V

PP

pin

and setting the control signal as following:

RESET =Vss

TEST =Vss

If the V

performed.

voltage is 5V±5% only readi ng may be

PP

RST_ADD, INC_ADD, RST_CONF, INC_CONF

and PHASE are the control signals used during the

Programming Mode.

PHASE, RST_CONF and RST_ADD signals are

active on level, the others are active on rising

edge.

VALID

DATA

DATA

IN

DATA

OUT

RST_CONF

INC_ADD

INC_CONF

PHASE

MEMORY UNLOCK

24/88

100nS

MEMORY WRITING

LOCATION ADDRESS =1

10

S

µ

IFY

E

Page 25

ST52T430/E430

PHASE and RST_ADD signals are active low,

RST_CONF signal is active high.

Port A is used for the memory data I/O.

(See Table

3.2 for pin reference on the different packages)

Memory may be locked by means of the Memory

Lock Status, which is a flag used to enable

EPROM operations.

If Memory Lock Status is 1 all EPROM operations

are enabled, otherwise the user may only read

(and verify) the OTP code and the Memory Lock

Status.

Only if EPROM is not locked by means of Lock Cell

(see EPROM Locking may E PR O M o perations be

enabled by changing the Memory Lock Status from

0 to 1.

RST_ADD signal resets the memory address

register and the Memory Lock Status. When the

RST_ADD becomes high, the memory must be

unlocked in order to read or write.

INC_ADD signal increments the memory address.

RST_CONF signal resets the EPROM Control

Register. When RST_CONF is high, the DATA I/

O Port A is in outpu t, ot her wise it is alwa ys in

inpu t.

INC_CONF signal increments the EPROM Control

Register value.

PHASE signal validates the operation selected by

means of the EPROM Control Register value.

3.1.1 EPROM Operati on.

In order to execute an EPROM operation (See

Table 3.2), the corresponding identification value

must be loaded in the EPROM Control Register.

The signal timing is the f ollowing: RST_ADD= high

and PHASE= high, RST_CONF changes from low

to high level, to reset the EPROM Control Register,

and INC_CONF signal generates a number of

positive pulses equal to the value to be loaded.

After this sequence, a negative pulse of the

PHASE signal will validate the operation selected.

The minimum PHASE signal pulse width must be

10 µs for EPROM Writing Operation and 100 ns for

the others.

When RST_CONF is high, DATA I/O Port A is

enabled in output and the reading/verifying

operation results are available.

After a writing operation, when RST_CONF is high,

Port A is in output without valid data.

3.1.2 EPROM Locking.

The Memory Lock operation, which is identified

with the number 4 in the EPROM Control Register,

.

writes “0 " in t he Memory Loc k Cell.

At the beginning of an External Operation, when

the RST_ADD signal changes from low level to

high level, the Memory Lock Status is “0", therefore

it must be unlocked before proceeding.

In order to unlock the Memory Lock Status the

operation, which is identified by the number 2 in

the EPROM Control Register must be executed

(see Figure 3.2).

Memory Lock Status can be changed only if

Memory Lock Cell is “1". After a Memory Lock

operation external operat ions cannot b e executed

except to read (or veri fy) the OTP Code and the

Memory Lock Status.

3.1.3 EPROM Writing.

When the memory is blank, all bits are at logic level

“1". Data is introduced by programming only the

zeros in the desired memory location. However, all

input data must contain both ”1" and “0".

The only way to change “0" into ”1" is to erase the

entire memory (by exposure to Ultra Violet light)

and reprogram it.

The memory is in Writing mode when the EPROM

Control Register value is 3.

The V

voltage must be 12V±5%, with stable data

PP

on the data bus PA(0:7).

The timing signals are the following (see Figure ):

1) RST_ADD and RST_CONF change from low to

high level,

2) two pulses on INC_CONF signal load the

Memory Unlock operation code,

3) a negative pulse (10 0 ns) on the PHASE signal

validates the Memory Unlock operation,

4) a negative pulse on RST _CONF signal resets

the EPROM Control Register,

5) three positive pulses on INC_CONF load the

Memory Writing operation code,

6) a train of positive pulses on INC_ADD signal

increments the memory location address up to the

requested value (generally this is a sequential

operation and only one pulse is used),

7) a negative pulse (10 µs) on the PHASE signal

validates the Memory Writing operation.

25/88

Page 26

ST52T430/E430

3.1.4 EPROM Read/Verify Margin Mode.

The read phase is executed with V

instead of the verify phase that needs V

PP=

5V±5%,

PP

12V±5%.

The Memory Verify operation is available in order

to verify the accuracy of the data written. A

Memory Verify Margin Mode operation can be

executed immediately after writing each byte, in

this case (see Figure ):

1) a positive pulse on RST_CONF signal resets the

EPROM Control Register, if it wasn’ t already reset;

2) one positive pulse on INC_CONF loads the

Memory Read/Verify operation code;

3) a negative pulse (100 n s) o n t he PH AS E signal

validates the Memory Reading / Verify operation;

4) a negative pulse on RST_CONF signal put s in

the PA(0:7) port the value stored in the actual

memory address and resets the EP ROM Control

Register;

If an error occurred writing, the user has to repeat

EPROM writing.

3.1.5 Stan d by M ode.

EPROM has a standby m ode, which reduces the

active current from 10mA (Programming mode) to

less than 100 µA. Memory is placed in standby

mode by setting the PHASE signal at a high level

or when the EPROM Control Register value is 0

and the PHASE signal is low.

3.1.6 ID code.

A software identification code , cal led ID c ode m ay

=

be written in order to distinguish which software

version is stored in the memory.

64 Bytes are dedicated to store this code by using

the address values from 0 to 63.

The ID Code may b e read or verified even if the

Memory Lock Status is “0".

The timing signals are the same as that of a normal

operation.

3.2 Eprom Erasure

The transparent window available in the

CSDIP32W package, allows the memory co ntents

to be erased by exposure to UV light.

Erasure begins when the device is exposed to light

with a wavelength shorter than 4000Å. Sunlight, as

well as some types of artificial light, includes

wavelengths in the 3000-4000Å range which, on

prolonged exposure can cause erasure of memory

contents. Therefore, it is recommended that

EPROM devices be fitted with an opaque label

over the window area in order to prevent

unintentional erasure.

The erasure procedure recommended for EPROM

devices consists of exposure to short wave UV

light having a wavelength of 2537Å. The m inimum

integrated dose recommended (intensity x exposure time) for complete erasure is 15Wsec/cm 2.

This is equivalent to an erasure time of 15-20

minutes using a UV source having an in tensity of

12mW/cm 2 at a distance of 25mm (1 inch) from

the device window.

26/88

Page 27

ST52T430/E430

Global Interrupt

4 INTERRUPTS

The Control Unit (CU) responds to peripheral

events and external events via its interrupt

channels.

When such an events occur, if the related interrupt

is not masked and according to a priority order, the

current program execution can be suspended to

allow the CU to execute a specific response

routine.

Each interrupt is associated with an interrupt

vector that contains the memory address of the

related interrupt service routine. Each vector is

located in the Program Space (EPRO M Memory)

at a fixed address (see Interrupt Vectors Table

4.2).

4.1 Interrupt Operation

If there are pending interrupts at the end of an

arithmetic or logic instruction, the one with the

highest priority is passed. Passing an interrupt

means storing the arithmetic flags and the current

PC in the stack and executing the associated

Interrupt routine, whose address is located in three

bytes of the EPROM memory location between

address 3 and 20.

The Interrupt routine is performed as a normal

code, checking if a higher priority inte rrupt has to

be passed at the end of each instruction. An

Interrupt request with the higher priority stops the

lower priority Interrupt. The Program Counter and

the arithmetic flags are stored in the stack.

With the RETI (Return from Interrupt) instruction

the arithmetic flags and Program Counter (PC) are

restored from the top of the stack. This stack wa s

already described in section RAM and STACK.

An Interrupt request cannot stop processing of the

fuzzy rule, but this is passed only after the end of

a fuzzy rule or at the end of a logic, or arithmetic

instruction.

NOTE: A fuzzy routine can only be interrupted

in the Main program. An interrupt request

cannot stop a Fuzzy function that is running

inside another interrupt routine. In order to use

a Fuzzy function inside an interrupt routine, the

user MUST include the Fuzzy function between

an UDGI (MDGI) instruction and an UEGI

(MEGI) instruction (see the following

paragraphs), so that the interrupt request m ay

be disabled during the executio n of the fuzzy

function.

Figure 4.1 Interrupt Flow

NORMAL

PROGRAM

FLOW

INTERRUPT

SERV ICE

ROUTINE

INTERRUP T

RETI

INSTRUCTION

Figure 4.2 Interrupt Vectors mapping

3

4

INT_ADC

5

6

7

INT_TIMER/PWM0

8

9

10

INT_TIMER/PWM1

11

12

13

INT_TIMER/PWM2

14

15

16

INT_SCI

17

18

INT_EXT

19

20

INTERRUPT

VECTORS

Figure 4.3 Global Interrupt Request generation

Global In te rr up t

Pending

Reque st

User Global

Interr up t Mas k

4.2 Global Interrupt Request Enabling

When an Interrupt occurs, it generates a Global

Interrupt Pending (GIP), that can be masked by

software. After a GI P a Global Interrupt Reques t

(GIR) will be generated and Interrupt service

Macro Global

27/88

Page 28

ST52T430/E430

Routine associated to the interrupt with higher

priority will start.

In order to avoid possible conflicts between

interrupt masking set in the main program, or

inside high level language compiler macros, the

GIP is hung up through the User Global I nterrupt

Mask or the Macro Global Interrupt Mask (see

Figure 4.2).

UEGI/UDGI instruction switches on/off the User

Global Interrupt Mask, enabl ing/disabling the GIR

for the main program.

MEGI/MDGI instructions switch t he Macro Global

Interrupt Mask on/off, in order to ensure that the

macro will not be broken.

4.3 Interrupt Sources

ST52x430 manages interrupt signals generated by

the internal peripherals (PWM/Timers, UART and

Analog to Digital Converter) or coming from the

INT/PC0 pin. The External Interrupt can be

programmed to be active on the rising or falling

edge of INT/PC0 signal by setting the PEXTIN T bit

of the Configuration Register to 0.

WARNING:

interrupt request is generated.

Each peripheral can be programmed in order to

generate the associated interrupt; further details

are described in the related chapter.

4.4 Interrupt Maskability

The interrupts can be masked by configuring the

REG_CONF 0 by means of LDCR, or LDCE,

instruction. The interrupt is enabled when the bit

associated to the mask interrupt is “1". Viceversa,

when the bit is ”0", the interrupt is ma sked and is

kept pendent.

For example:

LDRC 10,6 //load the constant 6 in the

RAM Register 10

LDCR 0, 10 // set the CONF_REG 0 with

the value stored in the RAM Register

10

the result is CONF_REG0 =00000110 enabling the

interrupts deriving from the ADC (INT_ADC) and

from the PWM/TIMER 0 (INT_PWM/TIMER0).

Changing the interrupt priority an

Table 4.1 Configuration Register 0

Description

Bit Name Value Description

0

0MSKE

1

0

1 MSKAD

1

0

2 MSKTM0

1

0

3 MSKTM1

1

0

4 MSKTM2

1

0

5MSCI

1

0

6 PEXTINT

1

External Interrupt

Masked

External Interrupt

Not Masked

A/D Converter

Interrupt

Masked

A/D Converter

Interrupt

Not Masked

PWM/TIMER

0Interrupt

Masked

PWM/TIMER 0

Interrupt

Not Masked

PWM/TIMER 1

Interrupt

Masked

PWM/TIMER 1

Interrupt

Not Masked

PWM/TIMER 2

Interrupt

Masked

PWM/TIMER 2

Interrupt

Not Masked

SCI Interrupt

Masked

SCI Interrupt Not

Masked

External Interrupt

Polarity

Active on Rising

External Interrupt

Polarity

Active on Falling

28/88

7 Not used

Reset Configuration ‘000000’

Page 29

Table 4.2 Interrupts Description

ST52T430/E430

Name Description Priority

INT_ADC ADC Int Programmable 000 yes 3-5

INT_PWM/

TIMER0

INT_PWM/

TIMER1

INT_PWM/

TIMER2

INT_SCI SCI Int Programmable 100 yes 15-17

INT_EXT

Figure 4.4 Interrupt Configuration Register 0

PWM/TIMER 0 Int Programmable 001 yes 6-8

PWM/TIMER 1 Int Programmable 010 yes 9-11

PWM/TIMER 2 Int Programmable 011 yes 12-14

External

Interrupt (INT)

Ext Highest - yes 18-20

Peripheral

Code

Maskable

REG_CONF0

Interrupts Mask

EPROM

Locations

D0

D1D2D3D4D5D6D7

MSKE: Ext. Int.

MSKAD: A/D Int.

M SK TM0 : Time r 0 I n t.

M SK TM1 : Time r 1 I n t.

M SK TM2 : Time r 2 I n t.

M SCI: SC I In t.

PEXTINT: Ext. Int. Polariry

Not Used

29/88

Page 30

ST52T430/E430

Figure 4.5 Interrupt Configuration Register 17 & 18

Interrup ts P rior ity

REG_CONF1 8

D10D1 1D12D13D14D15

D8D9

4.5 Interrupt Priority

Seven priority levels are available: level 6 has the

lowest priority, level 0 has the highest priority.

Level 6 is associated to the Main Program, levels 5

to 1 are programmable by means of the priority

registers called REG_CONF17 and

REG_CONF18 (see Figure 4.5 and Table 4.3);

whereas the higher level is related to the external

interrupt (INT_EXT).

PWM/Timers, UART and ADC are ident ified by a

three-bit Peripheral Codes (see Table 4.2); in order

i

to set the

peripheral label

-th priority level the user must write the

i

in the related INTi priority le v el.

i.e.

LDRC 10, 193 //(load the value

193=’11000001’ in the RAM Register 10)

LDRC 11, 168 //(load the value

168=’10101000’ in the RAM Register 11)

LDCR 17, 10 // set the REG_CONF17=

‘11000001’

LDCR 18, 11 // set the REG_CONF18=

‘10101000’

The following priority levels are defined:

■ Level 1: INT_PWM/TIMER0 (PWM/TI MER 0

Code: 001)

■ Level 2: INT_ADC (ADC Code: 000)

REG_CONF17

D0D1D2D3D4D5D6D7

INT 1

INT 2

INT 3

INT 4

INT 5

Not Used

Table 4.3 Conf. Register 17 & 18 Description

Bit Name Value Level

0, 1,2 INT1

3, 4,5 INT2

6,7,8 INT3

9,10,11 INT4

12,13,1

4

■ Level 3: Int_PWM/Timer2 (PWM/TIMER 2

INT5

Periphera

l Code

Periphera

l Code

Periphera

l Code

Periphera

l Code

Periphera

l Code

High

Medium-High

Medium-Low

Low

Very Low

Code: 011)

■ Level 4: INT_UART (UART Code: 100)

■ Level 5: INT_PWM/TIMER1 (PWM/TIMER 1

Code: 010)

30/88

Page 31

Figure 4.6 Examp le of a sequence of Interrupt req uests

Table 4.4 RINT Instruction code

PRIORITY

LEVEL

0

INT2 INT0 INT4 INT1 INT3

INT0

ST52T430/E430

Peripheral Name Value

PWM/TIMER 1 2

1

2

3

4

5

6

MAIN PROGRAM

INT2

REMARK: The Interrupt priority must be set at

the beginning of the main program, because at

the RESET REG_CONF1=’00000000’, this

condition could generate wrong operations.

Further, changing the priority levels must be

avoided in interrupt service routines.

When a source provides an In terrupt request and

the request processing is also enabled, the CU

changes the normal sequential flow of a program

by transferring program control to a selected

service routine.

When an interrupt occurs the CU executes a JUMP

instruction to the address loaded in the related

location of the Interrupt Vector.

When the execution returns to the original program

it immediately begins following the in struction that

was interrupted.

INT1

INT2

PWM/TIMER 2 3

SCI 4

INT2

External Interrupt 5

INT3

INT4

MAIN PROGRAM

4.6 Interrupts and Low power mode

All interrupts allow the processor to leave the WAIT

low power mode. Only the external Interrupt allows

the processor to leave the HALT low power mode.

4.7 Interrupt RESET

An eventually pending interrupt can be reset with

the instruction RINT j, which rese ts the interrupt

j

-th where j identifies the peripherals as described

in the following table (see Table 4.4).

The assembler instruction:

RINT 2

Resets the PWM/Timer 1 interrupt.

Note: The RINT command must be preceded

from a UDGI (or M DGI ) co mm and an d followed

by a UEGI (or MEGI) command.

Table 4.4 RINT Instruction code

Peripheral Name Value

A/D Converter 0

PWM/TIMER 0 1

WARNING: If an interrupt is reset, with the RINT

instructi on wi t hi n its own interrupt routi ne, the

priority level of the interrupt becomes the

lowest and the routine can be immediately

interrupted by a lower priority interrupt

request.

31/88

Page 32

ST52T430/E430

5 CLOCK, RESET & POWER SAVING MODE

5.1 System Clock

The ST52x430 Clock Generator module generates

the internal clock for the internal Control Unit, ALU

and on-chip peripherals and it is designed to

require a minimum number of external

components.

The ST52x430 oscillator circuit generates an

internal clock signal with the same period and

phase as that of the OSCin input pin. The

maximum frequency allowed is 20 Mhz.

Note: When the SCI peripheral is used only a 5,

10, or 20 MHz system clock must be used.

The system clock may be generated by using

either a quartz crystal, ceramic resonator or an

extern al clock.

The different methods of the clock generator are

illustrated in Figure 5.1.

When an external clock is used, it must be

connected on the OSCin pin, while OSCout can be

floating.

The crysta l oscilla tor st art-up tim e is a function of

many variables: crystal parameters (especially

), oscillator load capacitance (CL), IC

R

s

parameters, environment temperature, supply

voltage.

Figure 5.1 Oscillator Connections

Note: The crystal or ceramic leads and circuit

connections must be as short as possible. Typical

values for CL1, CL2 are 10pF for a 20 MHz crystal.

5.2 RESET

There are two Reset sources:

- RESET pin (external source.)

- WATCHDOG (internal source)

When a Reset event happens, the user program

restarts from the beginning.

The Reset pin is an i nput. An internal reset does

not affect this pin.

A Reset signal originated by external sources is

recognized instantaneously. The RESET pin may

be used to ensure V

has risen to a point where

DD

the MCU can operate correctly before the user

program runs. In working mode Reset must be set

to ‘1’ (see Table 2.1).

5.3 Power Saving Mode

There are two Power Saving modes: WAIT and

HALT mode. These conditions may be entered

using the WAIT or HALT instructions.

5.3.1 Wait Mode

Wait mode places the MCU in low power

consumption by stopping the CPU. All peripherals

32/88

CRYSTAL CLOCK EXTERNAL CLOCK

ST52X430

OSCin OSCout

Cl1

10pF

Cl2

10pF

ST52X430

OSCin

CLOCK

INPUT

OSCout

Page 33

ST52T430/E430

and the watchdog remain active. During WAIT

mode, Interrupts are enabled. The MCU will

remain in Wait mode until an Interrupt or a RESET

occurs, whereupon the Program Counter jumps to

the interrupt service routine or, if a RESET occurs,

at the beginning of the user program.

REMARK: In Wait mode the CPU clock does not

stop.

5.3.2 Halt Mode

Halt mode is MCU’s lowest power consumption

mode, which is entered by executing the HALT

instruction. The internal oscillator is turned off,

causing all internal processing to stop, including

the operations of the on-chip peripherals.

Figure 5.2 Reset Block Diagram

RESET INTERNAL

RESET

Halt mode can not be u sed when the watch do g

is enabled.

If the HALT instruction is executed while the

watchdog system is enabled, it will be skipped

without modifying the normal CPU operations.

The ICU can exit Halt mode after an external inter-

rupt or reset. The oscillator is then turned on and

stabilization time is provided before restarting

CPU operation s. Stabilization time is 4096 CPU

clock cycles after the interrupt and 1.000.000 after

the Reset.

After the start up delay, the CPU restarts operations by serving the external interrupt routine.

Reset makes the ICU exit f rom HALT mode and

restart, after the delay, from the beginning of the

user program after the delay.

Warning: if the External Interrupt is disabled, the

ICU exits from the Halt mode and jumps to the

lower priori t y in te rru pt rou tine.

Figure 5.4 WAIT Flow Chart

WATCHDOG RESET

Figure 5.3 Simple Reset Circuit

Vcc

100 F 10k

2.2k 2.2k 1 F

RESET

33/88

Page 34

ST52T430/E430

Figure 5.5 HALT Flow Chart

HALT INSTRUCTION

YES

HALT INSTRUCTION

SKIPPED

OSCILLATOR OFF

PERIPHERALS CLOCK OFF

CPU CLOCK OFF

NO

RESET

YES

OSCILLATOR ON

PERIPHERALS CLOCK ON

CPU CLOCK ON

1000000 CPU CLOCK

CYCLES DELAY

NO

WATCHDOG

ENABLED

NO

EXTERNAL

INTERRUPT

YES

OSCILLATOR ON

PERIPHERALS CLOCK ON

CPU CLOCK ON

4096 CPU CLOCK

CYCLES DELAY

34/88

RESET CPU

AND RESTART

USER PROGRAM

NO

RESTART PROGRAM

SERVICING THE

LOWER PRIORITY

INTERRUPT ROUTINE

EXTERNAL

INTERRUPT

ENABLED

YES

RESTART PROGRAM

SERVICING THE

EXTERNAL

INTERRUPT ROUTINE

Page 35

ST52T430/E430

6 I/O PORTS

6.1 In troduc t ion

ST52x430 devices feature flexible individually

programmable multi-functional input/output lines.

Refer to the following figure for specific pin

allocations.

23 I/O lines, grouped in 3 different ports are

available on the ST52x430:

PORT A = 7 or 8-bit ports (PA0 - PA7 pins)

PORT B = 7 or 8-bit ports (PB0 - PB7 pins)

PORT C = 8-bit port (PC0 - PC7 pins)

PIN 24 in the SO34 or PIN 22 in the PDIP32 can be

configured to belong to port A or to port B.

These I/O lines can be programmed to provide