Page 1

TECHNICAL DATA

Semiconductor

1

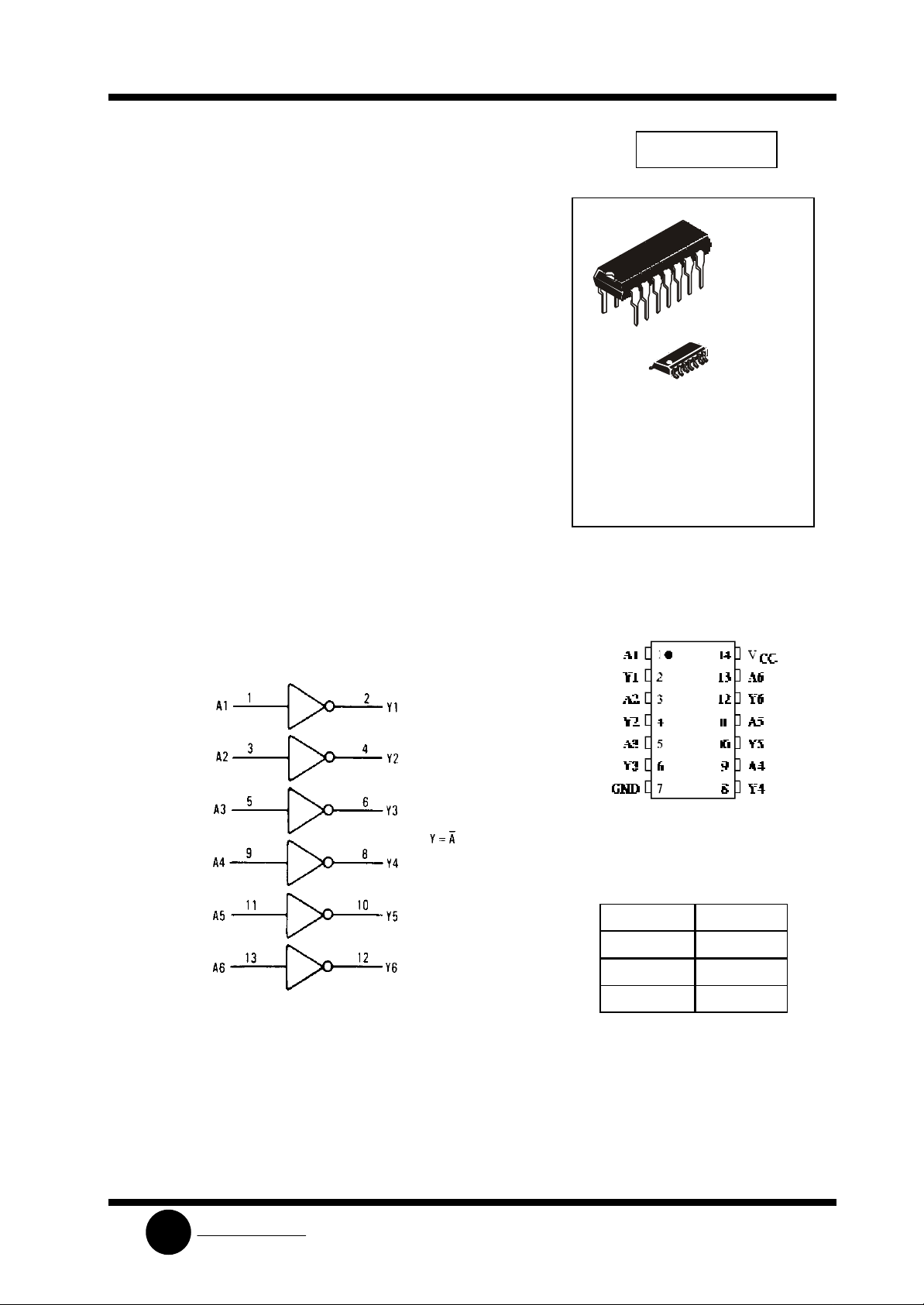

Hex Inverter

The 74LVU04 is a low -voltage, Si-gate CMOS device and is pin

compatible with the 74HCU04.

The 74LVU04 is a general purpose hex inverter. Each of the six

inverters is a single stage with unbuffered outputs.

• Wide Operating Voltage: 1.0÷5.5 V

• Optimized for Low Voltage applications: 1.0÷3.6 V

• Accepts TTL input levels between VCC =2.7 V and VCC =3.6 V

• Low Input Current

SL74LVU04

N SUFFIX

PLASTIC

14

1

14

ORDERING INFORMATION

SL74LVU04N Plastic

SL74LVU04D SOIC

SL74LVU04 Chip

TA = -40° ÷ 125° C for all packages

D SUFFIX

SOIC

LOGIC DIAGRAM

PIN 14 =VCC

PIN 7 = GND

PIN ASSIGNMENT

FUNCTION TABLE

Input Output

A Y

L H

H L

SLS

System Logic

1

Page 2

SL74LVU04

Semiconductor

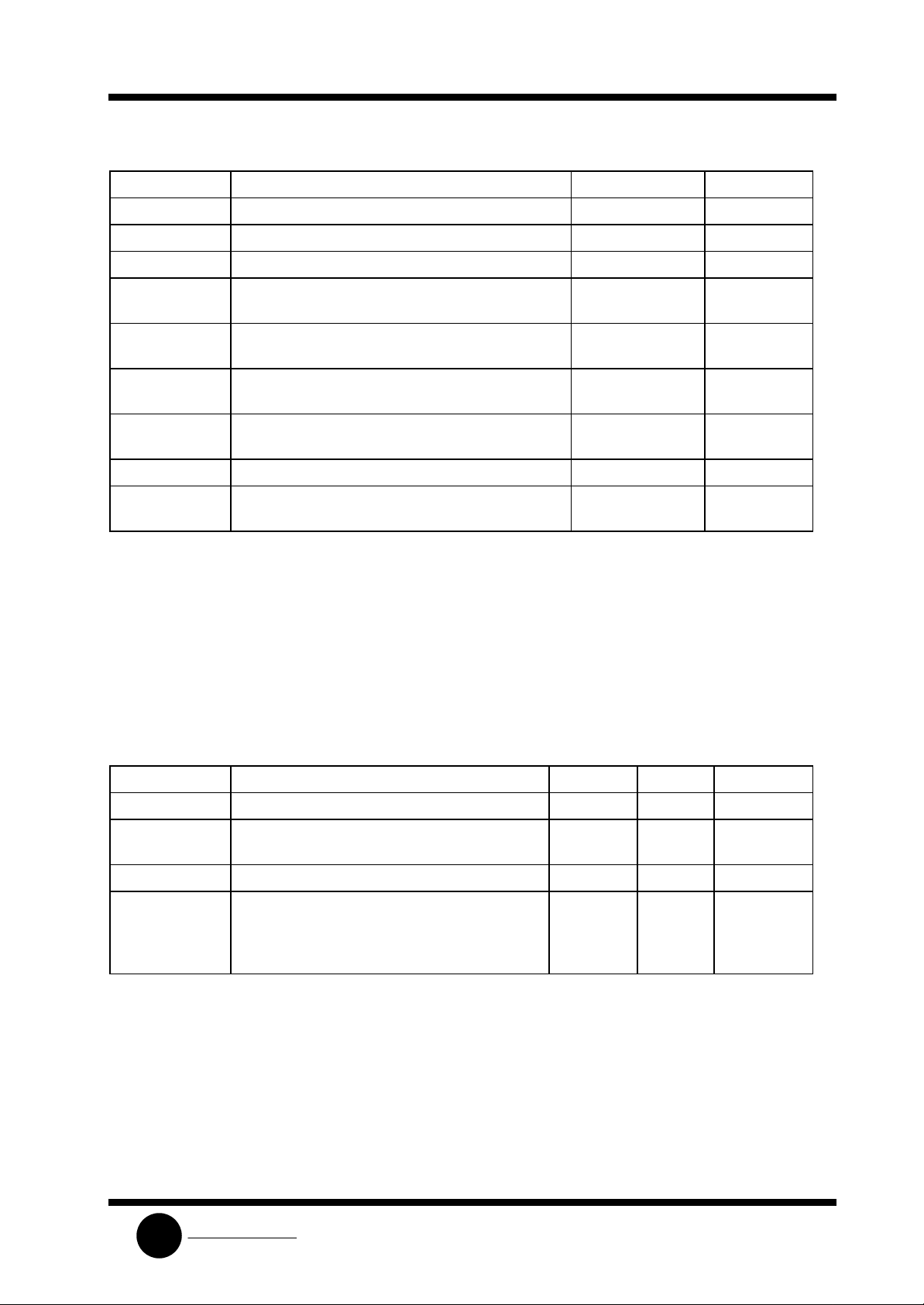

MAXIMUM RATINGS

*

Symbol Parameter Value Unit

VCC DC supply voltage (Referenced to GND) -0.5 ÷ +7.0 V

IIK *1 DC input diode current ±20 mA

IOK *2 DC output diode current ±50 mA

IO *3 DC output source or sink current

±25 mA

-bus driver outputs

ICC DC VCC current for types with

±50 mA

- bus driver outputs

I

DC GND current for types with

GND

±50 mA

- bus driver outputs

PD Power dissipation per package, plastic DIP+

SOIC package+

750

500

Tstg Storage temperature -65 ÷ +150 °C

TL Lead temperature, 1.5 mm from Case for 10 se conds

260 °C

(Plastic DIP ), 0.3 mm (SOIC Package)

*

Maximum Ratings are those values beyond which damage to the device may occur.

Functional operation should be restricted to the Recommended Operating Conditions.

+Derating - Plastic DIP: - 12 mW/°C from 70° to 125°C

SOIC Package: : - 8 mW/°C from 70° to 125°C

*1: VI < -0.5V or V

> VCC+0.5V

I

*2: Vo < -0.5V or Vo > VCC+0.5V

*3: -0.5V < Vo < VCC+0.5V

mW

RECOMMENDED OPERATING CONDITIONS

Symbol Parameter Min Max Unit

VCC DC Supply Voltage (Referenced to GND) 1.0 5.5 V

VIN, V

fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages

to this high-impedance circuit. For proper operation, VIN and V

V

)≤VCC.

OUT

outputs must be left open.

DC Input Voltage, Output Voltage (Referenced

OUT

0 VCC V

to GND)

TA Operating Temperature, All Package Types -40 +125 °C

tr, tf Input Rise and Fall Time 1.0 V ≤VCC <2.0 V

2.0 V ≤VCC <2.7 V

2.7 V ≤VCC <3.6 V

3.6 V ≤VCC ≤5.5 V

0

0

0

0

500

200

100

50

ns

This device contains protection circuitry to guard against damage due to high static voltages or electric

should be constrained to the range GND≤(VIN or

OUT

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or VCC). Unused

SLS

System Logic

2

Page 3

Semiconductor

DC ELECTRICAL CHARACTERISTICS (Voltages Referenced to GND)

SL74LVU04

VIH High-Level

Input Voltage

VIL Low -Level

Input Voltage

VOH High-Level

Output Vol tage

Test

Conditions

VCC,

V

1.2

2.0

2.7

3.0

3.6

4.5

5.5

1.2

2.0

2.7

3.0

3.6

4.5

5.5

VI = V

I0=-100 ìA

IH or VIL

1.2

2.0

2.7

3.0

3.6

4.5

5.5

Guaranteed Limit

25°C -40°C ÷ 85°C -40°C ÷ 125°C Symbol Parameter

min max min max min max

1.0

1.6

2.4

2.4

2.4

3.6

4.4

-

-

-

-

-

-

-

1.05

1.85

2.55

2.85

3.45

4.35

5.35

1.0

0.2

0.4

0.5

0.5

0.5

0.9

1.1

-

-

-

-

-

-

-

1.6

2.4

2.4

2.4

3.6

4.4

-

-

-

-

-

-

-

1.0

1.8

2.5

2.8

3.4

4.3

5.3

0.2

0.4

0.5

0.5

0.5

0.9

1.1

-

-

-

-

-

-

-

1.0

1.6

2.4

2.4

2.4

3.6

4.4

-

-

-

-

-

-

-

1.0

1.8

2.5

2.8

3.4

4.3

5.3

V

0.2

0.4

0.5

0.5

0.5

0.9

1.1

-

-

-

-

-

-

-

Unit

V

V

VOL Low-Level

Output Vol tage

VI = V

I0=-6.0 mA

VI = V

I0=-12 mA

VI = V

I0=100 ìA

VI = V

IH or VIL

IH or VIL

IH or VIL

IH or VIL

3.0 2.48 - 2.40 - 2.20 -

4.5 3.70 - 3.60 - 3.50 -

1.2

2.0

2.7

3.0

3.6

4.5

5.5

3.0

-

-

-

-

-

-

-

- 0.33

I0=6.0 mA

VI = V

IH or VIL

4.5

- 0.40

I0=12 mA

IIL Low-Level

VI=0 V 5.5 - -0.1 - -1.0 - -1.0 ìA

Input Leakage

Current

DC ELECTRICAL CHARACTERISTICS (continuation)

Conditions

VCC,

25°C -40°C ÷ 85°C -40°C ÷ 125°C

0.15

0.15

0.15

0.15

0.15

0.15

0.15

-

-

-

-

-

-

-

0.2

0.2

0.2

0.2

0.2

0.2

0.2

-

-

-

-

-

-

-

- 0.40 - 0.50

- 0.55 - 0.65

Guaranteed Limit Symbol Parameter Test

0.2

0.2

0.2

0.2

0.2

0.2

0.2

V

Unit

SLS

System Logic

3

Page 4

SL74LVU04

Semiconductor

IIH High-Level

VI= VÑÑ 5.5 - 0.1 - 1.0 - 1.0

V

Input Leakage

Current

ICC Quiescent

Supply Current

(per Package)

I

Additional

CC1

Quiescent

VI=0 Â or V

IO = 0 ìA

VI = V

- 0.6V 2.7

ÑÑ

5.5 - 4.0 - 20 - 40 ìA

ÑÑ

3.6

Supply Current

on input

AC ELECTRICAL CHARACTERISTICS (C

VCC

V

1.2

2.0

2.7

3.0

4.5

t

PHL

(t

Propagation

PLH)

Delay, Input A

to Output Y

(Figure 1 )

Test

Conditions

VI=0 V or

V

1

tLH = tHL

=2.5 ns

ÑL = 50 pF

RL = 1 kÙ

min max min max min max

-

-

0.2

0.2

-

-

0.5

0.5

-

0.85

-

0.85

-

=50 pF, tLH =tHL = 2.5 ns, RL=1 kÙ)

L

Guaranteed Limit

25°C -40°C ÷ 85°C -40°C ÷ 125°C Symbol Parameter

Min max min max min max

-

-

-

-

-

70

22

16

13

11

-

-

-

-

-

80

26

19

15

13

-

100

-

-

-

-

31

23

18

16

mA

Unit

ns

CI Input

5.5

Capacitance

Used to determine the no-load dynamic power consumption:

P

= CPDV

D

(CLV

2

fI+ (CLV

CC

2

fo) – sum of the outputs

CC

2

fo), fI - input frequency, fo - output frequency (MHz)

CC

- 7.0 - - - -

ÒÀ=25°Ñ, VI=0V or VCC pF CPD Power Dissipation Capacitance (Per Inverter)

36

pF

SLS

System Logic

4

Page 5

SL74LVU04

Semiconductor

GENERATOR

PULSE

Input À

Output Y

VX=0.5 VCC

0.1

t

H L

0.9

V

X

t

P HL

V

Y

0.9

t

L H

V

1

V

X

0.1

t

P L H

V

Y

GND

V

V

OH

OL

Figure 1. Switching Waveforms

V

CC

V

I

DEVICE

UNDER

R

TEST

T

V

O

C

L

Termination resistance RT – should

be equal to Z

R

L

of pulse generators

OUT

Figure 2. Test circuit

SLS

System Logic

5

Page 6

Semiconductor

1.42 0.03

±

1.33 0.03

±

CHIP PAD DIAGRAM SL74LVU04

SL74LVU04

13

12

11

10

14

01

02

03

Chip marking

IN74LVU04

(x=0.130; y=0.130

Pad size 0.108 x 0.108 mm (Pad size is given as per metallization layer)

Thickness of chip 0.46 ± 0,02 mm

04 05 06

)

09

08

07

PAD LOCATION

Pad No Symbol X Y

01 A1 0.130 0.463

02 Y1 0.130 0.230

03 A2 0.381 0.126

04 Y2 0.616 0.126

05 A3 0.881 0.126

06 Y3 1.116 0.126

07 GND 1.115 0.631

08 Y4 1.115 0.846

09 A4 1.115 1.181

10 Y5 0.804 1.194

11 A5 0.569 1.194

12 Y6 0.378 1.194

13 A6 0.143 1.194

14 VCC 0.130 0.813

SLS

System Logic

6

Loading...

Loading...