Page 1

Microcomputer Components

8-Bit CMOS Microcontroller

C540U / C541U

Data Sheet 10.97

Page 2

C540U/C541U Data Sheet

Revision History : 1997-10-01

Previous Releases : none (Original Version)

Page / Chapters Subjects (changes since last revision)

Edition 1997-10-01

Published by Siemens AG,

Bereich Halbleiter, MarketingKommunikation, Balanstraße 73,

81541 München

©

Siemens AG 1997.

All Rights Reserved.

Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes

and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies

and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact

your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will

take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components

written approval of the Semiconductor Group of Siemens AG.

1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the

failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain hu-

man life. If they fail, it is reasonable to assume that the health of the user may be endangered.

1

of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems

2

with the express

Page 3

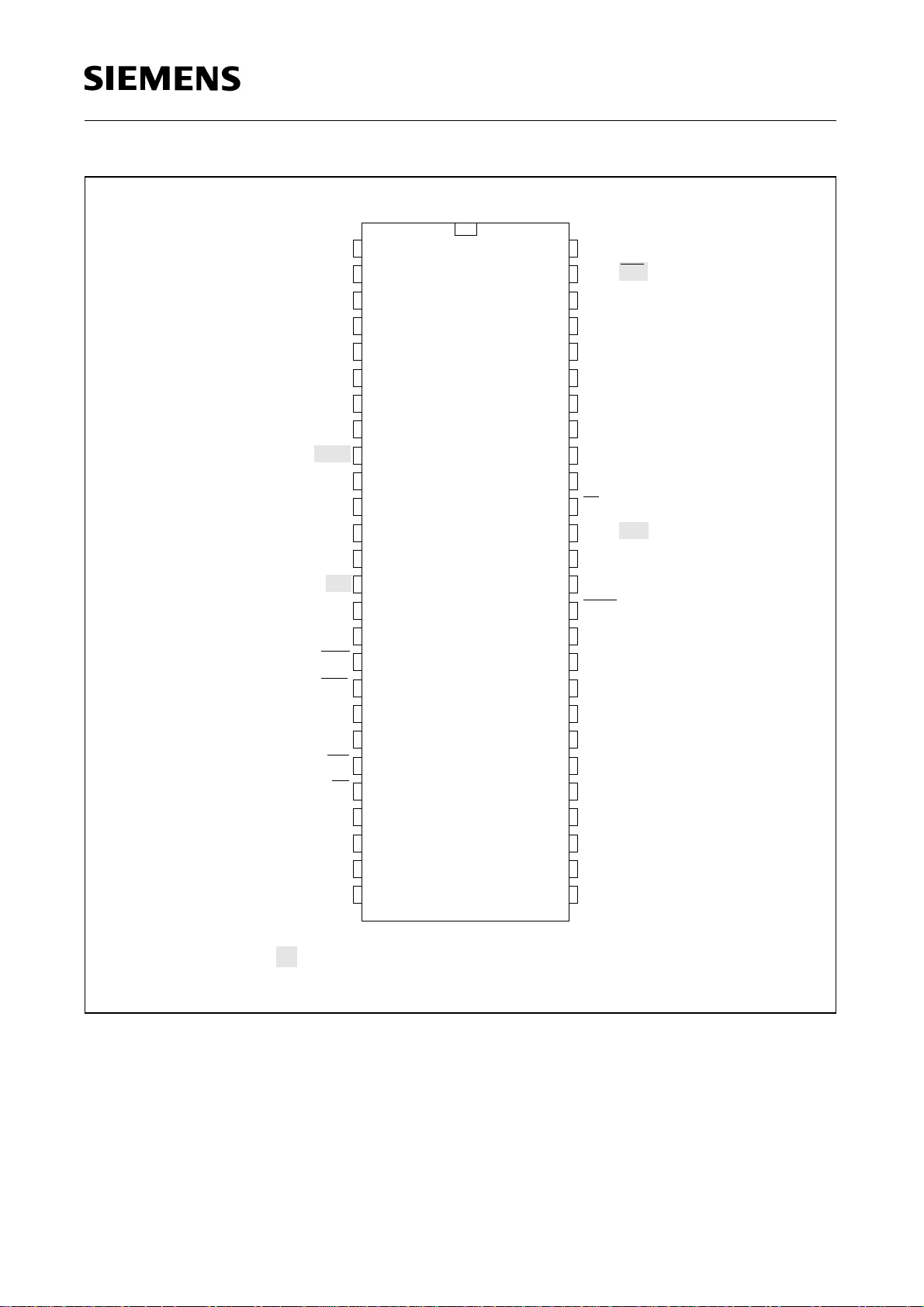

8-Bit CMOS Microcontroller

Advance Information

C540U

C541U

Enhanced 8-bit C500 CPU

•

– Full software/toolset compatible to standard 80C51/80C52 microcontrollers

12 MHz external operating frequency

•

– 500 ns instruction cycle

Built-in PLL for USB synchronization

•

On-chip OTP program memory

•

– C540U : 4K byte

– C541U : 8K byte

– Alternatively up to 64K byte external program memory

– Optional memory protection

On-chip USB module

•

– Compliant to USB specification

– Full speed or low speed operation

– Five endpoints : one bidirectional control endpoint

four versatile programmable endpoints

– Registers are located in special function register area

– On-chip USB transceiver

Oscillator

Watchdog

Power

Saving

Modes

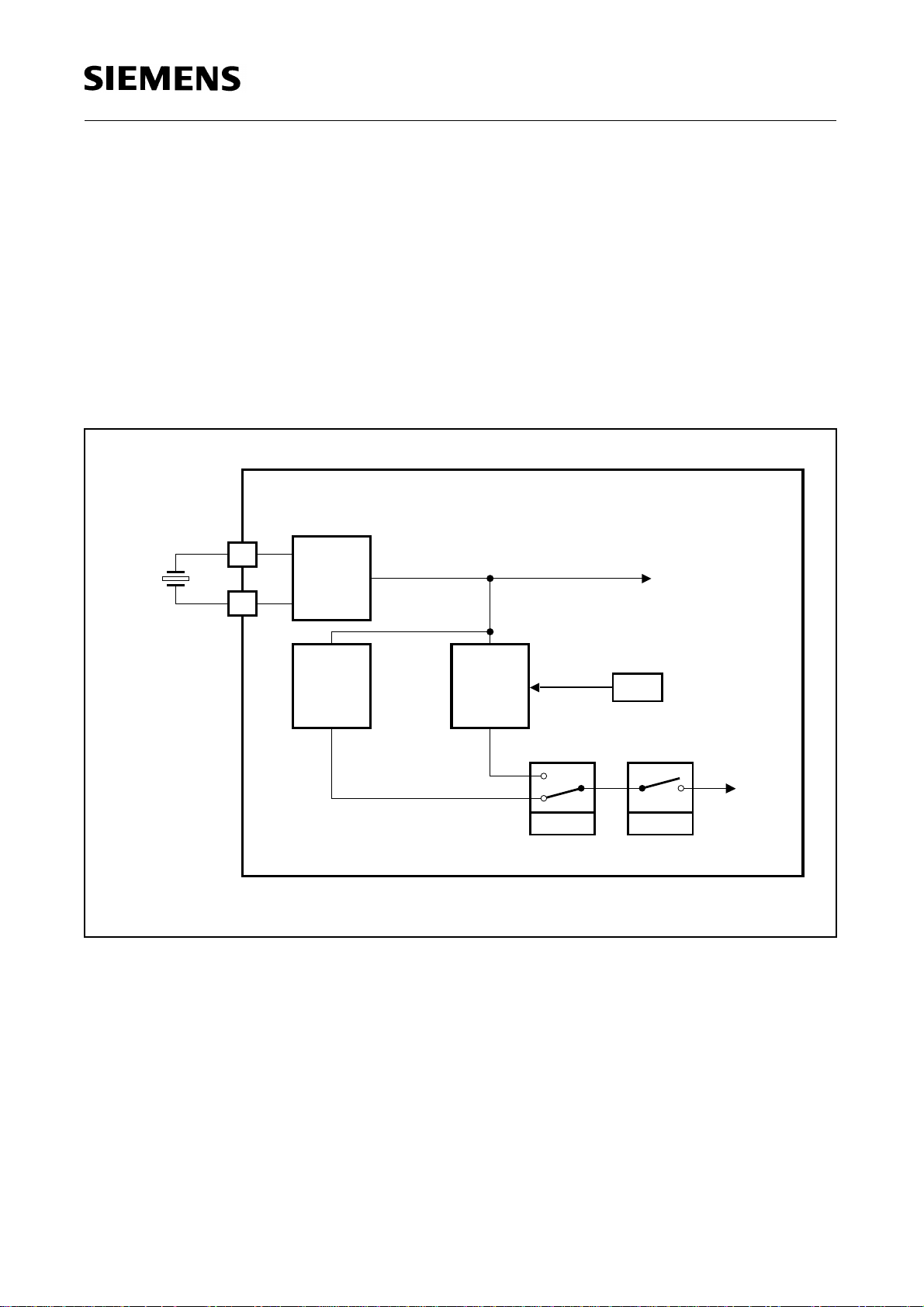

On-Chip Emulation Support Module

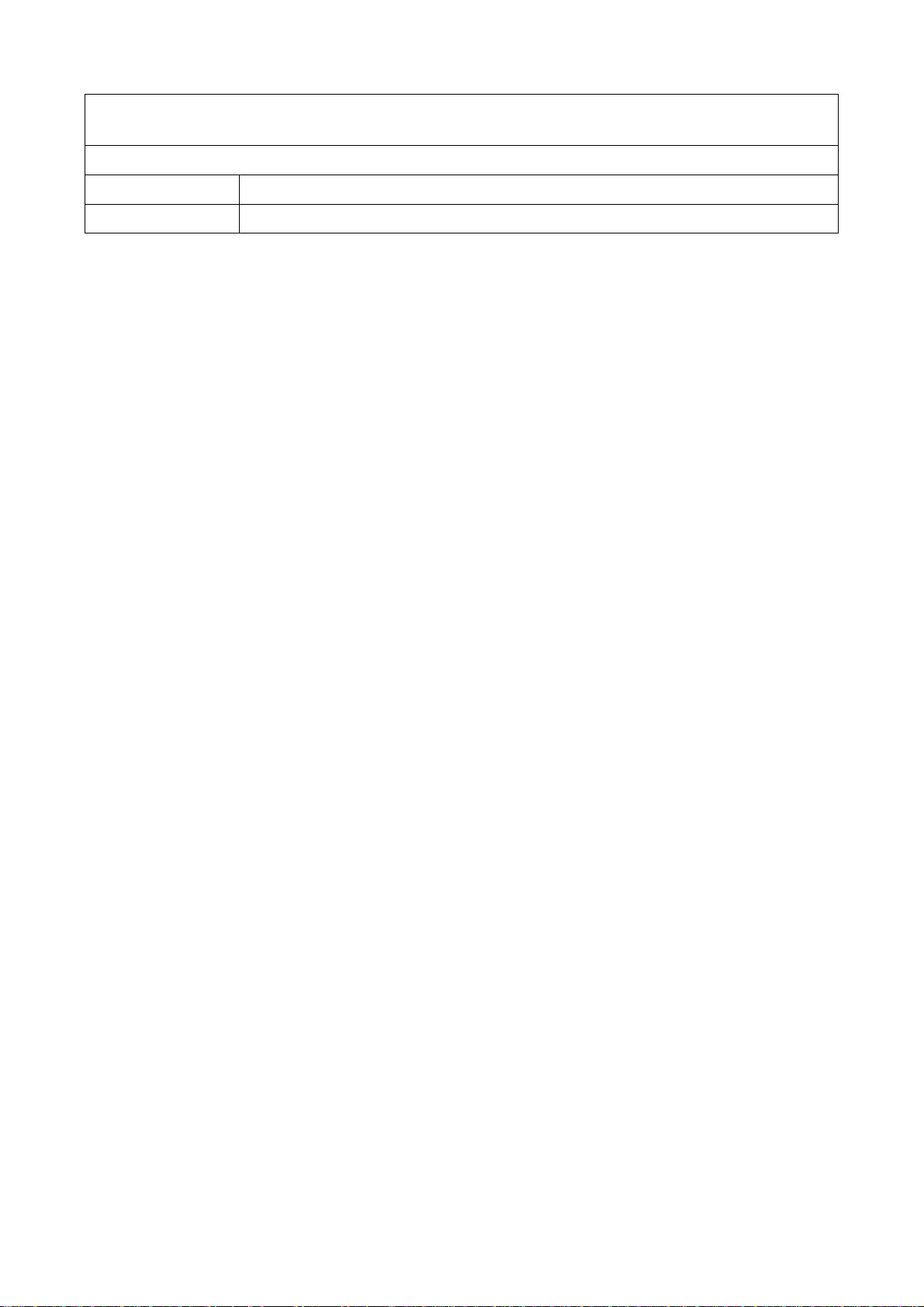

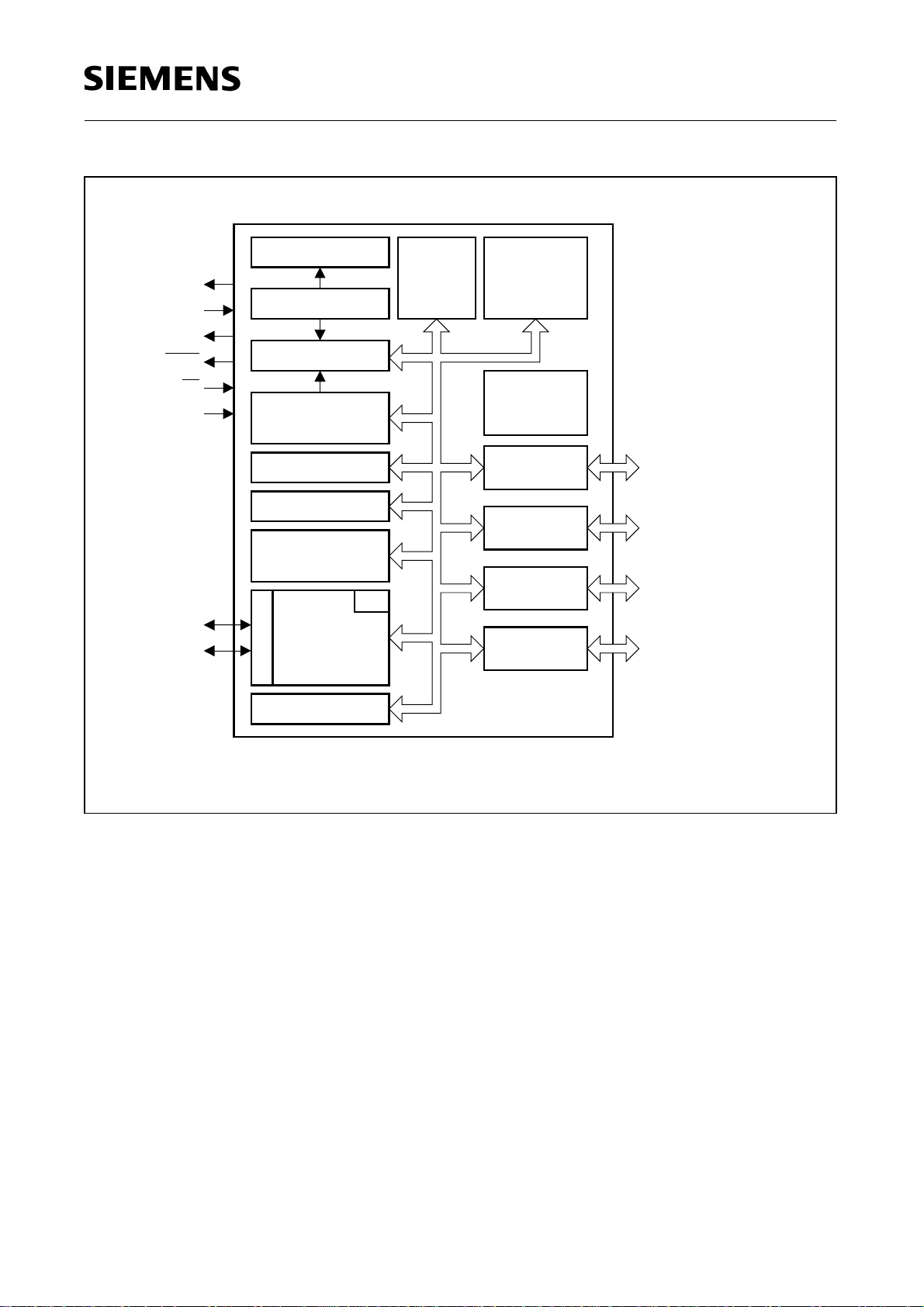

The shaded units are not available in the C540U.

Semiconductor Group 3 1997-10-01

Watchdog

Timer

SSC T0

USB

Module

USB Transceiver

D+ D-

T1

RAM

256 x 8

CPU

OTP Prog. Memory

C540U : 4 k x 8

C541U : 8 k x 8

Port 0

Port 1

Port 2

Port 3

I/O

I/O

I/O

I/O

MCA03373

Page 4

Features (cont’d) :

•

Up to 64K byte external data memory

•

256 byte on-chip RAM

•

Four parallel I/O ports

– P-LCC-44 package : three 8-bit ports and one 6-bit port

– P-SDIP-52 package : four 8-bit ports

– LED current drive capability for 3 pins (10 mA)

•

Two 16-bit timer/counters (C501 compatible)

•

SSC synchronous serial interface (SPI compatible) (only C541U)

– Master and slave capable

– Programmable clock polarity / clock-edge to data phase relation

– LSB/MSB first selectable

– 1.5 MBaud transfer rate at 12 MHz operating frequency

•

7 interrupt sources (2 external, 5 internal with 2 USB interrupts) selectable at 2 priority levels

•

Enhanced fail safe mechanisms

– Programmable watchdog timer (only C541U)

– Oscillator watchdog

•

Power saving modes

– idle mode

TM

)

pin or USB

– software power down mode with wake-up capability through INT0

•

On-chip emulation support logic (Enhanced Hooks Technology

•

P-LCC-44 and P-SDIP-52 packages

•

Power supply voltage range : 4.0V to 5.5V

•

Temperature Range : SAB-C540U

SAB-C541U

T

= 0 to 70 ° C

A

T

= 0 to 70 ° C

A

C540U

C541U

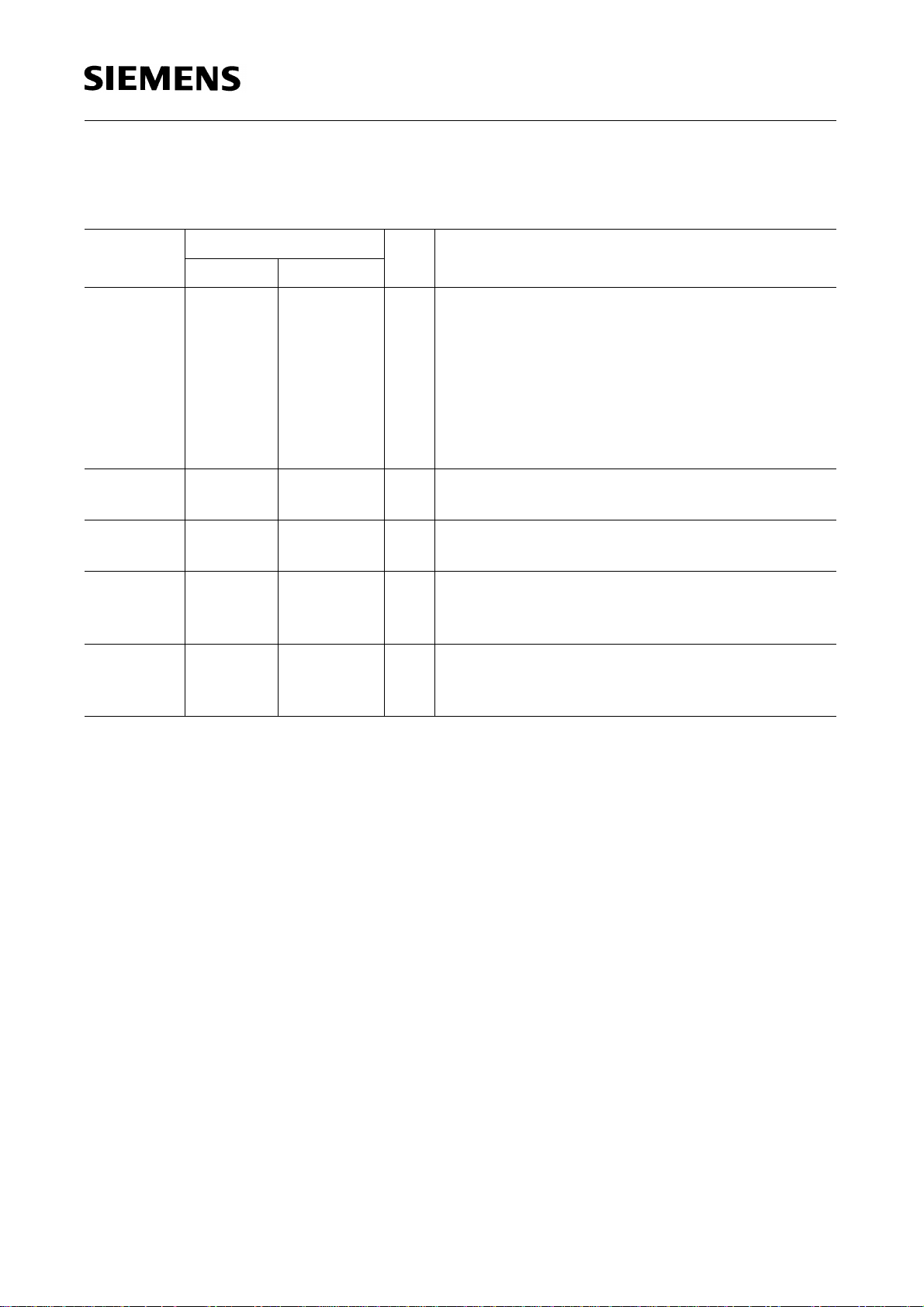

Table 1

Ordering Information

Type Ordering Code Package Description

(8-Bit CMOS microcontroller)

SAB-C540U-EN Q67126-C2042 P-LCC-44-2 8-Bit CMOS microcontroller (12 MHz)

SAB-C540U-EP Q67120-C2043 P-SDIP-52-1 8-Bit CMOS microcontroller (12 MHz)

SAB-C541U-1EN Q67126-C2001 P-LCC-44-2 8-Bit CMOS microcontroller (12 MHz)

SAB-C541U-1EP Q67120-C2021 P-SDIP-52-1 8-Bit CMOS microcontroller (12 MHz)

Semiconductor Group 4 1997-10-01

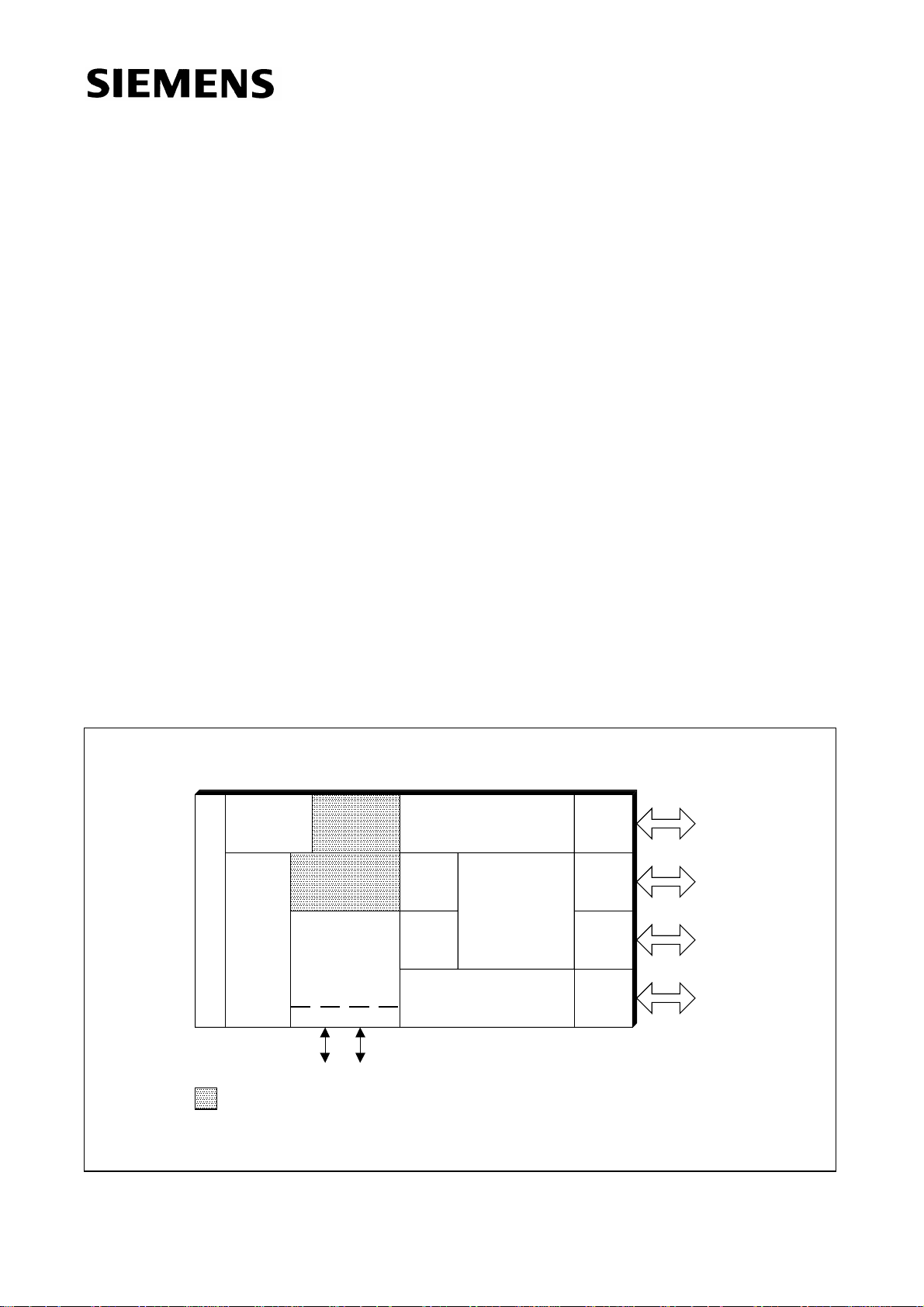

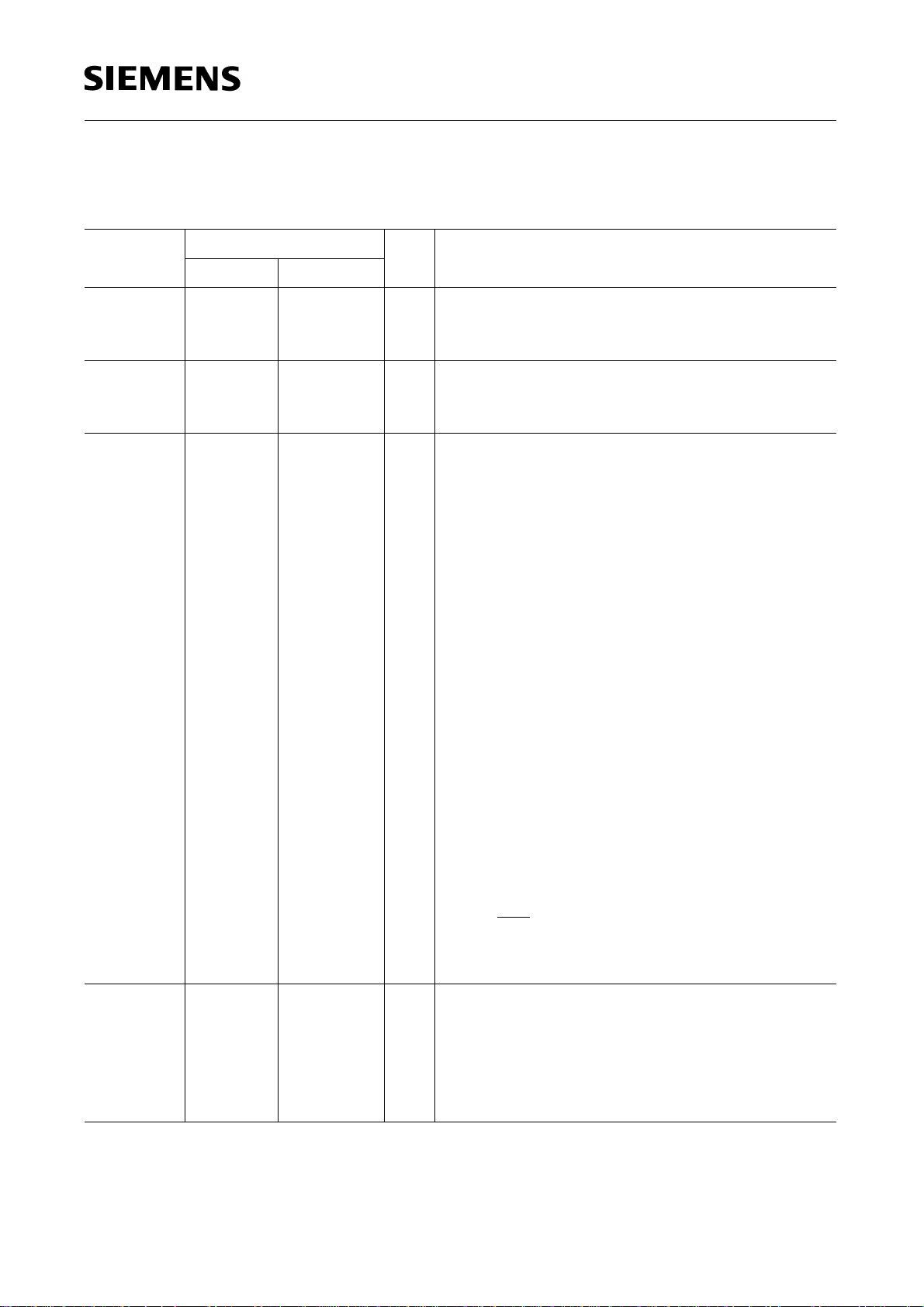

Page 5

C540U

C541U

Figure 2

Logic Symbol

XTAL2

XTAL1

ALE

PSEN

EA

RESET

D+

D-

V

CC

V

C540U

C541U

SS

Port

0

8-Bit Digital I / O

Port

1

P-LCC-44 : 6-Bit Digital I / O

P-SDIP-52 : 8-Bit Digital I / O

Port

2

8-Bit Digital I / O

Port

3

8-Bit Digital I / O

MCL03374

Additional Literature

For further information about the C540U/C541U the following literature is available :

Title Ordering Number

C540U/C541U 8-Bit CMOS Microcontroller User’s Manual B158-H????-X-X-7600

C500 Microcontroller Family

B158-H6987-X-X-7600

Architecture and Instruction Set User’s Manual

C500 Microcontroller Family - Pocket Guide B158-H6986-X-X-7600

Semiconductor Group 5 1997-10-01

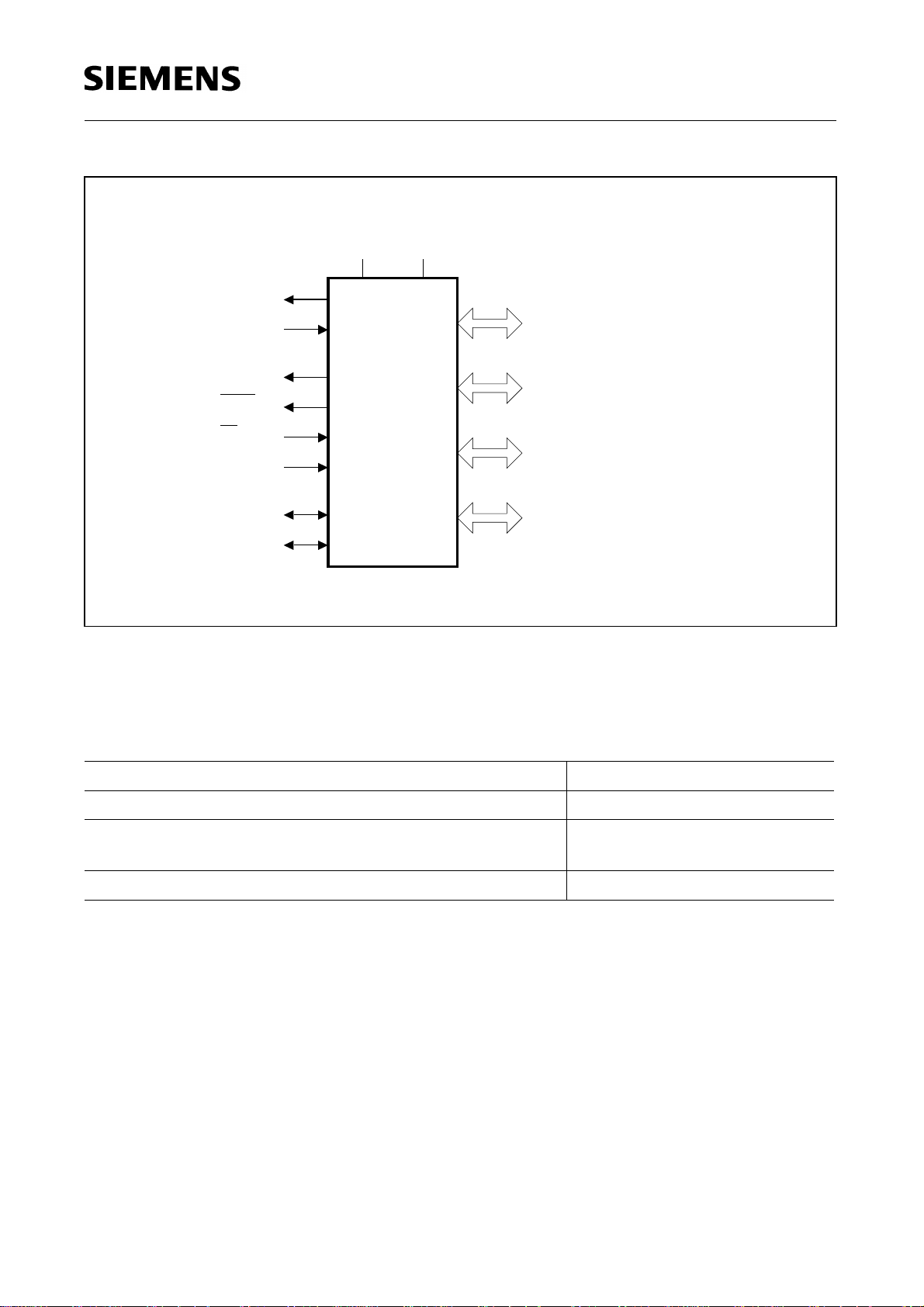

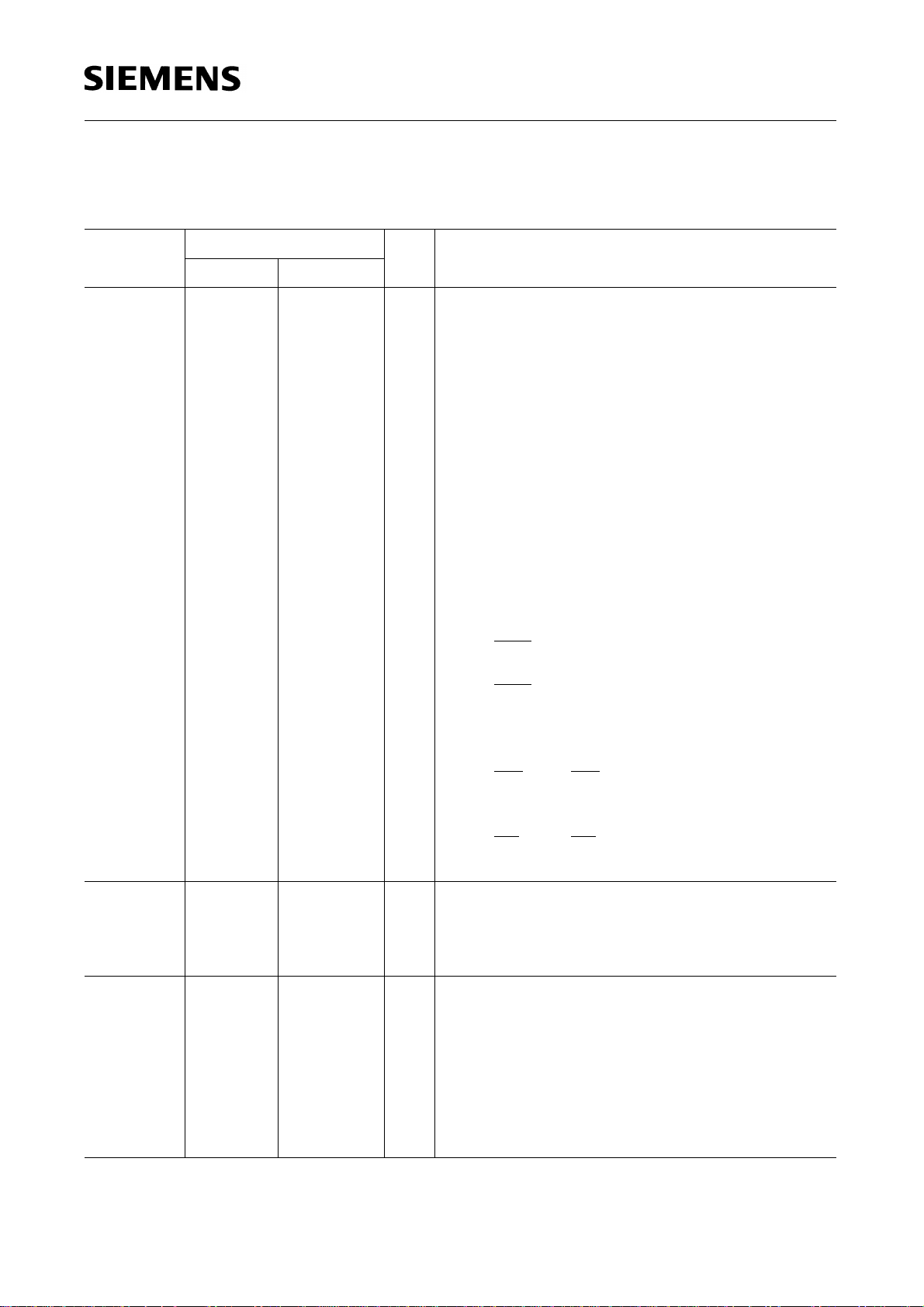

Page 6

C540U

C541U

P1.1 / LED1

P1.0 / LED0

D-

6543214443424140

P1.2 / SCLK 7

8

V

CC

9

V

SS

RESET

P3.0 / LED2

P1.3 / SRI

P3.1 / DADD

P3.2 / INT0

P3.3 / INT1

P3.4 / T0

P3.5 / T1

This pin functionality ist not available for the C540U.

10

11

12

13

14

15

16

17

18 19 20 21 22 23 24 25 26 27 28

XTAL2

P3.7 / RD

P3.6 / WR

SSUVCCU

D+

V

C540U

C541U

SS

V

XTAL1

P1.5 / SLS

P0.0 / AD0

CC

V

P2.0 / A8

P2.1 / A9

P0.1 / AD1

P0.2 / AD2

P0.3 / AD3

39

38

37

36

35

34

33

32

31

30

29

P2.2 / A10

P2.3 / A11

P2.4 / A12

P0.4 / AD4

P0.5 / AD5

P0.6 / AD6

P0.7 / AD7

EA

P1.4 / STO

ALE

PSEN

P2.7 / A15

P2.6 / A14

P2.5 / A13

MCP03343

Figure 3

Pin Configuration P-LCC-44 Package (top view)

Semiconductor Group 6 1997-10-01

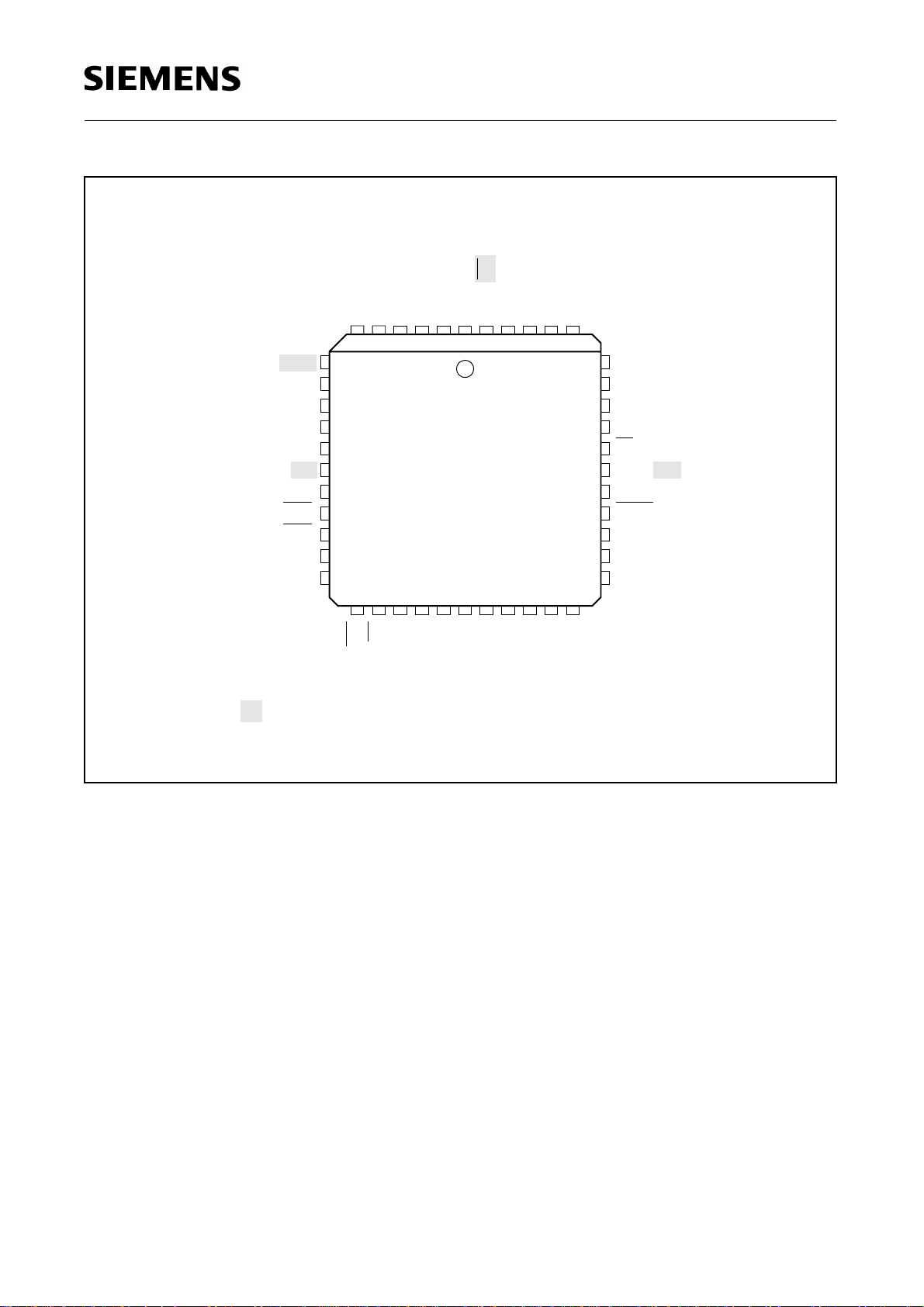

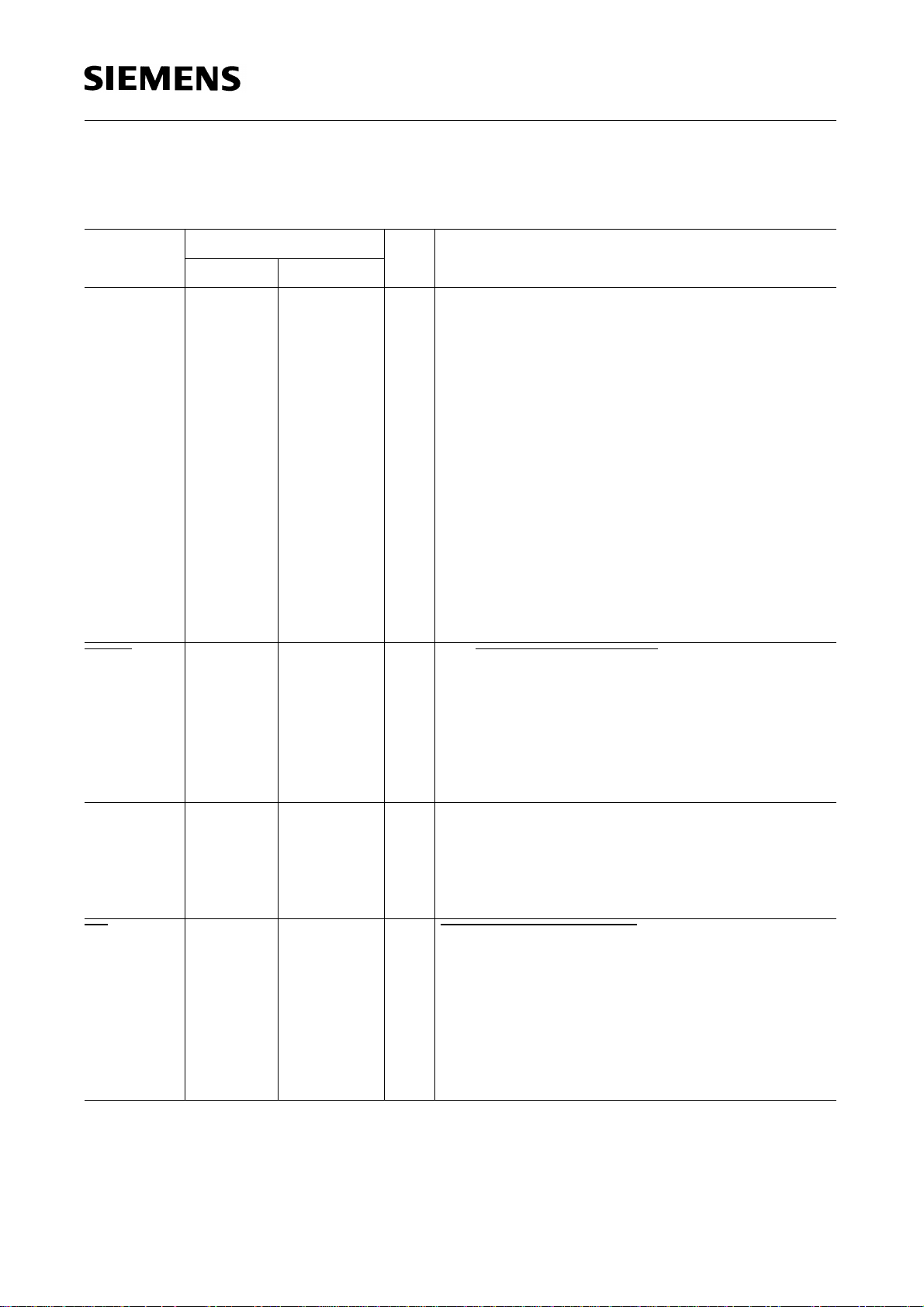

Page 7

C540U

C541U

V

CCU

V

SSU

D+

DN.C.

N.C.

P1.0 / LED0

P1.1 / LED1

P1.2 / SCLK

V

CC

V

SS

RESET

P3.0 / LED2

P1.3 / SRI

P1.6

P3.1 / DADD

P3.2 / INT0

P3.3 / INT1

P3.4 / T0

P3.5 / T1

P3.6 / WR

P3.7 / RD

XTAL2

XTAL1

V

SS

V

CC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

C540U

C541U

N.C.

52

P1.5 / SLS

51

P0.0 / AD0

50

P0.1 / AD1

49

P0.2 / AD2

48

P0.3 / AD3

47

P0.4 / AD4

46

P0.5 / AD5

45

P0.6 / AD6

44

P0.7 / AD7

43

EA

42

P1.4 / STO

41

P1.7

40

ALE

39

PSEN

38

N.C.

37

N.C.

36

P2.7 / A15

35

P2.6 / A14

34

P2.5 / A13

33

P2.4 / A12

32

P2.3 / A11

31

P2.2 / A10

30

P2.1 / A9

29

P2.0 / A8

28

N.C.

27

MCP03344

This pin functionality ist not available for the C540U.

Figure 4

Pin Configuration P-SDIP-52 Package (top view)

Semiconductor Group 7 1997-10-01

Page 8

Table 2

Pin Definitions and Functions

Symbol Pin Numbers I/O*) Function

P-LCC-44 P-SDIP-52

D+ 3 3 I/O USB D+ Data Line

The pin D+ can be directly connected to USB cable

(transceiver is integrated on-chip).

D- 4 4 I/O USB D- Data Line

The pin D- can be directly connected to USB cable

(transceiver is integrated on-chip).

C540U

C541U

P1.0 - P1.4 5 - 7,

12, 34, 44

5

6

7

12

34

44

–

–

7 - 9, 14, 41,

51, 15, 40

7

8

9

13

41

51

15

40

I/O Port 1

is an 6-bit (P-LCC-44) or 8-bit (P-SDIP-52) quasibidirectional I/O port with internal pullup resistors.

Port 1 pins that have 1's written to them are pulled

high by the internal pullup resistors, and in that

state can be used as inputs. As inputs, port 1 pins

being externally pulled low will source current ( I

in the DC characteristics) because of the internal

pullup resistors.

Port 1 also contains two outputs with LED drive

capability as well as the four pins of the SSC

(C541U only). The output latch corresponding to a

secondary function must be programmed to a one

(1) for that function to operate (except when used

for the compare functions). The secondary

functions are assigned to the port 1 pins as follows :

P1.0 / LED0 LED0 output

P1.1 / LED1 LED1 output

P1.2 / SCLK SSC Master Clock Output /

P1.3 / SRI SSC Receive Input (C541U only)

P1.4 / STO SSC Transmit Output (C541U only)

P1.5 / SLS

P1.6 (P-SDIP-52 only)

P1.7 (P-SDIP-52 only)

IL

SSC Slave Clock Input (C541U only)

SSC Slave Select Inp. (C541U only)

,

RESET 10 12 I

RESET

A high level on this pin for the duration of two

machine cycles while the oscillator is running

resets the C540U/C541U. A small internal pulldown

resistor permits power-on reset using only a

capacitor connected to V

*) I = Input

O = Output

CC

.

Semiconductor Group 8 1997-10-01

Page 9

Table 2

Pin Definitions and Functions (cont’d)

Symbol Pin Numbers I/O*) Function

P-LCC-44 P-SDIP-52

P3.0 - P3.7 11, 13 - 19 13, 16 - 22 I/O Port 3

is an 8-bit quasi-bidirectional I/O port with internal

pullup resistors. Port 3 pins that have 1's written to

them are pulled high by the internal pullup resistors,

and in that state can be used as inputs. As inputs,

port 3 pins being externally pulled low will source

current ( I

the internal pullup resistors. Port 3 also contains

the interrupt, timer, serial port and external memory

strobe pins that are used by various options. The

output latch corresponding to a secondary function

must be programmed to a one (1) for that function

to operate. The secondary functions are assigned

to the pins of port 3, as follows:

P3.0 / LED2 LED2 output

P3.1 / DADD Device attached input

P3.2 / INT0

P3.3 / INT1 External interrupt 1 input /

P3.4 / T0 Timer 0 counter input

P3.5 / T1 Timer 1 counter input

P3.6 / WR WR control output; latches the

P3.7 / RD

C540U

C541U

, in the DC characteristics) because of

IL

External interrupt 0 input /

timer 0 gate control input

timer 1 gate control input

data byte from port 0 into the

external data memory

RD control output; enables the

external data memory

XTAL2 20 23 –

XTAL1 21 24 –

*) I = Input

O = Output

Semiconductor Group 9 1997-10-01

XTAL2

is the output of the inverting oscillator amplifier.

This pin is used for the oscillator operation with

crystal or ceramic resonator.

XTAL1

is the input to the inverting oscillator amplifier and

input to the internal clock generator circuits.

To drive the device from an external clock source,

XTAL1 should be driven, while XTAL2 is left

unconnected.

low times as well as rise/fall times specified in the

AC characteristics must be observed.

Minimum and maximum high and

Page 10

Table 2

Pin Definitions and Functions (cont’d)

Symbol Pin Numbers I/O*) Function

P-LCC-44 P-SDIP-52

P2.0 - P2.7 24 - 31 28 - 35 I/O Port 2

is an 8-bit quasi-bidirectional I/O port with internal

pullup resistors. Port 2 pins that have 1's written to

them are pulled high by the internal pullup resistors,

and in that state can be used as inputs. As inputs,

port 2 pins being externally pulled low will source

current ( I

the internal pullup resistors.

Port 2 emits the high-order address byte during

fetches from external program memory and during

accesses to external data memory that use 16-bit

addresses (MOVX @DPTR). In this application it

uses strong internal pullup resistors when issuing

1's. During accesses to external data memory that

use 8-bit addresses (MOVX @Ri), port 2 issues the

contents of the P2 special function register.

C540U

C541U

, in the DC characteristics) because of

IL

PSEN

32 38 O The Program Store Enable

output is a control signal that enables the external

program memory to the bus during external fetch

operations. It is activated every six oscillator

periods except during external data memory

accesses. The signal remains high during internal

program execution.

ALE 33 39 O The Address Latch enable

output is used for latching the address into external

memory during normal operation. It is activated

every six oscillator periods except during an

external data memory access.

EA

35 42 I

External Access Enable

When held high, the C540U/C541U executes

instructions from the internal ROM as long as the

PC is less than 1000H for the C540U or less than

2000H for the C541U. When held low, the C540U/

C541U fetches all instructions from external

program memory. For the C540U-L/C541U-L this

pin must be tied low.

*) I = Input

O = Output

Semiconductor Group 10 1997-10-01

Page 11

Table 2

Pin Definitions and Functions (cont’d)

Symbol Pin Numbers I/O*) Function

P-LCC-44 P-SDIP-52

P0.0 - P0.7 44 - 36 50 - 43 I/O Port 0

is an 8-bit open-drain bidirectional I/O port. Port 0

pins that have 1's written to them float, and in that

state can be used as high-impedance inputs. Port 0

is also the multiplexed low-order address and data

bus during accesses to external program and data

memory. In this application it uses strong internal

pullup resistors when issuing 1's.

C540U

C541U

V

CCU

V

SSU

V

CC

V

SS

*) I = Input

O = Output

11 –

Supply voltage

for the on-chip USB transceiver circuitry.

22 –

Ground (0V)

for the on-chip USB transceiver circuitry.

8, 23 10, 26 –

Supply voltage

for ports and internal logic circuitry during normal,

idle, and power down mode.

9, 22 11, 25 –

Ground (0V)

for ports and internal logic circuitry during normal,

idle, and power down mode.

Semiconductor Group 11 1997-10-01

Page 12

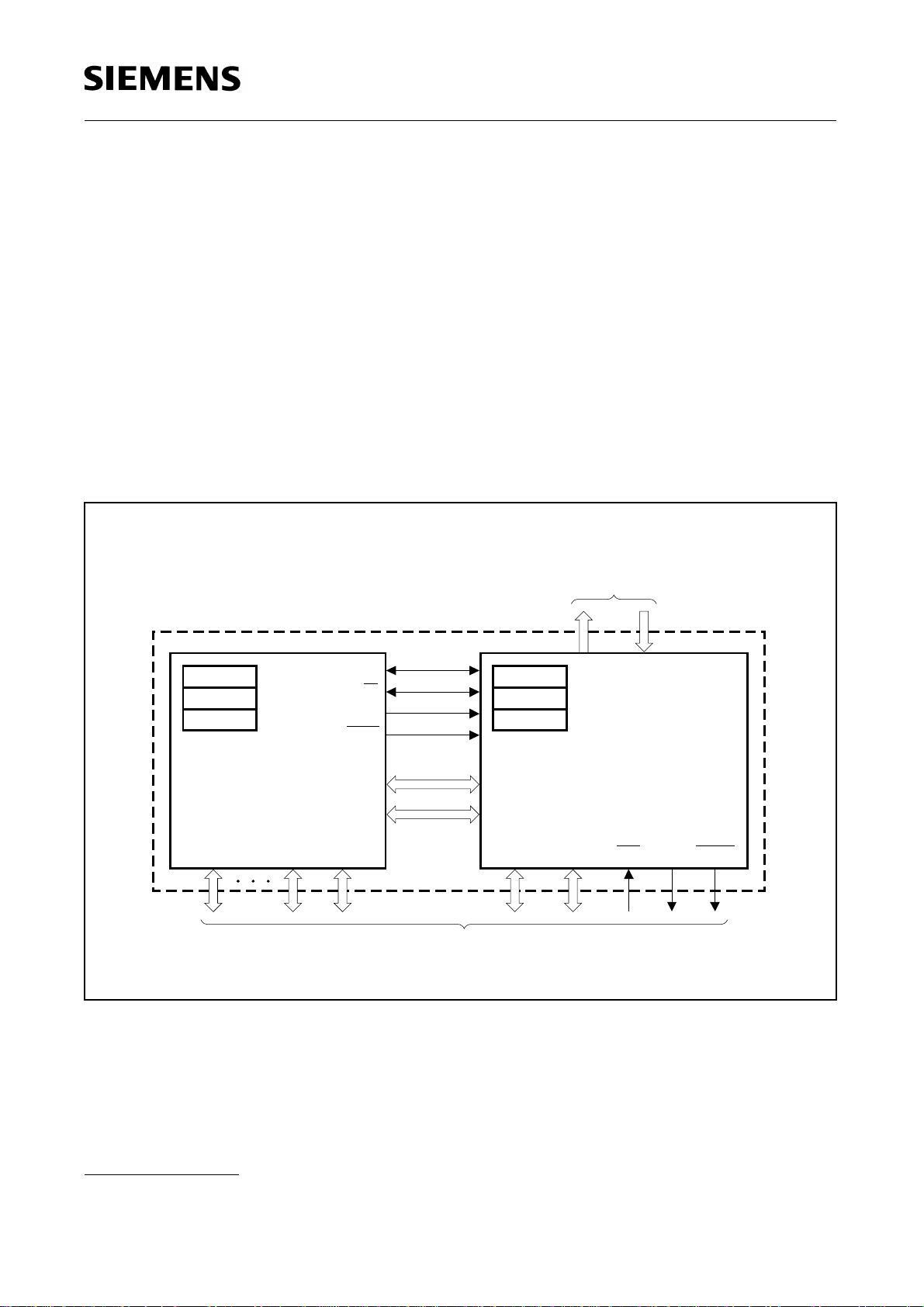

C540U

C541U

XTAL2

XTAL1

ALE

PSEN

EA

RESET

D+

-

D

Oscillator Watchdog

OSC & Timing

CPU

Progr. Watchdog

Timer (C541U only)

Timer 0

Timer 1

SSC (SPI) Interface

(C541U only)

PLL

USB

Module

Transceiver

Interrupt Unit

RAM

256 x 8

OTP Memory

4k x 8 (C540U)

8k x 8 (C541U)

Emulation

Support

Logic

Port 0

Port 1

Port 2

Port 3

C540U

C541U

Port 0

8-Bit Digit. I/O

Port 1

6- / 8-Bit Digit. I/O

Port 2

8-Bit Digit. I/O

Port 3

8-Bit Digit. I/O

1)

1)

P-LCC-44 : 6-Bit Port; P-SDIP-52 : 8-Bit Port MCB03345

Figure 5

Block Diagram of the C540U/C541U

Semiconductor Group 12 1997-10-01

Page 13

C540U

C541U

CPU

The C540U/C541U is efficient both as a controller and as an arithmetic processor. It has extensive

facilities for binary and BCD arithmetic and excels in its bit-handling capabilities. Efficient use of

program memory results from an instruction set consisting of 44 % one-byte, 41 % two-byte, and

15% three- byte instructions. With a 12 MHz crystal, 58% of the instructions are executed in 500ns.

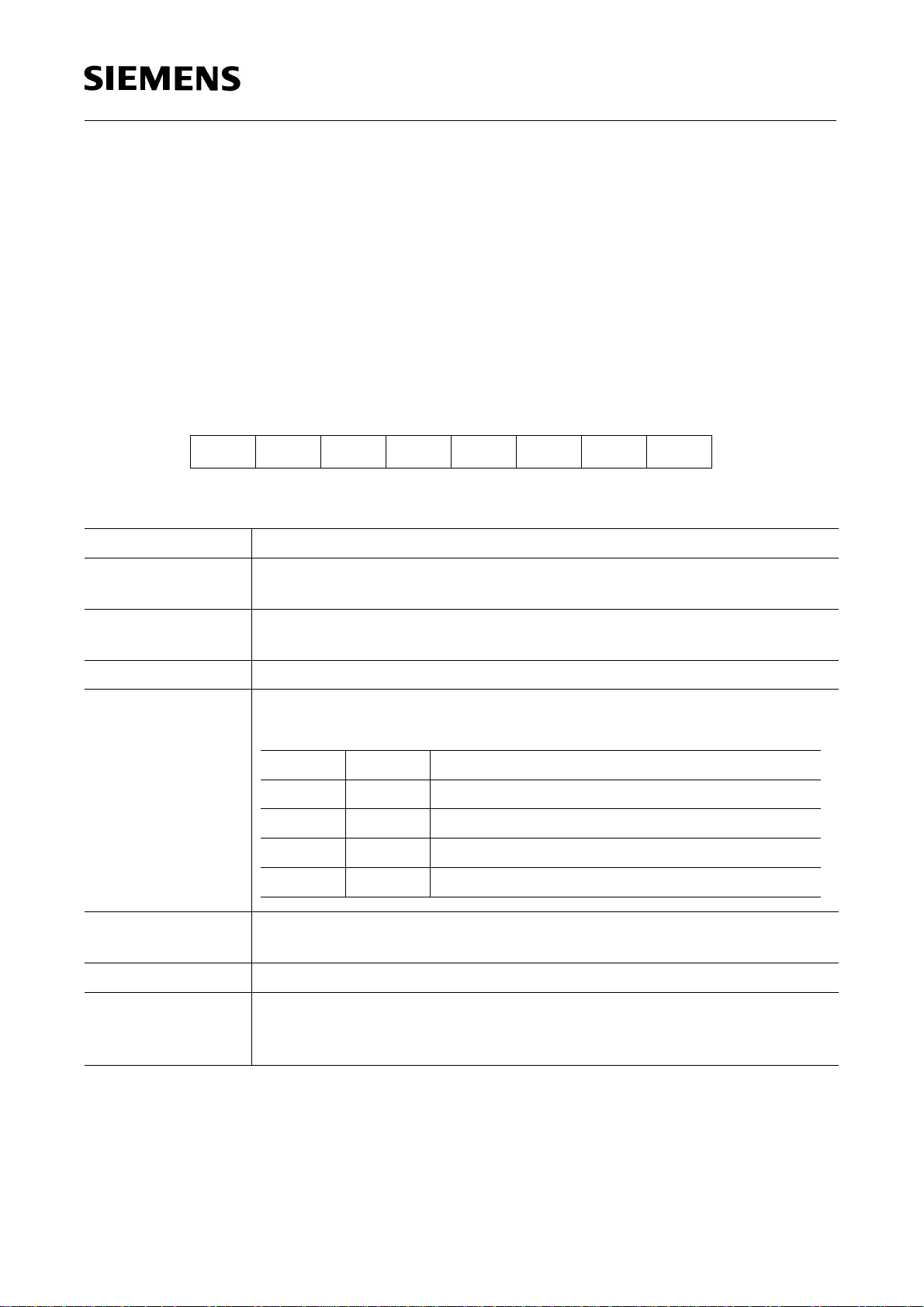

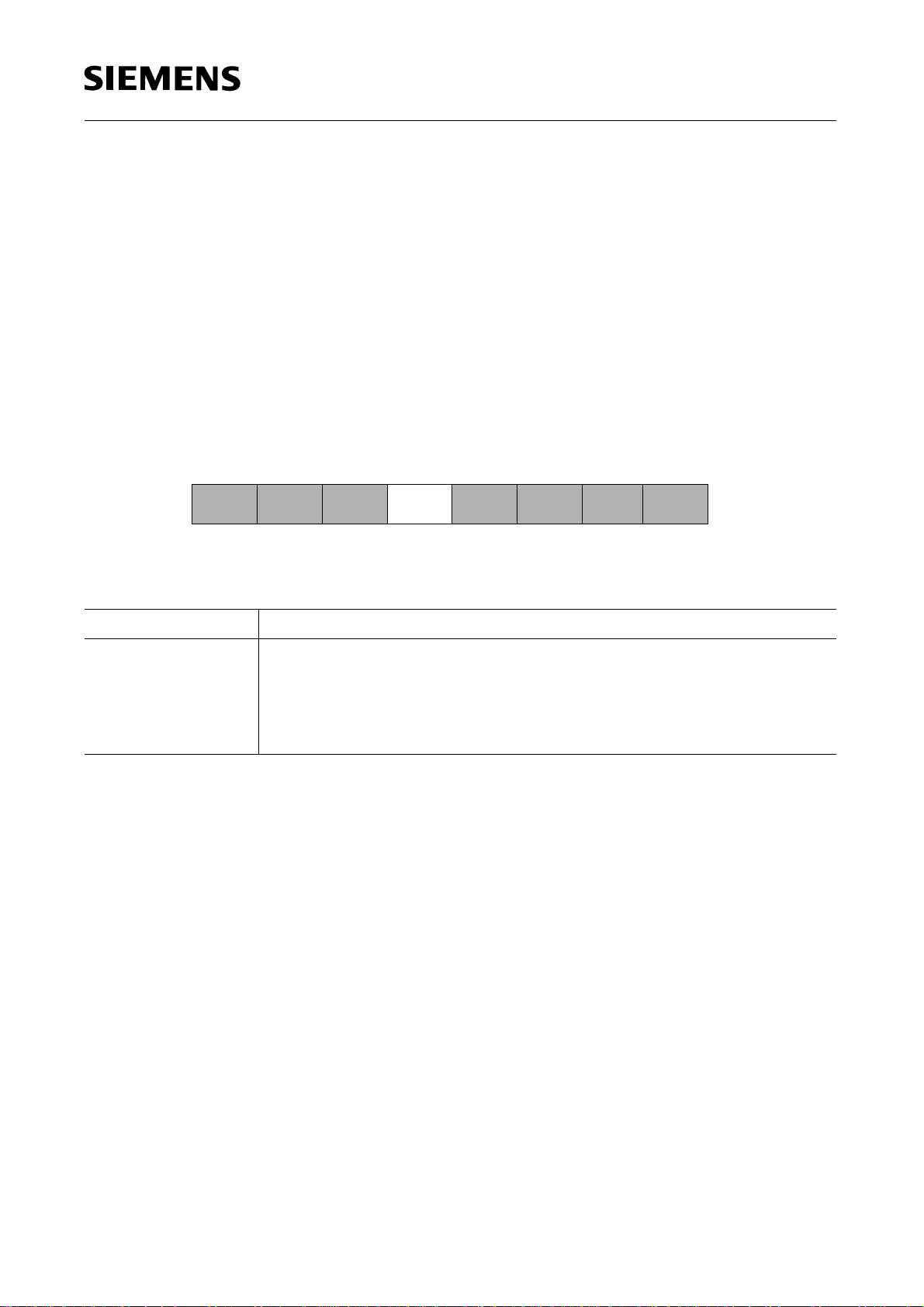

Special Function Register PSW (Address D0H) Reset Value : 00H

Bit No. MSB LSB

H

D7

CY AC

H

D6

H

D5

F0

H

D4

RS1 RS0 OV F1 PD0

Bit Function

CY Carry Flag

Used by arithmetic instruction.

AC Auxiliary Carry Flag

Used by instructions which execute BCD operations.

F0 General Purpose Flag

RS1

RS0

Register Bank Select Control Bits

These bits are used to select one of the four register banks.

RS1 RS0 Function

0 0 Bank 0 selected, data address 00H-07

0 1 Bank 1 selected, data address 08H-0F

1 0 Bank 2 selected, data address 10H-17

1 1 Bank 3 selected, data address 18H-1F

H

D3

H

D2

H

D1

H

D0

H

PSW

H

H

H

H

OV Overflow Flag

Used by arithmetic instruction.

F1 General Purpose Flag

P Parity Flag

Set/cleared by hardware after each instruction to indicate an odd/even

number of "one" bits in the accumulator, i.e. even parity.

Semiconductor Group 13 1997-10-01

Page 14

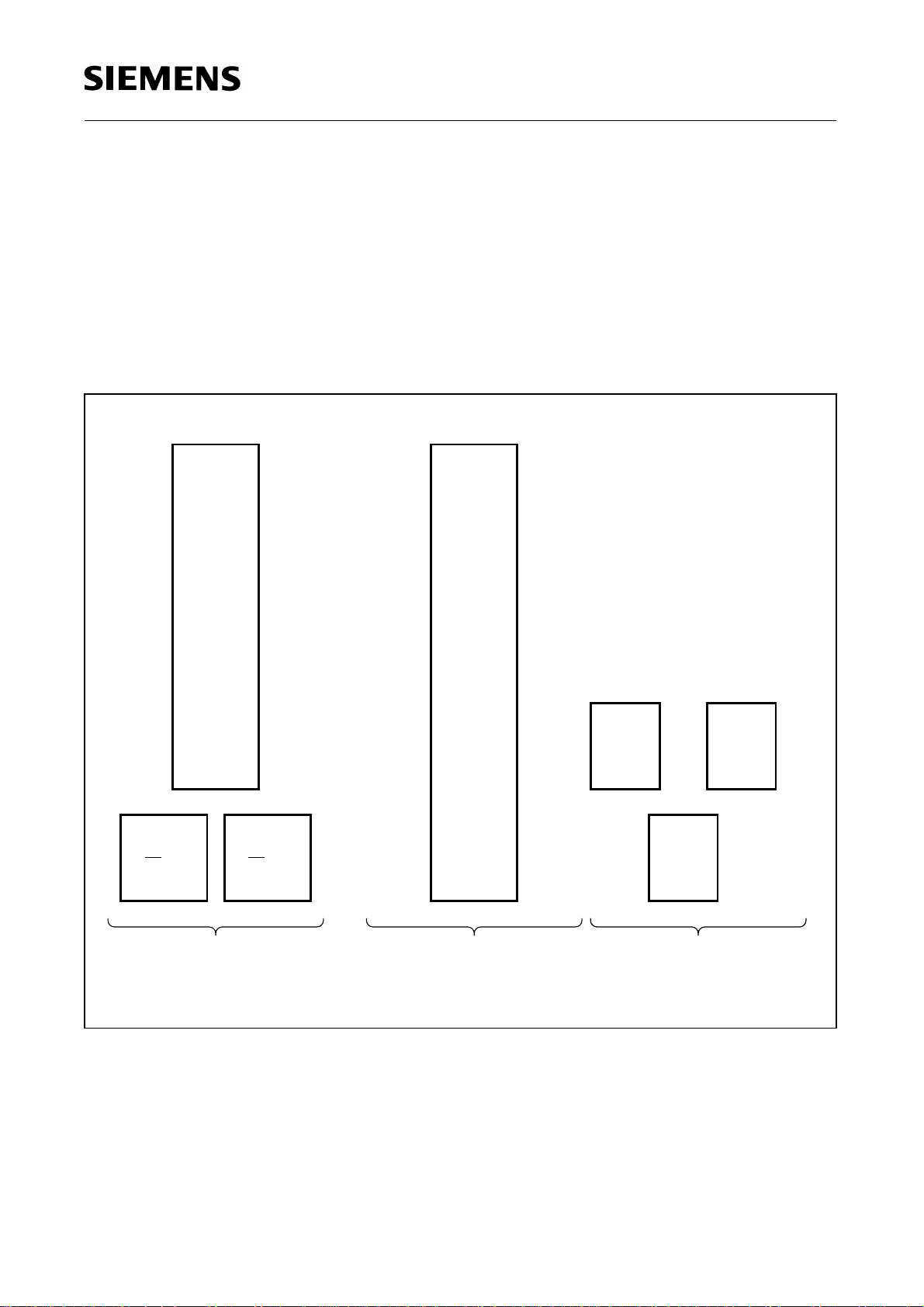

Memory Organization

The C540U/C541U CPU manipulates operands in the following four address spaces:

– 8 or 4 KByte on-chip OTP program memory

– Totally up to 64 Kbyte internal/external program memory

– up to 64 Kbyte of external data memory

– 256 bytes of internal data memory

– a 128 byte special function register area

Figure 6 illustrates the memory address spaces of the C540U/C541U.

C540U

C541U

Internal

(EA = 1)

External

FFFF

2000 1)

External

(EA = 0)

H

H

1FFF 1)

FFFF

H

H

H

Direct

Addr.

Special

Function

Register

7F

H

FF

80

H

H

External

Indirect

Addr.

FF

Internal

RAM

80

H

Internal

RAM

0000

H

0000

H

00

H

"Code Space" "External Data Space" "Internal Data Space"

1) For the C504U the int. / ext. program memory boundary is at 0FFF / 1000 .

H

H

MCD03375

Figure 6

C540U/C541U Memory Map Memory Map

Semiconductor Group 14 1997-10-01

Page 15

C540U

C541U

Reset and System Clock

The reset input is an active high input at pin RESET. Since the reset is synchronized internally, the

RESET pin must be held high for at least two machine cycles (12 oscillator periods) while the

oscillator is running. A pulldown resistor is internally connected to VSS to allow a power-up reset with

an external capacitor only. An automatic reset can be obtained when VCC is applied by connecting

the RESET pin to VCC via a capacitor. Figure 7 shows the possible reset circuitries.

V

CC

a)

+

C540U

C541U C541U

RESET RESET

V

CC

V

CC

c)

+

C540U

C541U

RESET

&

b)

C540U

MCD03376

Figure 7

Reset Circuitries

Semiconductor Group 15 1997-10-01

Page 16

C540U

C541U

The oscillator and clock generation circuitry of the C540U/C541U is shown in figure 5-8. The crystal

oscillator generates the system clock for the microcontroller. The USB module can be provided with

the following clocks :

– Full speed operation : 48 MHz with a data rate of 12 Mbit/s

– Low speed operation : 6 MHz with a data rate of 1.5 Mbit/s

The low speed clock is generated by a dividing the system clock by 2. The full speed clock is

generated by a PLL, which multiplies the system clock by a fix factor of 4. This PLL can be enabled

or disabled by bit PCLK of SFR DCR. Depending on full or low speed operation of the USB bit

SPEED of SFR has to be set or cleared for the selection of the USB clock. Bit UCLK is a general

enable bit for the USB clock.

XTAL1

12 MHz

XTAL2

Pin

Oscillator

Pin

6 MHz

C540U / C541U

Crystal

Divider PLL

by 2

12 MHz

48 MHz

Figure 8

Block Diagram of the Clock Generation Circuitry

x 4

1

0

SPEED

DCR.7

System Clock

of the

Microcontroler

Enable

PCLK

DCR.0

to USB

Module

UCLK

DCR.1

MCB03377

Semiconductor Group 16 1997-10-01

Page 17

C540U

C541U

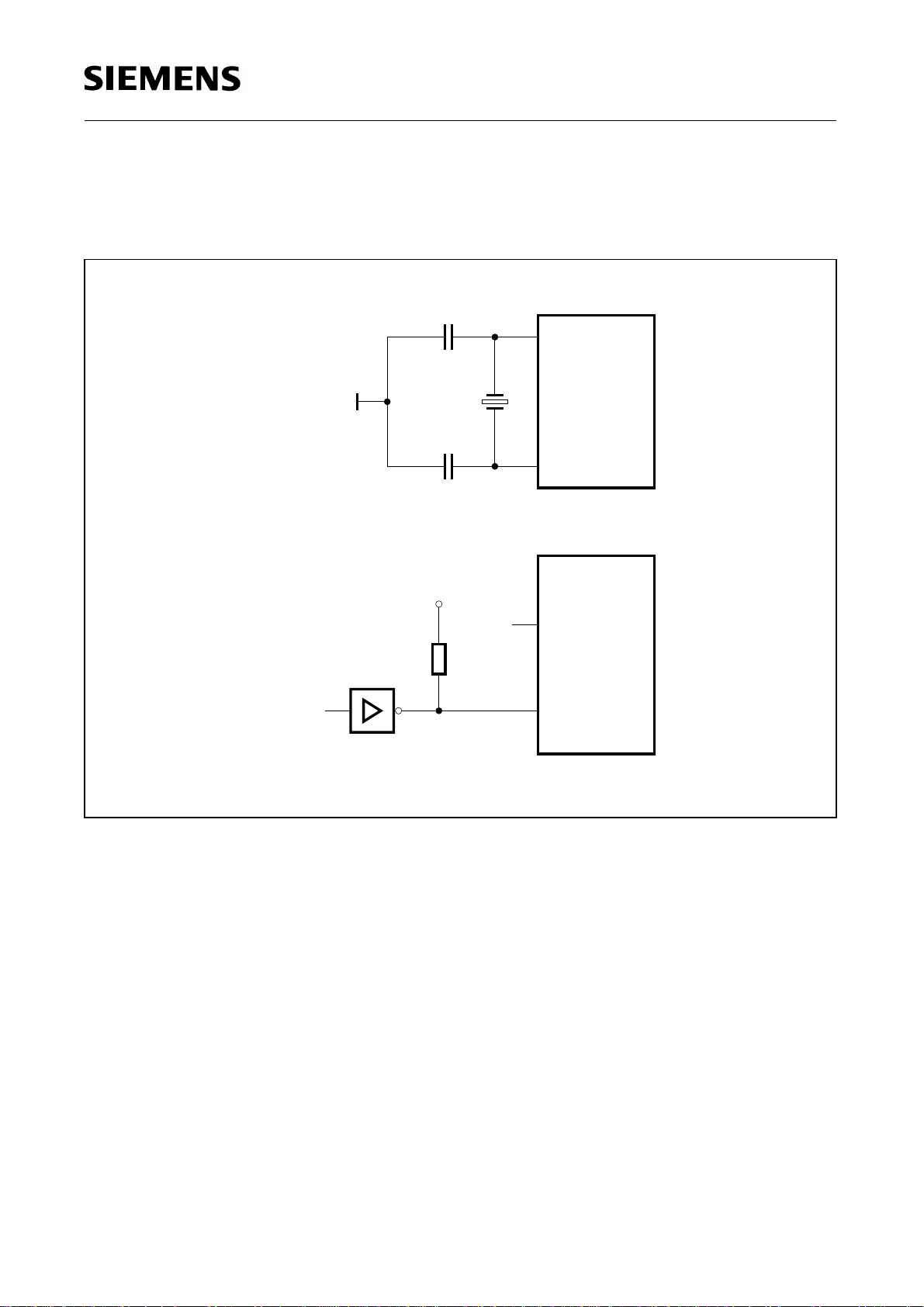

The clock generator provides the internal clock signals to the chip. These signals define the internal

phases, states and machine cycles. Figure 9 shows the recommended oscillator circuits for crystal

and external clock operation.

C

XTAL2

C = 20 pF 10 pF for crystal operation

External

Clock

Signal

Figure 9

Recommended Oscillator Circuitries

12 MHz

C

V

CC

N.C.

C540U

C541U

XTAL1

C540U

C541U

XTAL2

XTAL1

MCD03378

Semiconductor Group 17 1997-10-01

Page 18

C540U

C541U

Enhanced Hooks Emulation Concept

The Enhanced Hooks Emulation Concept of the C500 microcontroller family is a new, innovative

way to control the execution of C500 MCUs and to gain extensive information on the internal

operation of the controllers. Emulation of on-chip ROM based programs is possible, too.

Each production chip has built-in logic for the supprt of the Enhanced Hooks Emulation Concept.

Therefore, no costly bond-out chips are necessary for emulation. This also ensure that emulation

and production chips are identical.

1)

The Enhanced Hooks Technology

together with an EH-IC to function similar to a bond-out chip. This simplifies the design and reduces

costs of an ICE-system. ICE-systems using an EH-IC and a compatible C500 are able to emulate

all operating modes of the different versions of the C500 microcontrollers. This includes emulation

of ROM, ROM with code rollover and ROMless modes of operation. It is also able to operate in

single step mode and to read the SFRs after a break.

TM

, which requires embedded logic in the C500 allows the C500

SYSCON

PCON

TCON

Optional

I/O Ports

ICE-System Interface

to Emulation Hardware

RESET

EA

ALE

PSEN

C500

MCU Interface Circuit

Port 3 Port 1

Port 0

Port 2

Target System Interface

RSYSCON

RPCON

RTCON

Enhanced Hooks

RPort 0RPort 2

EH-IC

TEA TALE TPSEN

MCS02647

Figure 10

Basic C500 MCU Enhanced Hooks Concept Configuration

Port 0, port 2 and some of the control lines of the C500 based MCU are used by Enhanced Hooks

Emulation Concept to control the operation of the device during emulation and to transfer

informations about the programm execution and data transfer between the external emulation

hardware (ICE-system) and the C500 MCU.

1 “Enhanced Hooks Technology“ is a trademark and patent of Metalink Corporation licensed to Siemens.

Semiconductor Group 18 1997-10-01

Page 19

C540U

C541U

Special Function Registers

The registers, except the program counter and the four general purpose register banks, reside in

the special function register area. The special function register area consists of two portions: the

standard special function register area and the mapped special function register area. One special

function register of the C540U/C541U (PCON1) is located in the mapped special function register

area. All other SFRs are located in the standard special function register area.

For accessing PCON1 in the mapped special function register area, bit RMAP in special function

register SYSCON must be set.

Special Function Register SYSCON (Address B1H) Reset Value : XX10XXXX

Bit No. MSB LSB

76543210

B1

H

Bit Function

RMAP Special function register map bit

As long as bit RMAP is set, a mapped special function register can be accessed. This bit is not

cleared by hardware automatically. Thus, when non-mapped/mapped registers are to be accessed,

the bit RMAP must be cleared/set by software, respectively each.

––

The functions of the shaded bits are not described in this section.

RMAP = 0 : The access to the non-mapped (standard) special function

RMAP = 1 : The access to the mapped special function register area

EALE RMAP –

register area is enabled.

(PCON1) is enabled.

––

–

SYSCON

B

The registers, except the program counter and the four general purpose register banks, reside in

the special function register area. All SFRs with addresses where address bits 0-2 are 0 (e.g. 80H,

88H, 90H, 98H, ..., F8H, FFH) are bitaddressable.

The 75 special function registers (SFRs) in the SFR area include pointers and registers that provide

an interface between the CPU and the other on-chip peripherals. The SFRs of the C540U/C541U

are listed in table 3 to table 4. In table 3 they are organized in groups which refer to the functional

blocks of the C540U/C541U. Table 4 and table 4 illustrate the contents of the SFRs in numeric

order of their addresses.

Semiconductor Group 19 1997-10-01

Page 20

C540U

C541U

Table 3

Special Function Registers - Functional Blocks

Block Symbol Name Address Contents after

Reset

CPU ACC

B

DPH

DPL

PSW

SP

VR0

VR1

VR2

SYSCON

Interrupt

System

IEN0

IEN1

IP0

IP1

ITCON

Ports P0

P1

P2

P3

Timer 0 /

Timer 1

TCON

TH0

TH1

TL0

TL1

TMOD

SSC

Interface

(C541U

only)

SSCCON

STB

SRB

SCF

SCIEN

SSCMOD

Watchdog

(C541U

WDCON

WDTREL

only)

Accumulator

B Register

Data Pointer, High Byte

Data Pointer, Low Byte

Program Status Word Register

Stack Pointer

Version Register 0

Version Register 1

Version Register 2

System Control Register

Interrupt Enable Register 0

Interrupt Enable Register 1

Interrupt Priority Register 0

Interrupt Priority Register 1

External Interrupt Trigger Condition Register

Port 0

Port 1

Port 2

Port 3

Timer 0/1 Control Register

Timer 0, High Byte

Timer 1, High Byte

Timer 0, Low Byte

Timer 1, Low Byte

Timer Mode Register

SSC Control Register

SSC Transmit Buffer

SSC Receive Register

SSC Flag Register

SSC Interrupt Enable Register

SSC Mode Test Register

Watchdog Timer Control Register

Watchdog Timer Reload Register

E0

F0

83

82

D0

81

FC

FD

FE

B1

A8

A9

B8

B9

9A

80

90

A0

B0

88

8C

8D

8A

8B

89

93

94

95

AB

AC

96

C0

86

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

1)

1)

1)

1)

1)

)

1)

1)

1)

1)

1)

1)

1

1)

)

00

H

00

H

00

H

00

H

00

H

07

H

C5

H

C1

H

3)

YY

H

XX10XXXX

0XXX0000

XXXXX000

XXXX0000

XXXXX000

XXXX1010

FF

H

FF

H

FF

H

FF

H

00

H

00

H

00

H

00

H

00

H

00

H

07

H

2)

H

H

2)

XX

XX

XXXXXX00

XXXXXX00

00

H

XXXX0000

00

H

2)

B

2)

B

2)

B

2)

B

2)

B

2)

B

2)

B

2)

B

2)

B

1) Bit-addressable special function registers

2) “X“ means that the value is undefined and the location is reserved

3) The content of this SFR varies with the actual of the step C540U/C541U (eg. 01

4) This SFR is located in the mapped SFR area. For accessing this SFR, bit RMAP in SFR SYSCON must be

set.

for the first step)

H

Semiconductor Group 20 1997-10-01

Page 21

C540U

C541U

Table 3

Special Function Registers - Functional Blocks (cont’d)

Block Symbol Name Address Contents after

Reset

Pow.

Sav.

Modes

PCON

PCON1

Power Control Register

Power Control Register 1

87

88

H

H

X00X0000

4)

0XX0XXXX

2)

B

2)

B

USB

Module

1) These register are multiple registers (n=0-4) with the same SFR address; selection of register “n“ is done by

SFR EPSEL.

2) The reset value of ADROFF is valid only if USBVAL has not been read or written since the last hardware reset.

3) The reset value of EPIR0 is 11

EPSEL

USBVAL

ADROFF

GEPIR

DCR

DPWDR

DIER

DIRR

FNRL

FNRH

EPBCn

EPBSn

EPIEn

EPIRn

EPBAn

EPLENn

1)

1)

1)

1)

1)

1)

USB Endpoint Select Register

USB Data Register

USB Address Offset Register

USB Global Endpoint Interrupt Request Reg.

USB Device Control Register

USB Device Power Down Register

USB Device Interrupt Control Register

USB Device Interrupt Request Register

USB Frame Number Register, Low Byte

USB Frame Number Register, High Byte

USB Endpoint n Buffer Control Register

USB Endpoint n Buffer Status Register

USB Endpoint n Interrupt Enable Register

USB Endpoint n Interrupt Request Register

USB Endpoint n Base Address Register

USB Endpoint n Buffer Length Register

.

H

D2

D3

D4

D6

C1

C2

C3

C4

C6

C7

C1

C2

C3

C4

C5

C6

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

80

H

00

H

2)

00

H

00

H

000X0000

00

H

00

H

00

H

XX

H

00000XXX

00

H

20

H

00

H

3)

10

H

00

H

0XXXXXXX

B

B

B

Semiconductor Group 21 1997-10-01

Page 22

Table 4

Contents of the SFRs, SFRs in numeric order of their addresses

C540U

C541U

Addr Register Reset

Value

2)

80

81

82

83

86

P0 FF

H

SP 07

H

DPL 00

H

DPH 00

H

4)

WDTREL 00

H

H

H

H

H

H

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

1)

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

WDT

.6 .5 .4 .3 .2 .1 .0

PSEL

87

88

88

2) 3)

89

8A

8B

8CHTH0 00

8DHTH1 00

90

93

94

95

96

9A

A0

A8

A9

AB

4)

1) X means that the value is undefined and the location is reserved

2) Bit-addressable special function registers

3) SFR is located in the mapped SFR area. For accessing this SFR, bit RMAP in SFR SYSCON must be set.

4) This SFR is only available in the C541U.

PCON X00X-

H

2)

TCON 00

H

PCON1 0XX0-

H

TMOD 00

H

TL0 00

H

TL1 00

H

2)

P1 FF

H

4)

SSCCON

H

4)

STB XX

H

4)

SRB XX

H

4)

SSCMOD

H

ITCON XXXX-

H

2)

P2 FF

H

2)

IEN0 0XXX-

H

IEN1 XXXX-

H

SCF XXXX-

H

0000

H

XXXX

H

H

H

H

H

H

07

H

H

H

00

H

1010

H

0000

X000

XX00

– PDS IDLS – GF1 GF0 PDE IDLE

B

TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

EWPD – – WS – – – –

B

GATE C/T

M1 M0 GATE C/T M1 M0

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 SLS STO SRI SCLK LED1 LED0

SCEN TEN MSTR CPOL CPHA BRS2 BRS1 BRS0

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

LOOPB

TRIO 00000LSBSM

––––I1ETF I1ETR I0ETF I0ETR

B

.7 .6 .5 .4 .3 .2 .1 .0

EA – – – ET1 EX1 ET0 EX0

B

–––––EUDI EUEI ESSC

B

––––––WCOL TC

B

Semiconductor Group 22 1997-10-01

Page 23

Table 4

Contents of the SFRs, SFRs in numeric order of their addresses (cont’d)

C540U

C541U

Addr Register Reset

Value

AC

4)

B0

B1

SCIEN XXXX-

H

2)

P3 FF

H

SYSCON XX10-

H

XX00

H

XXXX

2)

B8

IP0 XXXX-

H

0000

B9

IP1 XXXX-

H

0000

C0

2)

C1H to C7

D0

2)

D2HEPSEL 80

D3HUSBVAL 00

D4HADROFF 00

D6HGEPIR 00

E0

F0

FC

3) 5)

WDCON

H

PSW 00

H

2)

ACC 00

H

2)

B 00

H

VR0 C5

H

H

XXXX0000

USB Device and Endpoint Register definition see table 3-4

H

H

H

H

H

H

H

H

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

1)

––––––WCEN TCEN

B

RD WR T1 T0 INT1 INT0 DADD LED2

– – EALE RMAP ––––

B

– – – – PT1 PX1 PT0 PX0

B

–––––PUDI PUEI PSSC

B

– – – – OWDS WDTS WDT SWDT

B

CY AC F0 RS1 RS0 OV F1 P

EPS7 0000EPS2 EPS1 EPS0

.7 .6 .5 .4 .3 .2 .1 .0

7)

0 0 AO5 AO4 AO3 AO2 AO1 AO0

0 0 0 EPI4 EPI3 EPI2 EPI1 EPI0

.7 .6 .5 .4 .3 .2 .1 .0

.7 .6 .5 .4 .3 .2 .1 .0

11000101

4)

FD

3) 5)

FE

3) 5)

1) X means that the value is undefined and the location is reserved

2) Bit-addressable special function registers

3) SFR is located in the mapped SFR area. For accessing this SFR, bit RMAP in SFR SYSCON must be set.

4) This SFR respectively bit is only available in the C541U.

5) These are read-only registers

6) The content of this SFR varies with the actual of the step C517A (e.g. 01

7) The reset value of ADROFF is valid only if USBVAL has not been read or written since the last hardware reset.

VR1 C1

H

VR2

H

H

6)

11000001

.7 .6 .5 .4 .3 .2 .1 .0

for the first step)

H

Semiconductor Group 23 1997-10-01

Page 24

Table 5

Contents of the USB Device and Endpoint Registers (Addr. C1H to C7H)

C540U

C541U

Addr Register Reset

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Value

EPSEL = 1XXX.XXXXB Device Registers

C1HDCR 000X.

0000

C2HDPWDR 00

C3HDIER 00

C4HDIRR 00

H

H

H

SPEED DA SWR SUSP DINIT RSM UCLK PCLK

B

0 0 0 0 0 0 TPWD RPWD

SE0IE DAIE DDIE SBIE SEIE STIE SUIE SOFIE

SE0I DAI DDI SBI SEI STI SUI SOFI

C5Hreserved

C6HFNRL XX

H

C7HFNRH 0000.

0XXX

EPSEL = 0XXX.X000

C1HEPBC0 00

C2HEPBS0 20

C3HEPIE0 00

C4HEPIR0 11

C5HEPBA0 00

H

H

H

H

H

C6HEPLEN0 0XXX.

XXXX

FNR7 FNR6 FNR5 FNR4 FNR3 FNR2 FNR1 FNR0

0 0 0 0 0 FNR10 FNR9 FNR8

B

Endpoint 0 Registers

B

STALL0 0 0 GEPIE0 SOFDE0 INCE0 0 DBM0

UBF0 CBF0 DIR0 ESP0 SETRD0

AIE0 NAIE0 RLEIE0 – DNRIE0 NODIE0 EODIE0 SODIE0

ACK0 NACK0 RLE0 – DNR0 NOD0 EOD0 SOD0

PAGE0 0 0 0 A06 A05 A04 A03

0 L06 L05 L04 L03 L02 L01 L00

B

C7Hreserved

SETWR0

CLREP0 DONE0

EPSEL = 0XXX.X001

C1HEPBC1 00

C2HEPBS1 20

C3HEPIE1 00

C4HEPIR1 10

C5HEPBA1 00

H

H

H

H

H

C6HEPLEN1 0XXX.

XXXX

Endpoint 1 Registers

B

STALL1 0 0 GEPIE1 SOFDE1 INCE1 0 DBM1

UBF1 CBF1 DIR1 ESP1 SETRD1

AIE1 NAIE1 RLEIE1 – DNRIE1 NODIE1 EODIE1 SODIE1

ACK1 NACK1 RLE1 – DNR1 NOD1 EOD1 SOD1

PAGE1 0 0 0 A16 A15 A14 A13

0 L16 L15 L14 L13 L12 L11 L10

SETWR1

CLREP1 DONE1

B

C7Hreserved

Semiconductor Group 24 1997-10-01

Page 25

Table 5

Contents of the USB Device and Endpoint Registers (Addr. C1H to C7H) (cont’d)

C540U

C541U

Addr Register Reset

Value

EPSEL = 0XXX.X010

C1HEPBC2 00

C2HEPBS2 20

C3HEPIE2 00

C4HEPIR2 10

C5HEPBA2 00

B

H

H

H

H

H

C6HEPLEN2 0XXX.

XXXX

C7Hreserved

EPSEL = 0XXX.X011

C1HEPBC3 00

C2HEPBS3 20

C3HEPIE3 00

C4HEPIR3 10

C5HEPBA3 00

B

H

H

H

H

H

C6HEPLEN3 0XXX.

XXXX

C7Hreserved

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Endpoint 2 Registers

STALL2 0 0 GEPIE2 SOFDE2 INCE2 0 DBM2

UBF2 CBF2 DIR2 ESP2 SETRD2

AIE2 NAIE2 RLEIE2 – DNRIE2 NODIE2 EODIE2 SODIE2

ACK2 NACK2 RLE2 – DNR2 NOD2 EOD2 SOD2

PAGE2 0 0 0 A62 A52 A42 A32

0 L62 L52 L42 L32 L22 L12 L02

SETWR2

CLREP2 DONE2

B

Endpoint 3 Registers

STALL3 0 0 GEPIE3 SOFDE3 INCE3 0 DBM3

UBF3 CBF3 DIR3 ESP3 SETRD3

AIE3 NAIE3 RLEIE3 – DNRIE3 NODIE3 EODIE3 SODIE3

ACK3 NACK3 RLE3 – DNR3 NOD3 EOD3 SOD3

PAGE3 0 0 0 A63 A52 A43 A33

0 L63 L53 L43 L33 L23 L13 L03

SETWR3

CLREP3 DONE3

B

EPSEL = 0XXX.X100

C1HEPBC4 00

C2HEPBS4 20

C3HEPIE4 00

C4HEPIR4 10

C5HEPBA4 00

H

H

H

H

H

C6HEPLEN4 0XXX.

XXXX

Endpoint 4 Registers

B

STALL4 0 0 GEPIE4 SOFDE4 INCE4 0 DBM4

UBF4 CBF4 DIR4 ESP4 SETRD4

AIE4 NAIE4 RLEIE4 – DNRIE4 NODIE4 EODIE4 SODIE4

ACK4 NACK4 RLE4 –4 DNR4 NOD4 EOD4 SOD4

PAGE4 0 0 0 A64 A54 A44 A34

0 L64 L54 L44 L34 L24 L14 L04

SETWR4

CLREP4 DONE4

B

C7Hreserved

Semiconductor Group 25 1997-10-01

Page 26

C540U

C541U

Digital I/O Ports

The C540U/C541U in the P-SDIP-52 package has four 8-bit I/O ports. In the P-LCC-44 package

port 1 is a 6-bit I/O port only. Port 0 is an open-drain bidirectional I/O port, while ports 1 to 3 are

quasi-bidirectional I/O ports with internal pullup resistors. That means, when configured as inputs,

ports 1 to 3 will be pulled high and will source current when externally pulled low. Port 0 will float

when configured as input.

The output drivers of port 0 and 2 and the input buffers of port 0 are also used for accessing external

memory. In this application, port 0 outputs the low byte of the external memory address, time

multiplexed with the byte being written or read. Port 2 outputs the high byte of the external memory

address when the address is 16 bits wide. Otherwise, the port 2 pins continue emitting the P2 SFR

contents. In this function, port 0 is not an open-drain port, but uses a strong internal pullup FET.

Two port lines of port 1 (P1.0/LED0, P1.1/LED1) and one port line of port 3 (P3.0/LED2) have the

capability of driving external LEDs in the output low state.

Semiconductor Group 26 1997-10-01

Page 27

Timer / Counter 0 and 1

Timer/Counter 0 and 1 can be used in four operating modes as listed in table 6 :

Table 6

Timer/Counter 0 and 1 Operating Modes

Mode Description TMOD Input Clock

M1 M0 internal external (max)

C540U

C541U

0 8-bit timer/counter with a

00

f

/6x32 f

OSC

OSC

/12x32

divide-by-32 prescaler

1 16-bit timer/counter 1 1

2 8-bit timer/counter with

10

8-bit autoreload

3 Timer/counter 0 used as one

11

/6 f

OSC

OSC

/12

f

8-bit timer/counter and one

8-bit timer

Timer 1 stops

In the “timer” function (C/T = ‘0’) the register is incremented every machine cycle. Therefore the

count rate is f

OSC

/6.

In the “counter” function the register is incremented in response to a 1-to-0 transition at its

corresponding external input pin (P3.4/T0, P3.5/T1). Since it takes two machine cycles to detect a

falling edge the max. count rate is f

/12. External inputs INT0 and INT1 (P3.2, P3.3) can be

OSC

programmed to function as a gate to facilitate pulse width measurements. Figure 11 illustrates the

input clock logic.

P3.4/T0

P3.5/T1

Gate

(TMOD)

P3.2/INT0

P3.3/INT1

OSC

=1

÷

6

C/T = 0

C/T = 1

Control

TR0

TR1

_

<

1

&

f

/6

OSC

Timer 0/1

Input Clock

MCS03117

Figure 11

Timer/Counter 0 and 1 Input Clock Logic

Semiconductor Group 27 1997-10-01

Page 28

C540U

C541U

SSC Interface (C541U only)

The C541U microcontroller provides a Synchronous Serial Channel unit, the SSC. This interface is

compatible to the popular SPI serial bus interface. Figure 12 shows the block diagram of the SSC.

The central element of the SSC is an 8-bit shift register. The input and the output of this shift register

are each connected via a control logic to the pin P1.3 / SRI (SSC Receiver In) and P1.4 / STO (SSC

Transmitter Out). This shift register can be written to (SFR STB) and can be read through the

Receive Buffer Register SRB.

Pin

P1.2 / SCLK

f

OSC

Pin

P1.3 / SRI

Clock Divider

. . .

Clock Selection

STB

Shift Register

Pin

Control

Logic

Pin

P1.4 / STO

Interrupt

SCIEN

Int. Enable Reg.

SSCCON

Control Register

SRB

Receive Buffer Register

Control Logic

SCF

Status Register

Internal Bus

Pin

P1.5 / SLS

MCB03379

Figure 12

SSC Block Diagram

The SSC has implemented a clock control circuit, which can generate the clock via a baud rate

generator in the master mode, or receive the transfer clock in the slave mode. The clock signal is

fully programmable for clock polarity and phase. The pin used for the clock signal is P1.2/ SCLK.

When operating in slave mode, a slave select input is provided which enables the SSC interface

and also will control the transmitter output. The pin used for this is P1.5 / SLS.

The SSC control block is responsible for controlling the different modes and operation of the SSC,

checking the status, and generating the respective status and interrupt signals.

Semiconductor Group 28 1997-10-01

Page 29

C540U

C541U

USB Module

The USB module in the C540U/C541U handles all transactions between the serial USB bus and the

internal (parallel) bus of the microcontroller. The USB module includes several units which are

required to support data handling with the USB bus : the on-chip USB bus transceiver, the USB

memory with two pages of 128 bytes each, the memory management unit (MMU) for USB and CPU

memory access control, the UDC device core for USB protocol handling, the microcontroller

interface with the USB specific special function registers and the interrupt control logic. A clock

generation unit provides the clock signal for the USB module for full speed and low speed USB

operation. Figure 13 shows the block diagram of the functional units of the USB module with their

interfaces.

XTAL1 XTAL2

Pin Pin PinPin

x 4

PLL

48 MHz

Osc.

12 MHz

2

6 MHz

USB

D+

Transceiver

(On-chip)

Device

Bus

D-

USB

Core

(UDC)

7

F

H

00

H

Data

Control

Page 1

Page 0

USB

Memory

(128 x 8)

Data

Address

MMU

USB Memory

Management

F

7

H

00

H

Control

USB

Module

MCU

Interface

11

SFR

Addr.

Internal

Bus

Interrupt Generation

MCB03380

Figure 13

USB Module Block Diagram

Semiconductor Group 29 1997-10-01

Page 30

C540U

C541U

USB Registers

Two different kinds of registers are implemented in the USB module. The global registers (GEPIR,

EPSEL, ADROFF, USBVAL) describe the basic functionality of the complete USB module and can

be accessed via unique SFR addresses. For reduction of the number of SFR addresses which are

needed to control the USB module inside the C540U/C541U, device registers and endpoint

registers are mapped into an SFR address block of seven SFR addresses (C1H to C7H). The

endpoint specific functionality of the USB module is controlled via the device registers DCR,

DPWDR, DIER, DIRR and the frame number registers. An endpoint register set is available for each

endpoint (n=0..4) and describes the functionality of the selected endpoint. Figure 14 explains the

structure of the USB module registers.

Global Registers

USBVAL (D3 )

.5

.3

.4

.1

H

.0

000

.4.3.2 .1

GEPIR (D6 )

H

.0

.7

.6

Device

Registers

C1

H

DPWDR

C2

H

C3

H

C4

H

C5

reserved

H

C6

H

C7

H

DCR

DIER

DIRR

FNRL

FNRH

0.0

Endpoint 0

Registers

EPBC0

C1

H

EPBS0

C2

H

C3

EPIE0

H

EPIR0

C4

H

EPBA0

C5

H

C6

EPLEN0

H

C7

reserved

H

ADROFF (D4 )

.5

.30

.4 .2 .1

Endpoint 1

Registers

EPBC1

C1

H

EPBS1

C2

H

C3

C4

C5

C6

C7

EPIE1

H

EPIR1

H

EPBA1

H

EPLEN1

H

reserved

H

HH

.7

EPSEL (D2 )

0

00

0

.2.2.1

.0

Decoder

Endpoint 2

Registers

EPBC2

C1

H

EPBS2

C2

H

EPIE2

C3

H

EPIR2

C4

H

EPBA2

C5

H

EPLEN2

C6

H

reserved

C7

H

Endpoint 3

Registers

EPBC3

C1

H

EPBS3

C2

H

EPIE3

C3

H

EPIR3

C4

H

EPBA3

C5

H

EPLEN3

C6

H

reserved

C7

H

Endpoint 4

Registers

EPBC4

C1

H

EPBS4

C2

H

EPIE4

C3

H

EPIR4

C4

H

EPBA4

C5

H

EPLEN4

C6

H

reserved

C7

H

MCD03312

Figure 14

Register Structure of the USB Module

Semiconductor Group 30 1997-10-01

Page 31

C540U

C541U

Interrupt System

The C541U provides seven (C540U : six) interrupt sources with two priority levels. Five interrupts

can be generated by the on-chip peripherals (timer 0, timer 1, SSC interface, and USB module), and

two interrupts may be triggered externally (P3.2/INT0 and P3.3/INT1).

Figure 15 to 17 give a general overview of the interrupt sources and illustrate the request and

control flags which are described in the next sections.

Low Priority

Timer 0 Overflow

TF0

TCON.5

ET0

IEN0.1

000B

H

PT0

IP0.1

High Priority

Timer 1 Overflow

P3.2 /

INT0

IT0

TCON.0

P3.3 /

INT1

IT1

TCON.2

Bit addressable

Request Flag is cleared by hardware

ITCON.0

ITCON.1

ITCON.2

ITCON.3

≥1

≥1

TF1

TCON.7

IE0

TCON.1

IE0

TCON.3

ET1

IEN0.3

EX0

IEN0.0

EX1

IEN0.2

001B

0003

0013

EA

IEN0.7

H

PT1

IP0.3

H

PX0

IP0.0

H

PX1

IP0.2

Figure 15

Interrupt Request Sources (Part 1)

Semiconductor Group 31 1997-10-01

Page 32

Endpoint Interrupts

Endpoint 4 Interrupts

Endpoint 3 Interrupts

Endpoint 2 Interrupts

Endpoint 1 Interrupts

Endpoint 0 Interrupts

C540U

C541U

ACK0

EPIR0.7

NACK0

EPIR0.6

RLE0

EPIR0.5

DNR0

EPIR0.3

NOD0

EPIR0.2

EOD0

EPIR0.1

SOD0

EPIR0.0

AIE0

EPIE0.7

NAIE0

EPIE0.6

RLEIE0

EPIE0.5

DNRIE0

EPIE0.3

NODIE0

EPIE0.2

EODIE0

EPIE0.1

SODIE0

EPIE0.0

>1

EPI0

GEPIR.0

GEPIE0

EPBC0.4

>1

EUEI

IEN1.1

004B

Low Priority

High Priority

H

PUEI

IP1.1

WCOL

SSC

Interrupts

(C541U only)

SCF.1

TC

SCF.0

WCEN

SCIEN.1

TCEN

SCIEN.0

>1

ESSC

IEN1.0

0043

H

EA

IEN0.7

PSSC

IP1.0

Bit addressable

Request flag is cleared by hardware after the corresponding register has been read.

MCB03382

Figure 16

Interrupt Request Sources (Part 2)

Semiconductor Group 32 1997-10-01

Page 33

Device Interrupts

C540U

C541U

SE0I

DIRR.7

DAI

DIRR.6

DDI

DIRR.5

SBI

DIRR.4

SEI

DIRR.3

STI

DIRR.2

SUI

DIRR.1

SOFI

DIRR.0

Bit addressable

SE0IE

DIER.7

DAIE

DIER.6

DDIE

DIER.5

SBIE

DIER.4

SEIE

DIER.3

STIE

DIER.2

SUIE

DIER.1

SOFIE

DIER.0

>1

EUDI

IE1.2

0053

EA

IE0.7

Low Priority

High Priority

H

PUDI

IP1.2

Request flag is cleared by hardware after the corresponding register has been read.

MCB03383

Figure 17

Interrupt Request Sources (Part 3)

Table 7

Interrupt Source and Vectors

Interrupt Source Interrupt Vector Address Interrupt Request Flags (SFRs)

External Interrupt 0 0003

Timer 0 Overflow 000B

External Interrupt 1 0013

Timer 1 Overflow 001B

SSC Interrupt (C541U only) 0043

USB Endpoint Interrupt 004B

USB Device Interrupt 0053

Wake-up from power down 007B

H

H

H

H

H

H

H

H

IE0

TF0

IE1

TF1

TC, WCOL

in SFRs EPIR0-4 and GEIPR

in SFRs DIRR

–

Semiconductor Group 33 1997-10-01

Page 34

C540U

C541U

Fail Save Mechanisms

The C540U/C541U offers enhanced fail safe mechanisms, which allow an automatic recovery from

software upset or hardware failure :

– a programmable watchdog timer (WDT), with variable time-out period from 256 µs up to

approx. 0.55 µs at 12 MHz. The WDT is not available in the C540U.

– an oscillator watchdog (OWD) which monitors the on-chip oscillator and forces the

microcontroller into reset state in case the on-chip oscillator fails; it also provides the clock for

a fast internal reset after power-on.

The watchdog timer in the C517A is a 15-bit timer, which is incremented by a count rate of f

or f

/192. The system clock of the C517A is divided by two prescalers, a divide-by-two and a

OSC

OSC

/12

divide-by-16 prescaler which are selected by bit WDTPSEL (WDTREL.7). For programming of the

watchdog timer overflow rate, the upper 7 bit of the watchdog timer can be written. Figure 8-18

shows the block diagram of the watchdog timer unit.

07

f

/ 6

OSC

---

External HW Reset

2

WDT Reset-Request

-

OWDS WDTS WDT SWDT

Control Logic

16

WDCON (CO )

WDTL

14

WDTH

H

WDTPSEL

670

WDTREL

8

MCB03384

Figure 18

Block Diagram of the Watchdog Timer

The watchdog timer can be started by software (bit SWDT) but it cannot be stopped during active

mode of the C541U. If the software fails to refresh the running watchdog timer an internal reset will

be initiated on watchdog timer overflow. For refreshing of the watchdog timer the content of the SFR

WDTREL is transfered to the upper 7-bit of the watchdog timer. The refresh sequence consists of

two consequtive instructions which set the bits WDT and SWDT each. The reset cause (external

reset or reset caused by the watchdog) can be examined by software (flag WDTS). It must be noted,

however, that the watchdog timer is halted during the idle mode and power down mode of the

processor.

Semiconductor Group 34 1997-10-01

Page 35

C540U

C541U

Oscillator Watchdog

The oscillator watchdog unit serves for three functions:

– Monitoring of the on-chip oscillator's function

The watchdog supervises the on-chip oscillator's frequency; if it is lower than the frequency

of the auxiliary RC oscillator in the watchdog unit, the internal clock is supplied by the RC

oscillator and the device is brought into reset; if the failure condition disappears (i.e. the onchip oscillator has a higher frequency than the RC oscillator), the part executes a final reset

phase of typ. 1 ms in order to allow the oscillator to stabilize; then the oscillator watchdog reset

is released and the part starts program execution again.

– Fast internal reset after power-on

The oscillator watchdog unit provides a clock supply for the reset before the on-chip oscillator

has started. The oscillator watchdog unit also works identically to the monitoring function.

– Control of external wake-up from software power-down mode (description see chapter 9)

When the power-down mode is left by a low level at the INT0 pin or by the USB, the oscillator

watchdog unit assures that the microcontroller resumes operation (execution of the powerdown wake-up interrupt) with the nominal clock rate. In the power-down mode the RC

oscillator and the on-chip oscillator are stopped. Both oscillators are started again when

power-down mode is released. When the on-chip oscillator has a higher frequency than the

RC oscillator, the microcontroller starts operation after a final delay of typ. 1 ms in order to

allow the on-chip oscillator to stabilize.

Semiconductor Group 35 1997-10-01

Page 36

C540U

C541U

EWPD

Activity on

USB Bus

P3.2 / INT0

XTAL1

XTAL2

WS

(PCON1.4)(PCON1.7)

Control

Logic

RC

Oscillator

On-Chip

Oscillator

Start /

Stop

f

RC

3 MHz

Start /

Stop

Power - Down

Mode Activated

f

10

1

Comparator

f

2

Frequency

Power-Down Mode

Wake - Up Interrupt

Control

Logic

<

f

f

2

1

Delay

OWDS

Internal Reset

>1

WDCON (C0 )

H

Figure 19

Functional Block Diagram of the Oscillator Watchdog

Int. Clock

MCD03385

Semiconductor Group 36 1997-10-01

Page 37

C540U

C541U

Power Saving Modes

The C540U/C541U provides two basic power saving modes, the idle mode and the power down

mode.

– Idle mode

In the idle mode the main oscillator of the C540U/C541U continues to run, but the CPU is

gated off from the clock signal. However, the interrupt system, the SSC (C541U only), the

USB module, and the timers with the exception of the watchdog timer (C541U only) are further

provided with the clock. The CPU status is preserved in its entirety : the stack pointer, program

counter, program status word, accumulator, and all other registers maintain their data during

idle mode. The idle mode can be terminated by activating any enabled interrupt. or by a

hardware reset.

– Power down mode

In the power down mode, the RC osciillator and the on-chip oscillator which operates with the

XTAL pins is stopped. Therefore, all functions of the microcontroller are stopped and only the

contents of the on-chip RAM, XRAM and the SFR's are maintained. The power down mode

can be left either by an active reset signal or by a low signal at the P3.2/INT0 pin or any activity

on the USB bus. Using reset to leave power down mode puts the microcontroller with its SFRs

into the reset state. Using the INT0 pin or USB bus for power down mode exit maintains the

state of the SFRs, which has been frozen when power down mode is entered.

In the power down mode of operation, VCC can be reduced to minimize power consumption. It must

be ensured, however, that VCC is not reduced before the power down mode is invoked, and that V

is restored to its normal operating level, before the power down mode is terminated. Table 8 gives

a general overview of the entry and exit procedures of the power saving modes.

Table 8

Power Saving Modes Overview

Mode Entering

2-Instruction

Example

Idle mode ORL PCON, #01H

ORL PCON, #20H

Power Down Mode ORL PCON, #02H

ORL PCON, #40H

Leaving by Remarks

Ocurrence of an

interrupt from a

peripheral unit

Hardware Reset

Hardware Reset Oscillator is stopped;

Short low pulse at

pin P3.2/INT0

activity on the USB

bus

or

CPU clock is stopped;

CPU maintains their data;

peripheral units are active (if

enabled) and provided with

clock

contents of on-chip RAM and

SFR’s are maintained;

CC

Semiconductor Group 37 1997-10-01

Page 38

C540U

C541U

OTP Memory Operation

The C540U/C541U contains a 8k byte one-time programmable (OTP) program memory (C540U :

4k byte). With the C540U/C541U fast programming cycles are achieved (1 byte in 100 µsec). Also

several levels of OTP memory protection can be selected.

For programming of the device, the C540U/C541U must be put into the programming mode. This

typically is done not in-system but in a special programming hardware. In the programming mode

the C540U/C541U operates as a slave device similar as an EPROM standalone memory device

and must be controlled with address/data information, control lines, and an external 11.5V

programming voltage. Figure 20 shows the pins of the C504-2E which are required for controlling

of the OTP programming mode.

A0 - A7 /

A8 - A12

PALE

PMSEL0

PMSEL1

XTAL1

XTAL2

Figure 20

Programming Mode Configuration

V

CC

Port 2 Port 0

V

SS

C540U

C541U

D0 - D7

EA /

V

PP

PROG

PRD

RESET

PSEN

PSEL

MCS03386

Semiconductor Group 38 1997-10-01

Page 39

Pin Configuration in Programming Mode

N.C.

N.C.

N.C.

5

6

CC

SS

7

8

9

10

11

12

13

14

15

16

17

N.C.

V

V

RESET

PMSEL0

N.C: N.C.

PMSEL1

PSEL

PRD

PALE

GND

18 19 20

3

4

21 22 24

N.C.

N.C.

N.C.

D0

N.C.

21444342 41

C540U

C541U

Programming

Mode

23 282625

D1

27

D2

40

D3

39

38

37

36

35

34

33

32

31

30

29

D4

D5

D6

D7

V

EA /

PROG

PSEN

A7

A6

A5

C540U

C541U

PP

CC

XTAL1

XTAL2

VSSV

A1 / A9

A0 / A8

A2 / A10

A3 / A11

A4 / A12

MCP03387

GND

GND

Figure 21

P-LCC-44 Pin Configuration of the C540U/C541U in Programming Mode (Top View)

Semiconductor Group 39 1997-10-01

Page 40

C540U

C541U

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

V

CC

V

SS

RESET

PMSEL0

N.C.

N.C.

PMSEL1

PSEL

PRD

PALE

GND

GND

GND

XTAL2

XTAL1

V

SS

V

CC

152

2

3

4

5

6

7

8

9

10

11

12

13

14

15

C540U

C541U

Programming

Mode

16

17

18

19

20

21

22

23

24

25

26

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

N.C.

P1.5 / SLS

D0

D1

D2

D3

D4

D5

D6

D7

EA /

V

PP

N.C.

N.C.

PROG

PSEN

N.C.

N.C.

A7

A6

A5

A4 / A12

A3 / A11

A2 / A10

A1 / A9

A0 / A8

N.C.

MCP03388

Figure 22

P-SDIP-52 Pin Configuration of the C540U/C541U in Programming Mode (Top View)

Semiconductor Group 40 1997-10-01

Page 41

C540U

e

C541U

The following table 9 contains the functional description of all C517A-2E pins which are required for

OTP memory programming.

Table 9

Pin Definitions and Functions in Programming Mode

Symbol Pin Numbers I/O*) Function

P-LCC-44 P-SDIP-52

RESET 10 12 I Reset

This input must be at static “1“ (active) level during the

whole programming mode.

PMSEL0

PMSEL11113

13

16

I

I

Programming mode selection pins

These pins are used to select the different access

modes in programming mode. PMSEL1,0 must satisfy

a setup time to the rising edge of PALE. When the

logic level of PMSEL1,0 is changed, PALE must be at

low level.

PMSEL1PMSEL0Access Mode

0 0 Reserved

0 1 Read version bytes

1 0 Program/read lock bits

1 1 Program/read OTP memory byt

PSEL 14 17 I Basic programming mode select

This input is used for the basic programming mode

selection and must be switched according figure 10-

23.

PRD

15 18 I Programming mode read strobe

This input is used for read access control for OTP

memory read, version byte read, and lock bit read

operations.

PALE 16 19 I Programming mode address latch enable

PALE is used to latch the high address lines. The high

address lines must satisfy a setup and hold time to/

from the falling edge of PALE. PALE must be at low

level whenever the logic level of PMSEL1,0 is

changed.

XTAL2 20 23 O XTAL2

Output of the inverting oscillator amplifier.

*) I = Input

O = Output

Semiconductor Group 41 1997-10-01

Page 42

Table 9

Pin Definitions and Functions in Programming Mode (cont’d)

Symbol Pin Numbers I/O*) Function

P-LCC-44 P-SDIP-52

XTAL1 21 24 I XTAL1

Input to the oscillator amplifier.

C540U

C541U

A0/A8 A7

24 - 31 28 - 35 I Address lines

P2.0-7 are used as multiplexed address input lines

A0-A7 and A8-A12. A8-A12 must be latched with

PALE. Address A12 is requred only for the C541U.

PSEN

32 38 I Program store enable

This input must be at static “0“ level during the whole

programming mode.

PROG

33 39 I Programming mode write strobe

This input is used in programming mode as a write

strobe for OTP memory program and lock bit write

operations During basic programming mode selection

a low level must be applied to PROG.

EA

/V

PP

35 42 I External Access / Programming voltage

This pin must be at 11.5 V (VPP) voltage level during

programming of an OTP memory byte or lock bit.

During an OTP memory read operation this pin must

be at high level (VIH). This pin is also used for basic

programming mode selection. At basic programming

mode selection a low level must be applied to EA/VPP.

D0 - 7 43 - 38 50 - 43 I/O Data lines 0-7

During programming mode, data bytes are read or

written from or to the C540U/C541U via the

bidirectional D0-7 lines which are located at port 0.

V

SS

9, 22 11, 25 – Circuit ground potential

must be applied to these pins in programming mode.

V

CC

8, 23 10, 26 – Power supply terminal

must be applied to these pins in programming mode.

N.C. 1, 12,,

34, 44

1 - 9, 14,

15, 27, 36,

37, 40, 41,

– Not Connected

These pins should not be connected in programming

mode.

52

GND 17 - 19 20 - 22 I Ground pins

In programming mode these pins must be connected

V

level.

to

IL

*) I = Input

O = Output

Semiconductor Group 42 1997-10-01

Page 43

Basic Programming Mode Selection

The basic programming mode selection scheme is shown in figure 23.

C540U

C541U

V

CC

Clock

(XTAL1 / XTAL2)

RESET

PSEN

PMSEL1,0

PROG

PRD

PSEL

PALE

5 V

Stable

"1"

"0"

0,1

"0"

"1"

"0"

EA /

V

PP

During this Period Signals

are not actively driven

Figure 23

Basic Programming Mode Selection

0 V

V

PP

V

IH1

Ready for Access

Mode Selection

MCT03389

Semiconductor Group 43 1997-10-01

Page 44

Table 10

Access Modes Selection

C540U

C541U

Access Mode

V

Program OTP memory byte V

Read OTP memory byte V

Program OTP lock bits V

Read OTP lock bits V

Read OTP version byte V

EA

/

PROG PRD

PP

PP

IH

PP

IH

IH

H

H

H L H Byte addr.

H H H A0-7

H H L – D1,D0 see

PMSEL Address

10

(Port 2)

A8-15

Data

(Port 0)

D0-7

table 11

D0-7

of sign. byte

Lock Bits Programming / Read

The C540U/C541U has two programmable lock bits which, when programmed according tabie 11,

provide four levels of protection for the on-chip OTP code memory. The state of the lock bits can

also be read.

Table 11

Lock Bit Protection Types

Lock Bits at D1,D0 Protection

D1 D0

Level

Protection Type

1 1 Level 0 The OTP lock feature is disabled. During normal operation of

the C540U/C541U, the state of the EA

pin is not latched on

reset.

1 0 Level 1 During normal operation of the C540U/C541U, MOVC

instructions executed from external program memory are

disabled from fetching code bytes from internal memory. EA

sampled and latched on reset. An OTP memory read operation

is only possible using the OTP verification mode for protection

level 1. Further programming of the OTP memory is disabled

(reprogramming security).

0 1 Level 2 Same as level 1, but also OTP memory read operation using

OTP verification mode is disabled.

0 0 Level 3 Same as level 2; but additionally external code execution by

setting EA

=low during normal operation of the C540U/C541U

is no more possible.

External code execution, which is initiated by an internal

program (e.g. by an internal jump instruction above the ROM

boundary), is still possible.

is

Semiconductor Group 44 1997-10-01

Page 45

C540U

C541U

Absolute Maximum Ratings

Ambient temperature under bias (TA) ......................................................... 0 to 70 °C

Storage temperature (T

Voltage on VCC pins with respect to ground (VSS) ....................................... – 0.5 V to 6.5 V

Voltage on any pin with respect to ground (VSS)......................................... – 0.5 V to VCC +0.5 V

Input current on any pin during overload condition..................................... – 10 mA to 10 mA

Absolute sum of all input currents during overload condition ..................... I 100 mA I

Power dissipation........................................................................................ TBD

Note:Stresses above those listed under “Absolute Maximum Ratings” may cause permanent

damage of the device. This is a stress rating only and functional operation of the device at

these or any other conditions above those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating conditions for longer

periods may affect device reliability. During overload conditions (

Voltage on

V

CC

absolute maximum ratings.

) .......................................................................... – 65 °C to 150 °C

stg

V

>

V

CC

or

pins with respect to ground (

IN

V

) must not exceed the values defined by the

SS

V

<

V

SS

) the

IN

Semiconductor Group 45 1997-10-01

Page 46

C540U

C541U

DC Characteristics

V

= 4.0V to 5.5V (5V +10%, -20%); VSS = 0 V TA = 0 to 70 °C

CC

Parameter Symbol Limit Values Unit Test Condition

min. max.

Input low voltage (except EA,

RESET)

Input low voltage (EA

) V

Input low voltage (RESET)

Input high voltage (except XTAL1,

RESET)

Input high voltage to XTAL1

Input high voltage to RESET

Output low voltage

Ports 1, 2, 3

P1.0, P1.1, P3.0

Output low voltage (port 0, ALE,

PSEN)

Output high voltage (ports 1, 2, 3) V

Output high voltage (port 0 in

external bus mode, ALE, PSEN

)

Logic 0 input current (ports 1, 2, 3) I

Logical 1-to-0 transition current

(ports 1, 2, 3)

V

IL

– 0.5 0.2 VCC –

V–

0.1

IL1

– 0.5 0.2 VCC –

V–

0.3

V

IL2

– 0.5 0.2 VCC +

V–

0.1

V

IH

0.2 VCC +

V

+ 0.5 V –

CC

0.9

V

IH1

V

IH2

V

OL

V

OL1

OH

V

OH2

IL

I

TL

0.7 V

0.6 V

–

–

CC

CC

V

+ 0.5 V –

CC

V

+ 0.5 V –

CC

0.45

0.45

V

V

I

= 1.6 mA

OL

I

= 10 mA

OL

– 0.45 V IOL = 3.2 mA

2.4

0.9 V

2.4

0.9 V

CC

CC

–

–

–

–

V IOH = – 80 µA,

I

= – 10 µA

OH

V IOH = – 800 µA

I

= – 80 µA

OH

– 10 – 50 µA VIN = 0.45 V

– 65 – 650 µA VIN = 2 V

1)

1)

1)

2)

Input leakage current (port 0, EA

Pin capacitance C

Overload current I

Programming voltage V

) I

LI

OV

PP

– ± 1 µA 0.45 < VIN < V

IO

–10pFf

– ± 5mA

10.9 12.1

V

= 1 MHz,

c

T

= 25 °C

A

6) 7)

11.5 V ± 5%

CC

7)

Notes see next page

Semiconductor Group 46 1997-10-01

Page 47

C540U

C541U

Power Supply Current

Parameter Symbol Limit Values Unit Test Condition

8)

typ.

Active mode 12 MHz I

Idle mode 12 MHz I

Power-down mode I

CC

CC

PD

15 TBD mA

TBD TBD mA

TBD 50 µA VCC = 2…5.5 V

Notes :

1) Capacitive loading on ports 0 and 2 may cause spurious noise pulses to be superimposed on the VOL of ALE

and port 3. The noise is due to external bus capacitance discharging into the port 0 and port 2 pins when these

pins make 1-to-0 transitions during bus operation. In the worst case (capacitive loading > 100 pF), the noise

pulse on ALE line may exceed 0.8 V. In such cases it may be desirable to qualify ALE with a schmitt-trigger,

or use an address latch with a schmitt-trigger strobe input.

V

2) Capacitive loading on ports 0 and 2 may cause the

V

0.9

specification when the address lines are stabilizing.

CC

on ALE and PSEN to momentarily fall below the

OH

max.

9)

4)

5)

3)

3) IPD (power-down mode) is measured under following conditions:

= Port 0 = VCC ; XTAL2 = N.C.; XTAL1 = VSS ; RESET = VSS; all other pins are disconnected.

EA

the USB transceiver is switched off;

I

(active mode) is measured with:

4)

CC

XTAL1 driven with

= RESET = Port 0 = Port 1 = VCC ; all other pins are disconnected.

EA

I

would be slightly higher if a crystal oscillator is used (appr. 1 mA).

CC

t

CLCH

, t