Datasheet SAB80C515A-M18-T3, SAB80C515A-N18, SAB80C515A-N18-T3, SAB83C515A-5M18-T3, SAB83C515A-5N18 Datasheet (Siemens)

...Page 1

Microcomputer Components

8-Bit CMOS Single-Chip Microcontroller

SAB 80C515A/83C515A-5

Data Sheet 08.95

Page 2

∞

High-Performance SAB 80C515A / 83C515A-5

8-Bit CMOS Single-Chip Microcontroller

Preliminary

SAB 83C515A-5 Microcontroller with factory mask-programmable ROM

SAB 80C515A Microcontroller for external ROM

SAB 80C515A / 83C515A-5, up to 18 MHz operation frequency

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

×

32 K

256

Additional 1 K

8 ROM (SAB 83C515A-5 only, ROM-Protection available)

×

8 on-chip RAM

8 on-chip RAM (XRAM)

×

Superset of SAB 80C51 architecture:

1

µ

s instruction cycle time at 12 MHz

666 ns instruction cycle time at 18 MHz

256 directly addressable bits

Boolean processor

64 Kbyte external data and program memory addressing

Three 16-bit timer/counters

Versatile "fail-safe" provisions

Twelve interrupt vectors, four priority levels selectable

Genuine 10-bit A/D converter with 8 multiplexed inputs

Full duplex serial interface with programmable Baudrate-Generator

Functionally compatible with SAB 80C515

Extended power saving mode

Fast Power-On Reset

Seven ports: 48 I/O lines, 8 input lines

Two temperature ranges available:

0 to 70 ° C (T1)

– 40 to 85 ° C (T3)

Plastic packages: P-LCC-68 and P-MQFP-80

The SAB 80C515A/83C515A-5 is a high-end member of the Siemens SAB 8051

microcontroller family. It is designed in Siemens ACMOS technology and based on the

SAB 8051 architecture. ACMOS is a technology which combines high-speed and density

characteristics with low-power consumption or dissipation.

While maintaining all the SAB 80C515 features and operating characteristics the

SAB 80C515A/83C515A-5 contains more on-chip RAM/ROM. Furthermore a new 10-bit A/DConverter is implemented as well as extended security mechanisms. The SAB 80C515A is

identical with the SAB 83C515A-5 except that it lacks the on-chip program memory. The

SAB 80C515A / 83C515A-5 is supplied in a 68-pin plastic leaded chip carrier package

(P-LCC- 68) and in a 80-pin plastic metric quad flat package (P-MQFP-80).

Versions for extended temperature range – 40 to + 110

C are available on request.

Semiconductor Group 1 08.95

Page 3

−

SAB 80C515A/83C515A-5

Ordering Information

Type Ordering

Code

Package Description

8-Bit CMOS microcontroller

SAB 80C515A-N18 Q67120-C0581 P-LCC-68 for external memory, 18 MHz

SAB 83C515A-5N18 Q67120-DXXXX P-LCC-68 with mask-programmable ROM,

18 MHz

SAB 80C515A-N18-T3 Q67120-C0784 P-LCC-68 for external memory, 18 MHz

ext. temperature − 40 to + 85 ° C

SAB 83C515A-5N18-T3 Q67120-DXXXX P-LCC-68 with mask-programmable ROM,

18 MHz

ext. temperature − 40 to + 85 ° C

SAB 80C515A-M18-T3 Q67120-C0851 P-MQFP-80 for external memory, 18 MHz

ext. temperature − 40 to + 85 ° C

SAB 83C515A-5M18-T3 Q67120-DXXXX P-MQFP-80 with mask-programmable ROM,

18 MHz

40 to + 85 ° C

Notes

ext. temperature

:

Versions for extended temperature range − 40 to + 110

The ordering number of ROM types (DXXXX extension) is defined after program release

(verification) of the customer.

C on request.

°

Semiconductor Group 2

Page 4

SAB 80C515A/83C515A-5

Logic Symbol

Semiconductor Group 3

Page 5

SAB 80C515A/83C515A-5

The pin functions of the SAB 80C515A are identical with those of the SAB 80C515 with

following exception:

Pin SAB 80C515A SAB 80C515

68

1

4

HWPD

P0.4/ADST

PE/SWD

V

CC

P4.0

PE

Pin Configuration

(P-LCC-68)

Semiconductor Group 4

Page 6

P4.7

P4.6

P4.5

P4.4

P4.3

/ SWD

P4.2

PE

P4.1

N.C.

P4.0 / ADST

N.C.

HWPD

N.C.

P5.0

SAB 80C515A/83C515A-5

P5.2

P5.1

P5.3

P5.4

P5.5

P5.6

RESET

N.C.

VAREF

VAGND

P6.7 / AIN7

P6.6 / AIN6

P6.5 / AIN5

P6.4 / AIN4

P6.3 / AIN3

P6.2 / AIN2

P6.1 / AIN1

P6.0 / AIN0

N.C.

N.C.

P3.0 / RXD0

P3.1 / TXD0

P3.2 / INT0

P3.3 / INT1

P3.4 / T0

P3.5 / T1

80

1

5

10

15

20

21 25 30

P3.6 / WR

SAB 80C515A / 80C515A-5

N.C.

P1.7 / T2

P3.7 / RD

P1.4 / INT2

P1.5 / T2EX

P1.6 / CLKOUT

P1.3 / INT6 / CC3

35

VSS

VCC

VCC

/ CC0

P1.2 / INT5 / CC2

P1.1 / INT4 / CC1

P1.0 / INT3

657075

VSS

XTAL2

XTAL1

61

60

55

50

45

41

40

P2.0 / A8

P2.1 / A9

P2.2 / A10

P5.7

P0.7 / AD7

P0.6 / AD6

P0.5 / AD5

P0.4 / AD4

P0.3 / AD3

P0.2 / AD2

P0.1 / AD1

P0.0 / AD0

N.C.

N.C.

EA

ALE

PSEN

N.C.

P2.7 / A15

P2.6 / A14

P2.5 / A13

P2.4 / A12

P2.3 / A11

N.C. pins must not be connected.

Pin Configuration

(P-MQFP-80 )

Semiconductor Group 5

Page 7

Pin Definitions and Functions

SAB 80C515A/83C515A-5

Symbol Pin

P-LCC-68

Pin

P-MQFP-80

P4.0-P4.7 1-3, 5-9 72-74,

76-80

PE

/SWD 4 75 I

Input (I)

Output (O)

I/O

Function

Port 4

is an 8-bit bidirectional I/O port with internal

pull-up resistors. Port 4 pins that have 1’s written to them are pulled high by the internal pullup resistors, and in that state can be used as

inputs. As inputs, port 4 pins being externally

pulled low will source current ( I

, in the DC

IL

characteristics) because of the internal pull-up

resistors.

P4 also contains the external A/D converter

control pin. The output latch corresponding to

a secondary function must be programmed to

a one (1) for that function to operate. The secondary function assigned to port 6:

– ADST

(P4.0): external A/D converter start

pin

Power saving mode enable/Start Watchdog Timer

A low level on this pin allows the software to

enter the power down, idle and slow down

mode. In case the low level is also seen during

reset, the watchdog timer function is off on default.

Use of the software controlled power saving

modes is blocked, when this pin is held on

high level. A high level during reset performs

an automatic start of the watchdog timer immediately after reset.

When left unconnected this pin is pulled high

by a weak internal pull-up resistor.

RESET

V

AREF1

V

AGND

10 1 I

11 3

12 4

Semiconductor Group 6

Reset pin

A low level on this pin for the duration of two

machine cycles while the oscillator is running

resets the SAB 80C515A. A small internal

pullup resistor permits power-on reset using

only a capacitor connected to

V

SS

Reference voltage for the A/D converter

Reference ground for the A/D converter

Page 8

Pin Definitions and Functions (cont’d)

SAB 80C515A/83C515A-5

Symbol Pin

P-LCC-68

Pin

P-MQFP-80

Input (I)

Output (O)

P6.7-P6.0 13-20 5-12 I

P3.0-P3.7 21-28 15-22 I/O

Function

Port 6

is an 8-bit unidirectional input port to the A/

D converter. Port pins can be used for digital

input, if voltage levels simultaneously meet

the specifications high/low input voltages, and

for the eight multiplexed analog inputs.

Port 3

is an 8-bit bidirectional I/O port with internal

pullup resistors. Port 3 pins that have1's

written to them are pulled high by the internal

pullup resistors, and in that state can be used

as inputs. As inputs, port 3 pins being

externally pulled low will source current (

I

, in

IL

the DC characteristics) because of the internal

pullup resistors. Port 3 also contains the

interrupt, timer, serial port and external

memory strobe pins that are used by various

options. The output latch corresponding to a

secondary function must be programmed to a

one (1) for that function to operate. The

secondary functions are assigned to the pins

of port 3, as follows:

–R

×

D (P3.0): serial port’s receiver data

input (asynchronous) or data

input/output (synchronous)

–T

×

D (P3.1): serial port’s transmitter data

output (asynchronous) or

clock output (synchronous)

– INT0

(P3.2): interrupt 0 input/timer 0 gate

control input

– INT1

(P3.3): interrupt 1 input/timer 1 gate

control input

– T0 (P3.4): counter 0 input

– T1 (P3.5): counter 1 input

–WR

(P3.6): the write control signal

latches the data byte from

port 0 into the external data

memory

–RD

(P3.7): the read control signal

enables the external data

memory to port 0

Semiconductor Group 7

Page 9

Pin Definitions and Functions (cont’d)

–

SAB 80C515A/83C515A-5

Symbol Pin

P-LCC-68

P1.7 P1.0

29-36 24-31 I/O

Pin

P-MQFP-80

Input (I)

Output (O)

Function

Port 1

is an 8-bit bidirectional I/O port with internal

pullup resistors. Port 1 pins that have 1's

written to them are pulled high by the internal

pullup resistors, and in that state can be used

as inputs. As inputs, port 1 pins being

externally pulled low will source current (

the DC characteristics) because of the internal

pullup resistors. The port is used for the loworder address byte during program

verification. Port 1 also contains the interrupt,

timer, clock, capture and compare pins that

are used by various options. The output latch

corresponding to a secondary function must

be programmed to a one (1) for that function to

operate (except when used for the compare

functions). The secondary functions are

assigned to the port 1 pins as follows:

– INT3

/CC0 (P1.0): interrupt 3 input /

compare 0 output /

capture 0 input

I

in

IL

XTAL2 39 36

– INT4/CC1 (P1.1): interrupt 4 input /

compare 1 output /

capture 1 input

– INT5/CC2 (P1.2): interrupt 5 input /

compare 2 output /

capture 2 input

– INT6/CC3 (P1.3): interrupt 6 input /

compare 3 output /

capture 3 input

– INT2

– T2EX (P1.5): timer 2 external

– CLKOUT (P1.6): system clock output

– T2 (P1.7): counter 2 input

XTAL2

Input to the inverting oscillator amplifier and

input to the internal clock generator circuits.

(P1.4): interrupt 2 input

reloadtrigger input

Semiconductor Group 8

Page 10

Pin Definitions and Functions (cont’d)

SAB 80C515A/83C515A-5

-

Symbol Pin

P-LCC-68

Pin

P-MQFP-80

Input (I)

Output (O)

XTAL1 40 37

P2.0-P2.7 41-48 38-45 I/O

Function

XTAL1

Output of the inverting oscillator amplifier.

To drive the device from an external clock

source, XTAL2 should be driven, while XTAL1

is left unconnected. There are no requirements on the duty cycle of the external clock

signal, since the input to the internal clokking circuitry is divided down by a divide-bytwo flip-flop. Minimum and maximum high and

low times and rise/fall times specified in the

AC characteristics must be taken into account.

Port 2

is an 8-bit bidirectional I/O port with internal

pullup resistors. Port 2 pins that have 1's

written to them are pulled high by the internal

pullup resistors, and in that state can be used

as inputs. As inputs, port 2 pins being

externally pulled low will source current (

I

in

IL,

the DC characteristics) because of the internal

pullup resistors.

Port 2 emits the high-order address byte

during fetches from external program memory

and during accesses to external data memory

that use 16-bit addresses (MOVX@DPTR). In

this application it uses strong internal pullup

resistors when issuing 1's. During accesses to

external data memory that use 8-bit

addresses (MOVX@Ri), port 2 issues the

contents of the P2 special function register.

PSEN

49 47 O The Program Store Enable

output is a control signal that enables the

external program memory to the bus during

external fetch operations. It is activated every

six oscillator periods, except during external

data memory accesses. The signal remains

high during internal program execution.

ALE 50 48 O The

output is used for latching the address into

external memory during normal operation. It is

activated every six oscillator periods, except

during an external data memory access.

Semiconductor Group 9

Address Latch enable

Page 11

Pin Definitions and Functions (cont’d)

SAB 80C515A/83C515A-5

Symbol Pin

P-LCC-68

Pin

P-MQFP-80

Input (I)

Output (O)

Function

EA 51 49 I External Access Enable

When held high, the SAB 80C515A executes

instructions from the internal ROM as long as

the PC is less than 32768. When held low, the

SAB 80C515A fetches all instructions from

external program memory. For the SAB

80C515A this pin must be tied low.

P0.0-P0.7 52-59 52-59 I/O Port 0

is an 8-bit open-drain bidirectional I/O port.

Port 0 pins that have 1's written to them float,

and in that state can be used as highimpedance inputs.

Port 0 is also the multiplexed low-order

address and data bus during accesses to

external program and data memory. In this

application it uses strong internal pullup

resistors when issuing 1's.

Port 0 also outputs the code bytes during

program verification in the SAB 80C515A.

External pullup resistors are required during

program verification.

P5.7-P5.0 60-67 60-67 I/O Port 5 is an 8-bit bidirectional I/O port with

internal pullup resistors. Port 5 pins that have

1's written to them are pulled high by the

internal pullup resistors, and in that state can

be used as inputs. As inputs, port 5 pins being

externally pulled low will source current

(I

in the DC characteristics) because of the

IL

internal pullup resistors.

HWPD

68 69 I Hardware Power Down

A low level on this pin for the duration of one

machine cycle while the oscillator is running

resets the SAB 80C515A.

A low level for a longer period will force the

part to Power Down Mode with the pins floating. (see table 5)

V

CC

37 32, 33 – Supply voltage

during normal, idle, and power-down operation.

V

SS

N.C. – 2, 13, 14, 23,

38 34, 35 – Ground (0 V)

– Not connected

46, 50, 51,

68, 70, 71

These pins of the P-MQFP-80 package must

not be connected.

Semiconductor Group 10

Page 12

SAB 80C515A/83C515A-5

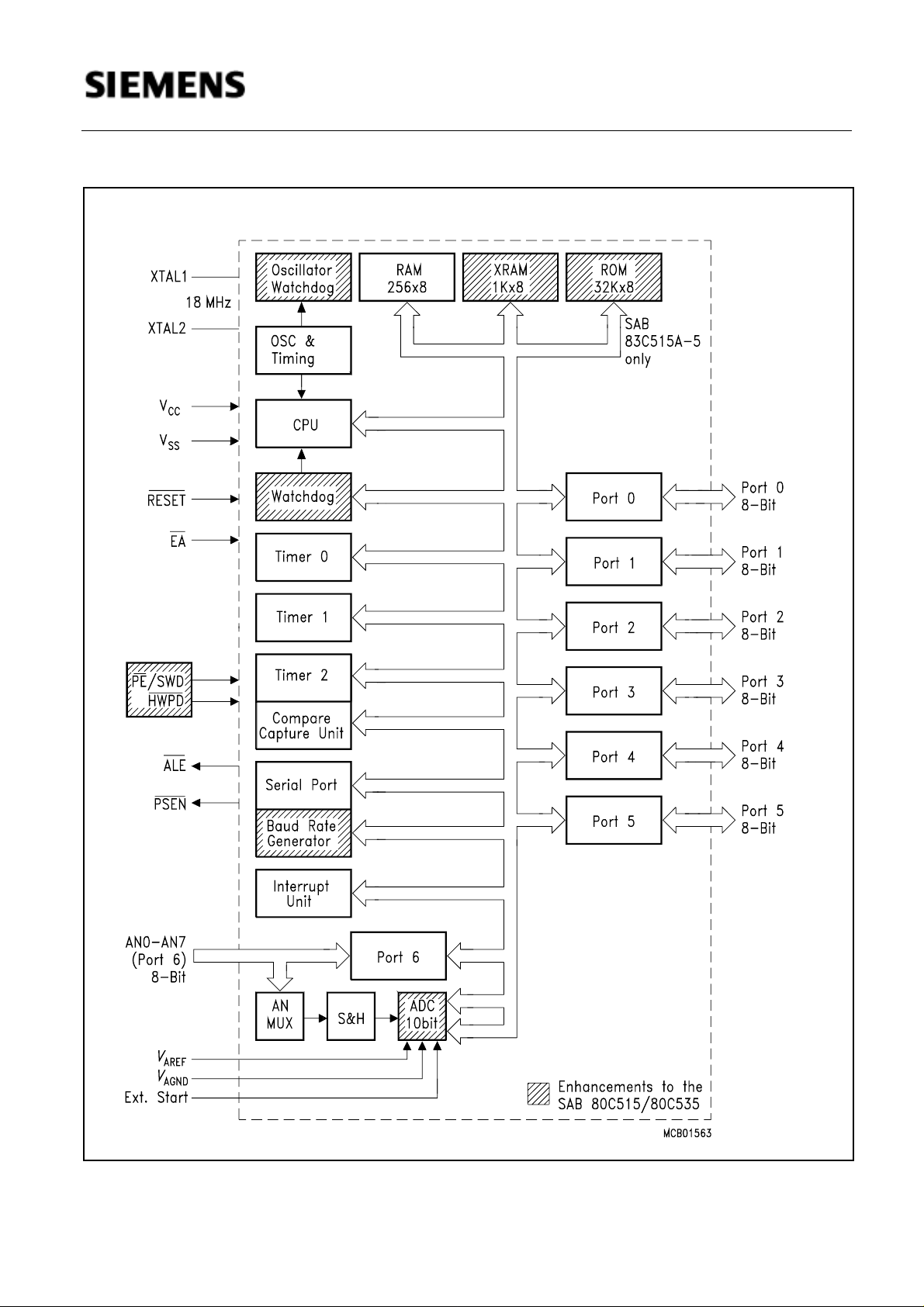

Figure 1

Block Diagram

Semiconductor Group 11

Page 13

SAB 80C515A/83C515A-5

Functional Description

The SAB 80C515A is based on 8051 architecture. It is a fully compatible member of the

Siemens SAB 8051/80C51 microcontroller family being an significantly enhanced

SAB 80C515. The SAB 80C515A is therefore code compatible with the SAB 80C515.

Having an 8-bit CPU with extensive facilities for bit-handling and binary BCD arithmetics the

SAB 80C515A is optimized for control applications. With a 18 MHz crystal, 58 % of the

instructions are executed in 666.67 ns.

While maintaining all architectural and operational characteristics of the SAB 80C515 the SAB

80C515A incorporates more on-chip RAM. A new 10-bit A/D-Converter is implemented as well

as an oscillator watchdog unit. Also the maximum operating frequency of 18 MHz is higher than

at the SAB 80C515.

With exception of the ROM sizes both parts are identical. Therefore the therm SAB 80C515A

refers to both versions within this specification unless otherwise noted.

Memory Organisation

According to the SAB 8051 architecture, the SAB 80C515A has separate address spaces for

program and data memory. Figure 2 illustrates the mapping of address spaces.

Figure 2

Memory Map

Semiconductor Group 12

Page 14

SAB 80C515A/83C515A-5

Program Memory ('Code Space')

The SAB 83C515A-5 has 32 Kbyte of on-chip ROM, while the SAB 80C515A has no internal

ROM. The program memory can externally be expanded up to 64 Kbyte. Pin EA

whether program fetches below address 8000

are done from internal or external memory.

H

As a new feature the SAB 83C515A-5 offers the possibility of protecting the internal ROM

against unauthorized access. This protection is implemented in the ROM-Mask. Therefore, the

decision ROM-Protection 'yes' or 'no' has to be made when delivering the ROM-Code. Once

enabled, there is no way of disabling the ROM-Protection.

Effect: The access to internal ROM done by an externally fetched MOVC instruction is

disabled. Nevertheless, an access from internal ROM to external ROM is possible.

To verify the read protected ROM-Code a special ROM-Verify-Mode is implemented. This

mode also can be used to verify unprotected internal ROM.

determines

ROM -Protection ROM-Verification Mode

Restrictions

(see 'AC Characteristics')

no ROM-Verification Mode 1

–

(standard 8051 Verification Mode)

ROM-Verification Mode 2

yes ROM-Verification Mode 2 – standard 8051

Verification Mode is

disabled

– externally applied MOVC

accessing internal ROM

is disabled

Semiconductor Group 13

Page 15

SAB 80C515A/83C515A-5

Data Memory ('Data Space')

The data memory space consists of an internal and an external memory space.The

SAB 80C515A contains another 1 Kbyte on On-Chip RAM additional to the 256-bytes internal

RAM of the base type SAB 80C515. This RAM is called XRAM ('extended RAM') in this

document.

External Data Memory

Up to 64 Kbyte external data memory can be addressed by instructions that use 8-bit or 16-bit

indirect addressing. For 8-bit addressing MOVX instructions in combination with registers R0

and R1 can be used. A 16-bit external memory addressing is supported by a 16-bit datapointer.

Registers XPAGE and SYSCON are controlling whether data fetches at addresses F800

FBFF

are done from internal XRAM or from external data memory.

H

Internal Data Memory

H

to

The internal data memory is divided into four physically distinct blocks:

– the lower 128 bytes of RAM including four register banks containing eight

registers each

– the upper 128 byte of RAM

– the 128 byte special function register area.

– a 1 K

chip at the address range from F800

× 8 area which is accessed like external RAM (MOVX-instructions), implemented on

to FBFFH. Special Function Register SYSCON

H

controls whether data is read from or written to XRAM or external RAM.

A map of the internal data memory is shown in figure 2. The overlapping address spaces of the

standard internal data memory (256 byte) are accessed by different addressing modes (see

User's Manual SAB 80C515). The stack can be located anywhere in the internal data memory.

Architecture of the XRAM

The contents of the XRAM is not affected by a reset or HW Power Down. After power-up the

contents is undefined, while it remains unchanged during and after a reset or HW Power Down

if the power supply is not turned off.

The additional On-Chip RAM is logically located in the "external data memory" range at the

upper end of the 64 Kbyte address range (F800

enabled the address range F800

to FFFFH is occupied. This is done to assure software

H

-FBFFH). Nevertheless when XRAM is

H

compatibility to SAB 80C517A. It is possible to enable and disable (only by reset) the XRAM. If

it is disabled the device shows the same behaviour as the parts without XRAM, i.e. all MOVX

accesses use the external bus to physically external data memory.

Semiconductor Group 14

Page 16

SAB 80C515A/83C515A-5

Accesses to XRAM

Because the XRAM is used in the same way as external data memory the same instruction

types must be used for accessing the XRAM.

Note:

If a reset occurs during a write operation to XRAM, the effect on XRAM depends on the

cycle which the reset is detected at (MOVX is a 2-cycle instruction):

Reset detection at cycle 1: The new value will not be written to XRAM. The old value

is not affected.

Reset detection at cycle 2: The old value in XRAM is overwritten by the new value.

Accesses to XRAM using the DPTR

There are a Read and a Write instruction from and to XRAM which use one of the 16-bit DPTR

for indirect addressing. The instructions are:

MOVX A, @DPTR (Read)

MOVX @DPTR, A (Write)

Normally the use of these instructions would use a physically external memory. However, in the

SAB 80C515A the XRAM is accessed if it is enabled and if the DPTR points to the XRAM

address space (DPTR ≥ F800

Accesses to XRAM using the Registers R0/R1

The 8051 architecture provides also instructions for accesses to external data memory range

which use only an 8-bit address (indirect addressing with registers R0 or R1). The instructions

are:

).

H

MOVX A, @Ri (Read)

MOVX @Ri, A (Write)

In application systems, either a real 8-bit bus (with 8-bit address) is used or Port 2 serves as

page register which selects pages of 256-byte. However, the distinction, whether Port 2 is

used as general purpose I/O or as "page address" is made by the external system design. From

the device’s point of view it cannot be decided whether the Port 2 data is used externally as

address or as I/O data!

Hence, a special page register is implemented into the SAB 80C515A to provide the possibility

of accessing the XRAM also with the MOVX @Ri instructions, i.e. XPAGE serves the same

function for the XRAM as Port 2 for external data memory.

Semiconductor Group 15

Page 17

Special Function Register XPAGE

SAB 80C515A/83C515A-5

Addr. 91

H

XPAGE

The reset value of XPAGE is 00H.

XPAGE can be set and read by software.

The register XPAGE provides the upper address byte for accesses to XRAM with MOVX @Ri

instructions. If the address formed from XPAGE and Ri is less than the XRAM address range,

then an external access is performed. For the SAB 80C515A the contents of XPAGE must be

greater or equal than F8

in order to use the XRAM. Of course, the XRAM must be enabled if

H

it shall be used with MOVX @Ri instructions.

Thus, the register XPAGE is used for addressing of the XRAM; additionally its contents are

used for generating the internal XRAM select. If the contents of XPAGE is less than the XRAM

address range then an external bus access is performed where the upper address byte is

provided by P2 and not by XPAGE!

Therefore, the software has to distinguish two cases, if the MOVX @Ri instructions with paging

shall be used:

a) Access to XRAM: The upper address byte must be written to XPAGE or P2;

both writes selects the XRAM address range.

b) Access to external memory: The upper address byte must be written to P2; XPAGE will

be loaded with the same address in order to deselect the

XRAM.

Semiconductor Group 16

Page 18

SAB 80C515A/83C515A-5

Control of XRAM in the SAB 80C515A

There are two control bits in register SYSCON which control the use and the bus operation

during accesses to the additional On-Chip RAM (XRAM).

Special Function Register SYSCON

Addr. 0B1

H

XMAP1 XMAP0 SYSCON

Bit Function

XMAP0 Global enable/disable bit for XRAM memory.

XMAP0 =0: The access to XRAM (= On-Chip XDATA memory) is en-

abled.

XMAP0 = 1: The access to XRAM is disabled. All MOVX accesses are

performed by the external bus (reset state).

XMAP1 Control bit for / RD/WR

signals during accesses to XRAM; this bit has no

effect if XRAM is disabled (XMAP0 = 1) or if addresses exceeding the

XRAM address range are used for MOVX accesses.

XMAP1 = 0: The signals RD

and WR are not activated during accesses

to XRAM.

XMAP1 = 1: The signals RD

and WR are activated during accesses to

XRAM.

Reset value of SYSCON is XXXX XX01B.

The control bit XMAP0 is a global enable/disable bit for the additional On-Chip RAM (XRAM).

If this bit is set, the XRAM is disabled, all MOVX accesses use external memory via the external

bus. In this case the SAB 80C515A does not use the additional On-Chip RAM and is compatible

with the types without XRAM.

Semiconductor Group 17

Page 19

SAB 80C515A/83C515A-5

XMAP0 is hardware protected by an unsymmetric latch. An unintentional disabling of XRAM

could be dangerous since indeterminate values would be read from external bus. To avoid this

the XMAP-bit is forced to '1' only by reset. Additionally, during reset an internal capacitor is

loaded. So after reset state XRAM is disabled. Because of the load time of the capacitor

XMAP0-bit once written to '0' (that is, discharging capacitor) cannot be set to '1' again by

software. On the other hand any distortion (software hang up, noise, ...) is not able to load this

capacitor, too. That is, the stable status is XRAM enabled. The only way to disable XRAM after

it was enabled is a reset.

The clear instruction for XMAP0 should be integrated in the program initialization routine before

XRAM is used. In extremely noisy systems the user may have redundant clear instructions.

The control bit XMAP1 is relevant only if the XRAM is accessed. In this case the external RD

and WR

debug purposes it might be useful to have these signals and the addresses at Ports 0.2

available. This is performed if XMAP1 is set.

The behaviour of Port 0 and P2 during a MOVX access depends on the control bits in register

SYSCON and on the state of pin EA

the following characteristics:

a) Use of P0 and P2 pins during the MOVX access.

Bus: The pins work as external address/data bus. If (internal) XRAM

I/0: The pins work as Input/Output lines under control of their latch.

b) Activation of the RD

c) Use of internal or external XDATA memory.

The shaded areas describe the standard operation as each 80C51 device without on-chip

XRAM behaves.

signals at P3.6 and P3.7 are not activated during the access, if XMAP1 is cleared. For

. The table 1 lists the various operating conditions. It shows

is accessed, the data written to the XRAM can be seen on the bus in

debug mode.

and WR pin during the access.

Semiconductor Group 18

Page 20

Semiconductor Group 19

Table 1:

Behaviour of P0/P2 and

RD/WR during MOVX accesses

MOVX

@DPTR

MOVX

@Ri

DPTR < XRAM

address

range

DPTR ≥ XRAM

address

range

XPAGE < XRAM

addr.

page

range

XPAGE ≥ XRAM

addr.

page

range

00 10 X1

a) P0/P2

b) RD

c) ext. memory is

used

a) P0/P2➝BUS

(WR -Data only)

b) RD/WR inactive

c) XRAM is used

a) P0➝Bus

P2

b)

c) ext. memory is

used

a) P0/P2➝BUS

(WR -Data only)

P2➝I/0

b)

c) XRAM is used

➝Bus

/WR active

➝I/0

RD/WR active

RD/WR inactive

EA = 0

XMAP1, XMAP0

a) P0/P2

b) RD

c) ext. memory is

used

a) P0/P2➝BUS

(WR -Data only)

b) RD/WR active

c) XRAM is used

a) P0

P2

b)

c) ext. memory is

used

a) P0/P2➝BUS

(WR -Data only)

P2➝I/0

b)

c) XRAM is used

➝Bus

/WR active

➝Bus

➝I/0

RD/WR active

RD/WR active

a) P0/P2

b)

c) ext. memory is

used

a) P0/P2

b)

c) ext. memory is

used

a) P0

P2

b)

c) ext. memory is

used

a) P0

P2

b)

c) ext. memory is

used

➝Bus

RD/WR active

➝Bus

RD/WR active

➝Bus

➝I/0

RD/WR active

➝Bus

➝I/0

RD/WR active

00 10 X1

a) P0/P2

b)

c) ext. memory is

used

a) P0/P2➝I/0

b)

c) XRAM is used

a) P0

P2

b)

c) ext. memory is

used

a) P0/P2➝I/0

b)

c) XRAM is used

➝Bus

RD/WR active

RD/WR inactive

➝Bus

➝I/0

RD/WR active

RD/WR inactive

EA = 1

XMAP1, XMAP0

a) P0/P2

b)

c) ext. memory is

used

a) P0/P2➝BUS

(WR -Data only)

b) RD/WR active

c) XRAM is used

a) P0

P2

b)

c) ext. memory is

used

a) P0➝BUS

(WR -Data only)

P2➝I/0

b)

c) XRAM is used

➝Bus

RD/WR active

➝Bus

➝I/0

RD/WR active

RD/WR active

a) P0/P2

b)

c) ext. memory is

used

a) P0/P2➝Bus

b)

c) ext. memory is

used

a) P0

P2

b)

c) ext. memory is

used

a) P0

P2

b)

c) ext. memory is

used

➝Bus

RD/WR active

RD/WR active

➝Bus

➝I/0

RD/WR active

➝Bus

➝I/0

RD/WR active

SAB 80C515A/83C515A-5

modes compatible to 8051 - family

Page 21

SAB 80C515A/83C515A-5

Special Function Registers

All registers, except the program counter and the four general purpose register banks, reside

in the special function register area. The special function registers include arithmetic registers,

pointers, and registers that provide an interface between the CPU and the on-chip peripherals.

There are also 128 directly addressable bits within the SFR area. All special function registers

are listed in table 2 and table 3.

In table 2 they are organized in numeric order of their addresses. In table 3 they are organized

in groups which refer to the functional blocks of the SAB 80C515A.

Table 2

Special Function Register

Address Register Contents

Address Register Contents

after Reset

1)

80

H

81

H

82

H

83

H

84

H

85

H

86

H

87

H

88

H

89

H

8A

H

8B

H

8C

H

8D

H

8E

H

8F

H

90

H

91

H

92

H

93

H

94

H

95

H

96

H

97

H

1)

Bit-addressable special function registers

2)

X means that the value is indeterminate and the location is reserved

P0

SP

DPL

DPH

(WDTL)

(WDTH)

WDTREL

PCON

TCON

1)

TMOD

TL0

TL1

TH0

TH1

reserved

reserved

1)

P1

XPAGE

reserved

reserved

reserved

reserved

reserved

reserved

0FF

07

00

00

00

00

00

00

00

00

00

00

XX

XX

0FF

XX

XX

XX

XX

XX

XX

XX

H

H

H

H

H

H

H

H

H

H

H

H

2)

H

2)

H

H

2)

H

2)

H

2)

H

2)

H

2)

H

2)

H

2)

H

98

99

9A

9B

9C

9D

9E

9F

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

AA

AB

AC

AD

AE

AF

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

S0CON

SBUF

reserved

reserved

reserved

reserved

reserved

reserved

1)

P2

reserved

reserved

reserved

reserved

reserved

reserved

reserved

1)

IEN0

IP0

SRELL

reserved

reserved

reserved

reserved

reserved

after Reset

1)

00

H

XXH

XX

H

XX

H

XX

H

XX

H

XX

H

XX

H

0FF

XX

H

XX

H

XX

H

XX

H

XX

H

XX

H

XX

H

00

H

00

H

0D9

XX

H

XX

H

XX

H

XX

H

XX

H

2)

2)

2)

2)

2)

2)

2)

H

2)

2)

2)

2)

2)

2)

2

H

2)

2)

2)

2)

2)

Semiconductor Group 20

Page 22

Table 2: Special Function Register (cont’d)

SAB 80C515A/83C515A-5

Address Register Contents

Address Register Contents

after Reset

B0

H

B1

H

B2

H

B3

H

B4

H

B5

H

B6

H

B7

H

B8

H

B9

H

BA

H

BB

H

BC

H

BD

H

BE

H

BF

H

C0

H

C1

H

C2

H

C3

H

C4

H

C5

H

C6

H

C7

H

C8

H

C9

H

CA

H

CB

H

CC

H

CD

H

CE

H

CF

H

1)

Bit-addressable special function registers

2)

X means that the value is indeterminate and the location is reserved

1)

P3

SYSCON

reserved

reserved

reserved

reserved

reserved

reserved

1)

EN1

IP1

SRELH

reserved

reserved

reserved

reserved

reserved

IRCON

1)

CCEN

CCL1

CCH1

CCL2

CCH2

CCL3

CCH3

T2CON

reserved

CRCL

CRCH

TL2

TH2

reserved

reserved

1)

0FF

H

XXXX XX01

2)

XX

H

2)

XX

H

2)

XX

H

2)

XX

H

2)

XX

H

2

XX

H

00

H

XX00 0000

XXXX XX11

2)

XX

H

2)

XX

H

2)

XX

H

2

XX

H

2)

XX

H

00

H

00

H

00

H

00

H

00

H

00

H

00

H

00

H

00

H

2)

XX

H

00

H

00

H

00

H

00

H

2)

XX

H

2

XX

H

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

DA

DB

DV

DD

DE

DF

E0

E1

E2

E3

E4

E5

E6

E7

E8

E9

EA

EB

EC

ED

EE

EF

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

2)

B

2)

B

2)

B

PSW

1)

reserved

reserved

reserved

reserved

reserved

reserved

reserved

ADCON0

ADDATH

ADDATL

P6

ADCVON1

reserved

reserved

reserved

1)

ACC

reserved

reserved

reserved

reserved

reserved

reserved

reserved

1)

P4

reserved

reserved

reserved

reserved

reserved

reserved

reserved

after Reset

00

XX

XX

XX

XX

XX

XX

XX

1)

00

00

00

XX

XXXX 0000

XX

XX

XX

00

XX

XX

XX

XX

XX

XX

XX

0FF

XX

XX

XX

XX

XX

XX

XX

H

2)

H

2)

H

2)

H

2)

H

2)

H

2)

H

2)

H

H

H

H

2)

H

2)

H

2)

H

2)

H

H

2)

H

2)

H

2)

H

2)

H

2)

H

2)

H

2)

H

H

2)

H

2)

H

2)

H

2)

H

2)

H

2)

H

2)

H

2)

B

Semiconductor Group 21

Page 23

Table 2: Special Function Register (cont’d)

SAB 80C515A/83C515A-5

Address Register Contents

Address Register Contents

after Reset

1)

F0

H

F1

H

F2

H

F3

H

F4

H

F5

H

F6

H

F7

H

1)

Bit-addressable special function registers

2)

X means that the value is indeterminate and the location is reserved

B

reserved

reserved

reserved

reserved

reserved

reserved

reserved

00

XX

XX

XX

XX

XX

XX

XX

H

2)

H

2)

H

2)

H

2)

H

2)

H

2)

H

2

H

F8

F9

FA

FB

FC

FD

FE

FF

H

H

H

H

H

H

H

H

1)

P5

reserved

reserved

after Reset

00F

H

2)

XX

H

2)

XX

H

Semiconductor Group 22

Page 24

SAB 80C515A/83C515A-5

Table 3

Special Function Registers - Functional Blocks

Block Symbol Name Address Contents

after Reset

1)

CPU ACC

B

DPH

DPL

PSW

SP

A/DConverter

ADCON0

ADCON1

ADDATH

ADDATL

Interrupt

System

EN0

IEN1

IP0

IP1

IRCON0

TCON

T2CON

Accumulator

B-Register

Data Pointer, High Byte

Data Pointer, Low Byte

Program Status Word Register

Stack Pointer

A/D Converter Control Register 0

A/D Converter Control Register 1

A/D Converter Data Reg. High Byte

A/D Converter Data Reg. Low Byte

Interrupt Enable Register 0

Interrupt Enable Register 1

Interrupt Priority Register 0

Interrupt Priority Register 1

Interrupt Request Control Register

2)

Timer Control Register

2)

Timer 2 Control Register

0E0

H

0F0H

83

H

82

H

0D0H

81

H

0D8

H

0DC

H

0D9

H

0DA

H

0A8

H

0B8H

0A9

H

0B9

H

0C0H

1)

88H

0C8

H

1)

1)

1)

1)

1)

1)

00

H

00

H

00

H

00

H

00

H

07

H

00

H

0XXX 0000

00

H

00

H

00

H

00

H

00

H

XX00 0000

00

H

00

H

00

H

3)

B

B

Compare/

CaptureUnit

(CCU)

XRAM XPAGE

CCEN

CCH1

CCH2

CCH3

CCL1

CCL2

CCL3

CRCH

CRCL

TH2

TL2

T2CON

Comp./Capture Enable Reg.

Comp./Capture Reg. 1, High Byte

Comp./Capture Reg. 2, High Byte

Comp./Capture Reg. 3, High Byte

Comp./Capture Reg. 1, Low Byte

Comp./Capture Reg. 2, Low Byte

Comp./Capture Reg. 3, Low Byte

Com./Rel./Capt. Reg. High Byte

Com./Rel./Capt. Reg. Low Byte

Timer 2, High Byte

Timer 2, Low Byte

Timer 2 Control Register

Page Address Register for Exten-

0C1

H

0C3

H

0C5

H

0C7

H

0C2

H

0C4

H

0C6

H

0CB

H

0CA

H

0CD

H

0CC

H

0C8H

91

H

1)

ded On Chip RAM

SYSCON

1)

Bit-addressable special function registers

2)

This special function register is listed repeatedly since some bits of it also belong to other

functional blocks.

3)

X means that the value is indeterminate and the location is reserved

XRAM Control Register

0B1

H

00

H

00

H

00

H

00

H

00

H

00

H

00

H

00

H

00

H

00

H

00

H

00

H

00

H

XXXX XX01

3)

B

Semiconductor Group 23

Page 25

SAB 80C515A/83C515A-5

Table 3

Special Function Registers - Functional Blocks (cont’d)

Block Symbol Name Address Contents

after Reset

1)

Ports P0

P1

P2

P3

P4

P5

P6

Port 0

Port 1

Port 2

Port 3

Port 4

Port 5

Port 6, Analog/Digital Input

80

H

1)

90H

0A0H

0B0H

0E8H

0F8H

0DB

H

1)

1)

1)

1)

0FF

0FF

0FF

0FF

0FF

0FF

H

H

H

H

H

H

Pow.Sav.M

PCON Power Control Register 87

H

ode

Serial

Channels

ADCON0

PCON

2)

SBUF

SCON

SRELL

2)

A/D Converter Control Reg.

Power Control Register

Serial Channel Buffer Reg.

Serial Channel Control Reg.

Serial Channel Reload Reg.,

0D8

87

99

98H

AA

1)

H

H

H

1)

H

low byte

SRELH

Serial Channel Reload Reg.,

BA

H

high byte

Timer 0/

Timer 1

Watchdog

1)

Bit-addressable special function registers

2)

This special function register is listed repeatedly since some bits of it also belong to other

functional blocks.

3)

X means that the value is indeterminate and the location is reserved

TCON

TH0

TH1

TL0

TL1

TMOD

IEN0

IEN1

IP0

IP1

2)

2)

2)

2)

WDTREL

Timer Control Register

Timer 0, High Byte

Timer 1, High Byte

Timer 0, Low Byte

Timer 1, Low Byte

Timer Mode Register

Interrupt Enable Register 0

Interrupt Enable Register 1

Interrupt Priority Register 0

Interrupt Priority Register 1

Watchdog Timer Reload Reg.

1)

88

H

8C

H

8D

H

8A

H

8B

H

89

H

0A8

H

0B8H

0A9

H

0B9

H

86

H

1)

1)

00

H

00

H

00

H

0XX

00

D9

3)

H

H

H

XXXX XX11

00

H

00

H

00

H

00

H

00

H

00

H

00

H

00

H

00

H

XX00 0000

00

H

3)

B

B

Semiconductor Group 24

Page 26

SAB 80C515A/83C515A-5

A/D Converter

In the SAB 80C515A a new high performance / high-speed 8-channel 10-bit A/D-Converter

(ADC) is implemented. Its successive approximation technique provides 7

= 16 MHz). The conversion principle is upward compatible to the one used in the

(f

OSC

SAB 80C515. The main functional blocks are shown in figure 3.

The comparator is a fully differential comparator for a high power supply rejection ratio and very

low offset voltages. The capacitor network is binary weighted providing genuine10-bit

resolution.

µs conversion time

The table below shows the sample time T

on f

f

OSC

and a new prescaler.

OSC

[MHz] Prescaler f

and the conversion time T C, which are dependend

S

[MHz] Sample Time

ADC

Conversion Time

(incl. sample time)

T

S

[µs]

T

[µs]

C

12 ÷ 8 1.5 2.67 9.3

÷ 16 0.75 5.33 18.66

16 ÷ 8 2.0 2.0 7.0

÷ 16 1.0 1.0 14.0

18 ÷ 8 – – –

÷ 16 1.125 3.55 12.4

The ADC is clocked (f

ADC

) with f

/8. Because of the ADC's maximum clock frequency of

OSC

2 MHz the prescaler (divide-by-2) has to be enabled (set Bit ADCL in SFR ADCON 1) when the

oscillator frequency (f

) is higher than 16 MHz.

OSC

Semiconductor Group 25

Page 27

SAB 80C515A/83C515A-5

Figure 3

Block Diagram A/D Converter

Semiconductor Group 26

Page 28

SAB 80C515A/83C515A-5

Timers /Counters

The SAB 80C515A contains three 16-bit timers/counters wich are useful in many applications

for timing and counting. the input clock for wach timer/counter is 1/12 of the oscillator frequency

in the timer operation or can be taken from an external clock source for the counter operation

(maximum count rate is 1/24 of the oscillator frequency).

– Timer/Counter 0 and 1

These timers/counters can operate in four modes:

Mode 0: 8-bit timer/counter with 32:1 prescaler

Mode 1: 16-bit timer/counter

Mode 2: 8-bit timer/counter with 8-bit auto-reload

Mode 3: Timer/counter 0 is configured as one 8-bit timer/counter and one

8-bit timer; Timer/counter 1 in this mode holds its count.

External inputs INTO

and 1 to facilitate pulse width measurements.

– Timer/Counter 2

Timer/counter 2 of the SAB 80C515A is a 16-bit timer/counter with several additional features.

It offers a 2:1 prescaler, a selectable gate function, and compare, capture and reload functions.

Corresponding to the 16-bit timer register there are four 16-bit capture/compare registers, one

of them can be used to perform a 16-bit reload on a timer overflow or external event. Each of

these registers corresponds to a pin of port 1 for capture input/compare output.

Figure 4 shows a block diagram of timer/counter 2.

Reload

A 16-bit reload can be performed with the 16-bit CRC register consisting of CRCL and CRCH.

There are two modes from which to select:

Mode 0: Reload is caused by a timer 2 overflow (auto-reload).

Mode 1: Reload is caused in response to a negative transition at pin T2EX

(P1.5), which can also request an interrupt.

and INT1 can be programmed to function as a gate for timer/counters 0

Semiconductor Group 27

Page 29

SAB 80C515A/83C515A-5

Capture

This feature permits saving of the actual timer/counter contents into a selected register upon

an external event or a software write operation. Two modes are provided to latch the current

16-bit value of timer 2 registers TL2 and TH2 into a dedicated capture register.

Mode 0: Capture is performed in response to a transition at the corresponding

port 1 pins CC0 to CC3.

Mode 1: Write operation into the low-order byte of the dedicated capture

register causes the timer 2 contents to be latched into this register.

Compare

In compare mode, the 16-bit values stored in the dedicated compare registers are compared

to the contents of the timer 2 registers. If the count value in the timer 2 registers matches one

of the stored values, an appropriate output signal is generated and an interrupt is requested.

Two compare modes are provided:

Mode 0: Upon a match the output signal changes from low to high. It goes

back to low level when timer 2 overflows.

Mode 1: The transition of the output signal can be determined by software.

A timer 2 overflow causes no output change.

Semiconductor Group 28

Page 30

SAB 80C515A/83C515A-5

Figure 4

Block Diagram of Timer/Counter 2

Semiconductor Group 29

Page 31

SAB 80C515A/83C515A-5

Interrupt Structure

The SAB 80C515A has 12 interrupt vectors with the following vector addresses and request

flags.

Table 4

Interrupt Sources and Vectors

Source (Request Flags) Vector Address Vector

IE0

TF0

IE1

TF1

RI + TI

TF2 + EXF2

IADC

IEX2

IEX3

IEX4

IEX5

IEX6

0003

000B

0013

001B

0023

002B

0043

004B

0053

005B

0063

006B

H

H

H

H

H

H

H

H

H

H

H

H

External interrupt 0

Timer 0 interrupt

External interrupt 1

Timer 1 interrupt

Serial port interrupt

Timer 2 interrupt

A/D converter interrupt

External interrupt 2

External interrupt 3

External interrupt 4

External interrupt 5

External interrupt 6

Each interrupt vector can be individually enabled/disabled. The minimum response time to an

interrupt request is more than 3 machine cycles and less than 9 machine cycles, if no other

interrrupt of the same or a higher priority level is in process.

Figure 5 shows the interrupt request sources.

External interrupts 0 and 1 can be activated by a low-level or a negative transition (selectable)

at their corresponding input pin, external interrupts 2 and 3 can be programmed for triggering

on a negative or a positive transition. The external interrupts 3 or 6 are combined with the

corresponding alternate functions compare (output) and capture (input) on port 1.

For programming of the priority levels the interrupt vectors are combined to pairs. Each pair can

be programmed individually to one of four priority levels by setting or clearing one bit in special

function register IP0 and one in IP1.

Figure 6 shows the priority level structure.

Semiconductor Group 30

Page 32

SAB 80C515A/83C515A-5

Figure 5

Interrupt Request Sources

Semiconductor Group 31

Page 33

SAB 80C515A/83C515A-5

Figure 6

Interrupt Priority Level Structure

Semiconductor Group 32

Page 34

SAB 80C515A/83C515A-5

I/O Ports

The SAB 80C515A has six 8-bit I/O ports and one input port. Port 0 is an open-drain

bidirectional I/O port, while ports 1 to 5 are quasi-bidirectional I/O ports with internal pull-up

resistors. That means, when configured as inputs, ports 1 to 5 will be pulled high and will source

current when externally pulled low. Port 0 will float when configured as input.

Port 0 and port 2 can be used to expand the program and data memory externally. During an

access to external memory, port 0 emits the low-order address byte and reads/writes the data

byte, while port 2 emits the high-order address byte. In this function, port 0 is not an open-drain

port, but uses a strong internal pull-up FET. Ports 1, 3 and 4 are provided for several alternate

functions, as listed below:

Port Symbol Function

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

P3.0

/CC0

INT3

INT4/CC1

INT5/CC2

INT6/CC3

INT2

T2EX

CLKOUT

T2

RxD

External interrupt 3 input, compare 0 output, capture 0 input

External interrupt 4 input, compare 1 output, capture 1 input

External interrupt 5 input, compare 2 output, capture 2 input

External interrupt 6 input, compare 3 output, capture 3 input

External interrupt 2 input

Timer 2 external reload trigger input

System clock output

Timer 2 external count or gate input

Serial port’s receiver data input (asynchronous) or

data input /output (synchronous)

P3.1

TxD

Serial port’s transmitter data output (asynchronous) or

clock output (synchronous)

P3.2

P3.3

P3.4

P3.5

P3.6

P3.7

P4.0

INT0

INT1

T0

T1

WR

RD

ADST

External interrupt 0 input, timer 0 gate control

External interrupt 1 input, timer 1 gate control

Timer 0 external counter input

Timer 1 external counter input

External data memory write strobe

External data memory read strobe

A/D Converter, external start of conversion

The SAB 80C515A has one dual-purpose input port. The ANx lines of port 6 in the SAB 80C515

can individually be used as analog or digital inputs. Reading the special function register P6

allows the user to input the digital values currently applied to the port pins. It is not necessary

to select these modes by software; the voltages applied at port 6 pins can be converted to

digital values using the A/D converter and at the same time the pins can be read via SFR P6.

It must be noted, however, that the results in port P6 bits will be indeterminate if the levels at

the corresponding pins are not within their V

to use port P6 as an output port. Special function register P6 is located at address 0DB

specifications. Furthermore, it is not possible

IL/VIH

.

H

In Hardware Power Down Mode the port pins and several control lines enter a floating state.

For more details see the section about Hardware Power Down Mode.

Semiconductor Group 33

Page 35

SAB 80C515A/83C515A-5

Power Saving Modes

The SAB 80C515A provides – due to Siemens ACMOS technology – four modes in which

power consumption can be significantly reduced.

– The Slow Down Mode

The controller keeps up the full operating functionality, but is driven with one eight of its

normal operating frequency. Slowing down the frequency remarkable reduces power

consumption.

– The Idle Mode

The CPU is gated off from the oscillator, but all peripherals are still supplied with the clock

and continue working.

– The Software Power Down Mode

Operation of the SAB 80C515A is stopped, the on-chip oscillator and the RC-oscillator are

turned off. This mode is used to save the contents of the internal RAM with a very low

standby current and is fully compatible to the Power Down Mode of the SAB 80C515.

– The Hardware Power Down Mode

Operation of the SAB 80C515A is stopped, the on-chip oscillator and the RC-oscillator are

turned off. The pin HWPD

floating state. The Hardware Power Down Mode is new in the SAB 80C515A and is

independent of the state of pin PE

reduction modes).

Hardware Enable for Software controlled Power Saving Modes

A dedicated pin PE

saving modes. Since this pin is mostly used in noise-critical application it is combined with an

automatic start of the Watchdog Timer.

/SWD = VIH (logic high level): Using of the power saving modes is not possible. The

PE

/SWD = VIL (logic low level): All power saving moes can be activated by software. The

PE

When left unconnected, pin PE

provide system protection on default.

/SWD of the SAB 80C515A allows to block the Software controlled power

controls this mode. Port pins and several control lines enter a

/SWD (which enables only the software initiated power

watchdog timer starts immediately after reset. The

instruction sequences used for entering of power saving

modes will not affect the normal operation of the device.

watchdog timer can be started by software at any time.

/SWD is pulled high by a weak internall pull-up. This is done to

The logic-level applied to pin PE/SWD can be changed during program execution to allow or to

block the use of the power saving modes without any effect on the on-chip watchdog circuitry.

Semiconductor Group 34

Page 36

Requirements for Hardware Power Down Mode

SAB 80C515A/83C515A-5

There is no dedicated pin to enable the Hardware Power Down Mode. The control pin PE

/SWD

has no control function in this mode. It enables and disables only the use of software controlled

power saving modes.

Software Controlled Power Saving Modes

All of these modes are entered by software. Special function register PCON (power control

register, address is 87

) is used to select one of these modes.

H

Slow Down Mode

During slow down operation all signal frequencies that are derived from the oscillator clock, are

divided by eight, also the clockout signal and and the watchdog timer count.

The slow down mode is enabled by setting bit SD. The controller actually enters the slow down

mode after a short synchronisation period (max. 2 machine cycles).

The slow down mode is disabled by clearing bit SD.

Idle Mode

During idle mode all peripherals of the SAB 80C515A (except for the watchdog timer) are still

supplied by the oscillator clock. Thus the user has to take care which peripheral should

continue to run and which has to be stopped during Idle.

The procedure to enter the Idle mode is similar to the one entering the power down mode. The

two bits IDLE and IDLS must be set by two consecutive instructions to minimize the chance of

unintentional activating of the idle mode.

There are two ways to terminate the idle mode:

– The idle mode can be terminated by activating any enabled interrupt. This interrupt will be

serviced and the instruction to be executed following the RETI instruction will be the one

following the instruction that set the bit IDLS.

– The other way to terminate the idle mode, is a hardware reset. Since the oscillator is still

running, the hardware reset must be held active only for two machine cycles for a complete

reset.

Normally the port pins hold the logical state they had at the time idle mode was activated. If

some pins are programmed to serve their alternate functions they still continue to output during

idle mode if the assigned function is on. The control signals ALE and PSEN

hold at logic high

levels (see table 5).

Semiconductor Group 35

Page 37

SAB 80C515A/83C515A-5

Software Power Down Mode

The power down mode is entered by two consecutive instructions directly following each other.

The first instruction has to set the flag PDE (power down enable) and must not set PDS (power

down set). The following instruction has to set the start bit PDS. Bits PDE and PDS will

automatically be cleared after having been set.

The instruction that sets bit PDS is the last instruction executed before going into power down

mode. The only exit from power down mode is a hardware reset.

The status of all output lines of the controller can be looked up in table 5.

Hardware Controlled Power Down Mode

The pin HWPD

normal operating modes. If pin HWPD

Power Down Mode; this is independent of the state of pin PE

HWPD

is sampled once per machine cycle. If it is found active, the device starts a complete

controls this mode. If it is on logic high level (inactive) the part is running in the

gets active (low level) the part enters the Hardware

/SWD.

internal reset sequence. The watchdog timer is stopped and its status flag WDTS is cleared

exactly the same effects as a hardware reset. In this phase the power consumption is not yet

reduced. After completion of the internal reset both oscillators of the chip are disabled. At the

same time the port pins and several control lines enter a floating state as shown in table 5. In

this state the power consumption is reduced to the power down current IPD. Also the supply

voltage can be reduced. Table 5 also lists the voltages which may be applied at the pins during

Hardware Power Down Mode without affecting the low power consumption.

Termination of HWPD Mode:

This power down state is maintained while pin HWPD

is held active. If HWPD goes to high level

(inactive state) an automatic start up procedure is performed:

– First the pins leave their floating condition and enter their default reset state (as they had

immediately before going to float state).

– Both oscillators are enabled. The oscillator watchdog’s RC oscillator starts up very fast (typ.

less than 2 ms).

– Because the oscillator watchdog is active it detects a failure condition if the on-chip oscillator

hasn’t yet started. Hence, the watchdog keeps the part in reset and supplies the internal

clock from the RC oscillator.

– Finally, when the on-chip oscillator has started, the oscillator watchdog releases the part

from reset with oscillator watchdog status flag set.

When automatic start of the watchdog was enabled (PE

/SWD connected to V

CC

), the

Watchdog Timer will start, too (with its default reload value for time-out period).

– The Reset

pin overrides the Hardware Power Down function, i.e. if reset gets active during

Hardware Power Down it is terminated and the device performs the normal

resetfunction.(Thus, pin Reset

function.(Thus, pin Reset

has to be inactive during Hardware Power Down Mode).

has to be inactive during Hardware Power Down Mode).

Semiconductor Group 36

Page 38

SAB 80C515A/83C515A-5

Table 5

Status of all pins during Idle Mode, Power Down Mode and Hardware Power

Down Mode

Pins Idle Mode

Last instruction

executed from

internal

ROM

external

ROM

Power Down Mode

Last instruction

executed from

internal

external

ROM

P0 Data float Data float

P1 Data

alt outputs

Dat

alt outputsa

Data

last outputs

Data

last outputs

P2 Data Address Data Data

P3 Data

alt outputs

P4 Data

alt outputs

P5 Data

alt output

P6

1) 1) 1) 1)

Data

alt outputs

Data

alt outputs

Data

alt output

Data

last output

Data

last outputs

Data

last output

Data

last output

Data

last output

Data

last output

ROM

1)

Hardware Power

Down

Status

floating

1)

outputs

disabled

input

function

EA

active input

2)

PE/SWD active input pull-up

disabled

2)

XTAL1 active output

XTAL2 disabled input

function

1)

PSEN high high low low floating output

ALE high high low low

V

AREF

V

AGND

active supply pins

RESET active input must

be high

1)

Applied voltage range at pin VSS ≤VIN ≤ V

2)

VIN = VSS or VIN = V

3)

VSS ≤ VIN ≤ VCC; V

CC

AREF

≥ V

AGND

CC

3)

Semiconductor Group 37

Page 39

SAB 80C515A/83C515A-5

Serial Interface

The SAB 80C515A has a full duplex and receive buffered serial interface. It is functionally

identical with the serial interface of the SAB 8051.

Table 6 shows possible configurations and the according baud rates.

Table 6

Baud Rate Generation

Mode Mode 0

8-Bit

synchronous

channel

8-Bit

UART

9-Bit

UART

Baudrate

f

O SC

f

OSC

f

OSC

=12 MHz

=16 MHz

=18 MHz

derived from f

1 MHz

1.33 MHz

1.5 MHz

OSC

Mode Mode 1

Baudrate

f

OSC

f

OSC

f

OSC

=12 MHz

=16 MHz

=18 MHz

1 Baud – 62.5 kBaud

1 Baud – 83 kBaud

1 Baud – 93.7 kBaud

183 Baud – 375 kBaud

244 Baud – 500 kBaud

Baud – 562.5 kBaud

2375

derived from Timer 1 10-Bit Baudrate

Generator

Mode Mode 2 Mode 3

Baudrate

f

OSC =

f

OSC

12 MHz

=16 MHz

187.5 kBaud/

375 kBaud

250 Baud/

500 kBaud

1 Baud –

62.5 kBaud

1 Baud –

83.3 kBaud

183 Baud –75 kBaud

244 Baud – 500 kBaud

f

=18 MHz

OSC

281.2 kBaud/

562.5 kBaud

derived from f

2 Timer 1 10-Bit

OSC/

Semiconductor Group 38

1 Baud –

93.7 kBaud

275 Baud – 562.5 kBaud

Baudrate

Generator

Page 40

The Serial Interface can operate in 4 modes:

Mode 0: Shift register mode:

Serial data enters and exits through R × D. T × D outputs the shift clock 8 data bits

are transmitted/received (LSB first). The baud rate is fixed at 1/12 of the oscillator frequency.

Mode 1: 8-bit UART, variable baud rate:

10-bit are transmitted (through T × D) or received (through R × D): a start bit (0), 8

data bits (LSB first), and a stop bit (1). On reception, the stop bit goes into RB80 in

special function register SCON. The baud rate is variable.

Mode 2: 9-bit UART, fixed baud rate:

11-bit are transmitted (through T × D) or received (through R × D): a start bit (0), 8

data bits (LSB first), a programmable 9th, and a stop bit (1). On transmission, the 9th

data bit (TB80 in SCON) can be assigned to the value of 0 or 1. For example, the parity bit (P in the PSW) could be moved into TB80 or a second stop bit by setting TB80

to 1. On reception the 9th data bit goes into RB80 in special function register SCON,

while the stop bit is ignored. The baud rate is programmable to either 1/32 or 1/64 of

the oscillator frequency.

SAB 80C515A/83C515A-5

Mode 3: 9-bit UART, variable baud rate:

11-bit are transmitted (through T × D) or received (through R × D): a start bit (0), 8

data bits (LSB first), a programmable 9th, and a stop bit (1). In fact, mode 3 is the

same as mode 2 in all respects except the baud rate. The baud rate in mode 3 is variable.

Variable Baud Rates for Serial Interface

Variable baud rates for modes 1 and 3 of serial interface can be derived from either timer 1 or

a new dedicated Baudrate Generator.

The baud rate is generated by a free running 10-bit timer with programmable reload register.

SMOD

Mode 1.3 baud rate =

2

* f

OSC

64 * (210 - SREL)

The default value after reset in the reload registers SRELL and SRELH provides a baud rate of

4.8 kBaud (SMOD = 0) or 9.6 kBaud (SMOD = 1) at 12 MHz oscillator frequency. This guarantees full compatibility to the SAB 80C515.

Semiconductor Group 39

Page 41

SAB 80C515A/83C515A-5

Fail Safe Units

The SAB 80C515A offers enhanced fail safe mechanisms, which allow an automatic recovery

from software upset or hardware failure:

– a programmable watchdog timer (WDT), with variable time-out period from 512 µs up to

appr. 1.1 s @12 MHz. Upward compatible to SAB 80C515 watchdog timer.

– an oscillator watchdog (OWD) which monitors the on-chip oscillator and forces the

microcontroller into reset state, in case the on-chip oscillator fails; it also controls the restart

from the Hardware Power Down Mode and provides the clock for a fast internal reset after

power-on.

Programmable Watchdog Timer

The WDT can be activated by hardware or software.

Hardware initialization is done when pin PE

SAB 80C515A then starts program execution with the WDT running. Since pin PE

sampled during Reset, the WDT cannot be started externally during normal operation.

Software initialization is done by setting bit SWDT in SFR IEN1.

A refresh of the watchdog timer is done by setting bits WDT (SFR IEN0) and SWDT

consecutively. This double instruction sequence has been implemented to increase system

security.

When a watchdog timer reset occurs, the watchdog timer keeps on running, but a status flag

WDTS (SFR IP0) is set. This flag can also be cleared by software.

Figure 7 shows the block diagram of the programmable Watchdog Timer.

Oscillator Watchdog

The unit serves three functions:

– Monitoring of the on-chip oscillator’s function.

The watchdog monitors the on-chip oscillator’s frequency; if it is lower than the frequency of

the auxiliary RC oscillator in the watchdog unit, the internal clock is supplied by the RC

oscillator and the device is forced into reset; if the failure condition disappears (i.e. the onchip oscillator has again a higher frequency than the RC oscillator), the part executes a final

reset phase of appr. 0.25 ms in order to allow the oscillator to stabilize; then the oscillator

watchdog reset is released and the part starts program execution again.

/SWD (Pin 4) is held high during RESET. The

/SWD is only

– Restart from the Hardware Power Down Mode.

If the Hardware Power Down Mode is terminated the oscillator watchdog has to control the

correct start-up of the on-chip oscillator and to restart the program. The oscillator watchdog

function is only part of the complete Hardware Power Down sequence; however, the

watchdog works identically to the monitoring function.

– Fast internal reset after power-on.

In this function the oscillator watchdog unit provides a clock supply for the reset before the

on-chip oscillator has started. In this case the oscillator watchdog unit also works identically

to the monitoring function.

Semiconductor Group 40

Page 42

SAB 80C515A/83C515A-5

Figure 8 shows the block diagram of the oscillator watchdog unit. It consists of an internal RC

oscillator which provides the reference frequency for the frequency comparator.

Figure 7

Block Diagram of the Programmable Watchdog Timer

Figure 8

Functional Block Diagram of the Oscillator Watchdog

Semiconductor Group 41

Page 43

SAB 80C515A/83C515A-5

Fast internal reset after power-on

The SAB 80C515A can use the oscillator watchdog unit for a fast internal reset procedure after

power-on.

Normally members of the 8051 family (like the SAB 80C515) enter their default reset state not

before the on-chip oscillator starts. The reason is that the external reset signal must be

internally synchronized and processed in order to bring the device into the correct reset state.

Especially if a crystal is used the start up time of the oscillator is relatively long (typ. 1 ms).

During this time period the pins have an undefined state which could have severe effects e.g.

to actuators connected to port pins.

In the SAB 80C515A the oscillator watchdog unit avoids this situation. After power-on the

oscillator watchdog’s RC oscillator starts working within a very short start-up time (typ. less than

2 ms). In the following the watchdog circuitry detects a failure condition for the on-chip oscillator

because this has not yet started (a failure is always recognized if the watchdog’s RC oscillator

runs faster than the on-chip oscillator). As long as this condition is valid the watchdog uses the

RC oscillator output as clock source for the chip rather than the on-chip oscillator’s output. This

allows correct resetting of the part and brings also all ports to the defined state.

Delay time between power-on and correct reset state:

Typ.: 18

Max.: 34

µs

µs

Instruction Set

The SAB 80C515A / 83C515A-5 has the same instruction set as the industry standard 8051

microcontroller.

A pocket guide is available which contains the complete instruction set in functional and

hexadecimal order. Furtheron it provides helpful information about Special Function Registers,

Interrupt Vectors and Assembler Directives.

Literature Information

Title Ordering No.

Microcontroller Family SAB 8051 Pocket Guide B158-H6497-X-X-7600

Semiconductor Group 42

Page 44

SAB 80C515A/83C515A-5

Absolute Maximum Ratings

Ambient temperature under bias – 40 to 85 ˚C

Storage temperature – 65 to 150 ˚C

Voltage on V

pins with respect to ground (V

CC

Voltage on any pin with respect to ground (V

Input current on any pin during overload condition – 10mA to + 10 mA

Absolute sum of all input currents during overload condition |100 mA|

Power dissipation 1 W

Note Stresses above those listed under "Absolute Maximum Ratings" may cause permanent

damage of the device. This is a stress rating only and functional operation of the device

at these or any other conditions above those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating conditions for longer

periods may affect device reliability. During overload conditions (V

theVoltage on V

pins with respect to ground (VSS) must not exeed the values defind-

CC

ed by the absolute maximum ratings.

) – 0.5 V to 6.5 V

SS

) – 0.5 to V

SS

>

V

CC

or

IN

V

CC

IN

+ 0.5 V

<

V

SS

)

DC Characteristics

= 5 V + 10 %, – 15 %; VSS = 0 V

V

CC

T

= 0 to 70 ˚C for the SAB 80C515A

A

T

= – 40 to 85 ˚C for the SAB 80C515A-T3

A

Parameter Symbol Limit V alues Unit Test condition

min. max.

Input low voltage

(exept EA

,RESET, HWPD)

Input low voltage EA

V

IL

– 0.5 0.2 V

CC

– 0.1

V

I L1

– 0.5 0.2 V

CC

V–

V–

– 0.3

Input low voltage

(HWPD, RESET)

Input high voltage (exept

RESET, XTAL2 and HWPD)

Input high voltage to XTAL2 V

V

I L2

– 0.5 0.2 V

CC

V–

+ 0.1

V

IH

0.2 V

CC

V

+ 0.5 V –

CC

+ 0.9

IH1

0.7 V

CC

V

+ 0.5 V –

CC

Input high voltage to RESET

V

IH2

0.6 V

and HWPD

Semiconductor Group 43

CC

V

+ 0.5 V –

CC

Page 45

SAB 80C515A/83C515A-5

DC Characteristics (cont’d)

Parameter Symbol Limit V alues Unit Test condition

min. max.

Output low voltage

(ports 1, 2, 3, 4, 5)

Output low voltage

(ports 0, ALE, RESET

)

Output high voltage,

(ports1, 2, 3, 4, 5)

Output high voltage

(port 0 in external bus mode,ALE, PSEN

)

Logic 0 input current

(ports 1, 2, 3, 4, 5)

Logical 1-to-0 transition

current, ports 1, 2, 3, 4, 5

Input leakage current

(port 0, EA

, P6, HWPD)

– 0.45 V I

V

OL

V

V

V

I

I

I

OL1

OH

OH1

IL

TL

L I

–

2.4

0.9 V

2.4

V

0.9

0.45 V I

–

–

C C

–

–

C C

– 10 – 70 µA V

– 65 – 650 µA V

–

–

± 100