Page 1

INTEGRATED CIRCUITS

DATA SH EET

SAA7712H

Sound effects DSP

Preliminary specification

File under Integrated Circuits, IC02

1999 Aug 05

Page 2

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

CONTENTS

1 FEATURES

1.1 Hardware features

1.2 Software features

2 APPLICATIONS

3 GENERAL DESCRIPTION

4 QUICK REFERENCE DATA

5 ORDERING INFORMATION

6 BLOCK DIAGRAM

7 PINNING INFORMATION

8 FUNCTIONAL DESCRIPTION

8.1 Analog outputs

8.1.1 Analog output circuit

8.1.2 DAC frequency

8.1.3 DACs

8.1.4 Upsample filter

8.1.5 Performance

8.1.6 Power-On Mute (POM)

8.1.7 Power-off plop suppression

8.1.8 Pin VREFDA

8.1.9 Internal DAC current reference

8.1.10 Supply of the analog outputs

8.2 I2S-bus inputs and outputs

8.2.1 Digital data stream formats

8.2.2 Slave I2S-bus inputs

8.2.3 Master I2S-bus inputs and outputs

8.3 Equalizer accelerator

8.3.1 Introduction

8.3.2 Configuration of equalizer sections

8.3.3 Overflow detection

8.4 Clock circuit and oscillator

8.4.1 General description

8.4.2 Supply of the crystal oscillator

8.5 Programmable phase-locked loop circuit

8.6 I2C-bus control

8.6.1 Introduction

8.6.2 Characteristics of the I2C-bus

8.6.3 Bit transfer

8.6.4 Start and stop conditions

8.6.5 Data transfer

8.6.6 Acknowledge

8.6.7 State of the I2C-bus interface during and after

Power-on reset

8.7 External control pins

8.8 Reset pin

8.9 Power supply connection and EMC

8.10 Test mode connections

9I

9.1 Addressing

9.2 Slave address (pin A0)

9.3 Write cycles

9.4 Read cycles

9.5 I2C-bus memory map summary

9.6 I2C-bus memory map details

10 LIMITING VALUES

11 THERMAL CHARACTERISTICS

12 DC CHARACTERISTICS

13 ANALOG OUTPUTS CHARACTERISTICS

14 OSCILLATOR CHARACTERISTICS

15 I2S-BUS TIMING CHARACTERISTICS

16 I2C-BUS TIMING CHARACTERISTICS

17 APPLICATION INFORMATION

18 PACKAGE OUTLINE

19 SOLDERING

19.1 Introduction to soldering surface mount

19.2 Reflow soldering

19.3 Wave soldering

19.4 Manual soldering

19.5 Suitability of surface mount IC packages for

20 DEFINITIONS

21 LIFE SUPPORT APPLICATIONS

22 PURCHASE OF PHILIPS I2C COMPONENTS

2

C-BUS FORMAT

packages

wave and reflow soldering methods

1999 Aug 05 2

Page 3

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

1 FEATURES

1.1 Hardware features

• Digital Signal Processor (DSP) core:

– 18 bits data width, 12 bits coefficient width

– SeparateX, Y and P memories(both384 bytesword

XRAM and YRAM, 3 kbytes word PROM)

– 1 kbytes delay line memory suited for Dolby Pro

Logic Surround.

• Inputs:

– 2 slave 18-bit digital stereo inputs: I2S-bus and

LSB-justified serial formats

– 2 master 18-bit digital stereo inputs: I2S-bus and

LSB-justified serial formats.

• Outputs:

– 4 DACs with 4-times oversampling and noise

shaping, fed to 4 output pins and configurable from

the DSP program, as left, right, front and surround

channels of a Dolby Pro Logic Surround system

– 2 master 18-bit digital stereo outputs: I2S-bus and

LSB-justified serial formats.

• 4-channel 5-band or 2-channel 10-band

I2C-bus controlled parametric equalizer

• I2C-bus microcontroller interface for:

– Access to full X and Y memory space

– Control of hardware settings: selectors,

programmable clock generations, etc.

• Controllable Phase-Locked Loop (PLL) to generate the

high frequency DSP clock from common fundamental

oscillator crystal

• 3.3 V process with 3.3 or 5 V digital periphery:

– 3.3 or 5 V I2S-bus and I2C-bus microcontroller

interfacing.

• Operating temperature range from 0 to 70 °C.

1.2 Software features

• Dolby Pro Logic Surround/Dolby 3 stereo:

Trademark of Dolby Laboratories Licensing Corporation

• Noise generation: A pink noise generator is included

for installation of the Dolby Pro Logic/Dolby 3 stereo

mode

• Hall/Matrix Surround: When no Dolby Pro Logic

Surround source material is available then this mode

can be used to produce a signal in the surround channel

• Incredible Surround (222-IS): This algorithm expands

the stereo width (stereo expander). This is intended to

be used when the 2 speakers are placed close together

(TV set and Midi set).

• Robust Incredible Surround (222-RIS): Same as

incredible surround only an alternative algorithm

• 3D Surround (422) or Incredible Virtual Surround:

Dolby Pro Logic Surround reproduced by 2 speakers

(L and R)

• IS-3D Surround (422-IS): Same as 3D Surround (422)

only with extra stereo width expander on left and right

• RIS-3D Surround (422-RIS): Same as IS-3D Surround

(422) with alternative algorithm

• 3D Surround (423) or Incredible Virtual Surround:

Dolby Pro Logic Surround reproduced by 3 speakers

(L, C and R)

• IS-3D Surround (423-IS): Same as 3D Surround (423)

only with extra stereo width expander on left and right

• RIS-3D Surround (423-RIS): Same as IS-3D Surround

(423-IS) with alternative algorithm

1999 Aug 05 3

Page 4

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

• Voice cancelling (karaoke): Rejects voice out of

source material, mainly intended to be used with

karaoke. Several karaoke modes available in stereo

modeandinDolbyProLogicmode,suchas(auto) voice

cancel, (auto) centre voice cancel, (auto) multi left and

(auto) multi right.

• Microphone mix modes (karaoke): Mono microphone

mixed to left, right and centre channel

• Spectrum analysis: 3-band spectrum analyser is

provided

• Dolby B: Both a Dolby B encoder as well as a Dolby B

decoder is implemented

• 2 Room solution: In all modes not requiring more than

2 output channels (stereo and karaoke incredible

surround) it is also possible to feed the source signal to

the other 2 output channels (with same processed or

not processed signal)

• Dynamic Bass Enhancement (DBE): Dynamic bass

enhancementgenerates a sub-woofer channel, which is

either a separate output or is added tothe front channels

• Volume processing: Independent volume processing

of all 4 output channels

• AC-3/MPEG-2: Inputs available intended to be used

with an AC-3/MPEG-2 co-processor. In this mode the

SAA7712H can be used as post-processor.

• Output redirection: Several output configurations are

possible (normal 4 channel, special 4 + 2 channel,

record 2 + 2 channel, 6 or 6 + 2 channel).

Dependingon the sample frequency several combinations

of the above mentioned features are possible.

3 GENERAL DESCRIPTION

The SAA7712H provides for digital signal processing

power in TV systems and home theatre systems.

A DSP core is equipped with digital inputs and outputs, a

5-band parametric equalizer accelerator, a digital

co-processor interface and a delay line memory. This

architecture accommodates on-chip standard sound

processing,incrediblesurround,DolbyProLogicSurround

and other surround sound processing algorithms.

The architecture also supports co-processing, e.g. to add

to the processing power of the internal DSP core or for

multi-channel surround decoding.

All settings and parameters are controlled by an I2C-bus

interface. The available interfaces support a high

application flexibility.

The DSP core communicates over 32 dedicated registers.

The selected digital input is master for the data rate of the

DSP core. This input can be selected among 2 slave

I2S-bus inputs. The 4 outputs from the core are passed

through 4 DACs and then routed to 4 output pins.

Two master I2S-bus outputs and two master I2S-bus

inputs can serve as an I2S-bus co-processor interface.

Eight of the remaining registers are used for

communication with the hardware equalizer, and eight for

communication with the delay line memory.

All I2S-bus inputs and outputs support the Philips I2S-bus

format as well as 16, 18 and 20-bit LSB-justified formats.

2 APPLICATIONS

The SAA7712H can be used in TV sets with:

• Dolby Pro Logic Surround, incredible surround,

3D Surround and advanced acoustics processing

• Multi-channelsound decoding (AC-3 and MPEG-2)on a

co-processor. The SAA7712H can be used for

post-processing.

1999 Aug 05 4

Page 5

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

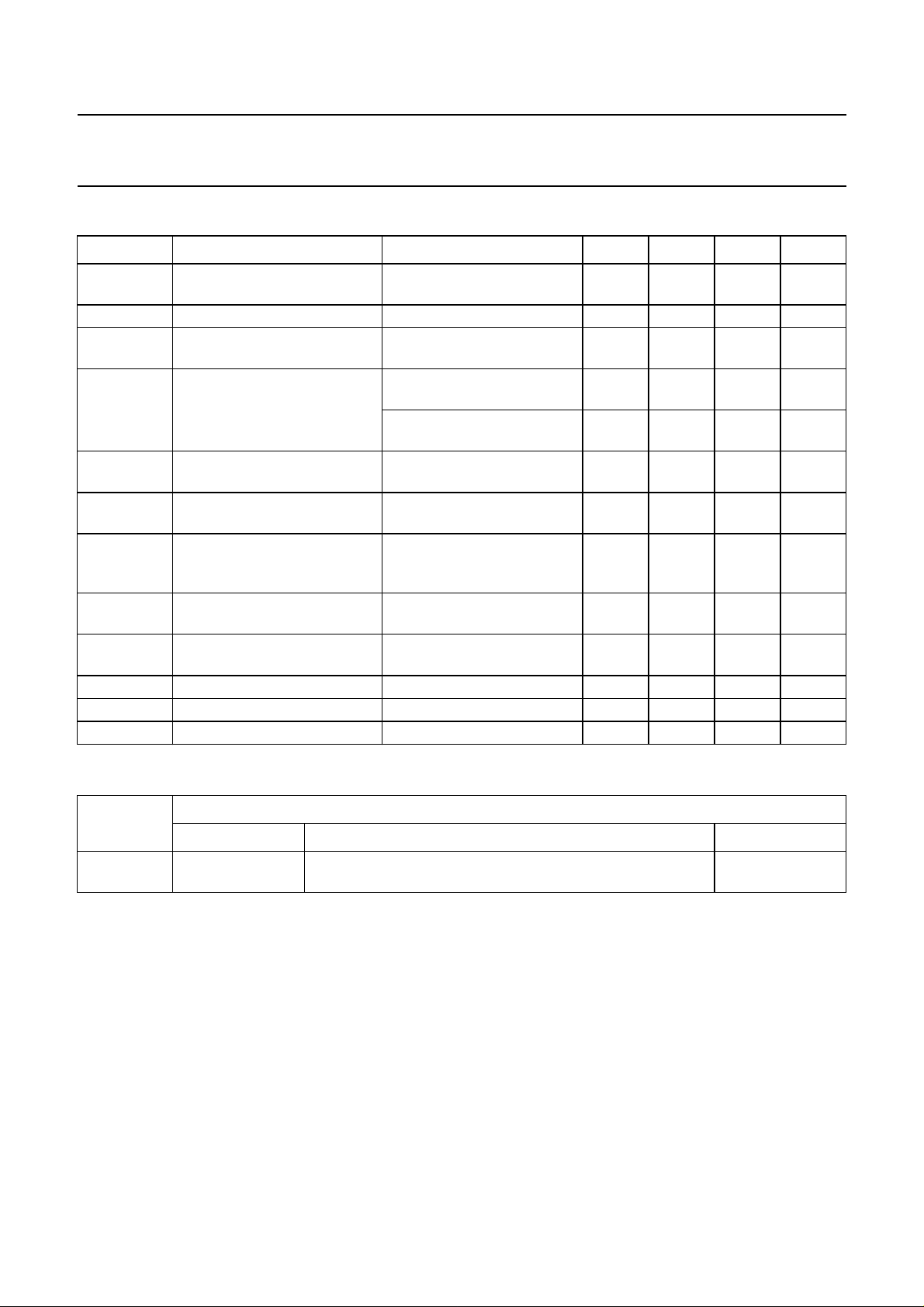

4 QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITION MIN. TYP. MAX. UNIT

V

DD3V

supply voltage 3.3 V analog

and digital

V

DD5V

I

DDD3V

supply voltage 5 V periphery with respect to V

DC supply current of the 3.3 V

digital core part

I

DDD5V

DC supply current of the 5 V

digital periphery part

I

DDA

DC supply current of the

analog part

P

tot

total power dissipation at f

(THD + N)/S DAC total harmonic

distortion-plus-noise to output

signal

DR

DS

f

xtal

f

DSP16

f

DSP18

DAC

DAC

DAC dynamic range f = 1 kHz; −60 dB;

DAC digital silence f = 20 Hz to 17 kHz;

crystal frequency 10.000 − 19.456 MHz

DSP clock frequency f

DSP clock frequency f

with respect to V

at f

; maximum activity

DSP18

SS

SS

3 3.3 3.6 V

3 3.3 or 5 5.5 V

−−80 mA

of the DSP

at f

of the DSP; V

at f

of the DSP; V

at zero input and output

; maximum activity

DSP18

DD5

; maximum activity

DSP18

DD5

−−5mA

=5V

−−5mA

= 3.3 V

−−10 mA

signal

; maximum activity

DSP18

−−0.4 W

of the DSP

R

>5kΩ; f = 1 kHz;

L

−−75 −60 dBA

A-weighted

90 96 − dBA

A-weighted

−−107 −102 dBA

A-weighted

= 16.384 MHz −−32.256 MHz

xtal

= 18.432 MHz −−32.544 MHz

xtal

5 ORDERING INFORMATION

TYPE

NUMBER

NAME DESCRIPTION VERSION

PACKAGE

SAA7712H QFP80 plastic quad flat package; 80 leads (lead length 1.95 mm);

body 14 × 20 × 2.7 mm; high stand-off height

1999 Aug 05 5

SOT318-1

Page 6

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

h

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

1999 Aug 05 6

andbook, full pagewidth

POMVREFDA

815

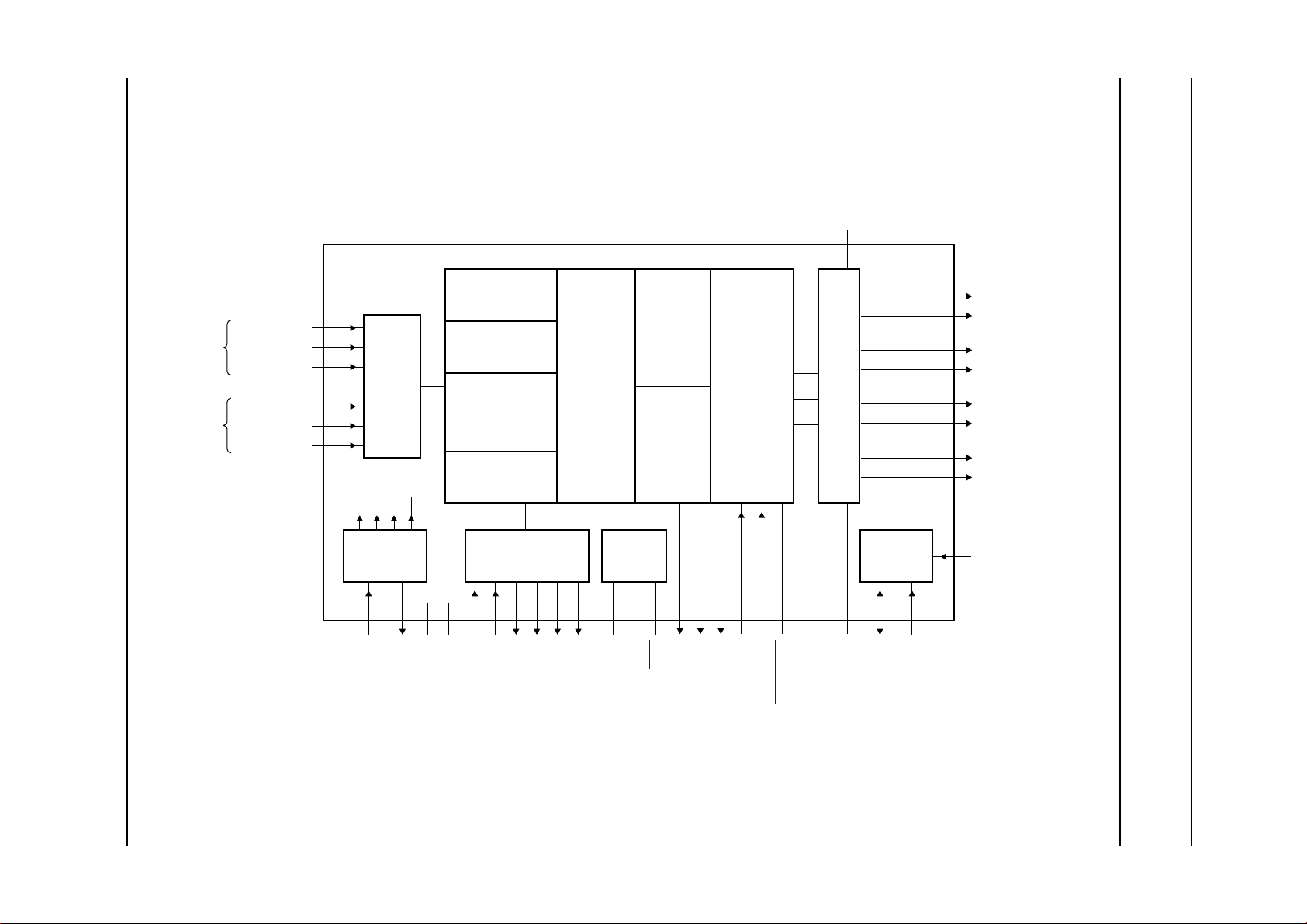

6 BLOCK DIAGRAM

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

from

audio

source 1

from

audio

source 2

2

I

S_IN1_WS

2

I

S_IN1_BCK

2

I

S_IN1_DATA

2

I

S_IN2_WS

2

I

S_IN2_BCK

2

I

S_IN2_DATA

SYS_CLK

SAA7712H

27

29

28

24

26

25

21

OSCILLATOR

AND PLL

I2S-BUS

INPUT

SWITCH

OSC_IN

DOLBY PRO LOGIC

DOLBY 3 STEREO

TEST2

TEST1

OSC_OUT

SURROUND

CHANNEL

DELAY

INCREDIBLE

SURROUND

(IS, RIS)

or

or

HALL/MATRIX

CENTRE

VOICE

CANCELLING

HOST I/O

S_IO_IN1

S_IO_IN2

2

2

S_IO_BCK

I

I

2

I

SURROUND

SURROUND

SURROUND

3630326362 33314847

S_IO_WS

2

I

S_IO_OUT1

2

I

3D

IS-3D

RIS-3D

TEST

37

TSCAN

S_IO_OUT2

2

I

2-CHANNEL

10-BAND

EQUALIZER

4-CHANNEL

5-BAND

EQUALIZER

5960 7776573938414020

58

RTCB

SHTCB

EQOV

DSP_OUT1

VOLUME

PROCESSING

DSP_IN1

DSP_IN2

DSP_OUT2

QUAD

DAC

VDACP1

DSP_RESET

I2C-BUS

INTERFACE

SDA SCL

VDACN1

4546

MGS206

18

OUT0_I

19

OUT0_V

17

OUT1_I

16

OUT1_V

11

OUT2_I

12

OUT2_V

10

OUT3_I

9

OUT3_V

44

A0

Fig.1 Block diagram.

Page 7

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

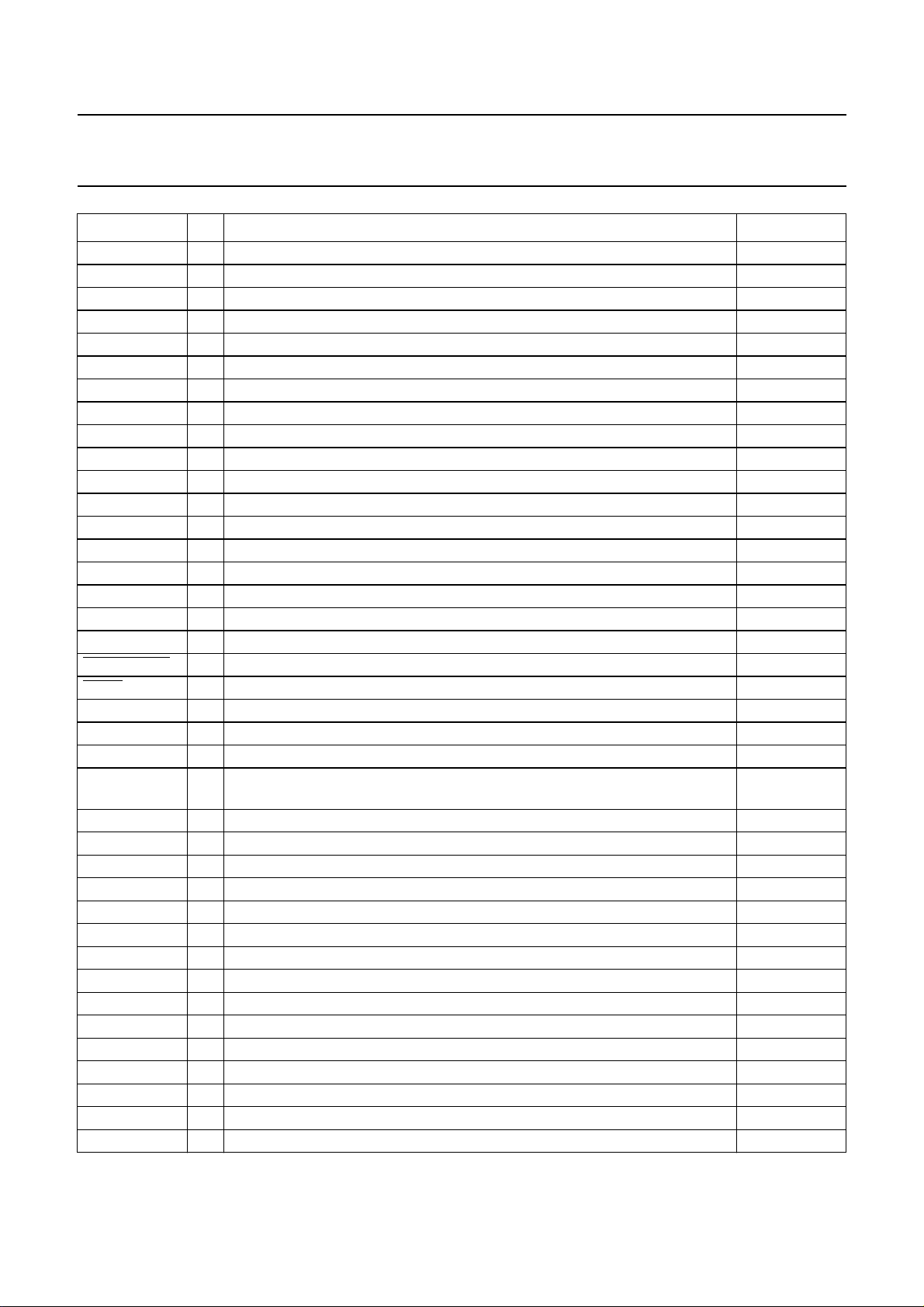

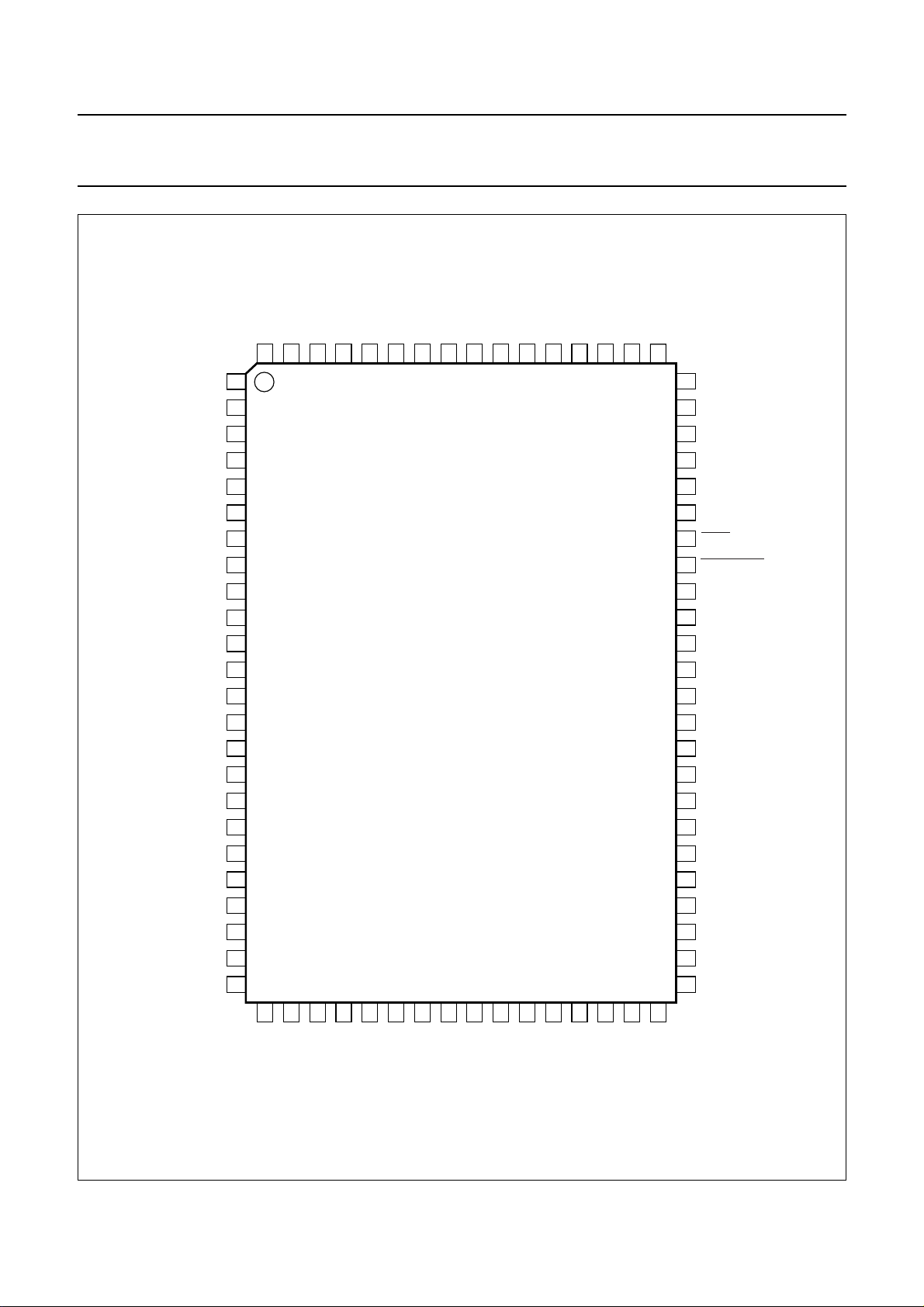

7 PINNING INFORMATION

SYMBOL PIN DESCRIPTION PIN TYPE

n.c. 1 not connected

n.c. 2 not connected

n.c. 3 not connected

n.c. 4 not connected

n.c. 5 not connected

n.c. 6 not connected

n.c. 7 not connected

POM 8 power-on mute; timing determined by external capacitor AP2D

OUT3_V 9 analog voltage output 3 AP2D

OUT3_I 10 analog current output 3 AP2D

OUT2_I 11 analog current output 2 AP2D

OUT2_V 12 analog voltage output 2 AP2D

V

SSA2

V

DDA2

VREFDA 15 voltage reference of the analog part AP2D

OUT1_V 16 analog voltage output 1 AP2D

OUT1_I 17 analog current output 1 AP2D

OUT0_I 18 analog current output 0 AP2D

OUT0_V 19 analog voltage output 0 AP2D

EQOV 20 equalizer overflow line output B4CR

SYS_CLK 21 test pin output BT4CR

V

DDD5V1

V

SSD5V1

2

I

S_IN2_WS 24 I2S-bus or LSB-justified format word select input from a digital audio source 2 IBUFD

2

S_IN2_DATA 25 I2S-bus or LSB-justified format left-right data input from a digital audio

I

2

S_IN2_BCK 26 I2S-bus clock or LSB-justified format input from a digital audio source 2 IBUFD

I

2

I

S_IN1_WS 27 I2S-bus or LSB-justified format word select input from a digital audio source 1 IBUFD

2

S_IN1_DATA 28 I2S-bus or LSB-justified format left-right data input from a digital audio

I

2

I

S_IN1_BCK 29 I2S-bus clock or LSB-justified format input from a digital audio source 1 IBUFD

2

S_IO_BCK 30 I2S-bus bit clock output for interface with DSP co-processor chip BT4CR

I

2

I

S_IO_IN1 31 I2S-bus input data channel 1 from DSP co-processor chip IBUFD

2

I

S_IO_IN2 32 I2S-bus input data channel 2 from DSP co-processor chip IBUFD

2

I

S_IO_WS 33 I2S-bus word select output for interface with DSP co-processor chip BT4CR

V

DDD5V2

V

SSD5V2

2

S_IO_OUT1 36 I2S-bus output data channel 1 to DSP co-processor chip BT4CR

I

2

I

S_IO_OUT2 37 I2S-bus output data channel 2 to DSP co-processor chip BT4CR

DSP_IN1 38 digital input 1 of the DSP core (F0 of the status register) IBUFD

13 analog ground supply 2 APVSS

14 analog supply voltage2 (3 V) APVDD

22 digital supply voltage1; peripheral cells only (3 or 5 V) VDD5

23 digital ground supply 1; peripheral cells only (3 or 5 V) VSS5

IBUFD

source 2

IBUFD

source 1

34 digital supply voltage2; peripheral cells only (3 or 5 V) VDD5

35 digital ground supply 2; peripheral cells only (3 or 5 V) VSS5

1999 Aug 05 7

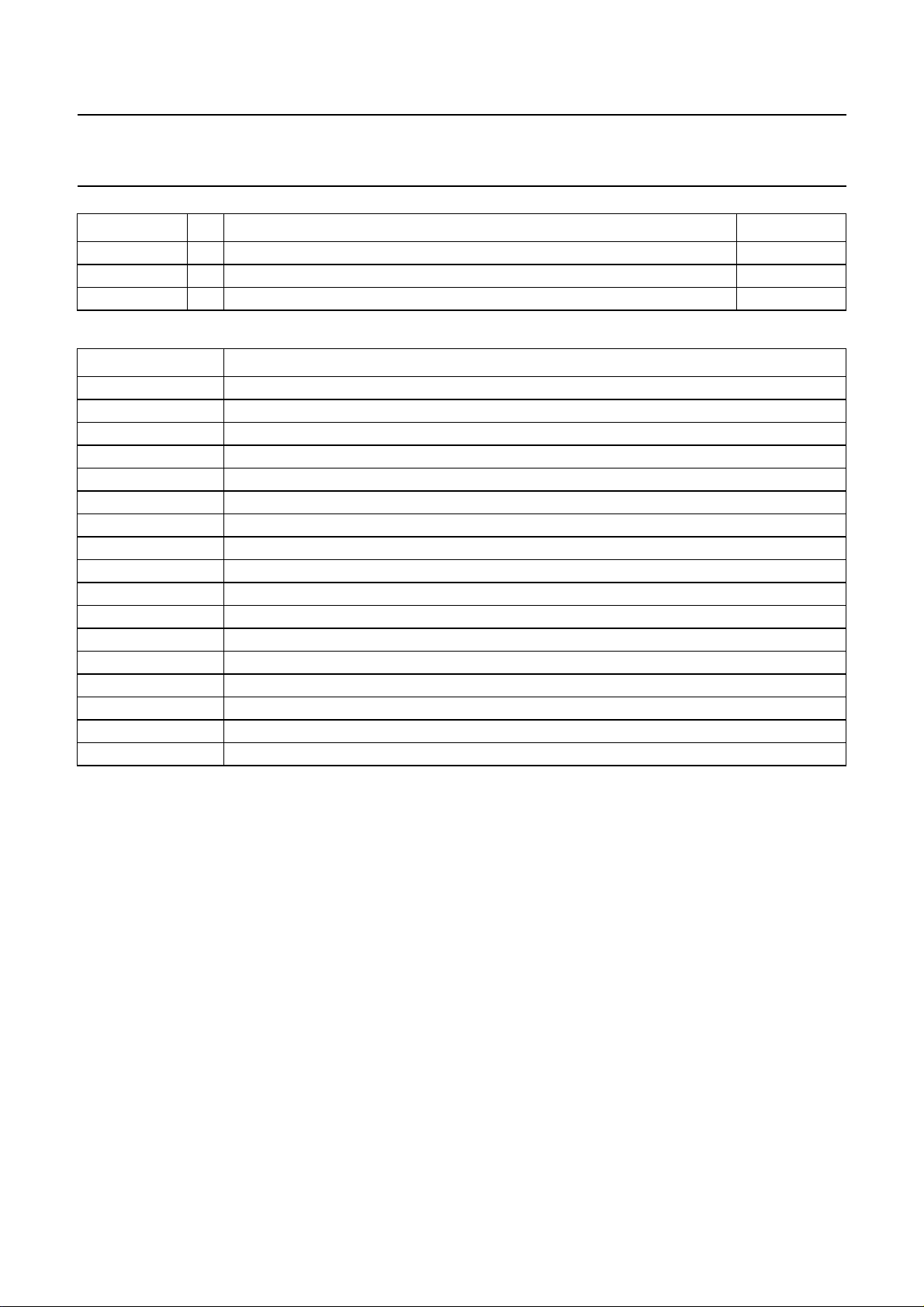

Page 8

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

SYMBOL PIN DESCRIPTION PIN TYPE

DSP_IN2 39 digital input 2 of the DSP-core (F1 of the status register) IBUFD

DSP_OUT1 40 digital output 1 of the DSP-core (F2 of the status register) B4CR

DSP_OUT2 41 digital output 2 of the DSP-core (F3 of the status register) B4CR

V

DDD5V3

V

SSD5V3

A0 44 I

SCL 45 I

SDA 46 I

TEST1 47 test pin 1 BD4CR

TEST2 48 test pin 2 BT4CR

V

SSD3V1

V

SSD3V2

V

SSD3V3

V

DDD3V1

V

DDD3V2

V

SSD3V4

V

SSD3V5

V

SSD3V6

DSP_RESET 57 reset (active LOW) IBUFU

RTCB 58 asynchronous reset test control block (active LOW) IBUFD

SHTCB 59 shift clock test control block IBUFD

TSCAN 60 scan control IBUFD

V

SS_OSC

OSC_IN 62 crystal oscillator input; crystal oscillator sense for gain control or forced input

OSC_OUT 63 crystal oscillator output; drive output to 11.2896 MHz crystal OSC

V

DD_OSC

n.c. 65 not connected

n.c. 66 not connected

n.c. 67 not connected

n.c. 68 not connected

n.c. 69 not connected

n.c. 70 not connected

n.c. 71 not connected

n.c. 72 not connected

n.c. 73 not connected

n.c. 74 not connected

n.c. 75 not connected

VDACP1 76 not used

VDACN1 77 not used

42 digital supply voltage3; peripheral cells only (3 or 5 V) VDD5

43 digital ground supply 3; peripheral cells only (3 or 5 V) VSS5

2

C-bus slave subaddress selection input IBUFD

2

C-bus serial clock input SCHMITCD

2

C-bus serial data input/output BD4SCI4

49 digital ground supply 1 of 3 V core only VSS3S

50 digital ground supply 2 of 3 V core only VSS3S

51 digital ground supply 3 of 3 V core only VSS3S

52 digital supply voltage1 of 3 V core only VDD3

53 digital supply voltage2 of 3 V core only VDD3

54 digital ground supply 4 of 3 V core only VSS3S

55 digital ground supply 5 of 3 V core only VSS3S

56 digital ground supply 6 of 3 V core only VSS3S

61 ground supply crystal oscillator circuit VSS3S

OSC

in slave mode

64 3 V supply voltage crystal oscillator circuit VDD3

1999 Aug 05 8

Page 9

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

SYMBOL PIN DESCRIPTION PIN TYPE

n.c. 78 not connected

n.c. 79 not connected

n.c. 80 not connected

Table 1 Pin types

PIN NAME PIN DESCRIPTION

B4CR 4 mA slew rate controlled digital output

BD4CR 4 mA slew rate controlled digital I/O

BD4CRD 4 mA slew rate controlled digital I/O with pull-down resistor

BT4CR 4 mA slew rate controlled 3-state digital output

IBUF digital input

IBUFU digital input with pull-up resistor

IBUFD digital input with pull-down resistor

BD4SCI4 I

SCHMITCD Schmitt trigger input

AP2D analog input/output

OSC analog input/output

VDD5 5 V V

VDD3 3 V V

VSS3S 3 or 5 V V

VSS5 5 V V

APVDD analog V

APVSS analog V

2

C-bus input/output with open-drain NMOS 4 mA output

internal

DD

internal

DD

internal substrate

SS

external

SS

DD

SS

1999 Aug 05 9

Page 10

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

handbook, full pagewidth

VDACN1

VDACP1

n.c.

n.c.

n.c.

n.c.

n.c.

n.c.

n.c.

n.c.

n.c.

n.c.

n.c.

66

65

V

64

DD_OSC

OSC_OUT

63

OSC_IN

62

V

61

SS_OSC

TSCAN

60

SHTCB

59

RTCB

58

DSP_RESET

57

V

56

SSD3V6

V

55

SSD3V5

V

54

SSD3V4

V

53

DDD3V2

V

52

DDD3V1

V

51

SSD3V3

V

50

SSD3V2

V

49

SSD3V1

TEST2

48

TEST1

47

SDA

46

SCL

45

A0

44

V

43

SSD5V3

V

42

DDD5V3

DSP_OUT2

41

OUT3_V

OUT3_I

OUT2_I

OUT2_V

V

V

VREFDA

OUT1_V

OUT1_I

OUT0_I

OUT0_V

EQOV

SYS_CLK

V

DDD5V1

V

SSD5V1

2

I

S_IN2_WS

n.c.

n.c.

n.c.

n.c.

n.c.

n.c.

n.c.

POM

SSA2

DDA2

n.c.

n.c.

n.c.

80

79

78

77

76

75

74

73

71

72

70

69

68

67

1

2

3

4

5

6

7

8

9

10

11

12

13

SAA7712H

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

S_IO_IN1

S_IO_IN2

2

S_IN2_BCK

2

S_IN2_DATA

I

2

I

S_IN1_WS

2

I

S_IN1_DATA

2

I

S_IO_BCK

2

S_IN1_BCK

I

2

I

2

I

I

Fig.2 Pin configuration.

1999 Aug 05 10

33

34

S_IO_WS

V

2

I

35

SSD5V2

DDD5V2

V

36

37

S_IO_OUT1

S_IO_OUT2

2

2

I

I

38

39

DSP_IN1

DSP_IN2

40

MGS207

DSP_OUT1

Page 11

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

8 FUNCTIONAL DESCRIPTION

8.1 Analog outputs

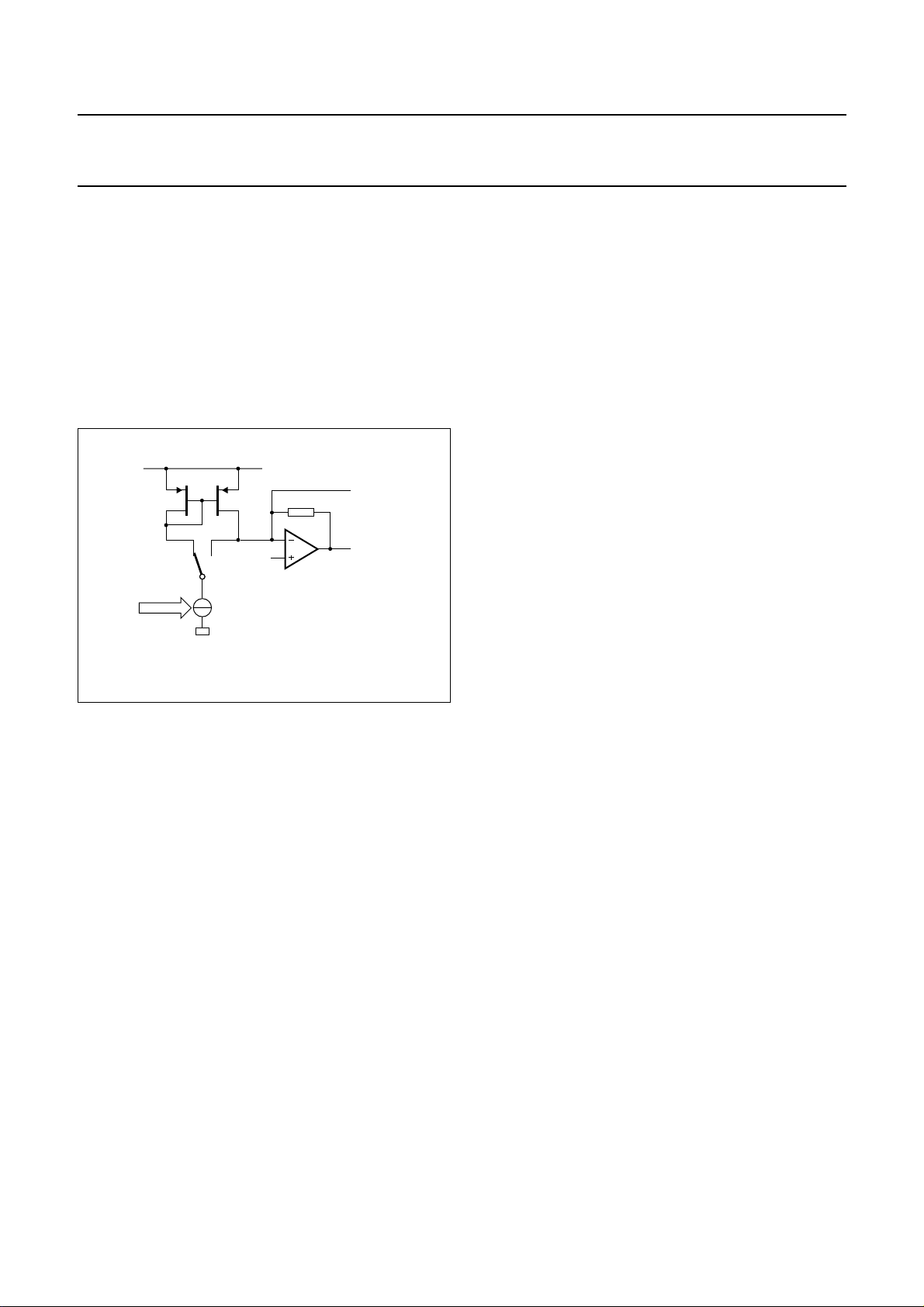

8.1.1 ANALOG OUTPUT CIRCUIT

Depending on the configuration of the equalizer sections,

the SAA7712H has 2 or 4 analog outputs which are

supplied by the samepower supply. Each ofthese outputs

hasavoltageand a current pin (see Fig.3). The signals are

available on 2 outputs (OUT0 and OUT1), or 4 outputs

(OUT0, OUT1, OUT2 and OUT3).

handbook, halfpage

BIT 0 to 13

MSB

DAC

MGS208

V

ref

OUT0_I

(OUT1_I)

OUT0_V

(OUT1_V)

8.1.3 DACS

Each of the four low noise high dynamic range DACs

consists of a signed-magnitude DAC with current output,

followed by a buffer operational amplifier.

8.1.4 UPSAMPLE FILTER

To reduce spectral components above the audio band, a

fixed 4 times oversampling and interpolating digital filter is

used. The filters give an out-of-audio-band attenuation of

at least 29 dB. The filter is followed by a first-order noise

shaper to expand the dynamic range to more than 105 dB.

The band around multiples of the sample frequency of the

DAC (4fs) is not affected by the digital filter. A capacitor

must be added in parallel with the DAC output amplifier to

attenuate this out-of-band noise further to an acceptable

level.

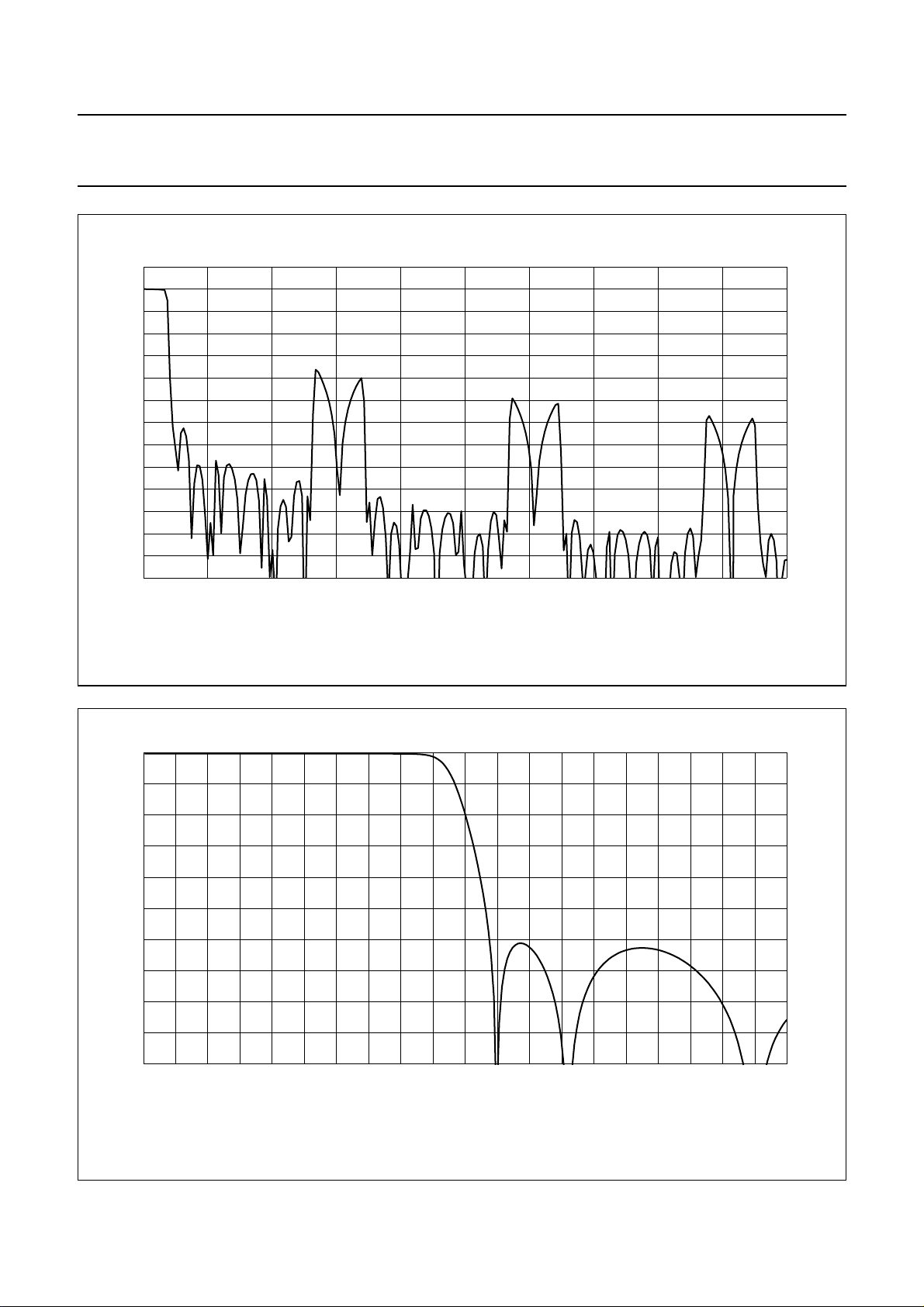

In Fig.4 the overall frequency spectrum at the DAC audio

output without external capacitor or low-pass filter for the

audio sampling frequencies of 38 kHz is shown. In Fig.5

the detailed spectrum around fs is shown for an fs of

38, 44.1 and 48 kHz. The pass band bandwidth (−3 dB) is

1

⁄2fs.

Fig.3 Analog output circuit.

8.1.2 DAC FREQUENCY

The sample rate (fs) of the selected source is the frame

rate of the DSP.The word clock for the upsample filter and

the clock for the DACs, at 4fs, are derived internally from

the word select of the selected audio source.

1999 Aug 05 11

Page 12

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

MGS209

handbook, full pagewidth

α

(dB)

0

−10

−20

−30

−40

−50

−60

0 100

handbook, full pagewidth

0

α

(dB)

−10

−20

−30

−40

300 400200

Fig.4 Overall frequency spectrum audio output.

fs = 38000 Hz

f (kHz)

500

MGS210

−50

0 10000 30000

0 11605 3481623211 fs = 44100 Hz

0 12632 3789525263 fs = 48000 Hz

20000

Fig.5 Detailed frequency spectrum audio output.

1999 Aug 05 12

fs = 38000 Hz

f (Hz)

Page 13

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

8.1.5 PERFORMANCE

The signed-magnitude noise-shaped DAC has a dynamic

range in excess of 100 dB. The signal-to-noise ratio of the

audio output at full-scale is determined by the word length

of the converter. The noise at low outputs is fully

determined by the noise performance of the DAC. Since it

is a signed-magnitude type, the noise at digital silence is

also low. As a disadvantage, the total THD is higher than

conventional DACs. The typical total harmonic

distortion-plus-noise to signal ratio as a function of the

output level is shown in Fig.6.

handbook, halfpage

−20

(THD + N)/S

(dB)

−40

MGS211

8.1.6 POWER-ON MUTE (POM)

To avoid any uncontrolled noise at the audio outputs after

power-on of the IC, the reference current source of the

DAC is switched off. The capacitor on pin POM

determines the time after which this current has a soft

switch-on.So at power-on the current audiosignal outputs

are always muted. The loading of the external capacitor is

done in two stages via two different current sources.

The loading starts at a current level that is 9 times lower

than the current loading after the voltage on pin POM has

passed the 1 V level. This results in an almost dB linear

behaviour.

8.1.7 POWER-OFF PLOP SUPPRESSION

Power should still be provided to the analog part of the

DAC, while the digital part is switching off. As a result, the

output voltage will decrease gradually allowing the power

amplifier some extra time to switch-off without audible

plops. If a 5 V power supply is present, the supply voltage

of the analog part of the DAC can be fed from the 5 V

power supply via a 1.8 V zener diode. A capacitor,

connected to the 3.3 V power supply, provides power to

the analog part when the 5 V power supply is switching off

fast.

−60

−80

−80 −60 −40 0

−20

output level (dB)

Fig.6 Typical (THD + N)/S curve as a function of

the output level.

1999 Aug 05 13

Page 14

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

8.1.8 PIN VREFDA

With two internal resistors half the supply voltage (V

DDA2

is obtained and coupled to an internal buffer. This

reference voltage is used as DC voltage for the output

operational amplifiers and as reference for the DAC.

In order to obtain the lowest noise and to have the best

ripple rejection, a filter capacitor has to be added between

this pin and ground.

8.1.9 INTERNAL DAC CURRENT REFERENCE

As a reference for the internal DAC current and for the

DAC current source output, a current is drawn from the

level on pin VREFDA to pin V

(ground) via an internal

SSA2

resistor. The absolute value of this resistor also

determines the absolute current of the DAC. This means

that the absolute value of the current is not that fixed due

to the spread of the current reference resistor value. This,

however, does not influence the absolute output voltages

because these voltages are also derived from a

conversion of the DAC current to the actual output voltage

via internal resistors.

8.1.10 SUPPLY OF THE ANALOG OUTPUTS

All the analog circuitry of the DACs and the operational

amplifiers are fed by 2 supply pins, V

Pin V

must have sufficient decoupling to prevent THD

DDA2

DDA2

and V

SSA2

.

degradation and to ensure a good power supply rejection

ratio.

The digital part of the DAC is fully supplied from the chip

core supply.

2

8.2 I

)

8.2.1 DIGITAL DATA STREAM FORMATS

S-bus inputs and outputs

For communication with external digital sources a serial

3-line bus is used. This I2S-bus has one line for data, one

line for clock and one line for the word select.

See Fig.7 for the general waveform formats of the four

possible formats.

Theserialdigitalinputs(andoutputs)oftheSAA7712Hare

capable of handling multiple formats: Philips I2S-bus and

LSB-justified formats of 16, 18 and 20 bits word sizes.

In Philips I2S-bus format, the number of bit clock (BCK)

pulses may vary in the application. When the transmitter

word length is smaller than the receiver word length, the

receiver will fill in zeroes at the LSB side. When the

transmitter word length exceeds the receiver word length,

the LSBs are skipped. For correct operation of the DACs,

there should be a minimum of 16 bit clocks per word

select.

In the LSB-justified formats, the transmitter and receiver

must be set to the same format. Be aware that a format

switch between 20, 18 and 16 bits LSB-justified formats is

done by changing the relative timing of the word select

edges. The data bits remain unchanged. In the 20 bits

format, the 2 LSBs are zeroes. In the 16 bits format, the

2 data bits following the word select edge are not zero, but

undefined. In fact, these are the LSBs of the 18-bit word.

The timing specification for the waveforms of the serial

digital inputs and outputs are given in Fig.17.

1999 Aug 05 14

Page 15

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

1999 Aug 05 15

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

WS

BCK

DATA

WS

BCK

DATA

WS

BCK

DATA

WS

BCK

LEFT

MSB B2 MSB MSBB2

LEFT

MSB LSBB2

LEFT

MSB B2 B3 B4

LEFT

RIGHT

1321

1516 1

32

LSB

2

S-BUS

INPUT FORMAT I

2

B15

LSB-JUSTIFIED FORMAT 16 BITS

215161718 1

B17

LSB-JUSTIFIED FORMAT 18 BITS

2151617181920 1

RIGHT

MSB LSBB2 B15

RIGHT

MSB B2 B3 B4

RIGHT

21516 1

215161718 1

B17

2151617181920 1

LSB

DATA

MSB B2 B3 B4 B5 B6

LSB

B19

LSB-JUSTIFIED FORMAT 20 BITS

Fig.7 All serial data I/O formats.

handbook, full pagewidth

MSB B2 B3 B4 B5 B6

B19

LSB

MGS212

Page 16

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

8.2.2 SLAVE I2S-BUS INPUTS

The SAA7712H has two slave I2S-bus inputs, I2S_IN1 and

I2S_IN2 with respective data lines I2S_IN1_DATA and

I2S_IN2_DATA, word select lines I2S_IN1_WS and

I2S_IN2_WS and bit clock lines I2S_IN1_BCK and

I2S_IN2_BCK. The external sourceis master and supplies

the bit clock and word select. The I2C-bus bits

audio_format(2 to 0) allow for selection of the desired

I2S-bus format (see Table 13). The bits, needed for

selecting a certain format, are explained in Table 2.

Theinput circuitry is limitedin handling the numberof BCK

pulses per WS period. If the word rate of the selected

digital input source is fs, the bit clockmust be a continuous

clock in the range of 16fs≤ f

≤ 256fs. The minimum

bit(CLK)

limit of the audio sample frequency is determined by

1

⁄18f

. The maximum limitof the audio sample frequency

SCL

is determined by DSP_clock/481 Hz.

Table 2 I

2

C-bus audio_format mode bits (0FF9H,

see Table 13)

AUDIO_FORMAT

OUTPUT

BIT 9 BIT 8 BIT 7

0 0 0 internal format (for test

purposes only)

− 0 1 LSB-justified, 16 bits

− 1 0 LSB-justified, 18 bits

− 1 1 LSB-justified, 20 bits

2

1 0 0 standard I

S-bus (default)

Table 3 I2C-bus audio_source mode bit (0FF9H,

see Table 13)

AUDIO_SOURCE

OUTPUT

Bit 5

2

S_IN1 (default)

2

S_IN2

8.2.3 M

0I

1I

ASTER I

2

S-BUS INPUTS AND OUTPUTS

For the co-processor I/O interface, the SAA7712H acts as

a master. The SAA7712H supplies both the bit clock and

2

word select. The I

C-bus bits host_io_format(1 and 0)

allow for selection of the desired I2S-bus format (see

Table 13).

The bits needed for selecting a certain format are given in

Table 4.

All I2S-bus output lines, I2S_IO_WS, I2S_IO_BCK,

I2S_IO_OUT1 and I2S_IO_OUT2, can be 3-stated with

I2C-bus bit en_host_io (see Table 13).

The word select and bit clock of the co-processor I/O

interface are derived from the word select and bit clock of

the audio source selected according to Table 3.

The incoming bit clock can be divided by 1, 2, 4 or 8

depending on the needs of an external connected

co-processor. These selections can be done with I2C-bus

bits cloop_mode(2 to 0) (see Table 13). The meaning of

these bits is shown in Table 5.

The selection of the DSP input among the decimated

2

analog input and the I

S-bus inputs I2S_IN1 and I2S_IN2

is controlled with I2C-bus bit audio_source (see Table 13).

The meaning of this bit can be found in Table 3.

1999 Aug 05 16

Page 17

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

Table 4 I2C-bus host_io_format bits (0FF9H, see Table 13)

HOST_IO_FORMAT

BIT 11 BIT 10

0 0 standard I

0 1 LSB-justified format, 16 bits

1 0 LSB-justified format, 18 bits

1 1 LSB-justified format, 20 bits

2

Table 5 I

C-bus cloop_mode bits (0FF9H, see Table 13)

CLOOP_MODE

BIT 15 BIT 14 BIT 13

0 −−bypass WS (default)

1 −−WS 50% duty factor

− 0 0 bypass BCLK (default)

− 0 1 divide BCLK by 2

− 1 0 divide BCLK by 4

− 1 1 divide BCLK by 8

8.3 Equalizer accelerator

8.3.1 INTRODUCTION

The equalizer accelerator is a hardware accelerator to the

DSP core. Both its inputs and outputs are stored in

registers of the DSP core.

The equalizer cannot be used and cannot be programmed

if no word select and bit clock signal are present on a

selected digital source input; see audio_source bit in

Table 3 (I2S_IN1 or I2S_IN2). The minimum required

DSP_clock is 481fs.

The equalizer accelerator contains one second-order filter

data path that is 20 times multiplexed. With this circuit, a

2-channel equalizer of 10 second-order sections per

channel or a 4-channel equalizer of 5 second-order

sections per channel can be realised. The centre

frequency, gain and Q-factor of all 20 second-order

sections can be set independently from each other. Every

sectionisfollowedbyaselectableattenuationof0 or 6 dB.

Per section, 4 bytes of the I2C-bus register are needed to

store the settings. The equalizer settings can be updated

during normal operation. An application program supports

the programming of the equalizer.

OUTPUT

2

S-bus (default)

OUTPUT

If the gain setting causes the audio signal to exceed the

maximum level in one of the filter sections, the signal will

be clipped and the equalizer overflow output (pin EQOV)

will be set HIGH until the end of the next audio sample

period.

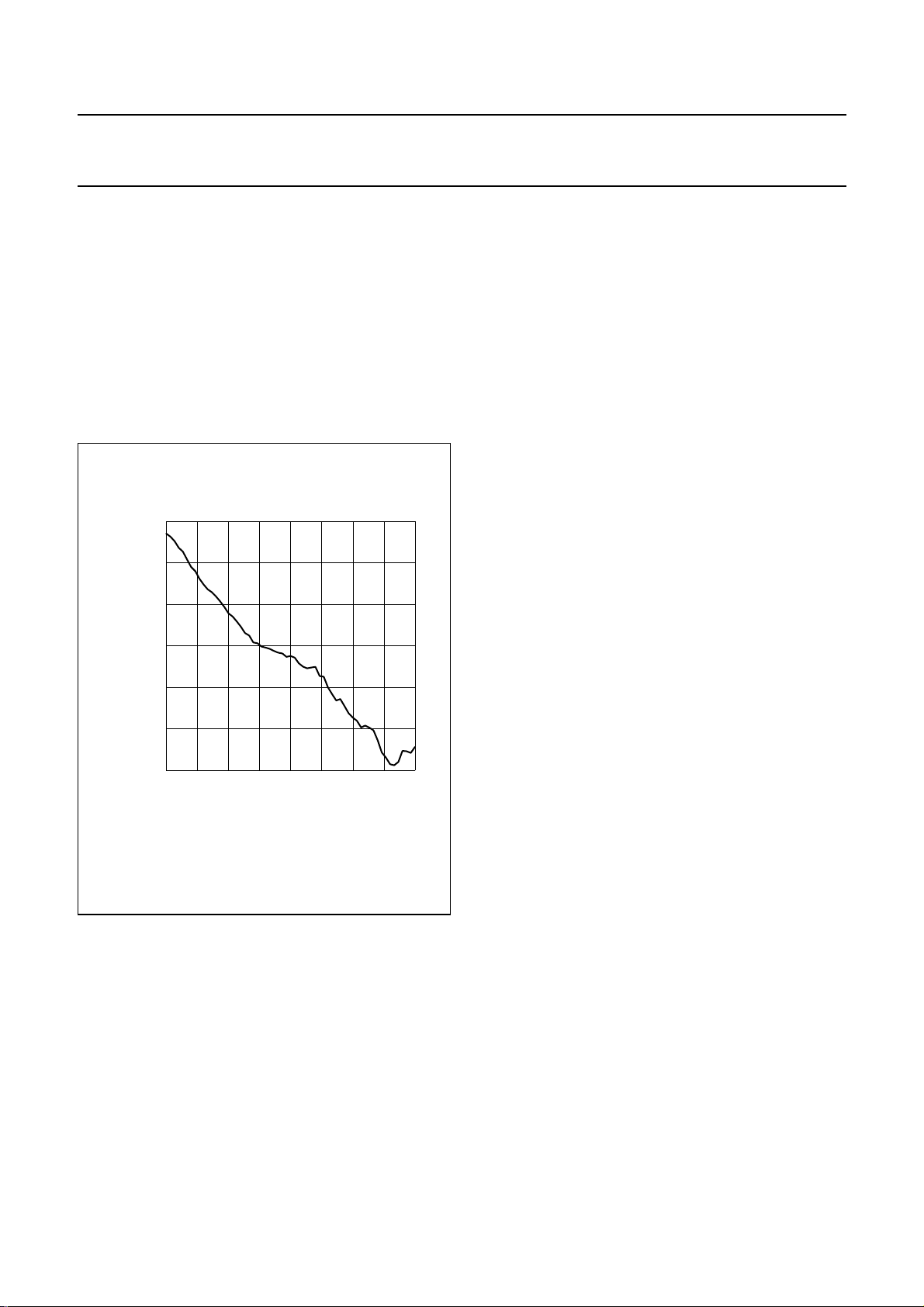

8.3.2 CONFIGURATION OF EQUALIZER SECTIONS

The equalizer accelerator can make a 2-channel equalizer

of 10 second-order sections per channel or a 4-channel

equalizer of 5 second-order sections per channel.

The sections of one channel can be chained one after the

other. Depending on the I2C-bus control bit two_four

(see Table 11), the 20 filter sections are combined for the

appropriate configuration, as illustrated in Fig.8.

1999 Aug 05 17

Page 18

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

handbook, full pagewidth

1

A

B

C

D

2 3 4 5

Fig.8 Configurations of the equalizer sections.

8.3.3 OVERFLOW DETECTION

The equalizer has an overflow flag. This flag is fed to

output pin EQOV. If an overflow is detected in one of the

filter sections, the signal is clipped to the maximum

allowed level. The overflow flag is immediately set.

It remains at a HIGH-level during the remaining part of the

currentaudiosample period and for the whole next sample

period. If no overflow is detected during this next sample

period, the overflow flag goes to a LOW-level at the

beginning of the sample period after that. Otherwise, the

overflowflag remains at a HIGH-levelforat least one other

audio sample period.

8.4 Clock circuit and oscillator

8.4.1 GENERAL DESCRIPTION

The chip has a crystal clock oscillator. It can use a crystal

at either f

f

= 18.432 MHz = 576 × 32 kHz in fundamental mode.

xtal

= 16.384 MHz = 512 × 32 kHz or

xtal

The block diagram of this Pierce oscillator is shown in

Fig.9. The active element needed to compensate for the

loss resistance of the crystal is the block Gm. This block is

placed between the external pins OSC_IN

and OSC_OUT.

OUT0IN0

2 channel

OUT1IN1

2 channel

OUT2IN2

OUT3IN3

MGS213

The gain of the oscillator is internally controlled by the

AGC block. A sinewave with a peak-to-peak voltage close

to the oscillator power supply voltage is generated.

The AGC block prevents clipping of the sine wave and

therefore the higher harmonics are as low as possible.

At the same time, the voltage of the sine wave is as high

as possible so reducing the jitter going from sine wave to

clock signal. The sinusoidal output is converted into a

CMOS compatible clock by the comparator.

The second mode of operation shown in Fig.10, is the

slave mode which is driven by a master clock directly.

The signal to pin OSC_IN can be driven to the power

supply voltages V

DD_OSC

and V

SS_OSC

.

8.4.2 SUPPLY OF THE CRYSTAL OSCILLATOR

The power supply connections of the oscillator are

separate from the other supply lines. This is to minimize

the feedback from the ground bounce of the chip to the

oscillatorcircuit. Pin V

and pin V

as the positive supply.

DD_OSC

SS_OSC

isused as the groundsupply

1999 Aug 05 18

Page 19

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

handbook, full pagewidth

0.5V

DD_OSC

handbook, full pagewidth

AGC

on chip

off chip

C1

10 pF

Gm

100 kΩ

R

62

OSC_IN

bias

10 pF

C2

OSC_OUT

clock out

V

DD_OSC

616463

V

SS_OSC

Fig.9 Block diagram of the crystal oscillator circuit.

0.5V

DD_OSC

MGS214

Gm

100 kΩ

R

62

OSC_IN

bias

10 pF

OSC_OUT

C2

on chip

off chip

C3

5 pF

AGC

C1

10 pF

slave input

Fig.10 Block diagram of the oscillator in slave mode.

1999 Aug 05 19

clock out

V

DD_OSC

616463

V

SS_OSC

MGS215

Page 20

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

8.5 Programmable phase-locked loop circuit

The clock of the DSP is generated with a programmable PLL.

To select the required DSP clock see Table 6. The N factor (ranging from 93 to 181) can be selected with I2C-bus bits

PLL_div(14 to 11), see Table 10. Depending on the crystal and the required DSP clock the I2C-bus bits pll_fs_sel and

bits dsp_turbo must be set. The maximum limit of the audio sample frequency is determined by DSP_clock/481 Hz.

2

Table 6 I

C-bus bits PLL_div and dividing factors N of the programmable DSP clock

PLL_DIV(14 to 11) N

TDA9875

0000 93 (default) 23.808

0001 99 25.344

(3)

(3)

(1)

MSP3410D

26.784

28.512

0010 106 27.136 30.528

0011 113 28.928 32.544

0100 121 30.976 34.848

0101 126 32.256 36.288

DSP CLOCK FREQUENCY (MHz)

0110 132 33.792

0111 137 35.072

1000 143 36.608

1001 148 37.888

1010 154 39.424

1011 159 40.704

1100 165 42.240

1101 170 43.520

1110 176 45.056

1111 181 46.336

(3)

(3)

(3)

(3)

(3)

(3)

(3)

(3)

(3)

(3)

38.016

39.456

41.184

42.624

44.352

45.792

47.520

48.960

50.688

52.128

Notes

1. f

2. f

= 16.384 MHz; pll_fs_sel = 1 and dsp_turbo = 1, see Table 11.

xtal

= 18.432 MHz; pll_fs_sel = 1 and dsp_turbo = 1, see Table 11.

xtal

3. Usable frequency.

(2)

(3)

(3)

(3)

(3)

(3)

(3)

(3)

(3)

(3)

(3)

(3)

(3)

1999 Aug 05 20

Page 21

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

8.6 I2C-bus control

8.6.1 INTRODUCTION

A general description of the I2C-bus format can be

obtained from Philips Semiconductors, International

Marketing and Sales Communications (IMSC).

For the external control of the SAA7712H a fast I2C-bus

is implemented. This is a400 kHz bus which isdownward

compatible with the standard 100 kHz bus.

There are different types of control instructions:

• Instructions to control the DSP program, program the

coefficient RAM and read the values of parameters

• Instructions to control the equalizer, program the

equalizer coefficient RAM to be able to change the

centre frequency, gain and Q-factor of the equalizer

sections

• Instructions to control the source selection and

programmable parts, e.g. PLL clock speed.

The detailed description of the I2C-bus and commands is

given in the following sections. The description of the

different bits in the memory map is given in Section 9.6.

The equalizer cannot be used and cannot be

programmed if there is no word select and bit clock signal

present on a selected digital source input; see

audio_source bit in Table 3 (I2S_IN1 and I2S_IN2).

The minimum limit of the audio sample frequency is

determined by1⁄18f

SCL

.

8.6.2 CHARACTERISTICS OF THE I2C-BUS

The I2C-bus is for 2-way, 2-line communication between

different ICs or modules. The two lines are a serial data

line (SDA) and a serial clock line (SCL). Both lines must

be connected to VDD via a pull-up resistor when

connected to the output stages of a microcontroller. For a

400 kHz I2C-bus the recommendation from Philips

Semiconductors must be followed (e.g. up to loads of

200 pFonthebusapull-upresistorcanbeused,between

200 to 400 pF a current source or switched resistor must

be used). Data transfer canonly be initiated whenthe bus

is not busy.

8.6.3 BIT TRANSFER

One data bit is transferred during each clock pulse.

The data on the SDA line must remain stable during the

HIGHperiod of the clock pulse aschangesin the data line

at this time will be interpreted as control signals

(see Fig.11). The maximum clock frequency is 400 kHz.

To be able to run on this high frequency all the inputs and

outputs connected to this bus must be designed for this

high speed I2C-bus according to the Philips specification.

handbook, full pagewidth

SDA

SCL

data line

stable;

data valid

change

of data

allowed

Fig.11 Bit transfer on the I2C-bus.

1999 Aug 05 21

MGS216

Page 22

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

8.6.4 START AND STOP CONDITIONS

Both data and clock lines will remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line, while

theclock is HIGH, isdefined as a STARTcondition (S). A LOW-to-HIGH transition of the data line whilethe clock is HIGH

is defined as a STOP condition (P) (see Fig.12).

handbook, full pagewidth

SDA

SCL

S P

START condition STOP condition

MGS217

Fig.12 START and STOP conditions.

8.6.5 DATA TRANSFER

A device generating a message is a ‘transmitter’ and a device receiving a message is the ‘receiver’. The device that

controls the message is the ‘master’ and the devices which are controlled by the master are the ‘slaves’.

handbook, full pagewidth

SDA

SCL

S

START condition

MSB

1 2 7 8 9 1 2 3 to 8 9

acknowledgement

signal from receiver

byte complete

interrupt within receiver

clock line held LOW while

interrupts are serviced

ACK ACK

acknowledgement

signal from receiver

MGS218

Fig.13 Data transfer on the I2C-bus.

1999 Aug 05 22

Page 23

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

8.6.6 ACKNOWLEDGE

The number of data bits transferred between the START

and STOP conditions from the transmitter to the receiver

is not limited. Each byte of eight bits is followed by one

acknowledge bit (see Fig.13). The acknowledge bit is a

HIGH-level left on the bus by the transmitter whereas the

master generates an extra acknowledge related clock

pulse.

A slave receiver which is addressed must generate an

acknowledge after the reception of each byte. Also a

master must generate an acknowledge after the reception

of each byte that has been clocked out of the slave

transmitter. The device that acknowledges has to pull

downthe SDA line (left HIGHbythe transmitter) during the

acknowledge clock pulse, so that the SDA line is stable

LOW during the HIGH period of the acknowledge related

clock pulse.

handbook, full pagewidth

data output

by transmitter

Set-up and hold times must be taken into account.

A master receiver must signal an end of data to the

transmitter by not generating an acknowledge on the last

byte that has been clocked out of the slave. In this event

thetransmittermust leave the data line HIGH toenablethe

master to generate a STOP condition (see Fig.14).

8.6.7 S

TATE OF THE I

AFTER

POWER-ON RESET

2

C-BUS INTERFACE DURING AND

Duringreset(seeSection 8.8),theinternalSDAlineiskept

HIGH and pin SDA is therefore high-impedance. The SDA

line remains HIGH until a master pulls it down to initiate

communication.

data output

by receiver

SCL from

master

S

START condition

Fig.14 Acknowledge on the I2C-bus.

not acknowledge

acknowledge

12 789

MGS219

clock pulse for

acknowledgement

1999 Aug 05 23

Page 24

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

8.7 External control pins

For external control two input pins are implemented.

The status of these pins can be changed by applying a

logic level. The status of these pins is recorded in the

internal status register. The function of each input pin is

determined by the DSP software.

Pin DSP_IN1:

• Logic 0 or left open-circuit means volume coefficients

updates are possible (default)

• Logic 1 means no updates of volume coefficients are

possible.

Pin DSP_IN2:

• If the 3-band spectrum analyser is used:

– Logic 1 will reset the band registers of the analyser

– Logic 0 or left open-circuit means no reset of the

band registers will be done (default).

• If the 3-band spectrum analyser is not used:

– Thestate of pin DSP_IN2 can bereadvia an I2C-bus

command.

To control external devices two output pins are

implemented. The status of these pins is controlled by the

DSP program. The functions of these pins are determined

by the DSP software.

Pin DSP_OUT1:

• To drive pin DSP_OUT1 via an I2C-bus command.

A more or less fixed relationship between the

DSP_RESET time constant and the POM time constant is

obligatory.Thevoltageonpin POM determines the current

flowing in the DACs. For 0 V on pin POM, the DAC

currents are zero and so also the DACs output voltages.

Whena3 Vsupplyvoltage(V

the DAC currents are at their nominal (maximum) value.

Long before the DAC outputs get their nominal output

voltages, the DSP must be in normal operating mode to

reset the output register. Therefore, the time constant of

DSP_RESET must be shorter than the time constant of

POM. For advised capacitors see the application diagram.

The reset has the following function:

• All I2C-bus registers are reset to their default values

• The DSP algorithm is re-started

• The external control output pins are reset

(see Section 8.7)

• Pin SDA is high-impedance.

WhenthelevelontheresetpinisHIGH,theDSPalgorithm

starts to run.

In addition to the reset pin, there is also a software reset;

bitPC_reset(bit 15, 0FFDH, see Table 11). This reset has

the following function:

• The DSP algorithm is re-started

• The external control output pins are reset

(see Section 8.7).

)issuppliedtopin POM,

DDA2

Pin DSP_OUT2:

• To drive pin DSP_OUT2 via an I2C-bus command.

8.8 Reset pin

The reset signal on pin DSP_RESET is active LOW and

has an internal pull-up resistor. Between this pin and

ground a capacitor should be connected to allow a proper

switch-on of the supply voltage. The capacitor value is

such that the chip is in the reset state as long as the power

supply is not stabilized.

1999 Aug 05 24

Page 25

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

8.9 Power supply connection and EMC

Thedigital part of the chip has intotal5 positive supply line

connections and 8 ground connections. To minimise

radiationthechipshouldbeputonadoublelayerPCBwith

a large ground plane on one side. The ground supply lines

shouldhave a short connectionto this ground plane. A coil

and capacitor network in the positive supply line can be

used as high frequency filter.

8.10 Test mode connections

Pins TSCAN, RTCB and SHTCB are used to put the chip

in test mode and to test the internal connections. Each pin

has an internal pull-down resistor to ground. In the

applicationthesepinscanbeleftopen-circuitorconnected

to ground.

2

C-BUS FORMAT

9I

9.1 Addressing

Before any data is transmitted on the I2C-bus, the device

whichshouldrespondisaddressed first. The addressing is

alwaysdonewiththefirstbytetransmittedaftertheSTART

procedure.

9.2 Slave address (pin A0)

The SAA7712H acts as a slave receiver or a slave

transmitter. Therefore, the clock signal SCL is only an

input signal. The data signal SDA is a bidirectional line.

The slave address is shown in Table 7.

Table 7 Slave address

MSB LSB

0 0 1 1 1 1 A0 R/W

The subaddress bit A0 corresponds to the hardware

address pin A0 which allows the device to have two

addresses. This allows the control of two SAA7712Hs via

the same I

2

C-bus.

9.3 Write cycles

The I2C-bus configuration for a write cycle is shown in

Fig.15. The write cycle is used to write the bytes to control

the PLL for the DSP clock generation, the format of the

I2S-bus and some other settings. More details can be

found in the I2C-bus memory map (see Table 8).

The data length is 2 or 3 bytes, depending on the

accessedmemory.The slave receiver detects the address

and adjusts the number of bytes accordingly. For XRAM,

the data word length is 18 bits and 3 bytes are sent over

the I2C-bus. The upper 6 bits (i.e. bit 7 to bit 2) of the first

byte DATA H are don’t care. For YRAM, the data word

lengthis12 bits and 2 bytes are sent over the I2C-bus.The

leftnibble(i.e.bit 7 tobit 4)ofthefirstbyte DATA H is don’t

care.

9.4 Read cycles

The I2C-bus configuration for a read cycle is shown in

Fig.16.The read cycle is usedto read the data valuesfrom

XRAM or YRAM. The master starts with a START

condition (S), the SAA7712H address ‘0011110’ and a

logic 0 (write) for the read/write bit. This is followed by an

acknowledge of the SAA7712H. The master then writes

the memory high address and memory low address where

the reading of the memory content of the SAA7712H must

start. The SAA7712H acknowledges these addresses

both.

The master than generates a repeated START and again

the SAA7712H address ‘0011110’ but this time followed

by a logic 1 (read) of the read/write bit. From this moment

on,the SAA7712H will sendthe memory content in groups

of 2 (YRAM) or 3 (XRAM) bytes to the I2C-bus, each time

acknowledged by the master. The master stops this cycle

by generating a negative acknowledge, then the

SAA7712H frees the I2C-bus and the master cangenerate

a STOP condition (P).

1999 Aug 05 25

Page 26

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

1999 Aug 05 26

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

0111000

0 ADDR H ADDR L DATA H DATA M

S

A

C

K

address

R/W

S = START condition.

ACK = acknowledge from DSP (SDA LOW).

ADDR H and ADDR L = address DSP register.

DATA H, DATA M and DATA L = data of XRAM or registers.

DATA H and DATA M = data of YRAM.

P = STOP condition.

A

C

K

R/W

A

C

K

0111000

0 011 1100

S

address

A

C

K

A

C

K

A

C

K

auto increment if repeated n-groups of 3 (2) bytes

Fig.15 Master transmitter writes to the DSP registers.

R/W

A

C

K

auto increment if repeated n-groups of 3 (2) bytes

A

0ADDR H ADDR L DATA H

C

S

K

A

C

K

A

DATA M DATA L

C

K

A

C

DATA L

A

C

K

K

MGD568

A

C

K

MGA808 - 1

P

P

S = START condition.

ACK = acknowledge from DSP (SDA LOW).

ADDR H and ADDR L = address DSP register.

DATA H, DATA M and DATA L = data of XRAM or registers.

DATA H and DATA M = data of YRAM.

P = STOP condition.

Fig.16 Master transmitter reads from the DSP registers.

Page 27

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

9.5 I2C-bus memory map summary

TheI2C-bus memorymap contains all defined I2C-bus bits.The map is split into two different sections:hardwarememory

registers and the RAM definitions. The preliminary memory map is given in Table 8.

2

Table 8 I

0FF9H to 0FFFH various settings (see Table 9) 4 × 16 bits

0F80H to 0FA7H equalizer 40 × 16 bits

0800H to 097FH YRAM 384 × 12 bits

0000H to 017FH XRAM 384 × 18 bits

Table 9 I

2

I

C_DCS_CTR 0FFFH (see Table 10)

2

C_ADDA 0FFDH (see Table 11)

I

2

I

C_SEL 0FFAH (see Table 12)

2

I

C_HOST 0FF9H (see Table 13)

C-bus memory map

SUBADDRESSES FUNCTION SIZE

2

C-bus memory map: overview of various settings

REGISTER NAME SUBADDRESS

2

9.6 I

Table 10 I

C-bus memory map details

2

C_DCS_CTR register (0FFFH)

NAME

SIZE

(BITS)

DESCRIPTION DEFAULT BIT POSITION

− 10 reserved 9 to 0

loopo_on_off 1 pin SYS_CLK output enable: on (logic 1) or off (logic 0) off 10

PLL_div 4 PLL clock division factor for DSP_clock (see Table 6) 93 14 to 11

− 1 reserved 15

1999 Aug 05 27

Page 28

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

Table 11 I2C_ADDA register (0FFDH)

NAME

SIZE

(BITS)

DESCRIPTION DEFAULT

BIT

POSITION

− 10 reserved 9 to 0

pll_fs_sel 1 divide oscillator by 2 (logic 1) division 10

dsp_turbo 1 double DSP_clock (logic 1) doubling 11

two_four 1 2-channel 10-band (logic 1) or 4-channel 5-band (logic 0)

equalizer configuration

4-channel

5-band

12

− 2 reserved 14 and 13

pc_reset 1 re-start DSP algorithm (logic 1) or DSP running (logic 0) DSP running 15

2

Table 12 I

C_SEL register (0FFAH)

NAME

SIZE

(BITS)

DESCRIPTION DEFAULT

BIT

POSITION

− 8 reserved 7 to 0

bypass_pll 1 bypass PLL used for DSP_clock (logic 1) or use PLL for

use PLL 8

DSP_clock (logic 0)

− 4 reserved 12 to 9

inv_host_ws 1 inverting (logic 1) or non-inverting (logic 0) word select non-inverting 13

− 2 reserved 15 and 14

Table 13 I

2

C_HOST register (0FF9H)

NAME

SIZE

(BITS)

DESCRIPTION DEFAULT

BIT

POSITION

− 5 reserved 4 to 0

audio_source 1 input source is I

2

S_IN1 or I2S_IN2 (see Table 3) I2S_IN1 5

− 1 reserved 6

audio_format 3 format of selected input source (see Table 2) standard I

host_io_format 2 host input/output data format (see Table 4) standard I

en_host_io 1 enable (logic 1) or disable (logic 0) co-processor I

2

S-bus disable 12

2

S-bus 9 to 7

2

S-bus 11 and 10

cloop_mode 3 cloop mode (see Table 5) bypassWS 15 to 13

1999 Aug 05 28

Page 29

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

10 LIMITING VALUES

In accordance with the Absolute Maximum Ratings system (IEC 134).

SYMBOL PARAMETER CONDITION MIN. MAX. UNIT

V

DD3V

supply voltage 3.3 V analog and

digital

V

DD5V

supply voltage 5 V periphery only valid for the voltages in

connection with the 5 V I/Os

∆V

DD

I

input clamping diode current Vi< −0.5 V or Vi>VDD+ 0.5 V − 10 mA

IK

I

O(sink/source)

voltage difference between two

V

pins

DDx

output sink or source current,

−0.5V<Vo<VDD+ 0.5 V − 20 mA

output type 4 mA

I

VDD or VSS current per supply

DD,ISS

pin

T

amb

T

stg

V

es

I

lu(prot)

ambient temperature 0 70 °C

storage temperature −65 +150 °C

electrostatichandlingvoltagefor

all pins

note 1 −3000 +3000 V

note 2 −300 +300 V

latch-up protection CIC specification/test method 100 − mA

P/out power dissipation per output − 100 mW

P

tot

total power dissipation − 400 mW

−0.5 +5 V

−0.5 +6.5 V

− 550 mV

− 750 mA

Notes

1. Human body model: equivalent to discharging a 100 pF capacitor through a 1.5 kΩ resistor.

2. Machine model: equivalent to discharging a 200 pF capacitor through a 2.5 µH inductance and a 0 Ω series resistor.

11 THERMAL CHARACTERISTICS

SYMBOL PARAMETER CONDITION VALUE UNIT

R

th(j-a)

thermal resistance from junction to ambient in free air; note 1 45 K/W

Note

1. Printed-circuit board mounting.

1999 Aug 05 29

Page 30

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

12 DC CHARACTERISTICS

Digital I/O at T

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Supplies

V

DD3V

V

DD5V

I

DDD3V

I

DDD5V

I

DAC

I

DD_OSC

P

tot

Logic

V

IH

V

IL

V

hys

V

OH

V

OL

V

OL(I2C)

I

output leakage current

O

R

pu

= 0 to 70 °C; V

amb

supply voltage 3.3 V analog

and digital

supply voltage 5 V periphery all VDD pins of the type VDD5

supply current of the 3.3 V

digital core part

supply current of the 5 V

digital periphery part

= 4.5 to 5.5 V; V

DD5V

= 3 to 3.6 V; unless otherwise specified.

DD3V

all VDD pins of the type VDD3

and APVVD referenced to V

referenced to V

at f

DSP18

SS

; maximum activity of

the DSP

at f

; maximum activity of

DSP18

the DSP

3 3.3 3.6 V

SS

4.5 5 5.5 V

3.0 3.3 3.6 V

− 33 80 mA

− 25 mA

supply current of the DACs at zero input and output signal − 47 mA

supply current of the crystal

at f

; functional mode − 3.5 3 mA

DSP18

oscillator

total power dissipation at f

; maximum activity of

DSP18

− 135 400 mW

the DSP

HIGH-levelinputvoltageof all

0.7V

DDD5V

−− V

digital inputs and I/Os on

pins 24 to 29, 38, 39,

44 to 47, 57 to 60

LOW-level input voltage of all

−−0.3V

DDD5V

V

digital inputs and I/Os on

pins 24 to 29, 38, 39,

44 to 47, 57 to 60

hysteresis voltage on pin 45

1 1.3 − V

(SCL)

HIGH-level output voltage of

IO= −4mA V

− 0.4 −− V

DDD5V

digital outputs on pins 20, 21,

30, 33, 36, 37, 40, 41, 47, 48

LOW-level output voltage of

digital outputs on pins 20, 21,

30, 33, 36, 37, 40, 41, 47, 48

LOW-level output voltage of

V

V

= 4.5 V; IO=4mA −−0.4 V

DDD5V

= 3.0 V; IO=4mA −−0.4 V

DDD5V

IO=4mA −−0.4 V

digital I2C-bus data output on

pin 46 (SDA)

VO= 0 or V

DD

−−5µA

3-state outputs on pins 21,

30, 33, 36, 37, 46 to 48

internal pull-up resistance to

V

on pin 57

DDD

23 50 80 kΩ

(DSP_RESET)

1999 Aug 05 30

Page 31

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

R

pd

t

, t

i(r)

t

LH5

t

LH3

t

LH(I2C5)

t

LH(I2C3)

t

HL5

t

HL3

t

HL(I2C5)

t

HL(I2C3)

i(f)

internal pull-down resistance

to V

on pins 24 to 29, 38,

SSD

39, 44, 58 to 60

input rise and fall times V

output rise time on pins 20,

21, 30, 33, 36, 37, 40, 41, 47,

48

output rise time on pins 20,

21, 30, 33, 36, 37, 40, 41, 47,

48

output rise time on pin 46

(SDA)

output rise time on pin 46

(SDA)

output fall time on pins 20,

21, 30, 33, 36, 37, 40, 41, 47,

48

output fall time on pins 20,

21, 30, 33, 36, 37, 40, 41, 47,

48

output fall time on pin 46

(SDA)

output fall time on pin 46

(SDA)

= 5.5 V − 6 200 ns

DDD5V

V

V

V

= 3.6 V − 6 200 ns

DDD5V

= 5.5 V;

DDD5V

= 3.6 V; Tj= −40 °C;

DDD3V

CL=60pF

V

DDD5V

= 4.5 V;V

DDD3V

=3V;

Tj= 125 °C; CL=60pF

V

V

= 3.6 V;

DDD5V

= 3.6 V; Tj= −40 °C;

DDD3V

CL=60pF

V

DDD5V

= 3.0 V;V

DDD3V

=3V;

Tj= 125 °C; CL=60pF

CLand Rpu are application

specific

CLand Rpuare application

specific

V

V

= 5.5 V;

DDD5V

= 3.6 V; Tj= −40 °C;

DDD3V

CL=60pF

V

DDD5V

= 4.5 V;V

DDD3V

=3V;

Tj= 125 °C; CL=60pF

V

V

= 3.6 V;

DDD5V

= 3.6 V; Tj= −40 °C;

DDD3V

CL=60pF

V

DDD5V

= 3.0 V;V

DDD3V

=3V;

Tj= 125 °C; CL=60pF

V

V

= 5.5 V;

DDD5V

= 3.6 V; Tj= −40 °C;

DDD3V

CL= 200 pF

V

DDD5V

= 4.5 V;V

DDD3V

=3V;

Tj= 125 °C; CL= 200 pF

V

V

= 3.6 V;

DDD5V

= 3.6 V; Tj= −40 °C;

DDD3V

CL= 200 pF

V

DDD5V

= 3.0 V;V

DDD3V

=3V;

Tj= 125 °C; CL= 200 pF

23 50 80 kΩ

5 −− ns

−−25 ns

7.5 −− ns

−−30 ns

−−−ns

−−−ns

5 −− ns

−−25 ns

7.5 −− ns

−−30 ns

30 −− ns

−−300 ns

40 −− ns

−−400 ns

1999 Aug 05 31

Page 32

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

13 ANALOG OUTPUTS CHARACTERISTICS

T

=25°C; V

amb

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

VREFDA

Z

VREFDA

V

o(rms)

V

O(AV)

I

pu(POML)

I

pu(POMH)

PSRR

DAC

∆I

α

I

o(sc)

RES

maximum deviation in output level

o(max)

ct

DAC

(THD + N)/S total harmonic

DR

DAC

DS

DAC

V

n(o)(rms)

d intermodulation

f

s(max)

B

DAC

C

L(DAC)

R

L(DAC)

= 3.3 V; unless otherwise specified.

DDA2

voltage on pin VREFDA with respect to V

impedance on pin VREFDA with respect to V

with respect to V

AC output voltage of operational

amplifiers (RMS value)

average DC output voltage of

maximum I2S-bus signal;

>5kΩ

R

L

RL>5kΩ 1.5 1.65 1.8 V

DDA2

DDA2

SSA2

− V

SSA2

47 50 53 %

− 37 − kΩ

− 37 − kΩ

0.62 0.7 0.82 V

operational amplifiers

low pull-up current to V

DDA2

on

voltage on pin POM < 0.6 V 3.3 − 5 µA

pin POM

high pull-up current to V

DDA2

on

voltage on pin POM > 0.8 V 50 − 75 µA

pin POM

powersupplyripplerejection DACs

(input via I2S-bus)

(plus or minus) of the 4 DAC

f

= 1 kHz; V

ripple

(peak value); C

ripple

VREFDA

= 100 mV

=22µF

with respect to the average of

the 4 outputs; full-scale output

45 60 − dB

−−0.38 dB

current outputs

crosstalk between all outputs in

the audio band

one output digital silence, other

three maximum volume

−−−69 dB

output short-circuit current output short-circuited to ground −−20 mA

DAC resolution 18 bits

distortion-plus-noise to signal ratio

f = 1 kHz;

V

= 0.72 V (RMS);

o(ref)

−−75 −60 dBA

A-weighted

dynamic range of DAC V

= 0.72 V (RMS);

o(ref)

90 96 − dBA

f = 1 kHz; −60 dB; A-weighted

digital silence of DAC f = 20 Hz − 17 kHz;

V

= 0.72 V (RMS);

o(ref)

−−107 −102 dBA

A-weighted

digital silence noise levelat output

A-weighted − 38µV

(RMS value)

f = 60 Hz and 7 kHz, ratio4:1 −−70 −55 dB

distortion/comparator

maximum sample frequency 48 −−kHz

bandwidth DAC at −3dB −

1

⁄2f

s

− kHz

load capacitance on DAC outputs −−2.5 nF

load resistance on DAC voltage

DC decoupled 5 −−kΩ

outputs

1999 Aug 05 32

Page 33

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

14 OSCILLATOR CHARACTERISTICS

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

f

xtal

∆f

xtal(adj)

∆f

xtal(T)

α

f

V

xtal(M)

g

m(start)

g

m(oper)

C

L

N

cy(start)

I

xtal

P

xtal

V

i(clk)

R

xtal

R

o

crystal frequency 10.000 − 19.456 MHz

crystal frequency variation with

T

=25°C −30 − +30 ppm

amb

adjustment

crystal frequency variation with

−30 − +30 ppm

temperature

spurious frequency attenuation 20 −−dB

voltage across the crystal

1.6 2.6 3.6 V

(absolute peak value)

transconductance at start-up 10.5 19 32 mS

transconductance when operating 3.6 − 38 mS

capacitive load of clock output − 15 − pF

number of cycles during start-up depends on quality of the

− 1000 − cycles

external crystal

supply current at start-up − 715mA

at oscillation − 0.6 2 mA

in slave mode − 0.65 0.9 mA

drive level at oscillation − 0.4 0.5 mW

external clock input voltage in slave mode 3 3.3 3.6 V

allowed loss resistance of the

crystal

Cp=5pF

C2 = 10 pF; see Fig.9

output resistance at start-up;

f

xtal

V

DD_OSC

(1)

; C1 = 10 pF;

= 18.432 MHz;

= 3.3 V

− 20 100 Ω

750 1300 2800 Ω

Note

1. Cpis the parasitic parallel capacitance of the crystal.

1999 Aug 05 33

Page 34

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

15 I2S-BUS TIMING CHARACTERISTICS

Timing of the serial digital data inputs and outputs (see Fig.17).

SYMBOL PARAMETER MIN. MAX. UNIT

T

cy

t

su(D)

t

h(D)

t

su(WS)

t

h(WS)

t

d(D)

t

d(WS)

bit clock cycle time 70 − ns

data set-up time (host) 32 − ns

data set-up time (I

2

S-bus) 10 − ns

data hold time (host) 5 − ns

data hold time (I

2

S-bus) 10 − ns

word select set-up time (I2S-bus) 10 − ns

word select hold time (I2S-bus) 10 − ns

data delay time (host) − 20 ns

word select delay time (host) − 15 ns

handbook, full pagewidth

WS OUT

WS IN

t

t

r

BCK

DATA IN LSB MSB

DATA OUT

BCK(H)

right

t

t

BCK(L)

t

f

T

cy

h(WS)

t

d(D)

t

su(WS)

left

t

d(WS)

t

su(D)

t

h(D)

MGS220

Fig.17 Timing definitions of the serial digital inputs and outputs.

1999 Aug 05 34

Page 35

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

16 I2C-BUS TIMING CHARACTERISTICS

2

Timing of the I

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

f

SCL

t

BUF

t

HD;STA

t

LOW

t

HIGH

t

SU;STA

t

HD;DAT

t

SU;DAT

t

r

t

f

t

SU;STO

C

b

t

SP

C-bus (see Fig.18); all values referred to VIHand VIL (see Section 12).

SCL clock frequency 0 400 kHz

busfree time between a STOPand

1.3 −µs

START condition

hold time (repeated) START

0.6 −µs

condition; after this period, the first

clock pulse is generated

LOW period of the SCL clock 1.3 −µs

HIGH period of the SCL clock 0.6 −µs

set-up time for a repeated START

0.6 −µs

condition

data hold time 0 0.9 µs

data set-up time for standard mode I2C-bus

rise time of both SDA and SCL

signals

system t

f

= 400 kHz 20 + 0.1C

SCL

f

= 100 kHz 20 + 0.1C

SCL

SU;DAT

> 250 ns

fall time of both SDA and SCL

100 − ns

(1)

300 ns

b

(1)

1000 ns

b

20 + 0.1C

(1)

b

300 ns

signals

set-up time for STOP condition 0.6 −µs

capacitive load for each bus line − 400 pF

maximum pulse width for spike

− 50 ns

suppression

Note

is the bus line capacitance in pF.

1. C

b

1999 Aug 05 35

Page 36

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

1999 Aug 05 36

SDA

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

SCL

t

BUF

P

S

t

LOW

t

HD;STA

t

r

t

HD;DAT

t

HIGH

t

f

t

SU;DAT

t

SU;STA

Sr

t

HD;STA

t

SP

t

SU;STO

MBC611

P

Fig.18 Timing definition of the I2C-bus.

handbook, full pagewidth

Page 37

Philips Semiconductors Preliminary specification

Sound effects DSP SAA7712H

17 APPLICATION INFORMATION

The application diagram (see Fig.19) must be considered as one of the examples of a (limited) application of the chip

e.g. in this case the I2S-bus inputs are not used. For the real application set-up the information of the application report

and application support by Philips are necessary on issues such as EMC, kappa reduction of the package,

DSP programming, etc.

handbook, full pagewidth

BLM32A07

+3 V

100 nF

V

DD_OSC

V

SS_OSC

RTCB

SHTCB

TSCAN

21SYS_CLK

64

61

58

59

60

11.2896 MHz

S_IN1_WS

S_IN1_BCK

2

2

I

I

27 29 28 24 26 25

OSCILLATOR

6362

OSC_IN

OSC_OUT

10 pF10 pF

S_IN1_DATA

S_IN2_WS

2

2

I

I

2

S_IN2_BCK

2

I

S_IN2_DATA

2

I

S_IO_OUT2

2

2

I

I

I2S-BUS

INPUT

SWITCH

PLL

S_IO_OUT1

SAA7712H

4847 13233556

5455

TEST2

TEST1

SSD3V5VSSD3V4

V

SSD3V3VSSD5V3

V

SSD3V2VSSD3V1

V

43495051

1 µF

S_IO_BCK

2

2

I

HOST I/O

57

DSP_RESET

S_IO_IN1

S_IO_IN2

2

I

I

3137

DSP

EQUALIZER

SSD3V6

SSD5V2

V

V

2

323036

V

S_IO_WS

I

33

SSA2

V

SSD5V1

4.7 kΩ

4.7 kΩ

+5 V

+3 V

DDA2

V

V

14

QUAD DAC

INTERFACE

SDA

DDD3V1

DDD3V2

V

53

I2C-BUS

SCL

+5 V

52

DDD5V2

V

34

444546

A0

+5 V

DDD5V3

V

42

22

19

18

16

17

12

11

9

10

15

39

40

41

20

BLM32A07

22

nF

V

DDD5V1

OUT0_V

OUT0_I

OUT1_V

OUT1_I

OUT2_V

OUT2_I

OUT3_V

OUT3_I