Page 1

INTEGRATED CIRCUITS

DATA SH EET

SAA1057

Radio tuning PLL frequency

synthesizer

Product specification

File under Integrated Circuits, IC01

November 1983

Page 2

Philips Semiconductors Product specification

Radio tuning PLL frequency synthesizer SAA1057

GENERAL DESCRIPTION

The SAA1057 is a single chip frequency synthesizer IC in

I2L technology, which performs all the tuning functions of a

PLL radio tuning system. The IC is applicable to all types

of radio receivers, e.g. car radios, hi-fi radios and portable

radios.

• On-chip programmable current amplifier (charge pump)

to adjust the loop gain.

• Only one reference frequency for both AM and FM.

• High signal purity due to a sample and hold phase

detector for the in-lock condition.

• High tuning speed due to a powerful digital memory

phase detector during the out-lock condition.

Features

• On-chip prescaler with up to 120 MHz input frequency.

• On-chip AM and FM input amplifiers with high sensitivity

(30 mV and 10 mV respectively).

• Low current drain (typically 16 mA for AM and 20 mA for

FM) over a wide supply voltage range (3,6 V to 12 V).

• Tuning steps for AM are: 1 kHz or 1,25 kHz for a VCO

frequency range of 512 kHz to 32 MHz.

• Tuning steps for FM are: 10 kHz or 12,5 kHz for a VCO

frequency range of 70 MHz to 120 MHz.

• Serial 3-line bus interface to a microcomputer.

• Test/features.

• On-chip amplifier for loop filter for both AM and FM (up

to 30 V tuning voltage).

QUICK REFERENCE DATA

Supply voltage ranges V

Supply currents I

Input frequency ranges

at pin FAM f

at pin FFM f

Maximum crystal input frequency f

Operating ambient temperature range T

CC1

V

CC2

V

CC3

CC1

I

CC3

FAM

FFM

XTAL

amb

+ I

CC2

3,6 to 12 V

3,6 to 12 V

V

to 31 V

CC2

typ. 18 mA

typ. 0,8 mA

512 kHz to 32 MHz

70 to 120 MHz

> 4 MHz

−25 to + 80 °C

PACKAGE OUTLINE

18-lead DIL; plastic (SOT102H); SOT102-1; 1996 September 2.

November 1983 2

Page 3

Philips Semiconductors Product specification

Radio tuning PLL frequency synthesizer SAA1057

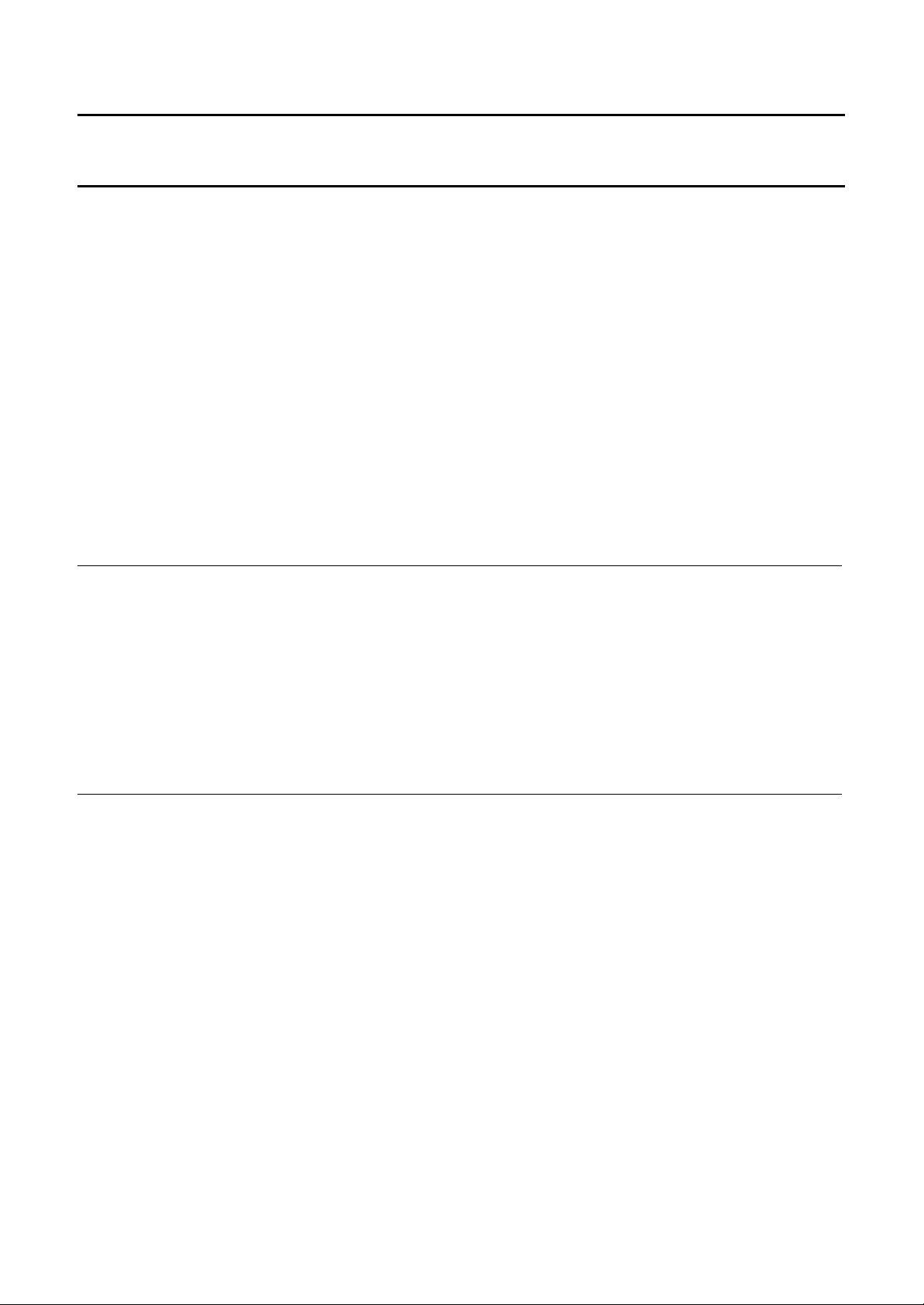

Fig.1 Block diagram.

GENERAL DESCRIPTION

The SAA1057 performs the entire PLL synthesizer

function (from frequency inputs to tuning voltage output)

for all types of radios with the AM and FM frequency

ranges.

The circuit comprises the following:

• Separate input amplifiers for the AM and FM

VCO-signals.

• A divider-by-10 for the FM channel.

• A multiplexer which selects the AM or FM input.

• A 15-bit programmable divider for selecting the required

frequency.

• A sample and hold phase detector for the in-lock

condition, to achieve the high spectral purity of the VCO

signal.

• A digital memory frequency/phase detector, which

operates at a 32 times higher frequency than the sample

and hold phase detector, so fast tuning can be achieved.

• An in-lock counter detects when the system is in-lock.

The digital phase detector is switched-off automatically

when an in-lock condition is detected.

• A reference frequency oscillator followed by a reference

divider. The frequency is generated by a 4 MHz quartz

crystal. The reference frequency can be chosen either

32 kHz or 40 kHz for the digital phase detector (that

means 1 kHz and 1,25 kHz for the sample and hold

phase detector), which results in tuning steps of 1 kHz

and 1,25 kHz for AM, and 10 kHz and 12,5 kHz for FM.

• A programmable current amplifier (charge pump), which

controls the output current of both the digital and the

sample/hold phase detector in a range of 40 dB. It also

allows the loop gain of the tuning system to be adjusted

by the microcomputer.

• A tuning voltage amplifier, which can deliver a tuning

voltage of up to 30 V.

• BUS; this circuitry consists of a format control part, a

16-bit shift register and two 15-bit latches. Latch A

contains the to be tuned frequency information in a

binary code. This binary-coded number, multiplied by

the tuning spacing, is equal to the synthesized

frequency. The programmable divider (without the fixed

divide-by-10 prescaler for FM) can be programmed in a

range between 512 and 32 767 (see Fig.3). Latch B

contains the control information.

November 1983 3

Page 4

Philips Semiconductors Product specification

Radio tuning PLL frequency synthesizer SAA1057

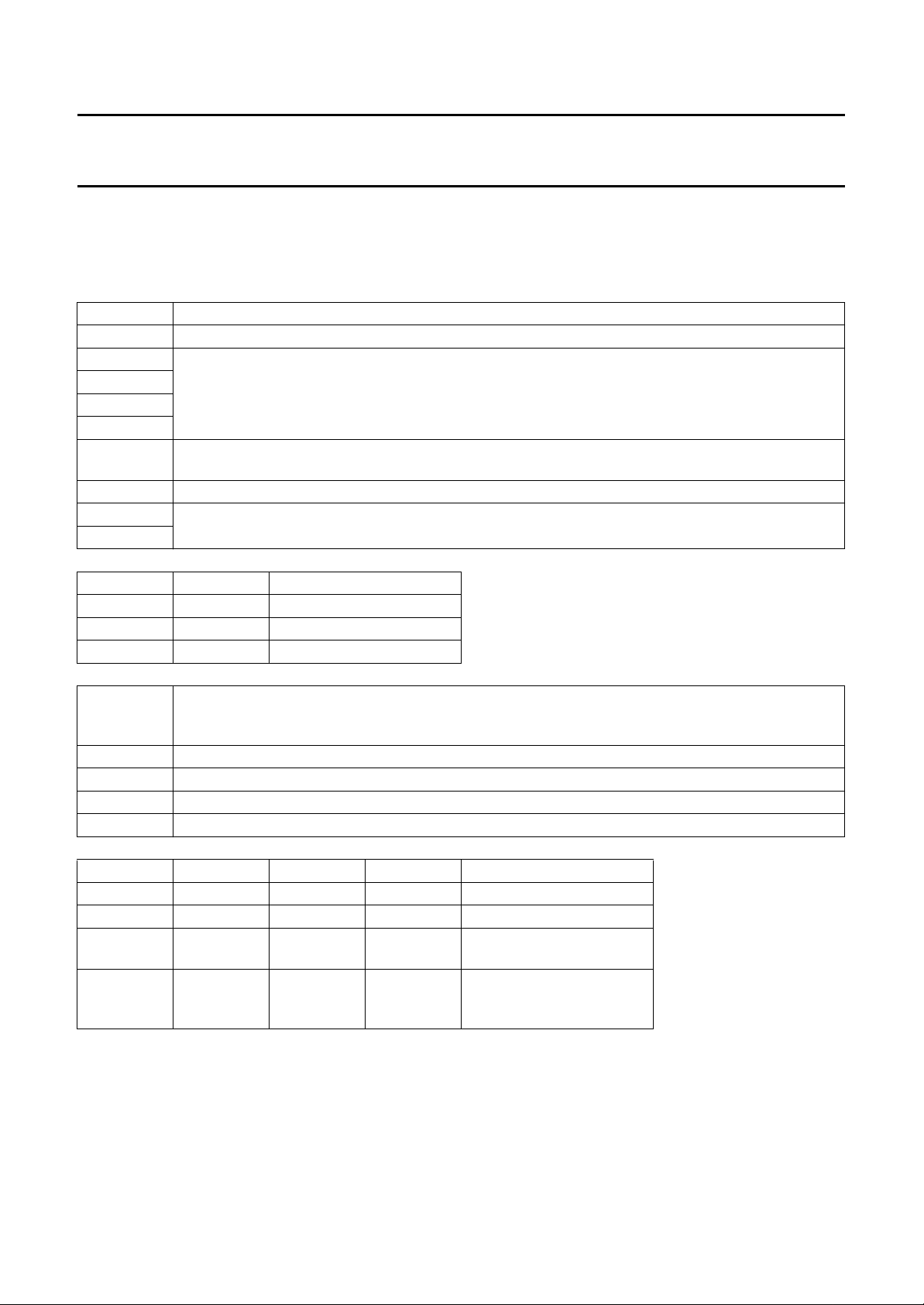

OPERATION DESCRIPTION

Control information

The following functions can be controlled with the data word bits in latch B. For data word format and bit position see

Fig.3.

FM FM/AM selection; ‘1’ = FM, ‘0’ = AM

REFH reference frequency selection; ‘1’ = 1,25 kHz, ‘0’ = 1 kHz (sample and hold phase detector)

CP3

CP2

CP1

CP0

SB2 enables last 8 bits (SLA to T0) of data word B; ‘1’ = enables, ‘0’ = disables; when programmed ‘0’, the

SLA load mode of latch A; ‘1’ = synchronous, ‘0’ = asynchronous

PDM1

PDM0

control bits for the programmable current amplifier (see section Characteristics)

last 8 bits of data word B will be set to ‘0’ automatically

phase detector mode

PDM1 PDM0 digital phase detector

0 X automatic on/off

10 on

1 1 off

BRM bus receiver mode bit; in this mode the supply current of the BUS receiver will be switched-off

automatically after a data transmission (current-draw is reduced); ‘1’ = current switched; ‘0’ = current

always on

T3 test bit; must be programmed always ‘0’

T2 test bit; selects the reference frequency (32 or 40 kHz) to the TEST pin

T1 test bit; must be programmed always ‘0’

T0 test bit; selects the output of the programmable counter to the TEST pin

T3 T2 T1 T0 TEST (pin 18)

00001

0 1 0 0 reference frequency

0 0 0 1 output programmable

counter

0 1 0 1 output in-lock counter

‘0’ = out-lock

‘1’ = in-lock

November 1983 4

Page 5

Philips Semiconductors Product specification

Radio tuning PLL frequency synthesizer SAA1057

(1) During the zero set-up time (t

used for other devices on the same data and clock lines.

) CLB can be LOW or HIGH, but no transient of the signal is permitted. This can be of use when an I2C bus is

LZsu

Fig.3 Bit organization of data words A and B.

Fig.2 BUS format.

November 1983 5

Page 6

Philips Semiconductors Product specification

Radio tuning PLL frequency synthesizer SAA1057

PINNING

1TR

2 TCA

resistor/capacitors for sample and hold

circuit

3 TCB

4 DCS decoupling of supply

5 IN input of output amplifier

6 OUT output of output amplifier

7V

positive supply voltage of

CC3

output amplifier

8 FFM FM signal input

9V

positive supply voltage of

CC1

high frequency logic part

10 DCA decoupling of input

amplifiers

11 FAM AM signal input

12 DATA

13 DLEN

BUS

14 CLB

15 V

16 V

ground

EE

positive supply voltage of low frequency

CC2

logic part and analogue part

17 XTAL reference oscillator input

18 TEST test output

Fig.4 Pinning diagram.

RATINGS

Limiting values in accordance with the Absolute Maximum System (IEC 134)

Supply voltage; logic and analogue part V

Supply voltage; output amplifier V

Total power dissipation P

Operating ambient temperature range T

Storage temperature range T

CC1

CC3

tot

amb

stg

November 1983 6

; V

CC2

−0,3 to 13,2 V

V

to +32 V

CC2

max. 800 mW

−30 to +85 °C

−65 to +150 °C

Page 7

Philips Semiconductors Product specification

Radio tuning PLL frequency synthesizer SAA1057

CHARACTERISTICS

= 0 V; V

V

EE

Supply voltages V

Supply currents

AM mode I

FM mode I

Operating ambient

temperature T

RF inputs (FAM, FFM)

AM input frequency f

FM input frequency f

Input voltage at FAM V

Input voltage at FFM V

Input resistance at FAM R

Input resistance at FFM R

Input capacitance at FAM C

Input capacitance at FFM C

Voltage ratio allowed

between selected and

non-selected input V

Crystal oscillator (XTAL)

Maximum input frequency f

Crystal series resistance R

BUS inputs (DLEN, CLB, DATA)

Input voltage LOW V

Input voltage HIGH V

Input current LOW −I

Input current HIGH I

BUS inputs timing

(DLEN, CLB, DATA) note 2

Lead time for CLB to DLEN t

Lead time for DATA to

the first CLB pulse t

Set-up time for DLEN

to CLB t

CLB pulse width HIGH t

CLB pulse width LOW t

CC1

= V

(6)

CC2

= 5 V; V

CC3

= 30 V; T

= 25 °C; unless otherwise specified

amb

SYMBOL MIN. TYP. MAX. CONDITIONS

CC1

V

CC2

V

CC3

tot

tot

I

CC3

amb

FAM

FFM

i (rms)

i (rms)

i

i

i

i

s/Vns

3,6 5 12 V

3,6 5 12 V

V

CC2

− 16 − mA

− 20 − mA

0,3 0,8 1,2 mA I

− 31 V

I

= I

tot

BRM = ‘1’; PDM = ‘0’

OUT

−25 − +80 °C

512 kHz − 32 MHz

70 − 120 MHz

30 − 500 mV

10 − 500 mV

− 2 − kΩ

− 135 −Ω

− 3,5 − pF

− 3 − pF

−−30 − dB

see note 1

XTAL

s

IL

IH

IL

IH

4 −− MHz

−−150 Ω

0 − 0,8 V

2,4 − V

CC1

V

−−10 µAVIL= 0,8 V

−−10 µAVIH= 2,4 V

see also Fig.2 and

CLBlead

Tlead

CLBlag1

CLBH

CLBL

1 −− µs

0,5 −− µs

5 −− µs

5 −− µs

5 −− µs

CC1

= 0

+ I

CC2

in-lock:

November 1983 7

Page 8

Philips Semiconductors Product specification

Radio tuning PLL frequency synthesizer SAA1057

SYMBOL MIN. TYP. MAX. CONDITIONS

Set-up time for DATA

to CLB t

Hold time for DATA to CLB t

Hold time for DLEN to CLB t

DATAlead

DATAhold

DLENhold

Set-up time for DLEN to

CLB load pulse t

CLBlag2

Busy time from load pulse

to next start of transmission t

DIST

Busy time or

asynchronous mode t

synchronous mode t

DIST

DIST

2 −− µs

0 −− µs

2 −− µs

2 −− µs

next transmission after

5 −− µs

word ‘B’ to other device

0,3 −− ms next transmission to

1,3 −− ms

SAA1057 after word

‘A’ (see also note 5)

Sample and hold circuit

(TR, TCA, TCB) see also notes 3; 4

,

Minimum output voltage V

Maximum output voltage V

Capacitance at TCA C

(external) C

Discharge time at TCA t

Resistance at TR R

V

V

t

TCA

TCB

TCA

TCB

TCA

TCA

dis

dis

TR

− 1,3 − V

,

−−V

−0,7 V

CC2

−−2,2 nF REFH = ‘1’

−−2,7 nF REFH = ‘0’

−−5 µs REFH = ‘1’

−−6,25 µs REFH = ‘0’

100 −− Ωexternal

Voltage at TR during

discharge V

Capacitance at TCB C

Bias current into TCA, TCB I

TR

TCB

bias

− 0,7 − V

−−10 nF external

−−10 nA in-lock

Programmable current amplifier

(PCA)

Output current of the

dig. phase detector ± I

dig

− 0,4 − mA

Current gain of PCA

CP3 CP2 CP1 CP0

P1 0 0 0 0 G

P2 0 0 0 1 G

P3 0 0 1 0 G

P4 0 1 1 0 G

P5 1 1 1 0 G

P1

P2

P3

P4

P5

− 0,023 − V

− 0,07 −

− 0,23 −

− 0,7 −

− 2,3 −

≥ 5 V (only for P1)

CC2

November 1983 8

Page 9

Philips Semiconductors Product specification

Radio tuning PLL frequency synthesizer SAA1057

SYMBOL MIN. TYP. MAX. CONDITIONS

Ratio between the output

current of S/H into PCA

and the voltage on

C

TCB

S

Offset voltage on TCB ∆V

Output amplifier (IN, OUT)

Input voltage V

Output voltages

minimum V

maximum V

maximum V

Maximum output current ± I

Test output (TEST)

(7)

Output voltage LOW V

Output voltage HIGH V

Output current OFF I

Output current ON I

Ripple rejection

at f

ripple

/∆V

∆V

CC1

/∆V

∆V

CC2

/∆V

∆V

CC3

(8)

= 100 Hz

OUT

OUT

OUT

Toff

Ton

TCB

TCB

IN

OUT

OUT

OUT

OUT

TL

TH

− 1,0 −µA/V

−−1 V in-lock

− 1,3 − V in-lock; equal to

internal reference

voltage

−−0,5 V −I

V

−2 −− VI

CC3

V

−1 −− VI

CC3

5 −− mA V

OUT

OUT

OUT

OUT

= 1 mA

= 1 mA

= 0,1 mA

=1⁄2 V

CC3

−−0,5 V

−−12 V

−−10 µAV

150 −− µAV

TH

TL

− 77 − dB

− 70 − dB

− 60 − dB V

OUT

≤ V

CC3

−3 V

November 1983 9

Page 10

Philips Semiconductors Product specification

Radio tuning PLL frequency synthesizer SAA1057

Notes

1. Pin 17 (XTAL) can also be used as input for an external clock.

The circuit for that is given in Fig.5. The values given in Fig.5 are a typical application example.

2. See BUS information in section ‘operation description’.

3. The output voltage at TCB and TCA is typically1⁄2 V

hold phase detector. The control voltage at TCB is defined as the difference between the actual voltage at TCB and

the value calculated from the formula1⁄2 V

4. Crystal oscillator frequency f

XTAL

= 4 MHz.

CC2

+0,3 V.

5. The busy-time after word “A” to another device which has more clock pulses than the SAA1057 (>17) must be the

same as the busy-time for a next transmission to the SAA1057.

When the other device has a separate DLEN or has less clock pulses than the SAA1057 it is not necessary to keep

to this busy-time, 5 µs will be sufficient.

6. When the bus is in the active mode (see BRM in Control Information), 4,5 mA should be added to the figures given.

7. Open collector output.

8. Measured in Fig.6.

+0,3 when the tuning system is in-lock via the sample and

CC2

Fig.5 Circuit configuration showing external 4 MHz clock.

APPLICATION INFORMATION

Initialize procedure

Either a train of at least 10 clock pulses should be applied to the clock input (CLB) or word B should be transmitted, to

achieve proper initialization of the device.

For the complete initialization (defining all control bits) a transmission of word B should follow. This means that the IC is

ready to accept word A.

Synchronous/asynchronous operation

Synchronous loading of the frequency word into the programmable counter can be achieved when bit ‘SLA’ of word B is

set to ‘1’. This mode should be used for small frequency steps where low tuning noise is important (e.g. search and

manual tuning). This mode should not be used for frequency changes of more than 31 tuning steps. In this case

asynchronous loading is necessary. This is achieved by setting bit ‘SLA’ to ‘0’. The in-lock condition will then be reached

more quickly, because the frequency information is loaded immediately into the divider.

Restrictions to the use of the programmable current amplifier

The lowest current gain (0,023) must not be used in the in-lock condition when the supply voltage V

is below 5 V (CP3,

CC2

CP2, CP1 and CP0 are all set to ‘0’). This is to avoid possible instability of the loop due to a too small range of the sample

and hold phase detector in this condition (see also section ‘Characteristics’).

November 1983 10

Page 11

Philips Semiconductors Product specification

Radio tuning PLL frequency synthesizer SAA1057

Transient times of the bus signals

When the SAA1057 is operating in a system with continuous activity on the bus lines, the transient times at the bus inputs

should not be less than 100 ns. Otherwise the signal-to-noise ratio of the tuning voltage is reduced.

(1) Values depend on the tuner diode characteristics.

Fig.6 Application example of the SAA1057PLL frequency synthesizer module.

November 1983 11

Page 12

Philips Semiconductors Product specification

Radio tuning PLL frequency synthesizer SAA1057

PACKAGE OUTLINE

DIP18: plastic dual in-line package; 18 leads (300 mil)

D

seating plane

L

Z

18

pin 1 index

e

b

SOT102-1

M

E

A

2

A

A

1

w M

b

1

b

2

10

E

c

(e )

1

M

H

1

0 5 10 mm

scale

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

A

A

A

UNIT

max.

mm

inches

Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

OUTLINE

VERSION

SOT102-1

12

min.

max.

IEC JEDEC EIAJ

b

1.40

1.14

0.055

0.044

b

1

0.53

0.38

0.021

0.015

b

cD E e M

2

0.32

1.40

0.23

1.14

0.013

0.055

0.009

0.044

REFERENCES

21.8

21.4

0.86

0.84

November 1983 12

9

(1) (1)

6.48

6.20

0.26

0.24

L

e

1

M

3.9

8.25

3.4

7.80

0.15

0.32

0.13

0.31

EUROPEAN

PROJECTION

E

0.37

0.33

H

9.5

8.3

w

max.

0.2542.54 7.62

0.854.7 0.51 3.7

0.010.10 0.30

0.0330.19 0.020 0.15

ISSUE DATE

93-10-14

95-01-23

(1)

Z

Page 13

Philips Semiconductors Product specification

Radio tuning PLL frequency synthesizer SAA1057

SOLDERING

Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and

surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for

surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often

used.

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our

“IC Package Databook”

Soldering by dipping or by wave

The maximum permissible temperature of the solder is 260 °C; solder at this temperature must not be in contact with the

joint for more than 5 seconds. The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the

specified maximum storage temperature (T

be necessary immediately after soldering to keep the temperature within the permissible limit.

(order code 9398 652 90011).

). If the printed-circuit board has been pre-heated, forced cooling may

stg max

Repairing soldered joints

Apply a low voltage soldering iron (less than 24 V) to the lead(s) of the package, below the seating plane or not more

than 2 mm above it. If the temperature of the soldering iron bit is less than 300 °C it may remain in contact for up to

10 seconds. If the bit temperature is between 300 and 400 °C, contact may be up to 5 seconds.

DEFINITIONS

Data sheet status

Objective specification This data sheet contains target or goal specifications for product development.

Preliminary specification This data sheet contains preliminary data; supplementary data may be published later.

Product specification This data sheet contains final product specifications.

Limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or

more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation

of the device at these or at any other conditions above those given in the Characteristics sections of the specification

is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information

Where application information is given, it is advisory and does not form part of the specification.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these

products can reasonably be expected to result in personal injury. Philips customers using or selling these products for

use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such

improper use or sale.

November 1983 13

Loading...

Loading...