Page 1

FEATURES

• SMBus 1.0 Compliant

• Support Pentium class and x86-based designs

• PMU, GPIO, and Alternative PMU modes

• WAKE output and Suspend Status input operates

synchronously with PMU in notebook chipsets

• LOW power-saving Suspend mode

• Hardware Debounced Wakeup/Suspend input as

pushbutton

• 4 Power Control programmable outputs with built-

in Power Sequencing at 10 ms to 1 second

programmable intervals

• Optional Wakeup-Disable inputs

• Optional Power-On inputs

• 8 programmable interrupt inputs for SMIEVENT

or SMBALERT#

• 8 Suspend/Wakeup edge-triggered

programmable inputs

• 20 possible programmable edge-sensitive

General Purpose Inputs/Outputs

• 8 Auto LED Flash(ALF) programmable outputs

with 10% or 50% duty cycles

• LOW power hardware driven speaker alarm

output

• Up to 6 programmable unique addresses for

device cascade

• 8 power-on modularized hardware ID

programmable inputs

• 32KHz operating frequency

• 5 V tolerant inputs

• Supports both 3.3 V and 5 V operating

environments

• Software programming kit available

ORDERING INFORMATION

OZ990S - 28 SSOP

OZ990

Intelligent Manager

Smart PMU/GPIO

GENERAL DESCRIPTION

Micro’s OZ990 Smart PMU/GPIO (Power

O

2

Management Unit/General Purpose Input Output) unit

allows the implementation of Green PC Desktop

Chipsets in notebook designs at considerably lower

cost than conventional methods while closing the

technology gap between desktop and notebook

computers by offering an extensive number of

powerful power management and general purpose I/O

features. With the OZ990 stand-alone PMU capability,

the ability to provide the One-Shot Design for

PMU/BIOS practically eliminates the need to redesign

PMUs to match the ever-changing core logic chipsets.

The OZ990 provides the perfect solution for leading

notebook vendors to stay ahead of the competition.

The OZ990 is an SMBus 1.0 compliant device with 4

Power Control and 16 Programmable General

Purpose I/Os pins flexible for a variety of functions

such as Power Control with sequencing,

programmable inputs/outputs, SMB/SMI interrupt

service, power-saving, Suspend/Wakeup,

modularized hardware ID, and Auto LED Flash (ALF)

status display. Other features include hardware-driv en

speaker alarm output and Suspend/Wakeup button.

As a Pentium class and x86-based system compatible

device, the OZ990 is a highly cost-effective and

practical solution for today’s notebook and palmtop

computers, pen-based data systems, personal digital

assistants, and portable data-collection terminals.

07/13/00 OZ990-SF-1.6 Page 1

Copyright 1998 by O

Micro All Rights Reserved

2

Page 2

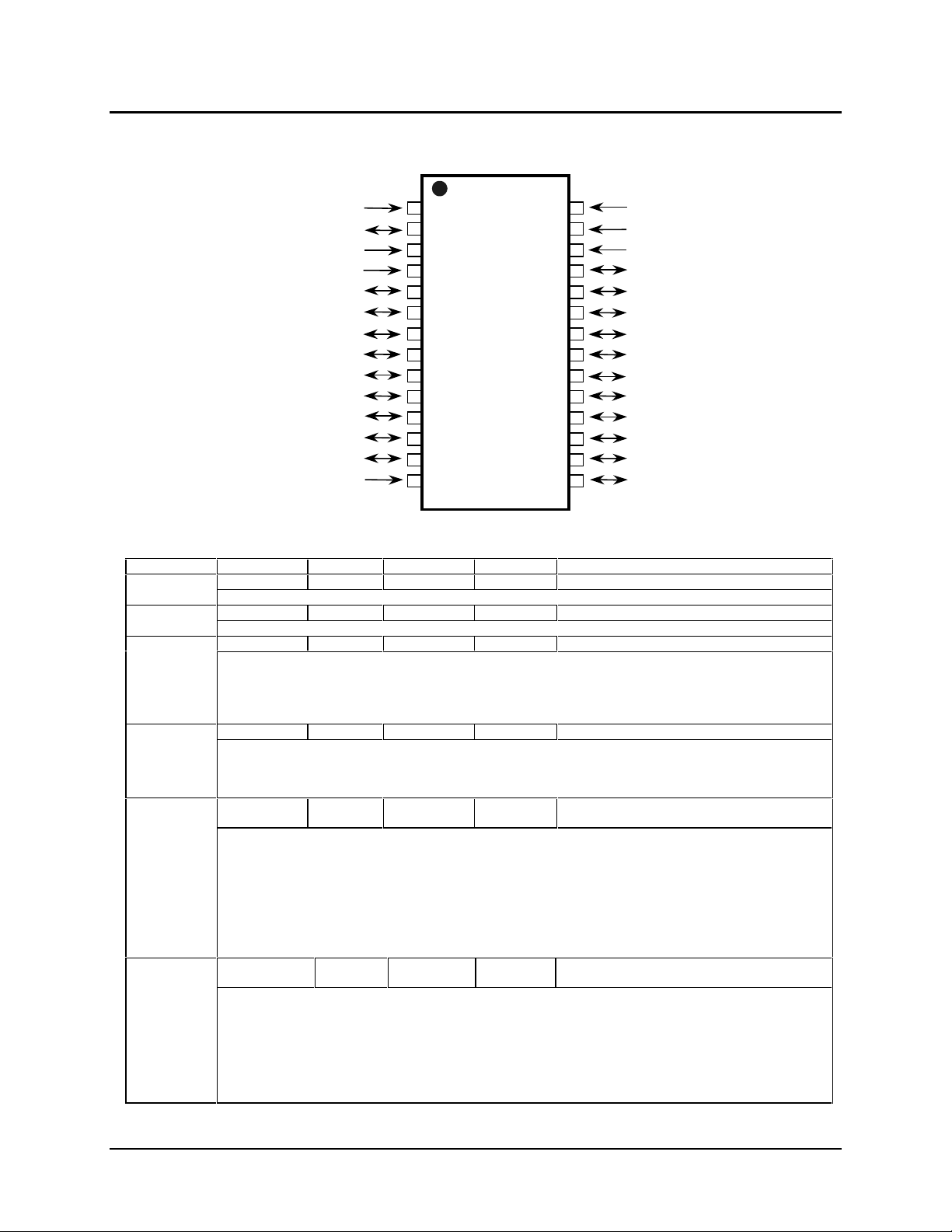

PIN ASSIGNMENT

OZ990

SMBCLK

SMBDATA

PWRGD

MODE

PC[0] / GPIO[16]

PC[1] / GPIO[17]

PC[2] / GPIO[18]

PC[3] / GPIO[19]

GPIO[0] / SMIEVENT

GPIO[1] / WAKE

GPIO[2] / SMBALERT#

GPIO[3]

GPIO[4]

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

VCC

32KHZ

RESETN

SRBTN # / GPIO[15]

GPIO[14]

GPIO[13]

GPIO[12]

GPIO[11]

GPIO[10]

GPIO[9]

GPIO[8]

SMBIDSEL[2] / GPO[7]

SMBIDSEL]1] / GPO[6]

SMBIDSEL[0] / GPO [5]

PIN CONFIGURATION

Name Pin No. Type Input Drive Definition

SMBCLK

1 I TTL SMBus Cl ock Input for SMBus protoc ol communicati on.

SMBDATA

2 I/O TTL 12mA

SMBus Dat a Input/Output for SMBus prot ocol communication.

PWRGD

3 I TTL -

This pin indicates that t he host system’s power, including the Core Logic c hipset s, is st able. Before t he host

system’s power is stable, this input pin will tri-state all the output pins from OZ990 with the exception of the

Power Control pins. The state of the PW RGD pin determines whether the OZ990 is in PMU or Alt ernate

PMU mode when RESETN is active. When pin MODE=1 and pin PW RGD=0, the OZ990 is in PMU mode.

When pin MODE=1 and pin PWRGD=1, the OZ990 is in Alternate PMU mode.

MODE

4 I TTL -

The OZ990 has 3 modes of operation: GP IO(with 20 GPIOs available), PMU(with 16 GPIOs available), and

Alternate PMU(with 16 GPIOs available). To use the OZ990 as a PMU, tie MODE pin to VDD and set

PWRGD LOW . For Alternate PMU mode, tie MODE pin to VDD and set PW RGD HIGH. For GPIO-only

mode, tie MODE pin LOW. Refer to MODE descript i on for more details.

PC[3:0]/

[8:5] I/O TTL 4mA

GPIO[19:16]

Pins PC[3:0]/GPIO[19:16] can be used as Power Control out put s for cold start, reset, Suspend, and Wakeup

or as regular GPIOs. Upon power up, if the OZ990 is in PMU mode, PC[3:0] will default to 0, with OZ990

initially in Suspend mode. B y default, on a falling edge-triggered S RBTN#/GP IO[ 15] (with Wakeup function),

PC[3:0] will be set to 1 to power on the sys tem. On a subsequent trigger of GPIO[15:8]’s Sus pend and

Wakeup functions , the values in PC_SUSPEND[3:0] and PC_W AKE[ 3:0] in register 0Bh will be copied onto

the PC[3:0] output pins. Additionally, the OZ990 provides a power sequencing feature that allows up to 8

different programmabl e values of staggering time for t he PC[3:0] outputs. PC[3:0] are also programmable

just like t he GPIO[19:16] pins but with bits PCI[3:0] in regis ter 0Bh as input data and PCO[3:0] i n register

0Ch as output data values.

GPIO[0]/

9 I/O TTL 4mA

SMIEVENT

Fully programmable GPIOs that can be used for a variety of dedicated or specific funct i ons. Pin GPIO[0] has

SMIEVENT output as an alt ernate function. GPIO[0] defaults as outputs in PMU mode, and as input in

Alternate PMU and GPIO modes . It is also program mable to funct ion as either GPI[0] input, GPO[0]output ,

ALF[0] output, PWRON input, WAKE_DIS input, or ID[0] input (in Alternate PMU and GPIO modes). When

implementing as ID[0] input, GPIO[0]/SMIEVENT pin is internally latched from external pull-ups or pulldowns, when RESETN is LOW. The values will be stored permanently in the ID Register and

GPIO[0]/SMIEVENT pin can then be reconfigured as an out put. Refer to GPIO Config.1&2 Registers for

more details and GPIO Confi g. Tables for input/output s el ections.

SMBus Clock Input

SMBus Data Input/Output

Host System Power Good

OZ990 Mode Input

Power Control Outputs /

General Purpose I/Os

General Purpose I/O /

SMIEVENT

OZ990-SF-1.6 Page 2

Page 3

Name Pin No. Type Input Drive Definition

GPIO[1]/

WAKE

GPIO[2]/

SMBALERT#

GPIO[4:3]

SMBIDSEL

[2:0]/

GPO[7:5]

GPIO[14:8]

SRBTN#/

GPIO[15]

RESETN

32KHz

GND

VCC

10 I/O TTL 4mA

Fully programmable GPIO t hat can be used for a vari ety of dedicated or specif ic functions . Pin GPIO[1] has

WAKE output as an alternate f unction. GPIO[ 1] pin defaults as W AKE output in PMU mode, and as input in

Alternate PMU and GPIO modes. It is als o programm able to function as GPI[1] input, GPO[1] output, ALF[1]

output, PWRON input, WAKE_DIS input, or ID[1] input. W hen implementing as I D[1] input, GPIO[1]/W AKE

pin is internally latched from external pull-ups or pull-downs, when RESETN is LOW. The values will be

stored permanently in the ID Register and GPIO[ 1]/W AKE pin can then be reconf igured as an output. Refer

to GPIO Config.1&2 Regist ers for more details and GPI O Conf i g. Tables for input/output s el ections.

11 I/O TTL 4mA

Fully programmable GPIO that can be used for a variety of dedicated or specific functions. Pin GPIO[2]

defaults as input in all modes. This pin, when programmed as an alternate function, can generate the

SMBALERT# interrupt. SMBALERT# is an i nterrupt service reques t signal to t he SMBus Host which c an be

generated by all devices connected to the OZ990. Pin GPIO[2]/SMBALERT# is also programmable to

function as either GPI[2] input, GPO[2] output, ALF[2] output, PWRON input, WAKE_DIS input, or ID[2] input.

When im plementing as ID[2] input , GPIO[2]/SMBALERT# pin is internally latched from external pull-ups or

pull-downs, when RESETN is LOW. The lat ched values will be stored permanently in the ID Register and

GPIO[2] pin can then be reconf i gured as an output. Refer to GPIO Conf i g. 1&2 Registers for more detai ls and

GPIO Config. Tables for I/O selections.

[13:12] I/O TTL 4mA

Fully programmable GPIOs that can be used f or a variety of dedicat ed or specifi c functions . Pins GP IO[4:3]

default as inputs in all m odes. They are programmable to functi on as GPI[4:3] inputs, GPO[4:3] outputs,

ALF[4:3] outputs, PWRON inputs, WAKE_DIS inputs, or ID[4:3] inputs. When implemented as ID[4:3] inputs,

GPIO[4:3] pins are internally latched from external pull-ups or pull-downs, when RESETN is LOW. The

values will be stored permanently in the ID Register. GPIO[4:3] pins can then be reconfigured as out puts.

Refer to GPIO Config.1&2 Regis ters for more details and GP IO Config. Tables for input/output selections.

[17:15] I/O-U TTL 4mA

Fully programmable GPIO that can be used for a variety of dedicated or specific functions. Pin

SMBIDSEL[2:0]/GPO[7:5] defaults as an input in all m odes. Upon power on, when RESETN is LOW, these

pins are internally latched to det ermine which SMBus address is used for the OZ990. It is also programmable

to function as either GPO[ 7: 5] or ALF[7:5] outputs.

[24:18] I/O TTL 4mA

Fully programmable GPIOs that can be us ed for a vari ety of dedi cat ed or specific funct ions . Pins GPIO[14: 8]

default as inputs in all m odes. Pins GP IO[14:8] as inputs are programm able to generate SMI/SMB interrupts

and WAKE signal(pin GPIO[1]), to enter Suspend mode, or to resume Wakeup mode from Suspend

(with/without interrupt generation). They are also program mable to function as GPI[14:8] inputs , GPO[14:8]

outputs, PWRON inputs , or WAKE_DIS inputs. Refer to GPIO Config.1&2 Registers for more details and

GPIO Config. Tables for input / output selections.

25 I/O TTL 4mA

Fully programmable GPIO that can be used for a variety of dedicated or specific functions. In PMU mode, this

pin defaults as SRBTN# with a debounc ed input with “Wakeup” function triggered on the falling edge t o turn

on pins PC[3:0] (PC[3:0]=1). This pin can be tied to a pushbutton to toggle between Suspend/Wakeup

modes. In Alternat e PMU and GPIO modes, pin GPIO[15] def aults as input. This pin is program mable to

generate an SMB/SMI interrupt and WAKE signal(pin GPIO[ 1]), to enter Suspend mode, resume Wakeup

mode from Suspend (with/without interrupt generati on). This pin is als o program m able t o functi on as GPI[15]

input, GPO[15] output, PWRON input, or WAKE_DIS input . Refer to GPIO Config.1&2 Registers for more

details and GPIO Config. Tables for input/output selec tions.

26 I TTL OZ990 hardware reset. RESETN(active LOW) resets all registers to their default values. This pin is

connected to the RC delay from the power supplied to OZ990.

27 I TTL 32KHz Clock Input.

14 GND - Ground.

28 PWR - -

3.3V or 5V Power Supply.

General Purpose I/O /

WAKE

General Purpose I/O /

SMBALERT#

General Purpose I/Os

SMBus ID Selects/

General Purpose Outputs

General Purpose I/Os

Suspend/Resume Button /

General Purpose I/O

Reset

32KHz Clock Input

Ground

3.3V/5V Power Supply

OZ990

OZ990-SF-1.6 Page 3

Page 4

OZ990

GPIO PINS ALTERNATE USAGE

Name Default Usage Alternate Usage

PMU Mode Alt PMU mode GPIO mode

MODE=1

PWRGD=0

PC[0] / GPIO[16] PCO[0] PCO[0] GPI[16] GPI[16], GPO[16]

PC[1] / GPIO[17] PCO[1] PCO[1] GPI[17] GPI[17], GPO[17]

PC[2] / GPIO[18] PCO[2] PCO[2] GPI[18] GPI[18], GPO[18]

PC[3] / GPIO[19] PCO[3] PCO[3] GPI[19] GPI[19], GPO[19]

GPIO[0]/SMIEVENT GPO[0] (SMIEVENT) GPI[0] GPI[0] GPI[0], GPO[0]

GPIO[1]/WAKE GPO[1] (WAKE) GPI[1] GPI[1] GPI[1], GPO[1]

GPIO[2]/SMBALERT# GPI[2] GPI[2] GPI[2] SMBALERT#

GPIO[3] GPI[3] GPI[3] GPI[3] GPO[3]

GPIO[4] GPI[4] GPI[4] GPI[4] GPO[4]

SMBIDSEL[0]/GPO[5] GPI[5] GPI[5] GPI[5] GPO[5]

SMBIDSEL[1]/GPO[6] GPI[6] GPI[6] GPI[6] GPO[6]

SMBIDSEL[2]/GPO[7] GPI[7] GPI[7] GPI[7] GPO[7]

GPIO[8] GPI[8] GPI[8] GPI[8] GPO[8]

GPIO[9] GPI[9] GPI[9] GPI[9] GPO[9]

GPIO[10] GPI[10] GPI[10] GPI[10] GPO[10]

GPIO[11] GPI[11] GPI[11] GPI[11] GPO[11]

GPIO[12] GPI[12] GPI[12] GPI[12] GPO[12]

GPIO[13] GPI[13] GPI[13] GPI[13] GPO[13]

GPIO[14] GPI[14] GPI[14] GPI[14] GPO[14]

SRBTN#/GPIO[15] GPI[15] (has ‘Wake-

up’ function)

Note: GPI[15:8] are SMI/SMB interruptible.

MODE=1

PWRGD=1

GPI[15] GPI[15] GPO[15]

MODE=0

ALF[0]

ID[0]

DIS_WAKE

PWRON

ALF[1]

ID[1]

DIS_WAKE

PWRON

GPO[2]

ALF[2]

ID[2]

DIS_WAKE

PWRON

ALF[3]

ID[3]

DIS_WAKE

PWRON

ALF[4]

ID[4]

DIS_WAKE

PWRON

ALF[5]

ALF[6]

ALF[7]

DIS_WAKE

PWRON

DIS_WAKE

PWRON

DIS_WAKE

PWRON

DIS_WAKE

PWRON

DIS_WAKE

PWRON

DIS_WAKE

PWRON

DIS_WAKE

PWRON

DIS_WAKE

PWRON

OZ990-SF-1.6 Page 4

Page 5

OZ990 PACKAGE INFORMATION

SSOP

E H

e

PACKAGE

(209 mil)

OZ990

INCHES MILLIMETERS DIM

MIN MAX MIN MAX

A 0.084 2.13

A1 0.002 0.010 0.05 0.25

B 0.009 0.015 0.22 0.38

C 0.004 0.008 0.09 0.20

D 0.390 0.413 9.90 10.50

E 0.197 0.220 5.00 5.60

e 0.0256 0.65

H 0.291 0.323 7.40 8.20

L 0.025 0.041 0.63 1.03

α 0° 8° 0° 8°

D

B

A1

A

D

C

L

OZ990-SF-1.6 Page 5

Loading...

Loading...