Page 1

NTE7115

Integrated Circuit

Color TV Horizontal Combination Circuit

Description:

The NTE71115 is a monolithic integrated circuit in a 18–Lead DIP type package designed for use in

color television receivers.

Features:

D Positive Video Input: Capacitively Coupled (Source Impedance < 200Ω)

D Adaptive Sync Separator: Slicing Level at 50% of Sync Amplitude

D Internal Vertical Pulse Separator

D Output Stage for Vertical Sync Pulse or Composite Sync Depending on the Load; Both are

Switched OFF at Muting

D ö

D Coincidence Detector ö

Phase Control Between Horizontal Sync and Oscillator

1

for Automatic Time Constant Switching; Overruled by the VCR Switch

3

D Time Constant Switch Between Two External Time Constants for Loop Gain; Both Controlled

by the Coincidence Detector ö

D ö

Gating Pulse Controlled by Coincidence Detector ö

1

D Mute Circuit Depending on TV Transmitter Identification

D ö

Phase Control Between Line Flyback and Oscillator; the Slicing Levels for ö2 Control and

2

Horizontal Blanking can be set Separately

D Burst Keying and Horizontal Blanking Pulse Generation, in Combination with Clamping of the

Vertical Blanking Pulse (Three–Level Sandcastle)

D Horizontal Drive Output with Constant Duty Cycle Inhibited by the Protection Circuit or the

Supply Voltage Sensor

D Detector for Too Low Supply Voltage

D Protection Circuit for Switching Off the Horizontal Drive Output Continuously if the Input Voltage

is Below 4V or Higher than 8V

D Line Flyback Control Causing the Horizontal Blanking Level at the Sandcastle Output Continuously

in Case of a Missing Flyback Pulse

D Spot Suppressor Controlled by the Line Flyback Control

w

/Double Slope Integrator

3

3

Applications:

D Television Receivers

D Video Receivers

Page 2

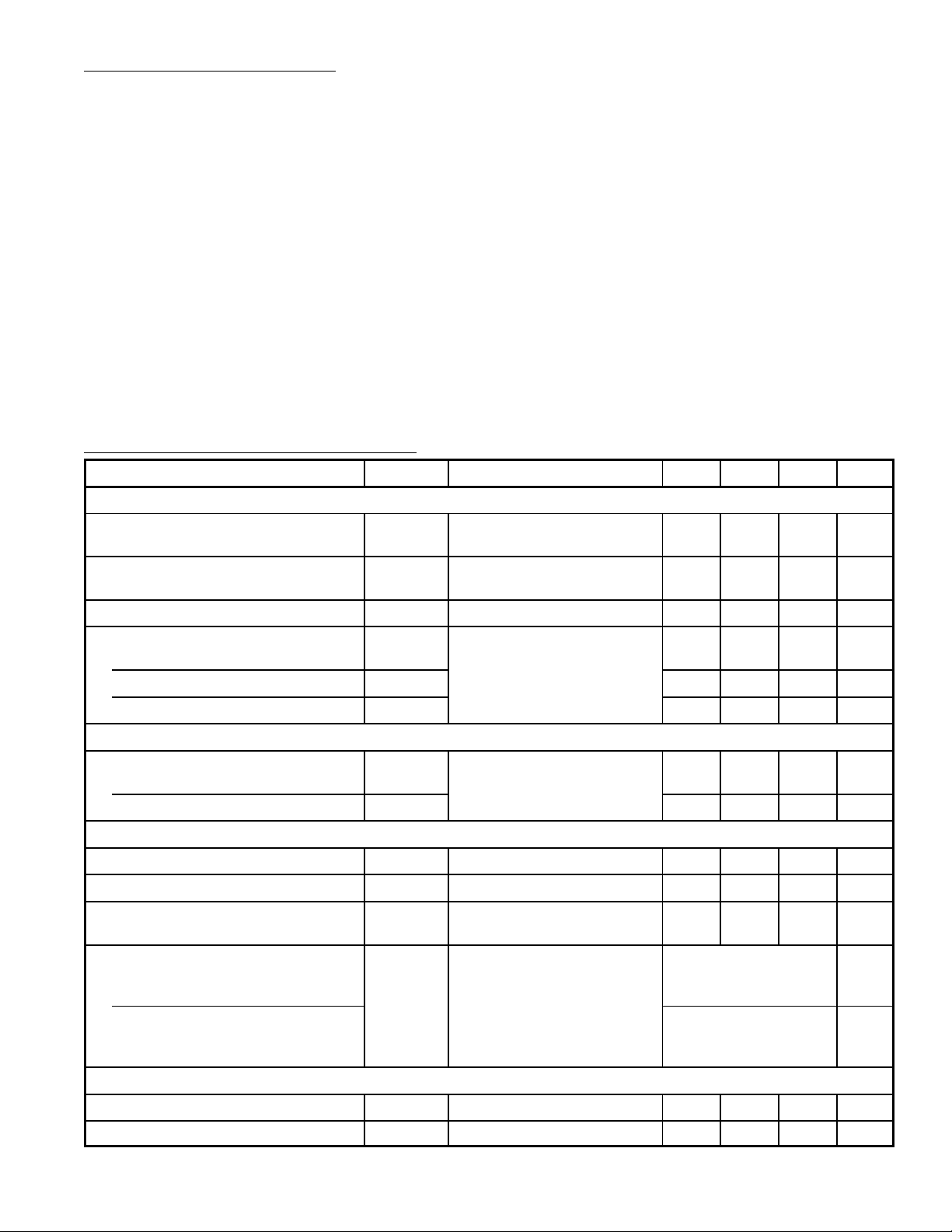

Absolute Maximum Ratings:

Supply Voltage (Pin19), V

15–5

= V

CC

Voltages at:

(Pin1, Pin4, and Pin7), V

(Pin8, Pin13, and Pin18), V

(Pin11 (Range)), V

11–5

1–5

, V

8–5

4–5

, V

, V

13–5

Currents at:

Pin1, I

Pin2 (Peak Value), ±I

Pin4, I

Pin6 (Peak Value), ±I

Pin7, I

Pin8 (Range), I

Pin9 (Range), I

Pin18, ±I

Total Power Dissipation, P

1

2M

4

6M

7

8

9

18

TOT

Operating Ambient Temperature Range, T

Storage Temperature Range, T

stg

A

7–5

, V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

18–5

13.2V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

18V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

V

CC

–0.5 to +6.0V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

100mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

–5 to +1mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

–10 to +3mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

800mW. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

–0° to +70°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

–65° to +150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DC and AC Electrical Characteristics:

Parameter Symbol Test Conditions Min Typ Max Unit

Composite Video Input and Sync Separator, Pin11 (Internal Black Level Determination)

Input Signal (Positive Video; Standard

Signal; Peak–to–Peak Value)

Sync Pulse Amplitude (Independent of

Video Content)

Generator Resistance R

Input Current During

Video

Sync Pulse –I

Black Level –I

Composite Sync Generation, Pin10 (Horizontal Slicing Level at 50% of the Sync Pulse Amplitude)

Capacitor Current During

Video

Sync Pulse –I

Vertical Sync Pulse Generation, Pin9 (Slicing Level at 30% (60% Between Black Level and Horizontal Slicing Level))

Output Voltage V

Pulse Duration t

Delay With Respect to the V ertical Sync

Pulse (LeadinG Edge)

Pulse–Mode Control

Output Current for Vertical Sync

Pulse (Dual Integrated)

(VCC = 12V, TA = +25°C unless otherwise specified)

V

11–5(P–P)

V

11–5(P–P)

I

11

I

10

10

9–5

p

t

D

G

11

11

0.2 1.0 3.0 V

50 – – mV

– – 200 Ω

– 5 – µA

– 40 – µA

– 25 – µA

– 16 – µA

– 170 – µA

10 – – V

– 190 – µs

– 45 – µs

No Current Applied

at Pin9

Output Current for Horizontal and

Vertical Sync Pulse (Non–Inte-

grated Separated Signal)

Horizontal Oscillator, Pin14 and Pin16

Free–Running Frequency f

Reference Voltage for f

OSC

V

OSC

14–5

Current Applied Via a

15kΩ from V

– 15.625 – kHz

– 6 – V

to Pin9

CC

Page 3

DC and AC Electrical Characteristics (Cont’d): (VCC = 12V, TA = +25°C unless otherwise specified)

Parameter Symbol Test Conditions Min Typ Max Unit

Horizontal Oscillator, Pin14 and Pin16 (Cont’d)

Frequency Control Sensitivity ∆f

Adjustment Range of Circuit ∆f

Spread of Frequency ∆f

OSC

/∆I

OSC

OSC

14

– 31 – Hz/µA

– ±10 – %

– – 5 %

Frequency Dependency (Excluding

Tolerance of External Components)

w

/Supply Voltage

w

/Supply Voltage Drop of 5V ∆f

w

/Temperature TC – – ±10

∆f

OSC/fOSC

∆V

15–5/V15–5

OSC

VCC = 12V – ±0.05 – %

– – 10 %

Capacitor Current During:

Charging

Discharging I

–I

16

16

– 1024 – µA

– 313 – µA

Sawtooth Voltage Timing (Pin14)

Rise Time

Fall Time t

t

R

F

– 49 – µs

– 15 – µs

Horizontal Output Pulse, Pin4

Output Voltage, Low V

Pulse Duration, High t

Supply Voltage for Switching Off the

V

4–5

P

CC

I4 = 30mA – – 0.5 V

– 29 ±1.5 – µs

– 4 – V

Output Pulse (Pin15)

Hysteresis for Switching On the Output

∆V

P

– 250 – mV

Pulse

Phase Compensation, ϕ1, Pin17

–4

°C

–1

Control Voltage Range V

Leakage Current I

Control Current:

for External Time Constant Switch

at V

or V

at V

18–5

13–5

18–5

= V

15–5

> 9.5V

= V

15–5

and V

and V

< 2V

13–5

= 2 to 9.5V 1.8 2.0 2.2 mA

13–5

17–5

17

±I

17

V

= 3.55 to 8.3V – – 1 µA

17–5

3.55 – 8.3 V

1.8 2.0 2.2 mA

– 8 – mA

Horizontal Oscillator Control

Control Sensitivity

Catching and Holding Range ∆f

S

ϕ

OSC

6 – – kHz/µs

– ±680 – Hz

Spread of Catching and Holding Range – ±10 – %

Internal Keying Pulse t

P

V

= 2.9 to 9.5V – 7.5 – µs

13–5

Time Constant Switch

Slow Time Constant

V

13–5

9.5 – 2.0 V

Fast Time Constant 2.0 – 9.5 V

Impedance Converter Offset Voltage

±V

17–18

– – 3 mV

(Slow Time Constant)

Output Resistance

Slow Time Constant

Fast Time Constant

R

18–5

– – 10 Ω

High

Impedance

– – Ω

Page 4

DC and AC Electrical Characteristics (Cont’d): (VCC = 12V, TA = +25°C unless otherwise specified)

Parameter Symbol Test Conditions Min Typ Max Unit

Phase Compensation, ϕ1, Pin17 (Cont’d)

Leakage Current I

Coincidence Detector, ϕ3, Pin13

Output Voltage

w

/o Coincidence w/Composite Video

V

13–5

Signal

w

/o Coincidence w/o Composite Video

Signal (Noise)

w

/Coincidence w/Composite Video

Signal

Output Current

w

/o Coincidence w/Composite Video

I

Signal

w

/Coincidence w/Composite Video

–I

Signal

Switching Current I

I

13(av)

Phase Comparison, ϕ2, Pin2 and Pin3 (Note 1)

Phase Relation Between Middle of the

∆t tFP = 12µs, Note 2 – 2.6 ±0.7 – µs

Horizontal Sync Pulse and the Middle

of the Line Flyback Pulse

If Additional Adjustment is Required, it

∆I/∆t – 30 – µA/µs

can be Arranged by Applying a

Current at Pin3, such that for Applied

Current

Input for Line Flyback Pulse, Pin2

18

13

13

13

– – 1 µA

– – 1 V

– – 2 V

– 6 – V

– 50 – µA

– 300 – µA

V

= VCC–0.5V – – 100 µA

13–5

V

= 0.5V (Average) – – 100 µA

13–5

Switching Level for ϕ2 Comparison V

Switching Level for Horizontal Blanking

2–5

V

2–5

– 3 – V

– 0.3 – V

and Flyback Control

Input Voltage Limiting V

2–5

– –0.7

– V

+4.5

Switching Current

at Horizontal Flyback

I

2

0.01 1.0 – mA

at Horizontal Scan – – 2.0 µA

Maximum Negative Input Current –I

2

– – 500 µA

Phase Detector Output, Pin3

Control Current for ϕ

2

Control Range ∆t

Static Control Error ∆t/∆t

Leakage Current I

±I

3

ϕ

2

d

3

– 1 – mA

– 19 – µs

– – 0.2 %

– – 5 µA

Note 1. Phase comparison between horizontal oscillator and the line flyback pulse. Generation of

) horizontal output pulse with constant duration.

2

Note 2. t

a phase–modulated (ϕ

is the line flyback pulse duration.

FP

Page 5

DC and AC Electrical Characteristics (Cont’d): (VCC = 12V, TA = +25°C unless otherwise specified)

Parameter Symbol Test Conditions Min Typ Max Unit

Burst Gating Pulse, Pin6 (Note 3)

Output Voltage V

Pulse Duration t

Phase Relation Between Middle of Sync

t

6–5

p

ϕ

6

V

= 7V 2.15 2.65 3.15 µs

6–5

10 11 – V

3.7 4.0 4.3 µs

Pulse at the Input and the Leading

Edge of the Burst Gating Pulse

Output Trailing Edge Current I

6

– 2 – mA

Horizontal Blanking Pulse, Pin6 (Note 3)

Output Voltage V

Output Trailing Edge Current I

Saturation Voltage at Horizontal Scan V

6–5

6

6–5sat

4.2 4.5 4.9 V

– 2 – mA

– – 0.5 V

Clamping Circuit for Vertical Blanking Pulse, Pin6 (Note 3)

Output Voltage V

Minimum Output Current I

Maximum Output Current I

6–5

6min

6max

I6 = 2.8mA 2.15 2.5 3.0 V

V

> 2.15V – 2.3 – mA

6–5

V

< 3V – 3.3 – mA

6–5

TV Transmitter Identification, Pin12

Output Voltage

No TV Transmitter

V

12–5

– – 1 V

TV Transmitter Identified 7 – – V

Mute Output, Pin7

Output Voltage, No TV Transmitter V

Output Resistance, No TV Transmitter R

Output Leakage Current,

7–5

7–5

I

7

I7 = 3mA – – 0.5 V

I7 = 3mA – – 100 Ω

V

> 3V – – 5 µA

12–5

TV Transmitter Identified

Protection Circuit, Pin8 (Beam Current/EHT Voltage Protection)

No–Load Voltage (Operative Condition) V

Threshold

Positive–Going Voltage

8–5

V

8–5

I8 = 0 – 6 – V

– 8 ±0.8 – V

Negative–Going Voltage – 4 ±0.4 – V

Current Limiting ±I

Input Resistance R

Response Delay of Threshold Switch t

8

8–5

d

V

= 1 to 8.5V – 60 – µA

8–5

V

> 8.5V – 3 – kΩ

8–5

– 10 – µs

Control Output of Line Flyback Pulse Condition, Pin1

Saturation V oltage at Standard Operation V

Output Leaka g e Current in Case of Break

1–5sat

I

1

I1 = 3mA – – 0.5 V

– – 5 µA

in Transmission

Note 3. Three–level sandcastle pulse.

Page 6

Pin Connection Diagram

Control Out Line FB Pulse Control

FB Pulse Input

Phase Det

Horiz Output Pulse

Vert Sync Pulse Gen

1

2

3

4

5GND

6Burst Gating Pulse

7Mute Output

8EHT Volt Protection

9

18 10

18

Volt Fol Output

Phase Com

17

16

Horiz OSC

15

V

CC

14 Horiz OSC

13 Coin Det

TV Trans Ident

12

11

Comp Video In/Sync Sep

Comp Sync Gen

10

19

.870 (22.1) Max

.250

(6.35)

.150

(3.8)

.100 (2.54) .125 (3.17) Min

.800 (20.3)

Loading...

Loading...