Page 1

NTE6508

Integrated Circuit

CMOS, 1K Static RAM (SRAM)

Description:

The NTE6508 is a 1024 x 1 fully static CMOS RAM in a 16–Lead DIP type package fabricated using

self–aligned silicon gate technology. Synchronous circuit design techniques are employed to acheive

high performance and low power operation. On chip latches are provided for address allowing effecient interfacing with microprocessor systems. The data output buffers can be forced to a high impedance state for use in expanded memory arrays.

Features:

D Low Power Standby: 50µW Max

D Low Power Operation: 20mW/MHz Max

D Fast Access Time: 300ns Max

D Data Retention: 2V Min

D TTL Compatible Input/Output

D High Output Drive: 2 TTL Loads

D On–Chip Address Register

Absolute Maximum Ratings:

Supply Voltage +7V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input, Output or I/O Voltage GND –0.3V to V

Typical Derating Factor 1.5mA/MHz increase in I

Gate Count 1925 Gates. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating Junction Temperature +175°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage Temperature Range –65° to +150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead Temperature (During Soldering, 10s max) +300°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Note 1. Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage

to the device. This is a stress only rating and operation of the device at these or any other

conditions above those indicated in the operational sections of this specification is not implied. This device is sensitive to electrostatic discharge, users should follow proper IC handling procedures.

Recommended Operating Conditions:

Operating Voltage Range +4.5V to +5.5V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating Temperature Range –40° to +85°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

(Note 1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CC

+0.3V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CC(OP)

Page 2

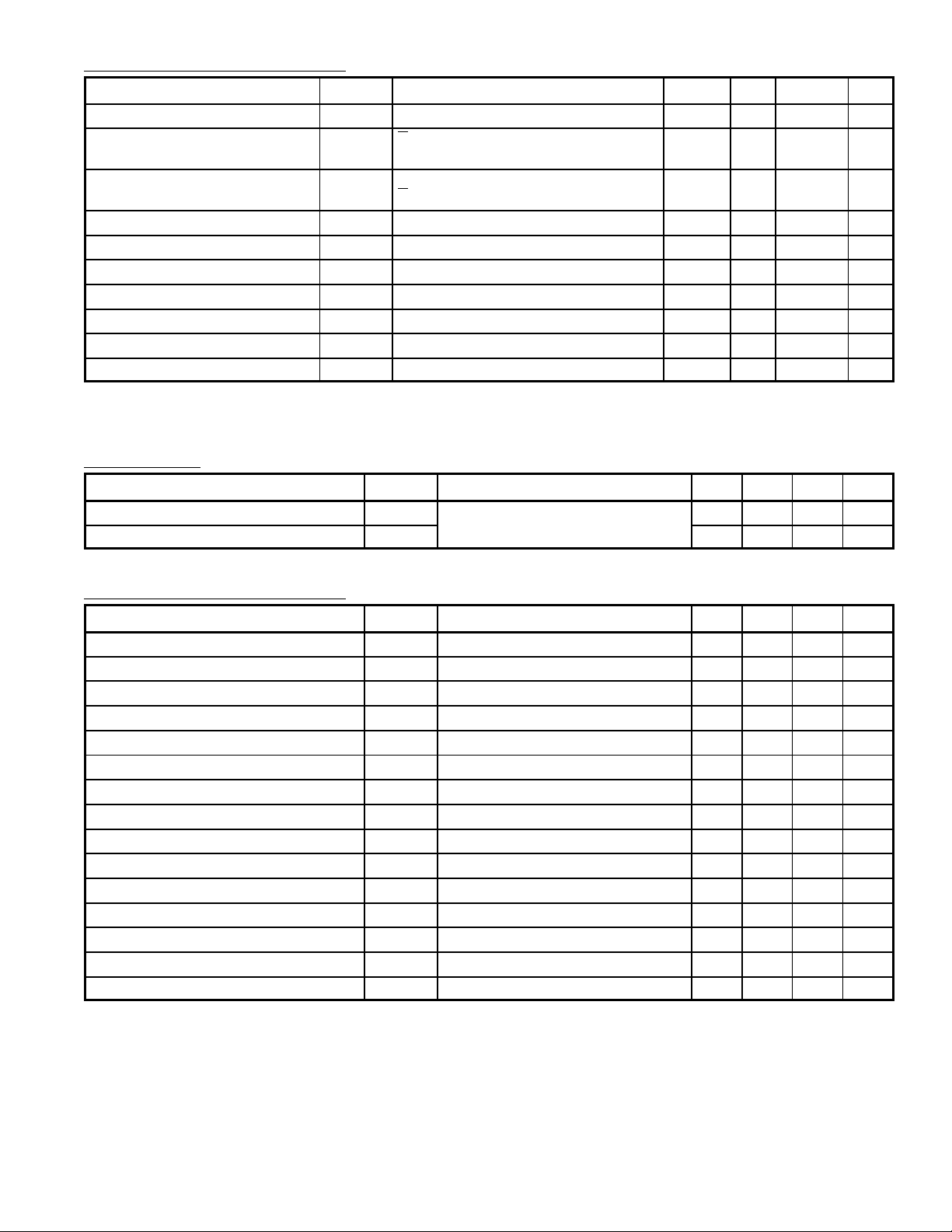

DC Electrical Characteristics: VCC = 5V ±10%, TA = –40° to +85°C unless otherwise specified)

Parameter Symbol Test Conditions Min Typ Max Unit

Standby Supply Current I

Operating Supply Current I

Data Retention Supply Current I

Data Retention Supply Voltage V

CC(SB)IO

CC(OP)

CC(DR)VCC

CC(DR)

Input Leakage Current I

Output Leakage Current I

Input Voltage, LOW V

Input Voltage, HIGH V

Output Voltage, LOW V

Output Voltage, HIGH V

I

OZ

IL

IH

OL

OH

= 0, VI = VCC or GND, VCC = 5V – – 10 µA

E = 1MHz, IO = 0, VI = VCC or GND,

= 5.5V, Note 2

V

CC

= 2V, IO = 0, VI = VCC or GND,

= V

E

CC

– – 4 mA

– – 10 µA

2.0 – – V

VI = VCC or GND, VCC = 5.5V –1.0 – +1.0 µA

VO = VCC or GND, VCC = 5.5V –1.0 – +1.0 µA

VCC = 4.5V –0.3 – +0.8 V

VCC = 5.5V VCC–2 – VCC+0.3 V

IO = 3.2mA, VCC = 4.5V – – 0.4 V

IO = –0.4mA, VCC = 4.5V 2.4 – – V

Note 2. Typical derating 1.5mA/MHz increase in I

Capacitance:

(TA = +25°C unless otherwise specified)

CC(OP)

.

Parameter Symbol Test Conditions Min Typ Max Unit

Input Capacitance C

Output Capacitance C

f = 1MHz, All measurements are ref-

I

erenced to device GND

O

– – 6 pF

– – 10 pF

AC Electrical Characteristics: VCC = 5V ±10%, TA = –40° to +85°C unless otherwise specified)

Parameter Symbol Test Conditions Min Typ Max Unit

Chip Enable Access Time TELQV Note 3, Note 5 – – 300 ns

Address Access Time TAVQV Note 3, Note 5, & Note 6 – – 300 ns

Chip Enable Output Enable Time TELQX Note 4, Note 5 5 – 160 ns

Write Enable Output Disable Time TWLQZ Note 4, Note 5 – – 160 ns

Chip Enable Output Disable Time TEHQZ Note 4, Note 5 – – 160 ns

Chip Enable Pulse Negative Width TELEH Note 3, Note 5 300 – – ns

Chip Enable Pulse Positive Width TEHEL Note 3, Note 5 100 – – ns

Address Setup Time TAVEL Note 3, Note 5 0 – – ns

Address Hold Time TELAX Note 3, Note 5 50 – – ns

Data Setup Time TDVWH Note 3, Note 5 110 – – ns

Data Hold Time TWHDX Note 3, Note 5 0 – – ns

Chip Enable Write Pulse Setup Time TWLEH Note 3, Note 5 130 – – ns

Chip Enable Write Pulse Hold Time TELWH Note 3, Note 5 130 – – ns

Write Enable Pulse Width TWLWH Note 3, Note 5 130 – – ns

Read or Write Cycle Time TELEL Note 3, Note 5 350 – – ns

Note 3. Input pulse levels: 0.8V to VCC –2V; Input rise and fall times: 5ns (max); Input and output

timing reference level: 1.5V; Output load: 1 TTL gate equivalent, CL = 50pF (min) – for C

greater than 50pF, access time is derated by 0.15ns per pF.

Note 4. Tested at initial design and after major design changes.

Note 5. V

= 4.5V and 5.5V.

CC

Note 6. TAVQV = TELQV + TAVEL.

L

Page 3

Read Cycle Truth Table:

Inputs Outputs

Time Reference

–1 H X X X Z Memory Disabled

0 H V X Z Cycle Begins, Addresses are Latched

1 L H X X X Output Enables

2 L H X X V Output Valid

3 H X X V Read Accomplished

4 H X X X Z Prepare for Next Cycle (Same as –1)

5 H V X Z Cycle Ends, Next Cycle Begins (Same as 0)

E W A D Q

Function

In the NTE6508 Read Cycle, the address information is latched into the on chip registers on the falling

edge of E

(T = 0). Minimum address setup and hold time requirements must be met. After the required

hold time, the addresses may change state without affecting device operation. During time (T = 1)

the data output becomes enabled; however, the data is not valid until during time (T = 2). W

remain high for the read cycle. After the output data has been read, E

may return high (T = 3). This

will disable the chip and force the output buffer to a high impedance state. After the required E

must

high

time (TEHEL) the RAM is ready for the next memory cycle (T = 4).

Write Cycle Truth Table:

Inputs Outputs

Time Reference

–1 H X X X Z Memory Disabled

0 X V X Z Cycle Begins, Addresses are Latched

1 L X X Z Write Period Begins

2 L X V Z Data is Written

3 H X X Z Write Completed

4 H X X X Z Prepare for Next Cycle (Same as –1)

5 X V X Z Cycle Ends, Next Cycle Begins (Same as 0)

E W A D Q

Function

The write cycle is initiated by the falling edge of E which latches the address information into the on

chip registers. The write portion of the cycle is defined as both E

may go low anytime during the cycle provided that the write enable pulse setup time (TWLEH) is

W

met. The write portion of the cycle is terminated by the first rising edge of either E

and W being low simultaneously.

or W . Data setup

and hold times must be referenced to the terminating signal.

If a series of consecutive write cycles are to be performed, the W

line may remain low until all desired

locations have been written. When this method is used, data setup and hold times must be referenced

to the rising edge of E

. By positioning the W pulse at different times within the E low time (TELEH),

various types of write cycles may be performed.

If the E

low time (TELEH) is greater than the W pulse (TWLWH) plus an output enable time (TELQX),

a combination read write cycle is executed. Data may be modified an indefinite number of times during any write cycle (TELEH). The data input and data output pins may be tied together for use with

a common I/O data bus structure. When using the RAM in this method allow a minimum of one output

disable time (TWLQZ) after W

goes low before applying input data to the bus. This will insure that

the output buffers are not active.

Page 4

Pin Connection Diagram

E

1

A0

2

3

A1

4

A2

5A3

6A4

Q

7

GND

8

16 9

V

16

15

14

W

13DA9

12

A8

11 A7

A6

10

9

A5

CC

18

.870 (22.0)

Max

.260 (6.6)

Max

.200 (5.08)

Max

.100 (2.54)

.099 (2.5) Min

.700 (17.78)

Loading...

Loading...