Page 1

CYStech Electronics Corp.

30V N-Channel Enhancement Mode MOSFET

MTA90N03ZN3

Features

Simple drive requirement.

•

Small package outline.

•

ESD protected.

•

Pb-free lead plating and halogen-free package.

•

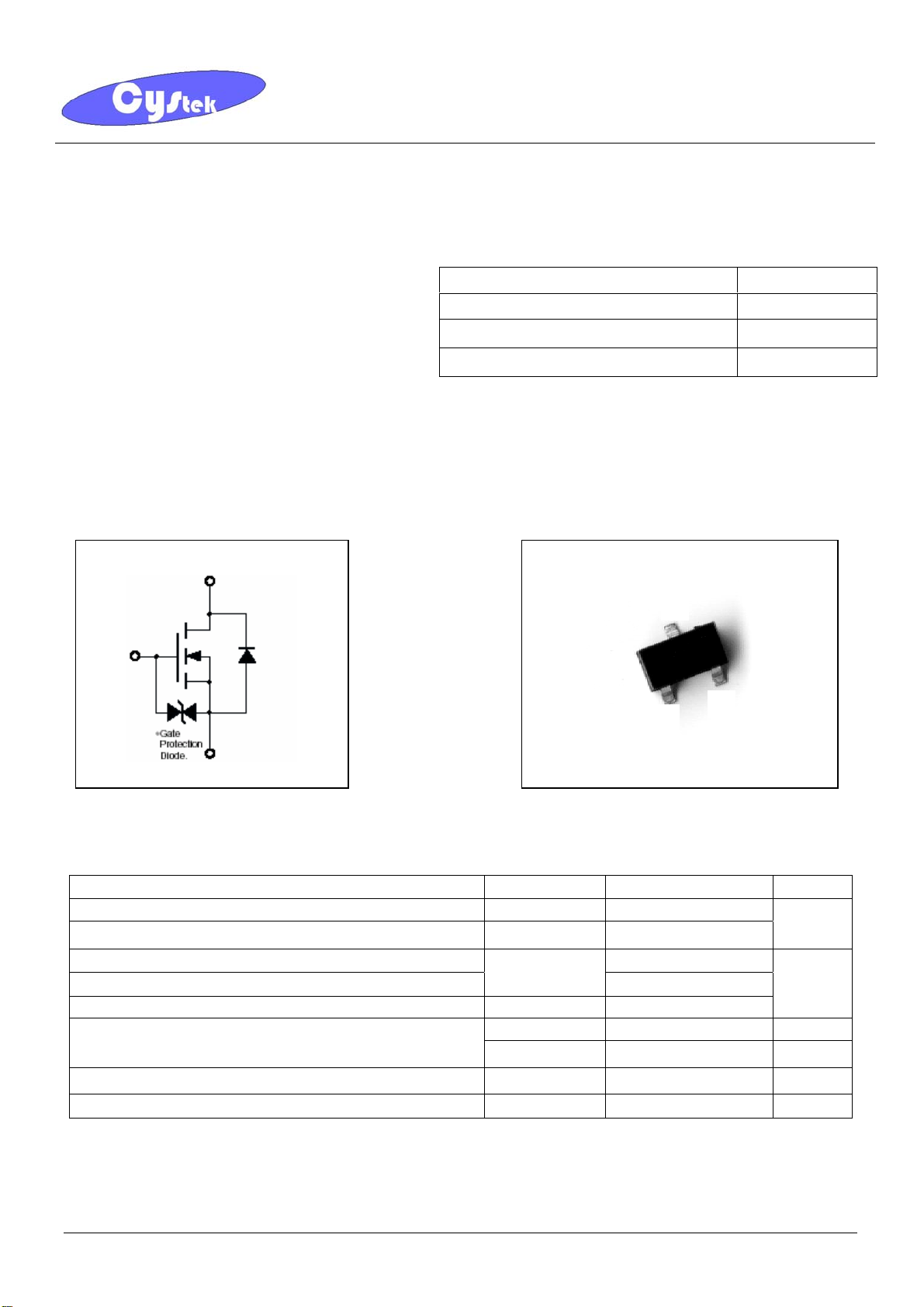

Symbol Outline

BVDSS 30V

ID

RDSON@VGS=4.5V, ID=2.5A

RDSON@VGS=3V,ID=2.5A

Spec. No. : C831N3

Issued Date : 2012.07.04

Revised Date : 2012.12.28

Page No. : 1/8

3.2A

130mΩ(typ)

144mΩ(typ)

MTA90N03ZN3 SOT-23

D

G:Gate

S:Source

D:Drain

G

S

Absolute Maximum Ratings (Ta=25°C)

Parameter

Drain-Source Voltage VDS 30

Gate-Source Voltage VGS ±12

Continuous Drain Current @ TA=25°C , VGS=4.5V

Continuous Drain Current @ TA=70°C, VGS=4.5V

Pulsed Drain Current (Notes 1, 2) IDM 10

Maximum Power Dissipation@ TA=25℃

Linear Derating Factor

ESD susceptibility

Operating Junction and Storage Temperature Tj, Tstg -55~+150

Note : 1. Pulse width limited by maximum junction temperature.

2. Pulse width≤ 300μs, duty cycle≤2%.

3. Surface mounted on 1 in² copper pad of FR-4 board, t≤10s.

4. Human body model, 1.5kΩ in series with 100pF.

Symbol Limits Unit

ID

PD 1.38 (Note 3) W

0.01

1000 (Note 4) V

3.2

2.6

V

A

W/°C

°C

MTA90N03ZN3 CYStek Product Specification

Page 2

Thermal Performance

Parameter Symbol Limit Unit

CYStech Electronics Corp.

Spec. No. : C831N3

Issued Date : 2012.07.04

Revised Date : 2012.12.28

Page No. : 2/8

Thermal Resistance, Junction-to-Ambient(PCB mounted) Rth,ja 90

Note : Surface mounted on 1 in² copper pad of FR-4 board, 270°C/W when mounted on minimum copper pad.

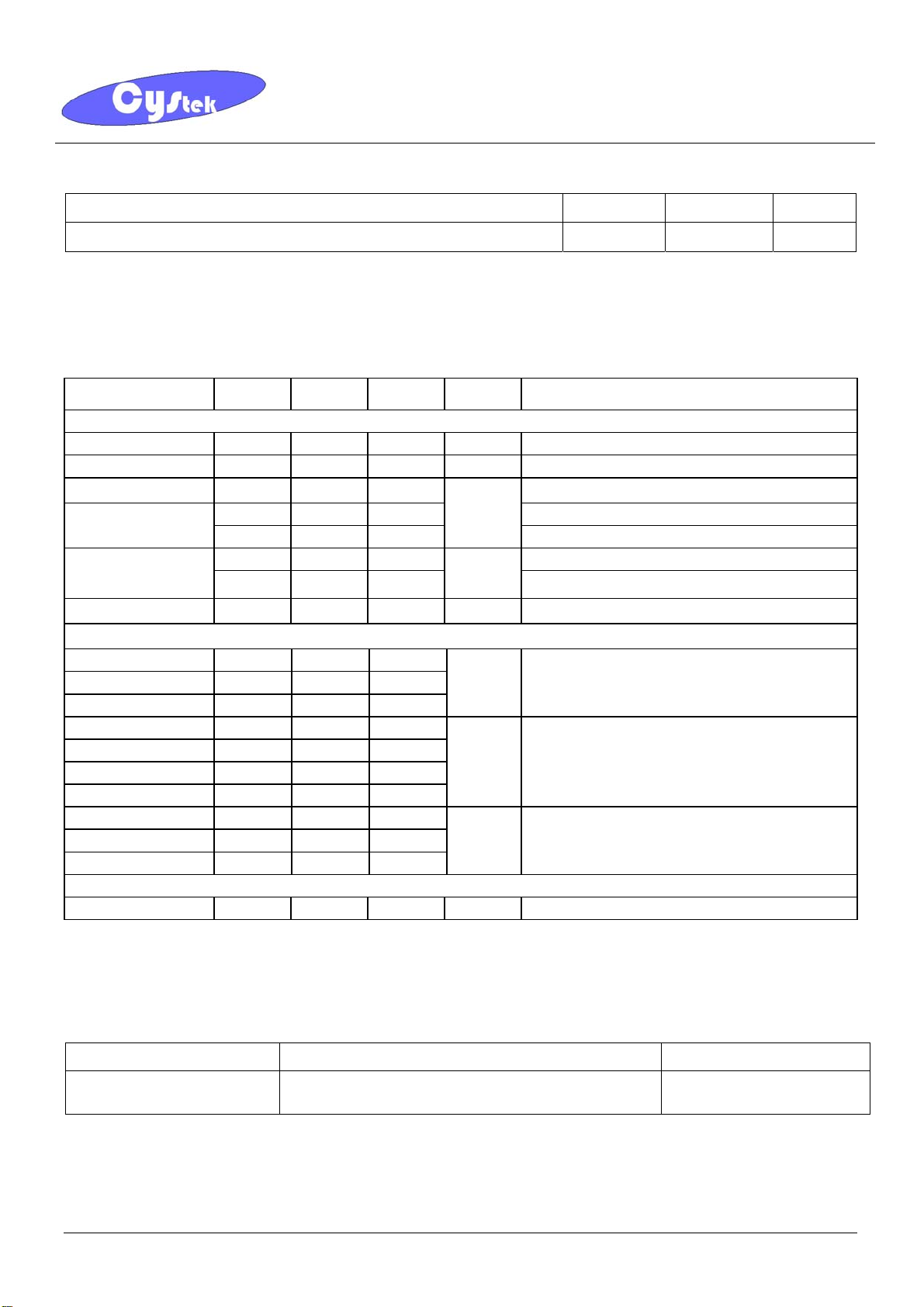

Electrical Characteristics (Tj=25°C, unless otherwise noted)

Symbol Min. Typ. Max. Unit Test Conditions

Static

BV

V

30 - - V VGS=0, ID=250μA

DSS

0.5 0.9 1.5 V VDS=VGS, ID=250μA

GS(th)

±

I

- -

GSS

I

DSS

- - 1 VDS=30V, VGS=0

- - 10

10 VGS=±12V, VDS=0

μA

VDS=24V, VGS=0 (Tj=70

- 130 160 VGS=4.5V, ID=2.5A

*R

DS(ON)

- 145 180

mΩ

VGS=3V, ID=2.5A

*GFS - 5.4 - S VDS=3V, ID=1.6A

Dynamic

Ciss - 309 -

Coss - 50 -

pF VDS=10V, VGS=0, f=1MHz

Crss - 38 -

t

- 15 -

d(ON)

tr - 35 -

t

- 51 -

d(OFF)

ns

VDS=15V, ID=500mA, VGS=2.5V,

RG=6Ω

tf - 27 -

Qg - 8 -

Qgs - 0.8 -

nC VDS=15V, ID=3.2A, VGS=4.5V

Qgd - 2.8 -

Source-Drain Diode

*VSD - 0.8 1.2 V VGS=0V, IS=1A

*Pulse Test : Pulse Width ≤300μs, Duty Cycle≤2%

°C)

°C/W

Ordering Information

Device Package Shipping

MTA90N03ZN3-0-T1-G

(Pb-free lead plating and halogen-free package)

SOT-23

3000 pcs / Tape & Reel

MTA90N03ZN3 CYStek Product Specification

Page 3

GS

V

GS

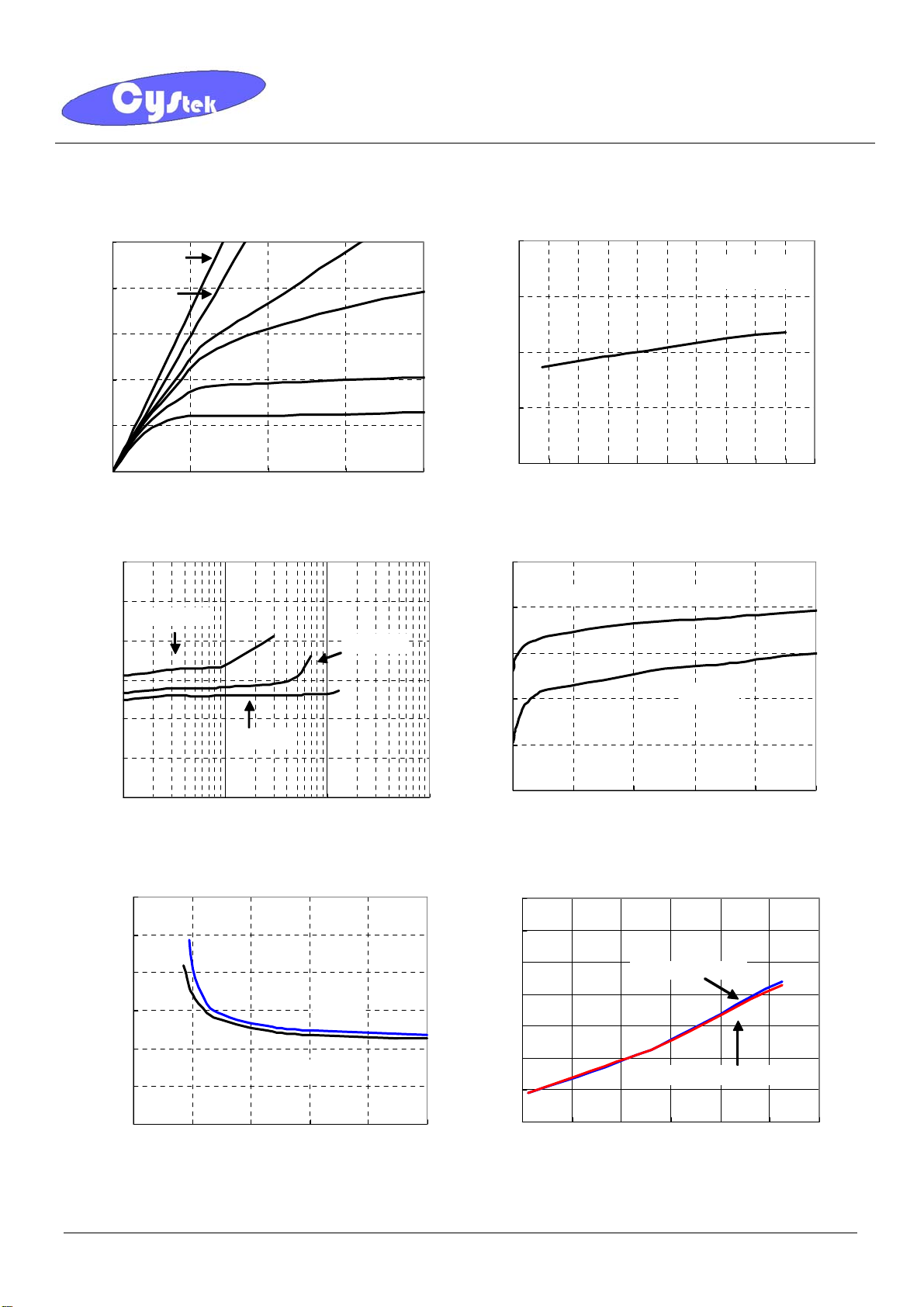

Typical Characteristics

CYStech Electronics Corp.

Spec. No. : C831N3

Issued Date : 2012.07.04

Revised Date : 2012.12.28

Page No. : 3/8

Typical Output Characteristics

10

V

=10V

GS

8

VGS=4.5V

6

4

, Drain Current (A)

D

I

2

0

00.511.5

Static Drain-Source On-State resistance vs Drain Current

300

250

200

150

Resistance(mΩ)

100

, Static Drain-Source On-State

DS (on)

50

R

VGS=2V

, Drain-Source Voltage(V)

V

DS

VGS=4.5V

VGS=3V

V =2.5V

VGS=2V

VGS=1.8

VGS=3V

Breakdown Voltage

, Normalized Drain-Source

DSS

BV

2

, Source-Drain Voltage(V)

SD

V

Brekdown Voltage vs Ambient Temperature

1.4

ID=250μA,

V

=0V

1.2

1

0.8

0.6

-75 -50 -25 0 25 50 75 100 125 150 175

Tj, Junction Temperature(°C)

Reverse Drain Current vs Source-Drain Voltage

1

VGS=0V

Tj=25°C

0.8

0.6

0.4

Tj=150°C

0.2

0

0.1 1 10 100

D

, Drain Current(A)

I

Static Drain-Source On-State Resistance vs Gate-Source

Voltage

300

250

200

150

ID=2.5A

0

0 0.2 0.4 0.6 0.8 1

, Reverse Drain Current (A)

I

DR

Drain-Source On-State Resistance vs Junction Tempearture

2

1.8

1.6

VGS=3V, ID=2.5A

1.4

1.2

, Static Drain-Source On-

100

State Resistance(mΩ)

DS(ON)

50

R

ID=100mA

0

024681

V

, Gate-Source Voltage(V)

GS

, Normalized Static Drain-

DS( ON)

R

0

1

Source On-State Resistance

VGS=4.5V, ID=2.5A

0.8

0.6

-60 -20 20 60 100 140 180

Tj, Junction Temperature(°C)

MTA90N03ZN3 CYStek Product Specification

Page 4

CYStech Electronics Corp.

S

Typical Characteristics(Cont.)

Spec. No. : C831N3

Issued Date : 2012.07.04

Revised Date : 2012.12.28

Page No. : 4/8

Capacitance vs Drain-to-Source Voltage

1000

100

Capacitance---(pF)

10

0.1 1 10 100

V

, Drain-Source Voltage(V)

DS

Single Pulse Power Rating, Junction to Ambient

(Note on page 2)

10

8

6

Crss

T

J( MAX)

T

A

θJA

R

C

oss

=25°C

=90°C/W

=150°C

Ciss

Threshold Voltage vs Junction Tempearture

1.6

1.4

1.2

1

0.8

, Normalized Threshold Voltage

0.6

GS( th)

V

0.4

-60 -40 -20 0 20 40 60 80 100 120 140 160

Tj, Junction Temperature(°C)

Forward Transfer Admittance vs Drain Current

10

V

=3V

D

1

ID=250μA

VDS=5V

Power (W)

4

2

0

0.01 0.1 1 10 100

Pulse Width(s)

Maximum Safe Operating Area

10

1

0.1

, Drain Current (A)

D

I

0.01

0.001

TA=25°C, Tj=150°C,

=4.5V, R

θ

=90°C/W

JA

V

GS

Single Pulse

0.01 0.1 1 10 100

, Drain-Source Voltage(V)

V

DS

100μs

1ms

10ms

100ms

DC

0.1

, Forward Transfer Admittance(S)

FS

G

0.01

0.001 0.01 0.1 1

, Drain Current(A)

I

D

Maximum Drain Current vs JunctionTemperature

4

3.5

3

2.5

2

1.5

1

, Maximum Drain Current(A)

D

I

TA=25°C, VGS=4.5V, R

0.5

0

25 50 75 100 125 150 175

Tj, Junction Temperature(°C)

θJA

=90°C/W

Ta=25°C

Pulsed

MTA90N03ZN3 CYStek Product Specification

Page 5

CYStech Electronics Corp.

Typical Characteristics(Cont.)

Spec. No. : C831N3

Issued Date : 2012.07.04

Revised Date : 2012.12.28

Page No. : 5/8

, Drain Current (mA)

D

I

Typical Transfer Characteristics

10000

VDS=3V

1000

100

0.01

150°C

25°C

10

0°C

1

0.1

00.511.522.5

, Gate-Source Voltage(V)

V

GS

1

D=0. 5

0.2

-40° C

Transient Thermal Response Curves

Power Derating Curve

1.6

1.4

1.2

1

0.8

0.6

, Power Dissipation(W)

D

0.4

P

0.2

0

0 20 40 60 80 100 120 140 160

T

Mounted on FR-4 board

, Ambient Temperature(℃)

A

0.1

0.1

0.05

0.02

0.01

0.01

Normalized Transient Thermal Resistance

0.001

1.E-04 1. E-03 1.E-02 1. E-01 1.E+00 1.E+01 1.E+02 1.E+03

Single Pulse

t

, Square Wave Pulse Duration(s)

1

JA

1.R

(t)= r(t)*R

θ

2.Duty Factor, D=t1/t

3.TJM-TA=PDM*Z

4.R

θJA

=90

°C/W

θJA

JA

θ

2

(t)

MTA90N03ZN3 CYStek Product Specification

Page 6

Reel Dimension

CYStech Electronics Corp.

Spec. No. : C831N3

Issued Date : 2012.07.04

Revised Date : 2012.12.28

Page No. : 6/8

Carrier Tape Dimension

MTA90N03ZN3 CYStek Product Specification

Page 7

CYStech Electronics Corp.

Recommended wave soldering condition

Product Peak Temperature Soldering Time

Spec. No. : C831N3

Issued Date : 2012.07.04

Revised Date : 2012.12.28

Page No. : 7/8

Pb-free devices

260 +0/-5 °C

Recommended temperature profile for IR reflow

5 +1/-1 seconds

Profile feature Sn-Pb eutectic Assembly

Average ramp-up rate

(Tsmax to Tp)

Preheat

−Temperature Min(T

S min)

−Temperature Max(TS max)

−Time(ts min to ts max)

Time maintained above:

−Temperature (T

− Time (t

L)

L)

Peak Temperature(TP)

Time within 5°C of actual peak

temperature(tp)

Ramp down rate

Time 25 °C to peak temperature

Note : All temperatures refer to topside of the package, measured on the package body surface.

3°C/second max. 3°C/second max.

100°C

150°C

60-120 seconds

183°C

60-150 seconds

240 +0/-5 °C 260 +0/-5 °C

10-30 seconds 20-40 seconds

6°C/second max. 6°C/second max.

6 minutes max. 8 minutes max.

Pb-free Assembly

150°C

200°C

60-180 seconds

217°C

60-150 seconds

MTA90N03ZN3 CYStek Product Specification

Page 8

SOT-23 Dimension

CYStech Electronics Corp.

Spec. No. : C831N3

Issued Date : 2012.07.04

Revised Date : 2012.12.28

Page No. : 8/8

Marking:

A

L

3

S

B

1

V

C

D

DIM

Min. Max. Min. Max.

G

Inches Millimeters Inches Millimeters

2

H

K

J

DIM

Style: Pin 1.Gate 2.Source 3.Drain

Min. Max. Min. Max.

2306

3-Lead SOT-23 Plastic

Surface Mounted Package

CYStek Package Code: N3

A 0.1102 0.1204 2.80 3.04 J 0.0032 0.0079 0.08 0.20

B 0.0472 0.0669 1.20 1.70 K 0.0118 0.0266 0.30 0.67

C 0.0335 0.0512 0.89 1.30 L 0.0335 0.0453 0.85 1.15

D 0.0118 0.0197 0.30 0.50 S 0.0830 0.1161 2.10 2.95

G 0.0669 0.0910 1.70 2.30 V 0.0098 0.0256 0.25 0.65

H 0.0000 0.0040 0.00 0.10

Notes: 1.Controlling dimension: millimeters.

Material:

• Lead: Pure tin plated.

• Mold Compound: Epoxy resin family, flammability solid burning class: UL94V-0.

2.Maximum lead thickness includes lead finish thickness, and minimum lead thickness is the minimum thickness of base material.

3.If there is any question with packing specification or packing method, please contact your local CYStek sales office.

Important Notice:

• All rights are reserved. Reproduction in whole or in part is prohibited without the prior written approval of CYStek.

• CYStek reserves the right to make changes to its products without notice.

• CYStek semiconductor products are not warranted to be suitable for use in Life-Support Applications, or systems.

• CYStek assumes no liability for any consequence of customer product design, infringement of patents, or application assistance.

TE

*: Typical

MTA90N03ZN3 CYStek Product Specification

Page 9

Loading...

Loading...