Page 1

E2A0034-16-X1

¡ Semiconductor MSM6948/6948V

¡ Semiconductor

This version: Jan. 1998

Previous version: Nov. 1996

MSM6948/6948V

1200 bps Single Chip MSK Modem

GENERAL DESCRIPTION

The MSM6948/6948V is a single chip MSK (Minimum Shift Keying) modem which is fabricated by

Oki’s low power consumption CMOS silicon gate technology.

The demodulator receives the data to be transmitted (SD) synchronized with the transmit timing

clock (ST) generated by the on-chip clock generator. The signal, which is modulated by MSK method,

is output.

The demodulator converts the received MSK signal to the received data (RD) by means of a delay

detection technique after limiting the band of the received MSK signal. This signal is input to the

digital PLL and the re-generated timing clock (RT) is output from the demodulator, synchronized

with the RD.

FEATURES

• Signal power supply: +5 V

• On-chip SCF (Switched Capacitor Filter)

• The transmit filter can be also used as voice splatter filter.

• The receive timing re-generator has two different lock-in time performance options to be chosen

from.

• Built-in crystal oscillation circuit.

• Small number of external components for easy application.

• Wide application-wireless data equipment, MCA system.

• Low power consumption CMOS.

• Package options:

18-pin plastic DIP (DIP18-P-300-2.54) (Product name: MSM6948RS)

24-pin plastic SOP (SOP24-P-430-1.27-K) (Product name: MSM6948GS-K)

1/13

Page 2

¡ Semiconductor MSM6948/6948V

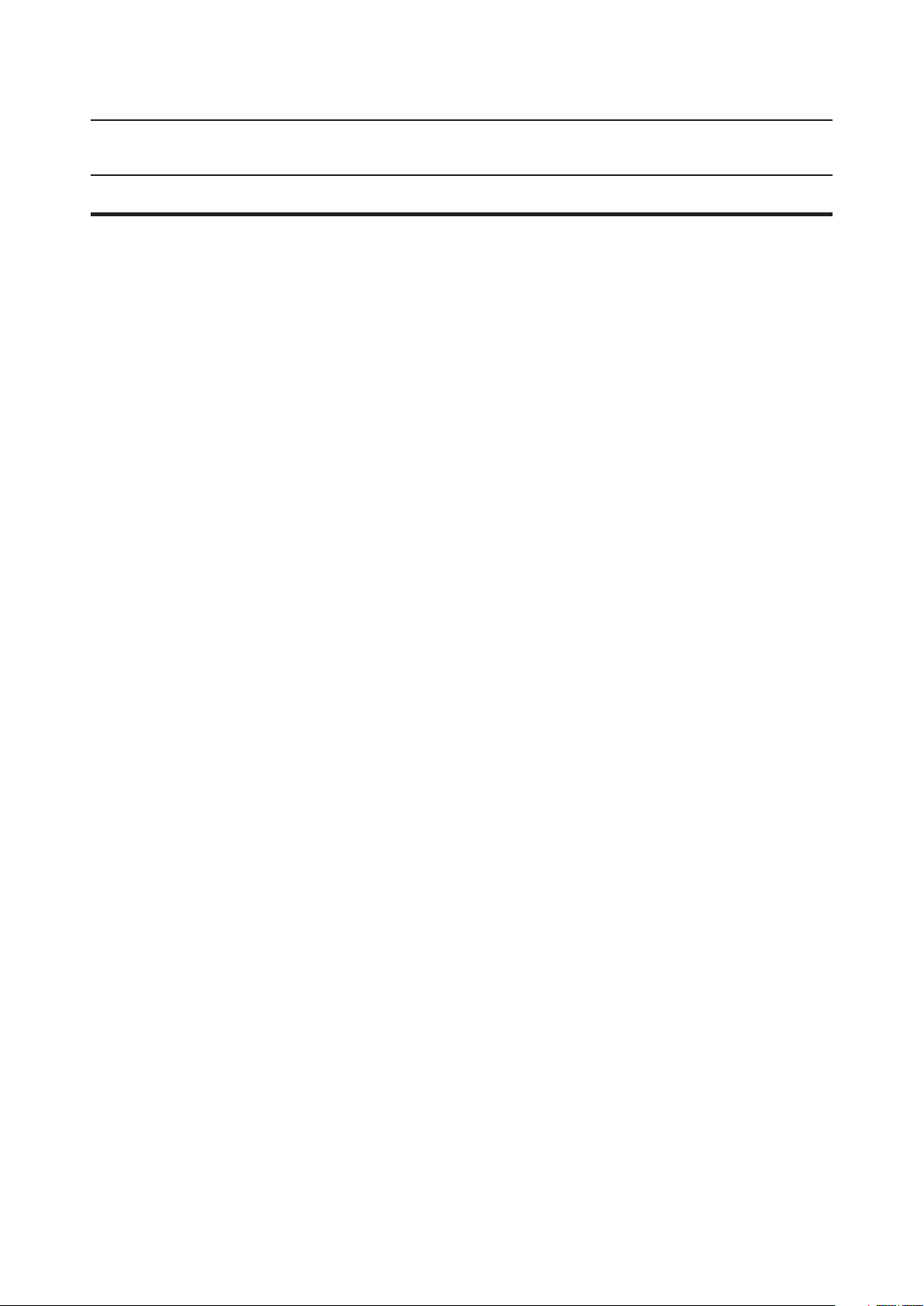

BLOCK DIAGRAM

ST

*2

SD

ME

TI

CF

RT

RD

CT

MCK

X1

Modulator

SH LIM

Timing

Re-generator

RC

LPF

Generator

RC

LPF

Clock

PDF

*1

Power

ON

Reset

Transmit

LPF

Receive

BPF

RC

LPF

Delay

Detector

RC

LPF

Signal

Ground

FT

AO

AI

V

AG

SG

DD

X2

*1 Post Detection Filter

*2 NC (MSM6948V)

DG

2/13

Page 3

¡ Semiconductor MSM6948/6948V

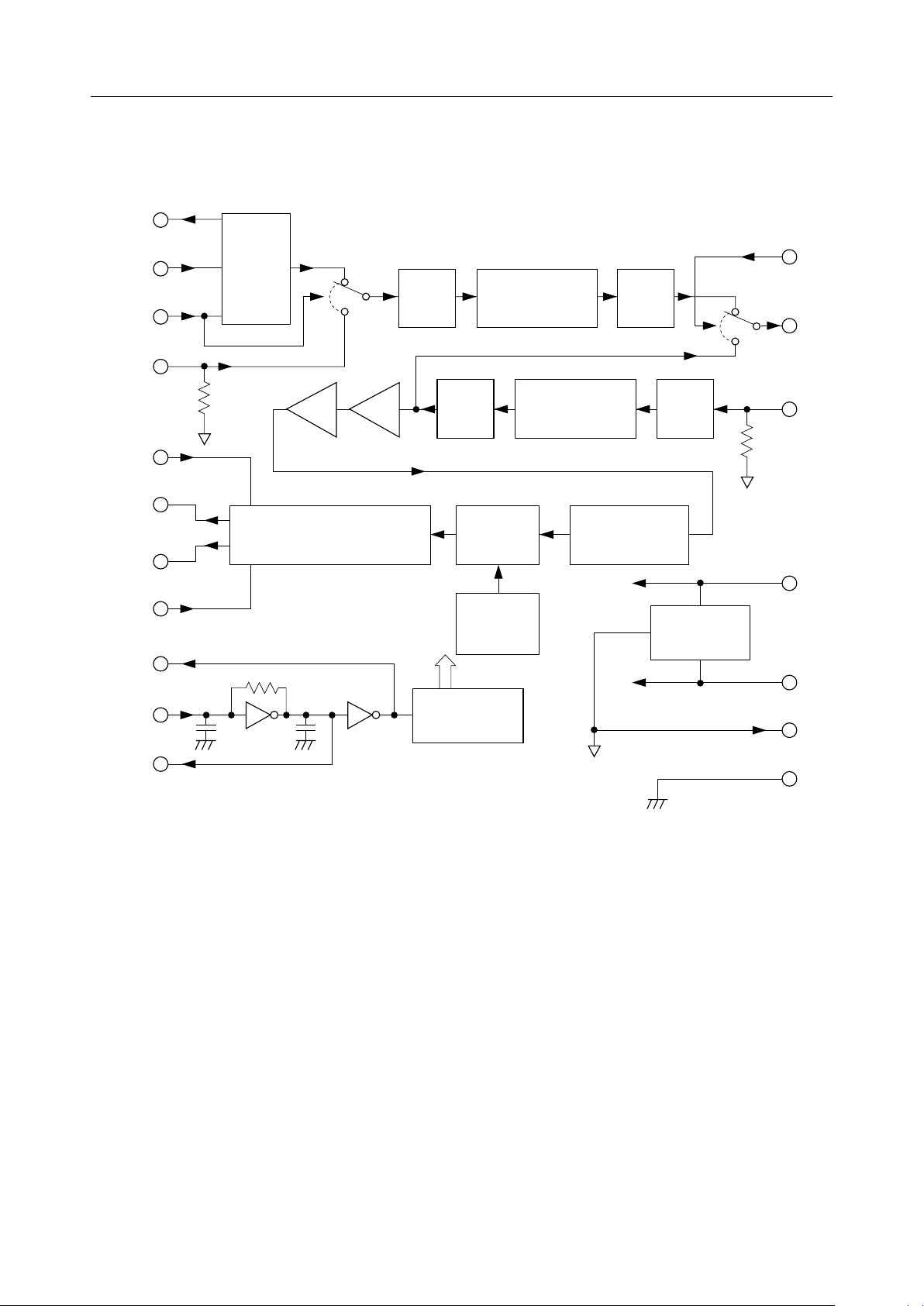

PIN CONFIGURATION (TOP VIEW)

1

X1

2 17X2 FT

3

4

5

6

7

8

9

DG

18

V

16*MCK CT

15ME CF

14SD RT

13ST RD

12SG AI

11AG AO

10

TI

DD

X1

X2

*MCK

ME

(NC)

SD

(NC)

(NC)

ST

1

2

3

4

5

6

7

8

9

10 15SG AI

11

12

24

V

23

FT

22

CT

21

CF

20

(NC)

19

RT

18

(NC)

17

(NC)

16

RD

14AG AO

13DG TI

DD

18-Pin Plastic DIP

*NC (MSM6948V)

NC : No connect pin

24-Pin Plastic SOP

3/13

Page 4

¡ Semiconductor MSM6948/6948V

PIN DESCRIPTION

Name Description

X1

X2

Crystal connection pins.

A 3.6864 MHz crystal shall be connected.

When an external clock is applied for MSM6948's oscillation source, it has to be input to X2.

In this case, X2 has to be AC-coupled by the capacitor of 200 pF. X1 shall be left open.

*MCK

ME

SD

ST

SG

3.6864 MHz ±0.02% clock output.

This can be used for other devices under limited load conditions.

When digital "1" is put on this pin, MSK modulator output is connected to the input of

transmit LPF.

When digital "0" is put on, the input of transmit LPF is connected to TI that is voice signal input.

The data put on ME terminal is synchronized with the rising edge of ST and input to internal

logic as a control data. The rising edge of this synchronized data resets MSK modulator.

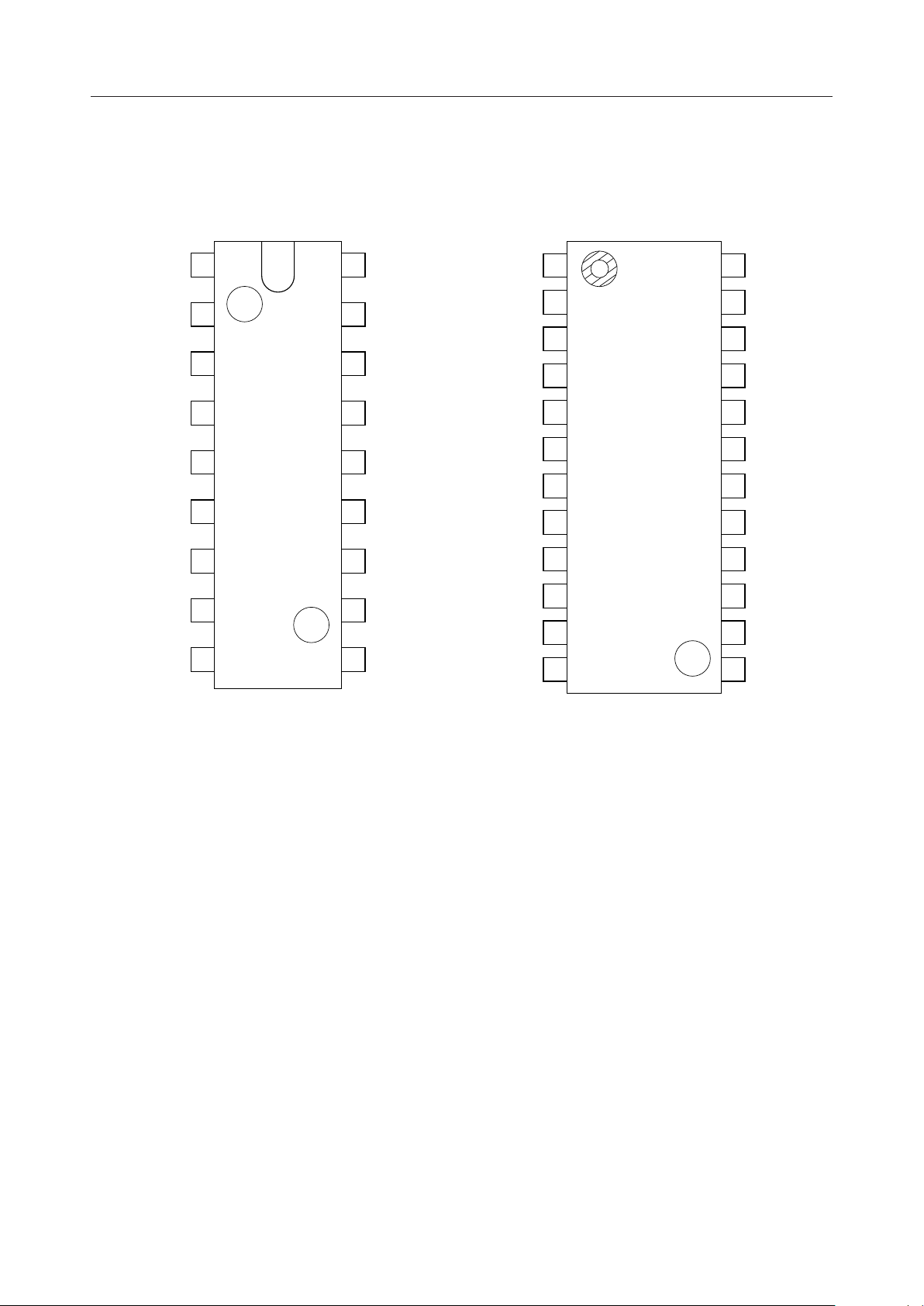

Transmit data input.

The data on this pin is synchronized with the rising edge of ST and input to MSK modulator

as an actual transmit data.

SD

50%SD

ST

50%SD

MSK

Modulated

Data

t

setup

t

; Min. 300 ns

setup

; Min. 300 ns

t

hold

t

hold

ST is synchronizing signal used for ME and SD.

This is made from master clock and is usually 1200 Hz.

Built-in analog signal ground.

The DC voltage is approximately half of V

, so the analog signals of AI, AO, and TI interfaces

DD

with peripheral circuits which must be implemented by AC-coupling. To make this voltage

source impedance lower and ensure the device performance, it is necessary to put a bypass

capacitor on SG in close physical proximity to the device.

AG

*NC : MSM6948V

Analog ground.

This pin should be common with DG at the system ground point as close as possible.

4/13

Page 5

¡ Semiconductor MSM6948/6948V

Name Description

DG

TI

Digital ground.

This pin should be common with AG at the system ground point as close as possible.

Voice signal input.

The signal input to this pin can be sent out to AO through the transmit LPF, the characteristics

of which, gives the splatter filter for voice band signal.

When this function is used, digital "0" must be input to ME.

TI is biased internally to SG with about 100 kW.

Transmit analog signal output.

According to the control data on ME and FT, AO is set to various state as an output terminal as

follows.

FT ME Transmit LPF State of AO

"1" "1"

Power On

"1" "0" Transmit LPF Voice Signal

"0" "1"

Power Down

"0" "0"

The output of MSK Signal

The Output of Receive BPF

(Used for Device Test Only)

No-signal Output

(DC-biased to SG)

AO

AI

TI

Modu-

SD

The state when FT and ME = "0" is shown above. When the input digital data on FT changes to

"1" from "0", AO remains to be connected to SG during about 12 ms and after that, and AO is

switched to transmit LPF.

This delay time prevents AO from outputting meaningless signal during transient time from

power down to on of LPF.

Receive analog signal input.

AI is biased internally to SG with about 100 kW same as TI. Receive BPF and demodulator

extract the information in this signal and convert it into a serial data stream at RD output.

lator

Power down

Transmit LPF

Receive BPF

SG

+

–

AO

AI

5/13

Page 6

¡ Semiconductor MSM6948/6948V

Name Description

RD

Demodulated serial data output.

This data is synchronized with the re-generated timing clock RT.

Receive data timing clock output.

This signal is re-generated by internal digital PLL.

Synchronizing to falling edge of RT, RD is output.

RT

CF

CT

RT

RD

Delay time (RT Æ RD) < 300 ns

Receive data timing clock is re-generated by digital PLL of which phase correcting speed can

be selected with CF.

When a digital "1" is put on CF and phase difference between receive data timing and RT is

more than 22.5 degree, phase correcting speed is high. In this case, as the phase difference

enters within 22.5 degrees, that speed changes to low immediately.

When digital "0" is input to CF, phase correcting speed of PLL remains low regardless of the

phase difference.

Usually, CF is connected to digital "1".

PLL's lock-in characteristics can be selected with CT.

When digital "1" is put on CT, PLL requires max. 50-bit alternative data pattern. On the other

hand, when digital "0" is input to CT,

PLL can be locked in below 18-bit data.

Equipment CT

Personal/MCA wireless terminals "1"

MCA wireless bases "0"

Control signal for the internal connection of AO.

FT

Refer to column AO.

When digital "0" is input to this pin, transmit LPF enters in power down mode, but the output

buffer operational amplifier remains active.

+5 V power supply.

V

DD

This device is sensitive to supply noises as switched capacitor techniques are utilized.

Bypass capacitors of more than 2.2 mF between V

and AG, and between VDD and DG are

DD

indispensable to ensure the performance.

6/13

Page 7

¡ Semiconductor MSM6948/6948V

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Condition Rating Unit

Power Supply Voltage V

Digital Input Voltage *2 V

Operating Temperature T

Storage Temperature T

DD

IA

ID

op

STG

Ta = 25°C

With respect to AG and DG

—

—

–0.3 to 7.0

–0.3 to VDD + 0.3

–0.3 to VDD + 0.3

–25 to 70

–55 to 150

VAnalog Input Voltage *1 V

°C

*1 TI, AI

*2 ME, SD, CF, CT, FT

RECOMMENDED OPERATING CONDITIONS

Parameter Symbol Condition Typ. Unit

V

Power Supply Voltage V

DD

With respect to AG and DG 54.75 5.25

Min. Max.

AG, DG — 0——

Operating Temperature

Crystal Resonant Frequency

Data Speed T

C1 — 2.2——

C2, C6 — 0.1——

C3 — 0.047——mF

C4 R

C5 — 0.047——

Temperature

Characteristics

Equivalent Series

Crystal

Resistance

T

f

X' TAL

—

—

—

—

—

—

—

—

—

op

—25–25 70 °C

— 3.68643.6860 3.6868 MHz

S

— 1200— — bit/sec

≥ 100 kW 0.01——

LX

25 ±5°C —–100 +100Frequency Deviation

ppm

At –40°C to +85°C —–100 +100

—

—

—— 100 W

16——pFLoad Capacitance

7/13

Page 8

¡ Semiconductor MSM6948/6948V

ELECTRICAL CHARACTERISTICS

DC and Digital Interface Characteristics

(V

= 5 V ±5%, Ta = –25°C to 70°C)

DD

Parameter Symbol Condition Typ. UnitMin. Max.

Normal Operating Mode 3—6Power Supply Current mA

f

= 3.6864 MHz ±0.01% 3.68643.6857 3.6871Oscilating Frequency

X'TAL

VIN = 0 V —–10 10

VIN = V

—

—

DD

—–10 10

—0 0.8

—2.2 V

DD

IOL = 1.6 mA —0 0.4

IOH = 400 mA—0.8V

RL > 50 kW

C

< 20 pF

L

DD

DD

—0 0.4

—0.6V

V

DD

V

DD

MHz

mA

V

Input Leakage Current *1

Input Voltage *1

Output Voltage *2

Output Voltage *3

f

V

V

V

V

I

DD

MCK

I

IL

I

IH

V

IL

V

IH

OL1

OH1

OL2

OH2

*1 ME, SD, CF, CT, FT

*2 ST, RD, RT

*3 MCK (NC : MSM6948V)

Analog Interface Characteristics

Transmit signal output (AO)

Parameter Symbol Condition Typ. UnitMin. Max.

f

V

R

M

S

OX

OX

LX

LX

OSX

Carrier Frequency

Carrier Level 0–2 +2 dBm

Output Resistance

Output Load Resistance R

Output Load Capacitance C

Output DC Voltage V

SD = "1" 12001199 1201

SD = "0"f

R

≥ 100 kW

L

£ 40 pF

C

L

f

AO

FT = "1"

ME = "1"

FT = "1"

ME = "1"

£ 4 kHz ——1

——100 —

———40pF

—V

= 5.0 V ±5%, Ta = –25°C to 70°C)

(V

DD

18001799 1801

V

DD

–

2

0.1

V

DD

2

V

DD

2

kW

+

0.1

Note 0 dBm = 0.775 Vrms

Hz

8/13

Page 9

¡ Semiconductor MSM6948/6948V

Voice signal input (TI)

Parameter Symbol Condition Typ. UnitMin. Max.

Input Signal Level

Input Resistance

GT VAO/V

TI

R

TI

—

f

£ 4 kHz —50 — kW

TI

TI

FT = "1"

ME = "0"

0–2 +2Voltage Gain dB

—— 0 dBmV

Built-in signal ground (SG)

Parameter Symbol Condition Typ. UnitMin. Max.

DC Voltage V

SG

V

Without DC Load V

DD

2

– 0.1

V

2

DD

V

DD

+ 0.1

2

Receive signal input (AI)

Parameter Symbol Condition Typ. UnitMin. Max.

Input Resistance R

Receive Signal Level V

IR

IR

Bit Error Rate BER N/N

S/N

at AI

f

£ 4 kHz — kW50 —

TI

—

8 dB

10 dB

——

——

— dBm–30 0

–3

1 ¥ 10

–5

5 ¥ 10

Re-generated receive data timing clock output (RT)

Parameter Symbol Condition Typ. UnitMin. Max.

Data Bit Number for PLL'

Lock-in

N

N

PLL1

PLL2

CF = "1"

CT= "0"

CT= "1"

*1 Data bit number to lock-in within 22.5 degree

*1

——18

bit

——50

9/13

Page 10

¡ Semiconductor MSM6948/6948V

BUILT-IN FILTER FREQUENCY CHARACTERISTICS

GAIN (dB)

0

–10

–20

–30

–40

–50

–60

–70

1

Transmit Low-Pass Filter

2345678910

FREQ (kHz)

GAIN (dB)

0

–10

–20

–30

–40

–50

–60

–70

0.5

Receive Band-Pass Filter

1 1.5 2 2.5 3 3.5 4

FREQ (kHz)

10/13

Page 11

¡ Semiconductor MSM6948/6948V

APPLICATION CIRCUIT

Crystal

3.6864 MHz

3.6864 MHz

Clock

Transmit Control

"1" : Data Signal (SD)

"0" : Voice Signal (TI)

Transmit Data

Transmit Data

Timing Clock

C6 C2

V

DD

1X1

2X2

3 *MCK

4ME

5SD

6ST

7SG

8AG

9DG

DD

18V

+

–

17FT

+5 V

C1

Filter Test

PLL's Lock-in Speed

16CT

"1" : Low Speed

"0" : High Speed

15CF

Phase Correcting Speed

"1" : High Speed Correction

"0" : Low Speed Correction

14RT

13RD

12AI

Receive Data Timing Clock

Receive Data

Receive Analog Signal

C3

11AO

Transmit Analog Signal

C4

10TI

Voice Signal

C5

*NC : MSM6948V

11/13

Page 12

¡ Semiconductor MSM6948/6948V

PACKAGE DIMENSIONS

(Unit : mm)

DIP18-P-300-2.54

Package material

Lead frame material

Pin treatment

Solder plate thickness

Package weight (g)

Epoxy resin

42 alloy

Solder plating

5 mm or more

1.30 TYP.

12/13

Page 13

¡ Semiconductor MSM6948/6948V

(Unit : mm)

SOP24-P-430-1.27-K

Mirror finish

Package material

Lead frame material

Pin treatment

Solder plate thickness

Package weight (g)

Epoxy resin

42 alloy

Solder plating

5 mm or more

0.58 TYP.

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which

are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki’s responsible sales person for the

product name, package name, pin number, package code and desired mounting conditions

(reflow method, temperature and times).

13/13

Loading...

Loading...