Page 1

1/10

¡

The MR27V3252D is a 32Mbit electrically Programmable Read-Only Memory with page mode. Its

configuration can be electrically switched between 2,097,152 word x 16bit and 4,194,304 word x 8

bit. The MR27V3252D operates on a single +3.3V power supply and is TTL compatible. The MR27

V3252D provides Page mode which can greatly reduce the read access time. Since the MR27V3252

D operates asynchronously , external clocks are not required , making this device easy-to-use. The

MR27V3252D is suitable as large-capacity fixed memory for microcomputers and data terminals. It

is manufactured using a CMOS double silicon gate technology and is offered in 44-pin SOP or 48pin TSOP packages.

1A

MR27V3252D

2,097,152-Word x 16-Bit or 4,194,304-Word x 8-Bit

8-Word x 16-Bit or 16-Word x 8-Bit Page Mode One Time PROM

DESCRIPTION

FEATURES

• 2,097,152 word x 16bit / 4,194,304 word x 8bit electrically switchable configuration

• Single +3.3V power supply

• Access time 100ns

Page mode access time 30ns

• Input / Output TTL compatible

• Three-state output

• Packages

44-pin plastic SOP (SOP44-P-600-1.27-K) (Product name : MR27V3252DMA)

48-pin plastic TSOP (TSOP II 48-P-550-0.80-K) (Product name : MR27V3252DTA)

Semiconductor

November 1999

Page 2

2/10

PIN CONFIGURATION (TOP VIEW)

MR27V3252D

45

A18

A8

A9

A11

A12

A13

A14

A15

A16

V

SS

D15/A-1

D7

D14

D6

D13

D5

D12

D4

V

CC

A10

44

43

42

4

5

6

7

41

40

39

38

8

9

10

11

37

36

35

34

12

13

14

15

33

32

31

30

16

17

18

19

29

28

27

26

20

21

22

23

2524

A19

A17

A7

A6

A5

A4

A3

A2

A1

A0

CE

V

SS

OE

D0

D8

D1

D9

D2

D10

D3

D11

48

NC

NC

47

1

2

NC

NC

NC

463

43

A18

A8

A9

A11

A12

A13

A14

A15

A16

V

SS

D15/A-1

D7

D14

D6

D13

D5

D12

D4

V

CC

A10

42

41

40

2

3

4

5

39

38

37

36

6

7

8

9

35

34

33

32

10

11

12

13

31

30

29

28

14

15

16

17

27

26

25

24

18

19

20

21

2322

A19

A17

A7

A6

A5

A4

A3

A2

A1

A0

CE

V

SS

OE

D0

D8

D1

D9

D2

D10

D3

D11

44

NC

1

BYTE/Vpp

BYTE/Vpp

48-pin TSOP (II)44-pin SOP

PIN NAMES

FUNCTIONS

D15/A-1 Data output / Address input

A0 - A20 Address input

D0 - D14 Data output

CE

OE

Output enable

V

CC

Power supply voltage

BYTE/V

PP

Mode switch / Program power supply voltage

NC

Non connection

Chip enable

V

SS

GND

A20

A20

Page 3

3/10

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

BLOCK DIAGRAM

D0

CE BYTE/V

PP

OE

CE PGMOE

Address Buffer

Row Decoder

Column Decoder

Memory Matrix

Multiplexer & Page Data Latch

Output Buffer

FUNCTION TABLE

STAND-BY

OUTPUT DISABLE

READ (8-Bit)

READ (16-Bit)

MODE

D15/A-1

CE OE

V

CC

LL

D

OUT

L

L

L/H

L

H

L

*

H

*

H

L

* : Don't Care

D1D2D3D4D5D6D7D8D9

D10

D11

D12

D13

D14

D15

X8/X16 Switch

A-1

In 8-bit output mode, these pins are

three-stated and pin D15 functions

as the A-1 address pin.

3.3V

D8 - D14D0 - D7

H

L

D

OUT

Hi-Z

H

Hi-Z

*

Hi-Z

PROGRAM

LH

D

IN

PROGRAM INHIBIT

H H Hi-Z

PROGRAM VERIFY

HL

D

OUT

9.75V

4.0V

MR27V3252D

BYTE/V

PP

2,097,152X16-Bit or 4,194,304X8-Bit

Page 4

4/10

Operating temperature under bias

Storage temperature

Input voltage

Output voltage

Power supply voltage

Program power supply voltage

Power dissipation per package

Parameter

Symbol

Topr

UnitValueCondition

RECOMMENDED OPERATING CONDITIONS FOR READ

VCC power supply voltage

VPP power supply voltage

Input "H" level

Input "L" level

Parameter Symbol

V

CC

Unit

3.6

Typ.

3.0

Condition

T

stg

V

I

V

O

V

CC

V

PP

P

D

0 to 70

-55 to 125

V-0.5 to V

CC

+ 0.5

V-0.5 to VCC + 0.5

V-0.5 to 5

V-0.5 to 11.5

W1.0

-

relative to V

SS

(Ta=0 to 70°C)

Min. Max.

V

V

CC

+0.5

-0.5

-

V

V

CC

+0.5*2.2

-

V

0.6-0.5**

-

V

V

PP

V

IH

V

IL

VCC=3.0V-3.6V

Voltage is relative to Vss

ABSOLUTE MAXIMUM RATINGS

-

-

MR27V3252D

°C

°C

* : Vcc+1.5V (Max.) when pulse width of overshoot is less than 10nS.

** : -1.5V (Min.) when pulse width of undershoot is less than 10nS.

Page 5

Output

0.4

-

5/10

ELECTRICAL CHARACTERISTICS (Read operation)

DC Characteristics

Input leakage current

Output leakage current

V

CC

power supply current

(Standby)

V

CC

power supply current

(Read)

V

PP

power supply current

Parameter

Symbol

UnitCondition

(V

CC

=3.3V±0.3V, Ta=0 to 70°C)

Input "H" level

Input "L" level

Output "H" level

Output "L" level

Voltage is relative to Vss

10

Typ.

-

Min. Max.

I

LO

I

CS1

I

CS2

I

CCA

µA

10

-

µA

50

-

µA

-

CE=V

CC

1

-

CE=V

IH

100

-mA

tc=100ns

-

-

I

PP

V

IH

V

IL

V

OH

V

OL

10

µA

V

PP=VCC

VCC+0.5*

2.2

V

-

0.6

-0.5** V

-

-2.4

V

I

OH

=-400µA

-

VI

OL

=2.1mA

-

-

-

CE=V

IL ,

OE=V

IH

VI=0 to Vcc

VO=0 to Vcc

MR27V3252D

mA

-

800ohms

100pF

2.08V

AC Characteristics

Address access time

Parameter

Symbol

T

ACC

UnitCondition

(V

CC

=3.3V±0.3V, Ta=0 to 70°C)

Min. Max.

ns

CE=OE=V

IL

100

Address access cycle time

T

C

100

ns

-

-

0V/3V

0.8V/2.0V

100pF

0.8V/2.0V

Measurement conditions

Input signal level

Input timing reference level

Output load

Output timing reference level

-

ns

CE access time

OE access time

Output disable time

-

T

CE

-

OE=V

IL

40

-

ns

CE=V

IL

30

0

ns

OE=V

IL

25

0

ns

-

0

T

OE

T

OH

CE=V

IL

CE=OE=V

IL

Output hold time

100

T

CHZ

T

OHZ

30

-

30

ns

ns

ns

Page access cycle time

Page access time

T

PC

T

PAC

-

-

I

LI

* : Vcc+1.5V (Max.) when pulse width of overshoot is less than 10nS.

** : -1.5V (Min.) when pulse width of undershoot is less than 10nS.

Page 6

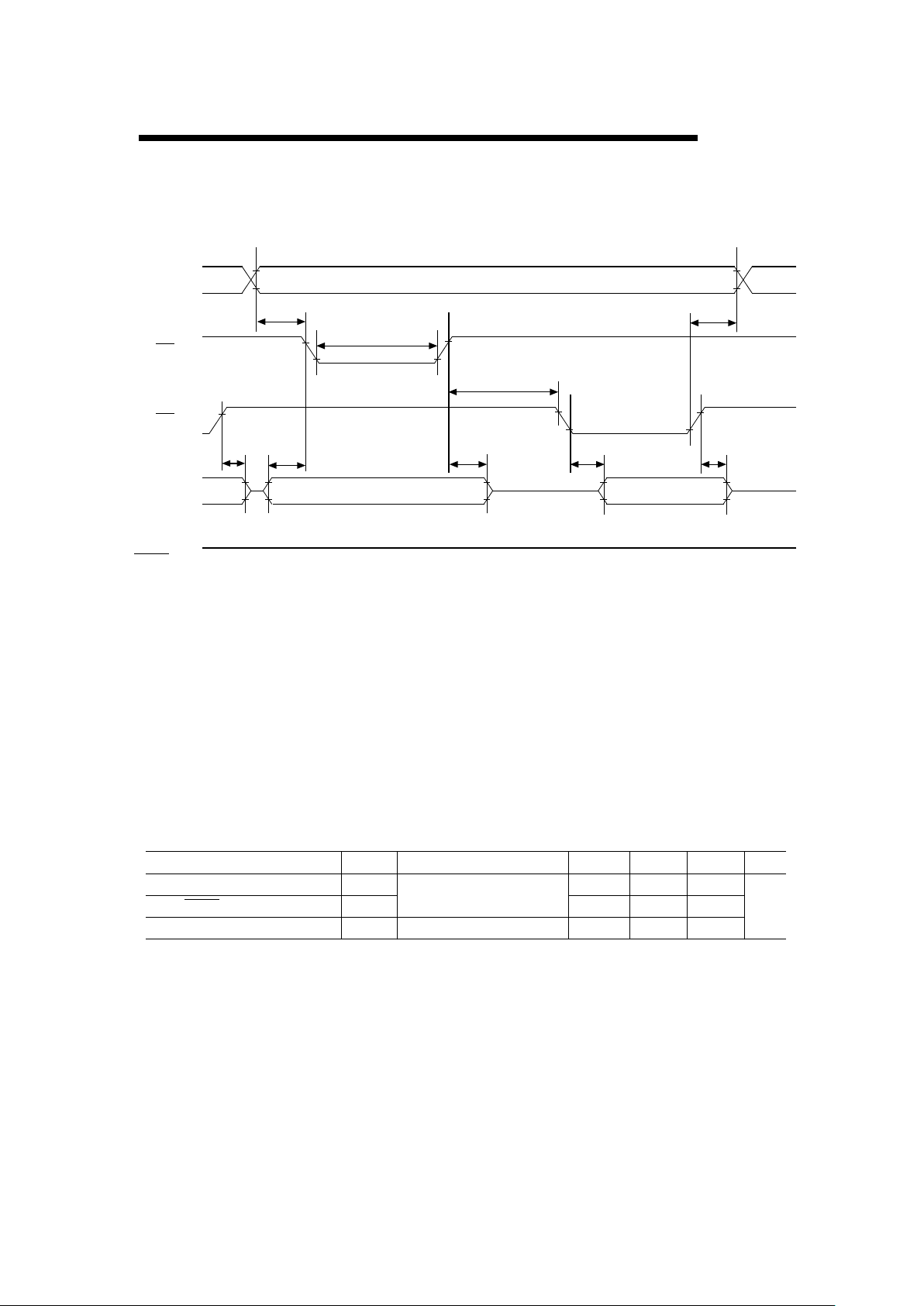

t

OHZ

A0 - A2 (Word mode)

A-1 - A2 (Byte mode)

ADDRESS

t

OH

t

CE

t

CHZ

t

OE

t

OHZ

t

ACC

CE

OE

Valid Data

Hi-ZHi-Z

DOUT

t

OH

t

CE

t

CHZ

t

OE

t

ACC

CE

OE

Hi-Z

Hi-Z

TIMING CHART

NORMAL MODE READ CYCLE

PAGE MODE READ CYCLE

t

PAC

t

PAC

DOUT

t

C

t

C

A3 - A20

t

PC

t

PC

MR27V3252D

6/10

Page 7

1

FF00

00FF

7/10

ELECTRICAL CHARACTERISTICS (Programming operation)

DC Characteristics

Input leakage current

V

PP

power supply current (Program)

V

CC

power supply current

Parameter

Symbol

I

LI

Unit

10

Typ.

-

Condition

(Ta=25°C±5°C)

Min. Max.

Input "L" level

I

PP2

I

CC

V

IH

V

IL

µA

-

V

I=VCC

+0.5V

50

-

mA

-

CE=V

IL

80

-

mA

-VCC+0.5

3.0

V

-

0.8

-0.5

V

-

-

9.75

-

Voltage is relative to Vss

Input "H" level

V

OH

-

2.4

VIOH=-400µA

-

Output "H" level

V

OL

0.45

-

V

I

OL

=2.1mA

-

Output "L" level

V

PP

10.09.5

V

-

Program voltage

V

CC

power supply voltage

V

CC

4.1

3.9

V

4.0

-

MR27V3252D

Pin Check Function

Pin Check Function is to check contact between each device-pin and each socket-lead with EPROM

programmer.

Setting up address as the following condition call the preprogrammed codes on device outputs.

A0

(Vcc=3.3V

±0.3V,CE=OE=V

IL

,BYTE/Vpp=V

IH

,Ta=25°C±5°C)

A1

A2 A3

A4

A5 A6

A7

A8 A9

A10

A11 A12

A13

A14 A15

A16

A17

A18 A19

010101010VH* 0

1

0101001

1

1

0

1

0

1

0101 VH*

1

01010110

0

DATA

* :VH=8V

±0.25V

A20

0

AC Characteristics

Address set-up time

OE set-up time

Data set-up time

Parameter

Symbol

T

AS

Unit

-

Typ.

100

Condition

Min. Max.

Data hold time

T

OES

T

DS

T

AH

T

DH

ns

-

-

2

µs

-

-

100

ns

--

-

2

µs

-

-

100 ns

-

-

-

Address hold time

T

OHZ

100

0

ns-

Output float delay from OE

T

VS

-

2

µs

-

V

PP

voltage set-up time

Program pulse width

T

PW

119

µs

10

-

Data valid from OE

T

OE

100

-

ns

--

-

-

-

-

(V

cc

=4.0V±0.1V,Vpp=9.75V±0.25V,Ta=25°C±5°C)

ns

Address hold from OE high

T

AHO

-

0

--

FFFFOther conditions

Page 8

Consecutive Programming Waveforms

A0 - A20

D0 - D15

BYTE/V

PP

OE

CE

Din Din

High

t

AS

t

AH

t

PW

t

DS

t

DH

t

VS

8/10

MR27V3252D

Consecutive Program Verify Waveforms

A0 - A20

D0 - D15

OE

CE

Dout

High

t

ACC

t

AHO

t

OE

t

OHZ

Dout

BYTE/V

PP

9.75V

Page 9

Program and Program Verify Cycle Waveforms

A0 - A20

D0 - D15

OE

CE

Din

t

AS

t

DH

Dout

BYTE/V

PP

9.75V

9/10

MR27V3252D

PIN Capacitance

Input

BYTE/V

PP

Parameter

C

IN1

Unit

8

Typ.

-

(VCC=3.3V, Ta=25°C, f=1MHz)

Min. Max.

C

IN2

pF

-

V

I

=0V

120

--

Output

C

OUT

10

--

V

O

=0V

Symbol

Condition

t

PW

t

OES

t

OE

t

OHZ

t

DS

t

OHZ

t

AHO

Page 10

Bad insertion

YES

Increment Address

Program 10µs

10/10

Programming / Verify Flow Chart

MR27V3252D

VCC=4.0V

VPP=9.75V

X=0

YES

PASS

NO

NG

NO

NG

PASS

X=2?

X=X+1

YES

NO

VCC=3.0V

VPP=3.0V

Programming

Pin Check

NO

OK

V

CC

=3.6V

V

PP

=3.6V

NG

PASS

VCC=3.0V

V

PP

=3.0V

NG

PASS

Verify

NO

OK

Start

Start

Pin Check

Last Address ?

Increment Address

Address = First location

Program 10µs

Verify (One Byte)

Last Address ?

Verify (One Byte)

Device Passed Device Failed

Device Passed Device Failed

Verify (One Byte)

Verify (One Byte)

Bad insertion

Address = First location

Address = First location

Loading...

Loading...