Page 1

查询MR27V3252D供应商

¡

Semiconductor

MR27V3252D

2,097,152-Word x 16-Bit or 4,194,304-Word x 8-Bit

8-Word x 16-Bit or 16-Word x 8-Bit Page Mode One Time PROM

DESCRIPTION

The MR27V3252D is a 32Mbit electrically Programmable Read-Only Memory with page mode. Its

configuration can be electrically switched between 2,097,152 word x 16bit and 4,194,304 word x 8

bit. The MR27V3252D operates on a single +3.3V power supply and is TTL compatible. The MR27

V3252D provides Page mode which can greatly reduce the read access time. Since the MR27V3252

D operates asynchronously , external clocks are not required , making this device easy-to-use. The

MR27V3252D is suitable as large-capacity fixed memory for microcomputers and data terminals. It

is manufactured using a CMOS double silicon gate technology and is offered in 44-pin SOP or 48pin TSOP packages.

FEATURES

• 2,097,152 word x 16bit / 4,194,304 word x 8bit electrically switchable configuration

• Single +3.3V power supply

• Access time 100ns

Page mode access time 30ns

• Input / Output TTL compatible

• Three-state output

• Packages

44-pin plastic SOP (SOP44-P-600-1.27-K) (Product name : MR27V3252DMA)

48-pin plastic TSOP (TSOP II 48-P-550-0.80-K) (Product name : MR27V3252DTA)

1A

November 1999

1/10

Page 2

PIN CONFIGURATION (TOP VIEW)

MR27V3252D

NC

A18

A17

A7

A6

A5

A4

A3

A2

A1

A0

CE

V

SS

OE

D0

D8

D1

D9

D2

D10

D3

D11

10

11

12

13

14

15

16

17

18

19

20

21

NC

1

NC

2

A20

1

2

3

4

5

6

7

8

9

44

A19

43

A8

42

A9

41

A10

40

A11

39

A12

38

A13

37

A14

36

A15

35

A16

34

33

BYTE/Vpp

V

32

D15/A-1

31

D7

30

D14

29

D6

28

D13

27

D5

26

D12

25

D4

24

V

2322

SS

CC

NC

A18

A17

A7

A6

A5

A4

A3

A2

A1

A0

CE

V

SS

OE

D0

D8

D1

D9

D2

D10

D3

D11

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

NC

48

NC

47

A20

463

A19

45

A8

44

A9

43

A10

42

A11

41

A12

40

A13

39

A14

38

A15

37

A16

36

35

BYTE/Vpp

V

34

D15/A-1

33

D7

32

D14

31

D6

30

D13

29

D5

28

D12

27

D4

26

V

2524

SS

CC

PIN NAMES

FUNCTIONS

D15/A-1 Data output / Address input

A0 - A20 Address input

D0 - D14 Data output

CE

OE

V

CC

V

SS

BYTE/V

NC

PP

Chip enable

Output enable

Power supply voltage

GND

Mode switch / Program power supply voltage

Non connection

48-pin TSOP (II)44-pin SOP

2/10

Page 3

BLOCK DIAGRAM

MR27V3252D

A-1

X8/X16 Switch

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

Address Buffer

CE BYTE/V

OE

CE PGMOE

Memory Matrix

Row Decoder

2,097,152X16-Bit or 4,194,304X8-Bit

Multiplexer & Page Data Latch

Output Buffer

Column Decoder

D0

D1D2D3D4D5D6D7D8D9

PP

D10

D11

D12

D13

D14

D15

FUNCTION TABLE

MODE

READ (16-Bit)

READ (8-Bit)

OUTPUT DISABLE

STAND-BY

PROGRAM

PROGRAM INHIBIT

PROGRAM VERIFY

* : Don't Care

In 8-bit output mode, these pins are

three-stated and pin D15 functions

as the A-1 address pin.

PP

V

CC

3.3V

4.0V

D

OUT

D8 - D14D0 - D7

D

Hi-Z

Hi-Z

Hi-Z

D

D

L

H

*

BYTE/V

H

L

H

L

H

L

CE OE

LL

L

L

H

LH

H H Hi-Z

9.75V

HL

D15/A-1

OUT

L/H

*

*

IN

OUT

3/10

Page 4

ABSOLUTE MAXIMUM RATINGS

MR27V3252D

Parameter

Operating temperature under bias

Storage temperature

Input voltage

Output voltage

Power supply voltage

Program power supply voltage

Power dissipation per package

Symbol

Topr

T

stg

V

I

V

O

V

CC

V

PP

P

D

-

relative to V

-

SS

RECOMMENDED OPERATING CONDITIONS FOR READ

Parameter Symbol

VCC power supply voltage

VPP power supply voltage

Input "H" level

Input "L" level

V

CC

V

PP

V

IH

V

IL

Voltage is relative to Vss

* : Vcc+1.5V (Max.) when pulse width of overshoot is less than 10nS.

** : -1.5V (Min.) when pulse width of undershoot is less than 10nS.

Condition

VCC=3.0V-3.6V

0 to 70

-55 to 125

+ 0.5

CC

(Ta=0 to 70°C)

Min. Max.

3.0

-0.5

Typ.

-

-

-

-

3.6

+0.5

V

CC

+0.5*2.2

V

CC

0.6-0.5**

UnitValueCondition

°C

°C

V-0.5 to V

V-0.5 to VCC + 0.5

V-0.5 to 5

V-0.5 to 11.5

W1.0

Unit

V

V

V

V

4/10

Page 5

ELECTRICAL CHARACTERISTICS (Read operation)

DC Characteristics

Parameter

Input leakage current

Output leakage current

V

power supply current

CC

(Standby)

V

power supply current

CC

(Read)

V

power supply current

PP

Input "H" level

Input "L" level

Output "H" level

Output "L" level

Voltage is relative to Vss

* : Vcc+1.5V (Max.) when pulse width of overshoot is less than 10nS.

** : -1.5V (Min.) when pulse width of undershoot is less than 10nS.

Symbol

I

LI

I

LO

I

CS1

I

CS2

I

CCA

I

PP

V

IH

V

IL

V

OH

V

OL

VI=0 to Vcc

VO=0 to Vcc

CE=V

IL ,

tc=100ns

I

CE=V

CE=V

OE=V

V

PP=VCC

=-400µA

OH

=2.1mA

OL

CC

IH

IH

-

-

MR27V3252D

=3.3V±0.3V, Ta=0 to 70°C)

(V

CC

Min. Max.

2.2

-0.5** V

Typ.

-

-

-

-

-mA

-

-

-

-

-

-

-

-

-

10

10

50

100

10

VCC+0.5*

0.6

-

-

0.4

UnitCondition

µA

µA

µA

1

mA

µA

V

-2.4

V

VI

AC Characteristics

Parameter

Address access cycle time

Address access time

Page access cycle time

Page access time

CE access time

OE access time

Output disable time

Output hold time

Symbol

T

C

T

ACC

T

PC

T

PAC

T

CE

T

OE

T

CHZ

T

OHZ

T

OH

Measurement conditions

Input signal level

Input timing reference level

Output load

Output timing reference level

-

CE=OE=V

-

-

OE=V

IL

CE=V

IL

OE=V

IL

CE=V

IL

CE=OE=V

0V/3V

0.8V/2.0V

100pF

0.8V/2.0V

2.08V

=3.3V±0.3V, Ta=0 to 70°C)

(V

CC

Min. Max.

100

IL

-

30

-

-

-

0

0

IL

0

-

100

-

30

100

40

30

25

-

UnitCondition

ns

ns

ns

ns

ns

ns

ns

ns

ns

Output

800ohms

100pF

5/10

Page 6

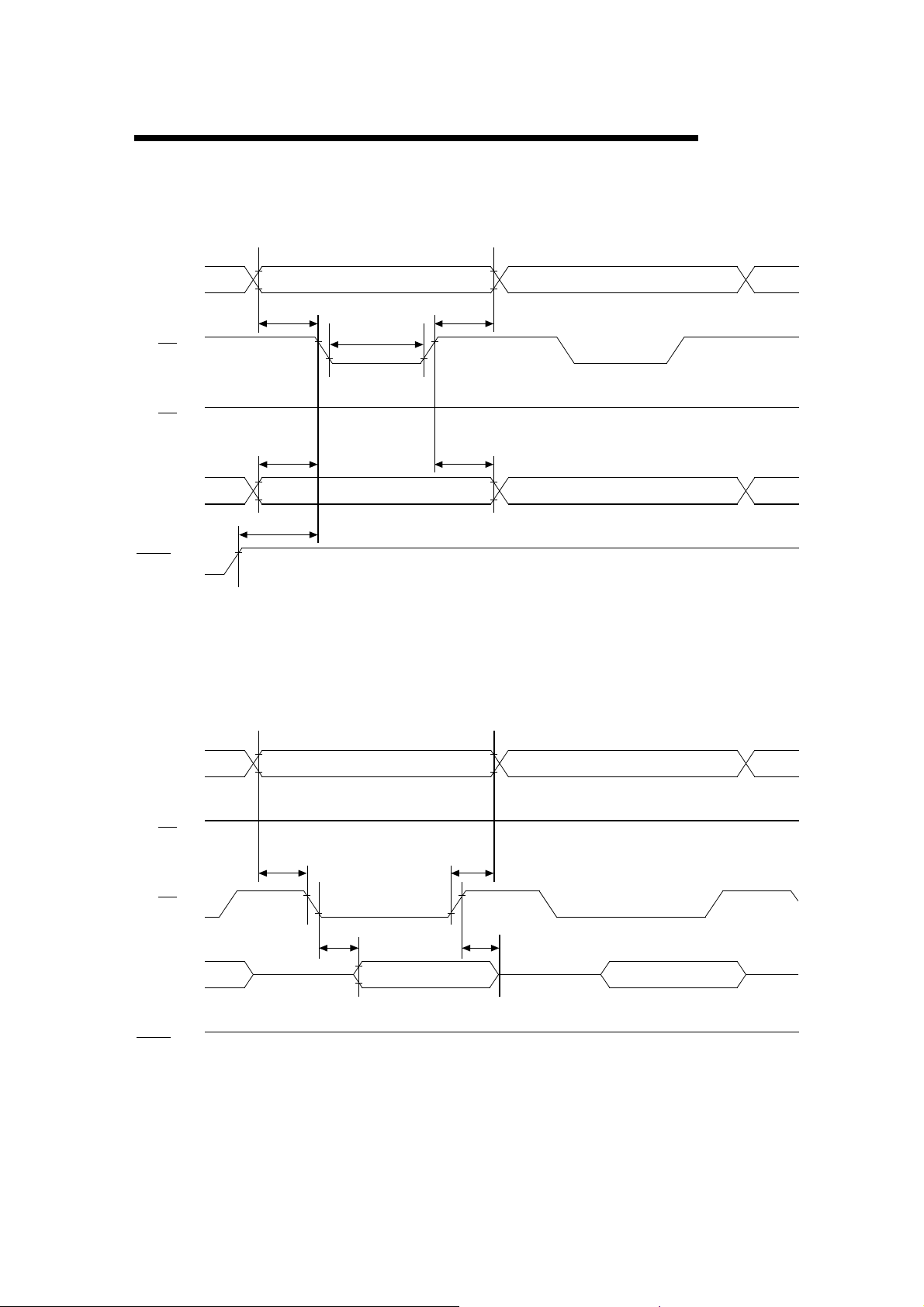

TIMING CHART

NORMAL MODE READ CYCLE

ADDRESS

CE

OE

MR27V3252D

t

C

t

t

CE

t

OE

OH

t

CHZ

DOUT

PAGE MODE READ CYCLE

A3 - A20

A0 - A2 (Word mode)

A-1 - A2 (Byte mode)

CE

t

ACC

t

OHZ

Valid Data

Hi-ZHi-Z

t

C

t

PC

t

CE

t

OE

t

PC

t

OH

t

CHZ

OE

DOUT

Hi-Z

t

ACC

t

PAC

t

PAC

t

OHZ

6/10

Hi-Z

Page 7

ELECTRICAL CHARACTERISTICS (Programming operation)

DC Characteristics

Parameter

Input leakage current

V

power supply current (Program)

PP

power supply current

V

CC

Input "H" level

Input "L" level

Output "H" level

Output "L" level

Program voltage

V

power supply voltage

CC

Voltage is relative to Vss

AC Characteristics

Parameter

Address set-up time

OE set-up time

Data set-up time

Address hold time

Data hold time

Output float delay from OE

voltage set-up time

V

PP

Program pulse width

Data valid from OE

Address hold from OE high

Symbol

I

LI

I

PP2

I

CC

V

IH

V

IL

V

OH

V

OL

V

PP

V

CC

Symbol

T

AS

T

OES

T

DS

T

AH

T

DH

T

OHZ

T

VS

T

PW

T

OE

T

AHO

Condition

V

+0.5V

I=VCC

CE=V

IL

-

-

=2.1mA

I

OL

-

-

(V

=4.0V±0.1V,Vpp=9.75V±0.25V,Ta=25°C±5°C)

cc

Condition

-

-

-

-

-

-

-

Min. Max.

-

-

-

3.0

-0.5

2.4

-

3.9

Min. Max.

100

2

100

2

100 ns

0

2

-

0

Typ.

-

-

--

-

-

-

-

9.75

4.0

Typ.

-

-

--

-

-

-

10

--

--

MR27V3252D

(Ta=25°C±5°C)

Unit

10

50

80

VCC+0.5

0.8

-

0.45

10.09.5

4.1

µA

mA

mA

V

V

VIOH=-400µA

V

V

V

Unit

-

-

-

-

ns

µs

ns

µs

-

100

-

119

100

-

ns-

µs

µs

ns

ns

Pin Check Function

Pin Check Function is to check contact between each device-pin and each socket-lead with EPROM

programmer.

Setting up address as the following condition call the preprogrammed codes on device outputs.

(Vcc=3.3V

A0

A1

A2 A3

A4

A5 A6

A7

A8 A9

010101010VH* 0

1

1

0

0

0101 VH*

1

±0.3V,CE=OE=V

A11 A12

A10

1

01010110

1

A13

0101001

,BYTE/Vpp=V

IL

A14 A15

A16

A17

IH

A18 A19

* :VH=8V

,Ta=25°C±5°C)

A20

1

1

0

±0.25V

0

7/10

DATA

FF00

00FF

FFFFOther conditions

Page 8

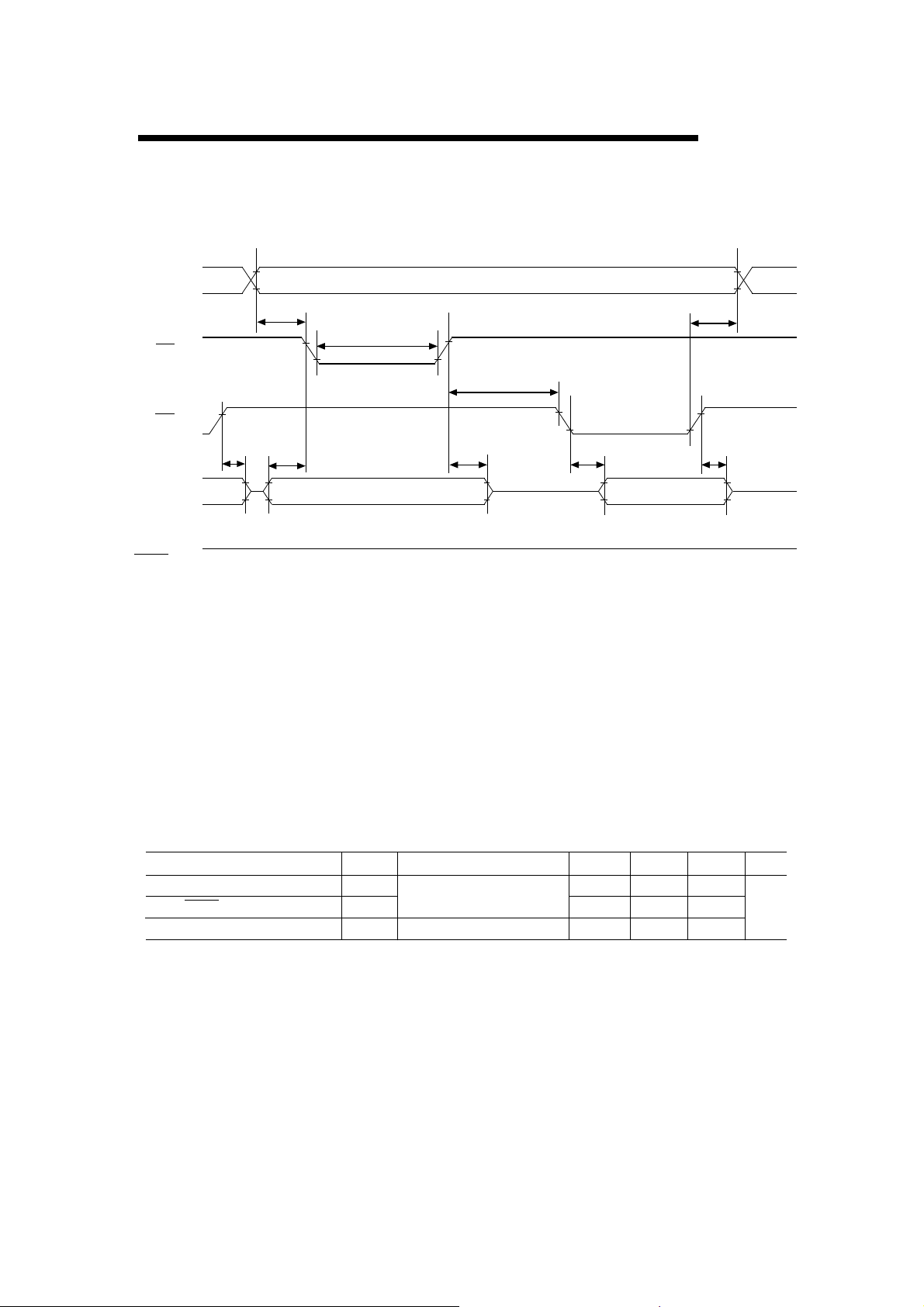

Consecutive Programming Waveforms

A0 - A20

MR27V3252D

t

AS

t

PW

CE

High

OE

t

DS

D0 - D15

t

VS

BYTE/V

PP

Consecutive Program Verify Waveforms

Din Din

t

AH

t

DH

A0 - A20

CE

OE

D0 - D15

BYTE/V

PP

t

ACC

High

t

AHO

t

OE

Dout

t

OHZ

Dout

9.75V

8/10

Page 9

Program and Program Verify Cycle Waveforms

A0 - A20

MR27V3252D

CE

OE

D0 - D15

BYTE/V

PP

t

OHZ

t

AS

t

PW

t

OES

t

DS

t

DH

t

OE

Din

Dout

t

AHO

t

OHZ

9.75V

PIN Capacitance

Parameter

Input

BYTE/V

PP

Output

Symbol

C

IN1

C

IN2

C

OUT

Condition

=0V

V

I

V

=0V

O

(VCC=3.3V, Ta=25°C, f=1MHz)

Min. Max.

-

--

Typ.

120

--

Unit

8

pF

10

9/10

Page 10

Programming / Verify Flow Chart

MR27V3252D

Programming

Bad insertion

Increment Address

Start

NO

Pin Check

OK

Address = First location

VCC=4.0V

VPP=9.75V

Program 10µs

NO

Last Address ?

YES

Verify

Start

Pin Check

OK

Address = First location

VCC=3.0V

V

=3.0V

PP

Verify (One Byte)

V

=3.6V

CC

V

=3.6V

PP

Verify (One Byte)

NO

Bad insertion

NG

PASS

NG

Increment Address

Address = First location

X=0

Verify (One Byte)

PASS

NO

Last Address ?

YES

VCC=3.0V

VPP=3.0V

Verify (One Byte)

PASS

PASS

Device Passed Device Failed

NG

X=X+1

YES

X=2?

NO

Program 10µs

NG

Device Passed Device Failed

10/10

Loading...

Loading...