Page 1

MITSUMI

Wide Discriminator MM1327

Wide Discriminator

Monolithic IC MM1327

Outline

This IC identifies the letter box portion of wide broadcast, etc. video signals. The luminance and chroma

signals are used so that the rate of identification on dark screens is increased. Output is the total of 6bit ADC

data and character signal, etc. white peak signal discriminator bit, for 7bit data output.

In addition, an EDTV2 simple discrimination function is built-in.

Features

1. Signal level discrimination using composite luminance and chroma signal

2. Discrimination of video signal within horizontal scanning interval can be done every scan due to integrated

output

3. Built-in white peak detection circuit for subtitles

4. Built-in EDTV2 simple discrimination function

5. 22H discrimination output (COMB-THROUGH) circuit built-in

6. Built-in window limiter circuit

7. Data output is 7bit serial output format : 6bit ADC + peak detection

8. Operates on +5V single power supply

Package

SDIP-30

Applications

Wide TV

Page 2

MITSUMI

SDIP-30

13 6

10

24587129

11 151413

30 24 2127 25 23 22 2026 161729 28 1819

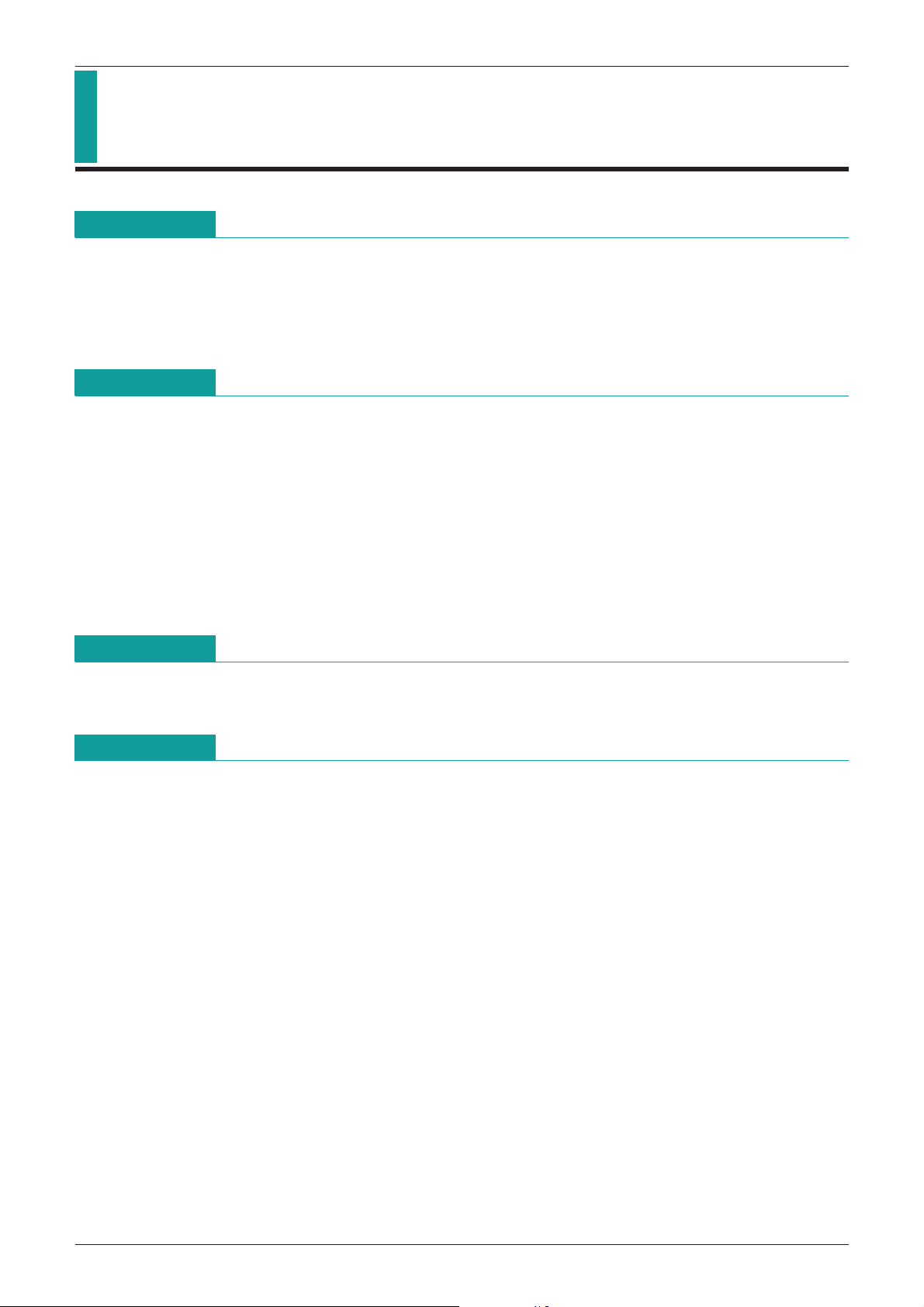

Block Diagram

Wide Discriminator MM1327

Pin Assignment

1 I 16 ADCLK

2 Q 17 NRZCLK

3 Y 18 DATA

4 AGND 19 EDTV2

5 MAX 20 VDO

6 VCOM 21 COMB

7 ZR 22 LIMIT

8 INT IN 23 COMB

9 INT OUT 24 NTSC/PAL

10 S/H 25 IR

11 DA 26 DELAY

12 DGND 27

13 HD 28

14 VD 29 GC

15 GP 30 V

SEPA-LEVEL

LIMIT-LEVEL

CC

-

-

-

TH

SW

SW

Page 3

MITSUMI

Wide Discriminator MM1327

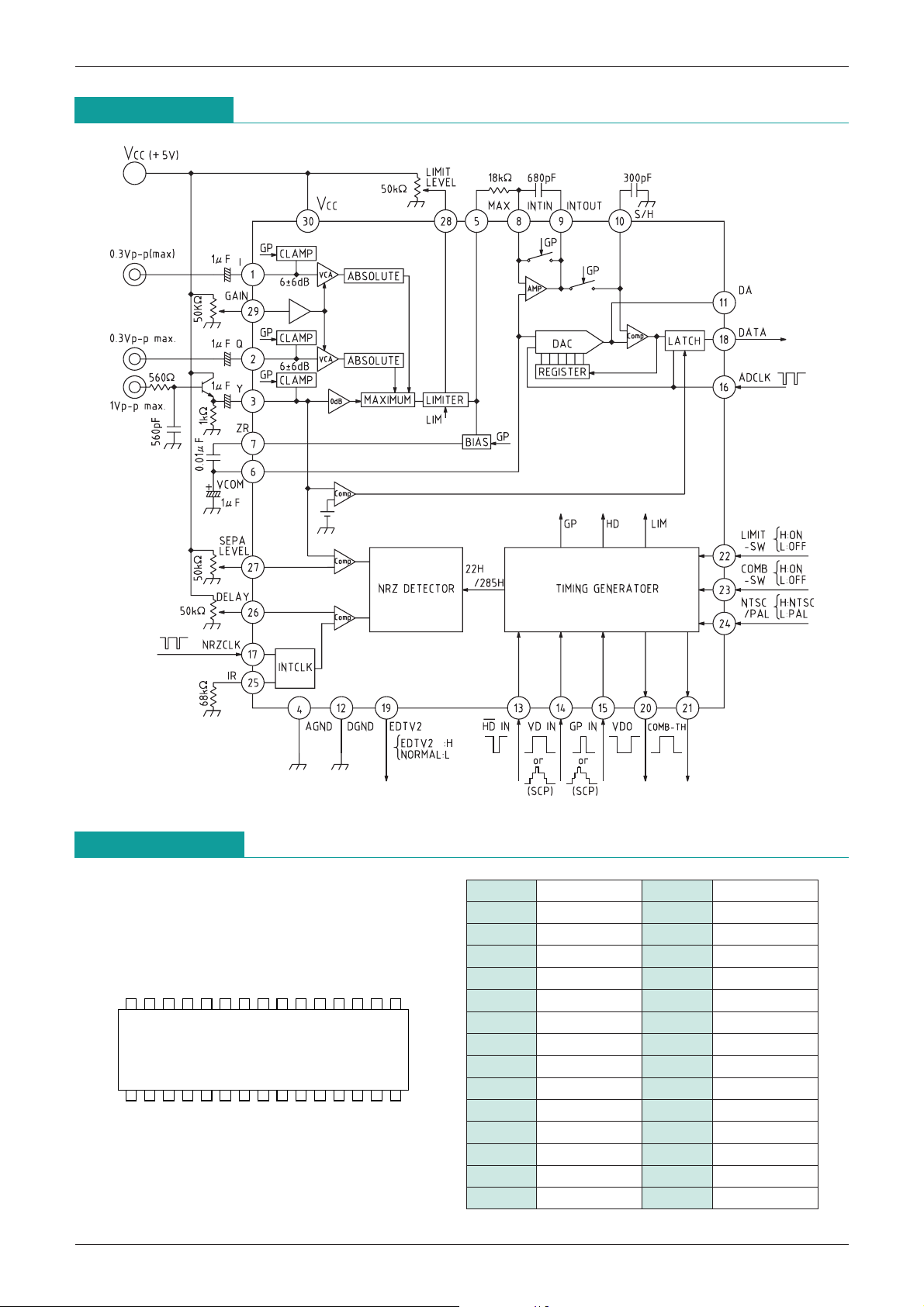

Pin Description

Pin no. Pin name Function Internal equivalent circuit diagram

1 I Video signal input pin

2 Q

3 Y

4 AGND

12 DGND

5 MAX

Composite output of input

video signal maximum

value

6 VCOM

7 ZR

8 INT IN

Internal reference voltage

output

Connect 1µF between this

pin and GND.

Connection pin for MAX

output clamp capacitor

Integrated circuit input pin

Integrated reset done at GP

timing.

Page 4

MITSUMI

Wide Discriminator MM1327

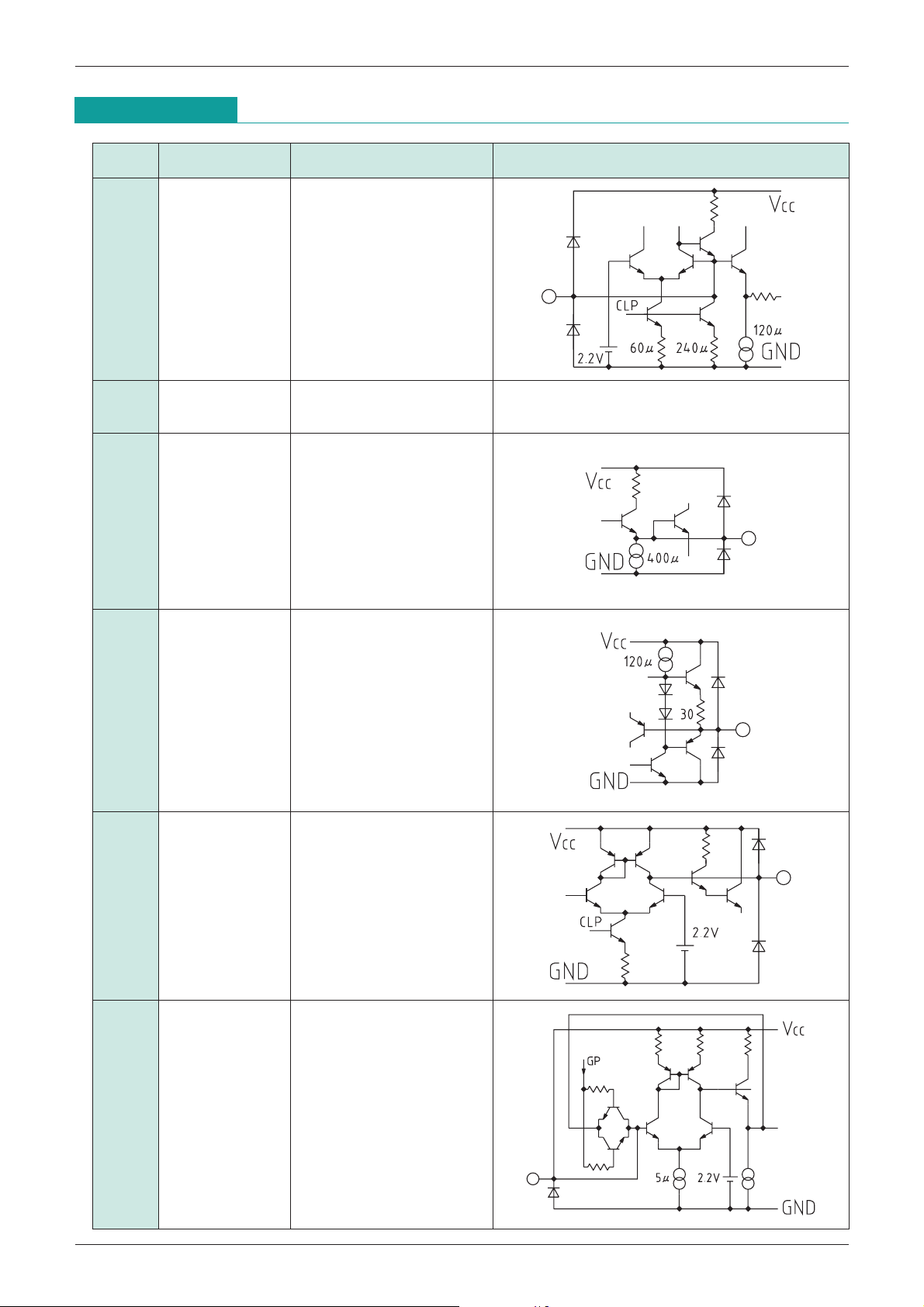

Pin no. Pin name Function Internal equivalent circuit diagram

9 INT OUT

10 S/H

11 DA

13 HD

--------------------------------------

IN

15 GP IN

Integrated output pin and

sample and hold pins

S/H of integration results

at HD timing

DAC output for consecutive

comparison ADC

Timing pulse input pins

GP operates even on SCP

14 VD IN

16 ADCLK

input (5V

P

-

P).

Timing pulse input pin

VD operates even on SCP

input (5V

P

-

P).

Clock input pin for

consecutive ADC

Page 5

MITSUMI

Wide Discriminator MM1327

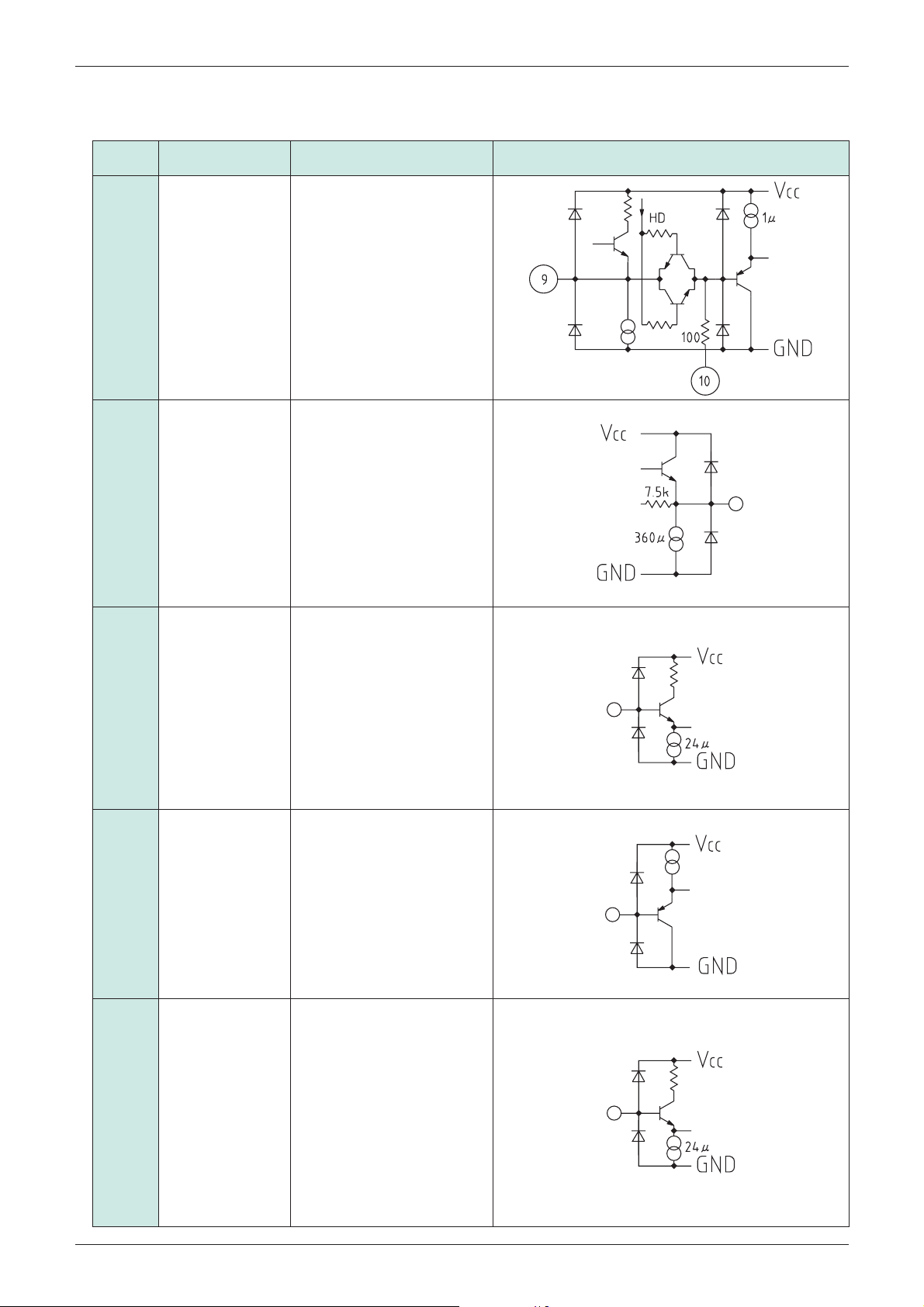

Pin no. Pin name Function Internal equivalent circuit diagram

17 NRZCLK

25 IR

26 DELAY

18 DATA

19 EDTV2

20 VDO

21 COMB

-

TH

22 LIMIT-SW

23 COMB

-

SW

24 NTSC/PAL

Clock input pins for NRZ

discrimination

Input CLK is integrated by

resistor connected between

Pin 25 and GND and

internal 20pF, and delay is

set by Pin 26 voltage.

Data output pins

Switching pins

27 SEPA LEVEL

28 LIMIT LEVEL

29 GAIN

NRZ discrimination

luminance signal SEPA

level adjustment pin

MAX composite output

limit level adjustment pin

Limit area:

NTSC : 42~241H

PAL : 46~291H

I, Q gain adjustment pin

30 VCC

Page 6

MITSUMI

Absolute Maximum Ratings

Item Symbol Ratings Units

Operating temperature T

OPR

Wide Discriminator MM1327

-

20~+75 °C

Storage temperature T

Power supply voltage V

Input voltage V

CC max. 7.0 V

IN max. GND

Allowable loss Pd 800 mW

Recommended Operating Conditions

Item Symbol Ratings Units

Operating temperature T

Operating voltage V

STG

OPR

OPR 4.5~5.5 V

-

40~+125 °C

<

<

=

-

20~+75 °C

VIN

V

CC V

=

Page 7

MITSUMI

Wide Discriminator MM1327

Electrical Characteristics

Item Symbol Measurement conditions Min. Typ. Max. Units

Consumption current I

MAX amp

Clamping level I V

MAX output pin voltage V max.

Maximum input level I V max.

Y input voltage gain G

Maximum gain

VCA

Minimum gain

I, Q gain difference G

(Except where noted otherwise, Ta=25°C, VCC=5.0V)

CC 20 30 mA

Y V

Q V

Y V max.

YIN

IIN

QIN

Y 1.0

I 0.6 VP

1 2.0 2.2 2.4

*

1 2.0 2.2 2.4 V

*

1 2.0 2.2 2.4

*

1 2.0 2.2 2.4 V

*

Q V max.Q 0.6

Y

I G max.

Q G max.

I G min.

Q G min.

IQ GIQ=GI

I VGC=1.2V

Q VGC=1.2V

I VGC=3.6V

Q VGC=3.6V

*

2

3 +11.5 +12.0 +12.5

*

3 +11.5 +12.0 +12.5

*

3

*

3

*

-

GQ

-

0.5 0.0 0.5 dB

-

0.5 0.0 0.5

-

0.5 0.0 0.5

-

0.5 0.0 0.5 dB

dB

dB

-

P

EDTV II discrimination

NRZ detection level

NRZ detection readout timing

NRZCLK pin input current

IR pin voltage V

EDTV II output voltage L V

Trigger signal

Sync signal separation level VD

HD pin input current

VD pin input current

GP pin input current

L V

H V

L V

H V

L I

H I

HD

IN VTHD HD 2.30 2.50 2.70

IN VTVD VD or SCP 0.63 0.83 1.03 V

GP

IN VTGP GP or SCP 3.69 3.89 4.09

L I

H I

L I

H I

L I

H I

YSL 57

YSH 27 30

CSL 0.4 0.7

CSH 1.5 1.8

NRZCL VNRZCLK=0.4V 1

NRZCH VNRZCLK=4.5V 1

IR 2.2 2.4 2.6 V

NL INL=1mA 0.4 V

HDL VHD=0.4V 1

HDH VHD=4.5V 1

VDL VVD=0.4V 1

VDH VVD=4.5V 1

GPL VGP=0.4V 1

GPH VGP=4.5V 1

IRE

µS

µA

µA

µA

µA

COMB-SW switching voltage

COMB-TH output voltage L V

VDO output voltage L V

L VTCOSL 0.7

H V

TCOSH 2.1

OCOMB ICOMB=1mA 0.4 V

OVDO IVDO=1mA 0.4 V

V

Page 8

MITSUMI

0.3V

0V

5V

0V

63.5µS

2µS

I or Q signal

GP pin

100IREY input

INT OUT output

V

INTL

Wide Discriminator MM1327

Note 1 :

Note 2 :

Note 3 :

Note 4 :

1 Clamp level and MAX output pin voltage

*

Measure voltage on each pin when GPIN and HDIN are connected to V

2 Y input voltage gain

*

Input a sweep signal to Y input, input a clamp pulse synchronized to H

measure voltage gain at MAX pin for 100kHz.

3 I, Q max/min gain

*

Input a square wave signal as shown below and a GPIN signal to I input (or Q input) and GPIN

pin, and measure voltage gain at MAX pin.

4 MAX amp limit level

*

Measure limit level at MAX pin when LIMIT-SW pin is high. However, the limit range is as follows

for the NTSC/PAL pin.

CC.

SYNC to GPIN pin, and

Note 5 :

Note 6 :

5 Offset voltage for reset

*

Connect GPIN pin to V

6 Integrated limit voltage

*

Input a 100% white signal to Y input and a clamp pulse synchronized to H

Measure INT OUT pin voltage at integration end at this time.

CC and measure potential difference between INT IN pin and INT OUT pin.

SYNC to GPIN pin.

Page 9

MITSUMI

259H

Composite

1st field 2nd field

SCP

GP

VB

RB

VDO

COMB-TB

25H

260H 261H 262H

1H 2H 3H 4H 5H 6H 7H 8H 9H 10H 11H 12H 13H 14H 15H 16H 17H 18H 19H 20H 21H 22H 23H 24H

-

5V

-

5V

-

5V

-

5V

-

2.8V

-

1.7V

-

0V

-

0V

-

0V

-

0V

260H

Composite

1st field 2nd field

SCP

GP

VB

RB

VDO

COMB-TB

25H

261H 262H 263H

1H 2H 3H 4H 5H 6H 7H 8H 9H 10H 11H 12H 13H 14H 15H 16H 17H 18H 19H 20H 21H 22H 23H 24H

-

5V

-

5V

-

5V

-

5V

-

2.8V

-

1.7V

-

0V

-

0V

-

0V

-

0V

Timing Chart 1

Wide Discriminator MM1327

Page 10

MITSUMI

50IRE

0IRE

50IRE

100IRE

Y input

I (Q) input

MAX output

tegrated output

S/H

GP

HD

ADCLX

DATA

PEAK 05 00

+0.15V

-

0.15

3FM

00M

10110

DELAY

Y

IN (22H)

NRZCLK

Integrated NRZCLK

NRZ discrimination timing

(Internal circuit)

Timing Chart 2

Wide Discriminator MM1327

1. The largest of Y, I and Q video input signals is output on MAX output pin.

2. MAX output date is integrated during horizontal scanning.

3. Integration results are sampled and held at HD pulse timing.

4. Consecutive comparison ADC outputs data as serial data.

(Serial data is 1H delayed from video signal input.)

5. Output data configuration is as shown in the table below.

Data configuration

Y input PEAK

Peak of more than 50IRE 1

No peak of more than 50IRE 0

Timing Chart 3

Video DATA

White scanning 00

⇔

Black scanning 3F

1. When YIN input signal matches "10110" at NRZ discrimination timing, it is identified as an EDTV2 signal.

EDTV2 pin is high for EDTV2 identification.

Page 11

MITSUMI

Measuring Circuit

Wide Discriminator MM1327

Loading...

Loading...