Page 1

ML6426

High Bandwidth Triple Video Filters with Buffered

Outputs for RGB or YUV

GENERAL DESCRIPTION

The ML6426 are a family of triple video filters with

buffered outputs. There are several versions of the

ML6426, each with different passband cut-off frequencies

of 6.7MHz, 12MHz, 15MHz, 24MHz, 30MHz, 36MHz,

and 48MHz. Each channel contains a 4

th

-order

Butterworth lowpass reconstruction video filter. The filter

is optimized for minimum overshoot and flat group delay

and guaranteed differential gain and phase at the outputs

of the integrated cable drivers.

All input signals from DACs are AC coupled into the

ML6426. All channels have DC restore circuitry to clamp

the DC input levels during video H-sync, using an output

feedback clamp. An external H-sync signal is required for

this purpose.

All outputs must be AC coupled into their loads. Each

output can drive 2V

P-P

into a 150Ω load. All channels

have a gain of 2 (6dB) at 1V

P-P

input levels.

FEATURES

■ 5V ±10% operation

■ RGB/YUV filters for ATSC Digital Television VESA

Standard

■ 2:1 Mux Inputs for multiple RGB/YUV inputs

■ Triple Reconstruction Filter options for 6.7, 12, 15, 24,

30, 36, and 48MHz to handle various line rates

■ Multiple ML6426 outputs can be paralleled to drive

RGB/YUV outputs at different frequencies for various

line rates by means of Disable/Enable pin.

■ 6dB drivers and sync tip clamps for DC restore

■ DC restore with minimal tilt

■ 0.4% differential gain on all channels

0.4º differential phase on all channels

0.8% total harmonic distortion on all channels

■ 2kV ESD protection

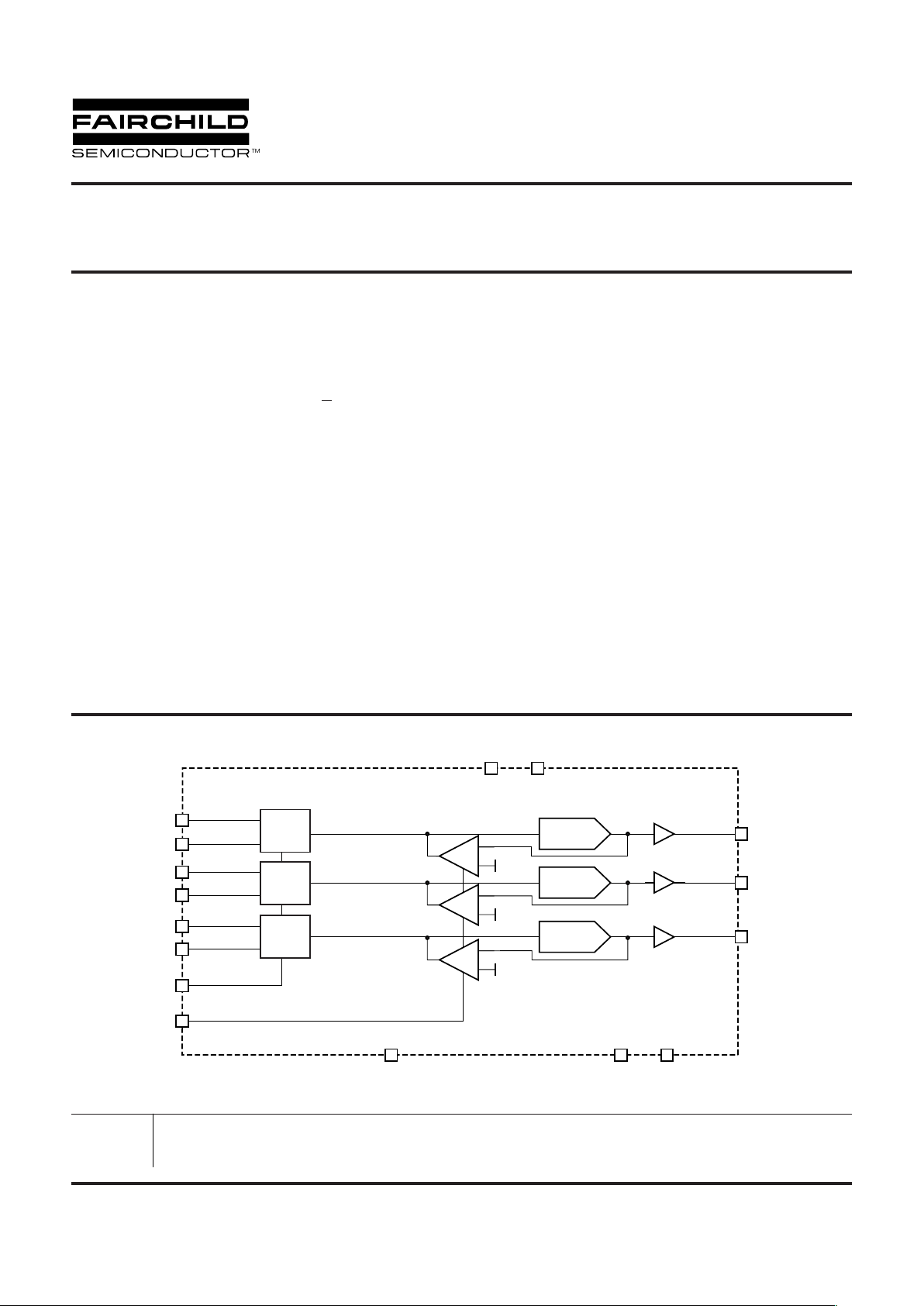

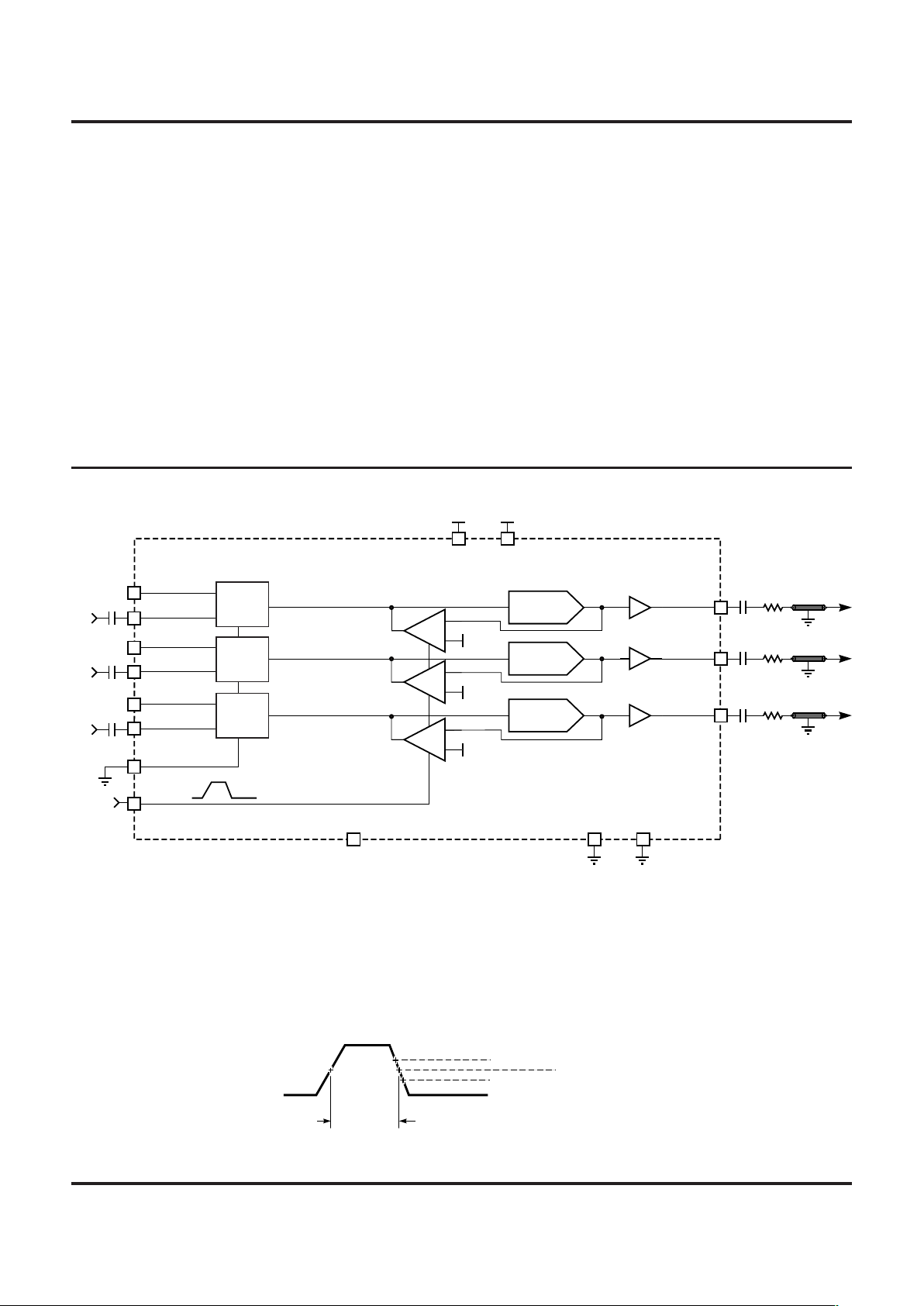

BLOCK DIAGRAM

RINA/YINA

2

RINB/YINB

BINA/VINA

8

BINB/VINB

9

A/B MUX

GINA/UINA

6

GIN/UINB

7

R

OUT/YOUT

13

G

OUT/UOUT

11

B

OUT/VOUT

10

4th-ORDER

FILTER A

4th-ORDER

FILTER B

4th-ORDER

FILTER C

MUX

MUX

MUX

×2

×2

×2

TRANSCONDUCTANCE

ERROR AMP

TRANSCONDUCTANCE

ERROR AMP

TRANSCONDUCTANCE

ERROR AMP

1

SYNCIN

16

GNDO

14

DISABLE

15

V

CCO

12

V

CC

4

GND

3

5

+

–

+

–

+

–

0.5V

0.5V

0.5V

ML6426-1 ML6426-2 ML6426-3 ML6426-4 ML6426-5 ML6426-6 ML6426-15

Filter A 6.7MHz 12MHz 24MHz 30MHz 36MHz 48MHz 15MHz

Filter B 6.7MHz 12MHz 24MHz 30MHz 36MHz 48MHz 15MHz

Filter C 6.7MHz 12MHz 24MHz 30MHz 36MHz 48MHz 15MHz

REV. 1.1 2/8/2001

Page 2

ML6426

2 REV. 1.1 2/8/2001

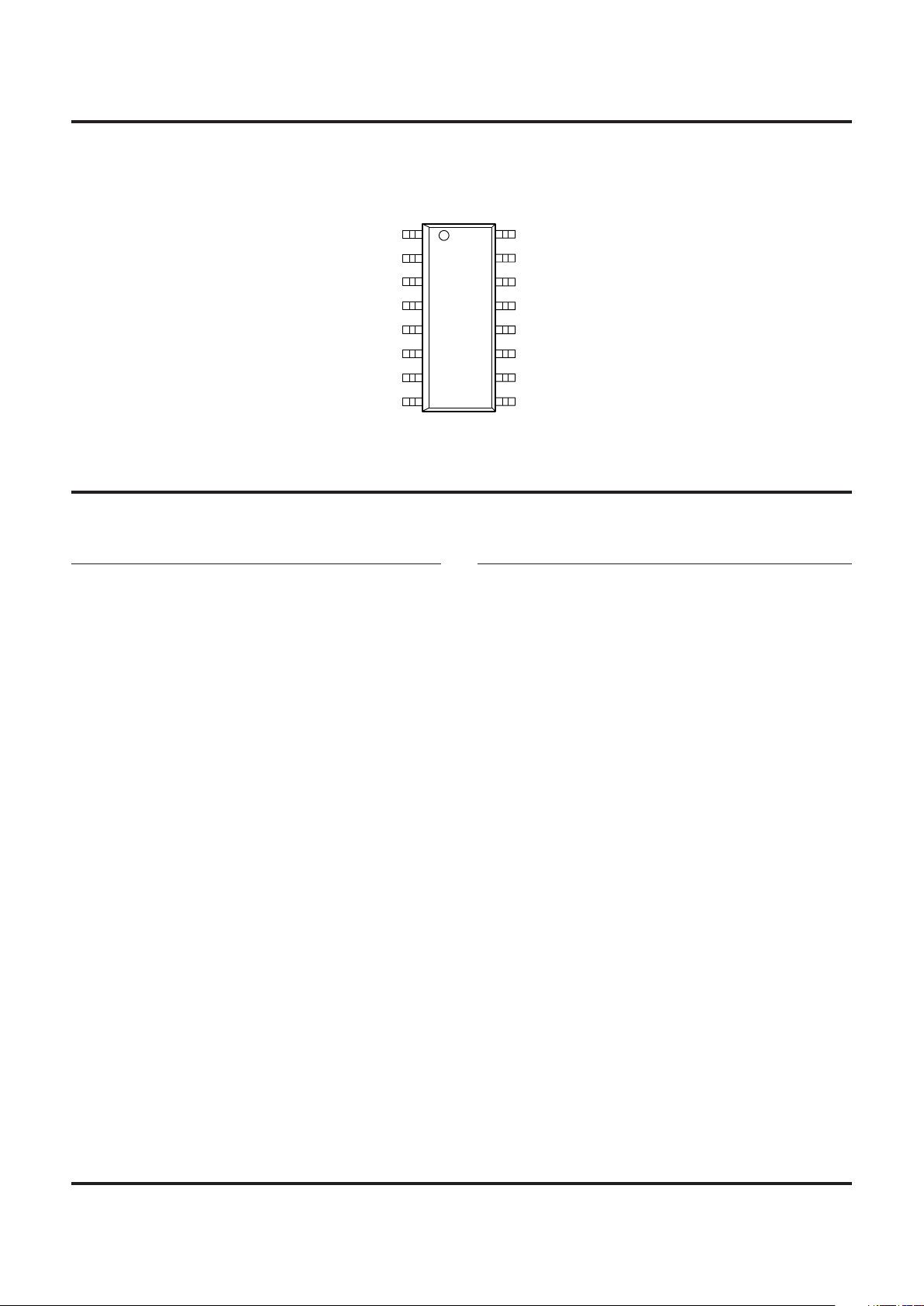

PIN CONFIGURATION

PIN DESCRIPTION

PIN NAME FUNCTION

1A/B MUX Logic input pin to select between

Bank <A> and Bank <B> video inputs.

This pin is internally pulled high.

2R

IN

A/YINA Unfiltered analog R- or Y-channel

input for Bank <A>. Sync must be

provided at SYNC IN pin.

3 GND Analog ground

4V

CC

Analog 5V supply

5R

IN

B/YINB Unfiltered analog R- or Y-channel

input for Bank <B>. Sync must be

provided at SYNC IN pin.

6G

IN

A/UINA Unfiltered analog G- or U-channel

input for Bank <A>. Sync must be

provided at SYNC IN pin.

7G

IN

B/UINB Unfiltered analog G- or U-channel

input for Bank <B>. Sync must be

provided at SYNC IN pin.

PIN NAME FUNCTION

8BINA/VINA Unfiltered analog B- or V-channel

input for Bank <A>. Sync must be

provided at SYNC IN pin.

9B

IN

B/VINB Unfiltered analog B- or V-channel

input for Bank <B>. Sync must be

provided at SYNC IN pin.

10 B

OUT

Analog B or V-channel output

11 G

OUT

Analog G or U-channel output

12 V

CCO

5V power supply for output buffers

13 R

OUT

Analog R or Y-channel output

14 GNDO Analog ground

15 DISABLE Disable/Enable pin. Turns the chip off

when logic high. Internally pulled low.

16 SYNC IN Input for an external H-sync logic

signal for filter channels. CMOS

level input. Active High.

ML6426

16-Pin Narrow SOIC (S16N)

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

TOP VIEW

A/B MUX

RINA/YINA

GND

V

CC

RINB/YINB

GINA/UINA

GINB/UINB

BINA/VINA

SYNC IN

DISABLE

GNDO

R

OUT/YOUT

V

CCO

G

OUT/UOUT

B

OUT/VOUT

BINB/VINB

Page 3

ML6426

REV. 1.1 2/8/2001 3

ABSOLUTE MAXIMUM RATINGS

Absolute maximum ratings are those values beyond which

the device could be permanently damaged. Absolute

maximum ratings are stress ratings only and functional

device operation is not implied.

V

CC

................................................................................

–0.3V to 7V

Junction Temperature .............................................. 150°C

ESD ..................................................................... >2000V

Analog and Digital I/O........... GND –0.3V to V

CC

+ 0.3V

Storage Temperature Range ..................... –65°C to 150°C

Lead Temperature (Soldering, 10 sec) ..................... 260°C

Thermal Resistance (θ

JA

) .................................... 100°C/W

OPERATING CONDITIONS

Temperature Range ....................................... 0°C to 70°C

V

CC

Range ...................................................4.5V to 5.5V

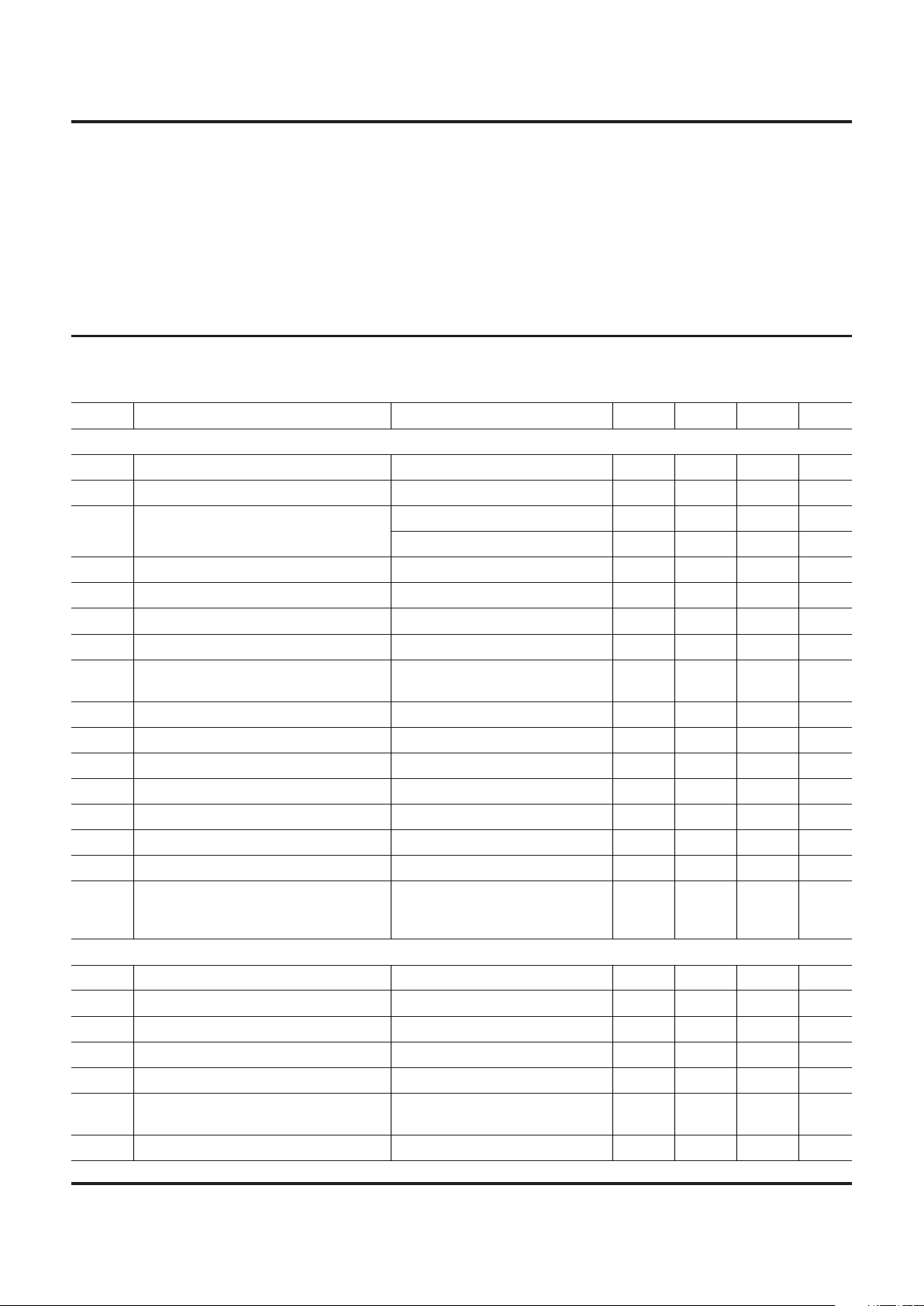

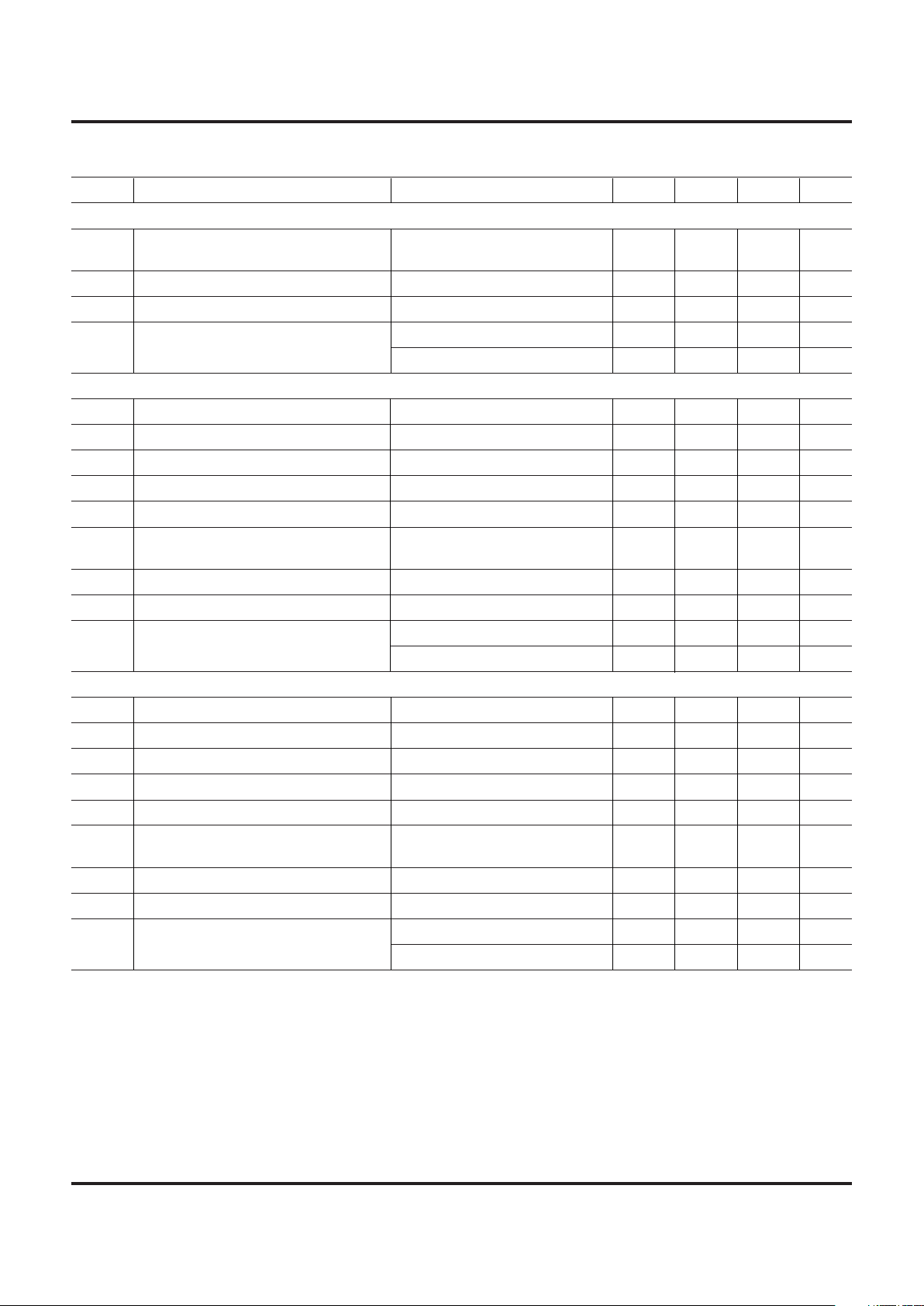

ELECTRICAL CHARACTERISTICS

Unless otherwise specified, VCC = 5V±10%, TA = Operating Temperature Range (Note 1)

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

GENERAL

I

CC

Supply Current No Load (VCC=5.5V) 52 80 mA

A

V

Low Frequency Gain (R, G, B) VIN= 100mV

P-P

at 100KHz 5.34 6.0 6.65 dB

V

OUT

Output Level during Sync (R, G, B,) DURING SYNC 0.7 0.9 1.1 V

Output Capability RL = 150W, AC-coupled@1MHz 2 VP-P

t

CLAMP

Clamp Response Time Settled to Within 10mV, CIN = 0.1µF 10 ms

V

I

Input Signal Dynamic Range (R, G, B,) AC Coupled 1.4 V

P-P

OS Peak Overshoot (R, G, B,) 2V

P-P

Output Pulse 4.3 %

C

L

Output Load Capacitance (R, G, B,) All Outputs 35 pF

Output Load Drive Capability, per Pin One Load is 150Ω 2 loads

(YUV or RGB Outputs)

dG Differential Gain (R, G, B,) All Outputs at fC/2 0.4 %

dφ Differential Phase (R, G, B,) All Outputs at fC/2 0.4 º

T

HD

Output Distortion (R, G, B,) V

OUT

= 2V

P-P

at 1 MHz 0.8 %

PSRR PSRR (R, G, B,) 0.5V

P-P

(100kHz) at V

CC

35 dB

I

SC

Output Short Circuit Current (R, G, B,) Note 2 120 mA

V

IH

Input Voltage Logic High DISABLE, SYNC IN 2.5 V

V

IL

Input Voltage Logic Low DISABLE, SYNC IN 1.0 V

T

MUX

Input Mux A/B Mux 2 µs

Data Valid Pin Valid

Time High or Low

6.7MHz FILTER: ML6426-1

f

1dB

–1dB Bandwidth Flatness (R, G, B,) 25ºC 4.0 4.8 MHz

f

c

–3dB Bandwidth Flatness (R, G, B,) 25ºC 6.0 6.7 7.3 MHz

f

0.8fc

0.8 x fC Attenuation 1.5 dB

f

SB

StopBand Rejection (All Channels ≥ 4 fC)fIN ≥ 4 fC, Note 3 –38 –42 dB

NOISE Output Noise (R, G, B,) Fullband 1.0 mV

RMS

X

TALK

Crosstalk Input of 0.5V

P-P

at 1 MHz –55 dB

Between any two Channels

X

TALK

A/B MUX Crosstalk Input of 0.5V

P-P

at 3.58/4.43MHz –54 dB

Page 4

ML6426

4 REV. 1.1 2/8/2001

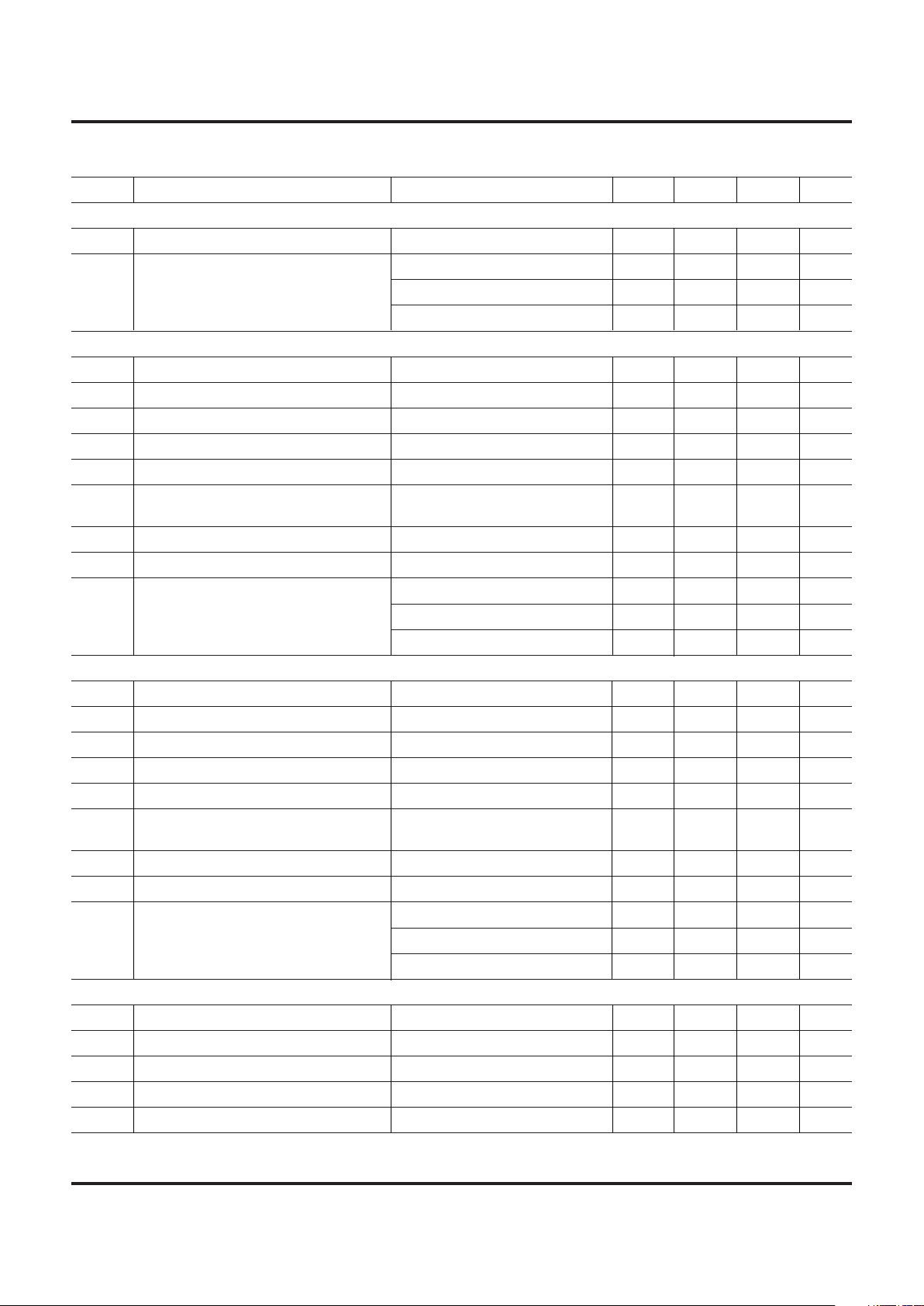

ELECTRICAL CHARACTERISTICS (Continued)

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

6.7MHZ FILTER: ML6426-1 (continued)

T

PD

Group Delay (R, G, B,) 100kHz 70 ns

∆T

PD

Group Delay Deviation from Flatness to 3.58MHz 4.0 ns

(R, G, B,) to 4.43MHz 8.0 ns

to 10MHz 9 ns

2MHz FILTER: ML6426-2

f

1dB

–1dB Bandwidth Flatness (R, G, B,) 25ºC 7.8 9.2 MHz

f

c

–3dB Bandwidth Flatness (R, G, B,) 25ºC 10.8 12 13.2 MHz

f

0.8fc

0.8 x fC Attenuation 1.2 dB

f

SB

StopBand Rejection (All Channels ≥ 4 fC)fIN ≥ 4 fC, Note 3 –40 dB

NOISE Output Noise (R, G, B,) Fullband 1 mV

RMS

X

TALK

Crosstalk Input of 0.5V

P-P

at 1 MHz –55 dB

Between any two Channels

X

TALK

A/B MUX Crosstalk Input of 0.5V

P-P

at 3.58/4.43MHz –54 dB

T

PD

Group Delay (R, G, B,) 100kHz 40 ns

∆T

PD

Group Delay Deviation from Flatness to 3.58MHz 1 ns

(R, G, B,) to 4.43MHz 1 n s

to 10MHz 7 ns

24MHz FILTER: ML6426-3

f

1dB

–1dB Bandwidth Flatness (R, G, B,) 25ºC 13.6 16 MHz

f

c

–3dB Bandwidth Flatness (R, G, B,) 25ºC 21.6 24 26.4 MHz

f

0.8fc

0.8 x fC Attenuation 1.7 dB

f

SB

StopBand Rejection (All Channels ≥ 4 fC)fIN ≥ 4 fC, Note 3 – 40 dB

NOISE Output Noise (R, G, B,) Fullband 1.0 mV

RMS

X

TALK

Crosstalk Input of 0.5V

P-P

at 1 MHz –55 dB

Between any two Channels

X

TALK

A/B MUX Crosstalk Input of 0.5V

P-P

at 3.58/4.43MHz -54 dB

T

PD

Group Delay (R, G, B,) 100kHz 22 ns

∆T

PD

Group Delay Deviation from Flatness to 3.58MHz 1 ns

(R, G, B,) to 4.43MHz 1 n s

to 10MHz 2 ns

30MHz FILTER: ML6426-4

f

1dB

–1dB Bandwidth Flatness (R, G, B,) 25ºC 15.3 18 MHz

f

c

–3dB Bandwidth Flatness (R, G, B,) 25ºC 27 30 3 3 MHz

f

0.8fc

0.8 x fC Attenuation 1.7 dB

f

SB

StopBand Rejection (All Channels ≥ 4 fC)fIN ≥ 4 fC, Note 3 –40 dB

NOISE Output Noise (R, G, B,) Fullband 1.0 mV

RMS

Page 5

ML6426

REV. 1.1 2/8/2001 5

Note 1. Limits are guaranteed by 100% testing, sampling, or correlation with worst case test conditions.

Note 2. Sustained short circuit protection limited to 10 seconds.

Note 3. 38dB is based on tester noise limits.

ELECTRICAL CHARACTERISTICS (Continued)

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

30MHz FILTER: ML6426-4 (Continued)

X

TALK

Crosstalk Input of 0.5V

P-P

at 1 MHz –55 dB

Between any two Channels

X

TALK

A/B MUX Crosstalk Input of 0.5V

P-P

at 3.58/4.43MHz -54 dB

T

PD

Group Delay (R, G, B,) 100kHz 18 ns

∆T

PD

Group Delay Deviation from Flatness to 10MHz 0.5 ns

(R, G, B,) to 27MHz 2 n s

36MHz FILTER: ML6426-5

f

1dB

–1dB Bandwidth Flatness (R, G, B,) 25ºC 17 20 MHz

f

c

–3dB Bandwidth Flatness (R, G, B,) 25ºC 32.4 36 39.6 MHz

f

0.8fc

0.8 x fC Attenuation 2dB

f

SB

StopBand Rejection (All Channels ≥ 4 fC)fIN ≥ 4 fC, Note 3 –40 dB

NOISE Output Noise (R, G, B,) Fullband 1.0 mV

RMS

X

TALK

Crosstalk Input of 0.5V

P-P

at 1 MHz –55 dB

Between any two Channels

X

TALK

A/B MUX Crosstalk Input of 0.5V

P-P

at 3.58/4.43MHz –54 dB

T

PD

Group Delay (R, G, B,) 100kHz 17 ns

∆T

PD

Group Delay Deviation from Flatness to 10MHz 0.5 ns

(R, G, B,) to 30MHz 4 n s

48MHz FILTER: ML6426-6

f

1dB

–1dB Bandwidth Flatness (R, G, B,) 25ºC 25.5 30 MHz

f

c

–3dB Bandwidth Flatness (R, G, B,) 25ºC 43.2 48 52.8 MHz

f

0.8fc

0.8 x fC Attenuation 1.2 dB

f

SB

StopBand Rejection (All Channels ≥ 4 fC)fIN ≥ 4 fC, Note 3 –40 dB

NOISE Output Noise (R, G, B,) Fullband 1.0 mV

RMS

X

TALK

Crosstalk Input of 0.5V

P-P

at 1 MHz –55 dB

Between any two Channels

X

TALK

A/B MUX Crosstalk Input of 0.5V

P-P

at 3.58/4.43MHz –54 dB

T

PD

Group Delay (R, G, B,) 100kHz 16 ns

∆T

PD

Group Delay Deviation from Flatness to 10MHz 0.5 ns

(R, G, B,) to 40MHz 2 n s

Page 6

ML6426

6 REV. 1.1 2/8/2001

FUNCTIONAL DESCRIPTION

The ML6426 is a triple monolithic continuous time video

filter designed for reconstructing video signals from an

YUV/RGB video D/A source. The ML6426 is intended for

use in AC coupled input and output applications.

The filters approximate a 4th-order Butterworth

characteristic with an optimization toward low overshoot

and flat group delay. All outputs are capable of driving

2V

P-P

into AC coupled 150Ω video loads, with up to 35pF

of load capacitance. All outputs are capable of driving a

75Ω load at 1V

P-P

.

All channels are clamped during sync to establish the

appropriate output voltage swing range (DC restore). Thus

the input coupling capacitors do not behave according to

the conventional RC time constant. In most applications,

the ML6426's input coupling capacitors are only 0.1µF.

Figure 1. Typical Application Schematic

An external CMOS compatible H

SYNC

pulse is required

which is Active High on the SYNC IN Pin. See Figure 2.

During sync, the feedback clamp sources/sinks current to

restore the DC level. The net result is that the average

input current is zero. Any change in the input coupling

capacitors' value will linearly affect the clamp response

times.

Each channel is essentially tilt-free. Each input is

clamped by a feedback amp which responds to the output

during sync.

The ML6426 is robust and stable under all stated load and

input conditions. Bypassing both V

CC

pins directly to

ground ensures this performance.

R

IN

5V 5V

R

G

0.1µF

220µF

75Ω

G

IN

0.1µF

220µF

75Ω

B

220µF

75Ω

B

IN

SYNC IN

0.1µF

RINA/YINA

2

RINB/YINB

BINA/VINA

8

BINB/VINB

9

A/B MUX

GINA/UINA

6

GINB/UINB

7

R

OUT/YOUT

13

G

OUT/UOUT

11

B

OUT/VOUT

10

4th-ORDER

FILTER A

4th-ORDER

FILTER B

4th-ORDER

FILTER C

MUX

MUX

MUX

×2

×2

×2

TRANSCONDUCTANCE

ERROR AMP

TRANSCONDUCTANCE

ERROR AMP

TRANSCONDUCTANCE

ERROR AMP

1

SYNCIN

16

GNDO

14

DISABLE

15

V

CCO

12

V

CC

4

GND

3

5

+

–

+

–

+

–

0.5V

0.5V

0.5V

ACTIVE HIGH

Figure 2. SYNC IN Pulse Width

VIL = 1.0V

50% x V

SYNC IN

V

IH

= 2.5V

PW

MIN

= 2µS

Page 7

ML6426

REV. 1.1 2/8/2001 7

STANDARD

PIXELS

VERTICAL

LINES

PICTURE

TRANSMISSION

RATE (Note 2)

DISPLAY

REFRESH

RATE (Note 2)

APPROXIMATE

SAMPLE

CLOCK

APPROXIMATE

HORIZONTAL

RATE

APPROXIMATE

RECONSTRUCTION

FILTER CUTOFF

MICRO LINEAR

FILTER TO USE

(Note 3)

SMPTE 1920 1080 60I 60Hz 35.3KHz 81MHz 40.5MHz ML6426-6

274M

1920 1080 30P, 24P 60Hz 70.6KHz 162MHz 81MHz N/A

SMPTE 1280 720 60P, 30P, 60Hz 47.1KHz 60MHz 30MHz ML6426-5

24P ML6426-4

704 480 (Note 1) 60I 60Hz 15.7KHz 13.5MHz 6.75MHz ML6426-1

704 480 60P, 30P, 60Hz 31KHz 27MHz 13.5MHz ML6426-2

24P ML6426-4

640 480 (Note 1) 60I 60Hz 15.7KHz 24.5MHz 12MHz ML6426-2

640 480 60P, 30P, 60Hz 31KHz 12.27MHz 6MHz ML6426-1

24P

P=progressive scan, I=interlaced scan, na = not available

Note 1: NTSC display rates, can be fed directly into NTSC encoder (set top box)

Note 2: 60 Hz also includes 59.94Hz

Note 3: custom frequencies ranging ± 3 to 6MHz can be special cut to order

Table 2: Choosing the Correct Reconstruction Filter and Video Amplifier for TV Applications, ML6426 options

TYPICAL APPLICATIONS

RECONSTRUCTION FILTER SELECTION FOR HDTV AND

VGA SIGNAL FILTERING

The filtering requirements for HDTV and VGA standards

vary depending on the resolution of the image to be

displayed, and its refresh rate. The actual refresh rate of

the display is not necessarily the same as the transmission

rate of the frames of images. Some formats use a frame

rate of 30Hz, but the display of those formats cannot be

scanned onto the CRT at 30Hz. Excessive large area

flicker would result. Such kinds of flicker can be seen on

a PAL display with its brightness set high. To avoid this,

the video will need to be stored in a frame buffer. This

buffer already exists in the MPEG decoder of HDTV

systems, so there is no cost penalty. The buffer is read out

at twice the rate as the frame rate for 30Hz systems, thus

getting us a refresh rate of 60Hz. Similar things are done

for the 24Hz frame rate formats to boost them to a 60Hz

refresh rate.

PIXELS VERTICAL LINES ASPECT RATIO PICTURE TRANSMISSION RATE

1920 1080 16:9 60I, 30P, 24P

1280 720 16:9 60P, 30P, 24P

704 480 16:9 and 4:3 60P, 60I, 30P,24P

640 480 4:3 60P, 60I, 30P,24P

P=progressive scan, I=interlaced scan

Table 1: HDTV / Advanced TV Applications: (From Table 10.3 from ATSC document A54)

Page 8

ML6426

8 REV. 1.1 2/8/2001

TYPICAL APPLICATIONS (Continued)

Pixel clock rates for the output D/A converters can be

roughly determined from the Table 1. Don’t forget that the

deflection system of a CRT display needs retrace time for

the vertical and horizontal.

This retrace time can vary from one design of an HDTV

set to another, as it only involves tradeoffs between the

frame buffer in the MPEG decoder and the CRT deflection

system. Allowing for 10% retrace time for the vertical and

20% for the horizontal, the appropriate Reconstruction

Filter is summarized in Table 2.

For VGA or RGB monitors, the following resolutions can

use the corresponding Reconstruction Filter and Video

Amplifier as shown in Table 3.

Figures 4, 5, and 6 show system diagrams when the

ML6426 provides a good solution. Figure 7 provides a

more detailed description for advanced TV applications

using various resolutions for legacy video, SDTV, and

HDTV.

640 480 VGA 60Hz 31.5kHz 25.175MHz 12.5MHz ML6426-2

VGA 72Hz 37.9kHz 31.5MHz 15.5MHz ML6426-3

VGA 75Hz 37.5kHz 31.5MHz 15.5MHz ML6426-3

800 600 SVGA 56Hz 35.1kHz 36MHz 18MHz ML6426-3

SVGA 60Hz 37.9kHz 40MHz 20MHz ML6426-3

SVGA 72Hz 48.1kHz 50MHz 25MHz ML6426-3

SVGA 75Hz 46.9kHz 49.5MHz 25MHz ML6426-3

1024 768 XGA 43Hz 35.5kHz 44.9MHz 23MHz ML6426-3

Interlaced

XGA 60Hz 37.9kHz 65MHz 33MHz ML6426-5

XGA 70Hz 56.5kHz 75MHz 37.5MHz ML6426-5

XGA 75Hz 60kHz 78.75MHz 39.4MHz ML6426-6

1280 1024 SXGA 75Hz 80kHz 135MHz 68MHz na

SXGA 60Hz 113MHz 57MHz na

1600 1200 UXGA 60Hz 166MHz 83MHz na

N/A = not available

Table 3: Choosing the Correct Reconstruction Filter and Video Amplifier for TV Applications, ML6426 options

VERTICAL LINES

PIXELS

NAME

REFRESH RATE

(prog except noted)

HORIZONTAL RATE

RECONSTRUCTION

FILTER CUTOFF

SAMPLE CLOCK

MICRO LINEAR

FILTER TO USE

USING THE ML6426 IN MULTIPLE RESOLUTIONS

Several ML6426 devices can be used in parallel to

construct a selectable filter selection block ranging from

frequencies between 6.7 MHz to 50MHz. Each ML6426

can be individually controlled via the disable pin. In a

parallel configuration, as shown in Figure 3 and 7, several

ML6426 devices can be used and selected via general

purpose I/O or other logic to perform the proper

reconstruction filtering for the resolution of choice. This

configuration allows for a minimum of bill of materials

and reduces cost. Micro Linears ML6426 EVAL Kit

demonstrates multi-resolution designs. Furthermore, since

the ML6426 pin-out is identical for all the options, the

filters can be interchanged. This allows for ease of product

migration to integrate newer resolutions to filter and drive

various DAC outputs at different sampling frequencies.

Page 9

ML6426

REV. 1.1 2/8/2001 9

Figure 3. ATSC Digital Television Application

YIN/R

IN

UIN/G

IN

5V

13

11

10

12 4

14 3

VIN/B

IN

15

2

5

6

7

8

9

16

1

13

11

10

12 4

14 3

15

2

5

6

7

8

9

16

1

13

11

10

12 4

14 3

15

2

5

6

7

8

9

16

1

SYNC IN

SELECT

LOGIC

GENERAL

PURPOSE I/O

DISABLE/ENABLE LINES

220µF

75Ω

220µF

75Ω

220µF

75Ω

R/Y

G/U

B/V

0.1µF

0.1µF

0.1µF

ML6426-1

6.7MHz

ML6426-5

36MHz

ML6426-2

12MHz

Page 10

ML6426

10 REV. 1.1 2/8/2001

Figure 4. Digital TV Receiver or HDTV Decoder Box

Figure 5. PC Graphics/Frame Grabber Editing Card

Figure 6. PC MRI, XRAY, Ultrasound, CT Scan

FROM SAT

OR CABLE

ML6426

U

V

Y

D/A

HDTV

DECODER

AND DISPLAY

PROCESSOR

GRAPHIC

PROCESSOR

MPEG2

TRANSPORT

AND DECODER

DIGITAL TV

FROM

CAMERA

VCR

FROM

DVD-ROM

OR MEMORY

YCrCb

DIGITAL

CV

S-VIDEO

ANALOG

ML6426

U

V

Y

D/A

RGB

VIDEO

DECODER

AND DISPLAY

PROCESSOR

VIDEO

ENCODER

RGB

MONITOR

MRI, XRAY,

ULTRASOUND, CT SCAN

DIGITAL YUV

ANALOG

ML6426

U

V

Y

MEDICAL

IMAGING

D/A

DSP

Page 11

ML6426

REV. 1.1 2/8/2001 11

Figure 7. Typical Applications Schematic

RINA

RINB

GNA

GNB

BINA

BINB

A/B MUX

SYNC IN

C 29

C 30

C 31

C 32

C 33

C 34

2

5

6

7

8

9

1

16

13

11

10

0.1µF

0.1µF

0.1µF

0.1µF

0.1µF

0.1µF

R

OUT

G

OUT

B

OUT

U3

ML6426-4

DISABLE

GNDO

GND

V

CCO

V

CC

15

14

3

12

4

C6

1µF

C14

0.1µF

C13

0.1µF

C5

1µF

R3 47kΩ

RINA

RINB

GNA

GNB

BINA

BINB

A/B MUX

SYNC IN

C 23

C 24

C 25

C 26

C 27

C 28

2

5

6

7

8

9

1

16

13

11

10

0.1µF

0.1µF

0.1µF

0.1µF

0.1µF

0.1µF

R

OUT

G

OUT

B

OUT

U2

ML6426-3

DISABLE

GNDO

GND

V

CCO

V

CC

15

14

3

12

4

C4

1µF

C12

0.1µF

HYSYNC IN

SW2

C11

0.1µF

C3

1µF

R2 47kΩ

R10

75Ω

0

1

RINA

RINB

C 17

C 18

2

5

13

11

10

0.1µF

0.1µF

C 19

C 20

6

7

0.1µF

0.1µF

C 21

C 22

8

9

1

16

0.1µF

0.1µF

R

OUT

R11

75Ω

R12

75Ω

R13

75Ω

R

OUT/YOUT

U1

ML6426-1

DISABLE

GNDO

GND

15

14

3

R1 47kΩ

RINA

RINB

GNA

GNB

BINA

BINB

A/B MUX

SYNC IN

C 35

C 36

C 37

C 38

C 39

C 40

2

5

6

7

8

9

1

16

13

11

10

0.1µF

0.1µF

0.1µF

0.1µF

0.1µF

0.1µF

R

OUT

G

OUT

B

OUT

UX

ML6426-X

DISABLE

GNDO

GND

V

CCO

V

CC

15

14

3

12

4

C8

1µF

C16

0.1µF

C15

0.1µF

C7

1µF

R4 47kΩ

BINB/VINB

4TH ORDER

FILTER

GINA

GINB

G

OUT

4TH ORDER

FILTER

BINA

BINB

B

OUT

4TH ORDER

FILTER

SYNC IN

A/B

MUX

V

CCO

V

CC

12

4

C2

1µF

C10

0.1µF

C9

0.1µF

C1

1µF

FB2

5V

GND

GND

FB1

C 41 220µF

G

OUT/UOUT

C 42 220µF

B

OUT/VOUT

C 43 220µF

2

3

4

1

3

5

7

2

JP1

SWI

4

6

8

R9

75Ω

BINA/VINA

R8

75Ω

GINB/UINB

R7

75Ω

GINA/UINA

R6

75Ω

RINB/YINB

R5

75Ω

RINA/YINA

Page 12

ML6426

12 REV. 1.1 2/8/2001

Figure 8. Passband Flatness all Outputs

(Normalized) 6.7 MHz, ML6426CS-1

Figure 9. Passband Flatness all Outputs

(Normalized) 12MHz, ML6426CS-2

Figure 10. Passband Flatness all Outputs

(Normalized) 24 MHz, ML6426CS-3

Figure 12. Passband Flatness all Outputs

(Normalized) 36MHz, ML6426CS-5

Figure 13. Passband Flatness all Outputs

(Normalized) 48MHz, ML6426CS-6

Figure 11. Passband Flatness all Outputs

(Normalized) 30 MHz, ML6426CS-4

PERFORMANCE DATA

10

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dB)

FREQUENCY (MHz)

0.01 1 100

0.1 10

AMPLITUDE (dB)

FREQUENCY (MHz)

100k 1M 10M 100M

10

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dB)

FREQUENCY (MHz)

1M 10M 100M

10

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dB)

FREQUENCY (MHz)

1M 10M 100M

10

0

–10

–20

–30

–40

–50

–60

–70

10

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dB)

FREQUENCY (Hz)

100k 1M 10M

100M 1G

10

0

–10

–20

–30

–40

–50

–60

–70

AMPLITUDE (dB)

FREQUENCY (Hz)

10k 100k 1M 10M

100M 1G

Page 13

ML6426

REV. 1.1 2/8/2001 13

Figure 14. Frequency Response All Outputs

ML6426-CS-1

Figure 15. Group Delay Deviation of Passband,

All Outputs ML6426CS-1

Figure 16. Group Delay Deviation All band,

All Outputs ML6426CS-1

Figure 17. Frequency Response All Outputs

ML6426CS-2

Figure 18. Group Delay Deviation of Passband,

All Outputs ML6426CS-2

Figure 19. Group Delay Deviation All Band,

All Outputs ML6426CS-2

12

10

8

6

4

2

0

–2

–4

–6

–8

GROUP DELAY DEVIATION (ns)

FREQUENCY (MHz)

04080

100

20 60

30 70 90

10 50

14

12

10

8

6

4

2

0

–2

–4

–6

GROUP DELAY DEVIATION (ns)

FREQUENCY (MHz)

04080

100

20 60

30 70 90

10 50

10

8

6

4

2

0

–2

–4

–6

–8

–10

GROUP DELAY DEVIATION (ns)

FREQUENCY (MHz)

048

10

26

379

15

12

10

8

6

4

2

0

–2

–4

–6

–8

GROUP DELAY DEVIATION (ns)

FREQUENCY (MHz)

0 2.8 5.6

7.0

1.4 4.2

2.1 4.9 6.3

0.7 3.5

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

AMPLITUDE (dB)

FREQUENCY (MHz)

04080

100

20 60

30 70 90

10 50

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

AMPLITUDE (dB)

FREQUENCY (MHz)

04080

100

20 60

30 70 90

10 50

PERFORMANCE DATA (Continuied)

Page 14

ML6426

14 REV. 1.1 2/8/2001

Figure 20. Frequency Response All Outputs

ML6426CS-3

Figure 21. Group Delay Deviation of Passband,

All Outputs ML6426CS-3

Figure 22. Group Delay Deviation All Band,

All Outputs ML6426CS-3

Figure 23. Frequency Response All Outputs

ML6426CS-4

Figure 24. Group Delay Deviation of Passband,

All Outputs ML6426CS-4

Figure 25. Group Delay Deviation All Band,

All Outputs ML6426CS-4

PERFORMANCE DATA (Continuied)

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

AMPLITUDE (dB)

FREQUENCY (MHz)

04080

100

20 60

30 70 90

10 50

10

8

6

4

2

0

–2

–4

–6

–8

–10

GROUP DELAY DEVIATION (ns)

FREQUENCY (MHz)

01020

25

515

7.5 17.5 22.5

2.5 12.5

12

10

8

6

4

2

0

–2

–4

–6

–8

GROUP DELAY DEVIATION (ns)

FREQUENCY (MHz)

04080

100

20 60

30 70 90

10 50

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

AMPLITUDE (dB)

FREQUENCY (MHz)

04080

100

20 60

30 70 90

10 50

10

8

6

4

2

0

–2

–4

–6

–8

–10

GROUP DELAY DEVIATION (ns)

FREQUENCY (MHz)

01632

40

824

12 28 36

420

6

4

2

0

–2

–4

–6

–8

–10

–12

–14

GROUP DELAY DEVIATION (ns)

FREQUENCY (MHz)

04080

100

20 60

30 70 90

10 50

Page 15

ML6426

REV. 1.1 2/8/2001 15

Figure 26. Frequency Response All Outputs

ML6426-CS-5

Figure 27. Group Delay Deviation of Passband,

All Outputs ML6426CS-5

Figure 28. Group Delay Deviation All band,

All Outputs ML6426CS-5

Figure 29. Frequency Response All Outputs

ML6426CS-6

Figure 30. Group Delay Deviation of Passband,

All Outputs ML6426CS-6

Figure 31. Group Delay Deviation All Band,

All Outputs ML6426CS-6

PERFORMANCE DATA (Continuied)

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

AMPLITUDE (dB)

FREQUENCY (MHz)

04080

100

20 60

30 70 90

10 50

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

AMPLITUDE (dB)

FREQUENCY (MHz)

04896

120

24 72

36 84 108

12 60

12

10

8

6

4

2

0

–2

–4

–6

–8

GROUP DELAY DEVIATION (ns)

FREQUENCY (MHz)

02040

50

10 30

15 35 45

525

10

8

6

4

2

0

–2

–4

–6

–8

–10

GROUP DELAY DEVIATION (ns)

FREQUENCY (MHz)

02040

50

10 30

15 35 45

525

12

10

8

6

4

2

0

–2

–4

–6

–8

GROUP DELAY DEVIATION (ns)

FREQUENCY (MHz)

04080

100

20 60

30 70 90

10 50

10

8

6

4

2

0

–2

–4

–6

–8

–10

GROUP DELAY DEVIATION (ns)

FREQUENCY (MHz)

04080

100

20 60

30 70 90

10 50

Page 16

ML6426

16 REV. 1.1 2/8/2001

PHYSICAL DIMENSIONS

SEATING PLANE

0.148 - 0.158

(3.76 - 4.01)

PIN 1 ID

0.228 - 0.244

(5.79 - 6.20)

0.386 - 0.396

(9.80 - 10.06)

0.012 - 0.020

(0.30 - 0.51)

0.050 BSC

(1.27 BSC)

0.015 - 0.035

(0.38 - 0.89)

0.059 - 0.069

(1.49 - 1.75)

0.004 - 0.010

(0.10 - 0.26)

0.055 - 0.061

(1.40 - 1.55)

16

0.006 - 0.010

(0.15 - 0.26)

0º - 8º

1

0.017 - 0.027

(0.43 - 0.69)

(4 PLACES)

Package: S16N

16-Pin Narrow SOIC

Page 17

ML6426

REV. 1.1 2/8/2001 17

ORDERING INFORMATION

PART NUMBER CUT-OFF FREQUENCY TEMPERATURE RANGE PACKAGE

ML6426CS-1 6.7MHz 0°C to 70°C 16-Pin Narrow SOIC (S16N)

ML6426CS-2 12MHz 0°C to 70°C 16-Pin Narrow SOIC (S16N)

ML6426CS-3 24MHz 0°C to 70°C 16-Pin Narrow SOIC (S16N)

ML6426CS-4 30MHz 0°C to 70°C 16-Pin Narrow SOIC (S16N)

ML6426CS-5 36MHz 0°C to 70°C 16-Pin Narrow SOIC (S16N)

ML6426CS-6 48MHz 0°C to 70°C 16-Pin Narrow SOIC (S16N)

ML6426CS-15 15MHz 0°C to 70°C 16-Pin Narrow SOIC (S16N)

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES

OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR

CORPORATION. As used herein:

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the body,

or (b) support or sustain life, and (c) whose failure to

perform when properly used in accordance with

instructions for use provided in the labeling, can be

reasonably expected to result in a significant injury of the

user.

2. A critical component in any component of a life support

device or system whose failure to perform can be

reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com © 2000 Fairchild Semiconductor Corporation

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO

ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME

ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN;

NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

Loading...

Loading...