Page 1

July 2000

PRELIMINARY

ML4833*

Electronic Dimming Ballast Controller

GENERAL DESCRIPTION

The ML4833 is a complete solution for a dimmable or a

non-dimmable, high power factor, high efficiency

electronic ballast. The BiCMOS ML4833 contains

controllers for “boost” type power factor correction as

well as for a dimming ballast. The ML4833 was designed

to minimize the number of external components required

to build an electronic ballast.

The PFC circuit uses a new, simple PFC topology which

requires only one loop for compensation. This system

produces a power factor of better than 0.99 with low

input current THD. An overvoltage protection comparator

inhibits the PFC section in the event of a lamp out or lamp

failure condition.

The ballast controller section provides for programmable

starting sequence with individually adjustable preheat and

lamp out-of-socket interrupt times. The IC controls lamp

output power through feedback. The ML4833 provides a

power down input which reduces power to the lamp, for

GFI, end of life, etc.

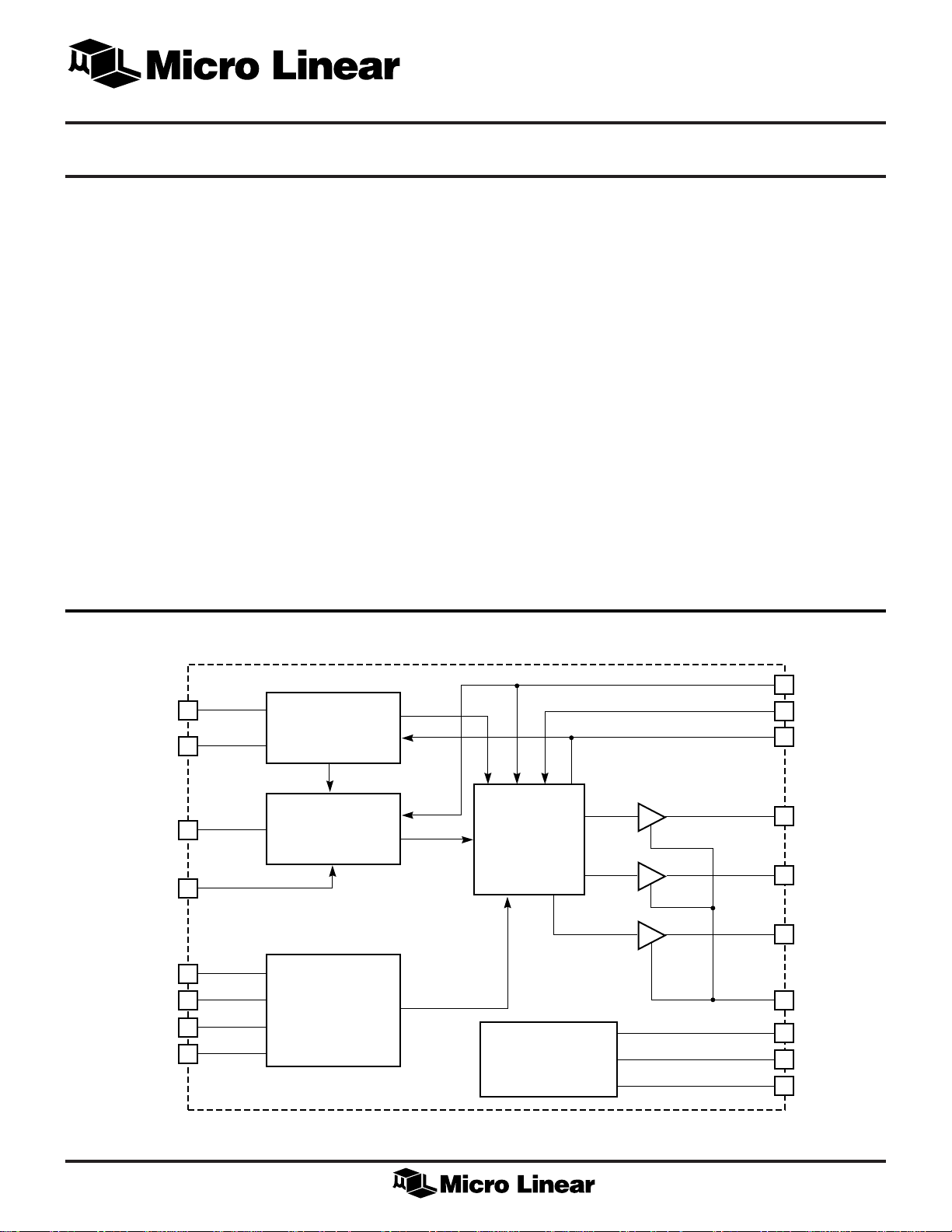

BLOCK DIAGRAM

FEATURES

■ Complete power factor correction and dimming

ballast control in one IC

■ Low distortion, high efficiency continuous boost,

peak current sensing PFC section

■ Programmable start scenario for rapid or

instant start lamps

■ Lamp current feedback for dimming control

■ Variable frequency dimming and starting

■ Programmable restart for lamp out condition to

reduce ballast heating

■ Internal over-temperature shutdown replaces

external heat sensor

■ PFC overvoltage comparator eliminates output

“runaway” due to load removal

■ Low start-up current <0.5mA

■ Power reduction pin for end of life and GFI detectors

(* Indicates part is End Of Life as of July 1, 2000)

6

7

9

3

10

2

1

18

R

SET

/CT

R

T

R

X/CX

PDWN

C

RAMP

PIFB

PEAO

PVFB/OVP

VARIABLE FREQUENCY

OSCILLATOR

PRE-HEAT

AND INTERRUPT

TIMERS

POWER

FACTOR

CONTROLLER

CONTROL

&

GATING LOGIC

UNDER-VOLTAGE

AND THERMAL

SHUTDOWN

OUTPUT

DRIVERS

INTERRUPT

LAMP FB

LFB OUT

OUT A

OUT B

PFC OUT

PGND

VCC

V

REF

GND

8

4

5

14

13

15

12

16

17

11

1

Page 2

ML4833

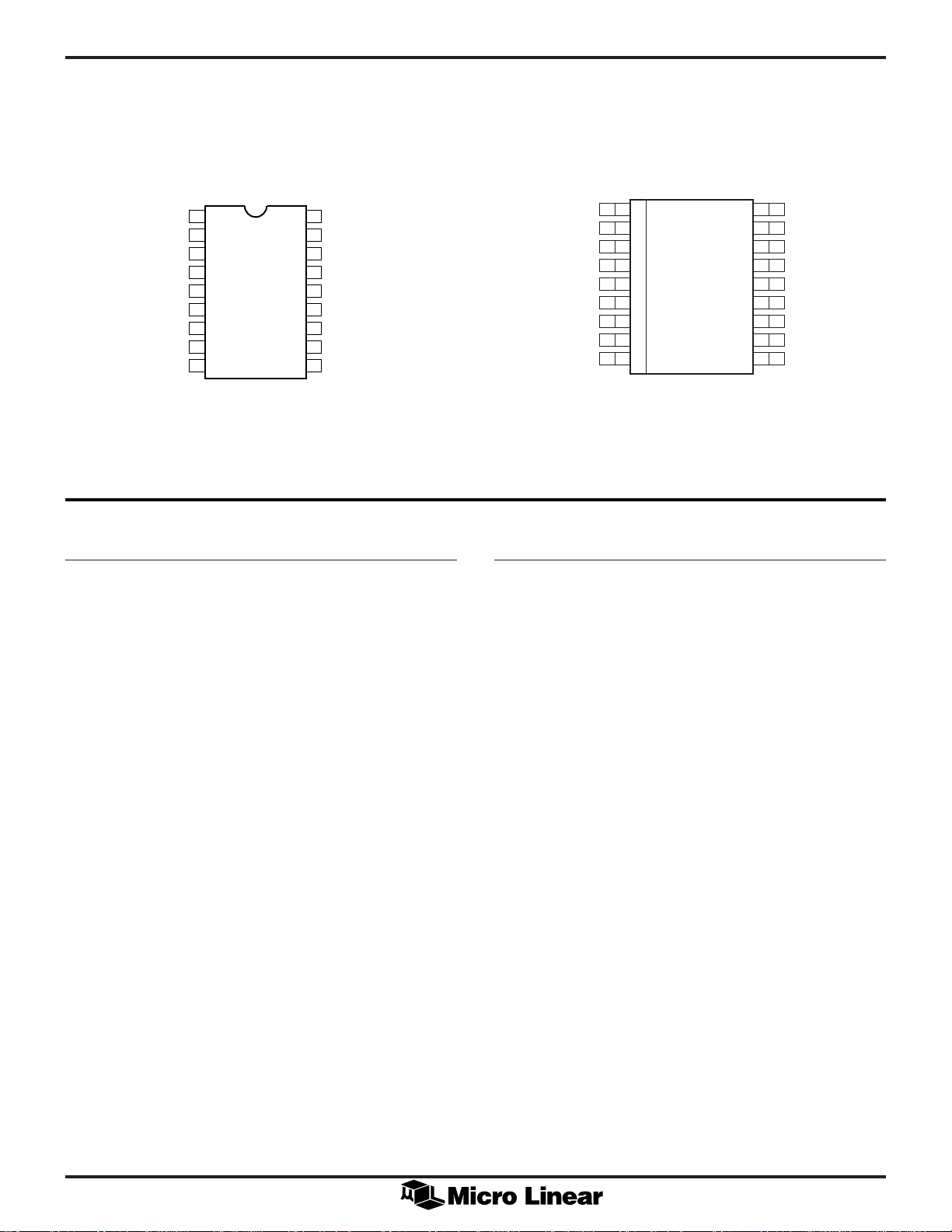

PIN CONFIGURATION

PEAO

PIFB

PDWN

LAMP FB

LFB OUT

R

SET

RT/C

INTERRUPT

R

X/CX

ML4833

18-Pin DIP (P18)

1

2

3

4

5

6

7

T

8

9

TOP VIEW

18

17

16

15

14

13

12

11

10

PVFB/OVP

V

REF

VCC

PFC OUT

OUT A

OUT B

P GND

GND

C

RAMP

PEAO

PIFB

PDWN

LAMP FB

LFB OUT

R

SET

RT/C

INTERRUPT

R

X/CX

T

ML4833

18-Pin SOIC (S18)

1

2

3

4

5

6

7

8

9

TOP VIEW

PIN DESCRIPTION

PIN# NAME FUNCTION PIN# NAME FUNCTION

1 PEAO PFC error amplifier output and

compensation node.

2 PIFB Sensing of the inductor current and

peak current sense point of the PFC

cycle by cycle current limit

comparator.

3 PDWN A one volt comparator threshold that

switches the operating frequency to

the preheat frequency when exceeded.

4 LAMP FB Inverting input of an error amplifier

used to sense (and regulate) lamp arc

current. Also the input node for

dimming control.

5 LFB OUT Output of the lamp current error

transconductance amplifier used for

lamp current loop compensation.

6R

SET

7RT/C

T

External resistor which sets oscillator

F

, and R(X)/C(X) charging current.

MAX

Oscillator timing components.

8 INTERRUPT Input used for lamp-out detection and

restart. A voltage less than 1.25 volts

resets the chip and causes a restart

after a programmable interval.

9RX/C

X

Sets the timing for the preheat,

dimming lockout, and interrupt.

10 C

RAMP

Integrated voltage of the error

amp out.

11 GND Ground.

12 P GND Power ground for the IC.

13 OUT B Ballast MOSFET drive output.

14 OUT A Ballast MOSFET drive output.

15 PFC OUT Power Factor MOSFET drive output.

16 VCC Positive supply for the IC.

17 V

REF

Buffered output for the 7.5V voltage

reference.

18 PVFB/OVP Inverting input to PFC error amplifier

and OVP comparator input.

18

17

16

15

14

13

12

11

10

PVFB/OVP

V

REF

VCC

PFC OUT

OUT A

OUT B

P GND

GND

C

RAMP

2

Page 3

ML4833

ABSOLUTE MAXIMUM RATINGS

Maximum Forced Voltage

(PEAO, LFB OUT) ...................................–0.3V to 7.7V

Absolute maximum ratings are those values beyond which

the device could be permanently damaged. Absolute

maximum ratings are stress ratings only and functional

device operation is not implied.

Supply Current (ICC) ............................................... 60mA

Output Current, Source or Sink

(OUT A, OUT B, PFC OUT) DC ......................... 250mA

Maximum Forced Current (PEAO, LFB OUT) ........ ±20mA

Junction Temperature ............................................ 150°C

Storage Temperature Range ..................... –65°C to 150°C

Lead Temperature (Soldering 10 sec.) .................... 260°C

Thermal Resistance (qJA)

ML4833CP ...................................................... 70°C/W

ML4833CS .................................................... 100°C/W

Output Energy (capacitive load per cycle).............. 1.5 mJ

Analog Inputs

OPERATING CONDITIONS

(LAMP FB, INTERRUPT, VCC) ........... –0.3V to VCC –2V

PIFB input voltage .........................................–1.5V to 2V

Temperature Range ........................................0°C to 85°C

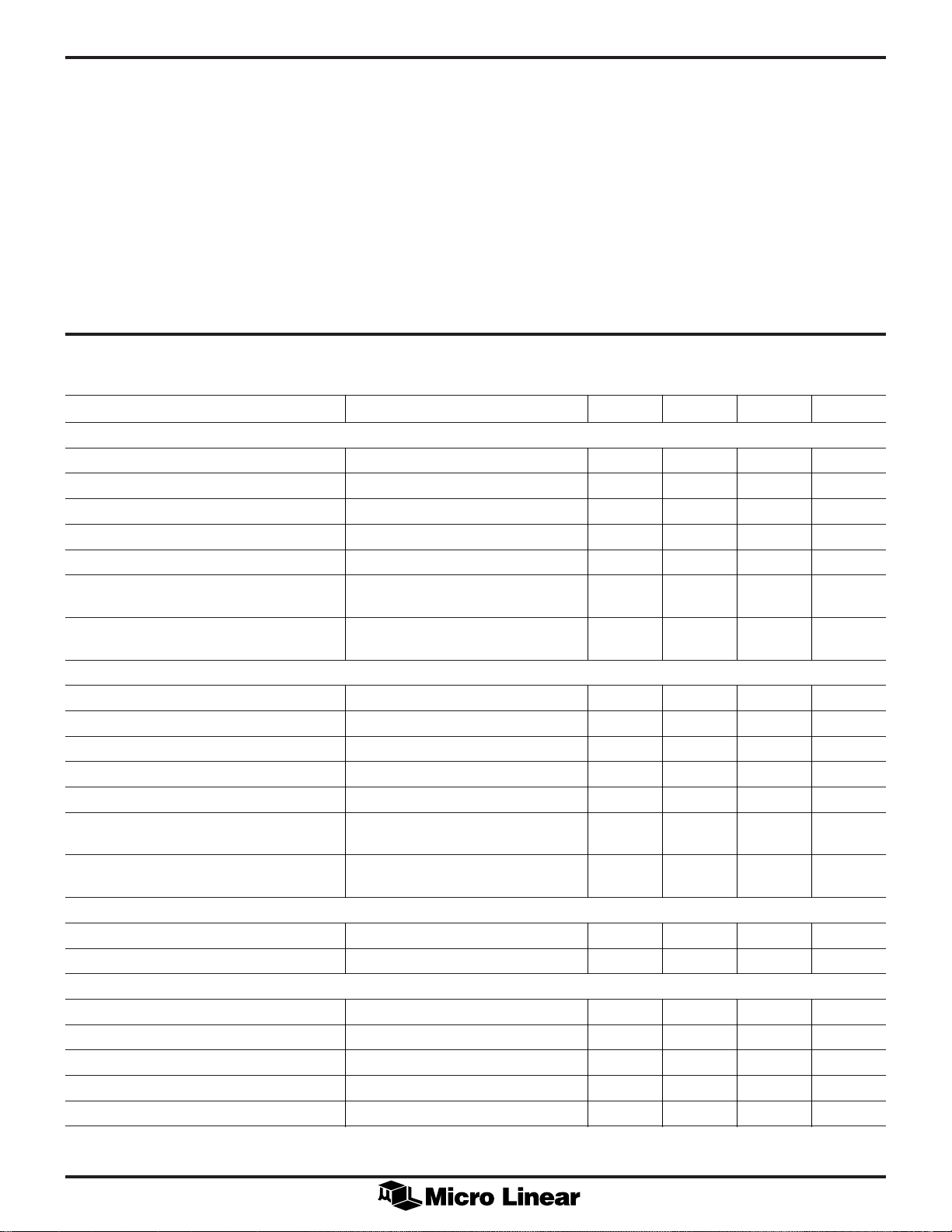

ELECTRICAL CHARACTERISTICS

Unless otherwise specified, R

PARAMETER CONDITIONS MIN TYP MAX UNITS

Lamp Current Amplifier (LAMP FB, LFB OUT)

Input Bias Current –0.3 –1.0 µA

Small Signal Transconductance 35 65 105 µW

Input Voltage Range –0.3 5.0 V

Output Low Voltage at LAMP FB = 3V, RL = 0.2 0.4 V

Output High Voltage at LAMP FB = 2V, RL = 7.1 7.5 7.8 V

Source Current Voltage at LAMP FB = 0V,

Sink Current Voltage at LAMP FB = 5V,

PFC Voltage Feedback Amplifier (PEAO, PVFB/OVP)

Input Bias Current –0.3 –1.0 µA

Small Signal Transconductance 35 65 105 µW

Input Voltage Range –0.3 5.0 V

Output Low Voltage at PVFB = 3V, RL = 0.2 0.4 V

Output High Voltage at PVFB = 2V, RL = 6.5 6.8 7.1 V

Source Current Voltage at PVFB/OVP = 0V,

Sink Current Voltage at PVFB/OVP = 3V,

PFC Current — Limit Comparator (PIFB)

Current-Limit Threshold –0.90 –1.05 –1.15 V

Propagation Delay 100mV step and 100mV overdrive 100 ns

Oscillator

Initial Accuracy TA = 25°C 72 76 80 kHz

Voltage Stability V

Temperature Stability 2%

Total Variation Line, temperature 69 83 kHz

Ramp Valley to Peak 2.5 V

= 22.1ký, RT = 15.8kW, CT = 1.5nF, C

SET

LFB OUT = 7V, TA = 25°C –0.05 –0.15 –0.25 mA

LFB OUT = 0.3V, TA = 25°C 0.05 0.12 0.22 mA

PEAO = 6V, TA = 25°C –0.05 –0.15 –0.25 mA

PEAO = 0.3V, TA = 25°C 0.03 0.07 0.16 mA

– 4.5V < VCC <V

CCZ

= 1µF, VCC = 12.5V. (Note 1)

VCC

– 0.5V 1 %

CCZ

W

W

3

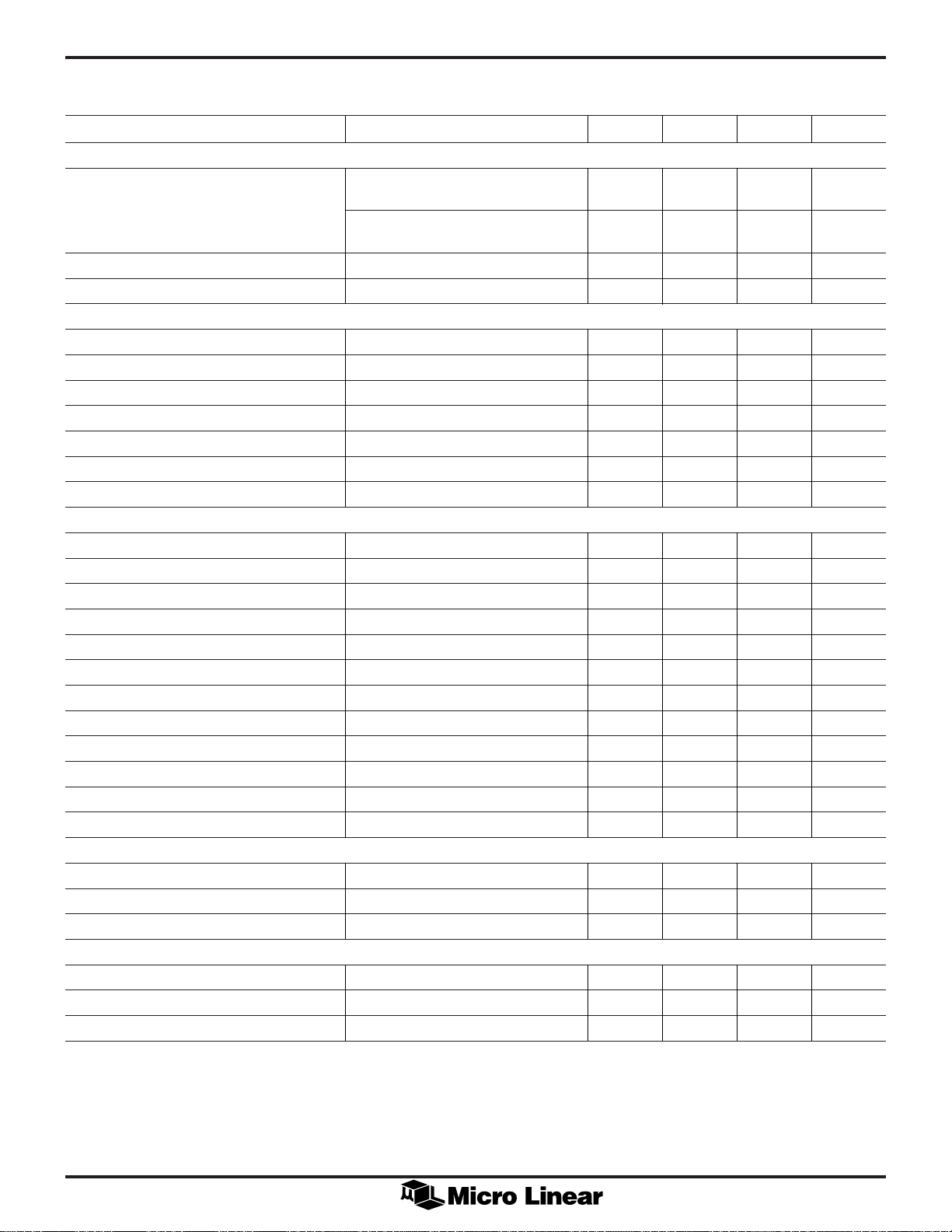

Page 4

ML4833

ELECTRICAL CHARACTERISTICS (Continued)

PARAMETER CONDITIONS MIN TYP MAX UNITS

Oscillator (Continued)

C

Charging Current Voltage at LAMP FB = 3V,

T

CT Discharge Current Voltage at RT/CT = 2.5V 4.0 5.5 7.0 mA

Output Drive Deadtime 0.65 1 1.35 µs

Reference Section

Output Voltage TA = 25°C, IO = 1mA 7.4 7.5 7.6 V

Line regulation V

Load regulation 1mA < IO < 5mA 2 15 mV

Temperature stability 0.4 %

Total Variation Line, load, temp 7.35 7.65 V

Output Noise Voltage 10Hz to 10kHz 50 µV

Long Term Stability TJ = 125°C, 1000 hrs 5 mV

Preheat and Interrupt Timer (RX/CX where RX = 680ký, CX = 4.7µF)

Initial Preheat Period 0.8 s

Subsequent Preheat Period 0.7 s

Start Period 1.2 s

Interrupt Period 5.7 s

RX/CX Charging Current –24 –28 –33 µA

RX/CX Open Circuit Voltage VCC < Start-up threshold 0.4 0.7 1.0 V

RX/CX Maximum Voltage 7.0 7.3 7.7 V

Input Bias Current Voltage at C

Preheat Lower Threshold 1.05 1.22 1.36 V

Preheat Upper Threshold 4.2 4.7 5.1 V

Interrupt Recovery Threshold 1.05 1.22 1.36 V

Start Period End Threshold 6.05 6.6 7.35 V

Interrupt Input (INTERRUPT)

Interrupt Threshold 1.1 1.22 1.4 V

Input Bias Current 0.1 µA

R

Voltage 2.4 2.5 2.6 V

SET

OVP Comparator (PVFB/OVP)

OVP Threshold 2.63 2.73 2.83 V

Hysteresis 0.18 0.23 0.27 V

Propagation Delay 1.4 µs

RT/CT = 2.5V, RX/CX = 0.9V (Preheat) –90 –110 –130 µA

LAMP FB = 3V, R

RX/CX = Open –180 –220 –260 µA

– 4.5V < VCC < V

CCZ

RAMP

= 2.5V,

T/CT

– 0.5V 2 35 mV

CCZ

= 1.2V 0.1 µA

4

Page 5

ML4833

ELECTRICAL CHARACTERISTICS

(Continued)

PARAMETER CONDITIONS MIN TYP MAX UNITS

Outputs (OUT A, OUT B, PFC OUT)

Output Voltage Low I

Output Voltage High I

Output Voltage Low in UVLO I

= 20mA 0.1 0.2 V

OUT

I

= 200mA 1.0 2.0 V

OUT

= –20mA VCC – 0.2 VCC – 0.1 V

OUT

I

= –200mA VCC – 2.0 VCC – 1.0 V

OUT

= 10mA, VCC < Start-up threshold 0.2 V

OUT

Output Rise/Fall Time CL = 1000pF 20 ns

Under-Voltage Lockout and Bias Circuits

IC Shunt Protection Voltage (V

)I

CCZ

= 15mA 14.2 15.0 15.8 V

CC

Start-up Current VCC - Start-up threshold 0.34 0.48 mA

Operating Current V

= 12.5V, 5.5 8.0 mA

CC

Voltage at LAMP FB = 0V,

LFB OUT = 2.3, PVFB/OVP = 2.3V

PIFB = Open

Start-up Threshold VCC – 1.2 V

Shutdown Threshold VCC – 5.3 V

Shutdown Temperature (T

Hysteresis (T

) 30 °C

DWN

) (Note 2) 130 °C

DWN

– 1.0 VCC – 0.8 V

CCZ

– 4.8 VCC – 4.3 V

CCZ

PDWN

PDWN Threshold 0.9 1.0 1.1 V

Note 1: Limits are guaranteed by 100% testing, sampling or correlation with worst case test conditions.

Note 2: Junction temperature.

5

Page 6

ML4833

FUNCTIONAL DESCRIPTION

OVERVIEW

The ML4833 consists of peak current controlled

continuous boost power factor front end section with a

flexible ballast control section. Start-up and lamp-out

retry timing are controlled by the selection of external

timing components, allowing for control of a wide variety

of different lamp types. The ballast section controls the

lamp power using frequency modulation (FM) with

additional programmability provided to adjust the VCO

frequency range. This allows for the IC to be used with a

variety of different output networks. Figure 1 depicts a

detailed block diagram of ML4833.

POWER FACTOR SECTION

The ML4833 power factor section is a peak current

sensing boost mode PFC control circuit in which only

voltage loop compensation is needed. It is simpler than a

conventional average current control method. It consists

of a voltage error amplifier, a current sense amplifier (no

compensation is needed), an integrator, a comparator, and

a logic control block. In the boost topology, power factor

correction is achieved by sensing the output voltage and

the current flowing through the current sense resistor. Duty

cycle control is achieved by comparing the integrated

voltage signal of the error amplifier and the voltage

across R

. The duty cycle control timing is shown in

SENSE

Figure 2. Setting minimum input voltage for output

regulation can be achieved by selecting C

RAMP

according

to equation 1.

PEAO

MAX

111

C

=−−µ

RAMP

() .

DTs s

{}

22

K

22

PVVV

OUTINOUT IN

−

1

−

2

L

−

18

()

DTs R

SENSE

(1)

OVERVOLTAGE PROTECTION AND INHIBIT

The OVP pin serves to protect the power circuit from

being subjected to excessive voltages if the load should

change suddenly (lamp removal). A divider from the high

voltage DC bus sets the OVP trip level. When the voltage

on PVFB/OVP exceeds 2.75V, the PFC transistor are

inhibited. The ballast section will continue to operate.

6

7

9

16

17

11

18

1

10

2

R

SET

RT/C

T

RX/C

X

VCC

V

REF

GND

PVFB/OVP

PEAO

C

RAMP

PIFB

UNDER-VOLTAGE

THERMAL SHUTDOWN

2.75V

–1.0V

REFOK

–

+

–

+

2.5V

OVP

ILIM

LFB OUT

OSC

CLK

+

PREHEAT

TIMER

+

I

SENSE

V TO I

SQ

R

AMPLIFIER

–

–

+

TQ

1.25V

–

SQ

R

+

–

+

–

2.5V

LAMP FB

INTERRUPT

1.0V

PFC OUT

PDWN

OUT A

OUT B

PGND

5

4

8

3

15

14

13

12

Figure 1. ML4833 Detailed Block Diagram

6

Page 7

TRANSCONDUCTANCE AMPLIFIERS

The PFC voltage feedback amplifier is implemented as an

operational transconductance amplifier. It is designed to

have low small signal forward transconductance such that

a large value of load resistor (R1) and a low value

ceramic capacitor (<1µF) can be used for AC coupling

(C1) in the frequency compensation network. The

compensation network shown in Figure 3 will introduce a

zero and a pole at:

f

ZP

EMI

FILTER

1

==

2

ππ

RC

11 12

f

1

2

RC

L

R

SENSE

PIFB

SINE

OUT A

(2)

142

SW1

SW2

PVFB/OVP

18

2.5V

–

+

Figure 3. Compensation Network

V

OUT

RA

INVERTER

RB

R1

C1

ML4833

LAMP

NETWORK

PVFB/OVP

18

C2

L

A

M

P

L

A

M

P

CLK

PFC OUT

RAMP

SINE

–A

+

R1

C1

RQ

S

PEAO

1

PEAO

CLK

C2

–

VREF1

+

–

OSC

V TO I

10

C

RAMP

C

RAMP

Figure 2. ML4833 PFC Controller Section

7

Page 8

ML4833

F

tt

OSC

CHG DIS

=

+

1

F

RC

OSC

TT

≅

×

1

051.

CLOCK

C

T

VTH = 3.75V

VTL = 1.25V

t

DIS t

CHG

Figure 4 shows the output configuration for the

operational transconductance amplifiers.

CURRENT

MIRROR

IN OUT

gmV

IN

2

IN OUT

CURRENT

MIRROR

io = gmV

IN

IQ –

gmV

IQ +

IN

2

Figure 4. Output Configuration

A DC path to ground or VCC at the output of the

transconductance amplifiers will introduce an offset error.

The magnitude of the offset voltage that will appear at the

input is given by VOS = io/gm. For an io of 1µA and a gm

of 0.05 µW the input referred offset will be 20mV.

W

Capacitor C1 as shown in Figure 3 is used to block the

DC current to minimize the adverse effect of offsets.

Slew rate enhancement is incorporated into all of the

operational transconductance amplifiers in the ML4833.

This improves the recovery of the circuit in response to

power up and transient conditions. The response to large

signals will be somewhat non-linear as the transconductance

amplifiers change from their low to high transconductance

mode. This is illustrated in Figure 5.

OSCILLATOR

The VCO frequency ranges are controlled by the output

of the LFB amplifier (R

). As lamp current increases,

SET

LFB OUT falls in voltage, causing the CT charging current

to increase, thereby causing the oscillator frequency to

increase. Since the ballast output network attenuates high

frequencies, the power to the lamp will be decreased.

V

REF

17

I

R

T

R

T/CT

7

C

T

5.5mA

CHG

1.25/3.75

CONTROL

+

–

V

REF

i

O

0

Linear Slope Region

VIN Differential

Figure 5. Transconductance Amplifier Characteristics

BALLAST OUTPUT SECTION

The IC controls output power to the lamps via frequency

modulation with non-overlapping conduction. This means

that both ballast output drivers will be low during the

discharging time t

of the oscillator capacitor CT.

DIS

Figure 6. Oscillator Block Diagram and Timing

The oscillator frequency is determined by the following

equations:

and

VIRV

tRCIn

=

CHG T T

REF CH T TL

VIRV

REF CH T TH

+−

+−

The oscillator’s minimum frequency is set when ICH = 0

where:

(3)

(4)

(5)

8

Page 9

ML4833

This assumes that t

CHG

>> t

DIS

.

When LFB OUT is high, ICH = 0 and the minimum

frequency occurs. The charging current varies according

to two control inputs to the oscillator:

1. The output of the preheat timer

2. The voltage at LFB OUT (lamp feedback amplifier

output)

In preheat condition, charging current is fixed at

.

I

CHG PREHEAT

()

25

=

R

SET

(6)

In running mode, charging current decreases as the

voltage rises from 0V to VOH at the LAMP FB amplifier.

The highest frequency will be attained when I

CHG

is

highest, which is attained when voltage at LFB OUT

is at 0V:

()0

=

5

R

SET

(7)

I

CHG

Highest lamp power, and lowest output frequency are

attained when voltage at LFB OUT is at its maximum

output voltage (VOH).

In this condition, the minimum operating frequency of the

ballast is set per equation 5 above.

For the IC to be used effectively in dimming ballasts with

higher Q output networks a larger CT value and lower R

T

value can be used, to yield a smaller frequency excursion

over the control range (voltage at LFB OUT). The

discharge current is set to 5mA. Assuming that I

DIS

>>

IRT:

tC

DIS VCO T()

≅×600

(8)

IC BIAS, UNDER-VOLTAGE LOCKOUT AND

THERMAL SHUTDOWN

The IC includes a shunt clamp which will limit the

voltage at VCC to 15V (V

). The IC should be fed with

CCZ

a current limited source, typically derived from the

ballast transformer auxiliary winding. When VCC is below

V

– 1.1V, the IC draws less than 0.48mA of quiescent

CCZ

current and the outputs are off. This allows the IC to start

using a “bleed resistor” from the rectified AC line.

To help reduce ballast cost, the ML4833 includes a

temperature sensor which will inhibit ballast operation if

the IC’s junction temperature exceeds 120°C. In order to

use this sensor in lieu of an external sensor, care should

be taken when placing the IC to ensure that it is sensing

temperature at the physically appropriate point in the

ballast. The ML4833’s die temperature can be estimated

with the following equation:

(9)

t

t

V

I

CC

CC

0.34mA

VCCZ

V(ON)

V(OFF)

5.5mA

TT P CW

≅++°(/)65

JAD

Figure 7. Typical VCC and ICC Waveforms when

the ML4833 is Started with a Bleed Resistor from

the Rectified AC Line and Bootstrapped from an

Auxiliary Winding.

STARTING, RE-START, PREHEAT AND INTERRUPT

The lamp starting scenario implemented in the ML4833

is designed to maximize lamp life and minimize ballast

heating during lamp out conditions.

The circuit in Figure 8 controls the lamp starting

scenarios: Filament preheat and lamp out interrupt. CX is

charged with a current of I

/4 and discharged through

R(SET)

RX. The voltage at CX is initialized to 0.7V (VBE) at power

up. The time for CX to rise to 4.8V is the filament preheat

time. During that time, the oscillator charging current

(I

CHG

) is 2.5/R

. This will produce a high frequency for

SET

filament preheat, but will not produce sufficient voltage

to ignite the lamp or cause significant glow current.

After cathode heating, the inverter frequency drops to F

MIN

causing a high voltage to appear to ignite the lamp. If

lamp current is not detected when the lamp is supposed

to have ignited, the lamp voltage feedback coming into

pin 8 remains below 1.25V, the CX charging current is

shut off and the inverter is inhibited until CX is discharged

by RX to the 1.2V threshold. Shutting off the inverter in

this manner prevents the inverter from generating

excessive heat when the lamp fails to strike or is out of

socket. Typically this time is set to be fairly long by

choosing a large value of RX.

9

Page 10

ML4833

0.625

R

1.2/4.8

1.2/6.8

–

+

SET

+

–

+

–

HEAT

DIMMING

LOCKOUT

R

Q

S

RX/C

X

9

C

X

R

X

6.8

INTERRUPT

8

1.25V

Figure 8. Lamp Preheat and Interrupt Timers

LFB OUT is ignored by the oscillator until CX reaches

6.8V threshold. The lamps are therefore driven to full

power and then dimmed. The CX pin is clamped to

about 7.5V.

INHIBIT

A summary of the operating frequencies in the various

operating modes is shown below.

Operating Mode Operating Frequency

[F(MAX) to F(MIN)]

Preheat 2

Dimming

Lock-out F(MIN)

Dimming

Control F(MIN) to F(MAX)

TYPICAL APPLICATIONS

Figure 10 shows a schematic for a dimming power-factor

corrected 60W ballast, designed to operate two F32T8

fluorescent lamps connected in series.

R

X/CX

HEAT

DIMMING

LOCKOUT

INT

INHIBIT

6.8

4.8

1.2

.65

0

>1.25

10

Figure 9. Lamp Starting and Restart Timing

Page 11

ML4833

R

R

Y

Y

B

B

T5

C8

10

1

56

TP5

D11

R24

R21

C21

DIMMER

0–10VDC

REMOTE MANUAL

GRAY

VIOLET

R2

U1

TP4

Q2

C23

43219

T4

8

C9

7

6

C22

Q3

R17

R18

3

T2

6

72

D8

D1

106

R11

D7

T1

R6

R12

Q1

98

D13

D2

D9

C10

C25

C26

R13

R7

C20

R8

+

D5

D3

D4

C3

C2

C1

L1

L2

TP1

8

1

C17

C19

R16

R19

TP2

C16

C12

C15

C14

U2

7

4

–

+

5

6

1

R1

8

–

+

3

2

R3

R4

D12

R20

D10

181716151413121110

CC

REF

V

V

PVFB

R22

U1

ML4833

PEAO

PIFB

R10

PDWN

123456789

OUT A

PFC OUT

LAMP FB

LFB OUT

OUT B

SETRT

R

PGND

T

C

RAMP

GND

C

X

C

X

INTERRUPT

R

R23

R15

C5

C13

TP3

C3

R5

C2

Q1

R6

R7

C6

D6

R1

R14

R2

R3

R25

C4

C11

R5

C7C24

D2

C4C1

R8

D1

4

3

DIMMER CONTROL INTERFACE SUBASSEMBLY

T1

R4

F1

PDWN

HOT

NEUTRAL

220 VAC

Figure 10. 220V Dimming Ballast

11

Page 12

ML4833

PHYSICAL DIMENSIONS inches (millimeters)

Package: P18

0.890 - 0.910

(22.60 - 23.12)

18

18-Pin PDIP

0.045 MIN

(1.14 MIN)

(4 PLACES)

0.170 MAX

(4.32 MAX)

0.125 MIN

(3.18 MIN)

18

PIN 1 ID

1

0.449 - 0.463

(11.40 - 11.76)

0.050 - 0.065

(1.27 - 1.65)

0.016 - 0.022

(0.40 - 0.56)

0.100 BSC

(2.54 BSC)

SEATING PLANE

Package: S18

18-Pin SOIC

0.240 - 0.260

(6.09 - 6.61)

0.015 MIN

(0.38 MIN)

0.295 - 0.325

(7.49 - 8.26)

0º - 15º

0.008 - 0.012

(0.20 - 0.31)

12

0.024 - 0.034

(0.61 - 0.86)

(4 PLACES)

0.090 - 0.094

(2.28 - 2.39)

0.291 - 0.301

(7.39 - 7.65)

PIN 1 ID

1

0.050 BSC

(1.27 BSC)

0.012 - 0.020

(0.30 - 0.51)

0.095 - 0.107

(2.41 - 2.72)

SEATING PLANE

0.398 - 0.412

(10.11 - 10.47)

0.005 - 0.013

(0.13 - 0.33)

0º - 8º

0.022 - 0.042

(0.56 - 1.07)

0.009 - 0.013

(0.22 - 0.33)

Page 13

ML4833

ORDERING INFORMATION

PART NUMBER TEMPERATURE RANGE PACKAGE

ML4833CP (End of Life) 0°C to 85°C Molded DIP (P18)

ML4833CS (Obsolete) 0°C to 85°C SOIC (S18)

© Micro Linear 1997 is a registered trademark of Micro Linear Corporation

Products described in this document may be covered by one or more of the following patents, U.S.: 4,897,611; 4,964,026; 5,027,116; 5,281,862; 5,283,483; 5,418,502; 5,508,570; 5,510,727; 5,523,940; 5,546,017;

5,559,470; 5,565,761; 5,592,128; 5,594,376; Japan: 2598946; 2619299. Other patents are pending.

Micro Linear reserves the right to make changes to any product herein to improve reliability, function or

design. Micro Linear does not assume any liability arising out of the application or use of any product

described herein, neither does it convey any license under its patent right nor the rights of others. The

circuits contained in this data sheet are offered as possible applications only. Micro Linear makes no

warranties or representations as to whether the illustrated circuits infringe any intellectual property rights of

others, and will accept no responsibility or liability for use of any application herein. The customer is urged

to consult with appropriate legal counsel before deciding on a particular application.

2092 Concourse Drive

San Jose, CA 95131

Tel: 408/433-5200

Fax: 408/432-0295

DS4833-01

13

Loading...

Loading...