Page 1

FEATURES

LTC3401

1A, 3MHz Micropower

Synchronous Boost Converter

U

DESCRIPTIO

■

Synchronous Rectification: Up to 97% Efficiency

■

1A Switch Current Rating

■

Fixed Frequency Operation Up to 3MHz

■

Wide Input Range: 0.5V to 5.5V (Operating)

■

Very Low Quiescent Current: 38µA (Burst Mode

Operation)

■

2.6V to 5.5V Adjustable Output Voltage

■

0.85V (Typ) Start-Up Voltage

■

No External Schottky Diode Required (V

■

Synchronizable Switching Frequency

■

Burst Mode Enable Control

■

Antiringing Control Reduces Switching Noise

■

PGOOD Output

■

OPTI-LOOP® Compensation

■

Very Low Shutdown Current: <1µA

■

Small 10-Pin MSOP Package

OUT

< 4.3V)

U

APPLICATIO S

■

Pagers

■

Handheld Instruments

■

Cordless Phones

■

Wireless Handsets

■

GPS Receivers

■

Battery Backup

■

CCFL Backlights

The LTC®3401 is a high efficiency, fixed frequency, stepup DC/DC converter that operates from an input voltage

below 1V. The device includes a 0.16Ω N-channel MOSFET

switch and a 0.18Ω P-channel synchronous rectifier.

®

Switching frequencies up to 3MHz are programmed with

an external timing resistor and the oscillator can be

synchronized to an external clock. An external Schottky

diode is optional but will slightly improve efficiency.

Quiescent current is only 38µA in Burst Mode operation,

maximizing battery life in portable applications. Burst

Mode operation is user controlled and can be enabled by

driving the MODE/SYNC pin high. If the MODE/SYNC pin

has either a clock or is driven low, then fixed frequency

switching is enabled.

Other features include 1µA shutdown, antiringing control,

open-drain power good output, thermal shutdown and

current limit. The LTC3401 is available in the 10-lead

thermally enhanced MSOP package. Higher current applications should use the 2A rated LTC3402 synchronous

boost converter. Applications that require V

OUT

< 2.6V

should use the LTC3423.

, LTC and LT are registered trademarks of Linear Technology Corporation.

Burst Mode and OPTI-LOOP are registered trademarks of Linear Technology Corporation.

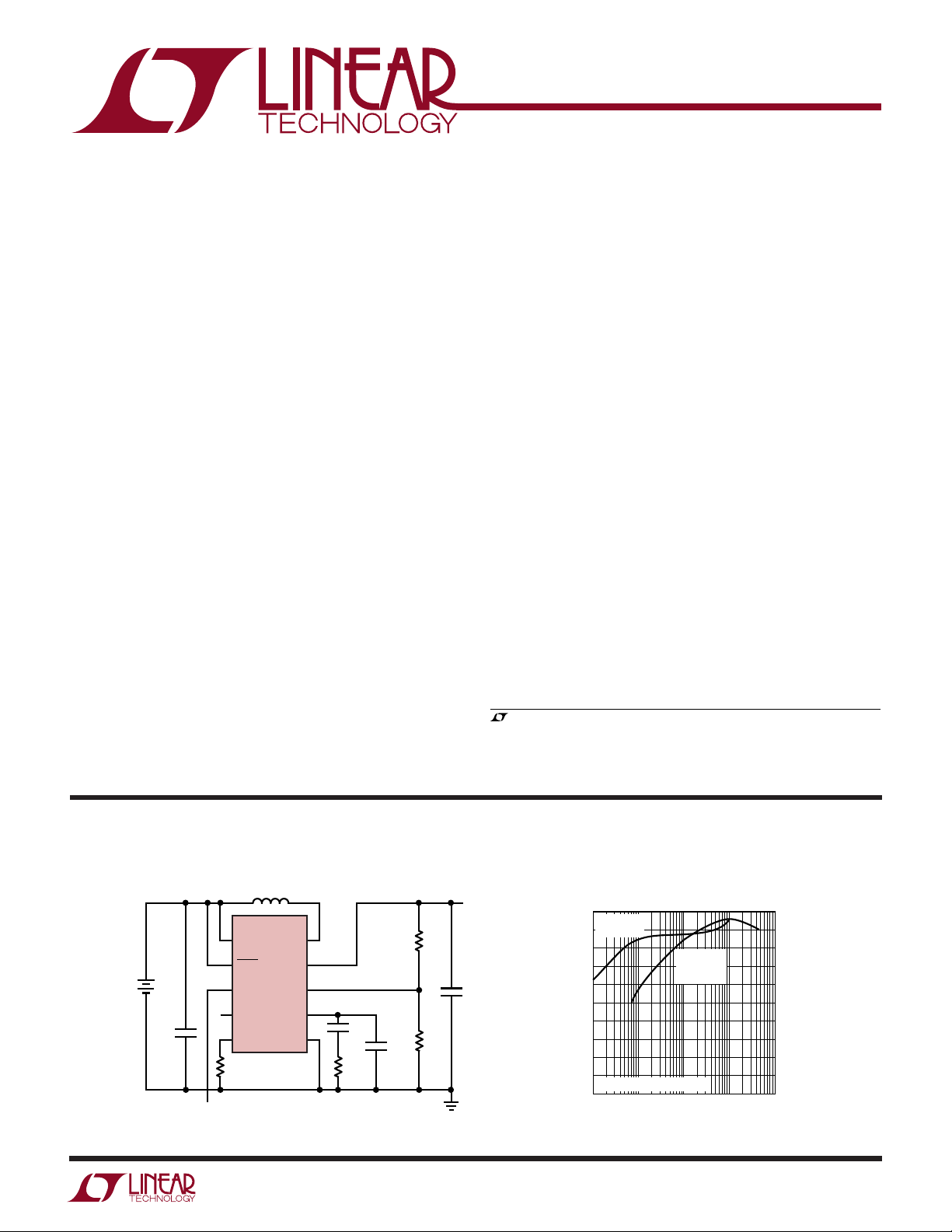

TYPICAL APPLICATION

All-Ceramic-Capacitor 2-Cell to 3.3V at 500mA Step-Up Converter

VIN = 1.8V to 3V

+

2

CELLS

C1

4.7µF

0 = FIXED FREQUENCY

1 = Burst Mode OPERATION

3

V

10

SHDN

2

MODE/SYNC

6

PGOOD

1

R

R

t

30.1k

IN

t

L1

4.7µH

LTC3401

SW

V

OUT

FB

V

C

GND

C1: TAIYO YUDEN JMK212BJ475MG

C2: TAIYO YUDEN JMK325BJ226MM

L1: SUMIDA CD43-4R7M

U

V

OUT

3.3V

500mA

4

7

8

9

C3

470pF

5

R5

82k

909k

C4

4.7pF

R2

C2

22µF

R1

549k

3404 TA01

100

Burst Mode

90

OPERATION

80

70

60

50

40

EFFICIENCY (%)

30

20

10

VIN = 2.4V WITH SCHOTTKY

0

0.1

Efficiency

1MHz

FIXED

FREQUENCY

1000

110

I

OUT

3401fa

100

(mA)

3401 TA02

1

Page 2

LTC3401

PACKAGE/ORDER I FOR ATIO

UU

W

WWWU

ABSOLUTE AXI U RATI GS

(Note 1)

VIN, V

SW Voltage ................................................. –0.5V to 6V

VC, Rt Voltages ......................... –0.5V to (V

PGOOD, SHDN, FB, MODE Voltages ........... –0.5V to 6V

Operating Temperature Range (Note 2) .. –40°C to 85°C

Storage Temperature Range ................. –65°C to 125°C

Lead Temperature (Soldering, 10 sec)..................300°C

Voltages...................................... –0.5V to 6V

OUT

OUT

+ 0.3V)

ORDER PART

TOP VIEW

10

1

R

t

MODE

2

V

3

IN

SW

4

GND

5

MS PACKAGE

10-LEAD PLASTIC MSOP

T

= 125°C

JMAX

= 130°C/W 1 LAYER BOARD

θ

JA

= 100°C/W 4 LAYER BOARD

θ

JA

Consult LTC Marketing for parts specified with wider operating temperature ranges.

9

8

7

6

SHDN

V

C

FB

V

OUT

PGOOD

NUMBER

LTC3401EMS

MS PART MARKING

LTPG

ELECTRICAL CHARACTERISTICS

The ● denotes specifications that apply over the full operating temperature range, otherwise specifications are at TA = 25°C.

VIN = 1.2V, V

PARAMETER CONDITIONS MIN TYP MAX UNITS

Minimum Start-Up Voltage I

Minimum Operating Voltage (Note 4) ● 0.5 V

Output Voltage Adjust Range ● 2.6 5.5 V

Feedback Voltage ● 1.22 1.25 1.28 V

Feedback Input Current VFB = 1.25V 1 50 nA

Quiescent Current—Burst Mode Operation VC = 0V, MODE/SYNC = 3.3V (Note 3) 38 65 µA

Quiescent Current—SHDN SHDN = 0V, Not Including Switch Leakage 0.1 1 µA

Quiescent Current—Active VC = 0V, MODE/SYNC = 0V, Rt = 300k (Note 3) 440 800 µA

NMOS Switch Leakage 0.1 5 µA

PMOS Switch Leakage 0.1 10 µA

NMOS Switch On Resistance 0.16 Ω

PMOS Switch On Resistance 0.18 Ω

NMOS Current Limit ● 1 1.6 A

NMOS Burst Current Limit 0.66 A

Maximum Duty Cycle Rt = 15k ● 80 85 %

Minimum Duty Cycle ● 0%

Frequency Accuracy Rt = 15k ● 1.6 2 2.4 MHz

MODE/SYNC Input High 1.4 V

MODE/SYNC Input Low 0.4 V

MODE/SYNC Input Current V

Error Amp Transconductance ∆I = –5µA to 5µA, VC = V

PGOOD Threshold Referenced to Feedback Voltage –6 –9 – 12 %

= 3.3V unless otherwise noted.

OUT

< 1mA 0.85 1.0 V

LOAD

MODE/SYNC

= 5.5V 0.01 1 µA

FB

85 µmhos

2

3401fa

Page 3

LTC3401

ELECTRICAL CHARACTERISTICS

The ● denotes specifications that apply over the full operating temperature range, otherwise specifications are at TA = 25°C.

VIN = 1.2V, V

PARAMETER CONDITIONS MIN TYP MAX UNITS

PGOOD Low Voltage I

PGOOD Leakage V

SHDN Input High V

SHDN Input Low 0.4 V

SHDN Input Current V

Thermal Shutdown 170 °C

= 3.3V unless otherwise noted.

OUT

= 1mA 0.1 0.2 V

PGOOD

= 1V, I

V

OUT

= 5.5V 0.01 1 µA

PGOOD

= VIN = V

SHDN

= 5.5V 0.01 1 µA

SHDN

= 20µA 0.1 0.4 V

PGOOD

OUT

1V

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: The LTC3401 is guaranteed to meet performance specifications

from 0°C to 70°C. Specifications over the –40°C to 85°C operating

temperature range are assured by design, characterization and correlation

Note 3: Current is measured into V

bootstrapped to the V

supply by (V

Note 4: Once the output is started, the IC is not dependant upon the V

supply.

with statistical process controls.

UW

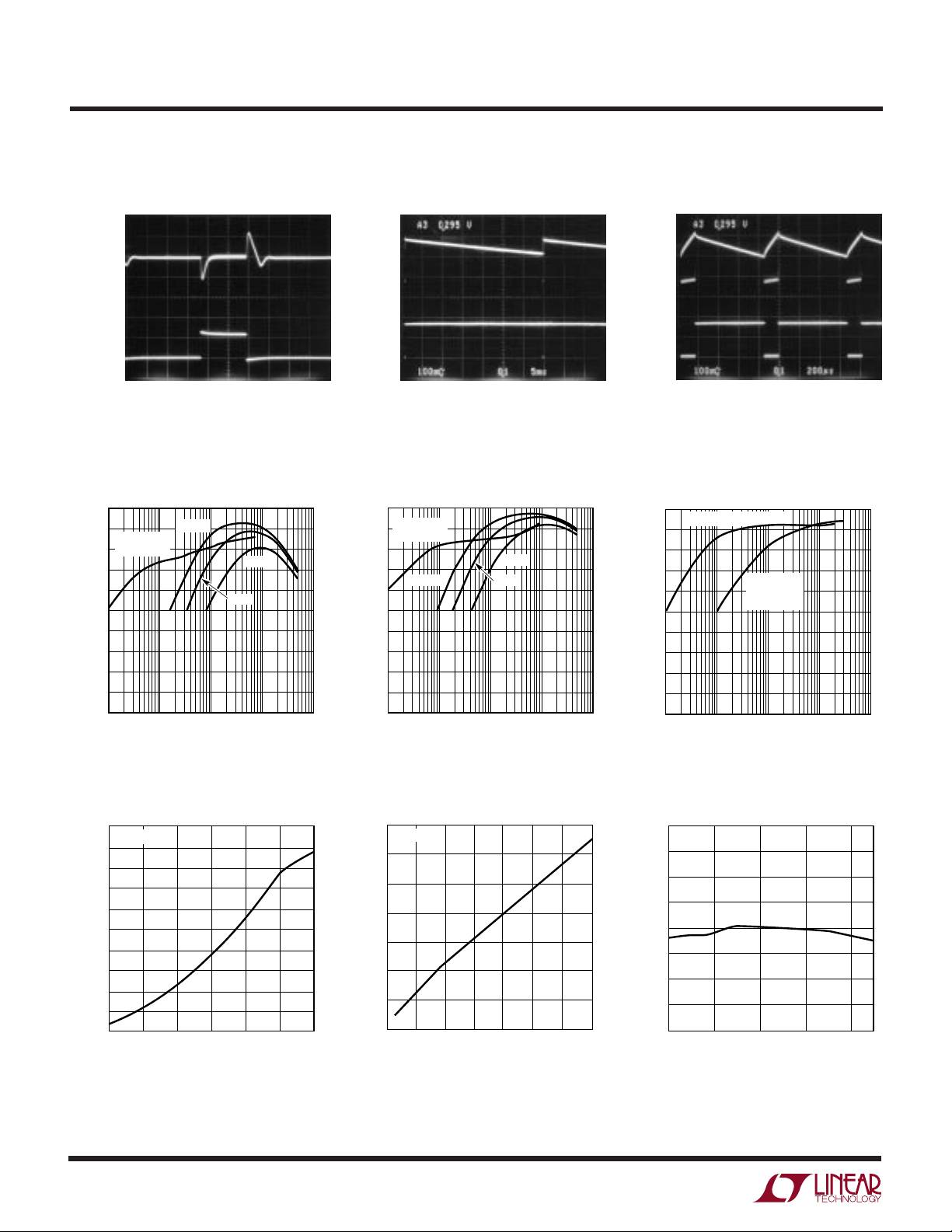

TYPICAL PERFOR A CE CHARACTERISTICS

SW Pin and Inductor Current (IC)

in Discontinuous Mode. Ringing

Control Circuitry Eliminates High

Switching Waveform on SW Pin

50mA/DIV

SW

1V/DIV

Frequency Ringing Transient Response 5mA to 50mA

I

L

0A

SW

1V/DIV

0V

since the supply current is

V

OUT

50mA

5mA

OUT

pin and in the application will reflect to the input

OUT

) • Efficiency. The outputs are not switching.

OUT/VIN

100mV/DIV

I

OUT

IN

50ns/DIV

3401 G01

200ns/DIV

3401 G02

C

= 22µF 200µs/DIV 3401 G03

OUT

L = 3.3µH

= 1MHz

f

OSC

3401fa

3

Page 4

LTC3401

UW

TYPICAL PERFOR A CE CHARACTERISTICS

Transient Response 50mA to 500mA

V

OUT

200mV/DIV

550mA

I

OUT

50mA

C

= 22µF 200µs/DIV 3401 G04

OUT

L = 3.3µH

= 1MHz

f

OSC

Converter Efficiency 1.2V to 3.3V

100

90

Burst Mode

80

OPERATION

70

60

50

40

EFFICIENCY (%)

30

20

10

0

0.1 10 100 1000

300kHz

1MHz

1

OUTPUT CURRENT (mA)

3MHz

3401 G07

Burst Mode Operation

V

OUT

AC

100mV/DIV

SW

1V/DIV

= 1.2V 5ms/DIV 3401 G05

V

IN

V

= 3.3V

OUT

= 100µF

C

OUT

= 250µA

I

OUT

MODE/SYNC PIN = HIGH

Converter Efficiency 2.4V to 3.3V

100

Burst Mode

90

OPERATION

80

70

300kHz

60

50

40

EFFICIENCY (%)

30

20

10

0

0.1 10 100 1000

1

OUTPUT CURRENT (mA)

3MHz

1MHz

3401 G08

Burst Mode Operation

V

OUT

AC

100mV/DIV

SW

1V/DIV

VIN = 1.2V 200µs/DIV 3401 G06

V

= 3.3V

OUT

= 100µF

C

OUT

= 20mA

I

OUT

MODE/SYNC PIN = HIGH

Converter Efficiency 3.6V to 5V

100

Burst Mode OPERATION

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

0

0.1

1MHz

FIXED

FREQUENCY

110

LOAD CURRENT (mA)

100

1000

3401 G10

Start-Up Voltage

vs I

OUT

500

TA = 25°C

400

300

200

OUTPUT CURRENT (mA)

100

0

0.8

0.9

4

1

1.1 1.2

VIN (V)

1.3

3401 G09

1.4

Efficiency Loss Without Schottky

vs Frequency

14

T

= 25°C

A

12

10

8

6

4

EFFICIENCY LOSS (%)

2

0

0.2

0.6 1.0

FREQUENCY (MHz)

1.8 2.6 3.0

1.4 2.2

3401 G11

Current Limit

1.80

1.75

1.70

1.65

1.60

1.55

CURRENT (A)

1.50

1.45

1.40

–15 25 105

–55

TEMPERATURE (°C)

3401fa

65

125

3401 G12

Page 5

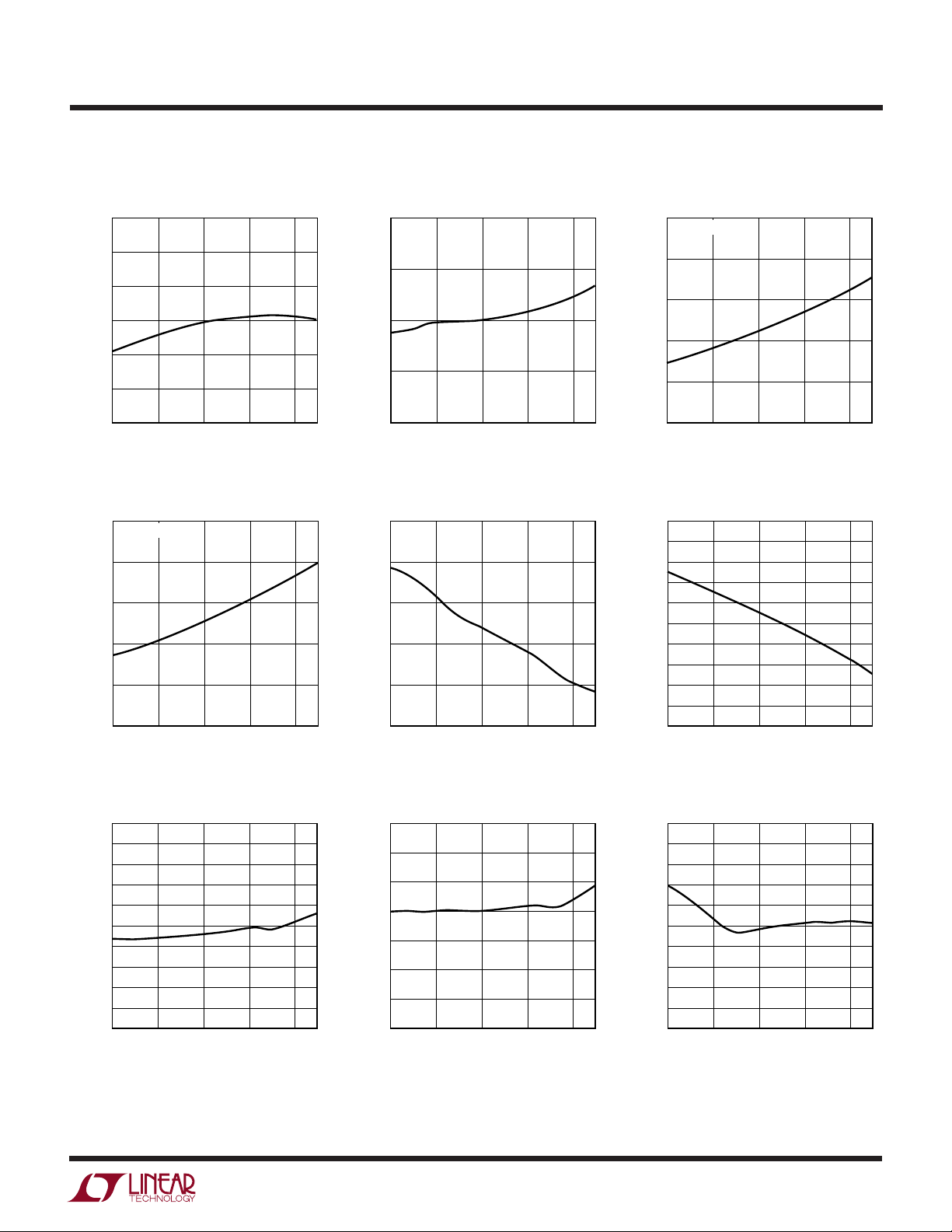

UW

TYPICAL PERFOR A CE CHARACTERISTICS

LTC3401

EA FB Voltage

1.28

1.27

1.26

1.25

VOLTAGE (V)

1.24

1.23

1.22

–55

PMOS R

0.30

V

OUT

0.25

0.20

0.15

RESISTANCE (Ω)

0.10

0.05

–55

–15 25 105

TEMPERATURE (°C)

65

DS(ON)

= 3.3V

–15 25 105

TEMPERATURE (°C)

65

3401 G13

3401 G16

125

125

Oscillator Frequency Accuracy

2.10

Rt = 15k

2.05

2.00

FREQUENCY (MHz)

1.95

1.90

–15 25 105

–55

TEMPERATURE (°C)

Start-Up Voltage

1.1

1.0

0.9

0.8

VOLTAGE (V)

0.7

0.6

–15 25 105

–55

TEMPERATURE (°C)

NMOS R

0.30

0.25

0.20

0.15

RESISTANCE (Ω)

0.10

65

125

3401 G14

0.05

–55

DS(ON)

V

= 3.3V

OUT

–15 25 105

TEMPERATURE (°C)

65

125

3401 G22

Shutdown Threshold

1.10

1.05

1.00

0.95

0.90

0.85

0.80

VOLTAGE (V)

0.75

0.70

0.65

65

125

3401 G17

0.60

–15 25 105

–55

TEMPERATURE (°C)

65

125

3401 G18

PGOOD Threshold

–7.0

–7.5

–8.0

–8.5

(%)

FB

–9.0

–9.5

–10.0

–10.5

PERCENT FROM V

–11.0

–11.5

–12.0

–55

–15 25 105

TEMPERATURE (°C)

65

3401 G19

125

Burst Mode Operation Current

44

42

40

38

36

CURRENT (µA)

34

32

30

–15 25 105

–55

TEMPERATURE (°C)

V

Turn-Off Voltage

OUT

2.50

2.45

2.40

2.35

2.30

2.25

2.20

VOLTAGE (V)

2.15

2.10

2.05

65

125

3401 G20

2.00

–15 25 105

–55

TEMPERATURE (°C)

3401fa

65

125

3401 G21

5

Page 6

LTC3401

U

UU

PI FU CTIO S

Rt (Pin 1): Timing Resistor to Program the Oscillator

Frequency.

10

•

OSC

310

=

Hz

R

t

f

MODE/SYNC (Pin 2): Burst Mode Select and Oscillator

Synchronization.

MODE/SYNC = High. Enable Burst Mode operation. The

inductor peak inductor current will be 1/3 the current

limit value and return to zero current on each cycle.

During Burst Mode operation the operation is variable

frequency, providing a significant efficiency improvement at light loads. It is recommended the Burst Mode

operation only be entered once the part has started up.

MODE/SYNC = Low. Disable Burst Mode operation and

maintain low noise, constant frequency operation.

MODE/SYNC = External CLK. Synchronization of the

internal oscillator and Burst Mode operation disable. A

clock pulse width of 100ns to 2µs is required to

synchronize.

VIN (Pin 3): Input Supply Pin.

SW (Pin 4): Switch Pin. Connect inductor and Schottky

diode here. For applications with output voltages over

4.3V, a Schottky diode is required to ensure that the SW

pin voltage does not exceed its absolute maximum rating.

Minimize trace length to keep EMI down. For discontinuous inductor current, a controlled impedance is placed

from SW to VIN from the IC to eliminate high frequency

ringing due to the resonant tank of the inductor and SW

node capacitance, therefore reducing EMI radiation.

GND (Pin 5): Signal and Power Ground for the IC.

PGOOD (Pin 6): Power Good Comparator Output. This

open-drain output is low when VFB < –9% from its

regulation voltage.

V

(Pin 7): Output of the Synchronous Rectifier and

OUT

Bootstrapped Power Source for the IC. A ceramic capacitor of at least 1µF is required and should be located as

close to the V

FB (Pin 8): Feedback Pin. Connect resistor divider tap

here. The output voltage can be adjusted from 2.6V to

5.5V. The feedback reference voltage is typically 1.25V.

VC (Pin 9): Error Amp Output. A frequency compensation

network is connected to this pin to compensate the loop.

See the section “Compensating the Feedback Loop” for

guidelines.

SHDN (Pin 10): Shutdown. Grounding this pin shuts down

the IC. Tie to >1V to enable (VIN or digital gate output). To

operate with input voltages below 1V once the converter

has started, a 1M resistor from SHDN to VIN, and a 5M

resistor from SHDN to V

esis During shutdown the output voltage will hold up to V

minus a diode drop due to the body diode of the PMOS

synchronous switch. If the application requires a complete disconnect during shutdown then refer to section

“Output Disconnect Circuits”.

and GND pins as possible (Pins 7 and 5).

OUT

will provide sufficient hyster-

OUT

IN

6

3401fa

Page 7

BLOCK DIAGRA

W

LTC3401

+

1V TO

V

+ 0.3

OUT

SHDN

GND

10

5

V

IN

3

SHUTDOWN

ANTIRING

ANTICROSS

COND

CURRENT

LIMIT

PWM

LOGIC

SLEEP

SW

4

N

+

–

CURRENT

COMP

+

I

SENSE

AMP

–

1.6A TYP

–

+

+–

Σ

10mV

P

V

OUT

7

V

OUT

2.6V TO 5V

+

+

–

I

ZERO

AMP

+

ERROR

AMP

1.25V

–

FB

8

V

9

R1

C

PGOOD

Burst Mode

CONTROL

R

t

1

6

OSC

N

SYNC

SLOPE COMP

–

+

1.25V – 9%

MODE/SYNC

2

0 = FIXED FREQ

1 = BURST MODE

3401 BD

3401fa

R2

7

Page 8

LTC3401

WUUU

APPLICATIO S I FOR ATIO

DETAILED DESCRIPTION

The LTC3401 provides high efficiency, low noise power

for applications such as portable instrumentation. The

current mode architecture with adaptive slope compensation provides ease of loop compensation with excellent

transient load response. The low R

synchronous switches provide the pulse width modulation control at high efficiency.

The Schottky diode across the synchronous PMOS switch

provides a lower drop during the break-before-make time

(typically 20ns) of the NMOS to PMOS transition. The

Schottky diode improves efficiency (see graph “Efficiency

loss without Schottky vs Frequency”). While the IC’s

quiescent current is a low 38µA, high efficiency is achieved

at light loads when Burst Mode operation is entered.

Low Voltage Start-Up

The LTC3401 is designed to start up at input voltages of

typically 0.85V. The device can start up under some load,

(see graph “Start-Up vs Input Voltage”). Once the output

voltage exceeds a threshold of 2.3V, the IC powers itself

from V

has no dependency on the VIN input voltage, eliminating

the requirement for a large input capacitor. The input

voltage can drop below 0.5V without affecting the operation, but the limiting factor for the application becomes the

availability of the power source to supply sufficient energy

to the output at the low voltages.

Low Noise Fixed Frequency Operation

Oscillator. The frequency of operation is set through a

resistor from the Rt pin to ground:

f = 3 • 1010/R

An internally trimmed timing capacitor resides inside the

IC. The oscillator can be synchronized with an external

clock inserted on the MODE/SYNC pin. When synchronizing the oscillator, the free running frequency must be set

to approximately 30% lower than the desired synchronized frequency. Keeping the sync pulse width below 2µs

will ensure that Burst Mode operation is disabled.

instead of VIN. At this point, the internal circuitry

OUT

t

, low gate charge

DS(ON)

Current Sensing. Lossless current sensing converts the

peak current signal to a voltage to sum in with the internal

slope compensation. This summed signal is compared to

the error amplifier output to provide a peak current control

command for the PWM. The slope compensation in the IC

is adaptive to the input and output voltage. Therefore, the

converter provides the proper amount of slope compensation to ensure stability and not an excess causing a loss of

phase margin in the converter.

Error Amp. The error amplifier is a transconductance

amplifier with gm = 0.1ms. A simple compensation network is placed from the VC pin to ground.

Current Limit. The current limit amplifier will shut the

NMOS switch off once the current exceeds its threshold.

The current amplifier delay to output is typically 50ns.

Zero Current Amp. The zero current amplifier monitors the

inductor current to the output and shuts off the synchronous rectifier once the current is below 50mA, preventing

negative inductor current.

Antiringing Control. The anitringing control will place an

impedance across the inductor to damp the ringing on the

SW pin during discontinuous mode operation. The LC

ringing (L = inductor, CSW = capacitance on the switch pin)

is low energy, but can cause EMI radiation.

Burst Mode Operation

Burst Mode operation is when the IC delivers energy to the

output until it is regulated and then goes into a sleep mode

where the outputs are off and the IC is consuming only

38µA. In this mode, the output ripple has a variable

frequency component with load current and the steady

state ripple will be typically below 3%.

During the period where the device is delivering energy to

the output, the peak current will be equal to 1/3 the current

limit value and the inductor current will terminate at zero

current for each cycle. In this mode the maximum output

current is given by:

V

I

OUT MAXBURST

()

IN

Amps

•≈6

V

OUT

SW

8

3401fa

Page 9

WUUU

APPLICATIO S I FOR ATIO

LTC3401

Burst Mode operation is user controlled by driving the

MODE/SYNC pin high to enable and low to disable. It is

recommended that Burst Mode operation be entered after

the part has started up.

COMPONENT SELECTION

Inductor Selection

The high frequency operation of the LTC3401 allows the

use of small surface mount inductors. The minimum

inductance value is proportional to the operating frequency and is limited by the following constraints:

3

L

H and L

>µ >

f

VV V

IN MIN OUT MAX IN MIN

•–

() ( ) ()

()

H

f Ripple V

••

OUT MAX

()

where

f = Operating Frequency (Hz)

Ripple = Allowable Inductor Current Ripple (A)

V

V

= Minimum Input Voltage (V)

IN(MIN)

OUT(MAX)

= Maximum Output Voltage (V)

SHDN

R

t

MODE

V

SW

GND

V

OUT

Figure 1. Recommended Component Placement. Traces

Carrying High Current Are Direct. Trace Area FB and VC Pins

Are Kept Low. Lead Length to Battery Should be Kept Short

IN

V

OUT

PGOOD

V

C

FB

3401 F01

Output Capacitor Selection

The output voltage ripple has several components. The

bulk value of the capacitor is set to reduce the ripple due

to charge into the capacitor each cycle. The max ripple due

to charge is given by:

IV

•

VR

BULK

PIN

=

CVf

••

OUT OUT

V

where

The inductor current ripple is typically set to 20% to 40%

of the maximum inductor current.

For high efficiency, choose an inductor with a high frequency core material, such as ferrite, to reduce core

losses. The inductor should have low ESR (equivalent

series resistance) to reduce the I2R losses and must be

able to handle the peak inductor current at full load without

saturating. Molded chokes or chip inductors usually do

not have enough core to support the peak inductor currents in the 1A to 2A region. To minimize radiated noise,

use a toroid, pot core or shielded bobbin inductor. See

Table 1 for a list of component suppliers.

Table 1. Inductor Vendor Information

SUPPLIER PHONE FAX WEBSITE

Coilcraft (847) 639-6400 (847) 639-1469 www.coilcraft.com

Coiltronics (516) 241-7876 (516) 241-9339 www.coiltronics.com

Murata (814) 237-1431 (814) 238-0490 www.murata.com

(800) 831-9172

Sumida

USA: (847) 956-0666 (847) 956-0702 www.japanlink.com

Japan: 81-3-3607-5111 81-3-3607-5144 sumida

IP = Peak Inductor Current

The ESR can be a significant factor for ripple in most power

converters. The ripple due to capacitor ESR is simply given

by:

VR

CESR

= IP • R

ESR

V

where

R

= Capacitor Series Resistance

ESR

Low ESR capacitors should be used to minimize output

voltage ripple. For surface mount applications, AVX TPS

series tantalum capacitors, Sanyo POSCAP, or TaiyoYuden ceramic capacitors are recommended. For throughhole applications Sanyo OS-CON capacitors offer low ESR

in a small package size. See Table 2 for a list of component

suppliers.

Table 2. Capacitor Vendor Information

SUPPLIER PHONE FAX WEBSITE

AVX (803) 448-9411 (803) 448-1943 www.avxcorp.com

Sanyo (619) 661-6322 (619) 661-1055 www.sanyovideo.com

Taiyo Yuden (408) 573-4150 (408) 573-4159 www.t-yuden.com

3401fa

9

Page 10

LTC3401

WUUU

APPLICATIO S I FOR ATIO

In some layouts it may be required to place a 1µF low ESR

capacitor as close to the V

and GND pins as possible.

OUT

Input Capacitor Selection

The input filter capacitor reduces peak currents drawn from

the input source and reduces input switching noise. Since

the IC can operate at voltages below 0.5V once the output

is regulated, demand on the input capacitor is much less

and in most applications a 3.3µF is sufficient.

Output Diode

For applications with output voltages over 4.3V, a Schottky

diode is required to ensure that the SW pin voltage does

not exceed its absolute maximum rating. The Schottky

diode across the synchronous PMOS switch provides a

lower drop during the break-before-make time (typically

20ns) of the NMOS to PMOS transition. The Schottky

diode improves peak efficiency (see graph “Efficiency

Loss Without Schottky vs Frequency”). Use of a Schottky

diode such as a MBRM120T3, 1N5817 or equivalent.

Since slow recovery times will compromise efficiency, do

not use ordinary rectifier diodes.

Operating Frequency Selection

There are several considerations in selecting the operating frequency of the converter. The first is determining

the sensitive frequency bands that cannot tolerate any

spectral noise. For example, in products incorporating

RF communications, the 455kHz IF frequency is sensitive

to any noise, therefore switching above 600kHz is desired. Some communications have sensitivity to 1.1MHz.

100

Burst Mode

90

OPERATION

80

70

300kHz

60

50

40

EFFICIENCY (%)

30

20

10

0

0.1 10 100 1000

Figure 2. Converter Efficiency 2.4V to 3.3V

1

OUTPUT CURRENT (mA)

3MHz

1MHz

3401 G08

In this case, converter frequencies up to 3MHz may be

employed.

The second consideration is the physical size of the

converter. As the operating frequency goes up, the inductor and filter caps go down in value and size. The trade off

is in efficiency since the switching losses due to gate

charge are going up proportional with frequency. For

example in Figure 2, for a 2.4V to 3.3V converter, the

efficiency at 100mA is 5% less at 2MHz compared to

300kHz.

Another operating frequency consideration is whether the

application can allow “pulse skipping.” In this mode, the

minimum on time of the converter cannot support the duty

cycle, so the converter ripple will go up and there will be

a low frequency component of the output ripple. In many

applications where physical size is the main criterion then

running the converter in this mode is acceptable. In

applications where it is preferred not to enter this mode,

then the maximum operating frequency is given by:

VV

–

f

MAX NOSKIP

where t

ON(MIN)

= minimum on time = 120ns

OUT IN

=

Vt

•

OUT ON MIN_()

Hz

Reducing Output Capacitance with a Load Feed

Forward Signal

In many applications the output filter capacitance can be

reduced for the desired transient response by having the

device commanding the change in load current, (i.e.

system microcontroller), inform the power converter of

the changes as they occur. Specifically, a “load feed

forward” signal coupled into the VC pin gives the inner

current loop a head start in providing the change in output

current. The transconductance of the LTC3401 converter

at the VC pin with respect to the inductor current is typically

130mA/100mV, so the amount of signal injected is proportional to the anticipated change of inductor current

with load. The outer voltage loop performs the remainder

of the correction, but because of the load feed forward

signal, the range over which it must slew is greatly

reduced. This results in an improved transient response.

3401fa

10

Page 11

WUUU

f

VR

LV

Hz

RHPZ

IN O

O

=

2

2

2••••π

APPLICATIO S I FOR ATIO

LTC3401

A logic level feed forward signal, VFF, is coupled through

components C5 and R6. The amount of feed forward

signal is attenuated with resistor R6 and is given by the

following relationship:

R

6

where ∆I

V

IN

VRV

515

•• •.

FF IN

VI

•–∆

OUT OUT

= load current change.

OUT

LTC3401

3

V

IN

10

SHDN

2

MODE/SYNC

6

PGOOD

1

R

LOAD FEED

FORWARD

SIGNAL

t

V

GND

SW

OUT

V

FB

V

C

FF

4

7

8

9

5

3.3nF

R6

Figure 3

R

5≈

V

OUT

C3

R5

C5

3404 F03

Closing the Feedback Loop

The LTC3401 uses current mode control with internal

adaptive slope compensation. Current mode control eliminates the 2nd order filter due to the inductor and output

capacitor exhibited in voltage mode controllers, and simplifies it to a single-pole filter response. The product of the

modulator control to output DC gain plus the error amp

open-loop gain equals the DC gain of the system.

GDC = G

G

CONTROL

CONTROLOUTPUT

2•

=

I

OUT

• G

V

IN

, GEA ≈ 2000

EA

where C

is the output filter capacitor.

OUT

The output filter zero is given by:

f

FILTERZERO

where R

=

2• • •π

is the capacitor equivalent series resistance.

ESR

1

RC

ESR OUT

Hz

A troublesome feature of the boost regulator topology is

the right half plane zero (RHP) and is given by:

At heavy loads this gain increase with phase lag can occur

at a relatively low frequency. The loop gain is typically

rolled off before the RHP zero frequency.

The typical error amp compensation is shown in Figure 4.

The equations for the loop dynamics are as follows:

f

POLE

≈

1

22010

•• • •

1

π

6

Hz

C

C

1

whichis extremelyclosetoDC

f

ZERO

f

POLE

=

1

≈

2

1

2

•• •

π

RC

1

•• •

π

RC

2

ERROR

AMP

Hz

ZC

1

Hz

ZC

2

1.25V

+

FB

8

–

V

C

9

V

OUT

R1

R2

C

R

Z

C

C1

C2

3401 F04

The output filter pole is given by:

I

OUT

VC

π••

OUT OUT

f

FILTERPOLE

=

Hz

Figure 4

Refer to Application Note AN-76 for more closed loop

examples.

3401fa

11

Page 12

LTC3401

U

U

OUTPUT DISCO ECT CIRCUITS

Single Cell Output Disconnect

VIN = 0.9V TO 1.5V

* SET RB TO FORCE BETA OF ≤100; RB =

0 = FIXED FREQUENCY

1 = Burst Mode OPERATION

Dual Cell Output Disconnect Alllowing Full Load Start-Up

VIN = 1.8V TO 3V

R7

1M

10

3

V

10

SHDN

2

MODE/SYNC

6

PGOOD

1

R

3

V

IN

SHDN

2

MODE/SYNC

6

PGOOD

1

R

t

LTC3401

IN

t

LTC3401

V

GND

SW

OUT

ZETEX

FMMT717

4

SW

7

V

OUT

8

FB

9

V

C

5

GND

(V

– V

INMIN

I

OUTMAX

– 0.7V) • 100

IRLML6401

RG

1M

OUT

4

7

8

FB

9

V

C

5

RB*

2N2222

C5

1µF

3404 TA03

V

OUT

V

OUT

C5

1µF

12

0 = FIXED FREQUENCY

1 = Burst Mode OPERATION

3404 TA04

3401fa

Page 13

TYPICAL APPLICATIO S

Single Cell to 3V at 50mA, 1.2mm High, 3MHz Step-Up Converter

L1

5.1M

3

V

IN

SHDN

2

MODE/SYNC

6

PGOOD

1

R

t

R

t

10k

1µH

LTC3401

SW

V

OUT

FB

V

C

GND

C1: TAIYO YUDEN JMK212BJ225MG

C2: TAIYO YUDEN JMK212BJ475MG

D1: CENTRAL SEMICONDUCTOR CMDSH-3

L1: TAIYO YUDEN LB2016

VIN = 0.9V TO 1.5V

R3

1M

+

1

CELL

C1

2.2µF

0 = FIXED FREQUENCY

1 = Burst Mode OPERATION

10

U

R4

LTC3401

D1

4

7

8

9

C3

470pF

5

R5

39k

866k

C4

20pF

R2

R1

619k

V

OUT

3V

100mA

C2

4.7µF

3404 TA05a

90

80

70

60

50

40

EFFICIENCY (%)

30

20

10

0

0.1 10 100 1000

Efficiency

Burst Mode

OPERATION

1

OUTPUT CURRENT (mA)

FIXED

FREQUENCY

VIN = 1.2V

3401 TA05b

Single Cell to 3V at 200mA, 600kHz Step-Up Converter

R4

L1

5.1M

VIN = 0.9V TO 1.5V

R3

1M

+

1

CELL

C1

3.3µF

0 = FIXED FREQUENCY

1 = Burst Mode OPERATION

3

V

10

SHDN

2

MODE/SYNC

6

PGOOD

1

R

R

t

50k

IN

t

10µH

LTC3401

SW

V

OUT

GND

C1: TAIYO YUDEN JMK212BJ335MG

C2: TAIYO YUDEN JMK325BJ226MM

D1: ON SEMICONDUCTOR MBRM120T3

L1: SUMIDA CD54-100

D1

4

7

8

FB

9

V

C

C3

470pF

5

R5

82k

866k

C4

4.7pF

V

OUT

3V

200mA

R2

C2

22µF

R1

619k

3404 TA06a

100

90

Burst Mode

80

OPERATION

70

60

50

40

EFFICIENCY (%)

30

20

10

0

0.1

Efficiency

FIXED

FREQUENCY

110

LOAD CURRENT (mA)

VIN = 1.2V

100

1000

3401 TA06b

3401fa

13

Page 14

LTC3401

LOAD CURRENT (mA)

0.1

0

EFFICIENCY (%)

10

30

40

50

100

70

3401 TA07b

20

80

90

60

110

100

1000

1MHz

FIXED

FREQUENCY

Burst Mode OPERATION

VIN = 3.6V

TYPICAL APPLICATIO S

Li-Ion to 5V at 300mA, 1MHz Step-Up Converter

L1

3

V

IN

10

SHDN

2

MODE/SYNC

6

PGOOD

1

R

t

R

t

30k

10µH

LTC3401

V

GND

SW

OUT

4

7

8

FB

9

V

C

5

VIN = 2.5V TO 4.2V

R3

1M

Li-Ion

C1

4.7µF

U

D1*

C3

470pF

R5

82k

1.65M

C4

4.7pF

V

OUT

5V

300mA

R2

C2*

22µF

R1

549k

Efficiency

1 = Burst Mode OPERATION

14

0 = FIXED FREQUENCY

C1: TAIYO YUDEN JMK212BJ106MG

C2: PANASONIC ECH-U

D1: ZETEX ZHCS-1000

D2 TO D4: 1N4148

*LOCATE COMPONENTS AS CLOSE TO

IC AS POSSIBLE

C1: TAIYO YUDEN JMK212BJ475MG

C2: TAIYO YUDEN JMK325BJ226MM

D1: ON SEMICONDUCTOR MBRM120T3

L1: SUMIDA CDC5023-100

3404 TA07a

High Efficiency, Compact CCFL Supply with Remote Dimming

C3

27pF

1kV

5

6

T1

4

CCFL

C2

Q2

L1

33µF

C5

1µF

C4

0.1µF

R4

D4

20k

D2 D3

R2

10k

CCFL BACKLIGHT APPLICATION CIRCUITS

CONTAINED IN THIS DATA SHEET ARE

COVERED BY U.S. PATENT NUMBER 5408162

AND OTHER PATENTS PENDING

R3

1k

DIMMING

INPUT

0V TO 2.5V

3404 TA08

= 2.5V TO 4.2V

V

IN

Li-Ion

C1

10µF

1M

10 2 3

1

R1

300Ω

D1

R5

LTC3401

3

V

IN

10

SHDN

2

MODE/SYNC

6

PGOOD

1

R

t

R

t

150k

L1: SUMIDA CD-54-330MC

Q1, Q2: ZETEX FMMT-617

T1: SUMIDA C1Q122

V

OUT

GND

SW

Q1

0.22µF

4

7

8

FB

9

V

C

5

3401fa

Page 15

PACKAGE DESCRIPTION

U

MS Package

10-Lead Plastic MSOP

(Reference LTC DWG # 05-08-1661)

0.889

± 0.127

(.035 ± .005)

LTC3401

5.23

(.206)

MIN

0.305 ± 0.038

(.0120 ± .0015)

TYP

RECOMMENDED SOLDER PAD LAYOUT

0.254

(.010)

GAUGE PLANE

0.18

(.007)

NOTE:

1. DIMENSIONS IN MILLIMETER/(INCH)

2. DRAWING NOT TO SCALE

3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

3.2 – 3.45

(.126 – .136)

DETAIL “A”

DETAIL “A”

0.50

(.0197)

BSC

° – 6° TYP

0

0.53 ± 0.01

(.021 ± .006)

SEATING

PLANE

3.00 ± 0.102

(.118 ± .004)

(NOTE 3)

4.88 ± 0.10

(.192 ± .004)

0.17 – 0.27

(.007 – .011)

1.10

(.043)

MAX

12

0.50

(.0197)

TYP

8910

3

7

6

45

0.497 ± 0.076

(.0196 ± .003)

REF

3.00 ± 0.102

(.118 ± .004)

NOTE 4

0.86

(.034)

REF

0.13 ± 0.05

(.005 ± .002)

MSOP (MS) 0402

3401fa

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

15

Page 16

LTC3401

TYPICAL APPLICATIO

U

Triple Output Converter

D2 D3

0.1µF

3

V

10

SHDN

2

MODE/SYNC

6

PGOOD

1

R

R

t

30k

L1, 4.7µH

LTC3401

IN

t

V

GND

SW

OUT

FB

V

0.1µF

VIN =1.8V TO 3V

R3

1M

+

2

CELLS

C1

4.7µF

0 = FIXED FREQ

1 = Burst Mode OPERATION

C1: TAIYO YUDEN JMK212BJ475MG

C2: TAIYO YUDEN JMK325BJ226MM

D1: ON SEMICONDUCTOR MBRM120T3

D2 TO D7: ZETEX FMND7000 DUAL DIODE

L1: SUMIDA CD43-4R7M

D4 D5

0.1µF 0.1µF 4.7µF

D1

4

7

8

9

C

5

C3

470pF

R5

82k

R2

909k

R1

549k

C4

4.7pF

D6

D7

4.7µF

–2.5V

1mA

8V

2mA

V

OUT

3.3V

500mA

C2

22µF

3401 TA09

RELATED PARTS

PART NUMBER DESCRIPTION COMMENTS

LT1306 Sync, Fixed Frequency, Step-Up DC/DC Converter Internal 2A Switches, VIN As Low As 1.8V

LT1308A/LT1308B High Current, Micropower, Single Cell 600kHz DC/DC Converter 5V at 1A from Single Li-Ion Cell

LT1317/LT1317B Micropower 600kHz PWM DC/DC Converter VIN As Low As 1.5V, IQ = 100µA

LT1610 1.7MHz, Single Cell Micropower DC/DC Converter 3V at 30mA from 1V, 5V at 200mA from 3.3V

LT1613 1.4MHz, Single Cell DC/DC Converter in SOT-23 VIN As Low As 1.1V, 3V at 30mA from Single Cell

LT1615 Micropower Step-Up DC/DC Converter in SOT-23 IQ = 20µA, 1µA Shutdown Current, VIN As Low As 1V

LT1619 High Efficiency Boost DC/DC Controller 1A Gate Drive, 1.1V to 20V Input, Separate VCC for Gate Drive

LT1930A 2.2MHz DC/DC Converter in SOT-23 VIN = 2.6V to 16V, 5V at 450mA from 3.3V Input

LT1949 600kHz, 1A Switch PWM DC/DC Converter 1.1A, 0.5Ω/30V Internal Switch, VIN As Low As 1.8V

LTC3400 Single Cell, High Current (600mA) Micropower, Synchronous VIN = 0.85V to 5.5V, Up to 92% Efficiency Synchronizable

1.2MHz Step-Up DC/DC Converter Oscillator from 100kHz to 1.2MHz, ThinSOT

LTC3402 Single Cell, High Current (2A) Micropower, Synchronous VIN = 0.5V to 5.5V, Up to 97% Efficiency Synchronizable

3MHz Step-Up DC/DC Converter Oscillator from 100kHz to 3MHz, 10-Lead MSOP Package

LTC3423 Single Cell, High Current (2A) Micropower, Synchronous V

3MHz Step-Up DC/DC Converter for V

< 2.6V Oscillator from 100kHz to 3MHz

OUT

= 1.5V, Up to 97% Efficiency Synchronizable

OUT

ThinSOT is a trademark of Linear Technology Corporation.

3401fa

LT/TP 0502 1.5K REV A • PRINTED IN USA

LINEAR TECHNOLOGY CORPORATION 2001

16

Linear T echnolog y Corporation

1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900 ● FAX: (408) 434-0507

●

www.linear.com

TM

Package

Loading...

Loading...