Page 1

Ordering number : ENN*6747

LC86E6548

8-Bit Single Chip Microcontroller

with the UVEPROM

Preliminary

Overview

The LC86E6548 is a CMOS 8-bit single chip microcontroller with UVEPROM for the LC866500 series.

This microcontroller has the function and the pin description of the LC866500 series mask ROM version, and 48K-byte

EPROM. The program data is rewritable. It is suitable to develop the program.

Features

(1) Option switching by EPROM data

The option function of the LC866500 series can be specified by the EPROM data.

LC86E6548 can be checked the function of the trial pieces using the mass production board.

(2) Internal one-time EPROM capacity : 49408 bytes

(3) Internal RAM capacity : 1152 bytes

Used EPROM or RAM capacity are equal ROM or RAM capacity of mask ROM version which applies

LC86E6548 .

Mask ROM version EPROM capacity RAM capacity

LC866548 49152 bytes 1152 bytes

LC866540 40960 bytes 1152 bytes

LC866532 32768 bytes 1152 bytes

LC866528 28672 bytes 896 bytes

LC866524 24576 bytes 896 bytes

CMOS IC

Ver.1.02

73196

91400 RM (IM) SK No.6747-1/21

Page 2

LC86E6548

(4) Operating supply voltage : 4.5V to 6.0V

(5) Instruction cycle time : 1.0µs to 366µs

(6) Operating temperature : +10°C to +40°C

(7) The pin compatible with the LC866500 series mask ROM devices

(8) Applicable mask ROM version : LC8665 48/LC866540//LC866532/LC866528/LC866524

(9) Factory shipment : QFC100S(with window)

Notice for use

LC86E6548 is provided for the first release and small shipping of the LC866500 series.

At using, take notice of the followings.

(1) A point of difference LC86E6548 and LC866500 series

Item LC86E6548 LC866548/40/32/28/24

Operation after reset

releasing

Pull-down resistor of

the following pins

•S0/T0 – S6/T6

•S7/T7 – S15/T15

•S16 – S31

•S32 – S47

•S48 – S51

Operating temperature

rang (Topg)

Power dissipation Refer to ‘electrical characteristics’ on the semiconductor news.

LC86E6548 uses 256 bytes that is addressed on FF00H to FFFFH in the program memory as the option configuration data

area. This option configuration cannot execute all options which LC866500 series have. Next tables show the options

that correspond and not correspond to LC86E6548.

• A kind of the option corresponding of the LC86E6548

A kind of option Pins, Circuits Contents of the option

Input/output form of

Input/output ports

*1) Specified in a bit

*2) Specified in nibble unit. The port of N-channel open drain output does not have the Pull-up MOS Tr..

The option is specified until 3ms after

going to a ‘H’ level to the reset terminal

by dgrees. The program is executed

from 00H of the program counter.

Pull-down resistor

provided/not provided

Not provi ded

Provided (fixed)

Provided (fixed)

Not provi ded

Not provi ded

+10°C to +40°C -30°C to +70°C

Port 0

Port 1

*1

Port 3

*1

1. N-channel open drain output

2. CMOS output *1

1. Pull-up MOS Tr. proveded

2. Pull-up MOS Tr. not provided *2

1. Input : Programmable pull-up MOS Tr.

2. Input : Programmable pull-up MOS Tr.

1. Input : No Programmable pull-up MOS Tr.

2. Input : Programmable pull-up MOS Tr.

Output : CMOS

The program is executed from 00H of the

program counter immediately after going to a

‘H’ level to reset terminal.

Pull-down resistor

provided/not provided

Specified by the option

Provided (fixed)

Specified by the option

Specified by the option

Not provi ded

Output : N-channel open drain

Output : CMOS

Output : N-channel open drain

No.6747-2/21

Page 3

LC86E6548

• A kind of the option not corresponding of the LC86E6548

A kind of option Pins, Circuits LC86E6548 LC866548/40/32/28/24

Pull-down resistor of

the high voltage

Withstand output terminals

•S0/T0 to S6/T6

•S16 to S31

•S32 to S47

Not provi ded

Provided (fixed)

Not provi ded

Specified by the option

Specified by the option

Specified by the option

(2) Option

The option data is created by the option specified program “SU86K.EXE”. The created option data is linked to the

program area by linkage loader “L86K.EXE” .

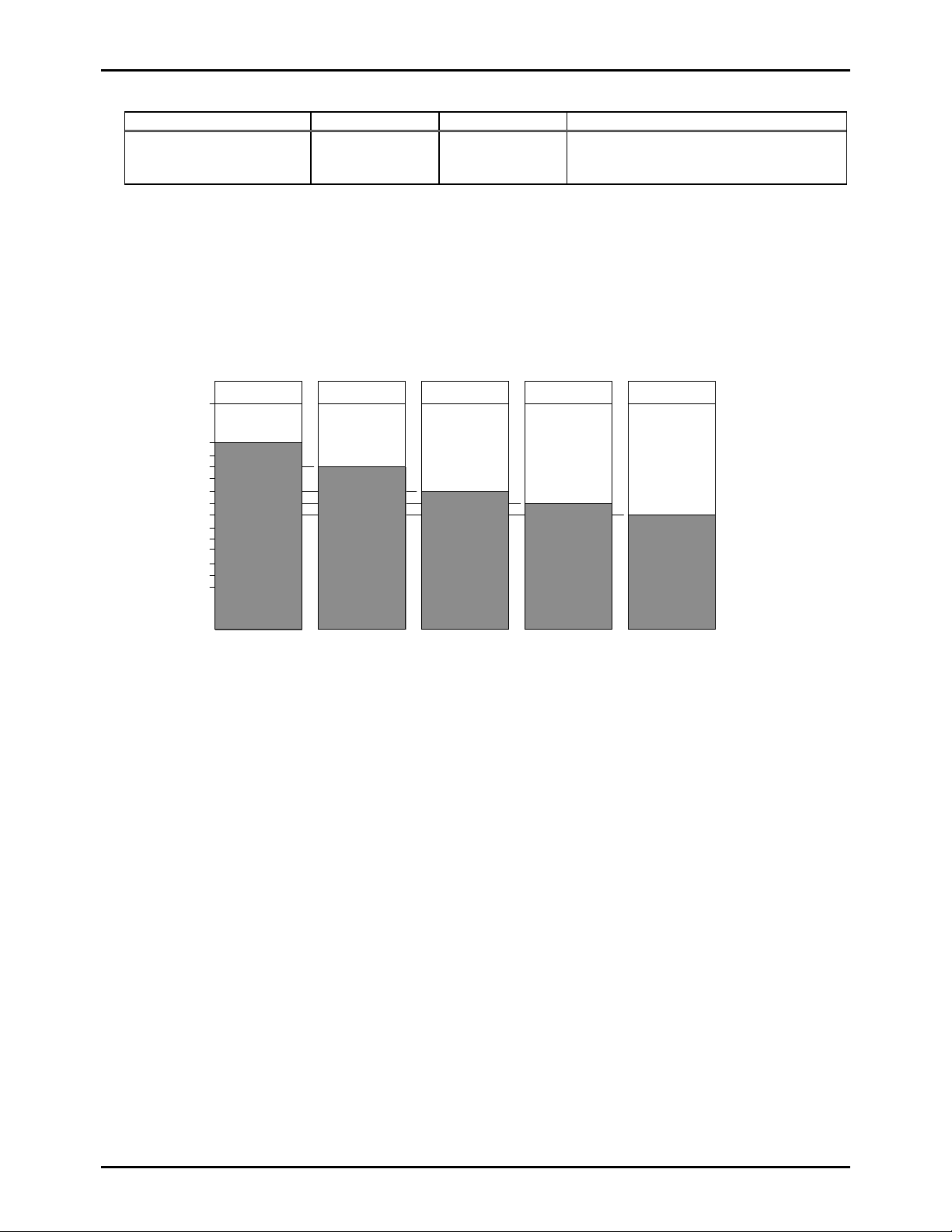

(3) ROM space

LC86E6548 and LC866500 series use 256 bytes that is addressed on 0FF00H to 0FFFFH in the program memory as the

option specified data area. These program memory capacity are 49152 bytes that is addressed on 0000H to BFFFH.

0FFFFH

0FF00H

0EFFFH

0DFFFH

0CFFFH

0BFFFH

0AFFFH

9FFFH

8FFFH

7FFFH

6FFFH

5FFFH

4FFFH

3FFFH

2FFFH

1FFFH

0FFFH

0000H

The option specified

area 256 bytes

Program area

48K bytes

LC866548

The option

specified area

Program area

40K bytes

LC866540

The option

specified area

Program area

32K bytes

LC866532

The option

specified area

Program area

28K bytes

LC866528

The option

specified area

Program area

24K bytes

LC866524

No.6747-3/21

Page 4

LC86E6548

How to use

(1) Preparation

A complete evaluation (EVA) file must be converted to an INTEL-HEX formatted file (HEX) file for program to the

LC86E6548.

An EVA2HEX.EXE. can convert a EVA file to a HEX file.

Program the file that converted by the EVA2HEX to the LC86E6548.

(2) How to program for the EPROM

LC86E6548 can be programmed by the EPROM programmer with attachment ; W86EP6548Q.

• Recommended EPROM programmer

Productor EEPROM programmer

Advantest R4945, R4944, R4943

Andou AF-9704

AVAL PKW-1100, PKW-3000

Minato electronics MODEL 1890A

• “27512 (Vpp=12.5V) Intel high speed programming” mode available. The address must be set to

“0 to 0FFFFH” and a jumper (D ASE C) must be set to ‘OFF’ at programming

.

(3) How to use the data security function

“Data security” is the disabled function to read the data of the EPROM.

The following is the process in order to execute the data security.

1. Set ‘ON’ the jumper of attachment.

2. Program again. Then EPROM programmer displays the error. The error means normally

activity of the data security. It is not a trouble of the EPROM programmer or the LSI.

Notes

• Data security is not executed when the data of all address have ‘FFH’ at the sequence 2 above.

• The programming by a sequential operation “BLANK⇒PROGRAM⇒VERIFY” cannot be executed data security at the

sequence 2 above.

• Set to ‘OFF’ the jumper after executing the data security.

Data security

of LSI

1 pin mark

1 pin

W86EP6548Q

Not data security

(4) How to eliminate

The programming data can be erased by using the EPROM eraser.

(5) Shielding

The UVEPROM (ultraviolet erasable programmable ROM) is in it. Put the seal on the window in use.

No.6747-4/21

Page 5

Pin Assignment

Z

N

N

S48/PG0

S49/PG1

S50/PG2

S51/PG3

P00

P01

P02

P03

VSS2

VDD2

P04

P05

P06

P07

P10/SO0

P11/SI0/SB0

P12/SCK0

P13/SO1

P14/SI1/SB1

P15/SCK1

LC86E6548

S47/PF7

S46/PF6

S45/PF5

S44/PF4

S43/PF3

S42/PF2

S41/PF1

S40/PF0

VDD4

S39/PE7

S38/PE6

S37/PE5

S36/PE4

S35/PE3

S34/PE2

S33/PE1

S32/PE0

S31/PD7

S30/PD6

S29/PD5

S28/PD4

S27/PD3

S26/PD2

S25/PD1

S24/PD0

8079787776757473727170696867666564636261605958575655545352

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

1 2 3 4 5 6 7 8 9

P30

P31

P32

P33

P16/BUZ

P17/PWM0

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

P34

P35

P36

P74

P37

RES

P70/INT0

CF1

CF2

VSS1

XT1/

XT2/P75

VDD1

P80/AN0

P81/AN1

P82/AN2

P83/AN3

P84/AN4

P85/AN5

P86/AN6

S23/PC7

26

P87/AN7

S22/PC6

27

P71/INT1

S21/PC5

28

P72/INT2/T0I

S20/PC4

29

P73/INT3/T0I

VP

51

30

S0/T0

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

S19/PC3

S18/PC2

S17/PC1

S16/PC0

VDD3

S15/T15

S14/T14

S13/T13

S12/T12

S11/T11

S10/T10

S9/T9

S8/T8

S7/T7

S6/T6

S5/T5

S4/T4

S3/T3

S2/T2

S1/T1

SANYO: QFC100S

No.6747-5/21

Page 6

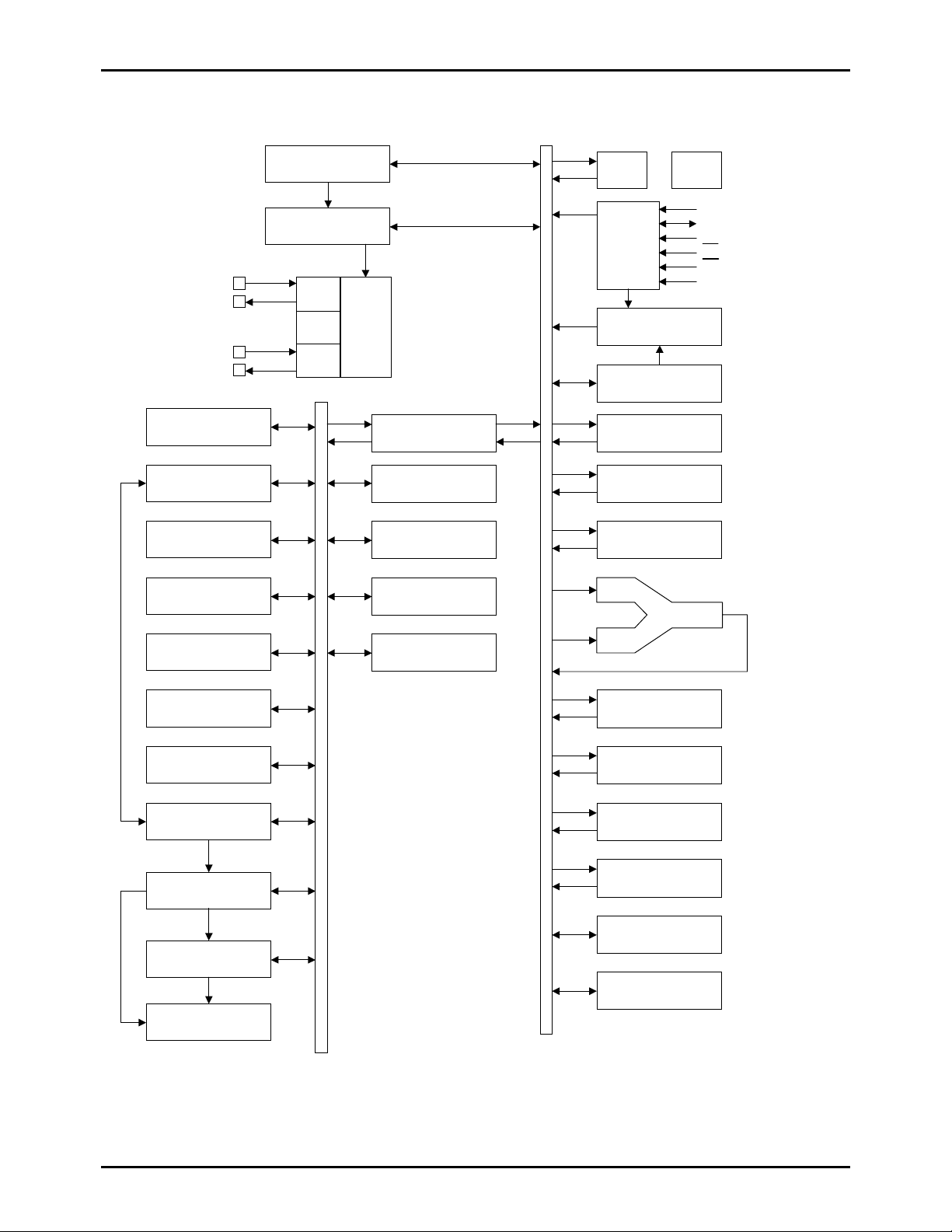

System Bl ock Diagram

Interrupt Control

Standby Control

Base Timer

SIO0

SIO1

Timer 0

Timer 1

ADC

INT0 to 3

Noise Filter

SIO Automatic

transmission

RAM

(128 bytes)

VFD controller

High voltage

Output

CF

RC

X’tal

Colck

Generator

LC86E6548

Bus Interface

Port 1

Port 3

Port 7

Port 8

IR PLA

EPROM

Control

EPROM (48KB)

PC

ACC

B Register

C Register

ALU

PSW

RAR

RAM

Stack Pointer

Port 0

Watchdog T i mer

A15-A0

D7-D0

TA

CE

OE

DASEC

No.6747-6/21

Page 7

LC86E6548

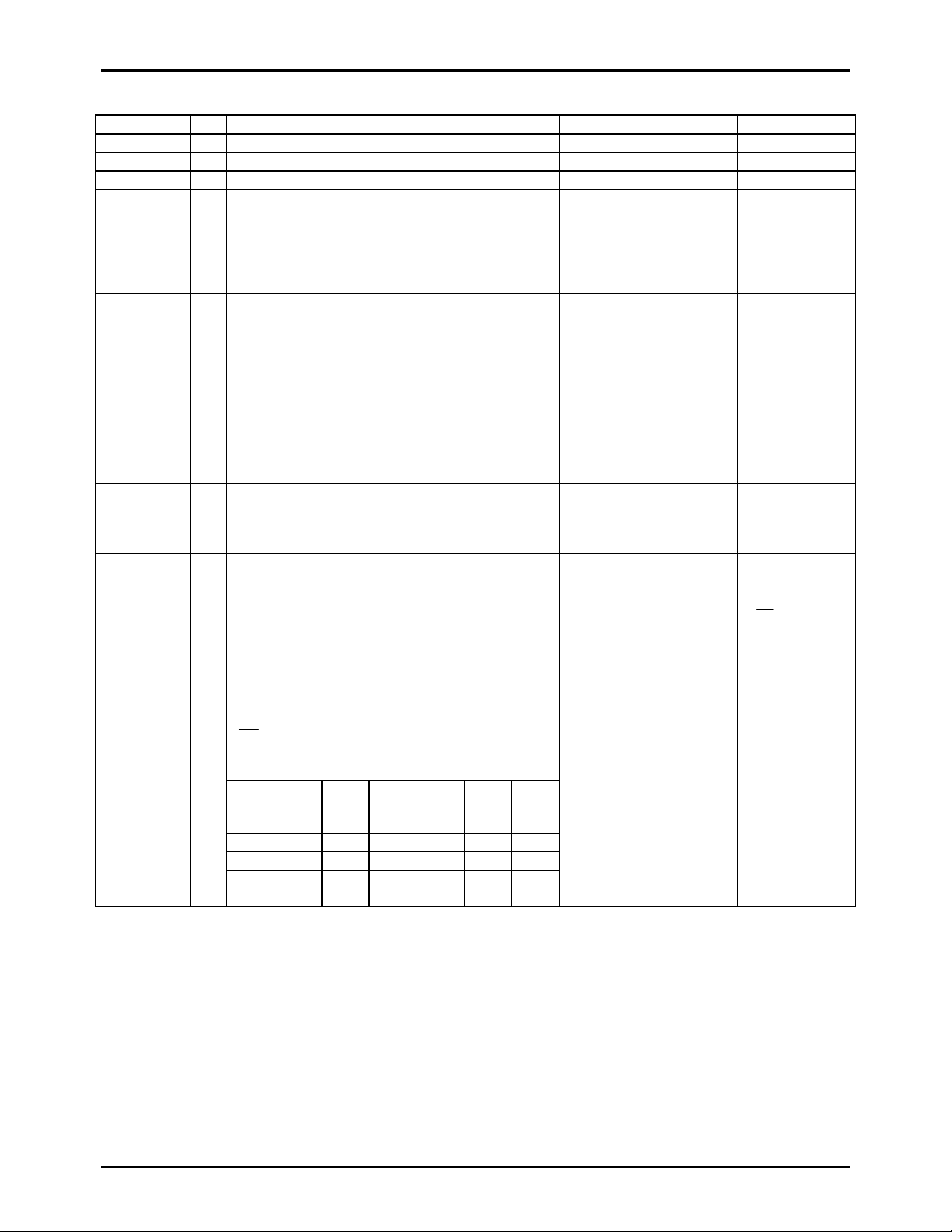

LC86E6548 Pin description

Pin name I/O Function description Option EPROM mode

VSS1,2 - Power pin (-) *4 - VDD1,2,3,4 - Power pin (+) *4 - VP - Power pin (+) for the VFD output pull-down resist - PORT0

P00 to P07

PORT1

P10 to P17

PORT3

P30 to P37

PORT7

P70 to P73

P74

to P75

I/O •8-bit input/output port

•Input for port 0 inter rupt

•Input/output in nibble units

•Input for HOL D rel ease

•15V withstand at N- channel open drain

output

I/O •8-bit input/output port

•Input/output can be specified in a bit unit

•Other pin functions

P10 SIO0 data output

P1 1 SIO 0 data input/bus input/output

P12 SIO0 clock input/output

P1 3 SIO 1 data output

P1 4 SIO 1 data input/bus input/output

P15 SIO1 clock input/output

P16 Buzzer output

P1 7 Timer 1 output (PWM0 output)

I/O •8-bit input/output port

•Input/output in bit unit

•15V withstand at N- channel open drain

output

•4-bit input/output port

•Input/output in bit un it

•2-bit input port

•Other pin functions

I/O

P70 : INT0 input/HOLD release/N-channel Tr.

I

output for watchdog timer

P71 : INT1 input/HOLD release inpu t

P72 : INT2 input/timer 0 event input

P73 : INT3 input with noise filter/timer 0 event

input

P74

: 32.768kHz crystal oscillation terminal XT1

P75 : 32.768kHz crystal oscillation terminal XT2

•Interrupt received forms, the vector addresses

rising falling rising

&

high

level

low

level

falling

INT0 enable enable disable enable enable 03H

INT1 enable enable disable enable enable 0BH

INT2 enable enable enable disable disable 13H

INT3 enable enable enable disable disable 1BH

Continue.

vector

•Pull-up resistor :

Provided/Not provided

(each nibble)

•Output form :

CMOS/N-channel open

drain (each bit)

•Output form :

CMOS/N-channel open

drain (each bit)

•Output form :

CMOS/N-channel open

drain (each bit)

-

Data line

D0 to D7

-

EPROM control

signals

DASEC (*1)

OE

(*2)

‚bE

(*3)

CE

No.6747-7/21

Page 8

LC86E6548

Pin name I/O Function description Option EPROM mode

PORT8

P80 to 83

P84 to 87

•4-bit input port

I

•Input/output in bit un it

I/O

•4-bit input port

- -

•Other functio n

AD input port (8 port pins)

S0/T0 to

S6/T6 *6

S7/T7 to

S15/T15

*7

O Output for VFD display controller

segment/timing in common

O •Output for VFD display controller

segmen t/timing with internal pull-down

resistor in common

- -

- TA (*5)

•Internal pull-down resistor output

S16 to S31

*8

I/O •Output for VFD display controller Segment

output

- •Address input

A15 to A0

•Other function

S16 : High voltage input port PC0

S17 : High voltage input port PC1

S18 : High voltage input port PC2

S19 : High voltage input port PC3

S20 : High voltage input port PC4

S21 : High voltage input port PC5

S22 : High voltage input port PC6

S23 : High voltage input port PC7

S24 : High voltage input port PD0

S25 : High voltage input port PD1

S26 : High voltage input port PD2

S27 : High voltage input port PD3

S28 : High voltage input port PD4

S29 : High voltage input port PD5

S30 : High voltage input port PD6

S31 : High voltage input port PD7

S32 to S47

*9

I/O •Output for VFD display controller Segment

•Other functio n

- -

S32 : High voltage input port PE0

S33 : High voltage input port PE1

S34 : High voltage input port PE2

S35 : High voltage input port PE3

S36 : High voltage input port PE4

S37 : High voltage input port PE5

S38 : High voltage input port PE6

S39 : High voltage input port PE7

S40 : High voltage I/O port PF0

S41 : High voltage I/O port PF1

S42 : High voltage I/O port PF2

S43 : High voltage I/O port PF3

S44 : High voltage I/O port PF4

S45 : High voltage I/O port PF5

S46 : High voltage I/O port PF6

S47 : High voltage I/O port PF7

Continue.

No.6747-8/21

Page 9

LC86E6548

Pin name I/O Function description Option EPROM mode

S48 to S51

*9

I/O •Output for VFD display controller segment

•Other functio n

- -

S48 : High voltage I/O port PG0

S49 : High voltage I/O port PG1

S50 : High voltage I/O port PG2

S51 : High voltage I/O port PG3

RES

XT1/

P74

I Reset pin - I •Input pin for 32.768kHz crystal oscillation

- -

•Other functio n

P74

XT 1 : Input port

In case of non use, connect to VDD1.

XT2/P75 O •Output pin for 32.768kHz crystal oscillation

- -

•Other functio n

XT 2 : Input port P75

In case of non use, connect to VDD1 at using

as port or unconnect at using as oscillation.

CF1 I Input pin for the ceramic resonator oscillation - CF2 O Output pin for the ceramic resonator oscillation - -

All of port options (except pull-up resistor of port 0) can be specified in bit unit.

♦

*1 Memory select input for data security

*2 Output enable input

*3 Chip enable input

*4 Connect like the following figure to reduce noise into a VDD1 terminal.

Shorted the VSS1 terminal to the VSS2 terminal and to make the back-up time long.

*5 TA ! EPROM control signal input

*6 S0/T0 to S6/T6 : not prov i ded the pull-down resist or

*7 S7/T7 to S15/T15 : provided the pull-down resistor (fixed)

*8 S16 to S31 : provided the pull-down resistor (fixed)

*9 S32 to S51 : not provided the pull-down resistor

Power

Supply

Back-up capacitor

LSI

VDD1

VDD2

VDD3

VDD4

VSS1 VSS2

VFD

powers

No.6747-9/21

Page 10

LC86E6548

V

1. Absolute Maximum Ratings at VSS1=VSS2=0V and Ta=25°C

Parameter Symbol Pins Conditions

Supply voltage VDDMAX VDD1, VDD2

VDD3, VDD4

Input voltage

VI(1)

•Ports

74

,75

VDD1=VDD2

=VDD3=VDD4

-0.3 VDD+0.3

Ratings

DD[V] min. typ. max.

-0.3 +7.0

unit

V

•Ports 80,81,82,83

•Port 8

RES

•

VI(2) VP VDD-45 VDD+0.3

Output voltage VO(1) S0/T0 to S15/T15 VDD-45 VDD+0.3

Input/Output

voltage

VIO(1) •Port 1

•Ports 70,71,72,73

-0.3 VDD+0.3

•Ports 84,85,86,87

•Ports 0, 3 at CMOS

output option

VIO(2) Ports 0, 3 at N-ch open

-0.3 15

drain output option

VIO(3) S16 to S51 VDD-45 VDD+0.3

High

level

output

current

Low

level

output

current

Peak

output

current

Total

output

current

output

current

Total

output

current

IOPH(1) Ports 0, 1, 3 •CMOS output

•At each pins

IOPH(2) S0/T0 to S15/ T15 At each pi ns -30

IOPH(3) S16 to S5 1 At each pins -15

ΣIOAH(1)

IOAH(2)

Σ

ΣIOAH(3)

IOAH(4)

Σ

ΣIOAH(5)

IOAH(6)

Σ

Port 0 The total of all pins -30

Ports 1, 3 The total of al l pins -30

S0/T0 to S15/T15 The total of all pins -55

S16 to S27 The total of all pins -60

S28to S39 The total of all pins -60

S40 to S51 The total of all pins -60

IOPL(1) Ports 0,1,3 At each pins 20 Peak

IOPL(2) •Ports 70,71,72,73

At each pins 15

•Ports 84,85,86,87

IOAL(1)

Σ

ΣIOAL(2)

IOAL(3)

Σ

Port 0 The total of all pins 60

Ports 1,3,70 The total of all pins 50

•Ports 71,72,73

The total of all pins 20

-10

mA

•Ports 84,85,86,87

Maximum powe r

dissipation

Operating

Pdmax QFC100S

Ta=+10 to+40°C

500

mW

Topr +10 +40

°C

temperature

range

Storage

Tstg -55 +125

temperature

range

No.6747-10/21

Page 11

LC86E6548

2. Recommended Operating Range at Ta=+10°C to +40°C, VSS1=VSS2=0V

Parameter Symbol Pins Conditions

Operating

Supply voltage

VDD(1) VDD1=VDD2

=VVDD3=VDD4

0.98µs ≤ tCYC

tCYC ≤ 400µs

VDD[V] min. typ. max.

Hold voltage VH D VDD1=VDD2 RAMs and the

registers hold

voltage at HOLD

mode.

Pull-down

VP VP 4.5 to 6.0 -35 VDD

Voltage

Input high

VIH(1) Port 0 at CMOS output Output disable 4.5 to 6.0

voltage

VIH(2) Port 0 at N-ch open drain

Output disable 4.5 to 6.0 0.75VDD 13.5

output

VIH(3) •Port 1

Output disable 4.5 to 6.0 0.75VDD VDD

•Ports 72,73

•Port 3 at CMOS

output

VIH(4) •Port 3 at N-ch open

drain output

VIH(5) •Port 70

Output disable

4.5 to 6.0 0.75VDD 13.5

Tr. OFF

Output disable 4.5 to 6.0 0.75VDD VDD

Port input/interrupt

•Port 71

RES

•

VIH(6) Port 70

Output disable 4.5 to 6.0 0.9VDD VDD

Watchdog timer

VIH(7) •Port 8

74

•Ports

,75

VIH(8) S16 to S51 Output P-channel

Output disable 4.5 to 6.0 0.75VDD VDD

4.5 to 6.0

Tr. OFF

Input low

voltage

VIL(1) Port 0 at CMOS

output option

VIL(2) Port 0 at N-ch open

Output disable 4.5 to 6.0 VSS 0.2VDD

Output disable 4.5 to 6.0 VSS 0.25VDD

drain output

VIL(3) •Ports 1,3

Output disable 4.5 to 6.0 VSS 0.25VDD

•Ports 72,73

VIL(4) •Port 70

Output disable 4.5 to 6.0 VSS 0.25VDD

Port input/interrupt

•Port 71

RES

•

VIL(5) Port 70

Output disable 4.5 to 6.0 VSS

Watchdog timer

VIL(6) •Port 8

74

•Ports

,75

VIL(7) S16 to S51 Output P-channel

Output disable 4.5 to 6.0 VSS 0.25VDD

4.5 to 6.0 VP 0.2VDD

Tr. OFF

Operation

tCYC 4.5 to 6.0 0.98 400

cycle time

Continue.

Ratings

4.5 6.0

unit

V

2.0 6.0

0.

33VDD

+1.0

VDD

33VDD

0.

VDD

+1.0

0.

8VDD

-1.0

µs

No.6747-11/21

Page 12

LC86E6548

Parameter Symbol Pins Conditions

Oscillation

frequency

range

(Note 1)

FmCF(1) CF1, CF2 •6MHz

(ceramic resonator

oscillation)

•Refer to figure 1

FmCF(2) CF1, CF2 •3MHz

(ceramic resonator

oscillation)

•Refer to figure 1

FmRC RC oscillation 4.5 to 6.0 0.3 0.8 3.0

FsXtal XT1, XT2 •32.768kHz

(crystal oscillation)

•Refer to figure 2

Oscillation

stabilizing

time period

(Note 1)

tmsCF(1) CF1, CF2 •6MHz

(ceramic resonator

oscillation)

•Refer to figure 3

tmsCF(2) CF1, CF2 •3MHz

(ceramic resonator

oscillation)

•Refer to figure 3

tssXtal XT1, XT2 •32.768kHz

(crystal oscillation)

•Refer to figure 3

(Note 1) The oscillation constant is shown on table 1.

Ratings

VDD[V] min. typ. max.

4.5 to 6.0 6

unit

MHz

4.5 to 6.0 3

4.5 to 6.0 32.768 kHz

4.5 to 6.0

ms

4.5 to 6.0

4.5 to 6.0 s

No.6747-12/21

Page 13

LC86E6548

3. Electrical Characteristics at Ta=+10°C to +40°C, VSS1=VSS2=0V

Parameter Symbol Pins Conditions

current

IIH(1) Ports 0,3 at open

drain output

•Output disable

•VIN=13.5V

(including off-le akage

current of the output Tr.)

IIH(2) •Ports 1,3

•Port 0 without

pull-up MOS Tr.

•Output disable

•Pull-up MOS Tr. OFF.

•VIN=VDD

(including off-le akage

current of the output Tr.)

IIH(3) •Ports 70,71,72,73

•Port 8

•Output disable

•VIN=VDD

(including off-le akage

current of the output Tr.)

Input low

current

IIH(4)

IIH(5)

RES

Ports

74

,75

IIH(6) •S32 to S51 without

pull-down resistor

IIL(1) •Ports 1,3

•Port 0 without

pull-up MOS Tr.

VIN=VDD 4.5 to 6.0 1

VIN=VDD 4.5 to 6.0 1

•Output P-channel Tr. OFF.

•VIN=VDD

•Output disable

•Pull-up MOS Tr. OFF.

•VIN=VSS

(including off-le akage

current of the output Tr.)

IIL(2) •Ports 70,71,72,73

•Port 8

•Output disable

•VIN=VSS

(including off-le akage

current of the output Tr.)

VIN=VSS 4.5 to 6.0 -1

VIN=VSS 4.5 to 6.0 -1

IOH=-0.1mA 4.5 to 6.0 VDD-0.5

•IOH=-1.0mA

Output high

voltage

IIL(3)

IIL(4)

VOH(1) IOH=-1.0mA 4.5 to 6.0 VDD-1

VOH(2)

VOH(3) IOH=-20mA 4.5 to 6.0 VDD-1.8

RES

74

Ports

,75

Ports 0,1,3 of

CMOS output

S0/T0 to S15 / T15

VOH(4)

•The current of any

unmeasurement pin is not

over 1mA.

VOH(5) IOH=-5mA 4.5 to 6.0 VDD-1.8

VOH(6)

S16 to S51

•IOH=-1.0mA

•The current of any

unmeasurement pins is not

over 1mA.

Output low

voltage

VOL(1) IOL=10mA 4.5 to 6.0 1.5

VOL(2)

Ports 0,1,3

IOL=1.6mA 4.5 to 6.0 0.4

VOL(3) Port 70 IOL=1mA 4.5 to 6.0 0.4

VOL(4) •Ports 71,72,73

IOL=1.6mA 4.5 to 6.0 0.4

•Ports 84,85,86,87

Pull-up MOS

Rpu Ports 0,1,3 VOH=0.9VDD 4.5 to 6.0 15 40 70

Tr. resistor

Continue.

Ratings

VDD[V] min. typ. max.

4.5 to 6.0 5 Input high

unit

µ

4.5 to 6.0 1

4.5 to 6.0 1

4.5 to 6.0 1

4.5 to 6.0 -1

4.5 to 6.0 -1

4.5 to 6.0 VDD-1

4.5 to 6.0 VDD-1

kΩ

A

V

No.6747-13/21

Page 14

LC86E6548

Parameter Symbol Pins Conditions

IOFF(1) •Output P-channel

leakage current

IOFF(2)

•S0/T0 to S6/T6

•S32 to S51

(without pull-down

resistor)

Tr. OFF

•VOUT=VSS

•Output P-channel

VDD[V] min. typ. max.

4.5 to 6.0 -1 Output off-

4.5 to 6.0 -30

Tr. OFF

•VOUT=VDD-40V

Resistance of

The low level

Hold Tr.

High voltage

Pull-down

resistor

Rinpd S16 to S51 •Output P-channel

Tr. OFF

•Using as input ports

Rpd •S7/T7 to S15/T15

•S16 to S31

•Output P-channel

Tr. OFF

•VOUT=3V

4.5 to 6.0 200

•Vp=-30V

VP pull-down

resistor

Hysteresis

voltage

Pin capacitance CP All pins •f=1MHz

Rvppd Vp •VSS=GND

•Vp=-30V

VHIS •Port 1

Output disable 4.5 to 6.0 0.1VDD V

•Ports 70,71,72,73,75

RES

•

4.5 to 6.0 10 pF

•VIN=VSS for all

unmeasured terminals.

•Ta=25°C

4. Serial Input / Output Characteristics at Ta=+10°C to +40°C, VSS1=VSS2=0V

Parameter Symbol Pins Conditions

Cycle tCKCY(1) 2

Low Level

tCKL(1) 1

SCK0,S CK1 Refer t o figure 5 4.5 to 6.0

Ratings

VDD[V] min. typ. max.

pulse width

High Level

Input clock

pulse width

Cycle tCKCY(2) 2

Serial clock

Low Level

pulse width

High Level

Output clock

pulse width

Data set-up time

Data hold time

Serial input

Output delay time

(External clock

using for serial

transfer clock)

Output delay time

(Internal cloc k

Serial output

using for serial

tCKH(1)

SCK0,SCK1 •Use pull-up

tCKL(2) 1/2tCKCY

resistor (1kΩ) in

4.5 to 6.0

the open drain

tCKH(2)

output.

•Refer to figure 5

tICK 0.1

•SI0,SI1

•SB0,SB1

•Data set-up to

SCK0,1

4.5 to 6.0

•Data hold from

tCKI

SCK0,1

•Refer to figure 5

tCKO(1) 7/12

•SO0,SO1

•SB0,SB1

•Use pull-up

resistor (1kΩ) in

4.5 to 6.0

the open drain

output.

tCKO(2)

•Data hold from

SCK0,1

•Refer to figure 5

transfer clock)

Ratings

unit

µA

kΩ

5.0 60 100 200

5.0 60 100 200

unit

tCYC

1

1/2tCKCY

s

µ

0.1

tCYC

+0.2

1/3

tCYC

+0.2

No.6747-14/21

Page 15

LC86E6548

5. Pulse Input Conditions at Ta=+10°C to +40°C, VSS1=VSS2=0V

Parameter Symbol Pins Conditions

High/low level

pulse width

tPIH(1)

tPIL(1)

tPIH(2)

tPIL(2)

•INT0, INT1

•INT2/T0IN

INT3/T0IN

(The noise rejection clock

•Interrupt acceptable

•Timer0-countable

•Interrupt acceptable

•Timer0-countable

Ratings

VDD[V] min. typ. max.

4.5 to 6.0 1

4.5 to 6.0 2

unit

tCYC

selected to 1/1.)

tPIH(3)

tPIL(3)

INT3/T0IN

(The noise rejection clock

•Interrupt acceptable

•Timer0-countable

4.5 to 6.0 32

selected to 1/16.)

tPIH(4)

tPIL(4)

INT3/T0IN

(The noise rejection clock

•Interrupt acceptable

•Timer0-countable

4.5 to 6.0 128

selected to 1/64.)

tPIL(5)

RES

Reset acceptable 4.5 to 6.0 200

µs

6. AD Converter Characteristics at Ta=+10°C to + 40°C, VSS1=VSS2=0V

Parameter Symbol Pins Conditions

Ratings

VDD[V] min. typ. max.

unit

Resolution N 4.5 to 6.0 8 bit

Absolute precision

ET 4.5 to 6.0 ±1.5 LSB

(Note 2)

Conversion time tCAD

AD conversion time =

16 × tCYC

(ADCR2=0)

4.5 to 6.0

15.68

(tCYC=

0.98µs)

65.28

(tCYC=

4.08µs)

s

µ

(Note 3)

AD conversion time =

32 × tCYC

(ADCR2=1)

31.36

(tCYC=

0.98 µs)

130.56

(tCYC=

4.08µs)

(Note 3)

Analog input

VAIN 4.5 to 6.0 VSS VDD V

AN0 to AN7

voltage range

input current

IAINH VAIN=VDD 4.5 to 6.0 1 Analog port

IAINL

VAIN=VSS 4.5 to 6.0 -1

µA

(Note 2) Absolute precision excepts the quantizing error (±1/2 LSB).

(Note 3 ) The conversion time means the time from executing the AD conversion instruction to setting the complete digital

conversion value to the register.

No.6747-15/21

Page 16

LC86E6548

7. Current Dissipation Characteristics at Ta=+10°C to +40°C, VSS1=VSS2=0V

Parameter Symbol Pins Conditions

Current dissipation

during basic

operation

(Note 4)

IDDOP(1) •FmCF=6MHz

Ceramic resonator

oscillation

•FsXtal=32.768kHz

Ratings

VDD[V] min. typ. max.

4.5 to 6.0 14 33

crystal oscillation

•System clock :

CF oscillation

•Internal RC

oscillation stops

•1/1 divided

IDDOP(2) •FmCF=3MHz

4.5 to 6.0 6 18

Ceramic resonator

oscillation

•FsXtal=32.768kHz

crystal oscillation

•System clock :

CF oscillation

•Internal RC

oscillation stops

•1/2 divided

IDDOP(3) •FmCF=0Hz

4.5 to 6.0 4 13

(The oscillation

stops)

•FsXtal=32.768kHz

crystal oscillation

•System clock :

RC oscillation

•1/2 divided

IDDOP(4)

•FmCF=0Hz

4.5 to 6.0 3 10

(The oscillation

stops)

•FsXtal=32.768kHz

crystal oscillation

•System clock :

32.768kHz

•Internal RC

oscillation stops

•1/2 divided

Continue.

unit

mA

No.6747-16/21

Page 17

LC86E6548

Parameter Symbol Pins Conditions

Current dissipation

in HALT mode

(Note 4)

IDDHALT(1) •HALT mode

•FmCF=6MHz

Ceramic resonator

Ratings

VDD[V] min. typ. max.

4.5 to 6.0 5 14

oscillation

•FsXtal=32.768kHz

crystal oscillation

•System clock :

CF oscillation

•Internal RC

oscillation stops

•1/1 divided

IDDHALT(2) •HALT mode

4.5 to 6.0 2.2 7

•FmCF=3MHz

Ceramic resonator

oscillation

•FsXtal=32.768kHz

crystal oscillation

•System clock :

CF oscillation

•Internal RC

oscillation stops

•1/2 divided

IDDHALT(3) •HALT mode

4.5 to 6.0 400 1600

FmCF=0Hz

(The oscillation

stops)

•FsXtal=32.768kHz

crystal oscillation

•System clock :

RC oscillation

•1/2 divided

IDDHALT(4)

•HALT mode

4.5 to 6.0 25 100

FmCF=0Hz

(The oscillation

stops)

•FsXtal=32.768kHz

crystal oscillation

•System clock :

crystal oscillation

•Internal RC

oscillation stops

•1/2 divided

Current dissipation

in HOLD mode

IDDHOLD(1) HOLD mode

4.5 to 6.0 0.05 30

(Note 4)

(Note 4) The currents of the output transistors and the pull-up MOS transistors are ignored.

unit

mA

µA

No.6747-17/21

Page 18

LC86E6548

Table 1. Ceramic resonator oscillation recommended constant (main-clock)

Oscillation type Maker Oscillator C1 C2

6MHz ceramic resonator

oscillation

Murata

Kyocera

3MHz ceramic resonator

oscillation

Murata

Kyocera

* Both C1 and C2 must be use K rank (±10%) and SL characteristics.

Table 2. Crystal oscillation guaranteed constant (sub-clock)

Oscillation type Maker Oscillator C3 C4 Rd Rf

32.768kHz crystal

oscillation

* Both C3 and C4 must be use J rank (±5%) and CH characteristics.

(Not in need of high precision, use K rank (±10%) and SL characteristics.)

(Notes) • Please place the oscillation-related parts as close to the oscillation pins as possible with the

shortest possible pattern length since the circuit pattern affects the oscillation frequency.

• If you use other oscillators herein, we provide no guarantee for the characteristics.

CF1 CF2

XT1 XT2

CF

C2 C1

Rf

X’tal

Rd

C4 C3

Figure 1 Main-clock circuit Figure 2 Sub-clock circuit

Ceramic resonator oscillation Crystal oscillation

No.6747-18/21

Page 19

LC86E6548

I

Power supply

RES

Reset time

VDD

VDD limit

0V

resonator oscillation

Internal RC

tmsCF

CF1, CF2

tssXtal

XT1, XT2

Operation mode

Unfixed

Reset

nstruction

execution

mode

OCR6=1

Instruction execution mode

<Reset time and oscillation stable time>

HOLD release signal

Valid

resonator oscillation

Internal RC

tmsCF

CF1, CF2

tssXtal

XT1, XT2

Operation mode

HOLD

Instruction execution mode

<HOLD release signal and oscillation stable time>

Figure 3 Oscillation stable time

No.6747-19/21

Page 20

LC86E6548

VDD

RES

R

RES

(Note) Fix the value of CRES, RRES that is

sure to reset until 200µs, after Power

RES

C

supply has be en over inferior limit o f

supply voltage.

Figure 4 Reset circuit

<AC timing point>

0.5VDD

tCKCY

VDD

tCKL tCKH

SCK0

SCK1

SI0

SI1

SO0, SO1

SB0, SB1

tCKO

tICK tCKI

<Timing>

1kΩ

50pF

<Test load>

Figure 5 Serial input / output test condition

tPIL tPIH

Figure 6 Pulse input timing conditionv

No.6747-20/21

Page 21

LC86E6548

No.6747-21/21

PS

Loading...

Loading...