Page 1

■

SIGNAL PROCESSING

– PR4 signal equalization and loops

– 8th order optimized low pass filter with program-

mable cut-off frequency and boost

– single flash 6-bit ADC

– 5-TAP programmable/self-adaptive digital FIR

for signal equalization

– Programmable/self-adaptive Offset and MR

Head Asymmetry compensation for signal

equalization

– Timing and Gain loops f or optimu m da ta recov-

ery

– Encoder scheme:

– Rate 304/338 with Local ECC (16/17 without

Local ECC)

– Detector scheme:

– Media Noise TerminatorTM Detector

– Optional Local ECC Post Processing scheme

– 8-bit NRZ interface to disk controller

– Thermal Asperity detection/compensation and

Erasure Flag

■

WRITE

– 2 level Write Precomp for Non Linear Transition

Shift compensation

– Asynchronous and Synchronous Direct Write

for disk/head characterization

■

SERVO

– Digital Synchronous Servo with data rates up to

75MHz (8x Ovsersampling)

– Internal Burst and Grey Code detection

– Repeatable Run Out Support

L6363

PRML READ/WRITE CHANNEL

PRODUCT PREVIEW

TQFP100

ORDERING NUMBER: L6363

■

CHANNEL QUALITY MONITOR

– Fast read parameters optimization for minimum

BER

– Advanced Disk Surface Defect Scan

■

QUALITY AND RELIABILITY

– BIST for analog front-end and digital back-end

– Iddq and I/O pins mapping

■

POWER SUPPLY AND CONTROL

– 2.5V Analog and 1.8V Digital supply; 1.8V to

3.3V supply for I/O pins

– Advanced Power Management features

DESCRIPTION

L6363 is a 0.18µm CMOS PRML R/W channel supporting data rates up to 750Mb/sec with Servo Demodulation, Clock Synthesis, Channel Quality

Monitor for channel optimization and Disk Surface

Defect Scan capability

June 2001

This is preliminary information on a new product now in development. Details are subject to change without notice.

1/4

Page 2

L6363

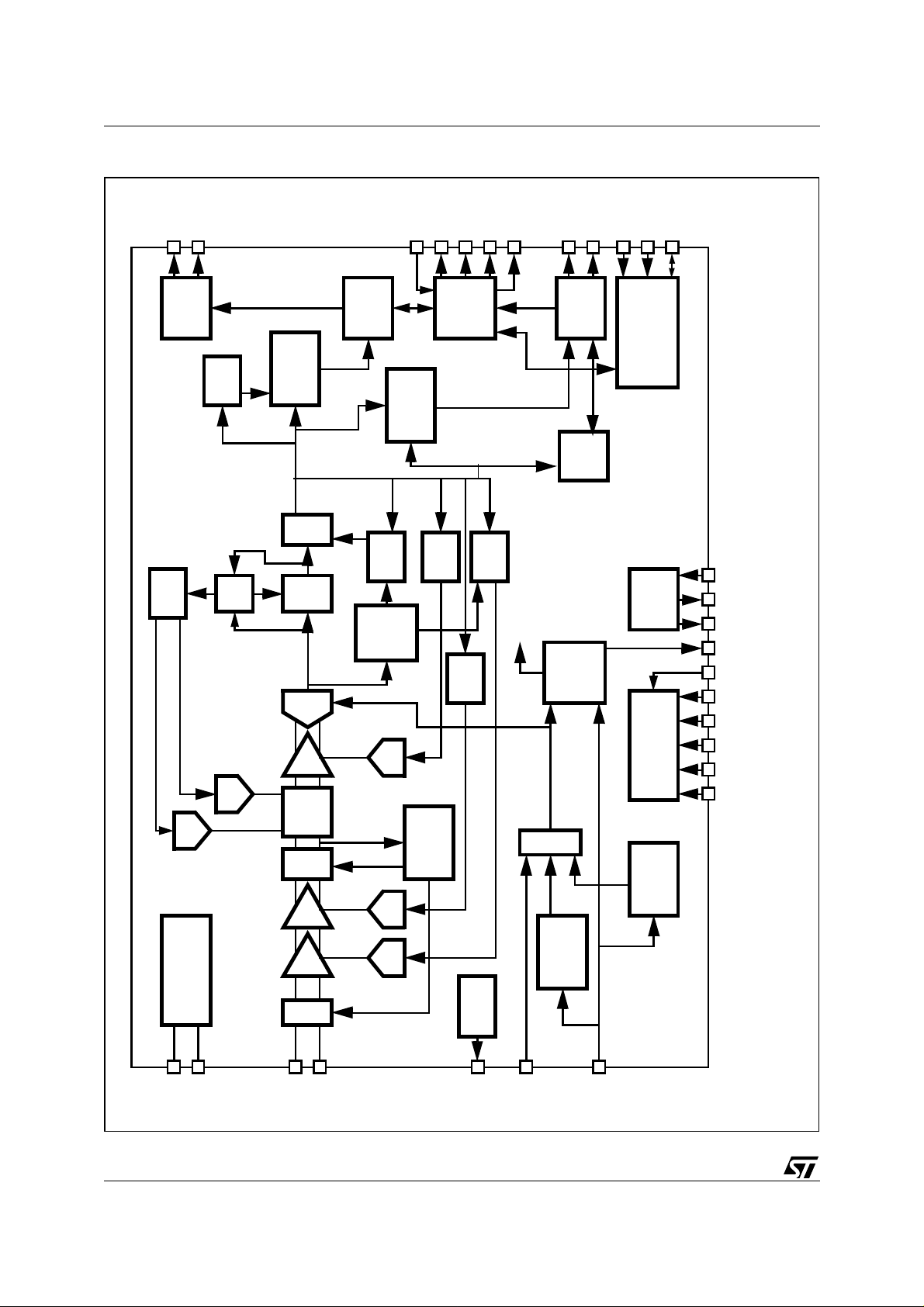

Figure 1. Block Diagram

WOP

WOM

WCLK

NRZ[7:0]

SBD*

ER_FLAG

TA_O UT

SVOCLK

SVO[1:0]

SCLK

SDEN

SDATA

Write

Precomp

Data

Low

Detector

SRC

FIR

ADC

Pass

Filter

SMD

LPFCA

BDAC

FCA

FDAC

ECC

Servo

Loop

Timing

Zero

Phase

& Gain

Restart

Encoder

Decoder

Interface

Detector

Gain

Loop

Offset

Control

Detection &

Thermal Asp.

Loop

Loop

Asymm.

Servo

Interface

Interface

Burst

Servo

Demod.

TI-[5:0]

Test

Block

Digital

Clock

Generator

Control Block

MUX

TESTBUS[7:0]

TBUSCLK

RRCLK

MODE[1 :0]

RESET*

PWD

RG

WG

SG

2/4

Data Freq.

Synthesizer

MDAC

VGA OFFMRA HPF

Analog Test Point

DIAG1

DIAG0

Zin

Ctrl

INP

INM

GDAC ODAC

Bandgap

IREF

Servo Freq.

Synthesizer

EXTCLK

REFCLK

Page 3

L6363

DIM.

mm inch

MIN. TYP. MAX. MIN. TYP. MAX.

A 1.60 0.063

A1 0.05 0.15 0.002 0.006

A2 1.35 1.40 1.45 0.053 0.055 0.057

B 0.17 0.22 0.27 0.007 0.009 0.011

C 0.09 0.20 0.003 0.008

D 16.00 0.630

D1 14.00 0.551

D3 12.00 0.472

e 0.50 0.019

E 16.00 0.630

E1 14.00 0.551

E3 12.00 0.472

L 0.45 0.60 0.75 0.018 0.024 0.030

L1 1.00 0.0393

K3.5°(min.), 7°(max.)

OUTLINE AND

MECHANICAL DATA

TQFP100

D

D1

D3

76

e

B

PIN 1

IDENTIFICATION

100

1

5175

25

50

26

TQFP100M

E3 E1 E

K

L

L1

0.076mm

.003 inch

Seating Plane

A

A2

A1

C

3/4

Page 4

L6363

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted

by implic ation or oth erwise unde r any paten t or patent ri ghts of STMi croelectroni cs. Speci fications me ntioned in this publication are s ubj ect

to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics product s are not

authorized for use as critical components in life su pport device s or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

2001 STMi croelectr oni cs - All Rights Reserved

Australi a - Brazil - China - Finland - France - Germany - Hong Ko ng - India - Italy - Ja pan - Malaysia - Mal ta - Morocco - Singapore - Spain

STMicroelectronics GROUP OF COMPANIES

- Sweden - Sw itzerland - United Kingdom - U.S.A.

http://www.s t. com

4/4

Loading...

Loading...