Datasheet KS5514B-16, KS5514B-15, KS5514B-12, KS5514B-10, KS5514B-09 Datasheet (Samsung)

...Page 1

JAN. 1998

SPECIFICATION

for KS5514B-XX

SYSTEM LSI BUSINESS

SAMSUNG ELECTRONICS CO.

Page 2

SPECIFICATION

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

for KS5514B-XX

CONTENTS

Important Notice

Copyright 1998 by SAMSUNG

The information in this publication has been carefully checked and is believed

to be accurate at the time of publication. Samsun

however, for possible errors or omissions, or for any consequences resultin

from the use of the information contained herein.

reserves the right to make changes in its products or product

Samsun

specifications with the intent to improve function or desi

without notice and is not required to update this documentation to reflect such

es.

chan

This publication does not convey to a purchaser of semiconductor devices

described herein any license under the patent ri

makes no warranty, representation, or guarantee regarding the

Samsun

suitability of its products for any particular purpose, nor does Samsun

assume any liability arising out of the application or use of any product or

circuit and specifically disclaims any liability, includin

consequence or incidental dama

*Typical* parameters can and do vary in different applications. All operatin

parameters, inc luding *Typicals,* must be validated for each customer

application by the customer*s technical experts.

products are not designed, intended, or authorized for use as

Samsun

components in systems intended for sur

applications intended to support or sustain life, or for any other application in

which the failure of the Samsun

death.

Should the buyer purchase or use a Samsun

unintended or unauthorized application, the buyer shall indemnify and hold

and its officers, employees, subsidiaries, affiliates, and distributors

Samsun

harmless a

attorney fees arisin

injury or death that may be associated with such unintended or unauthorized

use, even if such claim alle

desi

ainst all claims, costs, damages, expenses, and reasonable

out of, either directly or indirectly, any claim of personal

n or manufacture or manufacture of said product.

es.

product could cause personal injury or

es that Samsung was negligent regarding the

assumes no responsibility,

n at any time and

hts of Samsung or others.

without limitation any

ical implant into the body, for other

product for any such

FUNCTIONS -------------------------------

•

FEATURES --------------------------------

•

BLOCK DIAGRAM ----------------------

•

PIN DESCRIPTION ----------------------

•

ABSOLUTE MAXIMUM RATINGS --

•

ELECTRICAL CHARACTERISTICS -

•

OPERATION DESCRIPTION ----------

•

TEST CIRCUIT ----------------------------

•

APPLICATION CIRCUIT ---------------

•

PACKAGE DIMENSIONS --------------

•

3

3

3

4

5

6

7

13

14

16

Page 3

SPECIFICATION

KS5514B -XX ON SCREEN DISPLAY PROCESSOR

ON SCREEN DISPLAY PROCESSOR

The KS5514B is a BICMOS LSI with on screen display

function, sync. separator & expander function.

FUNCTIONS

• On screen display

• Sync separator and sync detector

• General expander

FEATURES

• Character capacity : 240 ( 24 column Ø 10 row )

• Construction of character : 12 Ø 18 dots

• 128 kinds of character

• Display position : 62 horizontal position

: 64 vertical position

• Character si ze : 4 Ø 4 times of normal

• Blinking : character unit

• Background coloring : 8 colors

• Synchronous ways : automatic selection internal

or external synchronization via MICOM control

• General output : 3 ports ( by serial data )

• Built-in sync separator & sync detector

• NTSC / PAL / SECAM mode

• Clamp circuit

BLOCK DIAGRAM

IN

OUT

XT

DVDD P3 P2 SYD AFCR FSC AVDD CVOUT SCC R CVIN

24 23 22 21 20 19 18 17 16 15 14 13

XT

24 - SDIP - 300

ORDERING INFORMATION

Device Package Operating Temprature

KS5514B-XX 24-SDIP-300 - 20 ~ + 70

OPTION CODE INFORMATION

Code No.

- 02

- 03

- 06

- 07

- 09

- 10

- 12

- 13

- 14

- 15

- 16

Remark

English

English, Russian

English

Korean

Korean , English

English, German

English, Arabic

English

Korean , English

English, Chinese

English, Russian, Arabic

Î

DET

SYNC

SEP

SYNC

DETECT

AFC

VIDEO

MIXER

CLAMP

INTERNAL

BIAS CKT

SC

DISPLAY

CONTROL

CONTROL

REGISTER

4F

BLUE BACK

GENERATOR

SHIFT

REGISTER

OSD ROM

OSD RAM

DATA

REGISTER

1 2 3 4 5 6 7 8 9 10 11

DGND SCK ACB OSCIN OSCOUT CSB SIN P1 CLAMPIN AGND LPF AFCF IL

INPUT

CONTROL

ADDR

REGISTER

DISPLAY

OSC

VSYNC

CLAMP

12

398-05-14

Page 4

SPECIFICATION

KS5514B -XX ON SCREEN DISPLAY PROCESSOR

PIN DESCRIPTION

Pin No. Symbol I/O Function

Digital Ground

1

DGND

-

2

3

4

5

6

7

8

9

SCK

ACB

OSCIN

OSCOUT

CSB

SIN

P1

CLAMPIN

I

Serial clock input. When CSB pin is `L` then serial

data is inp u tted by micom. Hyst er esis inpu t.

I

Auto clear pin. If `L`, then all circuit is reset.

Built-in pull up resistor. Hysteresis input.

I

LC oscillation pin. Standar d freq uency is 7MH z &

the horizontal start position is controlled by the

O

clock of oscillation block.

While pin 6 is low, serial data input is active.

I

Built - in pull up resistor

Serial data input pin. Built-in pull up resistor

I

General output port 1

O

Clamp input pin of composite video signal

I

10

11

12

13

14

15

16

17

18

19

AGND

LPF

AFCFIL

CVIN

SCCR

CVOUT

AVDD

FSC

AFCR

SYD

Analog ground

-

Low pass filter

-

AFC filt er o u tput

-

Composite video signal input

I

SECAM chroma input

I

Composite video output : 2 Vp-p

O

Analog VDD

-

FSC input (Not use)

I

VCO oscillation frequency control

I

When sync signal is inputted, then SYD is high.

O

498-05-14

Page 5

SPECIFICATION

KS5514B -XX ON SCREEN DISPLAY PROCESSOR

PIN DESCRIPTION

( Continued )

Pin No. Symbol I/O Function

20

21

22

23

24

XT

IN

XT

OUT

P2

P3

DVDD

ABSOLUTE MAXIMUM RATINGS

I

O

O

O

-

X-TAL

X-TAL

General output port 2

General output port 3

Digit al VD D

( Ta = 25Î )

Characteristics Symbol Value Unit

Supp ly Vo ltage

Input Voltage

Power Dissipation

Operating Temperatur e

Storage Temperature

V

DD

V

IN

Pd

Topr

Tstg

V

- 0.3 õ V

SS

- 0.3 ~ 6.0

õ

V

IN

300

- 20 ~ + 70

- 40 ~ + 125

DD

+ 0.3

V

V

mW

Î

Î

598-05-14

Page 6

SPECIFICATION

KS5514B -XX ON SCREEN DISPLAY PROCESSOR

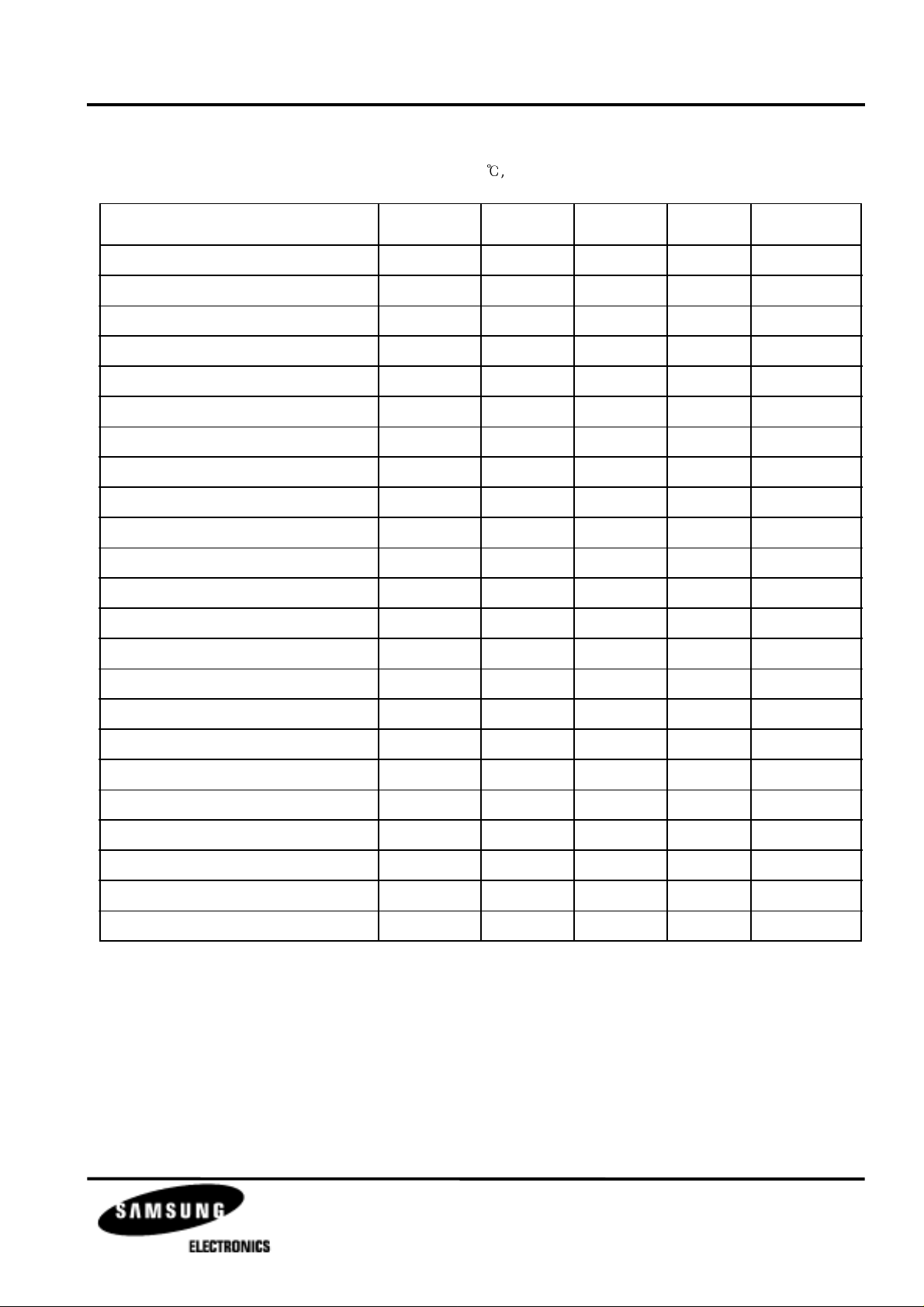

ELECTRICAL CHARACTERISTICS

Characteristics Symbol Unit

Operating Voltage

Operating Voltage

Operating Current

Pin 12 DC Voltage

Pin 13 DC Voltage

AFC Freerun Frequency

AFC Pulse Width

AFC Delay Time

AFC Lock Range H

AFC Lock Rnage L

AFC Capture Range H

AFC Capture Rrange L

DV

AV

Icc

Vpi2

Vpi3

Ffr

twd

td

Falh

Fall

Fach

Fac1

( Ta = 25Î, AV

Min Typ Max

DD

DD

3.5

4.5

10

2.3

1.3

15.5

3.7

1.0

+600

+400

-

DD

= DV

DD

= 5V )

5.0

5.0

20

2.5

1.45

15.7

4.0

2.5

-

-

-

-

5.5

5.5

25

2.7

1.6

15.9

4.3

4.0

-

-900

-

-700

V

V

mA

V

V

KHz

usec

usec

Hz

Hz

Hz

Hz

SYNC DET. Lock Range H

SYNC DET. Lock Range L

SYNC DET. Capture Range H

SYNC DET. Capture Range L

V - SYNC Delay Time

Oscillation Level

Oscillation Frequency

Blueback Sync Tip Level

Blueback Pedestal Level

Blueback Color Burst Level H

Blueb ack Co lor Level H

Flh

Fll

Fch

Fc1

tvd

Vosc

Fosc

Vbst

Vbpd

Vbbh

Vbch

143

6.7

100

14.3

10

4.0

6.3

1.85

2.5

2.75

3.1

153

7.7

107

15.3

14

4.5

7.0

2.05

2.7

2.95

3.3

163

8.7

114

16.3

-

5.0

7.7

2.25

2.9

3.15

3.5

KHz

KHz

KHz

KHz

usec

Vpp

MHz

V

V

V

V

698-05-14

Page 7

SPECIFICATION

KS5514B -XX ON SCREEN DISPLAY PROCESSOR

OPERATION DESCRIPTION

MEMORY STRUCTURE

After KS5514B records, in DATA RAM and CONTROL REGIS T ER, the serial DATA that is inputt ed from MICOM ,

in recording to the V-SYNC and H-SYNC signal, mix the COMPOSITE VIDEO signal and the font ROM data that is

mapped to data RAM.

In case that there is no composite video signal that is inputted to KS5514B, the SYNC detector becomes low,

KS5514B makes the blue back signal in dividi ng the 4fsc sign al and the blue back signal is output ted .

The following table is the data structure that is inputted from MICOM.

• Memory address consists of 16 bit

• The data of address 0 ~ 239 are character data which are display on the screen.

• The address 240 ~ 244 are the control registers.

• Don`t care bit : the upper 8 bits (DA8 ~ DAF) in address 0 ~ address 239, the upper 5bits (DAB ~ DAF) in

address 240 ~ address 244

Addr

239

240

241

242

Bit

DAF DAE DAD DAC DAB DAA DA9 DA8 DA7 DA6 DA5 DA4 DA3 DA2 DA1 DA0

0

·

·

·

* * * * * * * * BLIC6C5C4C3C2C1C0

(Font ROM Address)

·

·

·

********

*****

*****

*****

INT/

NON

BLI2 VSZ21VSZ20VSZ11VSZ10VP5 VP4 VP3 VP2 VP1 VP0

DSP3DSP2DSP1RAM

·

·

·

C6 C5 C4 C3 C2 C1 C0

BLI

HSZ21HSZ20HSZ11HSZ10HP5 HP4 HP3 HP2 HP1 HP0

TEST TC LEV1LEV0PH2 PH1 PH0

ERS

·

·

·

243

244

*****

*****

SECAM

-LEBKLE

CHA

NT/

PAL

DSPONBLK1BLK0BLI1BLI0EX YM BCO

- PD3 PD2 - PD0 PC3 PC2 PC1 PC0

798-05-14

Page 8

SPECIFICATION

KS5514B -XX ON SCREEN DISPLAY PROCESSOR

CONTROL REGISTER

1) Register 240

DA0 ~

DAA

0

1

2

3

4

5

6

7

Register

HP0

HP1

HP2

HP3

HP4

HP5

HSZ10

HSZ11

State

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Content

Function

HS is horizontal display start position

HS = Tc * ^ 4 * ê ( HPn * 2 ) + N

5

n=o

n

Tc : osc. period ( 1 / 7MHz = 143 nsec )

HSZ11

HSZ21

0

0

1

1

1st line

HSZ11

HSZ10

HSZ20

HSZ10

0

1

N

0

1

0

1

9

10

11

12

01

1X 2X

3X 4X

`

Remark

Horizontal

Start

Position

1st line char acter

size control to

horizontaldirection

8

9

HSZ20

HSZ21

0

1

0

2nd ~ 10 th

line

HSZ21

HSZ20

0

1

01

1X 2X

3X 4X

2nd ~ 10th line

character size control to ho r izontaldirectio n

1

A

INT/

NON

0

1

Interlace Mode

Non-interlace Mode

898-05-14

Page 9

SPECIFICATION

KS5514B -XX ON SCREEN DISPLAY PROCESSOR

2) Register 241

DA0 ~

DAA

0

1

2

3

4

5

6

7

Register

VP0

VP1

VP2

VP3

VP4

VP5

VSZ10

VSZ11

State

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Content

Function

VS is vertical start position

VS = H * ^ 4 * ê ( VPn * 2 ) + 3

5

n=o

H : horizontal synchronous pulse time

H-SYNC

V-SYNC

HS

VSZ11

VSZ10

0

1

01

1X 2X

3X 4X

Remark

Vertical

n

`

Start

Position

VS

1st line char acter

size control to

vertical direction

8

9

VSZ20

VSZ21

0

1

VSZ21

VSZ20

0

01

1X 2X

0

1

3X 4X

2nd ~ 10th line

character size control to vertical

directio n

1

A

BLI2

0

1

V - SYNC 64 divide ( = 1 sec )

V - SYNC 32 divide ( = 0.5 sec )

Control the blink

period

998-05-14

Page 10

SPECIFICATION

KS5514B -XX ON SCREEN DISPLAY PROCESSOR

3) Register 242

DA0 ~

DAA

0

1

2

3

4

5

Register

PH0

PH1

PH2

LEVEL0

LEVEL1

TC

State

0

1

0

1

0

1

0

1

0

1

0

1

P2

P1 P0 NTSC PAL

0

0

0

0

0

1

0

1

1

0

1

0

1

1

level 1

0

1

1H = 454Tc

1H = 455Tc

0

1

0

1

0

1

0

111

level 0

Content

Function

E

E

/4

E

/2

7E/4

0

E

3E/4

3E/2

5E/4

01

Internal bias 1 Internal bias 2

-

Tc = 2 / fosc

/4

E

/2

-E/4

0

²

E

3E/4

3E/2

5 E/4

Internal bias 3

Remark

Back ground

color control

bit

Color level

control

6

7

8

9

A

TEST

RAM

ERS

DSP1

DSP2

DSP3

0

1

0

1

0

1

0

1

0

1

Active mode

Test mode

RAM no erase

RAM erase

Display method of the 1st is fixed by BLK0 & BLK1

Display method of the 1st is variable

Display method of 2nd - 9th is fixed by BLK0 & BLK1

Display method of 2nd - 9th is variable

Display method of 10th is fixed by BLK0 & BLK1

Display method of 10th is variable

1098-05-14

Page 11

SPECIFICATION

KS5514B -XX ON SCREEN DISPLAY PROCESSOR

4) Register 243

DA0 ~

DAA

0

1

2

3

4

5

6

Register

BCO

YM

EX

BLI0

BLI1

BLK0

BLK1

State

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Content

Function

Blank in g ar ea co loring

Full TV screen colorin g

The same luminance level character and back ground

Variable background luminance level available

Extern al mo de availabl e

Internal mode available

Blinking mode

control

Blanking mode

control

BLI1

BLK1

BLI0

0

1

BLK0

0

1

01

OFF

DUTY 50%

DUTY 25%

DUTY 75%

01

OFF

O

C

R

Remark

Deter mined by

BLK0 & BLK1

Determined by

BCO,

BLK0 & BLK1

Blinking duty

control

C : charact er

O : outline

R : raster

7

DSP

ON

8

LECHA

0

1

0

1

9

LEBLK

0

1

A

-

0

1

Display off

Display on

Charact er luminance le v el 1

Charact er luminance le v el 2

Blank lum inance level 1

Blank lum inance level 2

-

-

1198-05-14

Page 12

SPECIFICATION

KS5514B -XX ON SCREEN DISPLAY PROCESSOR

5) Register 244

DA0 ~

DAA

0

1

2

3

4

5

6

Register

PC0

PC1

PC2

PC3

PD0

-

PD2

State

0

1

0

1

0

1

0

1

0

1

0

1

0

1

PC1

PC3

L output

H output

-

L output

H output

Content

Remark

Function

PC0

0

1

0

1

Hsync+Vsync output

Port(PD0) output

PC2

Hsync(pin22) &

Vsync(pin23) output

Port(PD2/PD3)

output

01

-

Character1 output

01

Test mo d e

Character2, BLK2

output

Pin 8 output

mode setting

Pin 22/23

output mode

setting

Pin 8 output

data setting

Pin 22 output

data setting

7

8

9

A

PD3

-

NT/

PAL

SECAM

0

1

0

1

0

1

0

1

L output

H output

-

NTSC mode

PAL mode

NTSC or PAL mode

SECAM mode

Pin 23 output

data setting

1298-05-14

Page 13

SPECIFICATION

KS5514B -XX ON SCREEN DISPLAY PROCESSOR

TEST CIRCUIT

VSYNC

DV

HSYNC

IN/OUT

DD

IN/OUT

0.82K0.82K

XT

OUT

24 23 22 21 20 19 18 17 16 15 14 13

XT

IN

SYD FSC AV

AFCR

12K

100K

CV

IN

1

Ó

+

DD

CV

OUT

CLAMP

OSD ROM

OSD RAM

4 FSC

VSYNC

DET

SYNC

DETECT

AFC

BLUE BACK

GENERATOR

DATA

REGISTER

INPUT

CONTROL

ADDR

REGISTER

DISPLAY

CONTROL

CONTROL

REGISTER

DISPLAY

OSC

SHIFT

REGISTER

SYNC

SEP

VIDEO

MIXER

CLAMP

INTERNAL

BIAS CKT

1 2 3 4 5 6 7 8 9 10 11 12

10uH

B

SW1

A

D

GND

SCK ACB OSC

IN

56p68p

OSC

CSB SIN P1 CLAMPINA

OUT

0.82K

4.7

Ó

200K

+

GND

100p

104

LPF AFCFIL

1K

+

0.47

Ó

1398-05-14

Page 14

SPECIFICATION

KS5514B -XX ON SCREEN DISPLAY PROCESSOR

APPLICATION CIRCUIT (APP-082)

R177

R100

100

C153

220

L104

5V

Q116

KA78T05

9V

R176

430

100uH

L105

XT

OUT

XT

IN

AFCR

100uH

1N4148

CR104

CR105

DD

DV

C139 C140

Y101

P3 P2

C152

203

SYD

24 23 22 21 20 19 18 17 16 15 14 13

R175

12K

FSC

C143

104

C144

+

100

CVOUT

Ó

75

Ó

+

Q116

A733

SECAM

VIDEO IN

VIDEO OUT

Vin : 2Vpp

Vsync : > 0. 3V pp

C138

1

Ó

R172

100K

+

CV

IN

CLAMP

OSD ROM

OSD RAM

4 FSC

VSYNC

DET

SYNC

DETECT

AFC

BLUE BACK

GENERATOR

DATA

REGISTER

INPUT

CONTROL

ADDR

REGISTER

DISPLAY

CONTROL

CONTROL

REGISTER

DISPLAY

OSC

SHIFT

REGISTER

SYNC

SEP

VIDEO

MIXER

CLAMP

INTERNAL

BIAS CKT

1 2 3 4 5 6 7 8 9 10 11 12

IN

L106

10uH

OSC

C141

82p

CSB SIN P1

OUT

Ó

4.7

CLAMPIN

R173C137

+

200K

C148

100p

A

GND

C149

122

LPF AFCFIL

C147

+

1

Ó

C142

68p

D

SCK ACB OS C

GND

DC 2.5V

R174

+

1K

C150

0.33

Ó

D

GND

A

GND

The circuit drawn above is for Demo Board.

• Y101 (4fsc X-TAL ) â NTSC : 14.31818MHz

PAL : 17.734475MHz

• C139 / C140 : The load CAP of X-TAL Y101 has a difference each according to its manufacturer.

1498-05-14

Page 15

SPECIFICATION

KS5514B -XX ON SCREEN DISPLAY PROCESSOR

APPLICATION CIRCUIT (APP-306)

* Control Program : osd-3.exe

L105

100uH

R100

100

1N4148

CR104

CR105

P3

DD

DV

24 23 22 21 20 19 18 17 16 15 14 13

P2

L104

100uH

XT

OUT

5V

XT

Q116

KA7805

AFCR

FSC

9V

R176

430

C152

203

SYD

IN

R175

12K

C153

220

C144

+

100

CVOUT

Ó

R177

75

Ó

+

VIDEO OUT

Q115

A733

Vin : 2Vpp

Vsync : > 0. 3V pp

C138

Ó

1

+

CV

IN

SECAM

VIDEO IN

R172

100K

R101

1K

CLAMP

OSD ROM

OSD RAM

4 FSC

VSYNC

DET

SYNC

DETECT

AFC

BLUE BACK

GENERATOR

DATA

REGISTER

INPUT

CONTROL

ADDR

REGISTER

DISPLAY

CONTROL

CONTROL

REGISTER

DISPLAY

OSC

SHIFT

REGISTER

SYNC

SEP

VIDEO

MIXER

CLAMP

INTERNAL

BIAS CKT

1 2 3 4 5 6 7 8 9 10 11 12

C147

+

Ó

1

C142

68p

D

GND

SCK ACB OS C

KSR1001

C154

15pF

Y103

17.734475MHz

L106

10uH

IN

Y102

14.31818MHz

OSC

C141

82p

CSB SIN

OUT

Ó

4.7

P1

CLAMPIN

To Pin 20 ( XT IN )

To Pin 21 ( XT OUT )

R173C137

+

200K

C148

100p

A

GND

C149

122

LPF AFCFL

DC 2.5V

R174

+

1K

C150

Ó

0.33

KSR2001

C155

47pF

The circuit drawn above is for Demo Board.

• Y102 (4fsc X-TAL ) â NTSC : 14.31818MHz

Y103 (4fsc X-TAL ) â PAL : 17.734475MHz

C157

47pF

D

GND

A

GND

1598-05-14

Page 16

SPECIFICATION

KS5514B -XX ON SCREEN DISPLAY PROCESSOR

PACKAGE DIMENSIONS

24-SDIP-300 Dimensions in Milime ters/ Inches

1698-05-14

Page 17

SPECIFICATI ON

MEMO

HEAD OFFICE :

8/11FL., SAMSUNG MAIN BLDG.

250, 2 - KA. TAEPYUNG - RO,

CHUNG - KU, SEOUL, KOREA

TEL ........ 2 - 727 - 7114

FAX ........ 2 - 753 - 0967

SEMICONDUCTOR BUSINESS

SALES & MARKETING DIVISION :

15/16 FL., SEVERANCE BLDG., 84 - 11,

5 - KA, NAMDAEMOON - RO, CHUNG - KU

SEOUL, KOREA

TEL ...... 2 - 259 - 1114

FAX ...... 2 - 259 - 2468

SAMSUNG SEMICONDUCTOR INC.

3655 NORTH FIRST STREET,

SAN JOSE, CA 95134, U.S.A

TEL ..... 408 - 954 - 7000

FAX ..... 408 - 954 - 7873

SAMSUNG SEMICONDUCTOR EUROPE GMBH

SAMSUNG HOUSE,

AM KRONBERGER HANG 6,

65824 SCHWALBACH/TS

TEL ..... 49 - 6196 - 663300

FAX ..... 49 - 6196 - 663311

SAMSUNG SEMICONDUCTOR EUROPE LTD.

GREAT WEST HOUSE

GREAT WEST ROAD, BRENTFORD,

MIDDLESEX TW8 9DQ

TEL ..... 181 - 380 - 7132

FAX ..... 181 - 380 - 7220

SAMSUNG ELECT RO NI CS CO. , LTD.

SEMICONDUCTOR BUSINESS BEIJING OFFICE

15FL., BRIGHT CHINA CHANG AN BLDG.,

NO.7, JIANGUOMEN, NEI AVENUE,

BEIJING, CHINA 100005

TEL ..... 8610 - 6510 - 1234(0)

FAX ..... 8610 - 6510 - 1545

SAMSUNG ELECTRONICS JAPAN CO., LTD.

HAMACHO CENTER BLDG.,

31 - 1, NIHONBASHI - HAMACHO, 2 - CHOME,

CHUO - KU, TOKYO 103, JAPAN

TEL ..... 3 - 5641 - 9850

FAX ..... 3 - 5641 - 9851

SAMSUNG ELECTRONICS HONGKONG CO., LTD.

65TH FL., CENTRAL PLAZA,

18 HARBOUR ROAD,

WANCHAI, HONG KONG

TEL ....... 852 - 2862 - 6900

FAX ....... 852 - 2866 - 1343

SAMSUNG ELECTRONICS TAIWAN CO., LTD.

30FL., NO.333, KEELUNG RD.,

SEC1, TAIPEI, TAIWAN, R.O.C

TEL ..... 886 - 2 - 757 - 7292

FAX ..... 886 - 2 - 757-7311

SAMSUNG ASIA PRIVATE LIMITED

80. ROBINSON ROAD, #20 - 01

SINGAPORE 068898

TEL ..... 65 - 535 - 2808

FAX ..... 65 - 227 - 2792

SAMSUNG ELECT RO NI CS CO. , LTD.

SHANGHAI OFFICE

9F, SHANGHAI INTERNATIONAL TRADE CENTRE,

NO.2200 YANAN(W) RD.,

SHANGHAI, CHINA 200335

TEL ..... 8621 - 6270 - 4168

FAX ..... 8621 - 6275 - 2975

JAN. 1998

Loading...

Loading...