Datasheet ILC707M, ILC706N, ILC705N, ILC705M, ILC708M Datasheet (Impala Linear Corporation)

...Page 1

The ILC705/ILC706/ILC707/ILC708 are low cost microprocessor supervisory circuits that monitor power supplies in microprocessor based systems. Circuit functions

include a watchdog timer, microprocessor reset, power

failure warning and a debounced manual reset input.

The ILC705 and ILC706 offer a watchdog timer function

while the ILC707 and ILC708 have an active high reset

output in addition to the active low reset output.

Supply voltage monitor levels of 4.65V and 4.4V are

available. The ILC705/ILC707 have a nominal reset

threshold level of 4.65V while the ILC706 and ILC708

have a 4.4V nominal reset threshold level. When the supply voltage drops below the respective reset threshold

level, RESET is asserted.

ILC705/706/707/708

mP Supervisory Circuit

Impala Linear Cor poration

Impala Linear Corporation

1

(408) 574-3939

www.impalalinear.com

Sept 1999

ILC705-708 1.0

! 4.4V or 4.65V Precision Voltage Monitor

! 200ms Reset Pulse Width

! Debounced TTL/CMOS Compatible Manual Reset Input

! Watchdog Timer with 1.6 sec Timeout (ILC705/ILC706)

! Voltage Monitor for Early Power Fail Warning or Low

Battery Detect

! 8-Pin SOIC or DIP Package

! Computers

! Controllers

! Critical Microprocessor Power Monitoring

! Intelligent Instruments

! Portable Equipment

! Controllers

ILC705

ILC706

ILC707

ILC708

Top View

MR

PFO

VCC

2

1 8

6 WDI

PFI

RESET

GND

4

3

5

7

N Package - 8 Lead Plastic DIP Package

M Package - 8 Lead Plastic SOIC Package

2

1 8

6

4

3

5

7

WDO

MR

PFO

VCC

NC

PFI

RESET

GND

RESET

Part Package Temp. Range

ILC70_N 8-Lead PDIP -40°C to +85°C

ILC70_M 8-Lead SOIC -40°C to +85°C

ILC705

ILC706

µµ

P

VCC

+5 V (Regulated)

VCC

WDI

NMI

WDO

GNDPFI

I/O Line

MR

RESET RESET

Manual

Reset

DC Voltage

(Unregulated)

InterruptPFO

Typical Circuit

Pin Package Configuration

General Description

Features

Applications

Ordering Information

Page 2

mP Supervisory Circuit

Impala Linear Corporation

2

(408) 574-3939

www.impalalinear.com

Sept 1999

ILC705-708 1.0

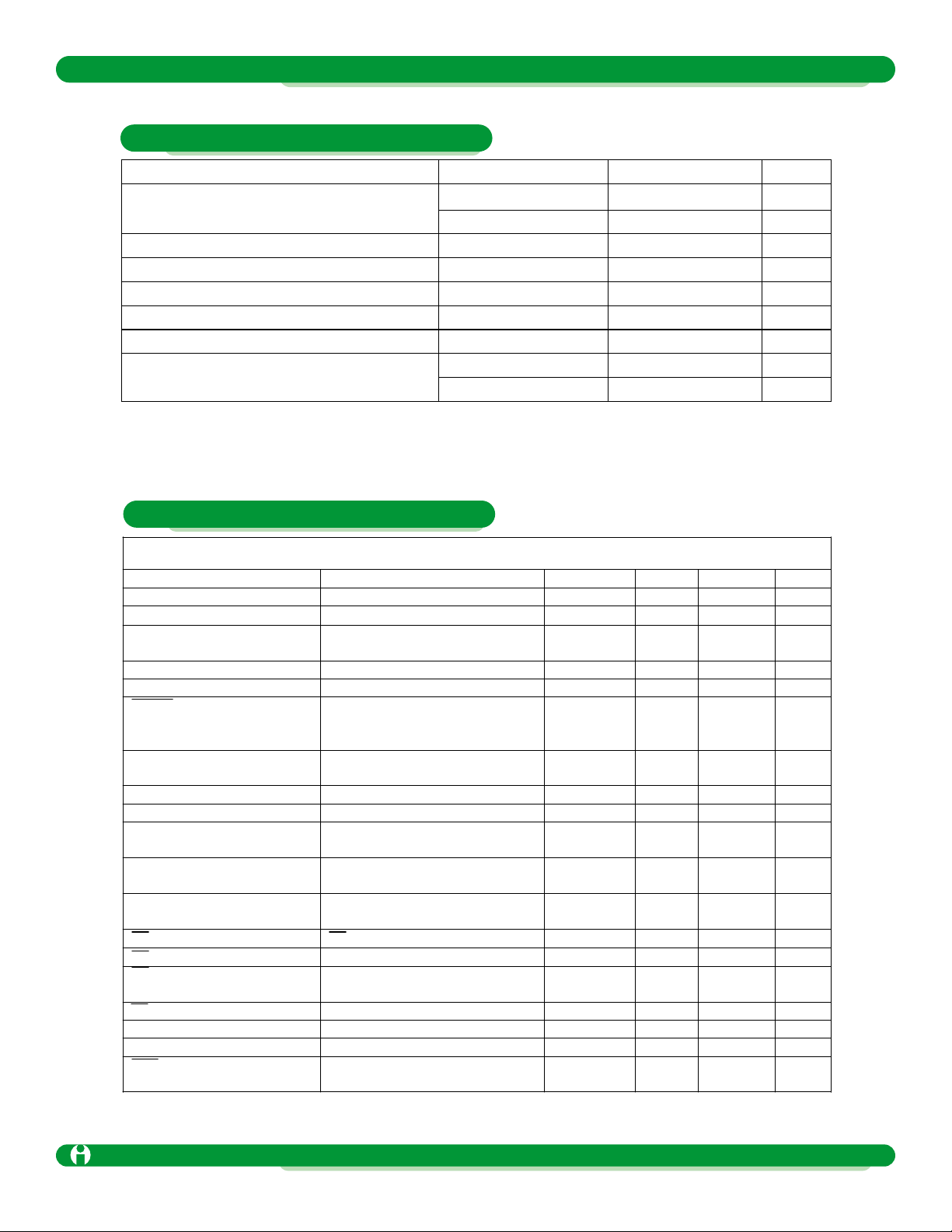

Parameter Symbol Ratings Units

V

CC

-0.3 to 6.0 VTerminal Volta ge

All other inputs

-0.3 to (VCC + 0.3)

V

Input Current V

CC,

GND 25 mA

Output Current All outputs 20 mA

Operating Temperature Range T

A

-40 to +85 °C

Storage Temperature Range -65 to +150 °C

Lead Temperature (Soldering, 10 sec.) 300 °C

PDIP 475 mWPower Dissipation

SOIC 400 mW

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality

at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device

reliability. Operating ranges define those limits between which the functionality of the device is guaranteed.

VCC = 4.75 V to 5.5 V for ILC705/I LC707, VCC = 4.5 V to 5.5 V for ILC706/I LC708, TA = Operating Temperature Range, unless

otherwise noted.

Parameter

Conditions

Min

Typ

Max

Units

Operating Voltage Range, VCC

ILC70__

1.4 5.5

V

Supply Current, ICC

ILC70__

60

µA

Reset Voltage Threshold

ILC705, ILC707

ILC706, ILC708

4.5

4.25

4.65

4.4

4.75

4.5

V

Reset Threshold Hysteresis

40 mV

Reset Pulse Width, tRS

140

200

280

ms

RESET Output Voltage

I

SOURCE

= 800 µA

I

SINK

= 3.2 mA

I

SINK

= 50 µA, VCC = 1.4V

VCC – 1.5V

0.4

0.3

V

RESET Output Voltage

I

SOURCE

= 800 µA

I

SINK

= 1.2 mA

VCC – 1.5V

0.4

V

Watchdog Timeout Period, tWD

1.0

1.6

2.25

sec

WDI Minimum Input Pulse, tWP

VIL = 0.4V, VIH = 80% of VCC

50

ns

WDI Threshold Voltage

VIH, VCC = 5V

VIL, VCC = 5V

3.5

0.8

V

WDI Input Current

WDI = 0V

WDI = VCC

-150

-50

50 150

µA

WDO Output Voltage

I

SOURCE

800 µA

I

SINK

= 1.2 mA

VCC – 1.5V

0.4

V

MR Pull-Up Current

MR = 0V

100

250

600

µA

MR Pulse Width, tMR

150

ns

MR Input Threshold

VIL

VIH 2.0

0.8

V

MR to Reset Output Delay, tMD

250

ns

PFI Input Threshold

VCC = 5V

1.2

1.25

1.3

V

PFI Input Current

-25

0.01

25

nA

PFO Output Voltage

I

SINK

= 3.2mA

VCC = 5V, I

SOURCE

= 800 µA

VCC - 1.5V

0.4

V

Absolute Maximum Ratings

Electrical Characterisitcs

Page 3

mP Supervisory Circuit

Impala Linear Corporation

3

(408) 574-3939

www.impalalinear.com

Sept 1999

ILC705-708 1.0

Pin Number

Pin

Name

ILC705

ILC706

ILC707

ILC708

Description

MR

1

1

Manual reset input. MR forces RESET to assert when pulled below 0.8V.

An internal pull-up current of 250 mA on this input forces it high when

left floating. This input can also be driven from TTL or CMOS logic.

Vcc

2

2

Power supply input, 5V.

GND

3

3

Ground pin, 0 V reference.

PFI

4

4

Power fail input. Internally connected to the power fail comparator, which

is referenced to 1.25V. The power fail output (PFO) remains high if PFI

is above 1.25V. PFI should be connected to GND or V

OUT

if the power

fail comparator is not used.

PFO

5

5

Power fail output. The power fail comparator is independent of all other

functions on this device.

WDI

6

N/A

Watchdog input. The WDI input monitors microprocessor activity, an

internal watchdog timer resets itself with each transition on the watchdog

input. If the WDI pin is held high or low for longer than the watchdog

timeout period, WDO is forced to active low. The watchdog function can

be disabled by floating the WDI pin.

N/C

N/A

6

No Connect.

RESET

7

7

RESET output. RESET is asserted if either VCC goes below the reset

threshold or by a low signal on the manual reset input (MR). RESET

remains asserted for one reset timeout period (200ms) after V

CC

exceeds the reset threshold or after the manual reset pin transitions from

low to high. The watchdog timer will not assert RESET unless WDO is

connected to MR.

WDO

8

N/A

Watchdog timer output. The watchdog timer resets itself with each

transition on the watchdog input. If the WDI pin is held high or low for

longer than the watchdog timeout period, WDO is forced low. WDO will

also be forced low if V

CC

is below the reset threshold and will remain low

until V

CC

returns to a valid level.

RESET

N/A

8

RESET output. RESET is the compliment of RESET and is asserted if

either V

CC

goes below the reset threshold or by a low signal on the

manual reset input (MR). RESET is suitable for microprocessors

systems that use an active high reset.

Pin Functions

Page 4

mP Supervisory Circuit

Impala Linear Corporation

4

(408) 574-3939

www.impalalinear.com

Sept 1999

ILC705-708 1.0

WDO

tMD

VRT

tRS

VCC

RESET

MR

tRS

tMR

Microprocessor Reset

The RESET pin is asserted whenever VCCfalls below the

reset threshold voltage or when MR goes low. The reset pin

remains asserted for a period of 200ms after V

CC

has risen

above the reset threshold voltage and MR goes high. The

reset function ensures the microprocessor is properly reset

and powers up into a known condition after a power failure.

RESET will remain valid with V

CC

as low as 1.4V

Watchdog Timer

The microprocessor can be monitored by connecting the

WDI pin (watchdog input) to a bus line or I/O line. If a transition does not occur on the WDI pin within the watchdog

timeout period, then WDO will go low. A minimum pulse of

50ns or any transition low-to-high or high-to-low on the WDI

pin will reset the watchdog timer. The output of the watchdog timer (WDO) will remain high if WDI sees a valid transition within the watchdog timeout period or if WDI is left

floating. If V

CC

falls below the reset threshold voltage then

WDO goes low immediately regardless of WDI. If WDI is left

floating, then WDO can be used as a low line indicator.

Manual Reset

The manual-reset input (MR) allows reset to be triggered by

a pushbutton switch which is debounced by the 140ms minimum reset pulse width. MR can be driven by external

TTL/CMOS compatible logic. By connecting WDO to MR a

watchdog timeout will generate a reset pulse in the

ILC705/ILC706.

Power Fail Warning

An additional comparator which is independent of other

functions on the ILC705/706/707/708 is provided for early

warning of power failure. An external voltage divider can be

used to compare unregulated DC to an internal 1.25V reference. The voltage divider ratio on the input of the power

fail comparator (PFI) can be chosen so as to trip the power

fail comparator a few milliseconds before VCCfalls below

the maximum reset threshold voltage. The output of the

power fail comparator (PFO) can be used to interrupt the

microprocessor when used in this mode and execute shutdown procedures prior to power loss

5

PFO

4

PFI

-

+

1.25 V

R1

R2

Unregulated DC

Industry P/N ILC Direct

Replacement

MAX705CPA ILC705N

MAX705CSA ILC705M

MAX705EPA ILC705N

MAX705ESA ILC705M

ADM705AN ILC705N

DS1705 ILC705

MAX706CPA ILC706N

MAX706CSA ILC706M

MAX706EPA ILC706N

MAX706C/D ILC706D

ADM706AN ILC706N

DS1706 ILC706

MAX707CPA ILC707N

MAX707CSA ILC707M

MAX707EPA ILC707N

MAX707ESA ILC707M

MAX707C/D ILC707D

ADM707AN ILC707N

DS1707 ILC707

MAX708CPA ILC708N

MAX708CSA ILC708M

MAX708EPA ILC708N

MAX708ESA ILC708M

MAX708C/D ILC708D

ADM708AN ILC708N

DS1708 ILC708

Circuit Description

Alternate Reference Guide

Page 5

mP Supervisory Circuit

Impala Linear Corporation

5

(408) 574-3939

www.impalalinear.com

Sept 1999

ILC705-708 1.0

Pin 1 identifier

0.197

0.190

0.155

0.150

0.244

0.228

0.069

0.053

0.011

0.004

0.060

0.040

0.019

0.013

0.050

0.016

0.012

0.009

0.8°

0.260

0.240

0.019

0.013

0.260

0.240

0.260

0.240

0.260

0.240

0.260

0.240

0.260

0.240

0.260

0.240

0.260

0.240

M Package, 8-Pin Small Outline

N Package, 8-Pin Plastic Dual In-line

Devices sold by Impala Linear Corporation are covered by the warranty and patent indemnification provisions appearing

in its Terms of Sale only. Impala Linear Corporation makes no warranty, express, statutory, implied, or by description

regarding the information set forth herein or regarding the freedom of the described devices from patent infringement.

Impala Linear Corporation makes no warranty of merchantability or fitness for any purpose. Impala Linear Corporation

reserves the right to discontinue production and change specifications and prices at any time and without notice.

This product is intended for use in normal commercial applications. Applications requiring an extended temperature

range, unusual environmental requirements, or high reliability applications, such as military and aerospace, are specifically not recommended without additional processing by Impala Linear Corporation.

Impala Linear Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an

Impala Linear Corporation product. No other circuits, patents, licenses are implied.

Life Support Policy

Impala Linear Corporation’s products are not authorized for use as critical components in life support devices or systems.

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or

(b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labelling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonbly expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Packaging Information

Loading...

Loading...