Page 1

Integrated

Circuit

Systems, Inc.

L VPECL F

ICS8431-11

255MHZ, LOW JITTER,

REQUENCY SYNTHESIZER

GENERAL DESCRIPTION

,&6

HiPerClockS™

510MHz providing an output frequency range of 95MHz to

255MHz. The output frequency can be programmed using the

parallel interface, M0 thru M8, to the configuration logic.

Spread spectrum clocking is programmed via the control

inputs SSC_CTL0 and SSC_CTL1.

Programmable features of the ICS8431-11 support four

operational modes. The four modes are spread spectrum

clocking (SSC), non-spread spectrum clock and two test

modes which are controlled by the SSC_CTL[1:0] pins. Unlike other synthesizers, the ICS8431-11 can immediately

change spread-spectrum operation without having to reset

the device.

In SSC mode, the output clock is modulated in order to

achieve a reduction in EMI. In one of the PLL bypass test

modes, the PLL is disconnected as the source to the

differential output allowing an external source to be

connnected to the TEST_I/O pin. This is useful for incircuit testing and allows the differential output to be driven

at a lower frequency throughout the system clock tree. In the

other PLL bypass mode, the oscillator divider is used as the

source to both the M and the Fout divide by 2. This is useful

for characterizing the oscillator and internal dividers.

The ICS8431-11 is a general purpose clock

frequency synthesizer for IA64/32 application and

a member of the HiPerClockS™ family of High

Performance Clock Solutions from ICS. The VCO

operates at a frequency range of 190MHz to

FEATURES

• Fully integrated PLL

• Differential 3.3V LVPECL output

• Programmable PLL loop divider for generating a variety of

output frequencies.

• Crystal oscillator interface

• Spread Spectrum Clocking (SSC) fixed at 1/2% modulation

for environments requiring ultra low EMI

• Typical RMS cycle-to-cycle jitter 2.6 ps

• LVTTL / L VCMOS control inputs

• PLL bypass modes supporting in-circuit testing and on-chip

functional block characterization

• 3.3V supply voltage

• 28 lead SOIC

• 0°C to 85°C ambient operating temperature

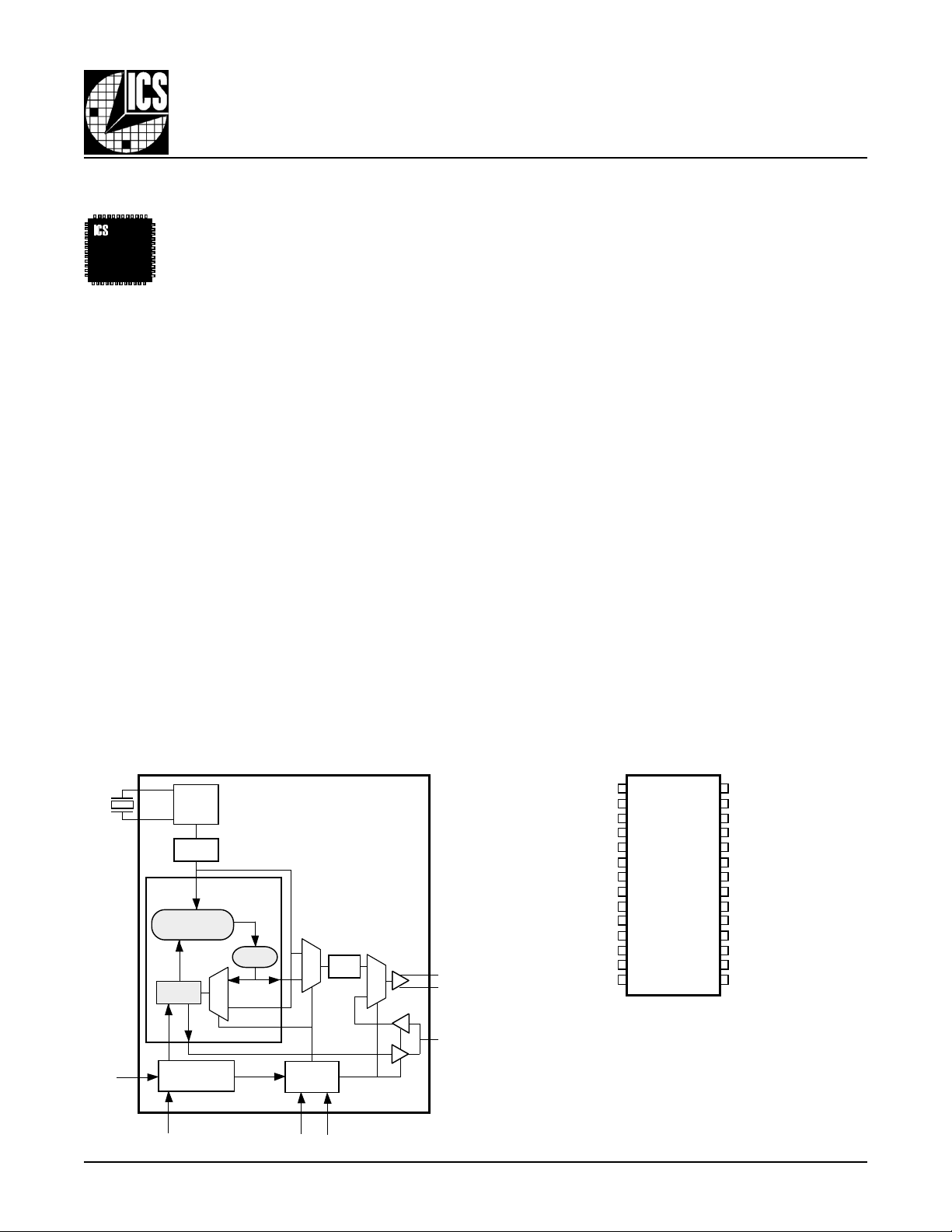

BLOCK DIAGRAM PIN ASSIGNMENT

nP_LOAD

1

XTAL1

XTAL2

OSC

÷ 16

PHASE

DETECTOR

÷ M

PLL

VCO

÷ 2

FOUT

nFOUT

M0

M1

M2

M3

M4

M5

M6

M7

M8

SSC_CTL0

SSC_CTL1

VEE

TEST_I/O

VDD

2

3

4

5

6

7

8

9

10

11

12

13

14

ICS8431-11

TEST_I/O

M0:M8

ICS8431CM-11 www.icst.com/products/hiperclocks.html REV. A JULY 11, 2001

Configuration

Logic

nP_LOAD

SSC_CTL0

SSC

Control

Logic

SSC_CTL1

1

28-Lead SOIC

M Package

Top View

28

27

26

25

24

23

22

21

20

19

18

17

16

15

VDDI

XTAL2

XTAL1

nc

nc

VDDA

VEE

MR

nc

VDDO

FOUT

nFOUT

VEE

Page 2

Integrated

Circuit

Systems, Inc.

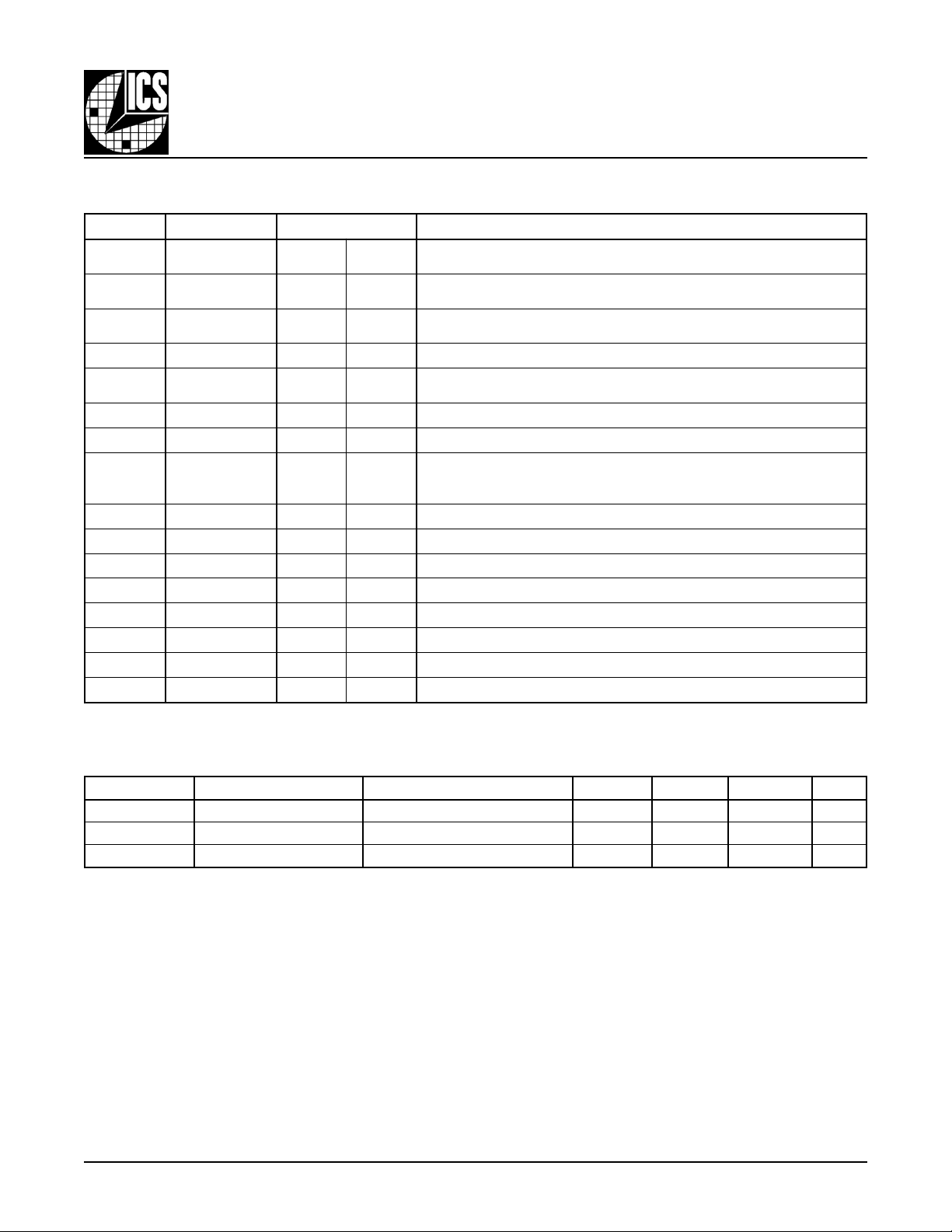

TABLE 1. PIN DESCRIPTIONS

rebmuNemaNepyTnoitpircseD

5-16M-0MtupnInwodlluP

8-68M-7MtupnIpulluP

11,01

21EEVrewoP.tuptuotsetdnaerocrofnipdnuorG

31O/ITSET

41DDVrewoP.tuptuotsetdnaerocrofnipylppusrewoP

51EEVrewoP.tuptuorofnipdnuorG

71,61TUOF,TUOFntuptuO

81ODDVrewoP.tuptuorofnipylppusrewoP

42,32,91cndesunU.noitcennocoN

02RMtupnInwodlluP.wolTUOFsecroF.retnuocMteseR

12EEVrewoP.nipdnuorG

22ADDVrewoP.nipylppusrewopLLP

62,522LATX,1LATXtupnI.tupnirotallicsolatsyrC

72IDDVrewoP.erocrofnipylppusrewoP

82DAOL_PntupnInwodlluP.slevelecafretniSOMCVL/LTTVL.tupnielbanehctalredividM

,0LTCCSS

1LTCCSS

tupnIpulluP.slevelecafretniSOMCVL/LTTVL.sniplortnocCCS

/tupnI

tuptuO

ICS8431-11

255MHZ, LOW JITTER,

L VPECL F

.cigol

REQUENCY SYNTHESIZER

fonoitsisnartHGIH-ot-WOLnodehctalataD.stupniredividM

.slevelecafretnisnipLTTVL/SOMCVL.tupniDAOL_Pn

fonoitsisnartHGIH-ot-WOLnodehctalataD.stupniredividM

.slevelecafretnisnipLTTVL/SOMCVL.tupniDAOL_Pn

.edomssapybLLPnitupnisademmargorP

.rezisehtnysehtrofsrevirdtuptuoniamerastuptuolaitnereffidesehT

LCEPVLdecnereferevitisopdetanimrethtiwelbitapmocerayehT

TABLE 2. PIN CHARACTERISTICS

lobmySretemaraPsnoitidnoCtseTmuminiMlacipyTmumixaMstinU

NICecnaticapaCniPtupnI 4Fp

PULLUPRrotsiseRpulluPtupnI 15KΩ

NWODLLUPRrotsiseRnwodlluPtupnI 15KΩ

ICS8431CM-11 www.icst.com/products/hiperclocks.html REV. A JULY 11, 2001

2

Page 3

Integrated

Circuit

Systems, Inc.

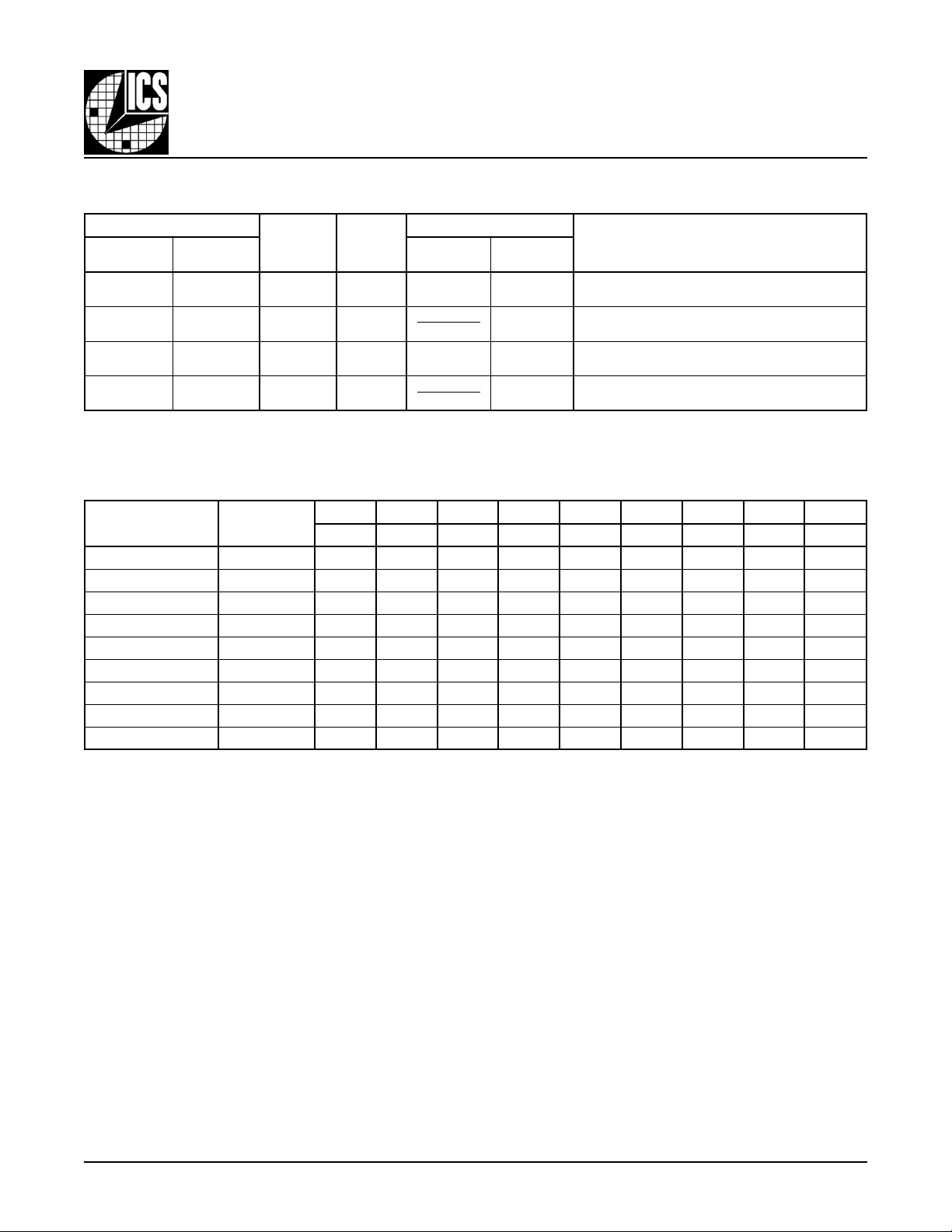

TABLE 3A. SSC CONTROL INPUT FUNCTION TABLE

L VPECL F

ICS8431-11

255MHZ, LOW JITTER,

REQUENCY SYNTHESIZER

stupnI

1LTC_CSS0LTC_CSS

00 lanretnIdelbasiDLATXf ÷ 23

01LLPdelbanE

10 lanretxEdelbasiDklCtseTtupnI

11LLPdelbasiD

O/I_TSET

ecruoS

CSS

23

23

.noitaziretcarahcdnagubedesuohnirofdesU:1ETON

stuptuO

,TUOF

TUOFn

LATXf ÷ 61

÷ M

MxLATXf

MxLATXf

Z-iHtnecreP½=rotcaFnoitaludoM;CSStluafeD

Z-iHnoitaludoMCSSoN

TABLE 3B. PROGRAMMABLE VCO FREQUENCY FUNCTION TABLE (NOTE 1)

ycneuqerFOCV

)zHM(

091091 010111110

191191 010111111

291291 011000000

391391 011000001

• • •••••••••

• • •••••••••

805805 111111100

905905 111111101

015015 111111110

tnuoCM

6528214623618421

8M7M6M5M4M3M2M1M0M

.latsyrczHM61asemussA:1ETON

sedoMlanoitarepO

O/I_TSET

NdnaM,rotallicso,rotallicsO;ssapybLLP

1ETON.edomtsetsredivid

,edoMssapyBLLP

zHM1( ≤ klCtseT ≤ 1ETON;)zHM002

ICS8431CM-11 www.icst.com/products/hiperclocks.html REV. A JULY 11, 2001

3

Page 4

Integrated

Circuit

Systems, Inc.

L VPECL F

REQUENCY SYNTHESIZER

ICS8431-11

255MHZ, LOW JITTER,

ABSOLUTE MAXIMUM RATINGS

Supply Voltage 4.6V

Inputs -0.5V to VDD + 0.5V

Outputs -0.5V to VDDO + 0.5V

Ambient Operating T emperature 0°C to 85°C

Storage T emperature -65°C to 150°C

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings

are stress specifications only and functional operation of product at these condition or any conditions beyond those listed in

the

DC Characteristics

periods may affect product reliability.

or

AC Characteristics

is not implied. Exposure to absolute maximum rating conditions for extended

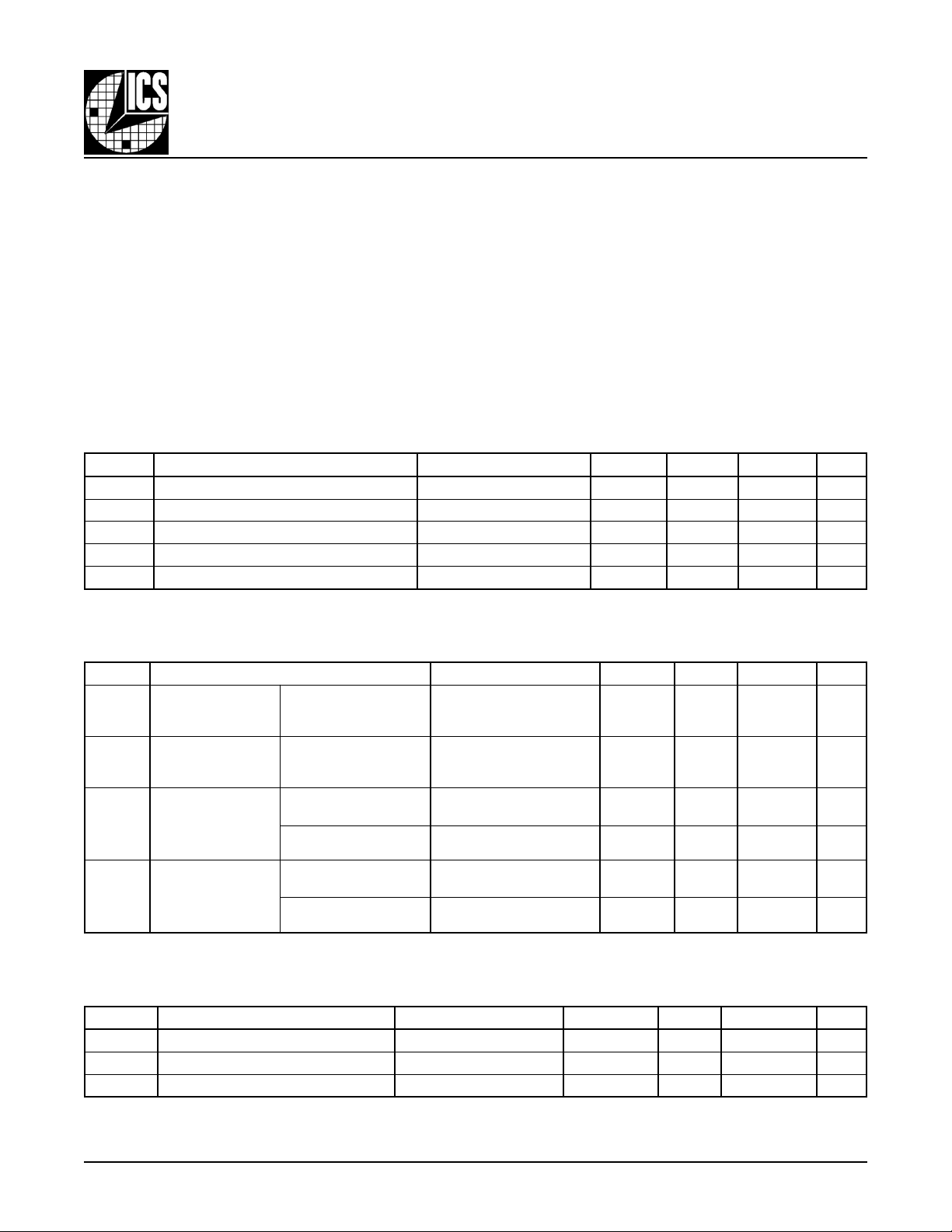

TABLE 4A. POWER SUPPLY DC CHARACTERISTICS, VDD = VDDA = VDDI = VDDO = 3.3V±5%, TA = 0°C TO 85°C

lobmySretemaraPsnoitidnoCtseTmuminiMlacipyTmumixaMstinU

DDVegatloVylppuSrewoP 531.33.3564.3V

ODDVegatloVylppuSrewoPtuptuO 531.33.3564.3V

ADDVegatloVylppuSrewoPgolanA 531.33.3564.3V

IDDVegatloVylppuSrewoPtupnI 531.33.3564.3V

EEI 041Am

TABLE 4B. LVCMOS / LVTTL DC CHARACTERISTICS, VDD = VDDA = VDDI = VDDO = 3.3V±5%, TA = 0°C TO 85°C

lobmySretemaraPsnoitidnoCtseTmuminiMlacipyTmumixaMstinU

,0LTC_CSS,8M:0M

HIVegatloVhgiHtupnI

LIVegatloVwoLtupnI

HIItnerruChgiHtupnI

LIItnerruCwoLtupnI

,6M:0M

,6M:0M

,RM,1LTC_CSS

DAOL_Pn,O/I_TSET

,0LTC_CSS,8M:0M

,RM,1LTC_CSS

DAOL_Pn,O/I_TSET

,0LTC_CSS,8M,7M

OI_TSET,1LTC_CSS

RM,DAOL_Pn

,0LTC_CSS,8M,7M

OI_TSET,1LTC_CSS

RM,DAOL_Pn

V531.3 ≤ DDV ≤ V564.32 3.0+DDVV

V531.3 ≤ DDV ≤ V564.33.0-8.0V

V564.3=NIV=DDV5Aµ

V564.3=NIV=DDV051Aµ

V0=NIV,V564.3=DDV051-Aµ

V0=NIV,V564.3=DDV5-Aµ

TABLE 4C. LVPECL DC CHARACTERISTICS, VDD = VDDA = VDDI = VDDO = 3.3V±5%, TA = 0°C TO 85°C

lobmySretemaraPsnoitidnoCtseTmuminiMlacipyTmumixaMstinU

HOV1ETON;egatloVhgiHtuptuO 82.1-ODDV89.0-ODDVV

LOVegatloVwoLtuptuO1ETON;0.2-ODDV7.1-ODDVV

GNIWSVgniwSegatloVtuptuOkaeP-ot-kaeP006007058Vm

05htiwdetanimrettuptuO:1ETON Ω .V2-ODDVot

ICS8431CM-11 www.icst.com/products/hiperclocks.html REV. A JULY 11, 2001

4

Page 5

Integrated

Circuit

Systems, Inc.

L VPECL F

REQUENCY SYNTHESIZER

ICS8431-11

255MHZ, LOW JITTER,

TABLE 5. CRYSTAL CHARACTERISTICS

retemaraPsnoitidnoCtseTmuminiMlacipyTmumixaMstinU

noitallicsOfoedoM latnemadnuF

ycneuqerF 0.61zHM

ecnareloTycneuqerF 05-05+mpp

ytilibatSycneuqerF 001-001+mpp

leveLevirD 001Wµ

)RSE(ecnatsiseRseireStnelaviuqE 05

ecnaticapaCtnuhS 37Fp

ecnaticapaCdaoL 018123Fp

ecnatcudnIniPseireS 37Hn

egnaRerutarepmeTgnitarepO 007C°

gnigAC°52@raeyreP5-5+mpp

TABLE 6. AC CHARACTERISTICS, VDD = VDDA = VDDI = VDDO = 3.3V±5%, TA = 0°C TO 85°C, 16MHZ CRYSTAL

Ω

lobmySretemaraPsnoitidnoCtseTmuminiMlacipyTmumixaMstinU

evaF4ETON;ycneuqerFtuptuOegarevA 057-057+mpp

t

j)cc(ti

cdo;elcyCytuDtuptuO2ETON7435%

Rt2,1ETON;emiTesiRtuptuO%08ot%02003054006sp

Ft2,1ETON;emiTllaFtuptuO%08ot%02003054006sp

latxF3ETON;egnaRtupnIlatsyrC416102zHM

mF

fmF

derCSS;noitcudeRlartcepS2,1ETON701Bd

ELBATSttuptuOkcolCelbatSotpu-rewoP 01sm

t

j.snoitinifed56DSEJCEDEJotmrofnoccdo,Ft,Rt,)cc(ti

2,1ETON

2,1ETON

2ETON;rettiJelcyC-ot-elcyC

;ycneuqerFnoitaludoMCSS

;rotcaFnoitaludoMCSS

.delbanegnikcolcmurtcepSdaerpS:1ETON

05htiwdetanimretstuptuO:2ETON Ω .V2-ODDVot

.egnargnitarepoOCVehtnihtiwdilavylnO:3ETON

.stnenopmoclatsyrclanretxetuohtiW:4ETON

zHM002=TUOF8103sp

53sp

0333.33zHK

4.06.0%

ICS8431CM-11 www.icst.com/products/hiperclocks.html REV. A JULY 11, 2001

5

Page 6

Integrated

Circuit

Systems, Inc.

PARAMETER MEASUREMENT INFORMATION

L VPECL F

ICS8431-11

255MHZ, LOW JITTER,

REQUENCY SYNTHESIZER

Clock Inputs

and Outputs

FOUT

nFOUT

80%

20%

➤

➤

trise tfall

FIGURE 1 — INPUT AND OUTPUT SLEW RATES

➤

t

cycle n

t

jit(cc) = tcycle n –tcycle n+1

➤

➤

FIGURE 2 — CYCLE-TO-CYCLE JITTER

80%

➤

t

cycle n+1

➤

Vswing

20%

➤

➤

➤

nFOUT

FOUT

Pulse Width (tPW)

t

t

PERIOD

PW

odc =

t

PERIOD

FIGURE 3 — odc & tPERIOD

ICS8431CM-11 www.icst.com/products/hiperclocks.html REV. A JULY 11, 2001

6

Page 7

Integrated

Circuit

Systems, Inc.

L VPECL F

REQUENCY SYNTHESIZER

ICS8431-11

255MHZ, LOW JITTER,

FUNCTIONAL DESCRIPTION

The ICS8431-11 features a fully integrated PLL and therefore requires no external components for setting the loop bandwidth.

A 16MHz series-resonant, fundamental crystal is used as the input to the on-chip oscillator . The output of the oscillator is divided by

16 prior to the phase detector. With a 16MHz crystal this provides a 1MHz reference frequency . The VCO of the PLL operates over

a range of 190 to 510MHz. The output of the loop divider is also applied to the phase detector .

The phase detector and the loop filter force the VCO output frequency to be M times the reference frequency by adjusting the

VCO control voltage. Note that for some values of M (either too high or too low) the PLL will not achieve lock. The output of the

VCO is scaled by a divider prior to being sent to the L VPECL output buffer . The divider provides a 50% output duty cycle.

The programmable features of the ICS8431-11 support four output operational modes and a programmable PLL loop divider .

The four output operational modes are spread spectrum clocking (SSC), non-spread spectrum clock and two test modes and

are controlled by the SSC_CTL[1:0] pins.

The PLL loop divider or M divider is programmed by using inputs M0 through M8. While the nP_LOAD input is held LOW , the

data present at M0:M8 is transparent to the M-divider. On the LOW -to-HIGH transition of nP_LOAD, the M0:M8 data is latched

into the M-divider and any further changes at the M0:M8 inputs will not be seen by the M-divider until the next LOW transition

on nP_LOAD.

The relationship between the VCO frequency, the crystal frequency and the loop counter/divider is defined as follows:

fxtal

fVCO =

The M count and the required values of M0:M8 for programming the VCO are shown in

Function T able. The frequency out is defined as follows:

16

x

M

T able 3B

, Programmable VCO Frequency

=

fVCO

FOUT

For the ICS8431-1 1, the output divider equals 2. V alid M values for which the PLL will achieve lock are defined as 190 ≤ M ≤ 510.

fxtal x M

=

2

32

ICS8431CM-11 www.icst.com/products/hiperclocks.html REV. A JULY 11, 2001

7

Page 8

Integrated

Circuit

Systems, Inc.

CRYSTAL INPUT AND OSCILLATOR INTERFACE

The ICS8431-11 features an internal oscillator that uses an

external quartz crystal as the source of its reference frequency.

A 16MHz crystal divided by 16 before being sent to the phase

detector provides the reference frequency. The oscillator is a

series resonant, multi-vibrator type design. This design provides

better stability and eliminates the need for large on chip capacitors.

Though a series resonant crystal is preferred, a parallel resonant

crystal can be used. A parallel resonant mode crystal used in a

series resonant circuit will exhibit a frequency of oscillation a few

hundred ppm lower than specified. A few hundred ppm translates

to KHz inaccuracy . In general computing applications this level

of inaccuracy is irrelevant. If better ppm accuracy is required, an

external capacitor can be added to a parallel resonant crystal in

series to pin 25.

Figure 1A

Figures 1A, 1B, and 1C show various crystal parameters

which are recommended only as guidelines. Figure 1A shows

how to interface a capacitor with a parallel resonant crystal.

Figure 1B

shows the capacitor value needed for the optimum

PPM performance over various parallel resonant crystals.

Figure 1C

shows the recommended tuning capacitance for a

various parallel resonant crystal.

shows how to interface with a crystal.

L VPECL F

ICS8431-11

FIGURE 1A. CRYSTAL INTERFACE

ICS8431-11

255MHZ, LOW JITTER,

REQUENCY SYNTHESIZER

XTAL2

(Pin 26, SOIC)

XTAL1

(Pin 25, SOIC)

➤

Optional

FIGURE 1B. Recommended tuning capacitance for various parallel

resonant crystals.

60

14.318

50

40

30

20

10

Series Capacitor, C1 (pF)

0

15.000

16.667

14 15 16 17 18 19 20 21 22 23 24 25

Crystal Frequency (MHz)

19.440

20.000

24.000

FIGURE 1C. Recommended tuning capacitance for various

parallel resonant crystal.

100

80

60

40

20

0

-20

0 102030405060

-40

-60

Frequency Accuracy ( ppm)

-80

-100

Series Capacitor, C1 (pF)

19.44MHz

16MHz

15.00MHz

ICS8431CM-11 www.icst.com/products/hiperclocks.html REV. A JULY 11, 2001

8

Page 9

Integrated

Circuit

Systems, Inc.

SPREAD SPECTRUM

Spread-spectrum clocking is a frequency modulation technique for EMI reduction. When spread-spectrum is enabled, a

30KHz triangle waveform is used with 0.5% down-spread

(+0.0% / -0.5%) from the nominal 200MHz clock frequency.

An example of a triangle frequency modulation profile is shown

Figure 2

in

• Fnom = Nominal Clock Frequency in Spread OFF mode

• Fm = Nominal Modulation Frequency (30KHz)

• δ = Modulation Factor (0.5% down spread)

(1 - δ) fnom + 2 fm x δ x fnom x t when 0 < t < ,

(1 - δ) fnom - 2 fm x δ x fnom x t when < t <

Fnom

below . The ramp profile can be expressed as:

(200MHz with 16MHz IN)

1

2 fm

➤

1

2 fm

1

fm

ICS8431-11

255MHZ, LOW JITTER,

L VPECL F

The ICS8431-11 triangle modulation frequency deviation will

not exceed 0.6% down-spread from the nominal clock frequency (+0.0% / -0.5%). An example of the amount of down

spread relative to the nominal clock frequency can be seen in

the frequency domain, as shown in

width to the fundamental frequency is typically 0.4%, and will

not exceed 0.6%. The resulting spectral reduction will be

greater than 7dB, as shown in Figure 3. It is important to note

the ICS8431-11 7dB minimum spectral reduction is the component-specific EMI reduction, and will not necessarily be the

same as the system EMI reduction.

REQUENCY SYNTHESIZER

Figure 3.

∆ − 10 dBm

The ratio of this

(1 - δ) Fnom

0.5/fm

FIGURE 2. TRIANGLE FREQUENCY MODULATION

1/fm

POWER SUPPLY FILTERING TECHNIQUES

As in any high speed analog circuitry, the power supply pins

are vulnerable to random noise. The ICS8431-11 provides

separate power supplies to isolate any high switching noise

from the outputs to the internal PLL. VDD, VDDI, VDDA, and

VDDO should be individually connected to the power supply

plane through vias, and bypass capacitors should be used

for each pin. To achieve optimum jitter performance, better

power supply isolation is required.

10Ω along with a 10µF and a .01µF bypass capacitor should

be connected to each power supply pin.

Figure 4

illustrates how a

➤

B

A

δ = .4%

FIGURE 3. 200MHZ CLOCK OUTPUT IN FREQUENCY DOMAIN

(A) SPREAD-SPECTRUM OFF

(B) SPREAD-SPECTRUM ON

3.3V

VDD

.01µF

VDDA

.01µF

FIGURE 4. POWER SUPPLY FILTERING

10Ω

10 µF

ICS8431CM-11 www.icst.com/products/hiperclocks.html REV. A JULY 11, 2001

9

Page 10

Integrated

Circuit

Systems, Inc.

TERMINATION FOR PECL OUTPUTS

The clock layout topology shown below is typical for

IA64/32 platforms. The two different layouts mentioned are

recommended only as guidelines.

FOUT and nFOUT are low impedance follower outputs that

generate ECL/PECL compatible outputs. Therefore, terminating resistors (DC current path to ground) or current sources

must be used for functionality. These outputs are designed to

ICS8431-11

255MHZ, LOW JITTER,

L VPECL F

drive 50Ω transmission lines. Matched impedance techniques

should be used to maximize operating frequency and minimize signal distortion. There are a few simple termination

schemes.

are recommended only as guidelines. Other suitable clock layouts may exist and it would be recommended that the board

designers simulate to guarantee compatibility across all printed

circuit and clock component process variations.

Figures 5A and 5B

REQUENCY SYNTHESIZER

show two different layouts which

3.3V

5

Z

o

2

Z

o

2

Z

o

2

3

Z

o

2

RTT =

(VOH + VOL / VCC –2) –2

Zo = 50Ω

= 50Ω

Z

o

50Ω

Zo = 50Ω

= 50Ω

Z

o

50Ω

➤

1

Z

o

FIGURE 5A. LVPECL OUTPUT TERMINATION

RTT

FINFOUT

VCC-2V

5

Zo = 50Ω Zo = 50Ω

FOUT FIN

Z

= 50Ω Zo = 50Ω

o

3

FIGURE 5B. LVPECL OUTPUT TERMINATION

LAYOUT GUIDELINE

The schematic of the ICS8431-11 layout example used in this layout guideline is shown in

PCB board layout for this example is shown in

Figure 6B.

This layout example is used as a general guideline. The layout in the actual

system will depend on the selected component types, the density of the components, the density of the traces, and the stacking of

the P .C. board.

U1

1

M0

2

M1

3

M2

4

M3

5

M4

6

M5

7

M6

8

M7

9

M8

10

SSC_CTL0

11

SSC_CTL1

12

GND

13

VDD

C1

0.1uF

TEST_IO

14 15

VDD GND

8431-11

nP_LOAD

VDDI

XTAL1

XTAL2

NC

NC

VDDA

NC

NC

NC

VDDO

FOUT

nFOUT

28

VDD

27

26

25

24

23

22

21

20

19

VDD

18

17

16

X1

C2

0.1uF

VDDA

C3

0.01uF

C6

0.01uF

R5

10

C4

10uF

Zo = 50 Ohm

TL1

Zo = 50 Ohm

TL2

Figure 6A.

Termination A

VDD0

R1

125

IN+

IN-

R2

84

The ICS8431-11 recommended

Termination

B (not shown

in the layout)

IN+

IN-

R3

125

R4

84

R1

R2

50

50

R3

50

FIGURE 6A. RECOMMENDED SCHEMAT IC LAYOUT

ICS8431CM-11 www.icst.com/products/hiperclocks.html REV. A JULY 11, 2001

10

Page 11

Integrated

Circuit

Systems, Inc.

L VPECL F

ICS8431-11

255MHZ, LOW JITTER,

REQUENCY SYNTHESIZER

The following component footprints are used in this layout

example:

All the resistors and capacitors are size 0603.

POWER AND GROUNDING

Place the decoupling capacitors C1, C2 and C3, C4, C5, C6 as

close as possible to the power pins. If space allows, placing the

decoupling capacitor at the component side is preferred. This can

reduce unwanted inductance between the decoupling capacitor

and the power pin generated by the via.

Maximize the pad size of the power (ground) at the decoupling

capacitor. Maximize the number of vias between power (ground)

and the pads. This can reduce the inductance between the power

(ground) plane and the component power (ground) pins.

If VDDA shares the same power supply with VDD, insert the RC

filter R5, C3, and C4 in between. Place this RC filter as close to

the VDDA as possible.

CLOCK TRACES AND TERMINATION

The component placements, locations and orientations should

be arranged to achieve the best clock signal quality . Poor clock

signal quality can degrade the system performance or cause

system failure. In the synchronous high-speed digital system,

the clock signal is less tolerable to poor signal quality than other

signals. Any ringing on the rising or falling edge or excessive ring

back can cause system failure. The trace shape and the trace

delay might be restricted by the available space on the board and

the component location. While routing the traces, the clock signal

traces should be routed first and should be locked prior to routing

other signals traces.

• The traces with 50Ω transmission lines TL1 and TL2 at

FOUT and nFOUT should have equal delay and run adjacent to each other. Avoid sharp angles on the clock trace.

Sharp angle turns cause the characteristic impedance to

change on the transmission lines.

• Keep the clock trace on same layer. Whenever possible,

avoid any vias on the clock traces. Any via on the trace

can affect the trace characteristic impedance and hence

degrade signal quality.

• To prevent cross talk, avoid routing other signal traces in

parallel with the clock traces. If running parallel traces is

unavoidable, allow more space between the clock trace

and the other signal trace.

• Make sure no other signal trace is routed between the

clock trace pair.

The matching termination resistors R1, R2, R3 and R4 should be

located as close to the receiver input pins as possible. Other termination scheme can also be used but is not shown in this example.

CRYSTAL

The crystal X1 should be located as close as possible to the pins

26 (XTAL1) and 25 (XTAL2). The trace length between the X1

and U1 should be kept to a minimum to avoid unwanted parasitic

inductance and capacitance. Other signal traces should not be

routed near the crystal traces.

U1

ICS8431-11

C6

X1

C3

C1

FIGURE 6B. PCB BOARD LAYOUT FOR ICS8431-11

ICS8431CM-11 www.icst.com/products/hiperclocks.html REV. A JULY 11, 2001

C4

R5

C2

TL1 (50 Ohm)

TL2 (50 Ohm)

11

IN+

IN-

GND

VDD

Signals

VIA

Close to the input

pins of the

receiver

R1

R2

R3

R4

Page 12

Integrated

Circuit

Systems, Inc.

PACKAGE OUTLINE - M SUFFIX

L VPECL F

ICS8431-11

255MHZ, LOW JITTER,

REQUENCY SYNTHESIZER

E

h x 45º

C

H

A

A1

N

1528

1

D

A2

e

14

B

TABLE 7. PACKAGE DIMENSIONS

LOBMYS

N82

A--56.2--401.0

1A01.0--0400.0--

2A50.255.2180.0001.0

B33.015.0310.0020.0

C81.023.0700.0310.0

D07.7104.81796.0427.0

E04.706.7192.0992.0

eCISAB72.1CISAB050.0

H00.0156.01493.0914.0

h52.057.0010.0920.0

L04.072.1610.0050.0

α

NIMXAMNIMXAM

°0 °8 °0 °8

sretemilliMsehcnI

SEATING

PLANE

.10 (.004)

L

α

REFERENCE DOCUMENT: JEDEC PUBLICATION 95, MS-013, MO-1 19

ICS8431CM-11 www.icst.com/products/hiperclocks.html REV. A JULY 11, 2001

12

Page 13

Integrated

Circuit

Systems, Inc.

TABLE 8. ORDERING INFORMATION

rebmuNredrO/traPgnikraMegakcaPtnuoCerutarepmeT

11-MC1348SCI11-MC1348SCICIOSdaeL82ebuTreP62C°07otC°0

T11-MC1348SCI11-MC1348SCIleeRdnaepaTnoCIOSdaeL820001C°07otC°0

L VPECL F

ICS8431-11

255MHZ, LOW JITTER,

REQUENCY SYNTHESIZER

While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems, Incorporated (ICS) assumes no responsibility for either its use

or for infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use

in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are

not recommended without additional processing by ICS. ICS reserves the right to change any circuitry or specifications without notice. ICS does not authorize or warrant any ICS

product for use in life support devices or critical medical instruments.

ICS8431CM-11 www.icst.com/products/hiperclocks.html REV. A JULY 11, 2001

13

Loading...

Loading...