Page 1

DATA SH EET

Product specification

File under Integrated Circuits, IC04

January 1995

INTEGRATED CIRCUITS

HEF4557B

LSI

1-to-64 bit variable length shift

register

For a complete data sheet, please also download:

•The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

•The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

Page 2

January 1995 2

Philips Semiconductors Product specification

1-to-64 bit variable length shift register

HEF4557B

LSI

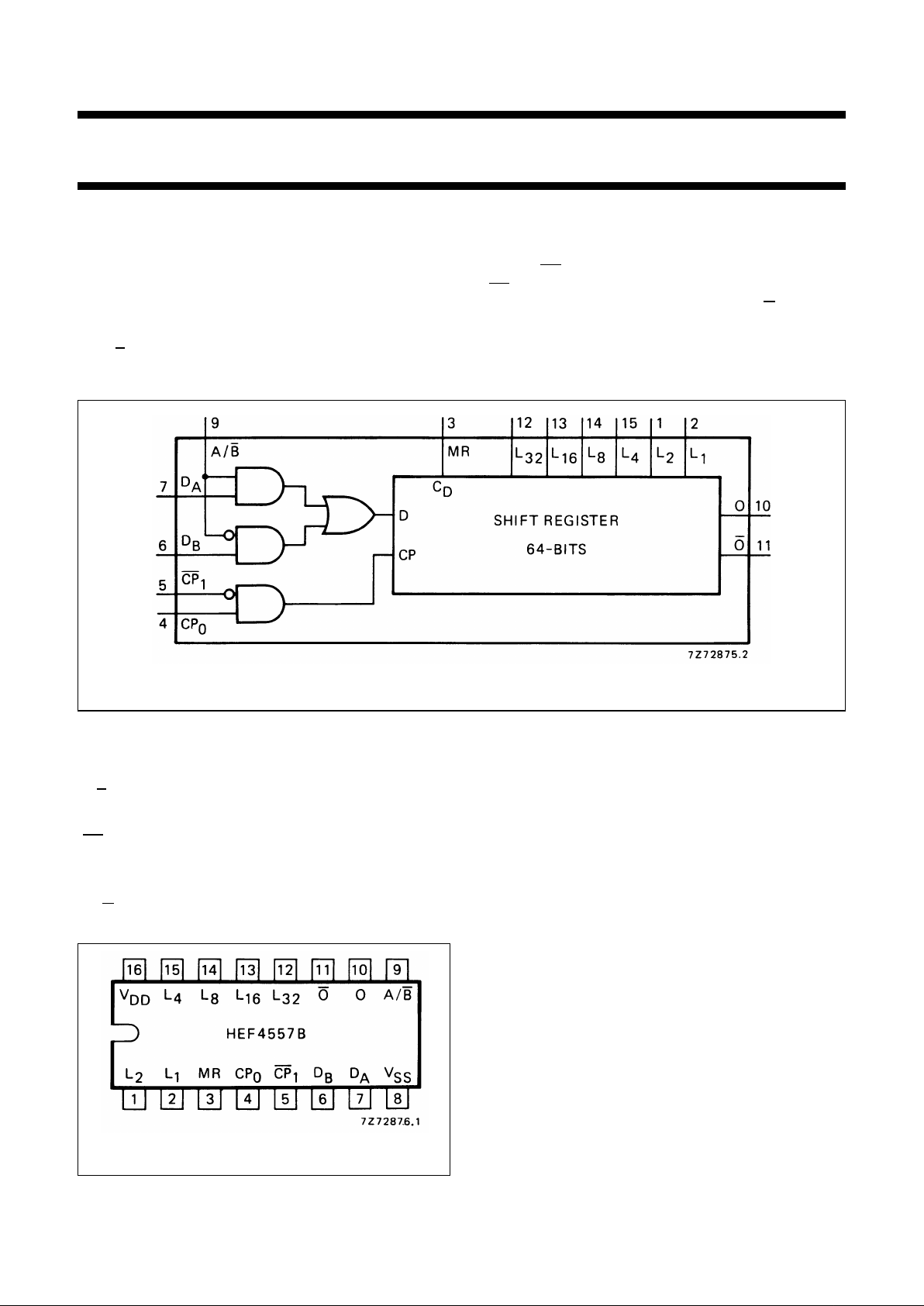

DESCRIPTION

The HEF4557B is a static clocked serial shift register

whose length may be programmed to be any number of

bits between 1 and 64. The number of bits selected is

equal to the sum of the subscripts of the enabled length

control inputs (L1, L2, L4, L8, L16and L32) plus one. Serial

data may be selected from the DAor DBdata inputs with

the A/B select input. This feature is useful for recirculation

purposes. Information on D

A

or DBis shifted into the first

register position and all the data in the register is shifted

one position to the right on the LOW to HIGH transition of

CP0while CP1is LOW or on the HIGH to LOW transition

of CP1while CP0is HIGH. A HIGH on master reset (MR)

resets the register and forces O to LOW and O to HIGH,

independent of the other inputs.

Fig.1 Functional diagram.

PINNING

D

A

, D

B

data inputs

A/

B select data input

CP

0

clock input

CP

1

clock enable input

MR asynchronous master reset

L

1

to L

32

bit-length control inputs

O,

O buffered outputs

Fig.2 Pinning diagram.

FAMILY DATA, IDDLIMITS category LSI

See Family Specifications

HEF4557BP(N): 16-lead DIL; plastic

(SOT38-1)

HEF4557BD(F): 16-lead DIL; ceramic (cerdip)

(SOT74)

HEF4557BT(D): 16-lead SO; plastic

(SOT109-1)

( ): Package Designator North America

Page 3

January 1995 3

Philips Semiconductors Product specification

1-to-64 bit variable length shift register

HEF4557B

LSI

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

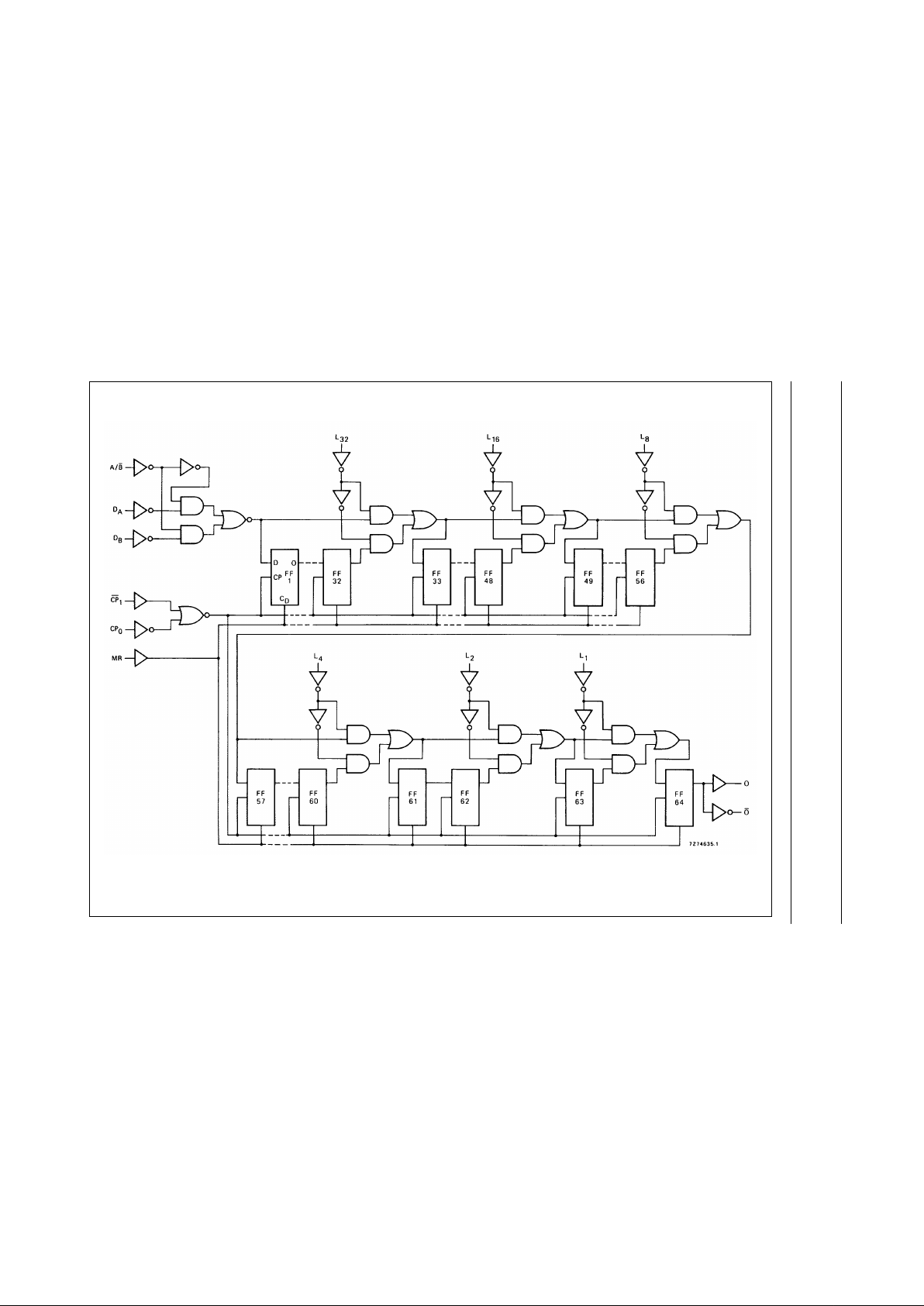

Fig.3 Logic diagram.

Page 4

January 1995 4

Philips Semiconductors Product specification

1-to-64 bit variable length shift register

HEF4557B

LSI

FUNCTION TABLE

INPUTS OUTPUT

MR A/BDADBCP

O

CP

1

O

(1)

LLD

1

D

2

LD

2

LHD

1

D

2

LD

1

LLD

1

D

2

HD

2

LHD

1

D

2

HD

1

HXXX X X L

Notes

1. The moment Dnappears at O depends on the

bit-length shown in the table below.

2. H = HIGH state (the more positive voltage)

3. L = LOW state (the less positive voltage)

4. X = state is immaterial

5. = positive-going transition

6. = negative-going transition

7. Dn= either HIGH or LOW

BIT-LENGTH SELECT FUNCTION TABLE

AC CHARACTERISTICS

V

SS

= 0 V; T

amb

=25°C; input transition times ≤ 20 ns

L

32

L

16

L

8

L

4

L

2

L

1

REGISTER LENGTH

LLLLLL 1-bit

LLLLLH 2-bits

L L L L H L 3-bits

L L L L H H 4-bits

L L L H L L 5-bits

L L L H L H 6-bits

L L L H H L 7-bits

L L L H H H 8-bits

↓↓↓↓↓↓ ↓

LHHHHH 32-bits

HLLLLL 33-bits

HLLLLH 34-bits

↓↓↓↓↓↓ ↓

H H H H L L 61-bits

H H H H L H 62-bits

HHHHHL 63-bits

HHHHHH 64-bits

V

DD

V

TYPICAL FORMULA FOR P (µW)

Dynamic power 5 3 500 f

i

+∑(foCL) × V

DD

2

where

dissipation per 10 15 000 f

i

+∑(foCL) × V

DD

2

fi= input freq. (MHz)

package (P) 15 37 000 f

i

+∑(foCL) × V

DD

2

fo= output freq. (MHz)

C

L

= load capacitance (pF)

∑ (f

oCL

) = sum of outputs

V

DD

= supply voltage (V)

Page 5

January 1995 5

Philips Semiconductors Product specification

1-to-64 bit variable length shift register

HEF4557B

LSI

AC CHARACTERISTICS

V

SS

= 0 V; T

amb

=25°C; CL= 50 pF; input transition times ≤20 ns

Interpolation table (see note next page)

Notes

1. H = HIGH state (the more positive voltage)

2. L = LOW state (the less positive voltage)

3. X = state is immaterial

V

DD

V

SYMBOL TYP. MAX.

TYPICAL EXTRAPOLATION

FORMULA

Propagation delays

CP0, CP1→ O, O 5 240 480 ns 213 ns + (0,55 ns/pF) C

L

HIGH to LOW 10 t

PHL

90 180 ns 79 ns + (0,23 ns/pF) C

L

15 65 130 ns 57 ns + (0,16 ns/pF) C

L

5 240 480 ns 213 ns + (0,55 ns/pF) C

L

LOW to HIGH 10 t

PLH

90 180 ns 79 ns + (0,23 ns/pF) C

L

15 65 130 ns 57 ns + (0,16 ns/pF) C

L

MR → O 5 170 340 ns 143 ns + (0,55 ns/pF) C

L

HIGH to LOW 10 t

PHL

80 160 ns 69 ns + (0,23 ns/pF) C

L

15 60 120 ns 52 ns + (0,16 ns/pF) C

L

MR → O 5 140 280 ns 113 ns + (0,55 ns/pF) C

L

LOW to HIGH 10 t

PLH

70 140 ns 59 ns + (0,23 ns/pF) C

L

15 55 110 ns 47 ns + (0,16 ns/pF) C

L

Output transition times 5 60 120 ns 10 ns + (1,0 ns/pF) C

L

HIGH to LOW 10 t

THL

30 60 ns 9 ns + (0,42 ns/pF) C

L

15 20 40 ns 6 ns + (0,28 ns/pF) C

L

5 60 120 ns 10 ns + (1,0 ns/pF) C

L

LOW to HIGH 10 t

TLH

30 60 ns 9 ns + (0,42 ns/pF) C

L

15 20 40 ns 6 ns + (0,28 ns/pF) C

L

LENGTH CONTROL INPUTS MINIMUM

NUMBER OF

BITS SELECTED

SET-UP, HOLD,

RECOVERY

TIMES

L

1

L

2

L

4

L

8

L

16

L

32

L L L L L L 1 specified

HLLLLL 2

XHLLLL 3

X X H L L L 5 six equal steps

XXXHLL 9

XXXXHL 17

X X X X X H 33 specified

Page 6

January 1995 6

Philips Semiconductors Product specification

1-to-64 bit variable length shift register

HEF4557B

LSI

AC CHARACTERISTICS

V

SS

= 0 V; T

amb

=25°C; CL= 50 pF; input transition times ≤20 ns; see also waveforms Fig.4

Note

1. The set-up, hold and recovery times vary with the minimum number of bits selected. For other values as specified

one may interpolate as shown in the table (see previous page).

V

DD

V

SYMBOL MIN. TYP.

Minimum clock

pulse width; 5 t

WCPL

180 90 ns

LOW for CP

0

or 10 or 60 30 ns

HIGH for

CP

1

15 t

WCPH

40 20 ns

Minimum reset 5 150 75 ns

pulse width; 10 t

WMRH

70 35 ns

HIGH 15 50 25 ns

Set-up times

see note

D

A

, DB, A/B → CP0, 5 360 180 ns

CP

1

10 t

su

140 70 ns

L

1

to L32= LOW 15 90 45 ns

540−20 ns

L

32

= HIGH 10 t

su

35 −10 ns

15 30 −5ns

Hold times

D

A

, DB, A/B → CP0,5 −40 −110 ns

CP

1

10 t

hold

−10 −45 ns

L

1

to L32= LOW 15 0 −30 ns

59030ns

L

32

= HIGH 10 t

hold

60 20 ns

15 50 15 ns

Recovery times for MR 5 500 250 ns

L

1

to L32= LOW 10 t

RMR

250 125 ns

15 150 75 ns

5 110 50 ns

L

32

= HIGH 10 t

RMR

70 30 ns

15 60 25 ns

Minimum clock 5 2,5 5 MHz

pulse frequency 10 f

max

7 14 MHz

15 10 20 MHz

Page 7

January 1995 7

Philips Semiconductors Product specification

1-to-64 bit variable length shift register

HEF4557B

LSI

Fig.4 Waveforms showing recovery time for MR and minimum CP0, CP1and MR pulse widths, set-up and hold

times for DA, DBand A/B to CP0and CP1. Set-up and hold times are shown as positive values but may

be specified as negative values.

Loading...

Loading...